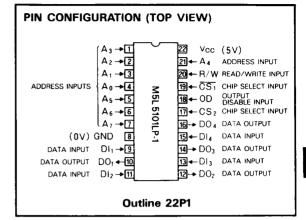

# M5L 5101LP-1

## 1024-BIT (256-WORD BY 4-BIT) CMOS STATIC RAM

#### DESCRIPTION

This is a 256-word by 4-bit static RAM fabricated with the silicon-gate CMOS process and designed for low power dissipation and easy application of battery back-up.

The device has two chip-select inputs  $\overline{CS}_1$  and  $CS_2$ . While maintained in the chip non-select state, the device consumes power at the low value of only 1µA (max) standby current and accordingly is especially suitable as a memory system for battery-operated applications and for battery back-up.

The device operates on a single 5V supply, as does TTL, and inputs and outputs are directly TTL-compatible and are provided with common I/O terminals.

#### **FEATURES**

Access time:

450ns (max)

Low power dissipation in the standby mode:

5nW/bit (max)

- Single 5V power supply

- Data holding at 2V supply voltage

- No external clock or refreshing operation required

- Both inputs and outputs are directly TTL-compatible

- Outputs are three-state, with OR-tie capability

- Simple memory expansion by chip-select signals

- Input and output data terminals are separate

- Interchangeable with Intel's 5101L-1 in pin configuration and electrical characteristics

#### APPLICATION

Battery-driven or battery back-up small-capacity memory units

#### **FUNCTION**

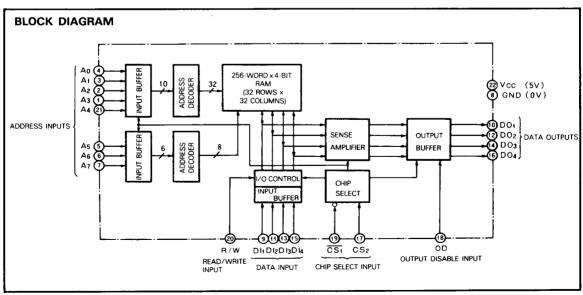

The device provides separate data input and output terminals.

During a write cycle, when a location is designated by address signals A<sub>0</sub>~A<sub>7</sub> and signal R/W goes low, the data of the DI inputs at that time is written.

During a read cycle, when a location is designated by address signals A<sub>0</sub>~A<sub>7</sub>, and signal R/W goes high, the data of the designated address is available at the DO terminals.

When signal  $\overline{CS}_1$  is high or  $CS_2$  is low, the chip is in the non-selectable state, disabling both reading and writing. In this case, the output is in the floating (high-impedance state) useful for OR-ties with the output terminals of other

When the signal OD is high, the output is in the floating state, so that OD is used as an input/output select control signal for common input/output operation.

The memory data can be held at a supply voltage of 2V, enabling battery back-up operation during power failure and power-down operation in the standby mode.

M5L 5101LP-1

# 1024-BIT (256-WORD BY 4-BIT) CMOS STATIC RAM

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                                    | Conditions          | Limits                    | Unit           |  |

|--------|----------------------------------------------|---------------------|---------------------------|----------------|--|

| Vcc    | Supply voltage                               |                     | -0.3~7                    | V              |  |

| Vı     | Input voltage                                | With respect to GND | -0.3~V <sub>CC</sub> +0.3 | T v            |  |

| ٧o     | Output voltage                               |                     | 0~Vcc                     | - <del>'</del> |  |

| Pd     | Maximum power dissipation                    | Ta = 25°C           | 700                       | mW             |  |

| Topr   | Operating free-air ambient temperature range |                     | 0~70                      | ***            |  |

| Tstg   | Storage temperature range                    |                     | -40~125                   |                |  |

# **RECOMMENDED OPERATING CONDITIONS** ( $Ta = 0 \sim 70 ^{\circ}C$ , unless otherwise noted)

| Symbol | Parameter                |      | Limits |      |      |

|--------|--------------------------|------|--------|------|------|

|        |                          | Min  | Nom    | Max  | Ųnit |

| Vcc    | Supply voltage           | 4.5  | 5      | 5.5  |      |

| Vss    | Supply voltage           | 0    | 0      | 0    |      |

| VIL    | Low-level input voltage  | -0.3 |        | 0.65 | ·    |

| ViH    | High-level input voltage | 2.2  |        | Vcc  |      |

# **ELECTRICAL CHARACTERISTICS** ( $Ta = 0 \sim 70\, ^{\circ}\text{C}$ . $V_{CC} = 5 \text{V} \pm 10\, ^{\circ}\text{M}$ , unless otherwise noted)

| Symbol | Parameter                           | Tost senditions                                                                 | Limits |     |      |          |

|--------|-------------------------------------|---------------------------------------------------------------------------------|--------|-----|------|----------|

|        | Test conditions                     | Min                                                                             | Тур    | Max | Unit |          |

| VIH    | High-level input voltage            |                                                                                 | 2.2    |     | Vcc  |          |

| VIL    | Low-level input voltage             |                                                                                 | -0.3   |     | 0.65 |          |

| Vон    | High-level output voltage           | $I_{OH} = -1mA$                                                                 |        |     | 0.4  | <u>·</u> |

| VoL    | Low-level output voltage            | I <sub>OL</sub> = 2 mA                                                          | 2.4    | _   | 0.4  | Ť        |

| lı .   | Input current                       | V <sub>1</sub> = 0 ~ 5.5V                                                       |        |     | ±1   | μА       |

| lozн   | Off-state high-level output current | $V_{1(\overline{CS1})} = 2.2V, V_0 = 2.4V \sim V_{CC}$                          | +      |     |      | μΑ       |

| lozL   | Off-state low-level output current  | $V_{1}(\overline{CS1}) = 2.2V, V_{0} = 0.4V$                                    |        |     | -1   | μΑ       |

| 1001   | Supply current from V <sub>CC</sub> | $\overline{CS}$ 1 $\leq$ 0.01V, other inputs = V <sub>CC</sub> ,<br>Output open |        | 9   | 22   | mA       |

| 1002   | Supply current from VCC             | $\overline{CS}_1 \leq 0.01V$ , other inputs = 2.2V,<br>Output open              |        | 13  | 27   | mA       |

| I CC3  | Supply current from VCC             | CS <sub>2</sub> ≤0.2V                                                           |        |     | 1    | μΑ       |

| Cı     | Input capacitance, all inputs       | V <sub>1</sub> = GND, V <sub>1</sub> = 25mVrms, f = 1MHz                        | 1 -    | 4   | - 8  | pF       |

| Co     | Output capacitance                  | V <sub>0</sub> =GND, V <sub>0</sub> = 25mVrms, f = 1MHz                         | +      | 8   | 12   | pF       |

Note 1: Current flowing into an IC is positive; out is negative.

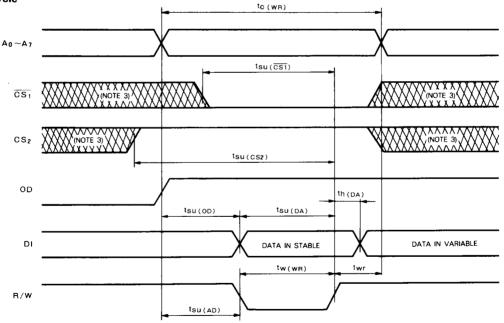

# TIMING REQUIREMENTS (For Write Cycle) ( $T_a = 0 \sim 70 \, \text{C}$ , $V_{CC} = 5 \text{V} \pm 10 \%$ , unless otherwise noted)

| Symbol    | Parameter                                      | Alt.            | Test conditions               | Limits | Unit |     |      |

|-----------|------------------------------------------------|-----------------|-------------------------------|--------|------|-----|------|

|           |                                                | symbol          |                               | Min    | Тур  | Max | Orin |

| tc (WR)   | Write cycle time                               | twc             |                               | 450    |      |     | ns   |

| tw(WR)    | Write pulse width                              | twp             | Input pulse                   | 250    |      |     | ns   |

| tsu (AD)  | Address setup time with respect to write pulse | taw             | V <sub>IH</sub> =2.2V         | 130    |      |     | ns   |

| twr       | Write recovery time                            | twn             | V <sub>IL</sub> =0.65V        | 50     |      | +   | ns   |

| tsu (OD)  | OD setup time with respect to data-in          | tos             | $t_f = t_f = 20$ ns           | 130    |      |     | ns   |

| tsu (DA)  | Data setup time                                | t <sub>DW</sub> | Reference level = 1.5V        | 250    |      |     | ns   |

| th (DA)   | Data hold time                                 | t <sub>DH</sub> | Load = $1TTL$ , $C_L = 100pF$ | 50     |      |     | ns   |

| tsu (CS1) | Chip select setup time                         | tcwı            | = . 4 C 100p.                 | 350    |      |     | ns   |

| tsu (CS2) | Chip select setup time                         | tcwz            |                               | 350    |      |     | ns   |

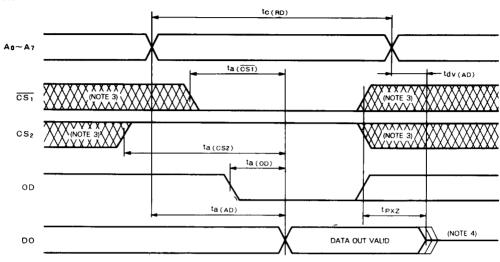

# SWITCHING CHARACTERISTICS (For Read Cycle) (Ta = 0 $\sim$ 70°C. V<sub>CC</sub>=5V $\pm$ 10%, unless without noted)

| Symbol   | Parameter                               | Alt. Test conditions | Limits                                                                                                                              |     |     | 11-4 |      |

|----------|-----------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

|          |                                         | symbol               | - Took delikations                                                                                                                  | Min | Тур | Max  | Unit |

| to(RD)   | Read cycle time                         | t <sub>RC</sub>      | Input pulse  V <sub>IH</sub> =2.2V  V <sub>IL</sub> =0.65V  tr=tf=20ns  Reference level = 1.5V  Load = 1TTL . C <sub>L</sub> =100pF | 450 |     | -    | ns   |

| ta(AD)   | Address access time                     | tA                   |                                                                                                                                     |     |     | 450  | ns   |

| ta (CSI) | Chip select access time                 | t <sub>CO1</sub>     |                                                                                                                                     |     |     | 400  | ns   |

| ta (CS2) | Chip select access time                 | t <sub>CO2</sub>     |                                                                                                                                     |     |     | 500  | ns   |

| ta (OD)  | OD access time                          | top                  |                                                                                                                                     |     |     | 250  | ns   |

| tpxz     | Output disable time (note 2)            | t <sub>DF</sub>      |                                                                                                                                     | _   |     | 130  | ns   |

| tdv (AD) | Data valid time with respect to address | t <sub>OH1</sub>     |                                                                                                                                     | 0   |     |      | ns   |

Note 2 :  $t_{PXZ}$  is from  $\overline{CS_1}$ .  $CS_2$  or OD, whichever occurs first.

### 1024-BIT (256-WORD BY 4-BIT) CMOS STATIC RAM

#### TIMING DIAGRAMS Read Cycle

### Write Cycle

- Note 3: Hatching indicates the state is unknown.

- 4 : Indicates that during this period the data-out is invalid for this definition of tdv(AD) and is in the floating state for this definition of tpxz.

# 1024-BIT (256-WORD BY 4-BIT) CMOS STATIC RAM

#### **POWER-DOWN OPERATION**

Electrical Characteristics (Ta=0~70°C, unless otherwise noted)

| C                    | D                                    | Test conditions                        |         | Limits |     |      |

|----------------------|--------------------------------------|----------------------------------------|---------|--------|-----|------|

| Symbol               | Parameter                            |                                        | Min     | Тур    | Max | Unit |

| V <sub>CC</sub> (PD) | Power-down supply voltage            |                                        | 2       |        |     | V    |

|                      |                                      | 2.2V≤Vcc(PD)≤Vcc                       | 2.2     |        |     | ٧    |

| Vi(CS)               | Power down chip select input voltage | 2 V ≨ V <sub>CC</sub> (PD) ≨ 2.2 V     | VCC(PD) |        |     | ٧    |

| I CC(PD)             | Power-down supply current from VCC   | V <sub>CC</sub> =2 V, all inputs = 2 V |         |        | 1   | μА   |

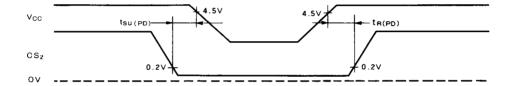

### Timing Requirements (Ta = 0 $\sim$ 70°C, VCC = 5 V $\pm$ 10 %. unless otherwise noted)

| Symbol  | Parameter                |        | Unit |     |      |

|---------|--------------------------|--------|------|-----|------|

|         |                          | Min    | Тур  | Max | Onit |

| tsu(PD) | Power-down setup time    | 0      |      |     | ns   |

| t R(PD) | Power-down recovery time | tc(RD) |      |     | ns   |

### **Timing Diagram**