# Universal LCD driver for low multiplex rates

PCF8566

|                 |                                         |        |                                                 |

|-----------------|-----------------------------------------|--------|-------------------------------------------------|

| <b>CONTENTS</b> |                                         |        |                                                 |

| 1               | FEATURES                                | 8      | LIMITING VALUES                                 |

| 2               | GENERAL DESCRIPTION                     | 9      | HANDLING                                        |

| 3               | ORDERING INFORMATION                    | 10     | DC CHARACTERISTICS                              |

| 4               | BLOCK DIAGRAM                           | 11     | AC CHARACTERISTICS                              |

| 5               | PINNING                                 | 12     | APPLICATION INFORMATION                         |

| 6               | FUNCTIONAL DESCRIPTION                  | 13     | CHIP DIMENSIONS AND BONDING PAD LOCATIONS       |

| 6.1             | Power-on reset                          | 14     | PACKAGE OUTLINES                                |

| 6.2             | LCD bias generator                      | 15     | SOLDERING                                       |

| 6.3             | LCD voltage selector                    | 15.1   | Introduction                                    |

| 6.4             | LCD drive mode waveforms                | 15.2   | DIP                                             |

| 6.5             | Oscillator                              | 15.2.1 | Soldering by dipping or by wave                 |

| 6.6             | Internal clock                          | 15.2.2 | Repairing soldered joints                       |

| 6.7             | External clock                          | 15.3   | SO and VSO                                      |

| 6.8             | Timing                                  | 15.3.1 | Reflow soldering                                |

| 6.9             | Display latch                           | 15.3.2 | Wave soldering                                  |

| 6.10            | Shift register                          | 15.3.3 | Repairing soldered joints                       |

| 6.11            | Segment outputs                         | 16     | DEFINITIONS                                     |

| 6.12            | Backplane outputs                       | 17     | LIFE SUPPORT APPLICATIONS                       |

| 6.13            | Display RAM                             | 18     | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS |

| 6.14            | Data pointer                            |        |                                                 |

| 6.15            | Subaddress counter                      |        |                                                 |

| 6.16            | Output bank selector                    |        |                                                 |

| 6.17            | Input bank selector                     |        |                                                 |

| 6.18            | Blinker                                 |        |                                                 |

| 7               | I <sup>2</sup> C-BUS DESCRIPTION        |        |                                                 |

| 7.1             | Bit transfer                            |        |                                                 |

| 7.2             | Start and stop conditions               |        |                                                 |

| 7.3             | System configuration                    |        |                                                 |

| 7.4             | Acknowledge                             |        |                                                 |

| 7.5             | PCF8566 I <sup>2</sup> C-bus controller |        |                                                 |

| 7.6             | Input filters                           |        |                                                 |

| 7.7             | I <sup>2</sup> C-bus protocol           |        |                                                 |

| 7.8             | Command decoder                         |        |                                                 |

| 7.9             | Display controller                      |        |                                                 |

| 7.10            | Cascaded operation                      |        |                                                 |

# Universal LCD driver for low multiplex rates

PCF8566

## 1 FEATURES

- Single-chip LCD controller/driver

- Selectable backplane drive configuration: static or 2, 3 or 4 backplane multiplexing

- Selectable display bias configuration: static,  $\frac{1}{2}$  or  $\frac{1}{3}$

- Internal LCD bias generation with voltage-follower buffers

- 24 segment drives: up to twelve 8-segment numeric characters; up to six 15-segment alphanumeric characters; or any graphics of up to 96 elements

- $24 \times 4$ -bit RAM for display data storage

- Auto-incremented display data loading across device subaddress boundaries

- Display memory bank switching in static and duplex drive modes

- Versatile blinking modes

- LCD and logic supplies may be separated

- 2.5 to 6 V power supply range

- Low power consumption

- Power saving mode for extremely low power consumption in battery-operated and telephone applications

- I<sup>2</sup>C-bus interface

- TTL/CMOS compatible

- Compatible with any 4-bit, 8-bit or 16-bit microprocessors/microcontrollers

- May be cascaded for large LCD applications (up to 1536 segments possible)

- Cascadable with the 40 segment LCD driver PCF8576C

- Optimized pinning for single plane wiring in both single and multiple PCF8566 applications

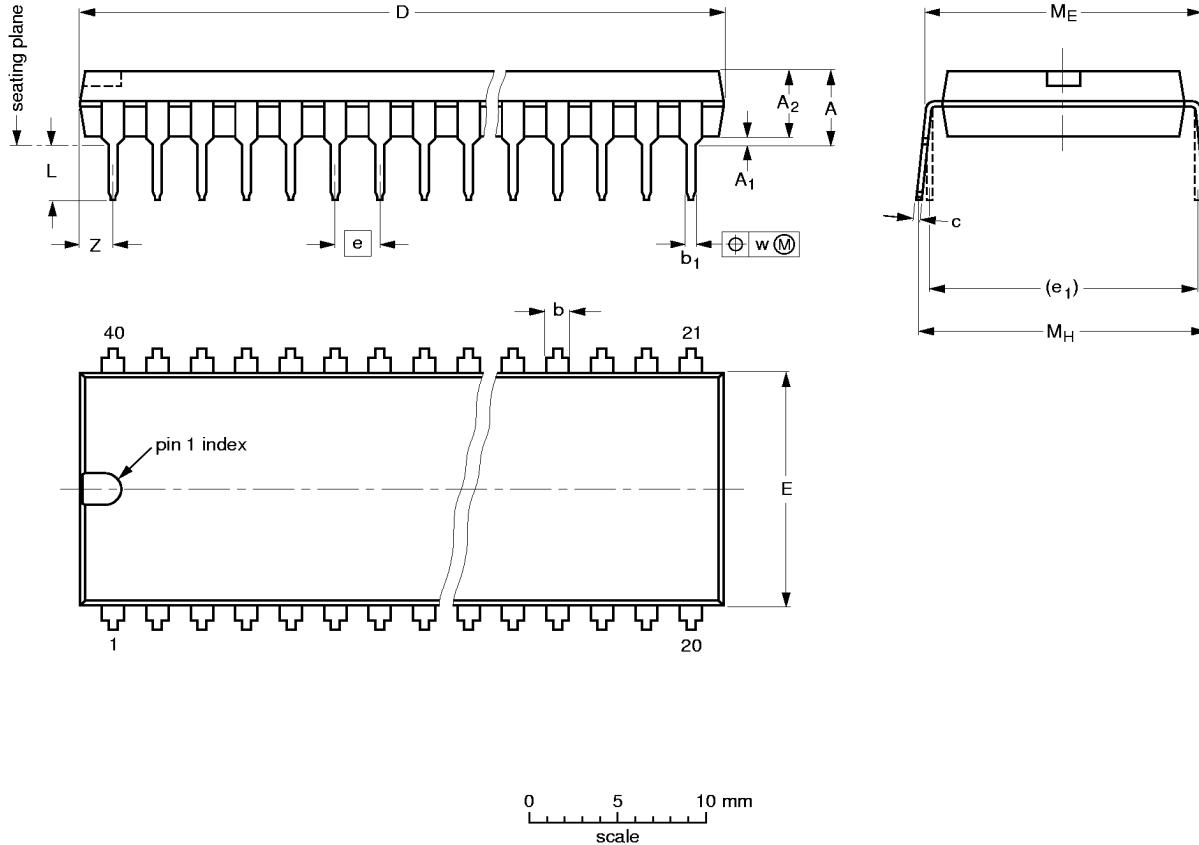

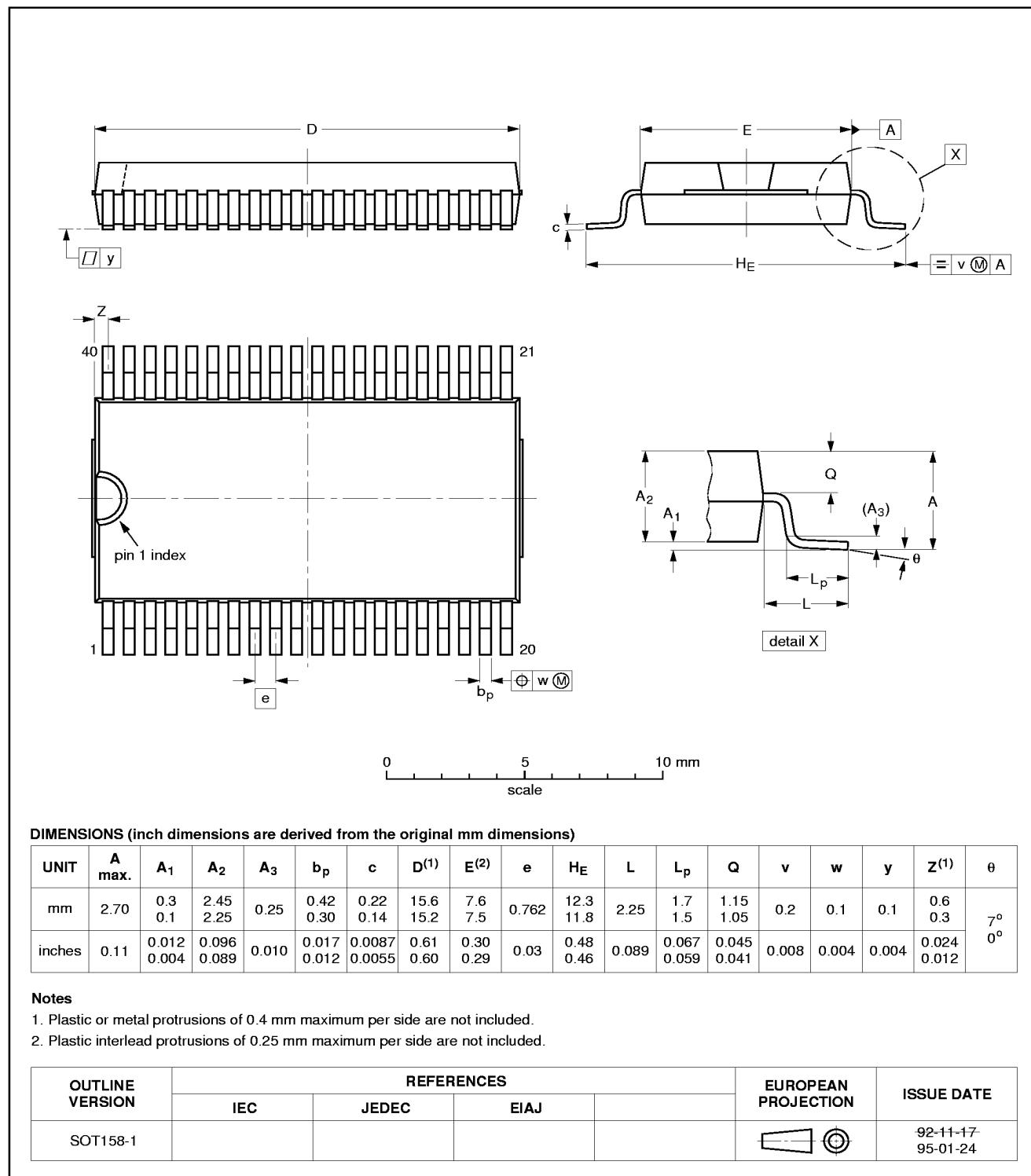

- Space-saving 40 lead plastic very small outline package (VSO40; SOT158-1)

- No external components required (even in multiple device applications)

- Manufactured in silicon gate CMOS process.

## 3 ORDERING INFORMATION

| TYPE NUMBER | PACKAGE |                                                  |          |

|-------------|---------|--------------------------------------------------|----------|

|             | NAME    | DESCRIPTION                                      | VERSION  |

| PCF8566P    | DIP40   | plastic dual in-line package; 40 leads (600 mil) | SOT129-1 |

| PCF8566T    | VSO40   | plastic very small outline package; 40 leads     | SOT158-1 |

# Universal LCD driver for low multiplex rates

PCF8566

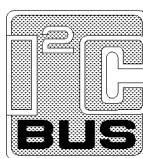

## 4 BLOCK DIAGRAM

Fig.1 Block diagram.

# Universal LCD driver for low multiplex rates

PCF8566

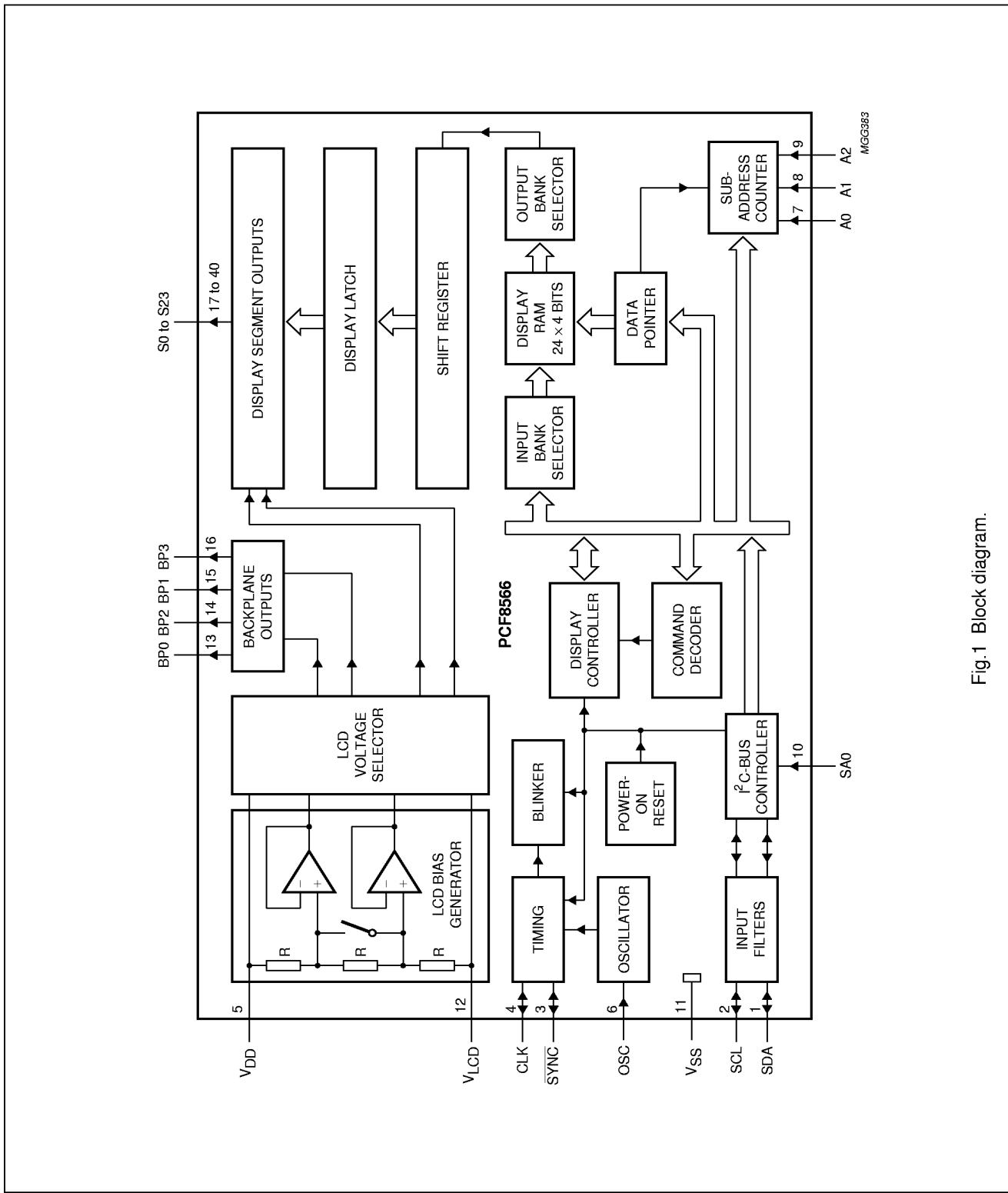

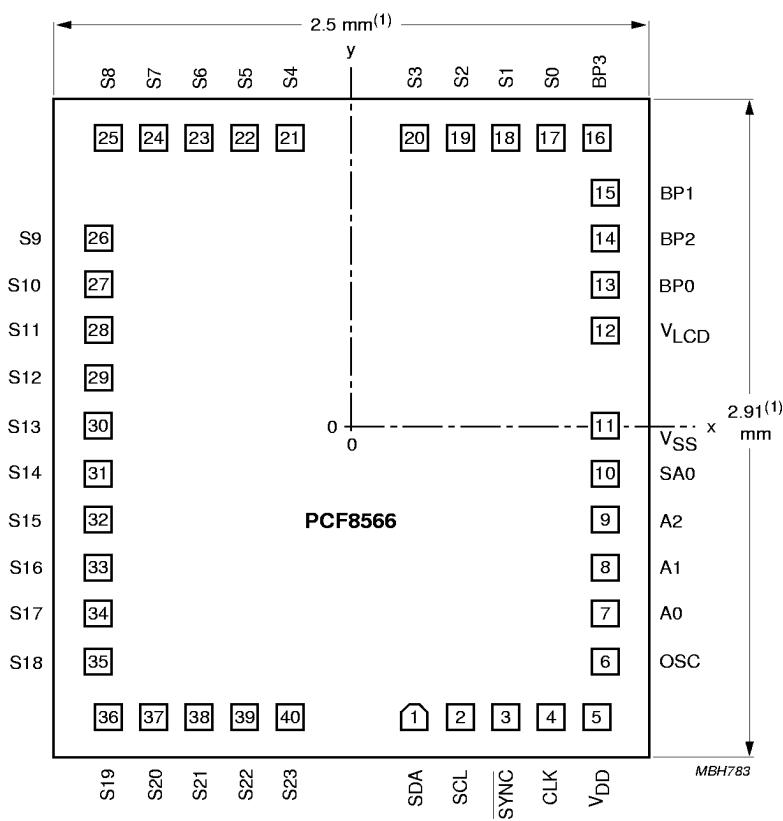

## 5 PINNING

| SYMBOL           | PIN      | DESCRIPTION                                    |

|------------------|----------|------------------------------------------------|

| SDA              | 1        | I <sup>2</sup> C-bus data input/output         |

| SCL              | 2        | I <sup>2</sup> C-bus clock input/output        |

| SYNC             | 3        | cascade synchronization input/output           |

| CLK              | 4        | external clock input/output                    |

| V <sub>DD</sub>  | 5        | positive supply voltage                        |

| OSC              | 6        | oscillator input                               |

| A0               | 7        |                                                |

| A1               | 8        | I <sup>2</sup> C-bus subaddress inputs         |

| A2               | 9        |                                                |

| SA0              | 10       | I <sup>2</sup> C-bus slave address bit 0 input |

| V <sub>SS</sub>  | 11       | logic ground                                   |

| V <sub>LCD</sub> | 12       | LCD supply voltage                             |

| BP0              | 13       |                                                |

| BP2              | 14       |                                                |

| BP1              | 15       | LCD backplane outputs                          |

| BP3              | 16       |                                                |

| S0 to S23        | 17 to 40 | LCD segment outputs                            |

Fig.2 Pin configuration.

# Universal LCD driver for low multiplex rates

PCF8566

## 6 FUNCTIONAL DESCRIPTION

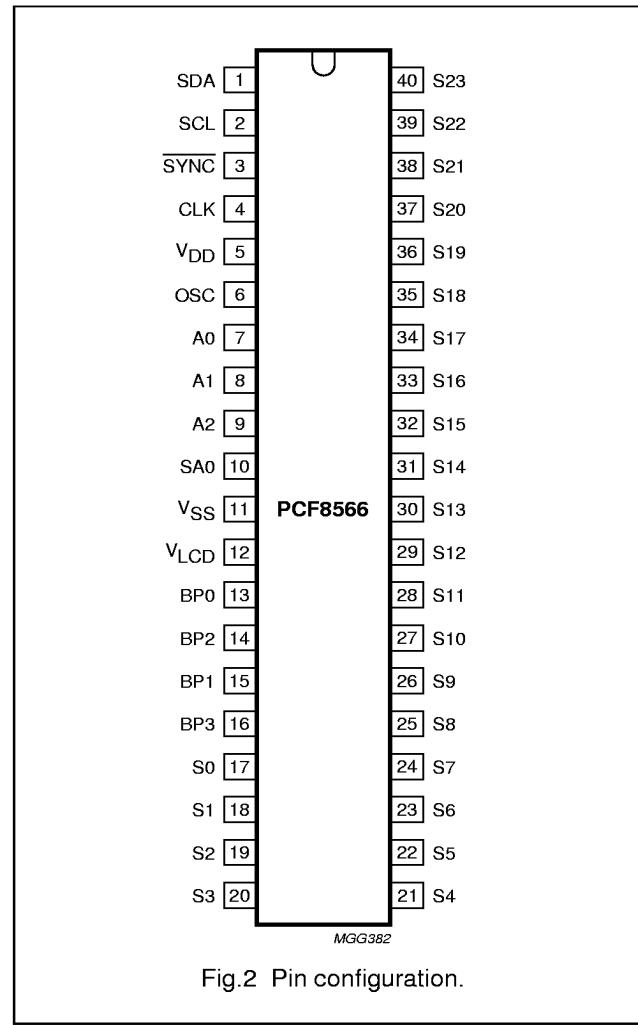

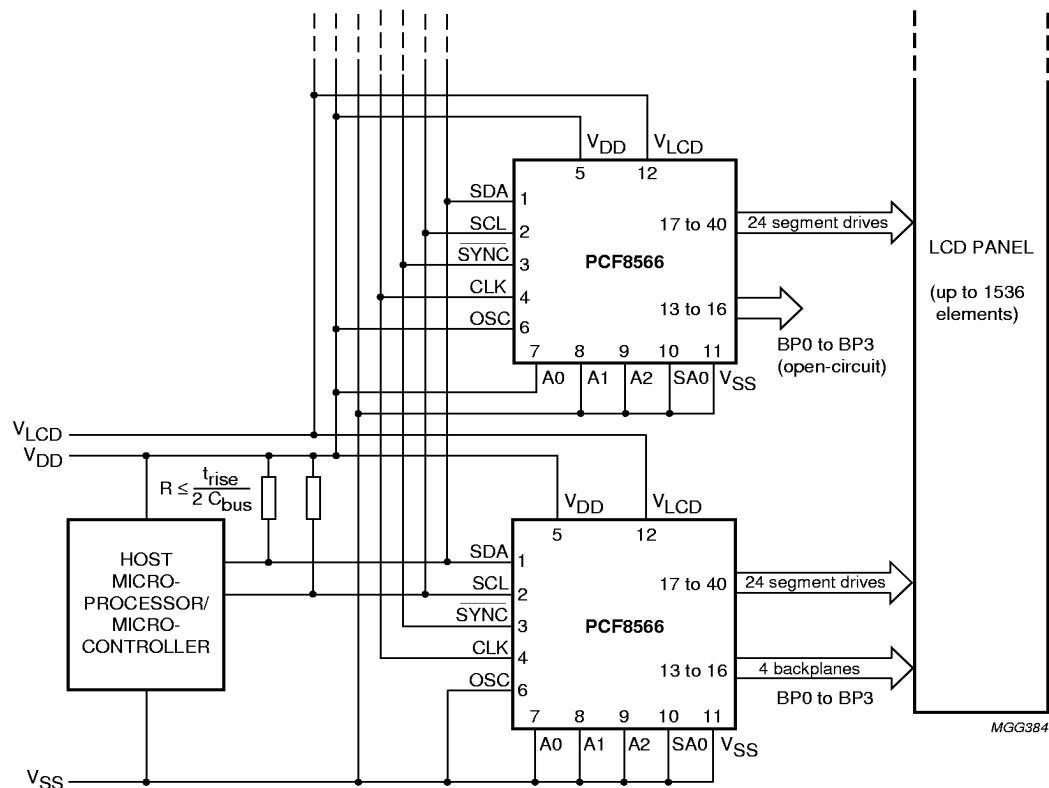

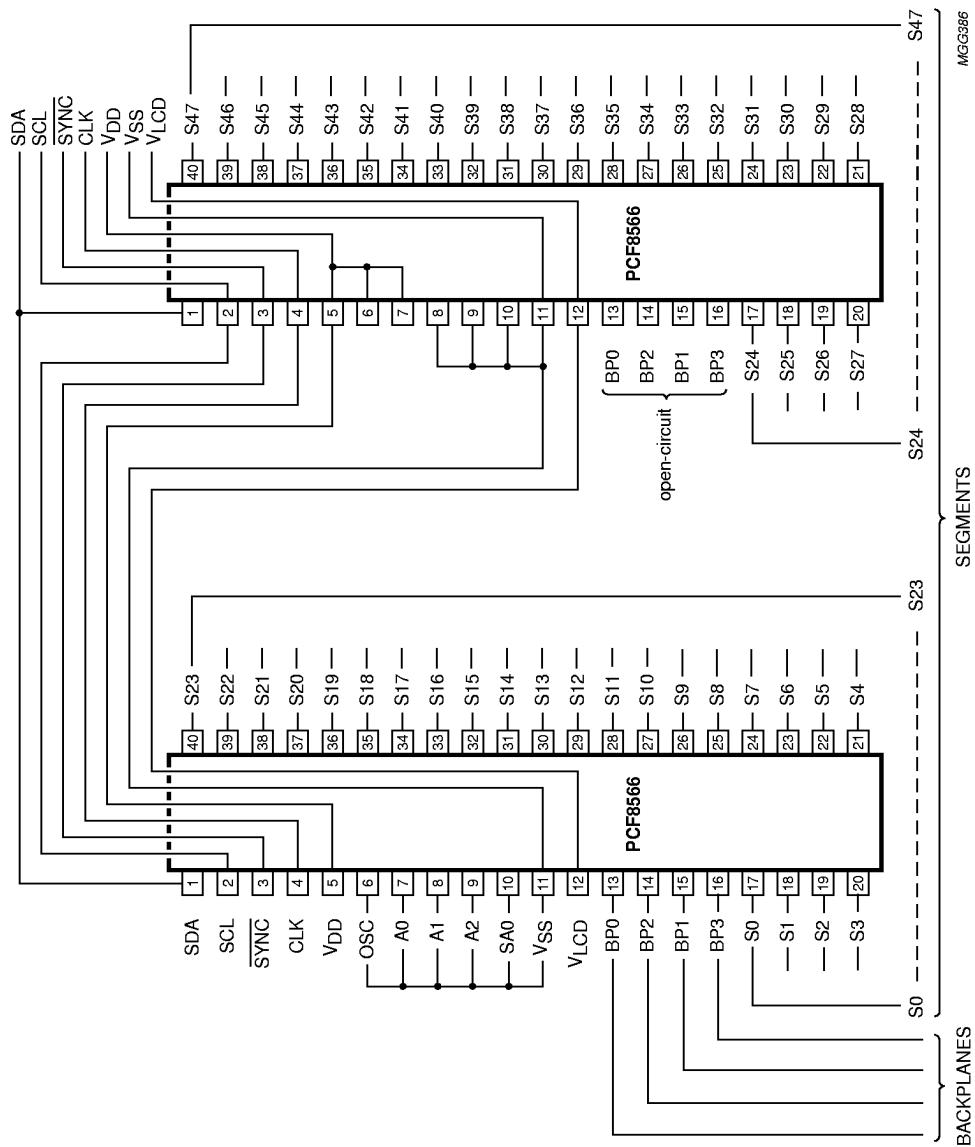

The PCF8566 is a versatile peripheral device designed to interface any microprocessor to a wide variety of LCDs. It can directly drive any static or multiplexed LCD containing up to 4 backplanes and up to 24 segments. The display configurations possible with the PCF8566 depend on the number of active backplane outputs required; a selection of display configurations is given in Table 1.

All of the display configurations given in Table 1 can be implemented in the typical system shown in Fig.3. The host microprocessor/microcontroller maintains the two-line I<sup>2</sup>C-bus communication channel with the PCF8566. The internal oscillator is selected by tying OSC (pin 6) to V<sub>SS</sub>. The appropriate biasing voltages for the multiplexed LCD waveforms are generated internally. The only other connections required to complete the system are to the power supplies (V<sub>DD</sub>, V<sub>SS</sub> and V<sub>LCD</sub>) and to the LCD panel chosen for the application.

**Table 1** Selection of display configurations

| ACTIVE BACKPLANE OUTPUTS | NUMBER OF SEGMENTS | 7-SEGMENT NUMERIC                | 14-SEGMENT ALPHANUMERIC             | DOT MATRIX       |

|--------------------------|--------------------|----------------------------------|-------------------------------------|------------------|

| 4                        | 96                 | 12 digits + 12 indicator symbols | 6 characters + 12 indicator symbols | 96 dots (4 × 24) |

| 3                        | 72                 | 9 digits + 9 indicator symbols   | 4 characters + 16 indicator symbols | 72 dots (3 × 24) |

| 2                        | 48                 | 6 digits + 6 indicator symbols   | 3 characters + 6 indicator symbols  | 48 dots (2 × 24) |

| 1                        | 24                 | 3 digits + 3 indicator symbols   | 1 character + 10 indicator symbols  | 24 dots          |

Fig.3 Typical system configuration.

# Universal LCD driver for low multiplex rates

PCF8566

## 6.1 Power-on reset

At power-on the PCF8566 resets to a defined starting condition as follows:

1. All backplane outputs are set to  $V_{DD}$

2. All segment outputs are set to  $V_{DD}$

3. The drive mode '1 : 4 multiplex with  $\frac{1}{3}$ bias' is selected

4. Blinking is switched off

5. Input and output bank selectors are reset (as defined in Table 5)

6. The I<sup>2</sup>C-bus interface is initialized

7. The data pointer and the subaddress counter are cleared.

Data transfers on the I<sup>2</sup>C-bus should be avoided for 1 ms following power-on to allow completion of the reset action.

## 6.2 LCD bias generator

The full-scale LCD voltage ( $V_{op}$ ) is obtained from  $V_{DD} - V_{LCD}$ . The LCD voltage may be temperature compensated externally through the  $V_{LCD}$  supply to pin 12. Fractional LCD biasing voltages are obtained from an internal voltage divider of three series resistors connected between  $V_{DD}$  and  $V_{LCD}$ . The centre resistor can be switched out of circuit to provide a  $\frac{1}{2}$ bias voltage level for the 1 : 2 multiplex configuration.

## 6.3 LCD voltage selector

The LCD voltage selector coordinates the multiplexing of the LCD according to the selected LCD drive configuration. The operation of the voltage selector is controlled by MODE SET commands from the command decoder. The biasing configurations that apply to the preferred modes of operation, together with the biasing characteristics as functions of  $V_{op} = V_{DD} - V_{LCD}$  and the resulting discrimination ratios (D), are given in Table 2.

A practical value of  $V_{op}$  is determined by equating  $V_{off(rms)}$  with a defined LCD threshold voltage ( $V_{th}$ ), typically when the LCD exhibits approximately 10% contrast. In the static drive mode a suitable choice is  $V_{op} \geq 3 V_{th}$ . Multiplex drive ratios of 1 : 3 and 1 : 4 with  $\frac{1}{2}$ bias are possible but the discrimination and hence the contrast ratios are smaller ( $\sqrt{3} = 1.732$  for 1 : 3 multiplex or  $\sqrt{21}/3 = 1.528$  for 1 : 4 multiplex). The advantage of these modes is a reduction of the LCD full scale voltage  $V_{op}$  as follows:

1 : 3 multiplex ( $\frac{1}{2}$ bias):

$$V_{op} = \sqrt{6} V_{op(rms)} = 2.449 V_{off(rms)}$$

1 : 4 multiplex ( $\frac{1}{2}$ bias):

$$V_{op} = \sqrt[4]{3}/3 V_{off(rms)} = 2.309 V_{off(rms)}$$

These compare with  $V_{op} = 3 V_{off(rms)}$  when  $\frac{1}{3}$ bias is used.

**Table 2** Preferred LCD drive modes: summary of characteristics

| LCD DRIVE MODE   | LCD BIAS CONFIGURATION   | $\frac{V_{off(rms)}}{V_{op}}$ | $\frac{V_{on(rms)}}{V_{op}}$ | $D = \frac{V_{on(rms)}}{V_{off(rms)}}$ |

|------------------|--------------------------|-------------------------------|------------------------------|----------------------------------------|

| Static (1 BP)    | static (2 levels)        | 0                             | 1                            | $\infty$                               |

| 1 : 2 MUX (2 BP) | $\frac{1}{2}$ (3 levels) | $\sqrt{2}/4 = 0.354$          | $\sqrt{10}/4 = 0.791$        | $\sqrt{5} = 2.236$                     |

| 1 : 2 MUX (2 BP) | $\frac{1}{3}$ (4 levels) | $\frac{1}{3} = 0.333$         | $\sqrt{5}/3 = 0.745$         | $\sqrt{5} = 2.236$                     |

| 1 : 3 MUX (3 BP) | $\frac{1}{3}$ (4 levels) | $\frac{1}{3} = 0.333$         | $\sqrt{33}/9 = 0.638$        | $\sqrt{33}/3 = 1.915$                  |

| 1 : 4 MUX (4 BP) | $\frac{1}{3}$ (4 levels) | $\frac{1}{3} = 0.333$         | $\sqrt{3}/3 = 0.577$         | $\sqrt{3} = 1.732$                     |

# Universal LCD driver for low multiplex rates

PCF8566

## 6.4 LCD drive mode waveforms

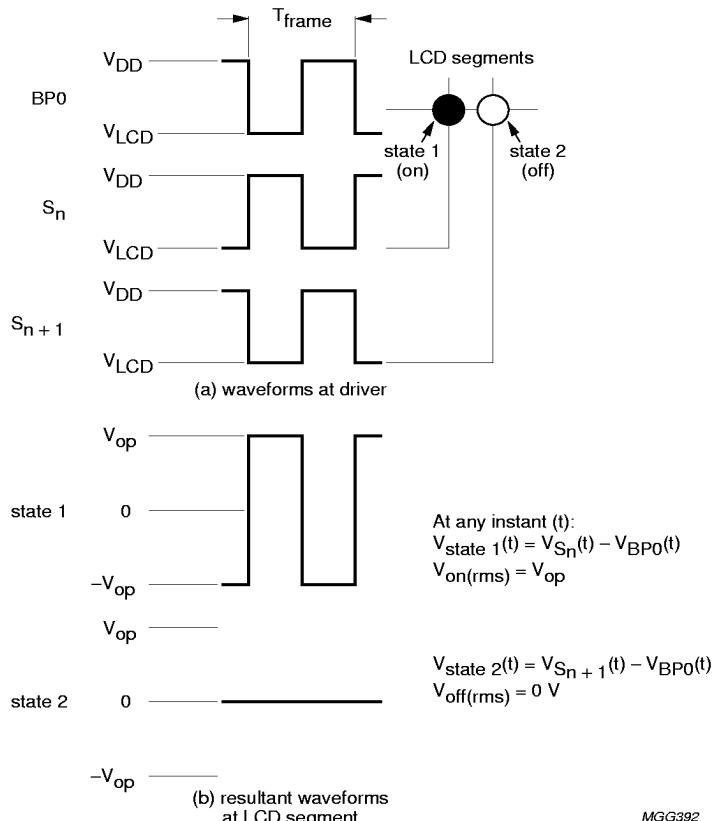

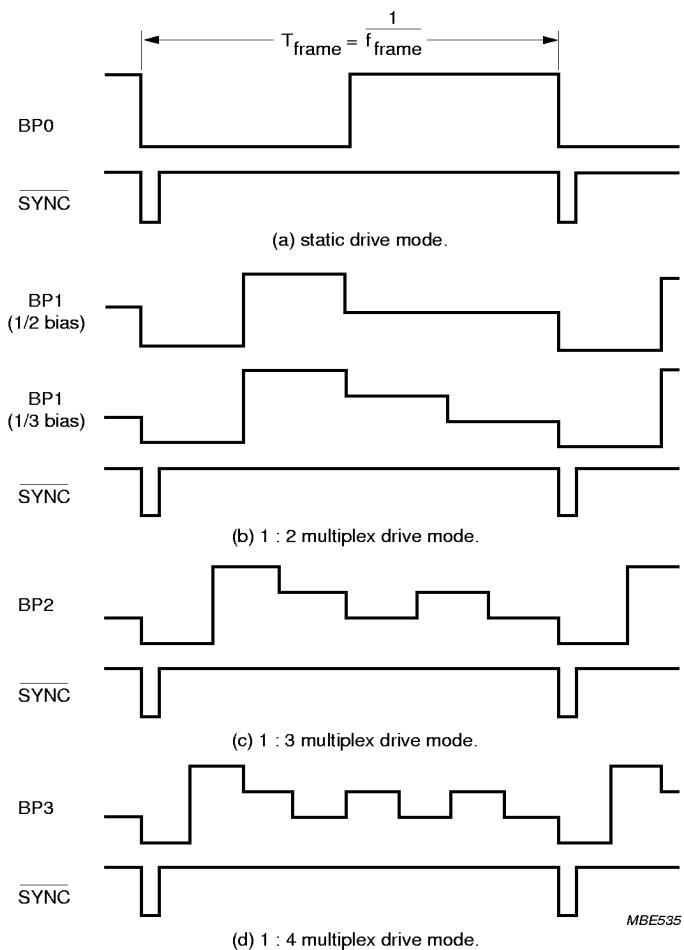

The static LCD drive mode is used when a single backplane is provided in the LCD. Backplane and segment drive waveforms for this mode are shown in Fig.4.

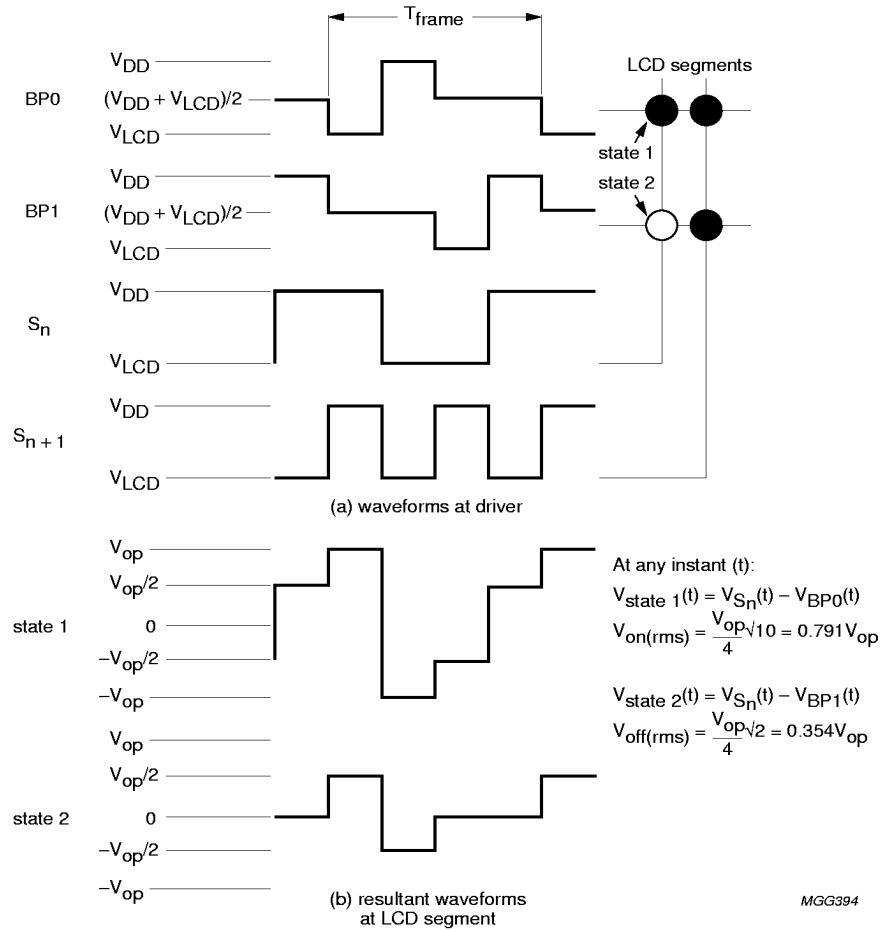

When two backplanes are provided in the LCD the 1 : 2 multiplex drive mode applies. The PCF8566 allows use of  $\frac{1}{2}$  or  $\frac{1}{3}$  bias in this mode as shown in Figs 5 and 6.

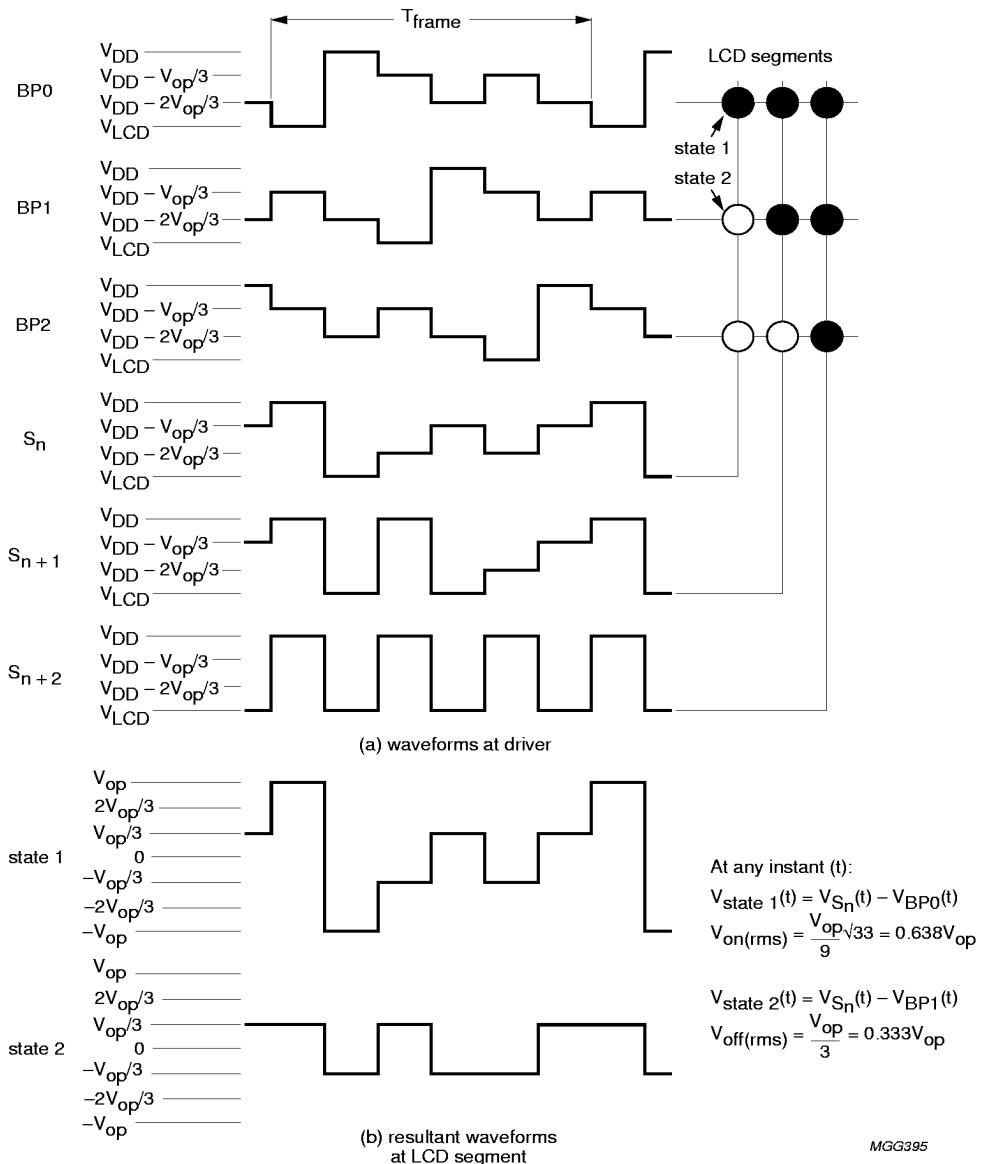

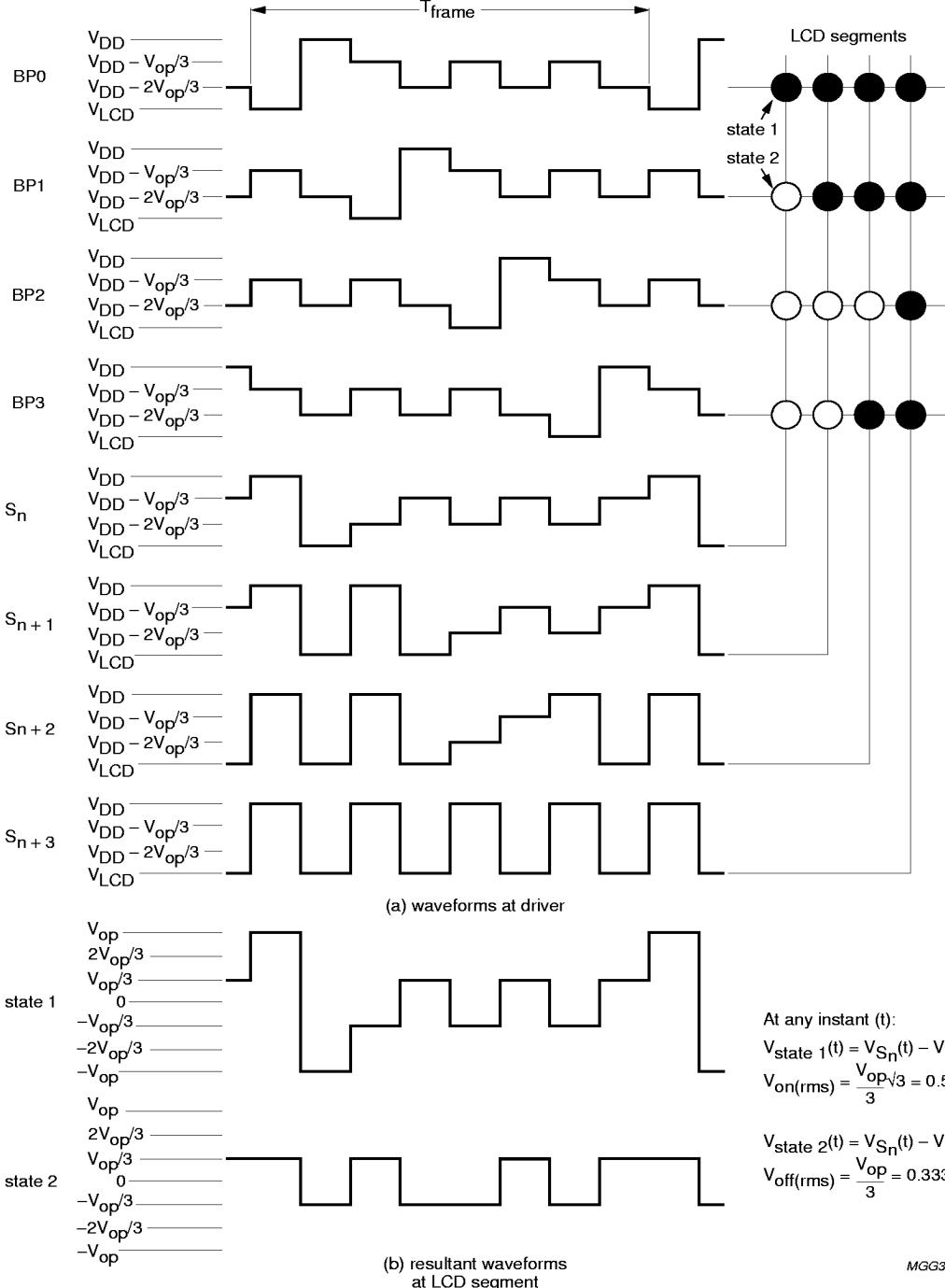

The backplane and segment drive waveforms for the 1 : 3 multiplex drive mode (three LCD backplanes) and for the 1 : 4 multiplex drive mode (four LCD backplanes) are shown in Figs 7 and 8 respectively.

Fig.4 Static drive mode waveforms:  $V_{op} = V_{DD} - V_{LCD}$ .

## Universal LCD driver for low multiplex rates

PCF8566

Fig.5 Waveforms for 1 : 2 multiplex drive mode with  $1/2$  bias:  $V_{op} = V_{DD} - V_{LCD}$ .

## Universal LCD driver for low multiplex rates

PCF8566

Fig.6 Waveforms for 1 : 2 multiplex drive mode with  $1/3$  bias:  $V_{op} = V_{DD} - V_{LCD}$ .

## Universal LCD driver for low multiplex rates

PCF8566

Fig.7 Waveforms for 1 : 3 multiplex drive mode:  $V_{op} = V_{DD} - V_{LCD}$ .

## Universal LCD driver for low multiplex rates

PCF8566

Fig.8 Waveforms for 1 : 4 multiplex drive mode:  $V_{op} = V_{DD} - V_{LCD}$ .

MGG396

# Universal LCD driver for low multiplex rates

PCF8566

## 6.5 Oscillator

The internal logic and the LCD drive signals of the PCF8566 or PCF8576 are timed either by the built-in oscillator or from an external clock.

The clock frequency ( $f_{CLK}$ ) determines the LCD frame frequency and the maximum rate for data reception from the I<sup>2</sup>C-bus. To allow I<sup>2</sup>C-bus transmissions at their maximum data rate of 100 kHz,  $f_{CLK}$  should be chosen to be above 125 kHz.

A clock signal must always be supplied to the device; removing the clock may freeze the LCD in a DC state.

## 6.6 Internal clock

When the internal oscillator is used, OSC (pin 6) should be tied to  $V_{SS}$ . In this case, the output from CLK (pin 4) provides the clock signal for cascaded PCF8566s and PCF8576s in the system.

## 6.7 External clock

The condition for external clock is made by tying OSC (pin 6) to  $V_{DD}$ ; CLK (pin 4) then becomes the external clock input.

## 6.8 Timing

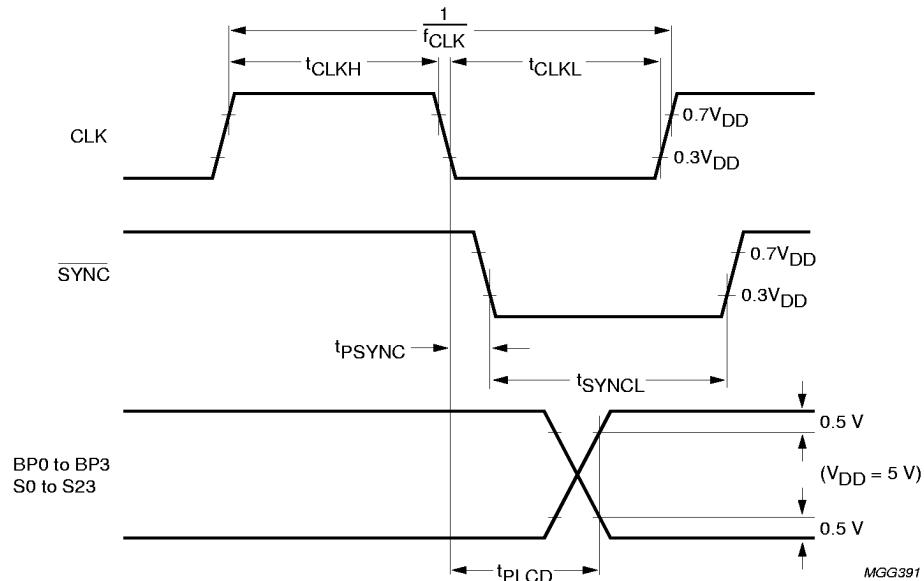

The timing of the PCF8566 organizes the internal data flow of the device. This includes the transfer of display data from the display RAM to the display segment outputs. In cascaded applications, the synchronization signal SYNC maintains the correct timing relationship between the PCF8566s in the system. The timing also generates the LCD frame frequency which it derives as an integer multiple of the clock frequency (Table 3). The frame frequency is set by MODE SET commands when internal clock is used, or by the frequency applied to pin 4 when external clock is used.

**Table 3** LCD frame frequencies

| PCF8566 MODE      | $f_{frame}$    | NOMINAL $f_{frame}$ (Hz) |

|-------------------|----------------|--------------------------|

| Normal mode       | $f_{CLK}/2880$ | 64                       |

| Power saving mode | $f_{CLK}/480$  | 64                       |

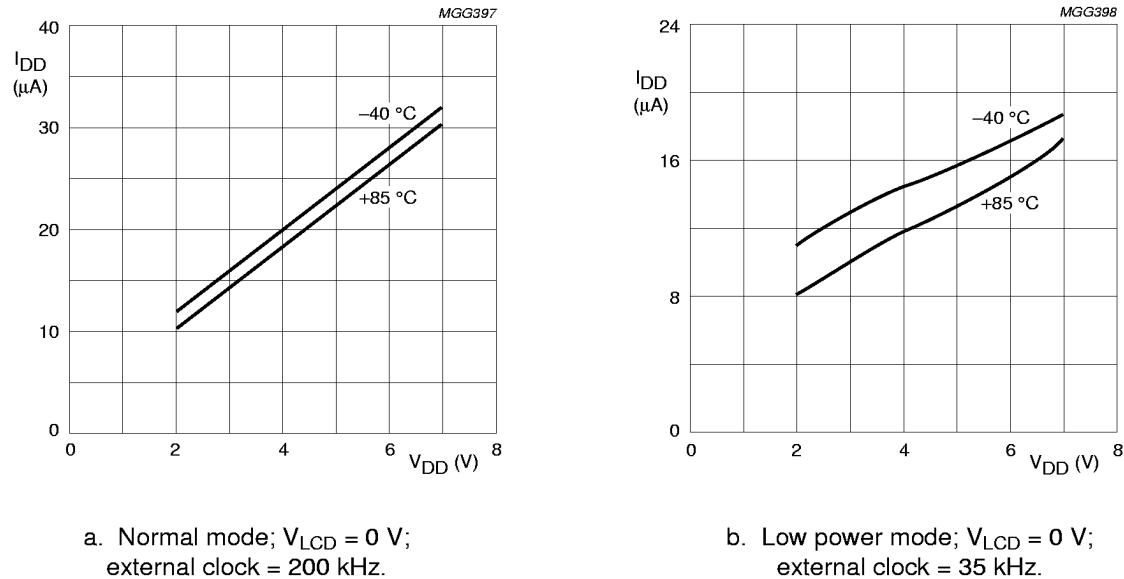

The ratio between the clock frequency and the LCD frame frequency depends on the mode in which the device is operating. In the power saving mode the reduction ratio is six times smaller; this allows the clock frequency to be reduced by a factor of six. The reduced clock frequency results in a significant reduction in power dissipation.

The lower clock frequency has the disadvantage of increasing the response time when large amounts of display data are transmitted on the I<sup>2</sup>C-bus. When a device is unable to 'digest' a display data byte before the next one arrives, it holds the SCL line LOW until the first display data byte is stored. This slows down the transmission rate of the I<sup>2</sup>C-bus but no data loss occurs.

## 6.9 Display latch

The display latch holds the display data while the corresponding multiplex signals are generated. There is a one-to-one relationship between the data in the display latch, the LCD segment outputs and one column of the display RAM.

## 6.10 Shift register

The shift register serves to transfer display information from the display RAM to the display latch while previous data are displayed.

## 6.11 Segment outputs

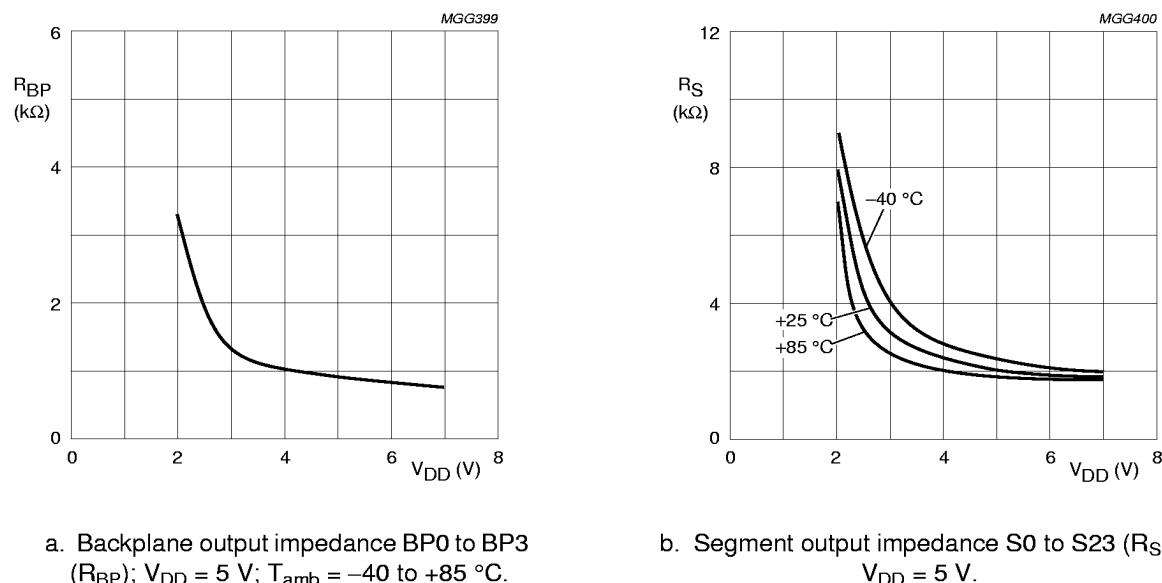

The LCD drive section includes 24 segment outputs S0 to S23 (pins 17 to 40) which should be connected directly to the LCD. The segment output signals are generated in accordance with the multiplexed backplane signals and with the data resident in the display latch. When less than 24 segment outputs are required the unused segment outputs should be left open-circuit.

## 6.12 Backplane outputs

The LCD drive section includes four backplane outputs BP0 to BP3 which should be connected directly to the LCD. The backplane output signals are generated in accordance with the selected LCD drive mode. If less than four backplane outputs are required the unused outputs can be left open. In the 1 : 3 multiplex drive mode BP3 carries the same signal as BP1, therefore these two adjacent outputs can be tied together to give enhanced drive capabilities. In the 1 : 2 multiplex drive mode BP0 and BP2, BP1 and BP3 respectively carry the same signals and may also be paired to increase the drive capabilities. In the static drive mode the same signal is carried by all four backplane outputs and they can be connected in parallel for very high drive requirements.

## 6.13 Display RAM

The display RAM is a static 24 × 4-bit RAM which stores LCD data. A logic 1 in the RAM bit-map indicates the 'on' state of the corresponding LCD segment; similarly, a logic 0 indicates the 'off' state.

# Universal LCD driver for low multiplex rates

PCF8566

There is a one-to-one correspondence between the RAM addresses and the segment outputs, and between the individual bits of a RAM word and the backplane outputs. The first RAM column corresponds to the 24 segments operated with respect to backplane BP0 (see Fig.9). In multiplexed LCD applications the segment data of the second, third and fourth column of the display RAM are time-multiplexed with BP1, BP2 and BP3 respectively.

When display data are transmitted to the PCF8566 the display bytes received are stored in the display RAM according to the selected LCD drive mode. To illustrate the filling order, an example of a 7-segment numeric display showing all drive modes is given in Fig.10; the RAM filling organization depicted applies equally to other LCD types.

With reference to Fig.10, in the static drive mode the eight transmitted data bits are placed in bit 0 of eight successive display RAM addresses. In the 1 : 2 multiplex drive mode the eight transmitted data bits are placed in bits 0 and 1 of four successive display RAM addresses. In the 1 : 3 multiplex drive mode these bits are placed in bits 0, 1 and 2 of three successive addresses, with bit 2 of the third address left unchanged. This last bit may, if necessary, be controlled by an additional transfer to this address but care should be taken to avoid overriding adjacent data because full bytes are always transmitted. In the 1 : 4 multiplex drive mode the eight transmitted data bits are placed in bits 0, 1, 2 and 3 of two successive display RAM addresses.

## 6.14 Data pointer

The addressing mechanism for the display RAM is realized using the data pointer. This allows the loading of an individual display data byte, or a series of display data bytes, into any location of the display RAM.

The sequence commences with the initialization of the data pointer by the LOAD DATA POINTER command. Following this, an arriving data byte is stored starting at the display RAM address indicated by the data pointer thereby observing the filling order shown in Fig.10. The data pointer is automatically incremented according to the LCD configuration chosen. That is, after each byte is stored, the contents of the data pointer are incremented by eight (static drive mode), by four (1 : 2 multiplex drive mode), by three (1 : 3 multiplex drive mode) or by two (1 : 4 multiplex drive mode).

## 6.15 Subaddress counter

The storage of display data is conditioned by the contents of the subaddress counter. Storage is allowed to take place only when the contents of the subaddress counter agree with the hardware subaddress applied to A0, A1 and A2 (pins 7, 8, and 9). A0, A1 and A2 should be tied to V<sub>SS</sub> or V<sub>DD</sub>. The subaddress counter value is defined by the DEVICE SELECT command. If the contents of the subaddress counter and the hardware subaddress do not agree then data storage is inhibited but the data pointer is incremented as if data storage had taken place. The subaddress counter is also incremented when the data pointer overflows.

The storage arrangements described lead to extremely efficient data loading in cascaded applications. When a series of display bytes are being sent to the display RAM, automatic wrap-over to the next PCF8566 occurs when the last RAM address is exceeded. Subaddressing across device boundaries is successful even if the change to the next device in the cascade occurs within a transmitted character.

|                                                     |   | display RAM addresses (rows)/segment outputs (S) |    |    |    |    |  |  |  |  |  |  |  |  |

|-----------------------------------------------------|---|--------------------------------------------------|----|----|----|----|--|--|--|--|--|--|--|--|

|                                                     |   | 0                                                | 1  | 2  | 3  | 4  |  |  |  |  |  |  |  |  |

| display RAM bits (columns) / backplane outputs (BP) | 0 |                                                  |    |    |    |    |  |  |  |  |  |  |  |  |

|                                                     | 1 |                                                  |    |    |    |    |  |  |  |  |  |  |  |  |

|                                                     | 2 |                                                  |    |    |    |    |  |  |  |  |  |  |  |  |

|                                                     | 3 |                                                  |    |    |    |    |  |  |  |  |  |  |  |  |

|                                                     | 4 |                                                  |    |    |    |    |  |  |  |  |  |  |  |  |

|                                                     |   | 19                                               | 20 | 21 | 22 | 23 |  |  |  |  |  |  |  |  |

Fig.9 Display RAM bit-map showing direct relationship between display RAM addresses and segment outputs, and between bits in a RAM word and backplane outputs.

## Universal LCD driver for low multiplex rates

PCF8566

| drive mode      | LCD segments | LCD backplanes | display RAM filling order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | transmitted display byte |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

|-----------------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|-------|-------|-------|-----|-----|-----|-------|---|---|----|----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|---|---|---|---|---|---|----|---|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|---|---|---|---|----|

| static          |              |                | <table border="1"> <tr><td>n</td><td>n+1</td><td>n+2</td><td>n+3</td><td>n+4</td><td>n+5</td><td>n+6</td><td>n+7</td></tr> <tr><td>bit/0</td><td>c</td><td>b</td><td>a</td><td>f</td><td>g</td><td>e</td><td>d</td></tr> <tr><td>BP1</td><td>x</td><td>x</td><td>x</td><td>x</td><td>x</td><td>x</td><td>x</td></tr> <tr><td>2</td><td>x</td><td>x</td><td>x</td><td>x</td><td>x</td><td>x</td><td>x</td></tr> <tr><td>3</td><td>x</td><td>x</td><td>x</td><td>x</td><td>x</td><td>x</td><td>x</td></tr> </table> | n                        | n+1 | n+2   | n+3   | n+4   | n+5 | n+6 | n+7 | bit/0 | c | b | a  | f  | g | e                                                                                                                                                                                                                                | d   | BP1 | x   | x   | x                                                                                                                                                                                                                                | x                                                                                                                                                                                                                                | x   | x   | x   | 2   | x   | x   | x   | x   | x  | x | x | 3 | x | x | x | x  | x | x | x | <table border="1"> <tr><td>MSB</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td></tr> <tr><td>c</td><td>b</td><td>a</td><td>f</td><td>g</td><td>e</td><td>d</td><td>DP</td></tr> </table> | MSB | --- | --- | --- | --- | --- | --- | --- | c | b | a | f | g | e | d | DP |

| n               | n+1          | n+2            | n+3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | n+4                      | n+5 | n+6   | n+7   |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| bit/0           | c            | b              | a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | f                        | g   | e     | d     |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| BP1             | x            | x              | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | x                        | x   | x     | x     |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| 2               | x            | x              | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | x                        | x   | x     | x     |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| 3               | x            | x              | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | x                        | x   | x     | x     |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| MSB             | ---          | ---            | ---                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ---                      | --- | ---   | ---   |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| c               | b            | a              | f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | g                        | e   | d     | DP    |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| 1 : 2 multiplex |              |                | <table border="1"> <tr><td>n</td><td>n+1</td><td>n+2</td><td>n+3</td></tr> <tr><td>bit/0</td><td>a</td><td>f</td><td>d</td></tr> <tr><td>BP1</td><td>b</td><td>g</td><td>DP</td></tr> <tr><td>2</td><td>x</td><td>x</td><td>x</td></tr> <tr><td>3</td><td>x</td><td>x</td><td>x</td></tr> </table>                                                                                                                                                                                                                | n                        | n+1 | n+2   | n+3   | bit/0 | a   | f   | d   | BP1   | b | g | DP | 2  | x | x                                                                                                                                                                                                                                | x   | 3   | x   | x   | x                                                                                                                                                                                                                                | <table border="1"> <tr><td>MSB</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td></tr> <tr><td>a</td><td>b</td><td>f</td><td>g</td><td>e</td><td>c</td><td>d</td><td>DP</td></tr> </table> | MSB | --- | --- | --- | --- | --- | --- | --- | a  | b | f | g | e | c | d | DP |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| n               | n+1          | n+2            | n+3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| bit/0           | a            | f              | d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| BP1             | b            | g              | DP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| 2               | x            | x              | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| 3               | x            | x              | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| MSB             | ---          | ---            | ---                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ---                      | --- | ---   | ---   |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| a               | b            | f              | g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e                        | c   | d     | DP    |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| 1 : 3 multiplex |              |                | <table border="1"> <tr><td>n</td><td>n+1</td><td>n+2</td></tr> <tr><td>bit/0</td><td>b</td><td>a</td><td>f</td></tr> <tr><td>BP1</td><td>DP</td><td>d</td><td>e</td></tr> <tr><td>2</td><td>c</td><td>g</td><td>x</td></tr> <tr><td>3</td><td>x</td><td>x</td><td>x</td></tr> </table>                                                                                                                                                                                                                            | n                        | n+1 | n+2   | bit/0 | b     | a   | f   | BP1 | DP    | d | e | 2  | c  | g | x                                                                                                                                                                                                                                | 3   | x   | x   | x   | <table border="1"> <tr><td>MSB</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td></tr> <tr><td>b</td><td>DP</td><td>c</td><td>a</td><td>d</td><td>g</td><td>f</td><td>e</td></tr> </table> | MSB                                                                                                                                                                                                                              | --- | --- | --- | --- | --- | --- | --- | b   | DP | c | a | d | g | f | e |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| n               | n+1          | n+2            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| bit/0           | b            | a              | f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| BP1             | DP           | d              | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| 2               | c            | g              | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| 3               | x            | x              | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| MSB             | ---          | ---            | ---                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ---                      | --- | ---   | ---   |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| b               | DP           | c              | a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | d                        | g   | f     | e     |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| 1 : 4 multiplex |              |                | <table border="1"> <tr><td>n</td><td>n+1</td></tr> <tr><td>bit/0</td><td>a</td><td>f</td></tr> <tr><td>BP1</td><td>c</td><td>e</td></tr> <tr><td>2</td><td>b</td><td>g</td></tr> <tr><td>3</td><td>DP</td><td>d</td></tr> </table>                                                                                                                                                                                                                                                                                | n                        | n+1 | bit/0 | a     | f     | BP1 | c   | e   | 2     | b | g | 3  | DP | d | <table border="1"> <tr><td>MSB</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td><td>---</td></tr> <tr><td>a</td><td>c</td><td>b</td><td>DP</td><td>f</td><td>e</td><td>g</td><td>d</td></tr> </table> | MSB | --- | --- | --- | ---                                                                                                                                                                                                                              | ---                                                                                                                                                                                                                              | --- | --- | a   | c   | b   | DP  | f   | e   | g  | d |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| n               | n+1          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

| bit/0           | a            | f              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |

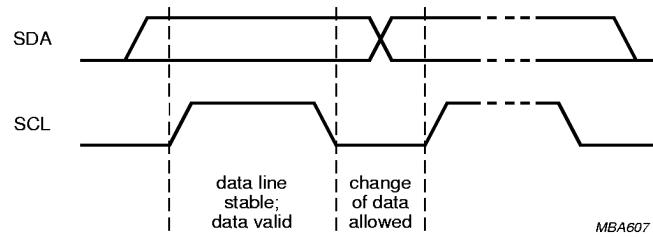

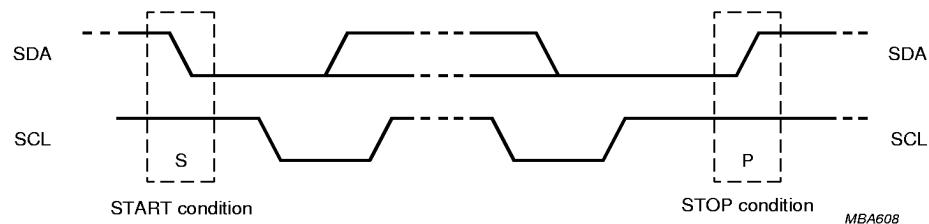

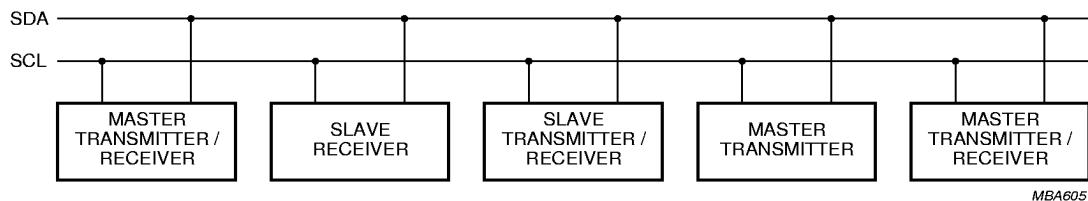

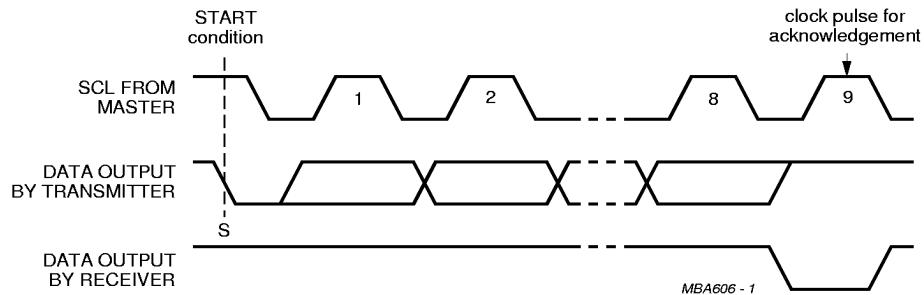

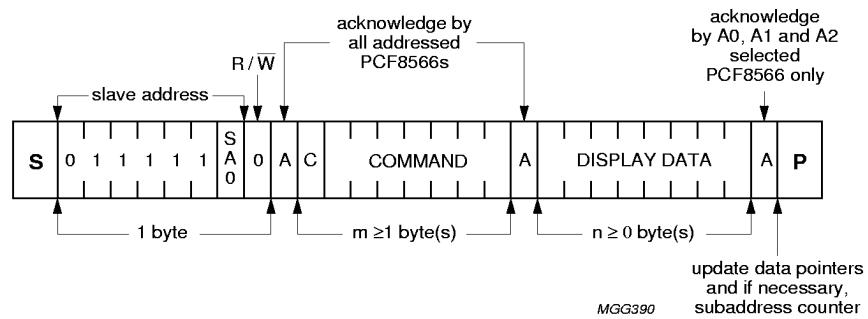

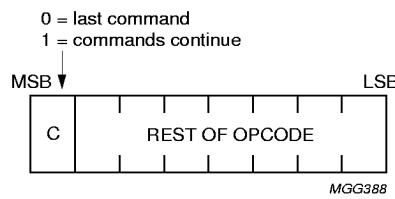

| BP1             | c            | e              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |     |       |       |       |     |     |     |       |   |   |    |    |   |                                                                                                                                                                                                                                  |     |     |     |     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |    |   |   |   |   |   |   |    |   |   |   |                                                                                                                                                                                                                                  |     |     |     |     |     |     |     |     |   |   |   |   |   |   |   |    |