#### **General Description**

The DS1388 I<sup>2</sup>C real-time clock (RTC), supervisor, and EEPROM is a multifunction device that provides a clock/calendar, programmable watchdog timer, powersupply monitor with reset, and 512 bytes of EEPROM. The clock provides hundredths of seconds, seconds, minutes, and hours, and operates in 24-hour or 12-hour format with an AM/PM indicator. The calendar provides day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. A watchdog timer provides a reset for an unresponsive microprocessor. It is programmable in 10ms intervals from 0.01 to 99.99 seconds. A temperaturecompensated voltage reference and comparator circuit monitors the status of VCC. If a primary power failure is detected, the device automatically switches to the backup supply and drives the reset output to the active state. The backup supply maintains time and date operation in the absence of Vcc. When Vcc returns to nominal levels, the reset is held low for a period to allow the power supply and processor to stabilize. The device also has a pushbutton reset controller, which debounces a reset input signal. The device is accessed through an I<sup>2</sup>C serial interface.

#### **Applications**

Portable Instruments Point-of-Sale Equipment Network Interface Cards Wireless Equipment

#### **Features**

- ♦ Fast (400kHz) I<sup>2</sup>C Interface

- ♦ RTC Counts Hundredths of Seconds, Seconds. Minutes, Hours, Day, Date, Month, and Year with Leap Year Compensation Valid Up to 2100

- **♦ Programmable Watchdog Timer**

- ◆ Automatic Power-Fail Detect and Switch Circuitry

- **♦** Reset Output with Pushbutton Reset Input Capability

- ♦ 512 x 8 Bits of EEPROM

- ♦ Integrated Trickle-Charge Capability for Backup Supply

- ♦ Three Operating Voltages: 5.0V, 3.3V, and 3.0V

- **♦ Low Timekeeping Voltage Down to 1.3V**

- ♦ -40°C to +85°C Temperature Range

- ♦ UL Recognized

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE     | TOP<br>MARK |

|-------------|----------------|-----------------|-------------|

| DS1388Z-5+  | -40°C to +85°C | 8 SO (150 mils) | DS1388-5    |

| DS1388Z-33+ | -40°C to +85°C | 8 SO (150 mils) | DS138833    |

| DS1388Z-3+  | -40°C to +85°C | 8 SO (150 mils) | DS1388-3    |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

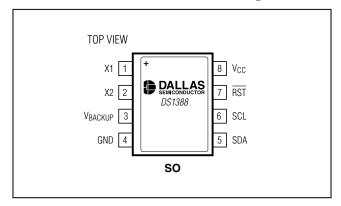

#### Pin Configuration

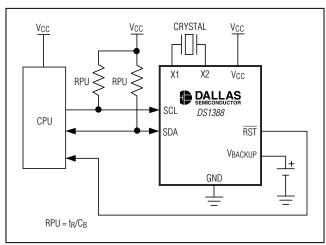

#### **Typical Operating Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on VCC Pin Relative to Ground0.3V to +6.0V | Storage Temperature Range | 55°C to +125°C           |

|----------------------------------------------------------|---------------------------|--------------------------|

| Voltage Range on Inputs Relative                         | Soldering Temperature     | Refer to the IPC/JEDEC   |

| to Ground0.3V to (V <sub>CC</sub> + 0.3V)                |                           | J-STD-020 Specification. |

| Operating Temperature Range                              |                           |                          |

| (noncondensing)40°C to +85°C                             |                           |                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$(T_A = -40$ °C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                              | SYMBOL          | CONDITIO | ONS        | MIN                       | TYP  | MAX                       | UNITS |

|----------------------------------------|-----------------|----------|------------|---------------------------|------|---------------------------|-------|

|                                        |                 |          | DS1388Z-5  | 4.5                       | 5    | 5.5                       |       |

| Supply Voltage                         | Vcc             | (Note 2) | DS1388Z-33 | 2.97                      | 3.3  | 3.63                      | V     |

|                                        |                 |          | DS1388Z-3  | 2.7                       | 3    | 3.3                       |       |

| Logic 1                                | VIH             | (Note 2) |            | 0.7 x<br>V <sub>C</sub> C |      | V <sub>CC</sub> + 0.3     | V     |

| Logic 0                                | V <sub>IL</sub> | (Note 2) |            | -0.3                      |      | +0.3 x<br>V <sub>CC</sub> | V     |

| Pullup Voltage (SCL, SDA),<br>VCC = 0V | V <sub>PU</sub> |          |            |                           |      | 5.5                       | V     |

| VBACKUP Voltage                        | VBACKUP         | (Note 2) |            | 1.3                       | 3.0  | 5.5                       | V     |

|                                        |                 |          | DS1388Z-5  | 4.15                      | 4.33 | 4.50                      |       |

| Power-Fail Voltage                     | VpF             | (Note 2) | DS1388Z-33 | 2.70                      | 2.88 | 2.97                      | V     |

|                                        |                 |          | DS1388Z-3  | 2.45                      | 2.60 | 2.70                      |       |

#### DC ELECTRICAL CHARACTERISTICS

(Vcc = Vcc(MIN) to Vcc(MAX),  $T_A = -40$ °C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                         | SYMBOL          | CONDITIONS   | MIN  | TYP  | MAX | UNITS |

|-------------------------------------------------------------------|-----------------|--------------|------|------|-----|-------|

| T: 11 01 0 11: ":                                                 | R1              | (Notes 3, 4) |      | 250  |     |       |

| Trickle-Charger Current-Limiting Resistors                        | R2              | (Note 5)     |      | 2000 |     | Ω     |

| 1163131013                                                        | R3              | (Note 6)     |      | 4000 |     |       |

| Input Leakage (SCL)                                               | I <sub>LI</sub> |              | -1   |      | +1  | μΑ    |

| I/O Leakage (SDA)                                                 | ILO             |              | -1   |      | +1  | μΑ    |

| I/O Leakage (RST)                                                 | ILORST          | (Note 7)     | -200 |      | +10 | μΑ    |

| SDA Logic 0 Output<br>(V <sub>OL</sub> = 0.15 x V <sub>CC</sub> ) | loldout         |              |      |      | 3   | mA    |

#### DC ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = V_{CC(MIN)}$  to  $V_{CC(MAX)}$ ,  $T_A = -40$ °C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                                          | SYMBOL          | С                                     | ONDITIONS                         | MIN  | TYP | MAX    | UNITS |  |

|------------------------------------------------------------------------------------|-----------------|---------------------------------------|-----------------------------------|------|-----|--------|-------|--|

|                                                                                    |                 | V <sub>CC</sub> > 2V; V <sub>OL</sub> | = 0.4V                            |      |     | 3.0    | mA    |  |

| RST Logic 0 Output                                                                 | Iolsir          | 1.8V < V <sub>CC</sub> < 2            | $V; V_{OL} = 0.2 \times V_{CC}$   |      |     | 3.0    | IIIA  |  |

|                                                                                    |                 | 1.3V < V <sub>CC</sub> < 1.           | .8V; $V_{OL} = 0.2 \times V_{CC}$ |      |     | 250    | μΑ    |  |

|                                                                                    |                 |                                       | DS1388Z-5                         |      |     | 600    |       |  |

| V <sub>CC</sub> Active Current, EEPROM<br>Read, I <sup>2</sup> C Read/Write Access | ICCER           | (Note 8)                              | DS1388Z-33                        |      |     | 250    | μΑ    |  |

| neau, i C neau/Wille Access                                                        |                 |                                       | DS1388Z-3                         |      |     | 225    |       |  |

| V <sub>CC</sub> Active Current, EEPROM<br>Write Cycle                              |                 |                                       | DS1388Z-5                         |      |     | 1.0    |       |  |

|                                                                                    | ICCEW           | (Note 8)                              | DS1388Z-33                        |      |     | 0.70   | mA    |  |

|                                                                                    |                 |                                       | DS1388Z-3                         |      |     | 0.65   |       |  |

|                                                                                    |                 |                                       | DS1388Z-5                         |      |     | 270    |       |  |

| V <sub>CC</sub> Standby Current                                                    | Iccs            | (Note 9)                              | DS1388Z-33                        |      | 100 | 150    | μΑ    |  |

|                                                                                    |                 |                                       | DS1388Z-3                         |      |     | 140    |       |  |

| VBACKUP Leakage Current<br>(VBACKUP = 3.7V,<br>VCC = VCC(MAX))                     | IBACKUPLKG      |                                       |                                   |      | 15  | 100    | nA    |  |

|                                                                                    |                 | $T_A = +25^{\circ}C$ (gu              | aranteed by design)               | 200k |     |        |       |  |

| EEPROM Write/Erase Cycles                                                          | t <sub>WR</sub> | T <sub>A</sub> = -40°C to + design)   | 50k                               |      |     | Cycles |       |  |

#### DC ELECTRICAL CHARACTERISTICS

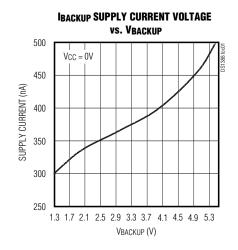

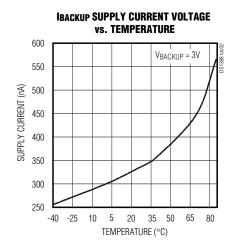

(Vcc = 0V,  $V_{BACKUP} = 3.7V$ ,  $T_A = +25$ °C, unless otherwise noted.) (Note 1)

| PARAMETER                                                                  | SYMBOL    | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------------------------|-----------|------------|-----|-----|-----|-------|

| VBACKUP Current, OSC On (EOSC = 0), SDA = SCL = 0V                         | IBACKUP   | (Note 10)  |     | 410 | 550 | nA    |

| VBACKUP Current, OSC Off<br>(EOSC = 1), SDA = SCL = 0V<br>(Data Retention) | IBACKUPDR | (Note 10)  |     | 10  | 100 | nA    |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{CC(MIN)})$  to  $V_{CC(MAX)}$ ,  $T_A = -40$ °C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                      | SYMBOL           | CONDITION     | MIN               | TYP | MAX  | UNITS |

|------------------------------------------------|------------------|---------------|-------------------|-----|------|-------|

| COL Clock Fraguency                            | f                | Fast mode     | 100               |     | 400  | Id Ia |

| SCL Clock Frequency                            | fSCL             | Standard mode | 0                 |     | 100  | kHz   |

| Bus Free Time Between a STOP                   | +                | Fast mode     | 1.3               |     |      |       |

| and START Condition                            | t <sub>BUF</sub> | Standard mode | 4.7               |     |      | μs    |

| Hold Time (Repeated) START                     | t                | Fast mode     | 0.6               |     |      |       |

| Condition (Note 11)                            | thd:STA          | Standard mode | 4.0               |     |      | μs    |

| LOW Period of SCL Clock                        | +. 0.11          | Fast mode     | 1.3               |     |      |       |

| LOW Period of SCL Clock                        | tLOW             | Standard mode | 4.7               |     |      | μs    |

| LUCI David of CCI Clask                        |                  | Fast mode     | 0.6               |     |      |       |

| HIGH Period of SCL Clock                       | tHIGH            | Standard mode | 4.0               |     |      | μs    |

| Setup Time for a Repeated                      |                  | Fast mode     | 0.6               |     |      |       |

| START Condition                                | tsu:sta          | Standard mode | 4.7               |     |      | μs    |

| D-t-    - -  Ti (N-t 10 10)                    |                  | Fast mode     | 0                 |     | 0.9  |       |

| Data Hold Time (Notes 12, 13)                  | thd:dat          | Standard mode | 0                 |     |      | μs    |

| Data Cation Time (Nata 44)                     | to               | Fast mode     | 100               |     |      | 20    |

| Data Setup Time (Note 14)                      | tsu:dat          | Standard mode | 250               |     |      | ns    |

| Rise Time of Both SDA and SCL                  | +5               | Fast mode     | 20 +              |     | 300  | 200   |

| Signals (Note 15)                              | t <sub>R</sub>   | Standard mode | 0.1C <sub>B</sub> |     | 1000 | ns    |

| Fall Time of Both SDA and SCL                  | +-               | Fast mode     | 20 +              |     | 300  | 200   |

| Signals (Note 15)                              | tF               | Standard mode | 0.1C <sub>B</sub> |     | 300  | ns    |

| Setup Time for STOP Condition                  | to 0.7.0         | Fast mode     | 0.6               |     |      | 0     |

| Setup Time for STOL Condition                  | tsu:sto          | Standard mode | 4.0               |     |      | μs    |

| Capacitive Load for Each Bus<br>Line (Note 15) | СВ               |               |                   |     | 400  | рF    |

| I/O Capacitance (SDA, SCL, RST)                | C <sub>I/O</sub> | +25°C         |                   |     | 10   | pF    |

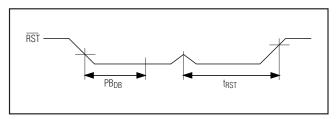

| Pushbutton Debounce                            | PB <sub>DB</sub> |               |                   | 160 | 180  | ms    |

| Reset Active Time                              | trst             |               |                   | 160 | 180  | ms    |

| EEPROM Write Cycle Time                        | twee             |               |                   | 8   | 10   | ms    |

| Oscillator Stop Flag (OSF) Delay (Note 16)     | tosf             |               |                   | 20  |      | ms    |

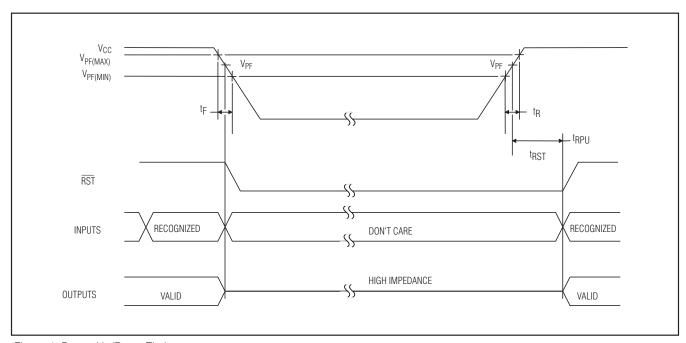

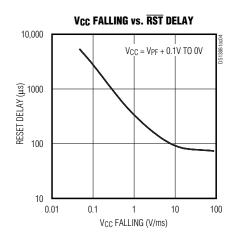

#### POWER-UP/POWER-DOWN CHARACTERISTICS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C) \text{ (Note 1) (Figures 1, 2)}$

| PARAMETER                                                               | SYMBOL           | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------------------------|------------------|------------|-----|-----|-----|-------|

| V <sub>CC</sub> Detect to Recognize Inputs (V <sub>CC</sub> Rising)     | t <sub>RST</sub> | (Note 17)  |     | 160 | 180 | ms    |

| V <sub>CC</sub> Fall Time; V <sub>PF(MAX)</sub> to V <sub>PF(MIN)</sub> | tF               |            | 300 |     |     | μs    |

| V <sub>CC</sub> Rise Time; V <sub>PF(MIN)</sub> to V <sub>PF(MAX)</sub> | t <sub>R</sub>   |            | 0   | •   |     | μs    |

Figure 1. Power-Up/Down Timing

Figure 2. Pushbutton Reset Timing

### WARNING: Under no circumstances are negative undershoots, of any amplitude, allowed when device is in write protection.

- Note 1: Limits at -40°C are guaranteed by design and are not production tested.

- Note 2: All voltages are referenced to ground.

- **Note 3:** Measured at V<sub>CC</sub> = typ, V<sub>BACKUP</sub> = 0V, register 0Ah, block 0h = A5h.

- **Note 4:** The use of the  $250\Omega$  trickle-charge resistor is not allowed at V<sub>CC</sub> > 3.63V and should not be enabled.

- **Note 5:** Measured at V<sub>CC</sub> = typ, V<sub>BACKUP</sub> = 0V, register 0Ah, block 0h = A6h.

- **Note 6:** Measured at  $V_{CC} = typ$ ,  $V_{BACKUP} = 0V$ , register 0Ah, block 0h = A7h.

- **Note 7:** The  $\overline{RST}$  pin has an internal  $50k\Omega$  pullup resistor to  $V_{CC}$ .

- **Note 8:** I<sub>CCA</sub>—SCL clocking at max frequency = 400kHz.

- Note 9: Specified with I<sup>2</sup>C bus inactive.

- Note 10: Measured with a 32.768kHz crystal attached to X1 and X2.

- Note 11: After this period, the first clock pulse is generated.

- Note 12: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 13: The maximum t<sub>HD:DAT</sub> need only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal.

- Note 14: A fast-mode device can be used in a standard-mode system, but the requirement t<sub>SU:DAT</sub> ≥ 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>R(MAX)</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns before the SCL line is released.

- Note 15: C<sub>B</sub>—total capacitance of one bus line in pF.

- Note 16: The parameter t<sub>OSF</sub> is the period of time that the oscillator must be stopped for the OSF flag to be set over the voltage range of 0V ≤ V<sub>CC</sub> ≤ V<sub>CC</sub>(MAX) and 1.3V ≤ V<sub>BACKUP</sub> ≤ 3.7V.

- Note 17: If the oscillator is disabled or stopped, RST goes inactive after t<sub>RST</sub> plus the startup time of the oscillator.

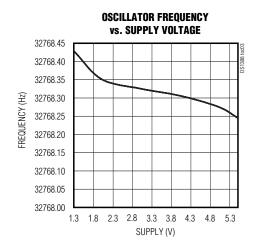

**Typical Operating Characteristics**

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### **Pin Description**

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | X1      | Connections for a Standard 32.768kHz Quartz Crystal. The internal oscillator circuitry is designed for operation with a crystal having a specified load capacitance (C <sub>L</sub> ) of 6.0pF. Pin X1 is the input to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2   | X1      | oscillator and can optionally be connected to an external 32.768kHz oscillator. The output of the internal oscillator, pin X2, is floated if an external oscillator is connected to pin X1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3   | VBACKUP | Connection for a Secondary Power Supply. Supply voltage must be held between 1.3V and 5.5V for proper operation. This pin can be connected to a primary cell, such as a lithium button cell. Additionally, this pin can be connected to a rechargeable cell or a super cap when used with the trickle-charge feature. If not used, this pin must be connected to ground. UL recognized to ensure against reverse charging current when used with a lithium battery ( <a href="https://www.maxim-ic.com/qa/info/ul/">www.maxim-ic.com/qa/info/ul/</a> ).                                                                                                                                          |

| 4   | GND     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5   | SDA     | Serial Data Output. SDA is the input/output for the $I^2C$ serial interface. This pin is open drain and requires an external pullup resistor. The pullup voltage can be up to 5.5V, regardless of the voltage on $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6   | SCL     | Serial Clock Input. SCL is the clock input for the I <sup>2</sup> C interface and is used to synchronize data movement on the serial interface. Up to 5.5V can be used for this pin, regardless of the voltage on V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7   | RST     | Active-Low, Open-Drain Reset Output. This pin indicates the status of $V_{CC}$ relative to the $V_{PF}$ specification. As $V_{CC}$ falls below $V_{PF}$ , the $\overline{RST}$ pin is driven low. When $V_{CC}$ exceeds $V_{PF}$ , for $t_{RST}$ , the $\overline{RST}$ pin is driven high impedance. The active-low, open-drain output is combined with a debounced pushbutton input function. This pin can be activated by a pushbutton reset request. It has an internal $50k\Omega$ nominal value pullup resistor to $V_{CC}$ . No external pullup resistors should be connected. If the crystal oscillator is disabled, the startup time of the oscillator is added to the $t_{RST}$ delay. |

| 8   | Vcc     | DC Power Pin for Primary Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

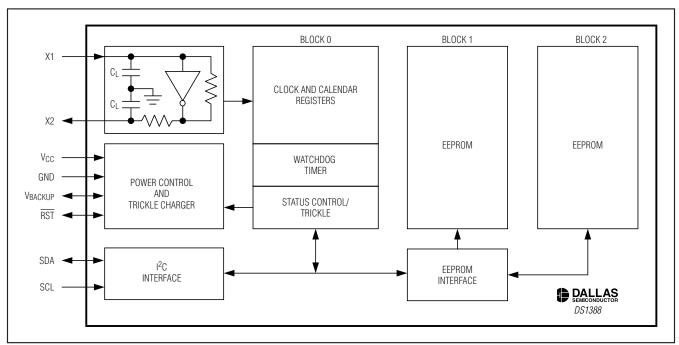

#### **Block Diagram**

#### **Detailed Description**

The DS1388 I<sup>2</sup>C RTC, supervisor, and EEPROM is a multifunction device that provides a clock/calendar. programmable watchdog timer, power-supply monitor with reset, and 512 bytes of EEPROM. The clock provides hundredths of seconds, seconds, minutes, and hours, and operates in 24-hour or 12-hour format with an AM/PM indicator. The calendar provides day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. A watchdog timer provides a reset for an unresponsive microprocessor. It is programmable in 10ms intervals from 0.01 to 99.99 seconds. A temperature-compensated voltage reference and comparator circuit monitors the status of VCC. If a primary power failure is detected, the device automatically switches to the backup supply and drives the reset output to the active state. When VCC returns to nominal levels, the reset is held low for a period to allow the power supply and processor to stabilize. The device also has a pushbutton reset controller, which debounces a reset input signal. The device is accessed through an I<sup>2</sup>C serial interface.

#### **Operation**

The DS1388 operates as a slave device on the I<sup>2</sup>C bus. Access is obtained by implementing a START condition and providing a device identification code followed by data. Subsequent registers can be accessed sequentially until a STOP condition is executed. See the *Block Diagram*, which shows the main elements of the serial real-time clock.

#### **Power Control**

The power-control function is provided by a precise, temperature-compensated voltage reference and a comparator circuit that monitors the V<sub>CC</sub> level. The device is fully accessible and data can be written and read when V<sub>CC</sub> is greater than V<sub>PF</sub>. However, when V<sub>CC</sub> falls below V<sub>PF</sub>, the internal clock registers are blocked from any access. If V<sub>PF</sub> is less than V<sub>BACKUP</sub>, the device power is switched from V<sub>CC</sub> to V<sub>BACKUP</sub> when V<sub>CC</sub> drops below V<sub>PF</sub>. If V<sub>PF</sub> is greater than V<sub>BACKUP</sub>, the device power is switched from V<sub>CC</sub> to

VBACKUP when VCC drops below VBACKUP. The registers are maintained from the VBACKUP source until VCC is returned to nominal levels (Table 1). After VCC returns above VPF, read and write access is allowed after  $\overline{\text{RST}}$  goes high (Figure 1).

On first application of power to the device, the time and date registers are set to 00/00/00 00 00:00:00 (MM/DD/YY DOW HH:MM:SS). The user should initialize all RTC registers to valid date and time settings.

Table 1. Power Control

| SUPPLY CONDITION          | READ/WRITE<br>ACCESS | POWERED<br>BY    |

|---------------------------|----------------------|------------------|

| VCC < VPF, VCC < VBACKPUP | No                   | VBACKUP          |

| VCC < VPF, VCC > VBACKUP  | No                   | Vcc              |

| VCC > VPF, VCC < VBACKUP  | Yes                  | Vcc              |

| VCC > VPF, VCC > VBACKUP  | Yes                  | V <sub>C</sub> C |

#### **Oscillator Circuit**

The DS1388 uses an external 32.768kHz crystal. The oscillator circuit does not require any external resistors or capacitors to operate. Table 2 specifies several crystal parameters for the external crystal. Using a crystal with the specified characteristics, the startup time is usually less than one second.

Table 2. Crystal Specifications\*

| PARAMETER            | SYMBOL | MIN | TYP    | MAX | UNITS |

|----------------------|--------|-----|--------|-----|-------|

| Nominal<br>Frequency | fo     |     | 32.768 |     | kHz   |

| Series<br>Resistance | ESR    |     |        | 50  | kΩ    |

| Load<br>Capacitance  | CL     |     | 6      |     | pF    |

<sup>\*</sup>The crystal, traces, and crystal input pins should be isolated from RF generating signals. Refer to Application Note 58: Crystal Considerations for Dallas Real-Time Clocks for additional specifications.

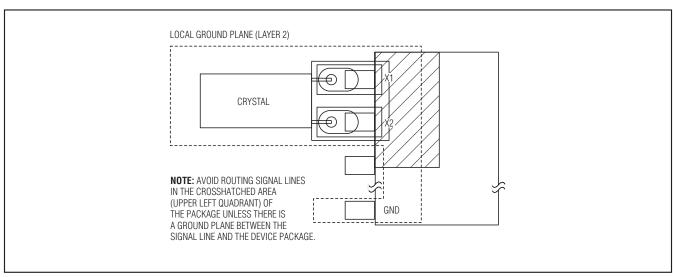

Figure 3. Layout Example

#### Clock Accuracy

The accuracy of the clock is dependent upon the accuracy of the crystal and the accuracy of the match between the capacitive load of the oscillator circuit and the capacitive load for which the crystal was trimmed. Additional error is added by crystal frequency drift caused by temperature shifts. External circuit noise coupled into the oscillator circuit can result in the clock running fast. Figure 3 shows a typical PC board layout for isolation of the crystal and oscillator from noise. Refer to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks for detailed information.

#### Address Map

Figure 4 shows the address map for the DS1388. The memory map is divided into three blocks. The memory block accessed is determined by the value of the block address bits in the slave address byte. The timekeeping registers reside in block 0h. During a multibyte access of the timekeeping registers, when the internal address pointer reaches 0Ch, it wraps around to location 00h. On an I<sup>2</sup>C START or address pointer incrementing to location 00h, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to reread the registers in case the main registers update during a

read. The EEPROM is divided into two 256-byte blocks located in blocks 1h and 2h. During a multibyte read of the EEPROM registers, when the internal address pointer reaches FFh, it wraps around to location 00h of the block of EEPROM specified in the block address. During a multibyte write of the EEPROM registers, when the internal address pointer reaches the end of the current 8-byte EEPROM page, it wraps around to the beginning of the EEPROM page. See the *Write Operation* section for details.

To avoid rollover issues when writing to the time and date registers, all registers should be written before the hundredths-of-seconds register reaches 99 (BCD).

#### Hundredths-of-Seconds Generator

The hundredths-of-seconds generator circuit shown in the *Block Diagram* is a state machine that divides the incoming frequency (4096Hz) by 41 for 24 cycles and 40 for 1 cycle. This produces a 100Hz output that is slightly off during the short term, and is exactly correct every 250ms. The divide ratio is given by:

Ratio =

$$[41 \times 24 + 40 \times 1] / 25 = 40.96$$

Thus, the long-term average frequency output is exactly 100Hz.

| ADD | DRESS  | BIT 7 | BIT 6                   | BIT 5        | BIT 4       | BIT 3  | DIT 0      | BIT 1                               | BIT 0   | FUNCTION                         | RANGE  |

|-----|--------|-------|-------------------------|--------------|-------------|--------|------------|-------------------------------------|---------|----------------------------------|--------|

| BLK | WORD   | BII / | ВПО                     | БПЭ          | BII 4       | ВПЗ    | BIT 2      | ВПП                                 | BII U   | FUNCTION                         | HANGE  |

| 0h  | 00h    |       | Tenth 9                 | enth Seconds |             |        | lundredths | of Secon                            | ds      | Hundredths of Seconds            | 00–99  |

| 0h  | 01h    | 0     |                         | 10 Secon     | ds          |        | Sec        | onds                                |         | Seconds                          | 00–59  |

| 0h  | 02h    | 0     |                         | 10 Minute    | es          |        | Min        | utes                                |         | Minutes                          | 00–59  |

| Oh  | 03h    | 0     | 12/24                   | AM/<br>PM    | PM 10 Hours |        | Hours      | 1–12+<br><del>AM</del> /PM<br>00–23 |         |                                  |        |

| 0h  | 04h    | 0     | 0                       | 0            | Hour<br>0   | X      |            | Dav                                 |         | Dov                              | 01-07  |

|     |        | _     | _                       |              |             | ^      |            |                                     |         | Day                              |        |

| 0h  | 05h    | 0     | 0                       | 10           | Date        |        | Da         | ate                                 |         | Date                             | 01–31  |

| 0h  | 06h    | 0     | 0                       | X            | 10<br>Month |        | Мс         | onth                                |         | Month                            | 01–12  |

| 0h  | 07h    |       | 10 Year                 |              |             |        | Ye         | ear                                 |         | Year                             | 00–99  |

| 0h  | 08h    | Watc  | chdog Tenths of Seconds |              |             | Watch  | dog Hundr  | edths of S                          | Seconds | Watchdog<br>Hundredth<br>Seconds | 00–99  |

| 0h  | 09h    | Wato  | chdog Ter               | nths of Se   | econds      |        | Watchdog   | g Seconds                           | 3       | Watchdog<br>Seconds              | 00–99  |

| 0h  | 0Ah    | TCS3  | TCS2                    | TCS1         | TCS0        | DS1    | DS0        | ROUT1                               | ROUT0   | Trickle Charger                  | _      |

| 0h  | 0Bh    | OSF   | WF                      | 0            | 0           | 0      | 0 0 0 0    |                                     |         | Flag                             | _      |

| 0h  | 0Ch    | EOSC  | 0                       | 0            | 0           | 0      | 0          | WDE                                 | WD/RST  | Control                          | _      |

| 1h  | 00-FFh |       | 256 x 8                 |              |             | EEPROM |            |                                     |         | EEPROM                           | 00-FFh |

| 2h  | 00-FFh |       | 256 x 8                 |              |             | EEPROM |            |                                     |         | EEPROM                           | 00-FFh |

Figure 4. Address Map

Note: Unless otherwise specified, the state of the registers is not defined when power (VCC and VBACKUP) is first applied.

X = General-purpose read/write bit.

0 = Always reads as a zero.

#### **Clock and Calendar**

The time and calendar information is obtained by reading the appropriate register bytes. Figure 4 illustrates the RTC registers. The time and calendar are set or initialized by writing the appropriate register bytes. The contents of the time and calendar registers are in the binary-coded decimal (BCD) format. The end of the month date is automatically adjusted for months with fewer than 31 days, including corrections for leap years through 2099. The day-of-week register increments at midnight. Values that correspond to the day-of-week

are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in undefined operation. The DS1388 can be run in either 12-hour or 24-hour mode. Bit 6 of the hours register is defined as the 12- or 24-hour mode-select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the  $\overline{\rm AM/PM}$  bit with logic-high being PM. In the 24-hour mode, bit 5 is the second 10-hour bit (20–23 hours). Changing the  $12/\overline{24}$  bit requires that the hours data be re-entered in the proper format.

#### **Watchdog Alarm Counter**

The contents of the watchdog alarm counter, which is a separate two-byte BCD down counter, are accessed in the address range 08h–09h in block 0h. It is programmable in 10ms intervals from 0.01 to 99.99 seconds. When this counter is written, both the counter and a seed register are loaded with the desired value. When the counter is to be reloaded, it uses the value in the seed register. When the counter is read, the current counter value is latched into a register, which is output on the serial data line and the watchdog counter reloads the seed value.

If the counter is not needed, it can be disabled and used as a 16-bit cache of battery-backed RAM by setting the WDE bit in the control register to logic 0. If all 16 bits of the watchdog alarm counter are written to a zero when WDE = 1, the counter is disabled and the WF bit is not set.

When the WDE bit in the control register is set to a logic 1 and a non-zero value is written into the watchdog registers, the watchdog alarm counter decrements every 1/100 second, until it reaches zero. At this point, the WF bit in the flag register is set. If WD/RST = 1, the RST pin is pulsed low for trast and access to the DS1388 is inhibited. At the end of trast, the RST pin becomes high impedance, and read/write access to the DS1388 is enabled. The WF flag remains set until cleared by writing WF to logic 0. The watchdog alarm counter can be reloaded and restarted before the counter reaches zero by reading or writing any of the watchdog alarm counter registers.

The WF flag and WDE bit must be set to zero before writing the watchdog registers. After writing the watchdog registers, WDE must be set to one to enable the watchdog.

### Power-Up/Down, Reset, and Pushbutton Reset Functions

A precision temperature-compensated reference and comparator circuit monitors the status of V<sub>CC</sub>. When an out-of-tolerance condition occurs, an internal power-fail signal is generated that blocks read/write access to the device and forces the  $\overline{\rm RST}$  pin low. When V<sub>CC</sub> returns to an in-tolerance condition, the internal power-fail signal is held active for t<sub>RST</sub> to allow the power supply to stabilize, and the  $\overline{\rm RST}$  pin is held low. If the  $\overline{\rm EOSC}$  bit is set to a logic 1 (to disable the oscillator in battery-back-up mode), the internal power-fail signal and the  $\overline{\rm RST}$  pin are kept active for t<sub>RST</sub> plus the oscillator startup time.

Access is inhibited whenever RST is low.

The DS1388 provides for a pushbutton switch to be connected to the  $\overline{RST}$  output pin. When the DS1388 is not in a reset cycle, it continuously monitors the  $\overline{RST}$  signal for a low-going edge. If an edge is detected, the part debounces the switch by pulling the  $\overline{RST}$  pin low and inhibits read/write access. After the internal timer has expired, the part continues to monitor the  $\overline{RST}$  line. If the line is still low, it continues to monitor the line looking for a rising edge. Upon detecting release, the part forces the  $\overline{RST}$  pin low and holds it low for trest.

#### Special-Purpose Registers

The DS1388 has three additional registers (control, flag, and trickle charger) that control the real-time clock, watchdog, and trickle charger.

Flag Register (00Bh)

Bit 7: Oscillator Stop Flag (OSF). A logic 1 in this bit indicates that the oscillator has stopped or was stopped for some period of time and may be used to judge the validity of the clock and calendar data. This bit is edge triggered and is set to logic 1 when the internal circuitry senses the oscillator has transitioned from a normal run state to a STOP condition. The following are examples of conditions that can cause the OSF bit to be set:

- 1) The first time power is applied.

- 2) The voltage present on both VCC and VBACKUP are insufficient to support oscillation.

- 3) The EOSC bit is turned off.

- 4) External influences on the crystal (i.e., noise, leakage, etc.).

This bit remains at logic 1 until written to logic 0. This bit can only be written to logic 0. Attempting to write OSF to logic 1 leaves the value unchanged.

**Bit 6: Watchdog Alarm Flag (WF).** A logic 1 in this bit indicates that the watchdog counter reached zero. If WDE and WD/RST are set to 1, the RST pin pulses low for tRST when the watchdog counter reaches zero and sets WF = 1. At the completion of the pulse, the WF bit remains set to logic 1. Writing this bit to logic 0 clears the WF flag. This bit can only be written to logic 0. Attempting to write logic 1 leaves the value unchanged.

Bits 5 to 0: These bits read as zero and cannot be modified.

#### Flag Register (00Bh)

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| OSF   | WF    | 0     | 0     | 0     | 0     | 0     | 0     |

#### **Control Register (00Ch)**

| DIT 7 | DIT   | DIT 6 | DIT 4 | DIT   | DIT   | DIT 4 | DITO   |

|-------|-------|-------|-------|-------|-------|-------|--------|

| BIT 7 | BIT 6 | BII 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BII 0  |

| EOSC  | 0     | 0     | 0     | 0     | 0     | WDE   | WD/RST |

#### **Control Register (00Ch)**

**Bit 7: Enable Oscillator** (EOSC). When set to logic 0, the oscillator is started. When set to logic 1, the oscillator is stopped when the DS1388 switches to battery power. This setting can be used to conserve battery power when timekeeping operation is not required. This bit is cleared (logic 0) when power is first applied. When the DS1388 is powered by V<sub>CC</sub>, the oscillator is always on regardless of the status of the EOSC bit. The clock can be halted whenever the timekeeping functions are not required, which minimizes V<sub>BAT</sub> current (I<sub>BACKUPDR</sub>).

Bits 6 to 2: These bits read as zero and cannot be modified.

**Bit 1: Watchdog Enable (WDE).** When set to logic one, the watchdog counter is enabled. When set to logic 0, the watchdog counter is disabled, and the two registers can be used as NV RAM. This bit is cleared (logic 0) when power is first applied.

**Bit 0: Watchdog Reset (WD/RST).** This bit enables the watchdog alarm output to drive the RST pin. When the WD/RST bit is set to logic 1, RST pulses low for tRST if WDE = 1 and the watchdog counter reaches zero. When the WD/RST bit is set to logic 0, the RST pin is not driven by the watchdog alarm; only the watchdog flag bit (WF) in the flag register is set to logic 1. This bit is logic 0 when power is first applied.

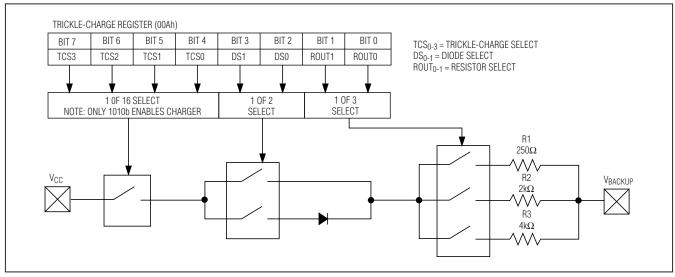

#### Trickle-Charge Register (00Ah)

The simplified schematic of Figure 5 shows the basic components of the trickle charger. The trickle-charge

select (TCS) bits (bits 4–7) control the selection of the trickle charger. To prevent accidental enabling, only a pattern on 1010 enables the trickle charger. All other patterns disable it. The trickle charger is disabled when power is first applied. The diode-select (DS) bits (bits 2 and 3) select whether or not a diode is connected between VCC and VBACKUP. If DS is 01, no diode is selected, yet if DS is 10, a diode is selected. The ROUT bits (bits 0 and 1) select the value of the resistor connected between VCC and VBACKUP. Table 3 shows the resistor selected by the resistor select (ROUT) bits and the diode selected by the diode-select (DS) bits.

**Warning:** The ROUT value of  $250\Omega$  must not be selected whenever V<sub>CC</sub> is greater than 3.63V.

The user determines the diode and resistor selection according to the maximum current desired for battery or super cap charging. The maximum charging current can be calculated as illustrated in the following example. Assume that a system power supply of 3.3V is applied to VCC and a super cap is connected to VBACKUP. Also, assume that the trickle charger has been enabled with a diode and resistor R2 between VCC and VBACKUP. The maximum current IMAX would be calculated as follows:

$I_{MAX} = (3.3V - diode drop) / R2 \approx (3.3V - 0.7V) / 2k\Omega \approx 1.3mA$

As the super cap charges, the voltage drop between VCC and VBACKUP decreases and therefore the charge current decreases.

**Table 3. Trickle-Charge Register**

| TCS3 | TCS2 | TCS1 | TCS0 | DS1 | DS0 | ROUT1 | ROUT0 | FUNCTION                        |

|------|------|------|------|-----|-----|-------|-------|---------------------------------|

| X    | Χ    | Χ    | Χ    | 0   | 0   | Χ     | Χ     | Disabled                        |

| X    | Χ    | Χ    | Χ    | 1   | 1   | Χ     | Χ     | Disabled                        |

| Х    | Χ    | Χ    | Χ    | Χ   | Χ   | 0     | 0     | Disabled                        |

| 1    | 0    | 1    | 0    | 0   | 1   | 0     | 1     | No diode, $250\Omega$ resistor  |

| 1    | 0    | 1    | 0    | 1   | 0   | 0     | 1     | One diode, $250\Omega$ resistor |

| 1    | 0    | 1    | 0    | 0   | 1   | 1     | 0     | No diode, 2kΩ resistor          |

| 1    | 0    | 1    | 0    | 1   | 0   | 1     | 0     | One diode, $2k\Omega$ resistor  |

| 1    | 0    | 1    | 0    | 0   | 1   | 1     | 1     | No diode, $4k\Omega$ resistor   |

| 1    | 0    | 1    | 0    | 1   | 0   | 1     | 1     | One diode, $4k\Omega$ resistor  |

| 0    | 0    | 0    | 0    | 0   | 0   | 0     | 0     | Initial default value—disabled  |

Figure 5. Programmable Trickle Charger

#### **EEPROM**

The DS1388 provides 512 bytes of EEPROM organized into two blocks of 256 bytes. Each 256-byte block is divided into 32 pages consisting of 8 bytes per page. The EEPROM can be written one page at a time. Page write operations are limited to writing bytes within a single physical page, regardless of the number of bytes actually being written. Physical page boundaries start at addresses that are integer multiples of the page size (8 bytes) and end at addresses that are integer multiples of [page size -1]. For example, page 0 contains word addresses 00h to 07h. Similarly, page 1 contains word addresses 08h to 0Fh. If a page write command attempts to write across a physical page boundary, the result is that the data wraps around to the beginning of the current page (overwriting data previously stored there), instead of being written to the next page as might be expected. Therefore, it is necessary for the application software to prevent page write operations that would attempt to cross a page boundary.

#### I<sup>2</sup>C Serial Data Bus

The DS1388 supports a bidirectional I<sup>2</sup>C bus and data transmission protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data is defined as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are slaves. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The DS1388

operates as a slave on the  $I^2C$  bus. Connections to the bus are made through the open-drain I/O lines SDA and SCL. Within the bus specifications, a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. The DS1388 works in both modes.

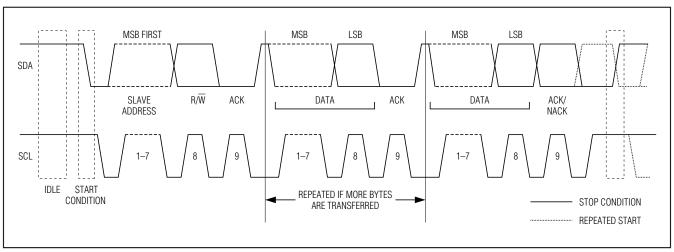

The following bus protocol has been defined (Figure 6):

- Data transfer can be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is high. Changes in the data line while the clock line is high will be interpreted as control signals.

Accordingly, the following bus conditions have been defined:

**Bus not busy:** Both data and clock lines remain high.

**Start data transfer:** A change in the state of the data line from high to low, while the clock line is high, defines a START condition.

**Stop data transfer:** A change in the state of the data line from low to high, while the clock line is high, defines a STOP condition.

**Data valid:** The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the high period of the clock signal. The data on the line must be changed during the low period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between the START and the STOP conditions is not limited, and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge (ACK) after the reception of each byte. The master device must generate an extra clock pulse, which is associated with this acknowledge bit. The DS1388 does not generate any acknowledge bits if access to the EEPROM is attempted during an internal programming cycle.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable low during the high period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by generating a not-acknowledge (NACK) bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line high to enable the master to generate the STOP condition.

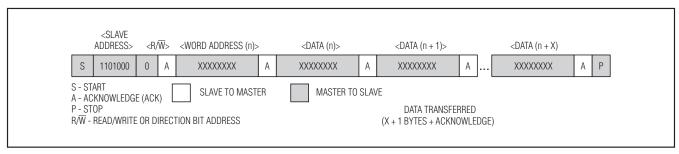

Figures 7 and 8 detail how data transfer is accomplished on the  $I^2C$  bus. Depending upon the state of the  $R\overline{W}$  bit, two types of data transfer are possible:

Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data are transferred with the most significant bit (MSB) first.

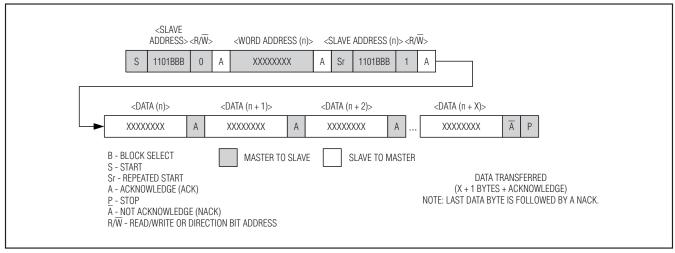

Data transfer from a slave transmitter to a master receiver. The first byte (the slave address) is transmitted by the master. The slave then returns an acknowledge bit. Next follows a number of data bytes transmitted by the slave to the master. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a NACK is returned.

The master device generates all the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus is not released. Data are transferred with the most significant bit (MSB) first.

Figure 6. I<sup>2</sup>C Data Transfer Overview

#### **Device Addressing**

The slave address byte is the first byte received following the START condition from the master device. The slave address byte consists of a 4-bit control code. For the DS1388, this is set as 1101 binary for read and write operations. The next three bits of the slave address byte are the block select bits (B2, B1, B0). B2 is always logic 0 for the DS1388. These bits are used by the master device to select which of the three blocks in the memory map are to be accessed. These bits are the three most significant bits of the word address. The last bit of the slave address byte defines the operation to be performed. When set to 1, a read operation is selected; when set to 0, a write operation is selected.

#### Write Operation

#### Slave Receiver Mode (Write Mode)

Following the START condition from the master, the device code (4 bits); the block address (3 bits); and the R/W bit, which is logic-low, is placed onto the bus by the master transmitter. This indicates to the DS1388 that a byte with a word address follows after the DS1388 has generated an acknowledge bit during the ninth clock cycle. The next byte transmitted by the master is the word address and will set the internal address pointer of the DS1388, with the DS1388 acknowledging the transfer on the ninth clock cycle. The master device can then transmit zero or more bytes of data, with the DS1388 acknowledging the transfer on the ninth clock cycle. The master generates a STOP condition to terminate the data write.

#### **Byte Write**

The write-slave address byte and word address are transmitted to the DS1388 as described in the *Slave*

Receiver Mode section. The master transmits one data byte, with the DS1388 acknowledging the transfer on the ninth clock cycle. The master then generates a STOP condition to terminate the data write. This initiates the internal write cycle, and, if the write was to the EEPROM, the DS1388 does not generate acknowledge signals during the internal EEPROM write cycle.

#### **EEPROM Page Write**

The write-slave address byte, word address, and the first data byte are transmitted to the DS1388 in the same way as in a byte write. But instead of generating a STOP condition, the master transmits up to 8 data bytes to the DS1388, which are temporarily stored in the on-chip page buffer and are written into the memory after the master has transmitted a STOP condition. Data bytes within the page that are not written remain unchanged. The internal address pointer automatically increments after each byte is written.

If the master should transmit more than 8 data bytes prior to generating the STOP condition, the address pointer rolls over and the previously received data is overwritten. As with the byte write operation, once the STOP condition is received an internal write cycle begins.

#### **RTC Multibyte Write**

Writing multiple bytes to the RTC works much the same way as the EEPROM page write, except that the entire contents of block 0h can be written at once. The 8-byte page size limitation does not apply to the block 0. If the master should transmit more bytes than exists in block 0 prior to generating the STOP condition, the internal address pointer rolls over and the previously received data is overwritten. As with the byte write operation, once the STOP condition is received an internal write cycle begins.

#### Slave Address Byte

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|

| 1     | 1     | 0     | 1     | B2    | B1    | В0    | R/W   |  |

| OPERATION                   | CONTROL CODE | BLOCK SELECT | R/W |

|-----------------------------|--------------|--------------|-----|

| Read Clock                  | 1101         | 000          | 1   |

| Write Clock                 | 1101         | 000          | 0   |

| Read Lower Block of EEPROM  | 1101         | 001          | 1   |

| Write Lower Block of EEPROM | 1101         | 001          | 0   |

| Read Upper Block of EEPROM  | 1101         | 010          | 1   |

| Write Upper Block of EEPROM | 1101         | 010          | 0   |

#### Acknowledge Polling

Since the DS1388 does not acknowledge during an EEPROM write cycle, acknowledge polling can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the master issues the STOP condition for a write command, the DS1388 initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master sending a START condition, followed by the slave address byte for a write command ( $R/\overline{W}=0$ ) to the EEPROM. If the device is still busy with the write cycle, then a NACK is returned. If the cycle is complete, then the device returns the ACK and the master can then proceed with the next read or write command. The RTC registers in block 0 are accessible during an EEPROM write cycle.

#### **Read Operation**

Read operations are initiated in the same  $\underline{w}$ ay as write operations with the exception that the R/W bit of the slave address is set to 1. There are three basic types of read operations: current address read, random read, and sequential read.

#### **Current Address Read**

The DS1388 contains an address pointer that maintains the last address accessed, internally incremented by 1. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n+1. Upon receipt of the slave address with the  $R/\overline{W}$  bit set to 1, the DS1388 issues an acknowledge and transmits the 8-bit data byte. The master issues a NACK followed by a STOP condition, and the DS1388 discontinues transmission.

#### **Random Read**

Random read operations allow the master to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the DS1388 as part of a write operation. After the word address is sent, the master generates a START condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the slave address byte again but with the R/W bit set to 1. The DS1388 then issues an acknowledge and transmits the 8-bit data byte. The master issues a NACK followed by a STOP condition, and the DS1388 discontinues transmission.

#### **Sequential Read**

Sequential reads are initiated in the same way as a random read except that after the DS1388 transmits the first data byte, the master issues an acknowledge as opposed to a STOP condition in a random read. This directs the DS1388 to transmit the next sequentially addressed 8-bit byte. To provide sequential reads, the DS1388 contains an internal address pointer, which is incremented by one at the completion of each operation. This allows the entire memory contents of the block specified in the slave address to be serially read during one operation. The master terminates the read by generating a NACK followed by a STOP condition.

No page boundaries exist for read operations. When the address pointer reaches the end of an EEPROM block (FFh), the address pointer wraps to the beginning (00h) of the same block.

The DS1388 can operate in the two modes illustrated in Figures 7 and 8.

Figure 7. Data Write—Slave Receiver Mode

|                              | SLAVE<br>ODRESS>         | <r <="" th=""><th><math>\overline{\mathbb{W}}&gt;</math></th><th><data (n)=""></data></th><th></th><th><data (n="" +="" 1)=""></data></th><th></th><th><data (n="" +="" 2)=""></data></th><th></th><th><data (n="" +="" x)=""></data></th><th></th><th></th></r> | $\overline{\mathbb{W}}>$ | <data (n)=""></data> |   | <data (n="" +="" 1)=""></data> |   | <data (n="" +="" 2)=""></data>                            |        | <data (n="" +="" x)=""></data> |   |   |

|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------|---|--------------------------------|---|-----------------------------------------------------------|--------|--------------------------------|---|---|

| S 11                         | 101BBB                   | 1                                                                                                                                                                                                                                                                | А                        | XXXXXXX              | А | XXXXXXX                        | А | XXXXXXX                                                   | Α      | XXXXXXXX                       | Ā | Р |

| <u>P</u> - STOP<br>A - NOT A | T<br>OWLEDGE<br>ACKNOWLE | DGE (                                                                                                                                                                                                                                                            | (NACK)                   | MASTER TO SLAVE      |   | SLAVE TO MASTE                 |   | DATA TRANSF<br>(X + 1 BYTES + ACK<br>LAST DATA BYTE IS FO | NOWLED |                                |   |   |

Figure 8. Data Read—Slave Transmitter Mode

Figure 9. Data Write/Read (Write Pointer, Then Read)—Slave Receive and Transmit

#### Thermal Information

Theta-JA: +170°C/W Theta-JC: +40°C/W

Chip Information

TRANSISTOR COUNT: 25,527

SUBSTRATE CONNECTED TO GROUND

PROCESS: CMOS

#### \_Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |  |  |

|--------------|--------------|----------------|--|--|

| 8 SO         | _            | <u>21-0041</u> |  |  |

#### \_Revision History

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                            | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 4/05             | Initial release.                                                                                                                                                                                                                                                       | _                |

|                    |                  | Removed the leaded parts from the Ordering Information.                                                                                                                                                                                                                | 1                |

|                    |                  | Indicated the pullup voltage for SDA and SCL in the Pin Description table.                                                                                                                                                                                             | 8                |

|                    |                  | Added the oscillator bias circuit to the <i>Block Diagram</i> and removed the original Figure 3.                                                                                                                                                                       | 8, 10            |

|                    |                  | Added time and date POR values in the <i>Power Control</i> section.                                                                                                                                                                                                    | 9                |

| 1                  | 9/08             | Changed the last sentence of the <i>Watchdog Alarm Counter</i> section (first paragraph) to "When the counter is read, the current counter value is latched into a register, which is output on the serial data line and the watchdog counter reloads the seed value." | 12               |

|                    |                  | Added "Access is inhibited whenever RST is low." To the end of the <i>Power-Up/Down, Reset, and Pushbutton Reset Functions</i> section (first paragraph).                                                                                                              | 12               |

|                    |                  | In the Control Register (00Ch) section, bit 7 description, added a statement that EOSC is used to reduce VBAT current when timekeeping is not required.                                                                                                                | 13               |

|                    |                  | Replaced the I <sup>2</sup> C read and write figures.                                                                                                                                                                                                                  | 17, 18           |

|                    |                  | Corrected the RTC power-on default values in the Power Control section.                                                                                                                                                                                                | 9                |

| 2                  | 10/09            | Corrected the date register range in Figure 4.                                                                                                                                                                                                                         | 11               |

|                    |                  | Added WF flag clear to the Watchdog Alarm Counter section.                                                                                                                                                                                                             | 12               |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.