Wireless Components

Edition 2002-11-28

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 11/29/02. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# TDA5255 E1 ASK/FSK 434MHz Wireless Transceiver

# Wireless Components

# Preliminary Specification Confidential

| Revision History: | 2002-11-28 | TDA5255 E1 |

|-------------------|------------|------------|

|-------------------|------------|------------|

| Previous | Version: 1.0, 2002-10-30                                 |

|----------|----------------------------------------------------------|

| Page     | Subjects (major changes since last revision)             |

| 12       | Wrong pin names and description at pin 7 and 8 corrected |

| 13       | Additional note at pin 15                                |

| 14,15    | Correction of pin names                                  |

| 31       | Serial resistor in VDD supply line                       |

| 85       | Serial resistor in VDD supply line                       |

| 87       | Serial resistor in VDD supply line                       |

|          |                                                          |

|          |                                                          |

|          |                                                          |

|          |                                                          |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM<sup>®</sup>, AOP<sup>®</sup>, ARCOFI<sup>®</sup>, ARCOFI<sup>®</sup>-BA, ARCOFI<sup>®</sup>-SP, DigiTape<sup>®</sup>, EPIC<sup>®</sup>-1, EPIC<sup>®</sup>-S, ELIC<sup>®</sup>, FALC<sup>®</sup>54, FALC<sup>®</sup>56, FALC<sup>®</sup>-E1, FALC<sup>®</sup>-LH, IDEC<sup>®</sup>, IOM<sup>®</sup>, IOM<sup>®</sup>-1, IOM<sup>®</sup>-2, IPAT<sup>®</sup>-2, ISAC<sup>®</sup>-P, ISAC<sup>®</sup>-S, ISAC<sup>®</sup>-S TE, ISAC<sup>®</sup>-P TE, ITAC<sup>®</sup>, IWE<sup>®</sup>, MUSAC<sup>®</sup>-A, OCTAT<sup>®</sup>-P, QUAT<sup>®</sup>-S, SICAT<sup>®</sup>, SICOFI<sup>®</sup>, SICOFI<sup>®</sup>-2, SICOFI<sup>®</sup>-4, SICOFI<sup>®</sup>-4μC, SLICOFI<sup>®</sup> are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

Controller Area Network (CAN): License of Robert Bosch GmbH

# ASK/FSK 434MHz Wireless Transceiver TDA5255 E1

#### Version 1.1

## **Product Info**

#### **General Description**

The IC is a low power consumption single chip FSK/ASK Transceiver for half duplex low datarate communication in the 433-435MHz band. The IC offers a very high level of integration and needs only a few external components. It contains a highly efficient power amplifier, a low noise amplifier (LNA) with AGC, a double balanced mixer, a complex direct conversion stage, I/Q limiters with RSSI generation, an FSK demodulator, a fully integrated VCO and PLL synthesizer, a tuneable crystal oscillator, an onboard data filter, a data comparator (slicer), positive and negative peak detectors, a data rate detection circuit and a 2/3-wire bus interface. Additionally there is a power down feature to save battery power.

#### **Features**

- Low supply current (I<sub>s</sub> = 9mA typ. receive, I<sub>s</sub>

= 13mA typ. transmit mode)

- Supply voltage range 2.1 5.5V

- Power down mode with very low supply current consumption

- FSK and ASK modulation and demodulation capability

- Fully integrated VCO and PLL synthesizer and loop filter on-chip with on chip crystal oscillator tuning

- I<sup>2</sup>C/3-wire μController Interface

- On-chip low pass channel select filter and data filter with tuneable bandwidth

- Data slicer with self-adjusting threshold and 2 peak detectors

- FSK sensitivity <-109dBm, ASK sensitivity < -109dBm

- Transmit power up to +13dBm

- Datarates up to 100kBit/s Manchester Encoded

- Self-polling logic with ultra fast data rate detection

## **Application**

- Low Bitrate Communication Systems

- Keyless Entry Systems

- Remote Control Systems

- Alarm Systems

- Telemetry Systems

- Electronic Metering

- Home Automation Systems

| Туре       | Ordering Code | Package      |

|------------|---------------|--------------|

| TDA5255 E1 |               | P-TSSOP-38-1 |

# **Table of Contents**

| 1                             | Product Description                       | page<br>8 |

|-------------------------------|-------------------------------------------|-----------|

| 1.1                           | Overview                                  | 8         |

| 1.2                           | Features                                  | 8         |

|                               |                                           | 9         |

| 1.3                           | Application                               | _         |

| 1.4                           | Package Outlines                          | 9         |

| 2                             | Functional Description                    | 10        |

| 2.1                           | Pin Configuration                         | 10        |

| 2.2                           | Pin Definitions and Functions             | 11        |

| 2.3                           | Functional Block Diagram                  | 17        |

| 2.4                           | Functional Block Description              | 18        |

| 2.4.1                         | Power Amplifier (PA)                      | 18        |

| 2.4.2                         | Low Noise Amplifier (LNA)                 | 18        |

| 2.4.3                         | Downconverter 1 <sup>st</sup> Mixer       | 18        |

| 2.4.4                         | Downconverter 2 <sup>nd</sup> I/Q Mixers  | 18        |

| 2.4.5                         | PLL Synthesizer                           | 19        |

| 2.4.6                         | I/Q Filters                               | 19        |

| 2.4.7                         | I/Q Limiters                              | 20        |

| 2.4.8                         | FSK Demodulator                           | 20        |

| 2.4.9                         | Data Filter                               | 21        |

| 2.4.10                        | Data Slicer                               | 21        |

| 2.4.11                        | Peak Detectors                            | 21        |

| 2.4.12                        | Crystal Oscillator                        | 21        |

| 2.4.13                        | Bandgap Reference Circuitry and Powerdown | 22        |

| 2.4.14                        | Timing and Data Control Unit              | 22        |

| 2.4.15                        | Bus Interface and Register Definition     | 23        |

| 2.4.16                        | Wakeup Logic                              | 30        |

| 2.4.17                        | Data Valid Detection, Data Pin            | 31        |

| 2.4.18                        | Sequence Timer                            | 32        |

| 2. <del>4</del> .10<br>2.4.19 | Clock Divider                             | 34        |

| 2.4.19                        | RSSI and Supply Voltage Measurement       | 35        |

| 3                             | Application                               | 37        |

|                               |                                           |           |

| 3.1                           | LNA and PA Matching                       | 37        |

| 3.1.1                         | RX/TX Switch                              | 37        |

| 3.1.2                         | Switch in RX-Mode                         | 37        |

| 3.1.3                         | Switch in TX-Mode                         | 40        |

| 3.1.4                         | Power-Amplifier                           | 42        |

| 3.2                           | Crystal Oscillator                        | 48        |

# **Table of Contents**

| 3.2.1  | Synthesizer Frequency setting                    | page<br>51 |

|--------|--------------------------------------------------|------------|

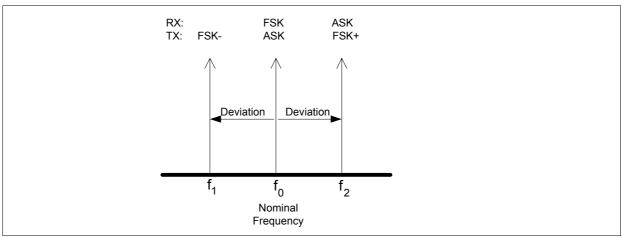

| 3.2.2  | Transmit/Receive ASK/FSK Frequency Assignment    | 51         |

| 3.2.3  | Parasitics                                       | 53         |

| 3.2.4  | Calculation of the external capacitors           | 55         |

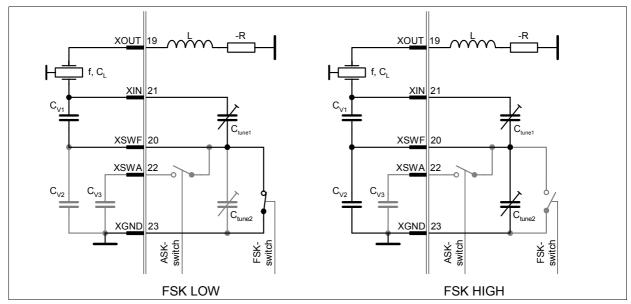

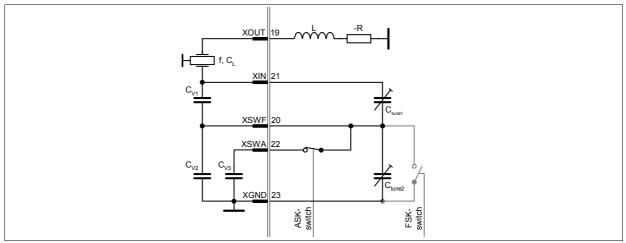

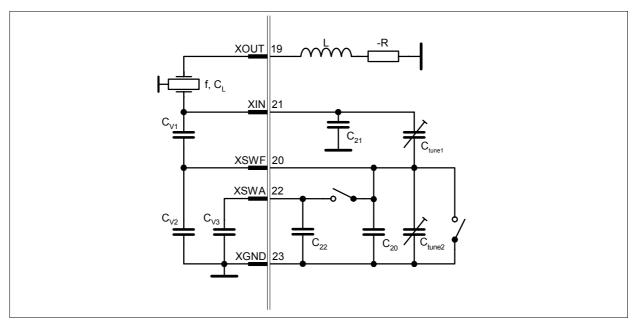

| 3.2.5  | FSK-switch modes                                 | 55         |

| 3.2.6  | Finetuning and FSK modulation relevant registers | 56         |

| 3.2.7  | Chip and System Tolerances                       | 57         |

| 3.3    | IQ-Filter                                        | 58         |

| 3.4    | Data Filter                                      | 59         |

| 3.5    | Limiter and RSSI                                 | 60         |

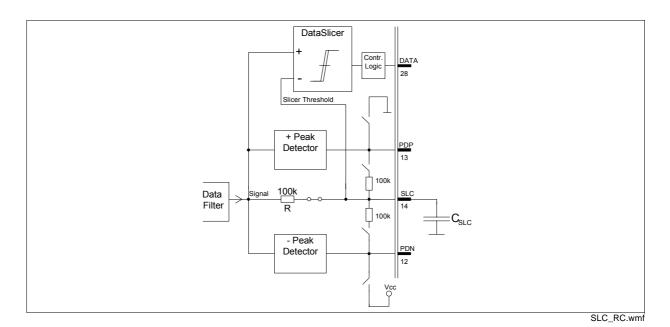

| 3.6    | Data Slicer - Slicing Level                      | 62         |

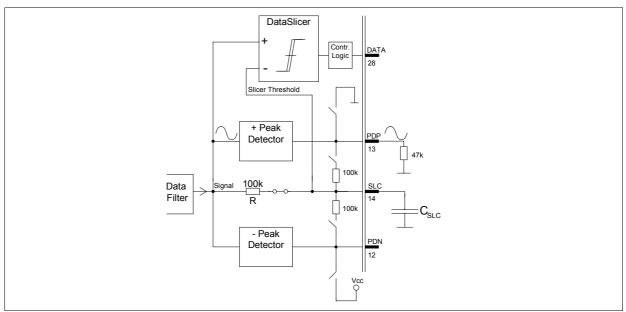

| 3.6.1  | RC Integrator                                    | 62         |

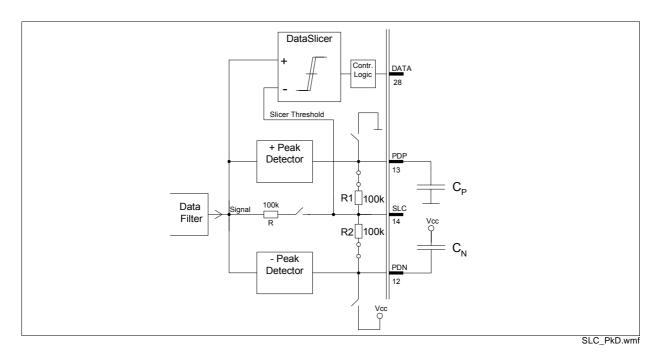

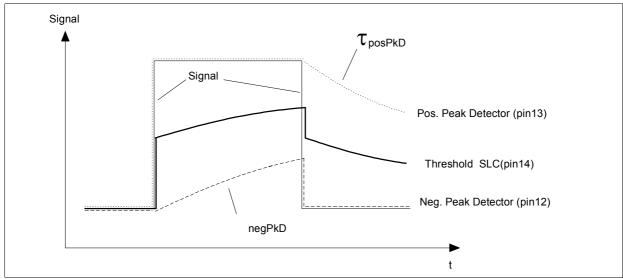

| 3.6.2  | Peak Detectors                                   | 63         |

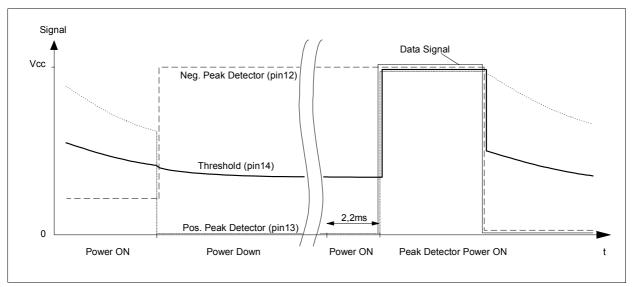

| 3.6.3  | Peak Detector - Analog output signal             | 65         |

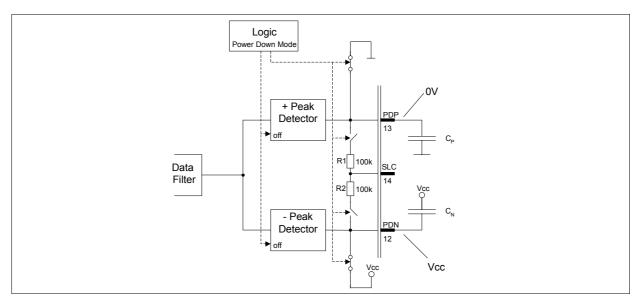

| 3.6.4  | Peak Detector – Power Down Mode                  | 65         |

| 3.7    | Data Valid Detection                             | 66         |

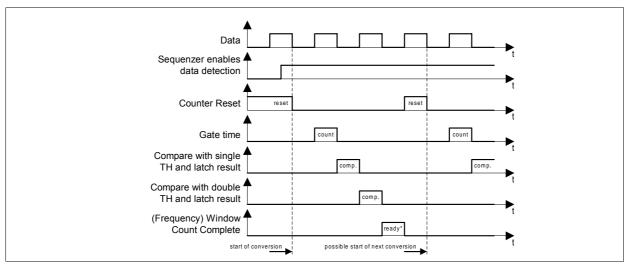

| 3.7.1  | Frequency Window for Data Rate Detection         | 68         |

| 3.7.2  | RSSI threshold voltage - RF input power          | 69         |

| 3.8    | Calculation of ON_TIME and OFF_TIME              | 69         |

| 3.9    | Example for Self Polling Mode                    | 70         |

| 3.10   | Sensitivity Measurements                         | 71         |

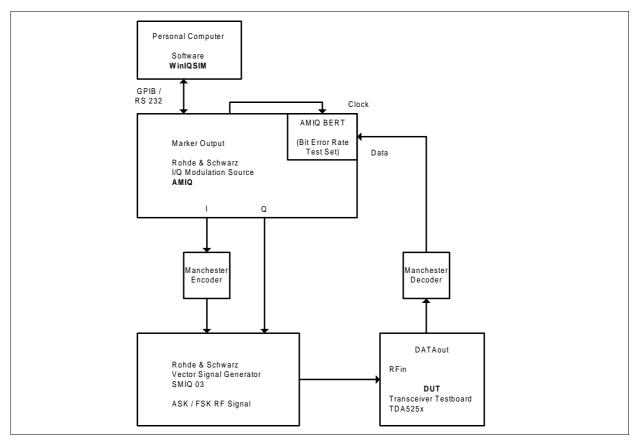

| 3.10.1 | Test Setup                                       | 71         |

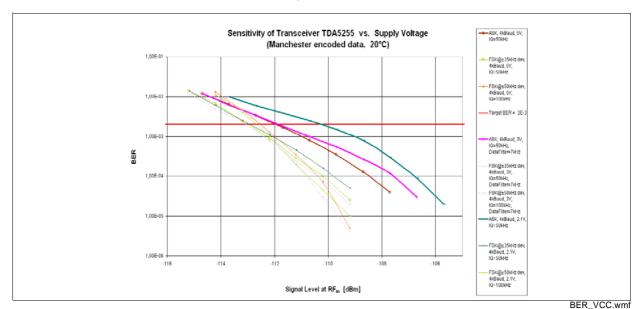

| 3.10.2 | BER performance depending on Supply Voltage      | 73         |

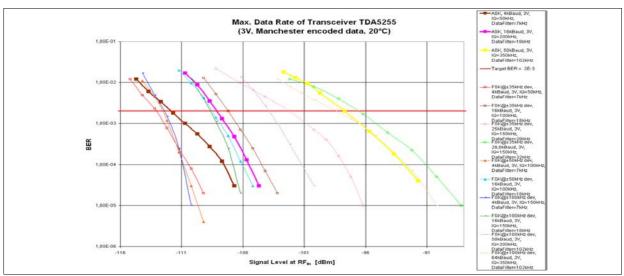

| 3.10.3 | Datarates and Sensitivity                        | 74         |

| 3.11   | Default Setup                                    | 75         |

| 4      | Reference                                        | 77         |

| 4.1    | Electrical Data                                  | 77         |

| 4.1.1  | Absolute Maximum Ratings                         | 77         |

| 4.1.2  | Operating Range                                  | 77         |

| 4.1.3  | AC/DC Characteristics                            | 78         |

| 4.1.4  | Digital Characteristics                          | 81         |

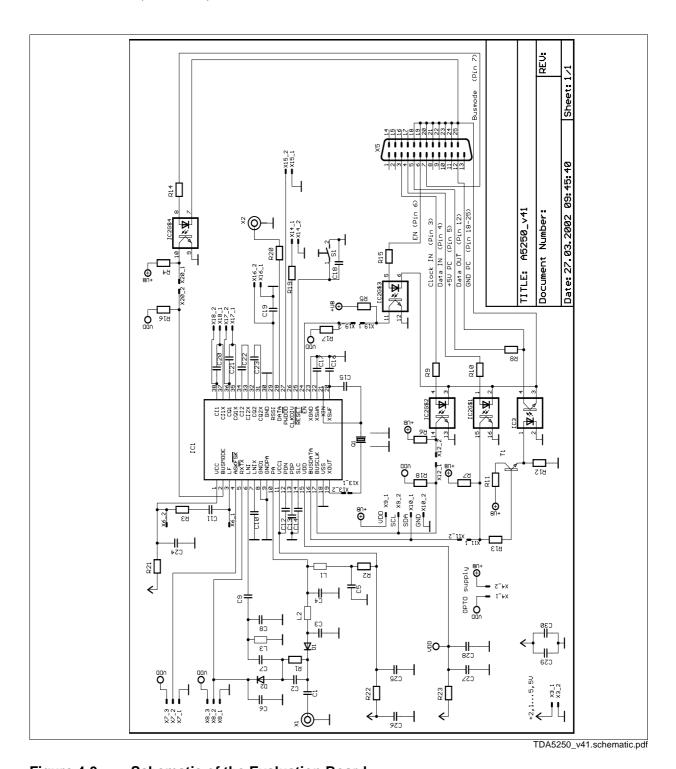

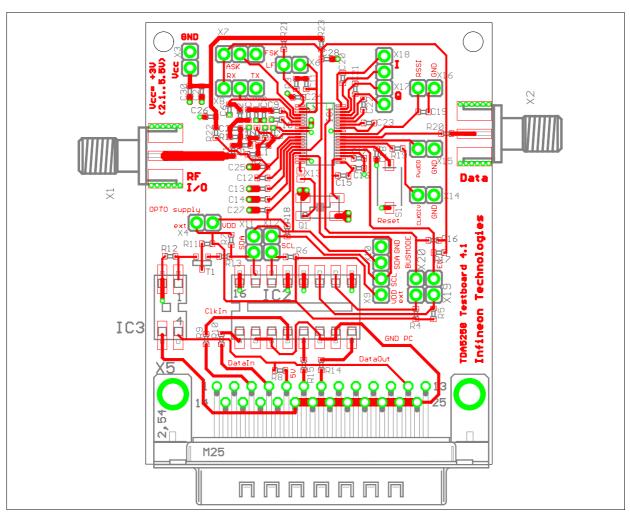

| 4.2    | Test Circuit                                     | 84         |

| 4.3    | Test Board Layout                                | 85         |

| 4.4    | Bill of Materials                                | 86         |

## **Product Description**

## 1 Product Description

#### 1.1 Overview

The IC is a low power consumption single chip FSK/ASK Transceiver for the frequency band 433-435 MHz. The IC combines a very high level of integration and minimum external part count. The device contains a low noise amplifier (LNA), a double balanced mixer, a fully integrated VCO, a PLL synthesizer, a crystal oscillator with FSK modulator, a limiter with RSSI generator, an FSK demodulator, a data filter, a data comparator (slicer), a positive and a negative data peak detector, a highly efficient power amplifier and a complex digital timing and control unit with I<sup>2</sup>C/3-wire microcontroller interface. Additionally there is a power down feature to save battery power.

The transmit section uses direct ASK modulation by switching the power amplifier, and crystal oscillator detuning for FSK modulation. The necessary detuning load capacitors are external. The capacitors for fine tuning are integrated. The receive section is using a novel single-conversion/direct-conversion scheme that is combining the advantages of both receive topologies. The IF is contained on the chip, no RF channel filters are necessary as the channel filter is also on the chip.

The self-polling logic can be used to let the device operate autonomously as a master for a decoding microcontroller.

#### 1.2 Features

- Low supply current ( $I_s = 9$  mA typ. receive,  $I_s = 13$ mA typ. transmit mode, both at 3 V supply voltage, 25°C)

- Supply voltage range 2.1 V to 5.5 V

- Operating temperature range -40°C to +85°C

- Power down mode with very low supply current consumption

- FSK and ASK modulation and demodulation capability without external circuitry changes, FM demodulation capability

- Fully integrated VCO and PLL synthesizer and loop filter on-chip with on-chip crystal oscillator tuning, therefore no additional external components necessary

- Differential receive signal path completely on-chip, therefore no external filters are necessary

- On-chip low pass channel select and data filter with tuneable bandwith

- Data slicer with self-adjusting threshold and 2 peak detectors

- Self-polling logic with adjustable duty cycle and ultrafast data rate detection and timer mode providing periodical interrupt

8

- FSK and ASK sensitivity < -109 dBm</li>

- Adjustable LNA gain

- Digital RSSI and Battery Voltage Readout

- Provides Clock Out Pin for external microcontroller

- Transmit power up to +13 dBm in  $50\Omega$  load at 5V supply voltage

- Maximum datarate up to 100 kBaud Manchester Encoded

- I<sup>2</sup>C/3-wire microcontroller interface, working at max. 400kbit/s

- meets the ETSI EN300 220 regulation and CEPT ERC 7003 recommendation

## **Product Description**

## 1.3 Application

- Low Bitrate Communication Systems

- Keyless Entry Systems

- Remote Control Systems

- Alarm Systems

- Telemetry Systems

- Electronic Metering

- Home Automation Systems

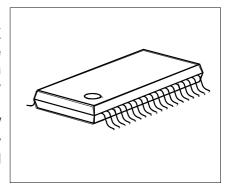

## 1.4 Package Outlines

P-TSSOP-38-1.EPS

Figure 1-1 P-TSSOP-38-1 package outlines

## **Functional Description**

## **2** Functional Description

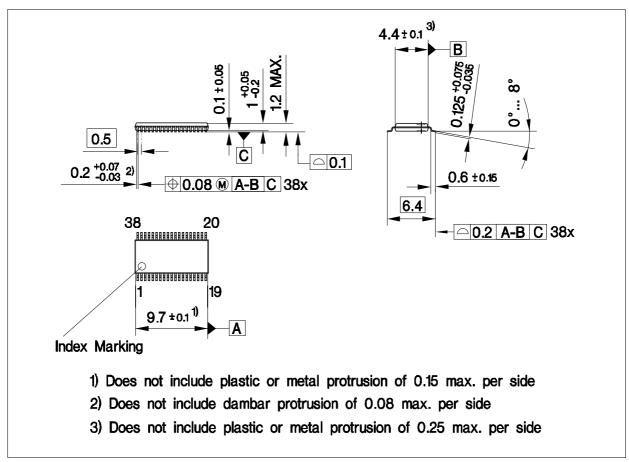

## 2.1 Pin Configuration

Figure 2-1 Pin Configuration

## **Functional Description**

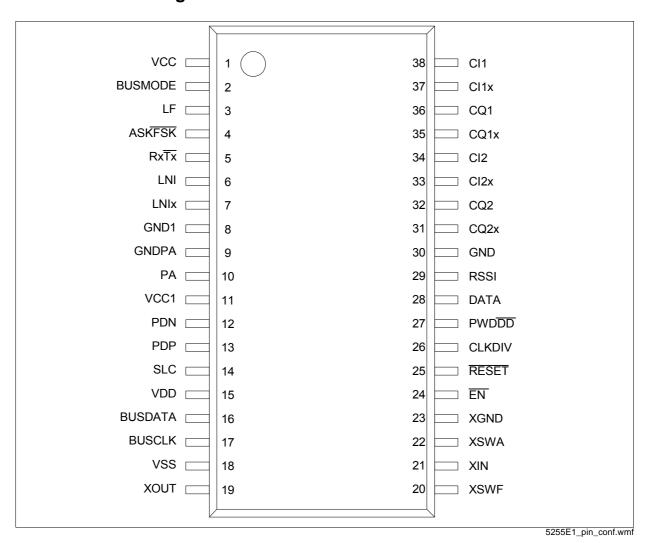

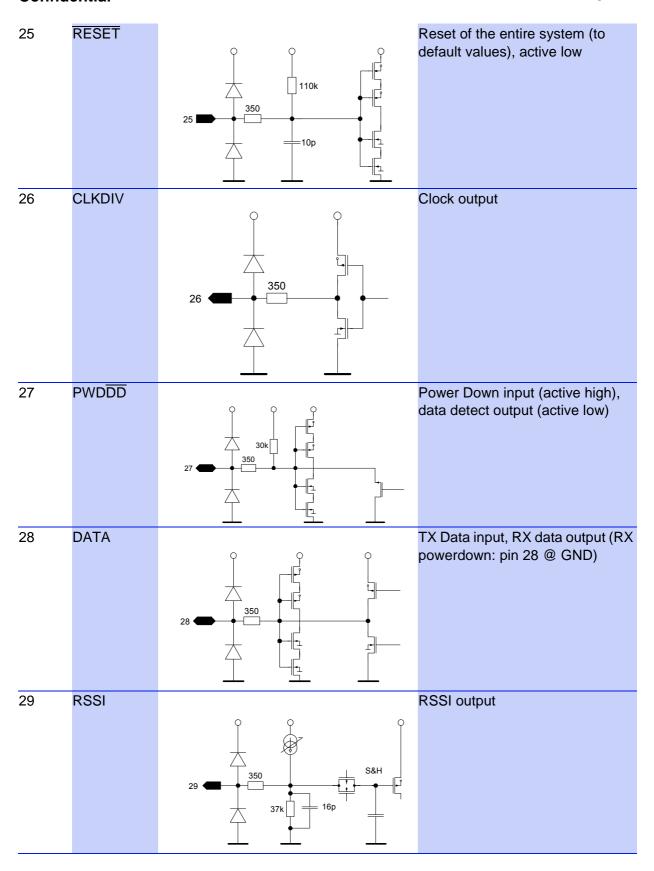

## 2.2 Pin Definitions and Functions

| Table 2 | Table 2-1 Pin Definition and Function |                          |                                                                 |  |  |

|---------|---------------------------------------|--------------------------|-----------------------------------------------------------------|--|--|

| Pin No. | Symbol                                | Equivalent I/O-Schematic | Function                                                        |  |  |

| 1       | VCC                                   | 11                       | Analog supply (antiparallel diodes between VCC, VCC1, VDD)      |  |  |

| 2       | BUSMODE                               | 2 350                    | Bus mode selection (I <sup>2</sup> C/3 wire bus mode selection) |  |  |

| 3       | LF                                    | 3 - 200                  | Loop filter and VCO control voltage                             |  |  |

| 4       | ASK <del>FSK</del>                    | 350                      | ASK/FSK- mode switch input                                      |  |  |

| 5  | RXTX  |                                        | RX/TX-mode switch input/output                              |

|----|-------|----------------------------------------|-------------------------------------------------------------|

|    |       | 5 - 350 TX                             |                                                             |

| 6  | LNI   | 5k 1.1v 5k 7                           | RF input to differential Low Noise<br>Amplifier (LNA))      |

| 7  | LNIX  | see Pin 6                              | Complementary RF input to differential LNA                  |

| 8  | GND1  | 8 ———————————————————————————————————— | Ground return for LNA and Power Amplifier (PA) dirver stage |

| 9  | GNDPA | see Pin 8                              | Ground return for PA output stage                           |

| 10 | PA    | 10 Ω<br>10 Ω<br>9 GndPA                | PA output stage                                             |

| 11 | VCC1  | see Pin 1                              | Supply for LNA and PA                                       |

| 18 | VSS  | see Pin 8                          | Ground for digital section                                                         |

|----|------|------------------------------------|------------------------------------------------------------------------------------|

| 19 | XOUT | Vcc-860mV<br>150μΑ                 | Crystal oscillator output, can also be used as external reference frequency input. |

| 20 | XSWF | 21<br>125fF 4pF 20<br>250fF 8pF 23 | FSK modulation switch                                                              |

| 21 | XIN  | see Pin 20                         |                                                                                    |

| 22 | XSWA | 22                                 | ASK modulation/FSK center frequency switch                                         |

| 23 | XGND | see Pin 22                         | Crystal oscillator ground return                                                   |

| 24 | ĒN   | 350                                | 3-wire bus enable input                                                            |

| 30 | GND  | see Pin 8                             | Analog ground                                    |

|----|------|---------------------------------------|--------------------------------------------------|

| 31 | CQ2x | Stage1:Vcc-630mV<br>Stage2: Vcc-560mV | Pin for external Capacitor<br>Q-channel, stage 2 |

| 32 | CQ2  | II                                    | Q-channel, stage 2                               |

| 33 | CI2x | II                                    | I-channel, stage 2                               |

| 34 | CI2  | II                                    | I-channel, stage 2                               |

| 35 | CQ1x | II                                    | Q-channel, stage 1                               |

| 36 | CQ1  | II                                    | Q-channel, stage 1                               |

| 37 | CI1x | II                                    | I-channel, stage 1                               |

| 38 | CI1  | II                                    | I-channel, stage 1                               |

## **Functional Description**

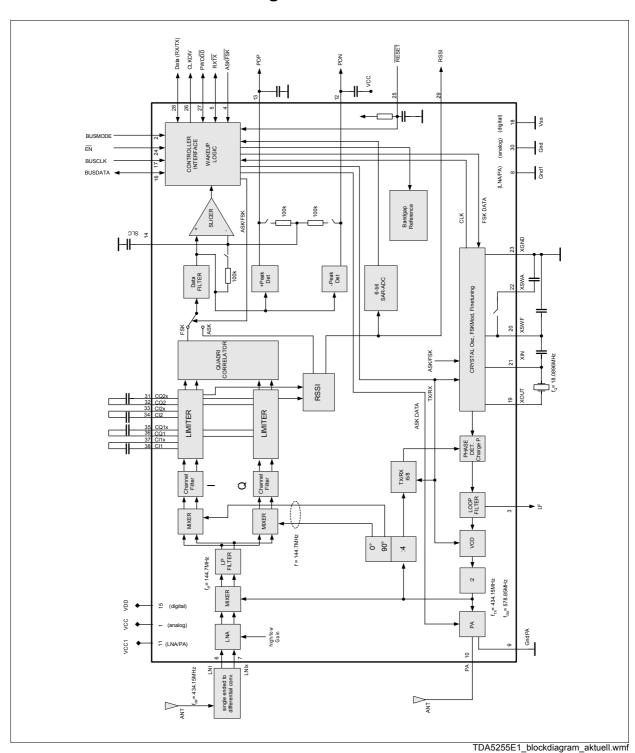

## 2.3 Functional Block Diagram

Figure 2-2 Main Block Diagram

## **Functional Description**

## 2.4 Functional Block Description

## 2.4.1 Power Amplifier (PA)

The power amplifier is operating in C-mode. It can be used in either high or low power mode. In high-power mode the transmit power is approximately +13dBm into 50 Ohm at 5V and +6dBm at 2.1V supply voltage. In low power mode the transmit power is approximately +10dBm at 5V and -32dBm at 2.1V supply voltage using the same matching network. The transmit power is controlled by the **D0**-bit of the **CONFIG** register (subaddress 00H) as shown in the following **Table 2-2**. The default output power mode is high power mode.

| Table 2- | 2-2 Sub Address 00H: CONFIG |                                   |   |  |  |

|----------|-----------------------------|-----------------------------------|---|--|--|

| Bit      | Function                    | Function Description              |   |  |  |

| D0       | PA_PWR                      | 0= low TX Power, 1= high TX Power | 1 |  |  |

In case of ASK modulation the power amplifier is turned fully on and off by the transmit baseband data, i.e. 100% On-Off-Keying.

## 2.4.2 Low Noise Amplifier (LNA)

The LNA is an on-chip cascode amplifier with a voltage gain of 15 to 20dB and symmetrical inputs. It is possible to reduce the gain to 0 dB via logic.

| Table 2 | ole 2-3 Sub Address 00H: CONFIG |                           |   |  |  |

|---------|---------------------------------|---------------------------|---|--|--|

| Bit     | Function                        | Function Description D    |   |  |  |

| D4      | LNA_GAIN                        | 0= low Gain, 1= high Gain | 1 |  |  |

## 2.4.3 Downconverter 1<sup>st</sup> Mixer

The Double Balanced 1<sup>st</sup> Mixer converts the input frequency (RF) in the range of 434-435 MHz to down to the intermediate frequency (IF) at approximately 144MHz. The local oscillator frequency is generated by the PLL synthesizer that is fully implemented on-chip as described in **Section 2.4.5**. This local oscillator operates at approximately 578MHz in receive mode providing the above mentioned IF frequency of 144MHz. The mixer is followed by a low pass filter with a corner frequency of approximately 175MHz in order to prevent RF and LO signals from appearing in the 144MHz IF signal.

## 2.4.4 Downconverter 2<sup>nd</sup> I/Q Mixers

The Low pass filter is followed by 2 mixers (inphase I and quadrature Q) that convert the 144MHz IF signal down to zero-IF. These two mixers are driven by a signal that is generated by dividing the local oscillator signal by 4, thus equalling the IF frequency.

## **Functional Description**

## 2.4.5 PLL Synthesizer

The Phase Locked Loop synthesizer consists of two VCOs (i.e. transmit and receive VCO), a divider by 4, an asynchronous divider chain with selectable overall division ratio, a phase detector with charge pump and a loop filter and is fully implemented on-chip. The VCOs are including spiral inductors and varactor diodes. The center frequency of the transmit VCO is 868MHz, the center frequency of the receive VCO is 1156MHz.

Generally in receive mode the relationship between local oscillator frequency  $f_{OSC}$ , the receive RF frequency  $f_{RF}$  and the IF frequency  $f_{IF}$  and thus the frequency that is applied to the I/Q Mixers is given in the following formula:

$$\frac{f_{osc}}{2} = 4/3 f_{RF} = 4 f_{IF}$$

[2 - 1]

The VCO signal is applied to a divider by 2 and afterwards by 4 which is producing approximately 144MHz signals in quadrature. The overall division ratio of the divider chain following the divider by 2 and 4 is 6 in transmit mode and 8 in receive mode as the nominal crystal oscillator frequency is 18.083MHz. The division ratio is controlled by the RxTx pin (pin 5) and the **D10** bit in the **CONFIG** register.

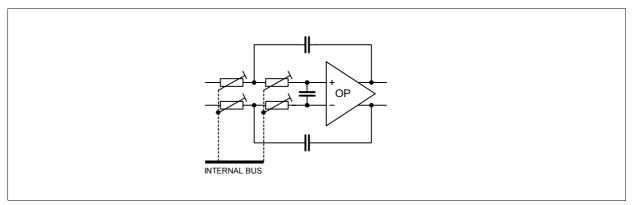

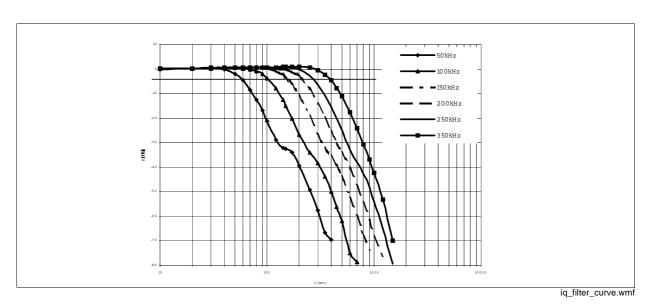

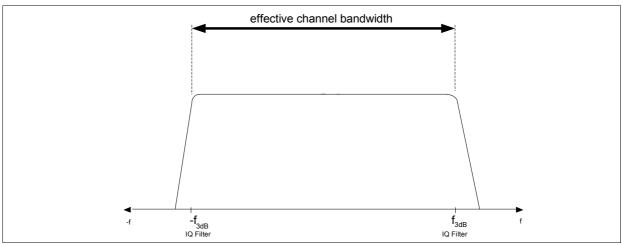

## 2.4.6 I/Q Filters

The I/Q IF to zero-IF mixers are followed by baseband 6<sup>th</sup> order low pass filters that are used for RF-channel filtering.

iq\_filter.wmf

#### Figure 2-3 One I/Q Filter stage

The bandwidth of the filters is controlled by the values set in the filter-register. It can be adjusted between 50 and 350kHz in 50kHz steps via the bits D1 to D3 of the **LPF** register (subaddress 03H).

## **Functional Description**

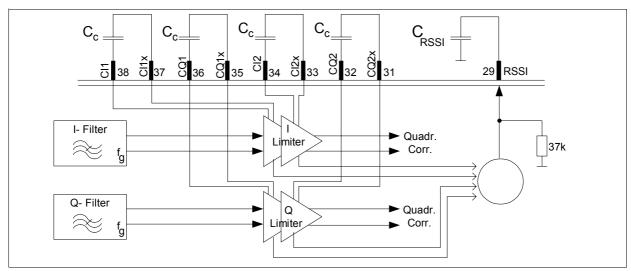

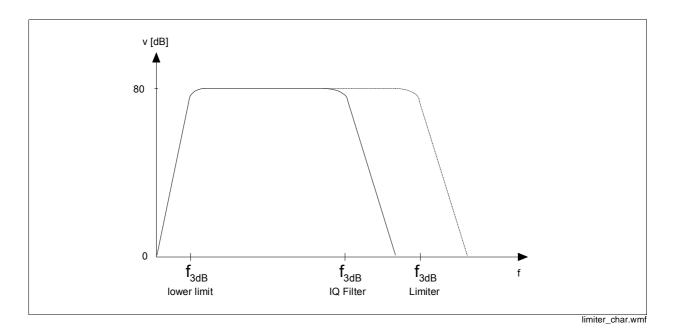

#### 2.4.7 I/Q Limiters

The I/Q Limiters are DC coupled multistage amplifiers with offset-compensating feedback circuit and an overall gain of approximately 80dB each in the frequency range of 100Hz up to 350kHz. Receive Signal Strength Indicator (RSSI) generators are included in both limiters which produce DC voltages that are directly proportional to the input signal level in the respective channels. The resulting I- and Q-channel RSSI-signals are summed to the nominal RSSI signal.

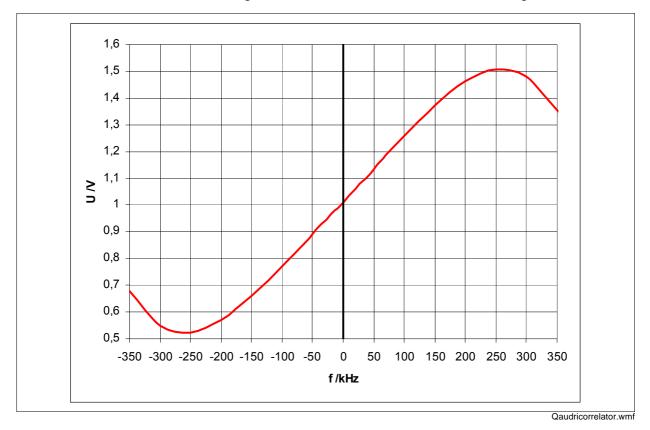

#### 2.4.8 FSK Demodulator

The output differential signals of the I/Q limiters are fed to a quadrature correlator circuit that is used to demodulate frequency shift keyed (FSK) signals. The demodulator gain is 2.4mV/kHz, the maximum frequency deviation is ±300kHz as shown in **Figure 2-4** below.

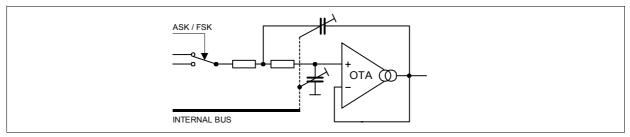

The demodulated signal is applied to the ASK/FSK mode switch which is connected to the input of the data filter. The switch can be controlled by the **ASKFSK** pin (pin 4) and via the D11 bit in the CONFIG register.

The modulation index *m* must be larger than 2 for correct demodulation of the signal.

Figure 2-4 Quadricorrelator Demodulation Characteristic

## **Functional Description**

#### 2.4.9 Data Filter

The 2-pole data filter has a Sallen-Key architecture and is implemented fully on-chip. The bandwidth can be adjusted between approximately 5kHz and 102kHz via the bits **D4** to **D7** of the **LPF** register as shown in **Table 3-10**.

data filter.wmf

Figure 2-5 Data Filter architecture

#### 2.4.10 Data Slicer

The data slicer is a fast comparator with a bandwidth of 100kHz. The self-adjusting threshold is generated by a RC-network (LPF) or by use of one or both peak detectors depending on the baseband coding scheme as described in **Section 3.6**. This can be controlled by the **D15** bit of the **CONFIG** register as shown in the following table.

| Table 2 | Table 2-4 Sub Address 00H: CONFIG |                                     |   |  |  |

|---------|-----------------------------------|-------------------------------------|---|--|--|

| Bit     | Function                          | Function Description Default        |   |  |  |

| D15     | SLICER                            | 0= Lowpass Filter, 1= Peak Detector | 0 |  |  |

#### 2.4.11 Peak Detectors

Two separate Peak Detectors are available. They are generating DC voltages in a fast-attack and slow-release manner that are proportional to the positive and negative peak voltages appearing in the data signal. These voltages may be used to generate a threshold voltage for non-Manchester encoded signals, for example. The time-constant of the fast-attack/slow-release action is determined by the RC network with external capacitor.

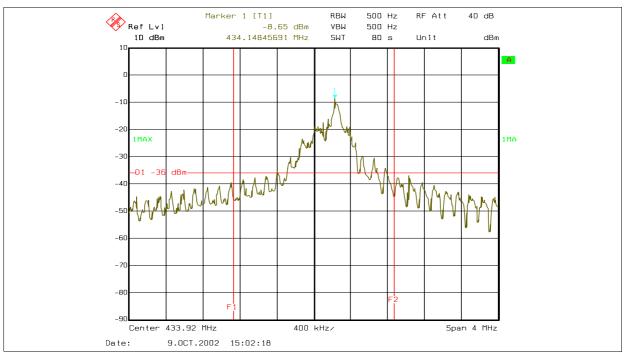

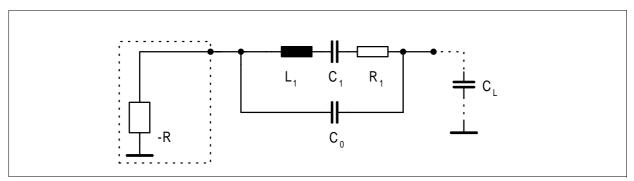

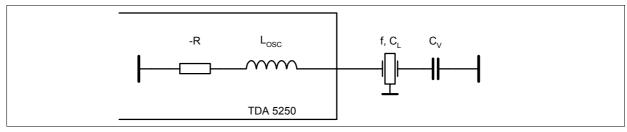

## 2.4.12 Crystal Oscillator

The reference oscillator is an NIC oscillator type (Negative Impedance Converter) with a crystal operating in serial resonance. The nominal operating frequency of 18.083MHz and the frequencies for FSK modulation can be adjusted via 3 external capacitors. Via microcontroller and bus interface the chip-internal capacitors can be used for finetuning of the nominal and the FSK modulation frequencies. This finetuning of the crystal oscillator allows to eliminate frequency errors due to crystal or component tolerances.

## **Functional Description**

## 2.4.13 Bandgap Reference Circuitry and Powerdown

A Bandgap Reference Circuit provides a temperature stable 1.2V reference voltage for the device. A power down mode is available to switch off all subcircuits that are controlled by the bidirectional Powerdown&DataDetect **PwdDD** pin (pin 27) as shown in the following table. Power down mode can either be activated by pin 27 or bit D14 in Register 00. In power down mode also pin 28 (DATA) is affected (see **Section 2.4.17**).

| Table 2-5 | PwdDD Pin Operating States |                 |

|-----------|----------------------------|-----------------|

|           | PwdDD                      | Operating State |

|           | VDD                        | Powerdown Mode  |

|           | Ground/VSS                 | Device On       |

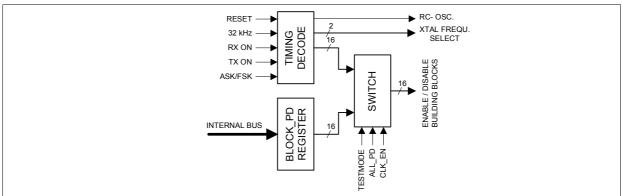

## 2.4.14 Timing and Data Control Unit

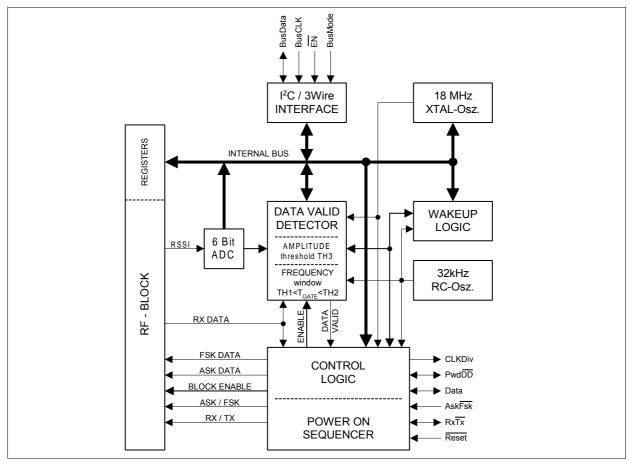

The timing and data control unit contains a wake-up logic unit, an I<sup>2</sup>C/3-wire microcontroller interface, a "data valid" detection unit and a set of configuration registers as shown in the subsequent figure.

logic.wmf

Figure 2-6 Timing and Data Control Unit

## **Functional Description**

The I<sup>2</sup>C / 3-wire Bus Interface gives an external microcontroller full control over important system parameters at any time.

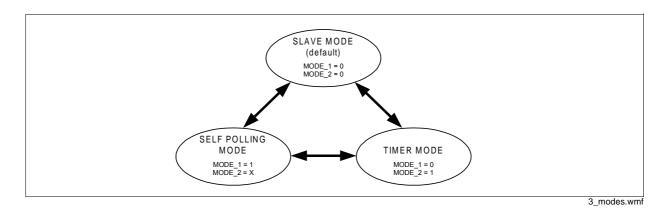

It is possible to set the device in three different modes: Slave Mode, Self Polling Mode and Timer Mode. This is done by a state machine which is implemented in the WAKEUP LOGIC unit. A detailed description is given in **Section 2.4.16**.

The DATA VALID DETECTOR contains a frequency window counter and an RSSI threshold comparator. The window counter uses the incoming data signal from the data slicer as the gating signal and the crystal oscillator frequency as the timebase to determine the actual datarate. The result is compared with the expected datarate.

The threshold comparator compares the actual RSSI level with the expected RSSI level.

If both conditions are true the  $Pwd\overline{DD}$  pin is set to LOW in self polling mode as you can see in **Section 2.4.16**. This signal can be used as an interrupt for an external  $\mu P$ . Because the  $Pwd\overline{DD}$  pin is bidirectional and open drain driven by an internal pull-up resistor it is possible to apply an external LOW thus enabling the device.

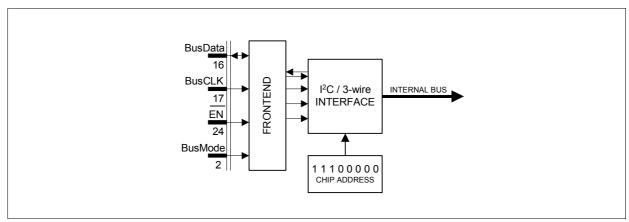

## 2.4.15 Bus Interface and Register Definition

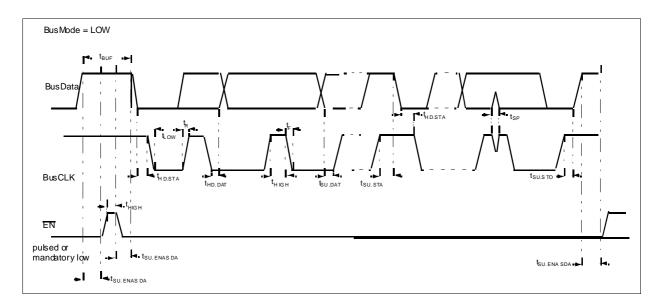

The TDA5255 supports the  $I^2C$  bus protocol (2 wire) and a 3-wire bus protocol. Operation is selectable by the **BusMode** pin (pin 2) as shown in the following table. All bus pins (BusData, BusCLK,  $\overline{\textbf{EN}}$ , BusMode) have a Schmitt-triggered input stage. The BusData pin is bidirectional where the output is open drain driven by an internal  $15k\Omega$  pull up resistor.

| Table 2-6 Bus I       | nterface Format |                 |             |             |

|-----------------------|-----------------|-----------------|-------------|-------------|

| Function              | BusMode         | EN              | BusCLK      | BusData     |

| I <sup>2</sup> C Mode | Low             | High= inactive, | Clock input | Data in/out |

| 3-wire Mode           | High            | Low= active     |             |             |

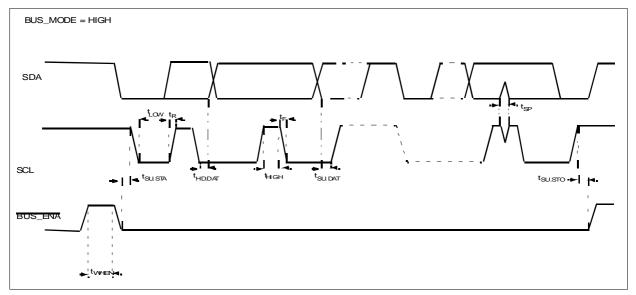

i2c\_3w\_bus.wmf

Figure 2-7 Bus Interface

**Note:** The Interface is able to access the internal registers at any time, even in POWER DOWN mode. There is no internal clock necessary for Interface operation.

## **Functional Description**

## I<sup>2</sup>C Bus Mode

In this mode the **BusMode** pin (pin 2) = LOW and the  $\overline{EN}$  pin (pin 24) = LOW.

#### Data Transition:

Data transition on the pin BusData can only occur when BusCLK is LOW. BusData transitions while BusCLK is HIGH will be interpreted as start or stop condition.

#### Start Condition (STA):

A start condition is defined by a HIGH to LOW transition of the BusData line while BusCLK is HIGH. This start condition must precede any command and initiate a data transfer onto the bus.

#### Stop Condition (STO):

A stop condition is defined by a LOW to HIGH transition of the BusData line while BusCLK is HIGH. This condition terminates the communication between the devices and forces the bus interface into the initial state.

## Acknowledge (ACK):

Indicates a successful data transfer. The transmitter will release the bus after sending 8 bit of data. During the 9th clock cycle the receiver will set the SDA line to LOW level to indicate it has received the 8 bits of data correctly.

#### Data Transfer Write Mode:

To start the communication, the bus master must initiate a start condition (STA), followed by the 8bit chip address. The chip address for the TDA5255 is fixed as "1110000" (MSB at first). The last bit (LSB=A0) of the chip address byte defines the type of operation to be performed:

A0=0, a write operation is selected and A0=1 a read operation is selected.

After this comparison the TDA5255 will generate an ACK and awaits the desired sub address byte (00H...0FH) and data bytes. At the end of the data transition the master has to generate the stop condition (STO).

#### Data Transfer Read Mode:

To start the communication in the read mode, the bus master must initiate a start condition (STA), followed by the 8 bit chip address (write: A0=0), followed by the sub address to read (80H, 81H), followed by the chip address (read: A0=1). After that procedure the data of the selected register (80H, 81H) is read out. During this time the data line has to be kept in HIGH state and the chip sends out the data. At the end of data transition the master has to generate the stop condition (STO).

## **Functional Description**

## Bus Data Format in I<sup>2</sup>C Mode

| Table 2-7 | C | hip ad | dress | Orga | nizatio | n |     |                    |

|-----------|---|--------|-------|------|---------|---|-----|--------------------|

| MSB       |   |        |       |      |         |   | LSB | Function           |

| 1         | 1 | 1      | 0     | 0    | 0       | 0 | 0   | Chip Address Write |

| 1         | 1 | 1      | 0     | 0    | 0       | 0 | 1   | Chip Address Read  |

| Tab | le 2- | 8 |    | l <sup>2</sup> | C I | 3u | s V | Vrite | Mod | le 8 | Bit |    |                |    |    |    |     |     |     |    |    |    |     |    |    |     |     |     |

|-----|-------|---|----|----------------|-----|----|-----|-------|-----|------|-----|----|----------------|----|----|----|-----|-----|-----|----|----|----|-----|----|----|-----|-----|-----|

|     | MSB   |   | СН | IP A<br>(WF    | DDR |    | ;   | LSB   |     | MSB  |     |    | DDRI<br>8H, 0I | (  |    | ,  | LSB |     | MSB |    |    | D  | ATA | IN |    | LSB |     |     |

| STA | 1     | 1 | 1  | 0              | 0   | 0  | 0   | 0     | ACK | S7   | S6  | S5 | S4             | S3 | S2 | S1 | S0  | ACK | D7  | D6 | D5 | D4 | D3  | D2 | D1 | D0  | ACK | STO |

| Tak | ole 2 | -9 |        | l <sup>2</sup> | C   | 3us | s W  | rite | Мо  | de ' | 16 B | Bit  |       |        |        |    |     |     |     |   |     |     |    |     |     |     |

|-----|-------|----|--------|----------------|-----|-----|------|------|-----|------|------|------|-------|--------|--------|----|-----|-----|-----|---|-----|-----|----|-----|-----|-----|

|     | MSB   | СН | IIP AI | DDR            | ESS | (WR | ITE) | LSB  |     | MSB  | s    | UB A | DDRI  | ESS (V | VRITE  | :) | LSB |     | MSB |   | D   | ATA | IN | LSB |     |     |

|     |       |    |        |                |     |     |      |      |     |      | 00   | )H0  | 8H, 0 | DH, 0E | EH, OF | H  |     |     |     |   |     |     |    |     |     |     |

| STA | 1     | 1  | 1      | 0              | 0   | 0   | 0    | 0    | ACK | S7   | S6   | S5   | S4    | S3     | S2     | S1 | S0  | ACK | D15 | D | ACK | D7  | D6 | D0  | ACK | STO |

| Tal | ole | 2-  | 10  |    | <sup>2</sup>   | С | Вι  | ıs l | Rea | ıd N | /lod | е    |       |             |                |     |    |     |     |     |     |    |       |    |     |       |     |     |     |

|-----|-----|-----|-----|----|----------------|---|-----|------|-----|------|------|------|-------|-------------|----------------|-----|----|-----|-----|-----|-----|----|-------|----|-----|-------|-----|-----|-----|

|     | MSE | 3 C | HIP | AD | DRES           | S | (WR | ITE) | LSB |      | MSB  | 5    | SUB A | ADDR<br>80H | ESS (<br>, 81H |     | D) | LSB |     |     | MSB | CH | IIP A | DD | RES | S (RE | AD) | LSB |     |

| STA | 1   | 1   | 1   | 1  | 0 (            | ) | 0   | 0    | 0   | ACK  | S7   | S6   | S5    | S4          | S3             | S2  | S1 | S0  | ACK | STA | 1   | 1  | 1     | 0  | 0   | 0     | 0   | 1   | ACK |

| Tal | ole | 2-  | 10  |    | l <sup>2</sup> | C | Вι  | ıs I | Rea | d N  | /lod | e (d | con   | tinı        | ıed            | )   |    |     |     |     |     |    |       |    |     |       |     |     |     |

|     | MS  | В   |     |    |                |   |     |      |     | DAT  | A OU | T FR | омѕ   | UB A        | DDRE           | ESS |    |     |     |     |     |    | LSB   |    |     |       |     |     |     |

|     | R7  |     |     |    | R6             |   |     | F    | R5  |      | R-   | 4    |       | R3          | 3              |     | R2 |     |     | R1  |     |    | R0    |    |     | AC    | (*  |     | STO |

<sup>\*</sup> mandatory HIGH

#### 3-wire Bus Mode

In this mode pin 2 (BusMode)= HIGH and Pin 16 (BusData) is in the data input/output pin. Pin 24  $(\overline{EN})$  is used to activate the bus interface to allow the transfer of data to / from the device. When pin 24  $(\overline{EN})$  is inactive (HIGH), data transfer is inhibited.

#### Data Transition:

Data transition on pin 16 (BusData) can only occur if the clock BusCLK is LOW. To perform a data transfer the interface has to be enabled. This is done by setting the  $\overline{\text{EN}}$  line to LOW. A serial transfer is done via BusData, BusCLK and  $\overline{\text{EN}}$ . The bit stream needs no chip address.

#### Data Transfer Write Mode:

To start the communication the  $\overline{\text{EN}}$  line has to be set to LOW. The desired sub address byte and data bytes have to follow. The subaddress (00H...0FH) determines which of the data bytes are transmitted. At the end of data transition the  $\overline{\text{EN}}$  must be HIGH.

#### Data transfer Read Mode:

To start the communication in the read mode, the  $\overline{\text{EN}}$  line has to be set to LOW followed by the sub address to read (80H, 81H). Afterwards the device is ready to read out data. At the end of data transition  $\overline{\text{EN}}$  must be HIGH.

## **Functional Description**

## **Bus Data Format 3-wire Bus Mode**

| Table | 2-11 | 3-w   | ire Bu | s Writ | e Mod | de         |     |     |        |      |       |         |    |     |

|-------|------|-------|--------|--------|-------|------------|-----|-----|--------|------|-------|---------|----|-----|

| MSB   | ,    | SUB A | DDRI   | ESS (V | VRITE | <u>:</u> ) | LSB | MSB | DATA   | IN X | 0 (X= | 7 or 15 | 5) | LSB |

|       | (    | 0H00  | )8H, 0 | DH, 01 | EH,0F | H          |     |     |        |      |       |         |    |     |

| S7    | S6   | S5    | S4     | S3     | S2    | S1         | S0  | DX  | <br>D5 | D4   | D3    | D2      | D1 | D0  |

| Table | 2-12 | 3-w   | ire Bu | s Rea  | d Moc | le |     |     |    |    |      |       |    |    |     |

|-------|------|-------|--------|--------|-------|----|-----|-----|----|----|------|-------|----|----|-----|

| MSB   |      | SUB A | ADDR   | ESS (I | READ  | )  | LSB | MSB |    | DA | TA O | JT FR | OM |    | LSB |

|       |      |       | 80H    | , 81H  |       |    |     |     |    | S  | UB A | DRE   | SS |    |     |

| S7    | S6   | S5    | S4     | S3     | S2    | S1 | S0  | R7  | R6 | R5 | R4   | R3    | R2 | R1 | R0  |

## **Register Definition**

## **Sub Addresses Overview**

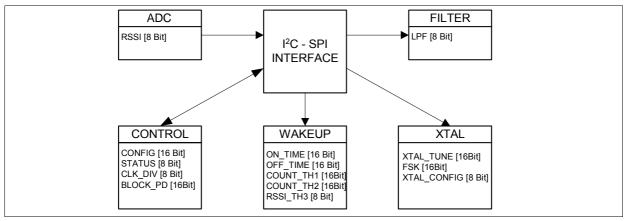

register\_overview.wmf

Figure 2-8 Sub Addresses Overview

## **Functional Description**

## **Subaddress Organization**

| Table | <b>2</b> -′ | 13 | Sı | ub A | Addr | ess | es of | Data | Registers W | rite                                     |            |

|-------|-------------|----|----|------|------|-----|-------|------|-------------|------------------------------------------|------------|

| MSB   |             |    |    |      |      |     | LSB   | HEX  | Function    | Description                              | Bit Length |

| 0     | 0           | 0  | 0  | 0    | 0    | 0   | 0     | 00h  | CONFIG      | General definition of status bits        | 16         |

| 0     | 0           | 0  | 0  | 0    | 0    | 0   | 1     | 01h  | FSK         | Values for FSK-shift                     | 16         |

| 0     | 0           | 0  | 0  | 0    | 0    | 1   | 0     | 02h  | XTAL_TUNING | Nominal frequency                        | 16         |

| 0     | 0           | 0  | 0  | 0    | 0    | 1   | 1     | 03h  | LPF         | I/Q and data filter cutoff frequencies   | 8          |

| 0     | 0           | 0  | 0  | 0    | 1    | 0   | 0     | 04h  | ON_TIME     | ON time of wakeup counter                | 16         |

| 0     | 0           | 0  | 0  | 0    | 1    | 0   | 1     | 05h  | OFF_TIME    | OFF time of wakeup counter               | 16         |

| 0     | 0           | 0  | 0  | 0    | 1    | 1   | 0     | 06h  | COUNT_TH1   | Lower threshold of window counter        | 16         |

| 0     | 0           | 0  | 0  | 0    | 1    | 1   | 1     | 07h  | COUNT_TH2   | Higher threshold of window counter       | 16         |

| 0     | 0           | 0  | 0  | 1    | 0    | 0   | 0     | 08h  | RSSI_TH3    | Threshold for RSSI signal                | 8          |

| 0     | 0           | 0  | 0  | 1    | 1    | 0   | 1     | 0Dh  | CLK_DIV     | Configuration and Ratio of clock divider | 8          |

| 0     | 0           | 0  | 0  | 1    | 1    | 1   | 0     | 0Eh  | XTAL_CONFIG | XTAL configuration                       | 8          |

| 0     | 0           | 0  | 0  | 1    | 1    | 1   | 1     | 0Fh  | BLOCK_PD    | Building Blocks Power Down               | 16         |

| Tabl | e 2- | 14 |   | Sub | Ad | dre | sses | of D | ata Registers | Read                                |            |

|------|------|----|---|-----|----|-----|------|------|---------------|-------------------------------------|------------|

| MSB  |      |    |   |     |    |     | LSB  | HEX  | Function      | Description                         | Bit Length |

| 1    | 0    | 0  | 0 | 0   | 0  | 0   | 0    | 80h  | STATUS        | Results of comparison: ADC & WINDOW | 8          |

| 1    | 0    | 0  | 0 | 0   | 0  | 0   | 1    | 81h  | ADC           | ADC data out                        | 8          |

## **Data Byte Specification**

| Table 2 | -15 Sub Address 0 | 0H: CONFIG                                                                 |         |

|---------|-------------------|----------------------------------------------------------------------------|---------|

| Bit     | Function          | Description                                                                | Default |

| D15     | SLICER            | 0= Lowpass, 1= Peak Detector                                               | 0       |

| D14     | ALL_PD            | 0= normal operation, 1= all Power down                                     | 0       |

| D13     | TESTMODE          | 0= normal operation, 1=Testmode                                            | 0       |

| D12     | CONTROL           | 0= RX/TX and ASK/FSK external controlled, 1= Register controlled           | 0       |

| D11     | ASK_NFSK          | 0= FSK, 1=ASK                                                              | 0       |

| D10     | RX_NTX            | 0= TX, 1=RX                                                                | 1       |

| D9      | CLK_EN            | 0= CLK off during power down, 1= always CLK on, ever in PD                 | 0       |

| D8      | RX_DATA_INV       | 0= no Data inversion, 1= Data inversion                                    | 0       |

| D7      | D_OUT             | 0= Data out if valid, 1= always Data out                                   | 1       |

| D6      | ADC_MODE          | 0= one shot, 1= continuous                                                 | 1       |

| D5      | F_COUNT_MODE      | 0= one shot, 1= continuous                                                 | 1       |

| D4      | LNA_GAIN          | 0= low gain, 1= high gain                                                  | 1       |

| D3      | EN_RX             | 0= disable receiver, 1= enable receiver (in self polling and timer mode) * | 1       |

| D2      | MODE_2            | 0= slave mode, 1= timer mode                                               | 0       |

| D1      | MODE_1            | 0= slave or timer mode, 1= self polling mode                               | 0       |

| D0      | PA_PWR            | 0= low TX Power, 1= high TX Power                                          | 1       |

**Note D3:** Function is only active in selfpolling and timer mode. When D3 is set to LOW the RX path is not enabled if  $Pwd\overline{DD}$  pin is set to LOW. A delayed setting of D3 results in a delayed power ON of the RX building blocks.

| Table 2 | -16 Su   | b Address 0' | IH: FSK                     |         |

|---------|----------|--------------|-----------------------------|---------|

| Bit     | Function | Value        | Description                 | Default |

| D15     |          |              | not used                    | 0       |

| D14     |          |              | not used                    | 0       |

| D13     | FSK+5    | 8pF          | Setting for                 | 0       |

| D12     | FSK+4    | 4pF          | positive                    | 0       |

| D11     | FSK+3    | 2pF          | frequency<br>shift: +FSK or | 1       |

| D10     | FSK+2    | 1pF          | ASK-RX                      | 0       |

| D9      | FSK+1    | 500fF        |                             | 1       |

| D8      | FSK+0    | 250fF        |                             | 0       |

| D7      |          |              | not used                    | 0       |

| D6      |          |              | not used                    | 0       |

| D5      | FSK-5    | 4pF          | Setting for                 | 0       |

| D4      | FSK-4    | 2pF          | negative                    | 0       |

| D3      | FSK-3    | 1pF          | frequency<br>shift: -FSK    | 1       |

| D2      | FSK-2    | 500fF        | 2 1 011                     | 1       |

| D1      | FSK-1    | 250fF        |                             | 0       |

| D0      | FSK-0    | 125fF        |                             | 0       |

| Table 2-18 Sub Address 03H: LPF |              |                          |         |

|---------------------------------|--------------|--------------------------|---------|

| Bit                             | Function     | Description              | Default |

| D7                              | Datafilter_3 |                          | 0       |

| D6                              | Datafilter_2 | 3dB cutoff               | 0       |

| D5                              | Datafilter_1 | frequency of data filter | 0       |

| D4                              | Datafilter_0 |                          | 1       |

| D3                              | IQ_Filter_2  | 3dB cutoff               | 1       |

| D2                              | IQ_Filter_1  | frequency of             | 0       |

| D1                              | IQ_Filter_0  | IQ-filter                | 0       |

| D0                              | not used     |                          | 0       |

| Table 2-17 Sub Address 02H: X |                 | TAL_TUNING |             |         |

|-------------------------------|-----------------|------------|-------------|---------|

| Bit                           | Function        | Value      | Description | Default |

| D15                           |                 |            | not used    | 0       |

| D14                           |                 |            | not used    | 0       |

| D13                           |                 |            | not used    | 0       |

| D12                           |                 |            | not used    | 0       |

| D11                           |                 |            | not used    | 0       |

| D10                           |                 |            | not used    | 0       |

| D9                            |                 |            | not used    | 0       |

| D8                            |                 |            | not used    | 0       |

| D7                            |                 |            | not used    | 0       |

| D6                            |                 |            | not used    | 0       |

| D5                            | Nominal_Frequ_5 | 8pF        | Setting for | 0       |

| D4                            | Nominal_Frequ_4 | 4pF        | nominal     | 1       |

| D3                            | Nominal_Frequ_3 | 2pF        | frequency   | 0       |

| D2                            | Nominal_Frequ_2 | 1pF        | ASK-TX      | 0       |

| D1                            | Nominal_Frequ_1 | 500fF      | FSK-RX      | 1       |

| D0                            | Nominal_Frequ_0 | 250fF      |             | 0       |

| Table 2-1 | 9 Sub Addı     | resses 04H / 05H: ( | ON/OFF_TIME         |

|-----------|----------------|---------------------|---------------------|

| Bit       | Function       | Default ON_TIME     | Default<br>OFF TIME |

| D15       | ON_15 / OFF_15 | 1                   | 1                   |

| D14       | ON_14 / OFF_14 | 1                   | 1                   |

| D13       | ON_13 / OFF_13 | 1                   | 1                   |

| D12       | ON_12 / OFF_12 | 1                   | 1                   |

| D11       | ON_11 / OFF_11 | 1                   | 0                   |

| D10       | ON_10 / OFF_10 | 1                   | 0                   |

| D9        | ON_9 / OFF_9   | 1                   | 1                   |

| D8        | ON_8 / OFF_8   | 0                   | 1                   |

| D7        | ON_7 / OFF_7   | 1                   | 1                   |

| D6        | ON_6 / OFF_6   | 1                   | 0                   |

| D5        | ON_5 / OFF_5   | 0                   | 0                   |

| D4        | ON_4 / OFF_4   | 0                   | 0                   |

| D3        | ON_3 / OFF_3   | 0                   | 0                   |

| D2        | ON_2 / OFF_2   | 0                   | 0                   |

| D1        | ON_1 / OFF_1   | 0                   | 0                   |

| D0        | ON_0 / OFF_0   | 0                   | 0                   |

| Table 2-2 | 0 Sub Address 06H: COUNT_Th | <del>1</del> 1 |

|-----------|-----------------------------|----------------|

| Bit       | Function                    | Default        |

| D15       | not used                    | 0              |

| D14       | not used                    | 0              |

| D13       | not used                    | 0              |

| D12       | not used                    | 0              |

| D11       | TH1_11                      | 0              |

| D10       | TH1_10                      | 0              |

| D9        | TH1_9                       | 0              |

| D8        | TH1_8                       | 0              |

| D7        | TH1_7                       | 0              |

| D6        | TH1_6                       | 0              |

| D5        | TH1_5                       | 0              |

| D4        | TH1_4                       | 0              |

| D3        | TH1_3                       | 0              |

| D2        | TH1_2                       | 0              |

| D1        | TH1_1                       | 0              |

| D0        | TH1_0                       | 0              |

| Table 2-21 Sub Address 07H: COUNT_TH2 |          |         |

|---------------------------------------|----------|---------|

| Bit                                   | Function | Default |

| D15                                   | not used | 0       |

| D14                                   | not used | 0       |

| D13                                   | not used | 0       |

| D12                                   | not used | 0       |

| D11                                   | TH2_11   | 0       |

| D10                                   | TH2_10   | 0       |

| D9                                    | TH2_9    | 0       |

| D8                                    | TH2_8    | 0       |

| D7                                    | TH2_7    | 0       |

| D6                                    | TH2_6    | 0       |

| D5                                    | TH2_5    | 0       |

| D4                                    | TH2_4    | 0       |

| D3                                    | TH2_3    | 0       |

| D2                                    | TH2_2    | 0       |

| D1                                    | TH2_1    | 0       |

| Table 2-22 Sub Add |          | dress 08H: RSSI_TH3 |         |

|--------------------|----------|---------------------|---------|

| Bit                | Function | Description         | Default |

| D7                 | not used |                     | 1       |

| D6                 | SELECT   | 0= VCC, 1= RSSI     | 1       |

| D5                 | TH3_5    |                     | 1       |

| D4                 | TH3_4    |                     | 1       |

| D3                 | TH3_3    |                     | 1       |

| D2                 | TH3_2    |                     | 1       |

| D1                 | TH3_1    |                     | 1       |

| D0                 | TH3 0    |                     | 1       |

| Table 2-23 Sub Address 0DH: CLK_DIV |           |         |

|-------------------------------------|-----------|---------|

| Bit                                 | Function  | Default |

| D7                                  | not used  | 0       |

| D6                                  | not used  | 0       |

| D5                                  | DIVMODE_1 | 0       |

| D4                                  | DIVMODE_0 | 0       |

| D3                                  | CLKDIV_3  | 1       |

| D2                                  | CLKDIV_2  | 0       |

| D1                                  | CLKDIV_1  | 0       |

| D0                                  | CLKDIV_0  | 0       |

| Table 2- | 24 Sub /    | Sub Address 0EH: XTAL_CONFIG |         |  |

|----------|-------------|------------------------------|---------|--|

| Bit      | Function    | Description                  | Default |  |

| D7       |             | not used                     | 0       |  |

| D6       |             | not used                     | 0       |  |

| D5       |             | not used                     | 0       |  |

| D4       |             | not used                     | 0       |  |

| D3       |             | not used                     | 0       |  |

| D2       | FSK-Ramp 0  | only in bipolar mode         | 0       |  |

| D1       | FSK-Ramp 1  |                              | 0       |  |

| D0       | Bipolar_FET | 0= FET, 1=Bipolar            | 1       |  |

| Table 2-25 Sub Addre |                      | ress 0FH: BLOCK_PD               |         |

|----------------------|----------------------|----------------------------------|---------|

| Bit                  | Function Description |                                  | Default |

| D15                  | REF_PD               | 1= power down Band Gap Reference | 1       |

| D14                  | RC_PD                | 1= power down RC Oscillator      | 1       |

| D13                  | WINDOW_PD            | 1= power down Window Counter     | 1       |

| D12                  | ADC_PD               | 1= power down ADC                | 1       |

| D11                  | PEAK_DET_PD          | 1= power down Peak Detectors     | 1       |

| D10                  | DATA_SLIC_PD         | 1= power down Data Slicer        | 1       |

| D9                   | DATA_FIL_PD          | 1= power down Data Filter        | 1       |

| D8                   | QUAD_PD              | 1= power down Quadri Correlator  | 1       |

| D7                   | LIM_PD               | 1= power down Limiter            | 1       |

| D6                   | I/Q_FIL_PD           | 1= power down I/Q Filters        | 1       |

| D5                   | MIX2_PD              | 1= power down I/Q Mixer          | 1       |

| D4                   | MIX1_PD              | 1= power down 1st Mixer          | 1       |

| D3                   | LNA_PD               | 1= power down LNA                | 1       |

| D2                   | PA_PD                | 1= power down Power Amplifier    | 1       |

| D1                   | PLL_PD               | 1= power down PLL                | 1       |

| D0                   | XTAL_PD              | 1= power down XTAL Oscillator    | 1       |

| Table 2 | able 2-26 Sub Address 80H: STATUS |                                     |

|---------|-----------------------------------|-------------------------------------|

| Bit     | Function                          | Description                         |

| D7      | COMP_LOW                          | 1 if data rate < TH1                |

| D6      | COMP_IN                           | 1 if TH1 < data rate < TH2          |

| D5      | COMP_HIGH                         | 1 if TH2 < data rate                |

| D4      | COMP_0,5*LOW                      | 1 if data rate < 0,5*TH1            |

| D3      | COMP_0,5*IN                       | 1 if 0,5*TH1 < data rate < 0,5*TH2  |

| D2      | COMP_0,5*HIGH                     | 1 if 0,5*TH2 < data rate            |

| D1      | RSSI=TH3                          | 1 if RSSI value is equal TH3        |

| D0      | RSSI>TH3                          | 1 if RSSI value is greater than TH3 |

| Table 2-27 |          | ub Address 81H: ADC         |

|------------|----------|-----------------------------|

| Bit        | Function | Description                 |

| D7         | PD_ADC   | ADC power down feedback Bit |

| D6         | SELECT   | SELECT feedback Bit         |

| D5         | RSSI_5   | RSSI value Bit5             |

| D4         | RSSI_4   | RSSI value Bit4             |

| D3         | RSSI_3   | RSSI value Bit3             |

| D2         | RSSI_2   | RSSI value Bit2             |

| D1         | RSSI_1   | RSSI value Bit1             |

| D0         | RSSI_0   | RSSI value Bit0             |

## **Functional Description**

## 2.4.16 Wakeup Logic

Figure 2-9 Wakeup Logic States

| Table 2-28 MODE | settings: CONFIG reg | ister             |

|-----------------|----------------------|-------------------|

| MODE_1          | MODE_2               | Mode              |

| 0               | 0                    | SLAVE MODE        |

| 0               | 1                    | TIMER MODE        |

| 1               | X                    | SELF POLLING MODE |

**SLAVE MODE:** The receive and transmit operation is fully controlled by an external control device via the respective RxTx, AskFsk, PwdDD, and Data pins. The wakeup logic is inactive in this case.

After RESET or 1<sup>st</sup> Power-up the chip is in SLAVE MODE. By setting MODE\_1 and MODE\_2 in the CONFIG register the mode may be changed.

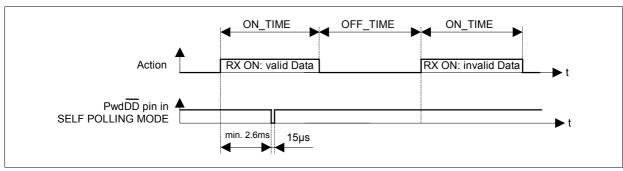

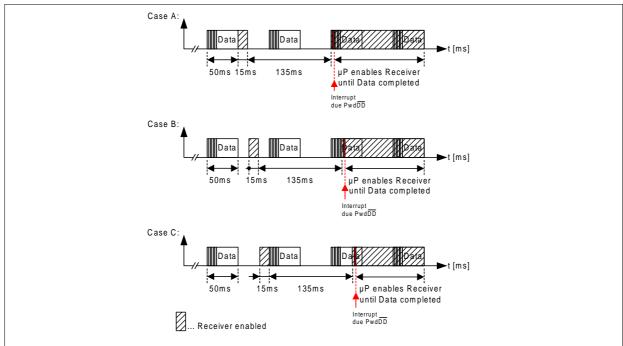

**SELF POLLING MODE:** The chip turns itself on periodically to receive using a built-in 32kHz RC oscillator. The timing of this is determined by the **ON\_TIME** and **OFF\_TIME** registers, the duty cycle can be set between 0 and 100% in 31.25μs increments. The data detect logic is enabled and a 15μs LOW impulse is provided at **PwdDD** pin (Pin 27), if the received data is valid.

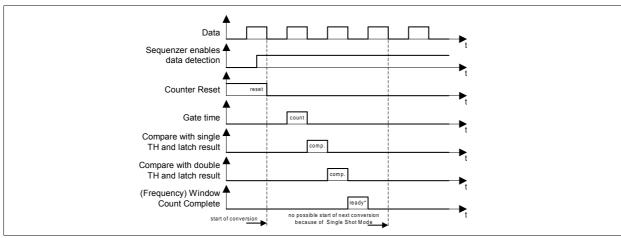

timing\_selfpllmode.wmf

Figure 2-10 Timing for Self Polling Mode (ADC & Data Detect in one shot mode)

## **Functional Description**

**Note:** The time delay between start of ON time and the 15µs LOW impulse is 2.6ms + 3 period of data rate.

If ADC & Data Detect Logic are in continuous mode the 15µs LOW impulse is applied at **PwdDD** after each data valid decision.

In self polling mode if D9=0 (Register 00h) and when **PwdDD** pin level is HIGH the CLK output is on during ON time and off during OFF time. If D9=1, the CLK output is always on.

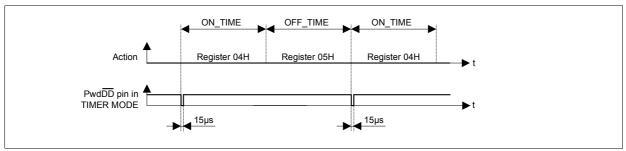

**TIMER MODE:** Only the internal Timer (determined by the **ON\_TIME** and **OFF\_TIME** registers) is active to support an external logic with periodical Interrupts. After ON\_TIME + OFF\_TIME a 15μs LOW impulse is applied at the **PwdDD** pin (Pin 27).

timing\_timermode.wmf

Figure 2-11 Timing for Timer Mode

Please note to add a serial resistor in the VDD supply line as mentioned on page 13 and in Section 4.4

## 2.4.17 Data Valid Detection, Data Pin

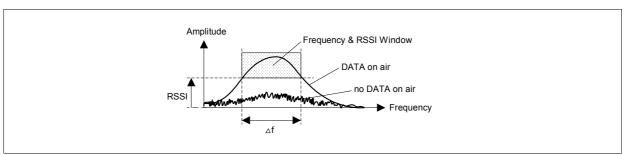

Data signals generate a typical spectrum and this can be used to determine if valid data is on air.

data rate detect.wmf

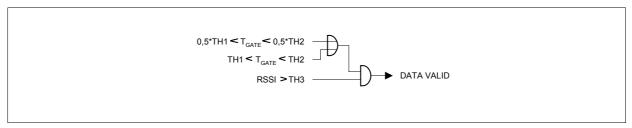

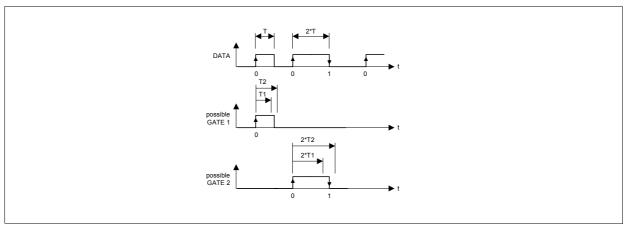

Figure 2-12 Frequency and RSSI Window

The "data valid" criterion is generated from the result of RSSI-TH3 comparison and  $t_{GATE}$  between TH1 and TH2 result as shown below. In case of Manchester coding the 0,5\*TH1 and 0,5\*TH2 gives improved performance.

## **Functional Description**

The use of permanent data valid recognition makes it absolutely necessary to set the RSSI-ADC and the Window counter into continuous mode (Register 00H, Bit D5 = D6 = 1).

data\_valid.wmf

Figure 2-13 Data Valid Circuit

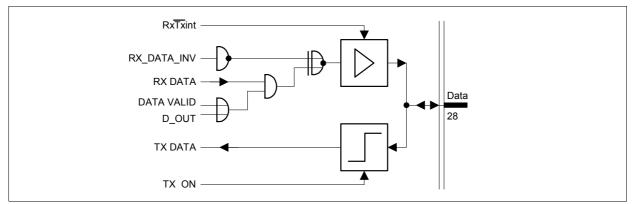

D\_OUT and RX\_DATA\_INV from the CONFIG register determine the output of data at Pin 28. **RxTxint** and TX\_ON are internally generated signals.

In RX and power down mode Data pin (Pin 28) is tied to GND.

data switch.wmf

Figure 2-14 Data Input/Output Circuit

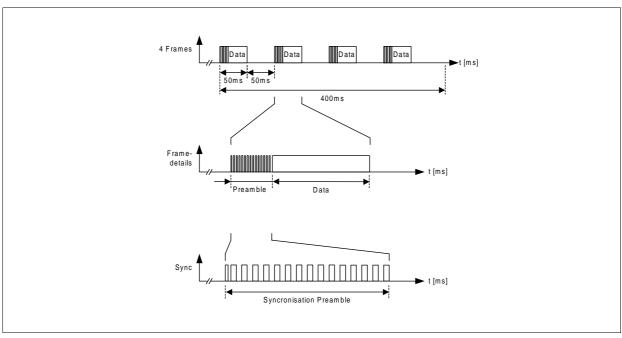

## 2.4.18 Sequence Timer

The sequence timer has to control all the enable signals of the analog components inside the chip. The time base is the 32 kHz RC oscillator.

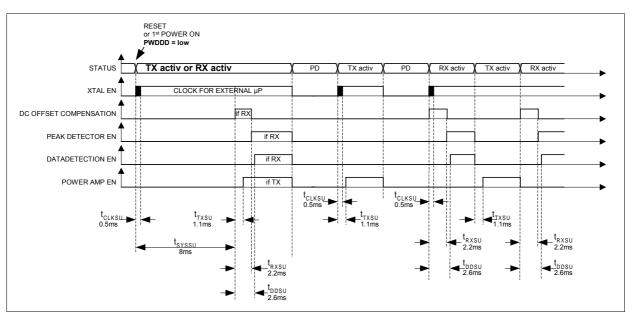

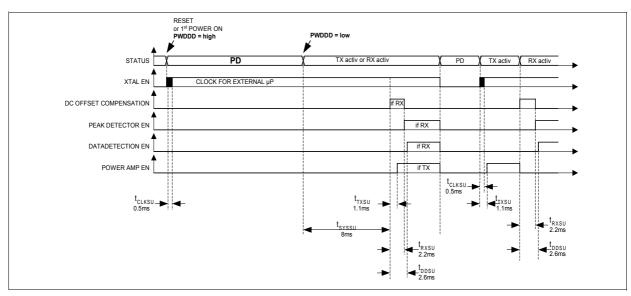

After the first POWER ON or RESET a 1 MHz clock is available at the clock output pin. This clock output can be used by an external  $\mu P$  to set the system into the desired state and outputs valid data after 500  $\mu$ s (see **Figure 2-15** and **Figure 2-16**, t<sub>CLKSU</sub>)

There are two possibilities to start the device after a reset or first power on:

- PWDDD pin is LOW: Normal operation timing is performed after t<sub>SYSSU</sub> (see Figure 2-15).

- PWDDD pin is HIGH (device in power down mode): A clock is offered at the clock output pin until the device is activated (PWDDD pin is pulled to LOW). After the first activation the time t<sub>SYSSU</sub> is required until normal operation timing is performed (see Figure 2-16).

This could be used to extend the clock generation without device programming or activation.

## **Functional Description**

**Note:** It is **required** to activate the device for the duration of  $t_{SYSSU}$  after first power on or a reset. Only if this is done the normal operation timing is performed.

With default settings the clock generating units are disabled during PD, therefore no clock is available at the clock output pin. It is possible to offer a clock signal at the clock output pin every time (also during PD) if the CLK\_EN Bit in the CONFIG register is set to HIGH.

Sequenzer\_Timing\_pupstart.wmf

Figure 2-15 1<sup>st</sup> start or reset in active mode

Note: The time values are typical values

$Sequenzer\_Timing\_pdstart.wmf$

Figure 2-16 1st start or reset in PD mode

## **Functional Description**

Note: The time values are typical values

This means that the device needs  $t_{DDSU}$  setup time to start the data detection after RX is activated. When activating TX it requires  $t_{TXSU}$  setup time to enable the power amplifier.

For timing information refer to **Table 4-3**.

For Test purposes a TESTMODE is provided by the Sequencer as well. In this mode the BLOCK\_PD register be set to various values. This will override the Sequencer timing. Depending on the settings in Config Register 00H the corresponding building blocks are enabled, as shown in the subsequent figure.

Figure 2-17 Sequencer's capability

sequencer\_raw.wmf

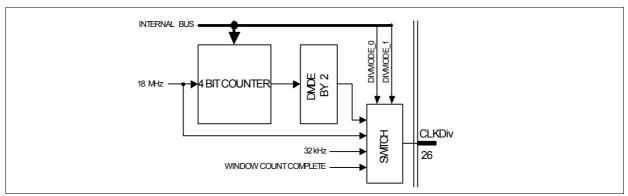

## 2.4.19 Clock Divider

It supports an external logic with a programmable Clock at pin 26 (CLKDIV).

clk div.wmf

Figure 2-18 Clock Divider

The Output Selection and Divider Ratio can be set in the CLK\_DIV register.

## **Functional Description**

| <b>Table 2-29</b> | CLK_DIV Output Selection |                               |  |

|-------------------|--------------------------|-------------------------------|--|

| D5                | D4                       | Output                        |  |

| 0                 | 0                        | Output from Divider (default) |  |

| 0                 | 1                        | 18.089MHz                     |  |

| 1                 | 0                        | 32kHz                         |  |

| 1                 | 1                        | Window Count Complete         |  |

Note: Data are valid 500  $\mu$ s after the crystal oscillator is enabled (see Figure 2-15 and Figure 2-16,  $t_{CLKSU}$ ).

| Table 2 | -30 ( | CLK_DI\ | / Setting | g                   |                        |

|---------|-------|---------|-----------|---------------------|------------------------|

| D3      | D2    | D1      | D0        | Total Divider Ratio | Output Frequency [MHz] |

| 0       | 0     | 0       | 0         | 2                   | 9,0                    |

| 0       | 0     | 0       | 1         | 4                   | 4,5                    |

| 0       | 0     | 1       | 0         | 6                   | 3,0                    |

| 0       | 0     | 1       | 1         | 8                   | 2,25                   |

| 0       | 1     | 0       | 0         | 10                  | 1,80                   |

| 0       | 1     | 0       | 1         | 12                  | 1,50                   |

| 0       | 1     | 1       | 0         | 14                  | 1,28                   |

| 0       | 1     | 1       | 1         | 16                  | 1,125                  |

| 1       | 0     | 0       | 0         | 18                  | 1,00 (default)         |

| 1       | 0     | 0       | 1         | 20                  | 0,90                   |

| 1       | 0     | 1       | 0         | 22                  | 0,82                   |

| 1       | 0     | 1       | 1         | 24                  | 0,75                   |

| 1       | 1     | 0       | 0         | 26                  | 0,69                   |

| 1       | 1     | 0       | 1         | 28                  | 0,64                   |

| 1       | 1     | 1       | 0         | 30                  | 0,60                   |

| 1       | 1     | 1       | 1         | 32                  | 0,56                   |

**Note:** As long as default settings are used, there is no clock available at the clock output during Power Down. It is possible to enable the clock during Power Down by setting CLK\_EN (Bit D9) in the Config Register (00H) to HIGH.

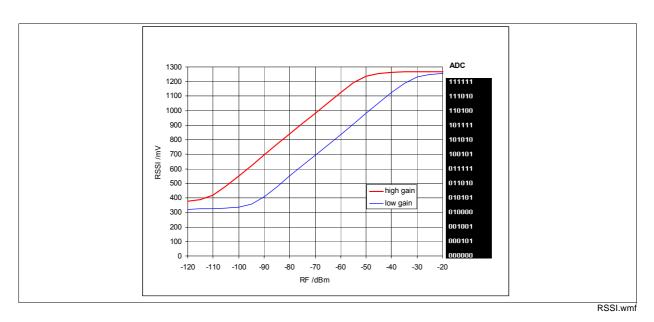

## 2.4.20 RSSI and Supply Voltage Measurement

The input of the 6Bit-ADC can be switched between two different sources: the RSSI voltage (default setting) or a resistor network dividing the Vcc voltage by 5.

| Table 2-31 So | Source for 6Bit-ADC Selection (Register 08H) |  |  |  |

|---------------|----------------------------------------------|--|--|--|

| SELECT        | Input for 6Bit-ADC                           |  |  |  |

| 0             | Vcc / 5                                      |  |  |  |

| 1             | RSSI (default)                               |  |  |  |

## **Functional Description**

To prevent wrong interpretation of the ADC information (read from Register 81H: ADC) you can use the ADC- Power Down feedback Bit (D7) and the SELECT feedback Bit (D6) which correspond to the actual measurement.

**Note:** As shown in **Section 2.4.18** there is a setup time of 2.6ms after RX activating. Thus the measurement of RSSI voltage does only make sense after this setup time.

# 3 Application

### 3.1 LNA and PA Matching

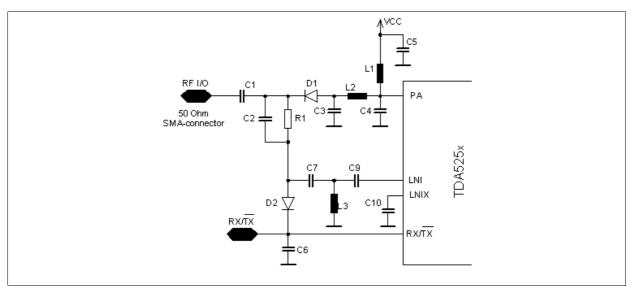

### 3.1.1 RX/TX Switch

RX/TX\_Switch.wmf

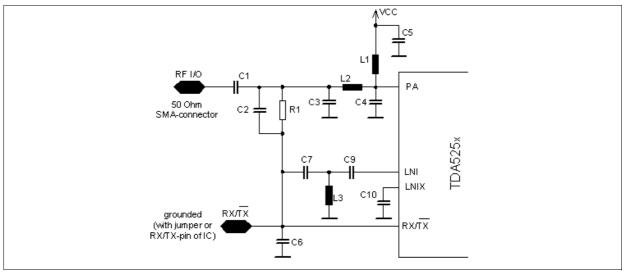

Figure 3-1 RX/TX Switch

The RX/TX-switch combines the PA-output and the LNA-input into a single 50 Ohm SMA-connector. Two pin-diodes are used as switching elements. If no current flows through a pin diode, it works as a high impedance for RF with very low capacitance. If the pin-diode is forward biased, it provides a low impedance path for RF. (some  $\Omega$ )

#### 3.1.2 Switch in RX-Mode

The RX/TX-switch is set to the receive mode by either applying a high level or an open to the RX/TX-jumper on the evalboard or by leaving it open. Then both pin-diodes are not biased and therefore have a high impedance.

RX\_Mode.wmf

Figure 3-2 RX-Mode

The RF-signal is able to run from the RF-input-SMA-connector to the LNA-input-pin LNI via C1, C2, C7, L3 and C9. R1 does not affect the matching circuit due to its high resistance. The other input of the differential LNA LNIX can always be AC-grounded using a large capacitor without any loss of performance. In this case the differential LNA can be used as a single ended LNA, which is easier to match. The S11 of the LNA at pin LNI on the evalboard is  $0.94 / -23^{\circ}$  (equals a resistor of 1.67kOhm in parallel to a capacitor of 1.5pF) for both high and low-gain-mode of the LNA. (pin LNIX AC-grounded) This impedance has to be matched to 50 Ohm with the parts C9, L3, C7 and C2. C1 is a DC-decoupling-capacitor. On the evalboard the most important matching components are (shunt) L3 and (series)C7, C2. The capacitors is mainly a DC-decoupling-capacitor and may be used for some fine tuning of the matching circuit. A good CAE tool (featuring smith-chart) may be used for the calculation of the values of the components. However, the final values of the matching components always have to be found on the board because of the parasitics of the board, which highly influence the matching circuit at RF.

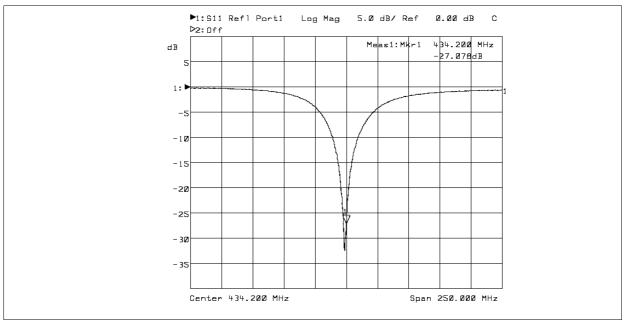

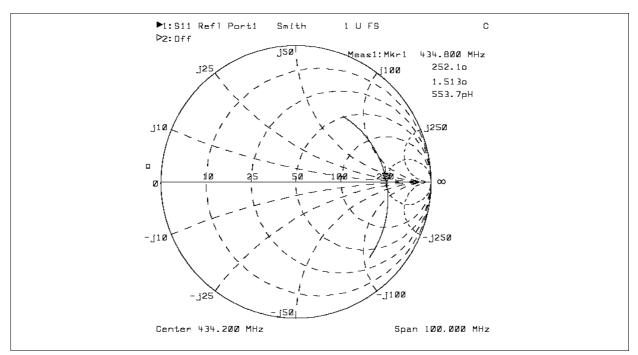

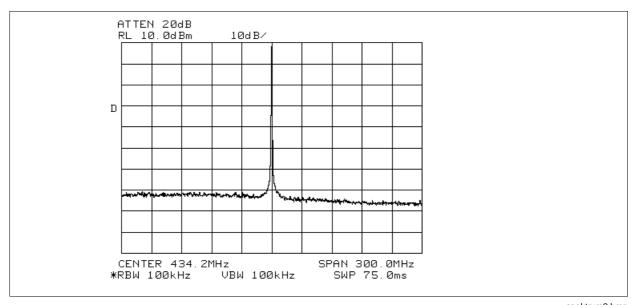

Measured Magnitude of S11 of evalboard:

S11\_measured\_434.pcx.

### Figure 3-3 S11 measured

Above you can see the measured S11 of the evalboard. The -3dB-points are at 404MHz and 468MHz. So the 3dB-bandwidth is:

$$B = f_U - f_L = 468MHz - 404MHz = 64MHz$$

$$Q_L = \frac{f_{center}}{B} = \frac{434,2MHz}{64MHz} = 6,8$$

[3 - 1]

The unloaded Q of the resonant circuit is equal to the Q of the inductor due to its losses.

$$Q_U = Q_{INDUCTOR} \approx 32 @ 434MHz$$

[3 - 3]

An approximation of the losses of the input matching network can be made with the formula:

$$LOSS = -20 * \log \left[ 1 - \frac{Q_L}{Q_U} \right] = -20 * \log \left[ 1 - \frac{6.8}{32} \right] = 2dB$$

[3 - 4]

The noise figure of the LNA-input-matching network is equal to its losses. The input matching network is always a compromise of sensitivity and selectivity. The loaded Q should not get too high because of 2 reasons:

more losses in the matching network and hence less sensitivity

tolerances of components affect matching too much. This will cause problems in a tuning-free mass production of the application. A good CAE-tool will help to see the effects of component tolerances on the input matching more accurate by tweaking each value.

A very high selectivity can be reached by using SAW-filters at the expense of higher cost and lower sensitivity which will be reduced by the losses of the SAW-Filter of approx. 4dB.

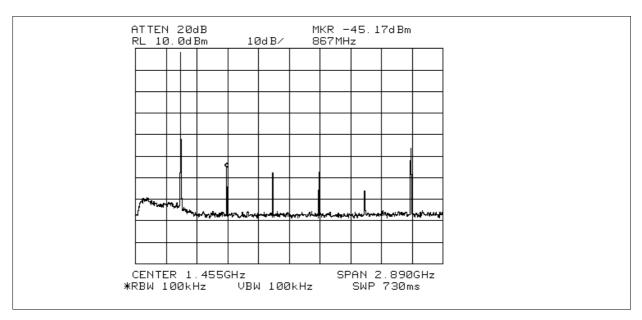

Image-suppression:

Due to the quite high 1<sup>st</sup>-IF of the frontend, the image frequency is quite far away. The image frequency of the receiver is at:

$$f_{IMAGE} = f_{SIGNAL} + 2 * f_{IF} = 434,2MHz + 2 * 144,7 = 723,7MHz$$

[3 – 5]

The image suppression on the evalboard is about 16dB.

#### LO-leakage:

The LO of the 1st Mixer is at:

$$f_{LO} = f_{RECEIVE} * \frac{4}{3} = 434,2MHz * \frac{4}{3} = 578,9MHz$$

[3 - 6]

The LO-leakage of the evalboard on the RF-input is about –102dBm. This is far below the ETSI-radio-regulation-limit for LO-leakage.

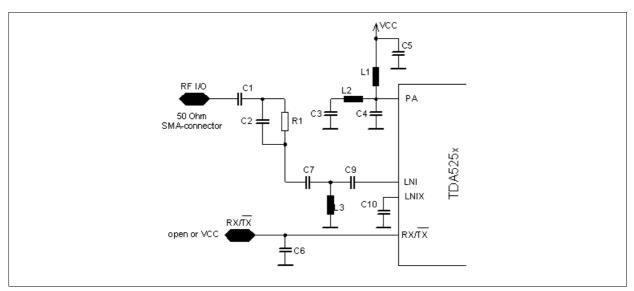

#### 3.1.3 Switch in TX-Mode

The evalboard can be set into the TX-Mode by grounding the RX/TX-jumper on the evalboard or programming the TDA5255 to operate in the TX-Mode. If the IC is programmed to operate in the TX-Mode, the RX/TX-pin will act as an open drain output at a logical LOW. Then a DC-current can flow from VCC to GND via L1, L2, D1, R1 and D2.

$$I_{PIN\ DIODE} \quad \frac{Vcc \quad 2 \quad V_{FORWARD,PIN\ DIODE}}{R_{1}}$$

[3 - 7]

Now both pin-diodes are biased with a current of approx. 0.3mA@3V and have a very low impedance for RF.

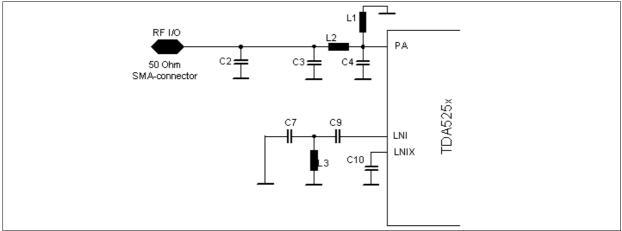

TX\_Mode.wmf

#### Figure 3-4 TX\_Mode

R1 does not influence the matching because of its very high resistance. Due to the large capacitance of C1, C6 and C5 the circuit can be further simplified for RF:

TX\_Mode\_simplified.wmf

Figure 3-5 TX\_Mode\_simplified

The LNA-matching is RF-grounded now, so no power is lost in the LNA-input. The PA-matching consists of C2, C3 L2, C4 and L1.

When designing the matching of the PA, C2 must not be changed anymore because its value is already fixed by the LNA-input-matching.

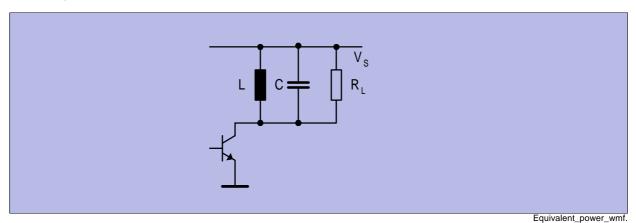

### 3.1.4 Power-Amplifier

The power amplifier operates in a high efficient class C mode. This mode is characterized by a pulsed operation of the power amplifier transistor at a current flow angle of  $\theta << \pi$ . A frequency selective network at the amplifier output passes the fundamental frequency component of the pulse spectrum of the collector current to the load. The load and its resonance transformation to the collector of the power amplifier can be generalized by the equivalent circuit of **Figure 3-6**. The tank circuit L//C//RL in parallel to the output impedance of the transistor should be in resonance at the operating frequency of the transmitter.

Figure 3-6 Equivalent power amplifier tank circuit

The optimum load at the collector of the power amplifier for "critical" operation under idealized conditions at resonance is:

$$R_{LC} = \frac{V_S^2}{2P_C}$$

[3 – 8]

A typical value of  $R_{LC}$  for an RF output power of  $P_0$ = 13mW is:

$$R_{LC} = \frac{3^2}{2*0.013} = 350\Omega$$

[3 - 9]

Critical" operation is characterized by the RF peak voltage swing at the collector of the PA transistor to just reach the supply voltage  $V_S$ . The high efficiency under "critical" operating conditions can be explained by the low power loss at the transistor.

During the conducting phase of the transistor there is no or only a very small collector voltage present, thus minimizing the power loss of the transistor ( $i_C^*u_{CE}$ ). This is particularly true for low current flow angles of  $\theta <<\pi$ . In practice the RF-saturation voltage of the PA transistor and other parasitics will reduce the "critical"  $R_{LC}$ .

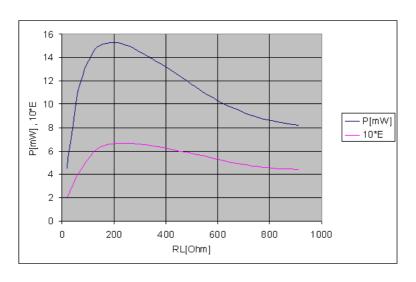

The output power  $P_0$  will be reduced when operating in an "overcritical" mode at a  $R_L > R_{LC}$ . As shown in Figure 3-7, however, power efficiency E (and bandwidth) will increase by some degree when operating at higher  $R_I$ . The collector efficiency E is defined as

$$E = \frac{P_O}{V_c I_C}$$

[3 – 10]

The diagram of Figure 3-7 has been measured directly at the PA-output at  $V_S=3V$ . A power loss in the matching circuit of about 3dB will decrease the output power. As shown in the diagram, 250 Ohm is the optimum impedance for operation at 3V. For an approximation of  $R_{OPT}$  and  $P_{OUT}$  at other supply voltages those 2 formulas can be used:

$$R_{OPT} \sim V_S$$

[3 – 11]

and

$$P_{OUT} \sim R_{OPT}$$

[3 – 12]

Power\_E\_vs\_RL\_434.wmf

Figure 3-7 Output power  $P_0$  (mW) and collector efficiency E vs. load resistor  $R_L$ .

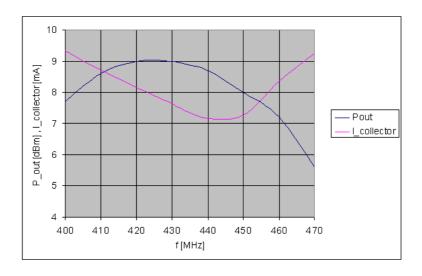

The DC collector current  $I_C$  of the power amplifier and the RF output power  $P_O$  vary with the load resistor  $R_L$ . This is typical for overcritical operation of class C amplifiers. The collector current will show a characteristic dip at the resonance frequency for this type of "overcritical" operation. The depth of this dip will increase with higher values of  $R_I$ .

As **Figure 3-8** shows, detuning beyond the bandwidth of the matching circuit results in a significant increase of collector current of the power amplifier and in some loss of output power. This diagram shows the data for the circuit of the test board at the frequency of 434MHz. The effective load resistor of this circuit is  $R_L$ = 250Ohm, which is the optimum impedance for operation at 3V. This will lead to a dip of the collector current f approx. 20%.

pout\_vs\_frequ\_434.wmf

Figure 3-8 Power output and collector current vs. frequency