December 2012

# HI-3000H, HI-3001H

1Mbps Avionics CAN Transceiver with High Operating Temperature

### **GENERAL DESCRIPTION**

The HI-3000H is a 1 Mbps Controller Area Network (CAN) transceiver optimized for use in high temperature avionics applications. The device is capable of operating at extended temperature ranges of -55°C to 175°C for plastic packages and -55°C to 200°C for the ceramic CERDIP-8 package. It interfaces between a CAN protocol controller and the physical wires of the bus in a CAN network. Differential output amplitude and current drive capability are specifically enhanced to meet the needs of long cable runs typical of avionics applications.

The HI-3000H supports two modes of operation: Normal Mode and Standby Mode. The Standby Mode is a very low-current mode which continues to monitor bus activity and allows an external controller to manage wake-up.

Superior common-mode receiver performance makes the device especially suitable for applications where ground reference voltages may vary from point to point over long distances along the CAN bus. In addition, the HI-3000H provides a SPLIT pin to give an output reference voltage of VDD/2 which can be used for stabilizing the recessive bus level when the split termination technique is used to terminate the bus.

A TXD dominant time-out feature protects the bus from being driven into a permanent dominant state (so-called "babbling idiot") if pin TXD becomes permanently low due to application failure.

The device also has short circuit protection to +/-58V on CANH, CANL and SPLIT pins and ESD protection to +/-6kV on all pins.

The HI-3001H is identical to the HI-3000H except the SPLIT pin is substituted with a VIO supply voltage pin. This allows the HI-3001H to interface directly with controllers with 3.3V supply voltages.

### PIN CONFIGURATIONS (Top Views)

8-Pin Plastic SOIC package (Narrow Body) & 8-Pin Ceramic CERDIP

### **FEATURES**

- Extended Temperature Ranges -55°C to 175°C (plastic SOIC-8 package) and -55°C to 200°C (ceramic CERDIP-8 package)

- Compatible with ARINC 825 and ISO 11898-5 standards.

- · Signaling rates up to 1Mbit/s.

- Internal VDD/2 voltage source available to stabilize the recessive bus level if split termination is used (HI-3000H SPLIT pin).

- VIO input on HI-3001H allows for direct interfacing with 3.3V controllers.

- Detection of permanent dominant on TXD pin (babbling idiot protection).

- High impedance allows connection of up to 120 nodes.

- Input levels compatible with 3.3V or 5V controllers.

- CANH, CANL and SPLIT pins short-circuit proof to +/-58V.

- Will not disturb the bus if unpowered.

## PIN DESCRIPTIONS

| SIGNAL     | FUNCTION | DESCRIPTION                                                                                   |

|------------|----------|-----------------------------------------------------------------------------------------------|

| TXD        | INPUT    | 100kOhm internal pull-up. Transmit Data Input.                                                |

| GND        | POWER    | Chip 0V supply                                                                                |

| VDD        | POWER    | Positive supply, 5V +/-5%. Bypass with 0.1uF ceramic capacitor.                               |

| RXD        | OUTPUT   | Receive Data Output.                                                                          |

| CANL       | BUS I/O  | CAN Bus Line Low.                                                                             |

| CANH       | BUS I/O  | CAN Bus Line High.                                                                            |

| STB        | INPUT    | 100kOhm internal pull-up. Standby Mode selection input. Drive STB low or connect to GND       |

|            |          | for Normal operation. Drive STB high to select low-current Standby Mode.                      |

| SPLIT      | INPUT    | Supplies a VDD/2 output to provide recessive bus level stabilization when a split termination |

| (HI-3000H) |          | is used to terminate the bus.                                                                 |

| VIO        | INPUT    | Connect to a 3.3V supply to allow compatibility of all digital I/O (RXD, TXD, STB) with a     |

| (HI-3001H) |          | 3.3V controller input.                                                                        |

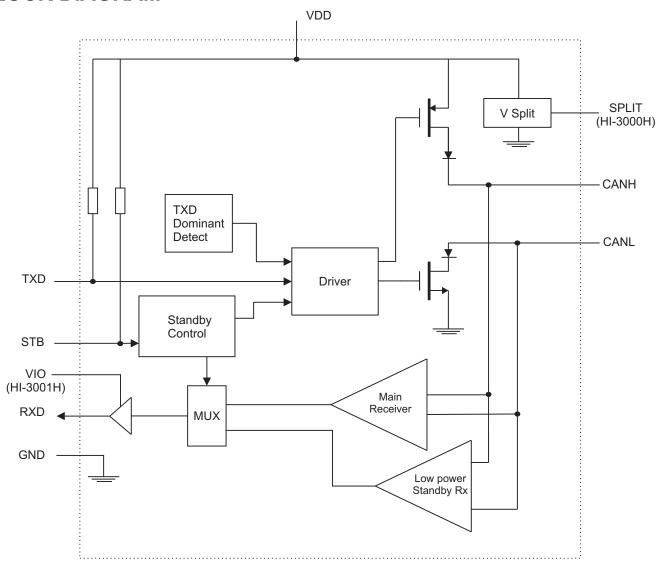

## **BLOCK DIAGRAM**

Figure 1. HI-3000H Functional Block Diagram

#### **FUNCTIONAL DESCRIPTION**

#### **OPERATING MODES**

The HI-3000H provides two modes of operation which are selectable via the STB pin. Table 1 summarizes the modes.

Table 1 - Operating Modes

| MODE    | STB pin |

|---------|---------|

| Normal  | LOW     |

| Standby | HIGH    |

#### **Normal Mode**

Normal mode is selected by setting the STB pin to a LOW logic level (GND). In this mode, the transceiver transmits and receives data in the usual way from the CANH and CANL bus lines. The differential receiver converts the analog bus data to digital data which is output on the RXD pin (Note: the RXD output on HI-3001H is compatible with 3.3V controllers if the VIO pin is connected to a 3.3V supply).

#### Standby Mode

Standby Mode is selected by setting the STB pin to a HIGH logic level. In this mode, the transmitter is switched off and a low power differential receiver monitors the bus lines for activity. A dominant signal of more than  $3\mu$ s will be reflected on the RXD pin as a logic LOW, where it may be detected by the host as a wake-up request. The device will not leave standby mode until the host forces the STB pin to a logic low.

#### **SPLIT Circuit**

The SPLIT pin provides a stable VDD/2 DC voltage. This pin can be used to stabilize the recessive common mode voltage by connecting the SPLIT pin to the center tap of the split termination (see figure 7). In the case of a recessive bus voltage dropping below the ideal value of VDD/2 (e.g.

due to an unpowered node with high leakage from the bus lines to ground), the split circuit will force the recessive voltage to VDD/2.

#### INTERNAL PROTECTION FEATURES

#### **Short-circuit protection**

Short-circuit protection is provided on the CANH, CANL and SPLIT pins. These pins are protected from ESD to over 6KV (HBM) and from shorts between -58V and +58V continuous, as specified in ISO 11898-5. The short circuit current is limited to less than 200mA typical.

#### TXD permanent dominant time-out

A timer circuit prevents the bus lines being driven into a permanent dominant state, which would result in a situation blocking all bus traffic. This could happen in the case of the TXD pin becoming permanently low due to a hardware or application failure. The timer is triggered by a negative edge on the TXD pin (start of dominant state). If the TXD pin is not set high (recessive state) after a typical time of 2ms, the transmitter outputs will be disabled, driving the bus lines into the recessive state. The timer is reset by a positive edge on the TXD pin. Note that the minimum TXD dominant time-out time, tdom =  $300\mu s$ , defines the minimum possible bit rate of 40kbit/s (the CAN protocol specifies a maximum of 11 successive dominant bits – 5 successive dominant bits immediately followed by an error frame).

#### Fail-safe features

Pin TXD has a pull up in order to force a recessive level if pin TXD is left open.

Pins TXD and STB will become floating if power is lost. This will prevent reverse currents via these pins.

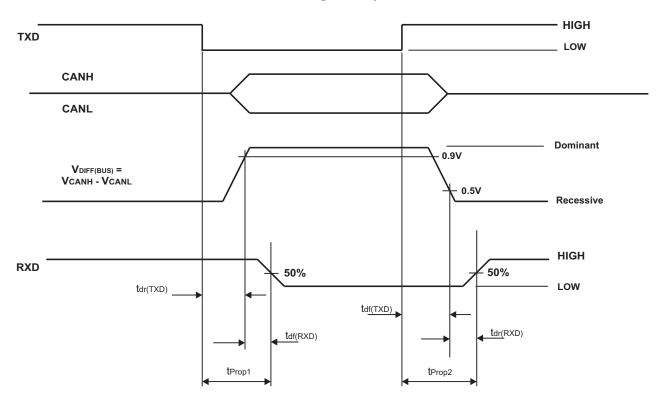

### **TIMING DIAGRAMS**

## **Timing Delays**

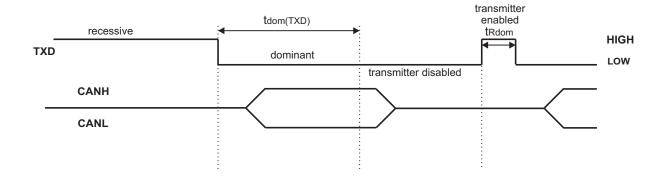

### TXD dominant time-out feature

### **ABSOLUTE MAXIMUM RATINGS**

(Voltages referenced to GND = 0V)

| Supply Voltage, VDD, VIO:                                                        | Operating Temperature Range: (Plastic)55°C to +175°C (Ceramic)55°C to +200°C |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| DC Voltages at CANH, CANL and SPLIT:58V to +58V Internal Power Dissipation:900mW | Storage Temperature Range: -65°C to +150°C                                   |

| Electrostatic Discharge (ESD)¹, All pins+/- 6kV                                  | Soldering Temperature: (Ceramic)                                             |

#### NOTES:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

VDD = 5V±5%, Operating temperature range (unless otherwise noted). Positive currents flow into the IC.

| DADAMETED                                                                           | CONDITIONS                 |                                                                                |                 |               |                     |          |  |

|-------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------|-----------------|---------------|---------------------|----------|--|

| PARAMETER                                                                           | SYMBOL                     | CONDITIONS                                                                     | MIN             | TYP           | MAX                 | UNIT     |  |

| SUPPLY CURRENT                                                                      |                            |                                                                                |                 |               |                     |          |  |

| VDD Supply Current                                                                  | IDD                        | Recessive: VTXD = VDD<br>Dominant: VTXD = 0 V<br>Standby Mode: VTXD = VDD      |                 | 6<br>50<br>15 | 10<br>70<br>50      | mA<br>mA |  |

| VIO Supply Current                                                                  | lio                        | Standby Mode. VIXD - VDD                                                       |                 | 15            | 100                 | μA<br>μA |  |

| DIGITAL INPUTS (Pins TXD, STB)                                                      |                            |                                                                                |                 |               |                     |          |  |

| HIGH-level input voltage (see Note 1)<br>LOW-level input voltage (TXD pin)          | VIH<br>VIL                 |                                                                                | 80%VDD<br>- 0.5 |               | VDD + 0.5<br>20%VDD | V        |  |

| HIGH-level input current<br>LOW-level input current                                 | Iıн<br>Iı∟                 | VTXD = VDD or VIO<br>VTXD = 0 V                                                | - 5             | 0<br>- 50     | + 5<br>- 150        | μA<br>μA |  |

| DIGITAL OUTPUTS                                                                     |                            |                                                                                |                 |               |                     |          |  |

| HIGH-level output voltage (RXD Pin) (see Note 1) LOW-level output voltage (RXD Pin) | Vон<br>Vol                 | IOH = 1mA<br>IOL = 1mA                                                         | 90%VDD<br>0     | 0.1           | 10%Vpd              | V        |  |

| Output voltage (SPLIT Pin)<br>Standby leakage current (SPLIT Pin)                   | Vsplit<br>Istb             | – 100 μA < IspLiT < 100 μA                                                     | 0.45VDD<br>-5   | 0.5VDD        | 0.55VDD<br>+5       | V<br>µA  |  |

| DRIVER                                                                              |                            |                                                                                |                 |               |                     |          |  |

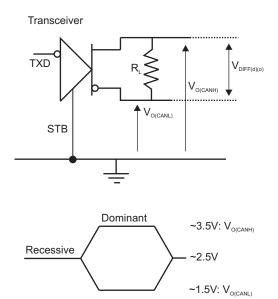

| CANH dominant output voltage<br>CANL dominant output voltage                        | Vo(canh)<br>Vo(canl)       | $V_{TXD} = 0 V$<br>$V_{TXD} = 0 V (See Fig. 2)$                                | 3<br>0.5        | 3.6<br>1.4    | 4.25<br>1.75        | V        |  |

| Recessive output voltage                                                            | VCANH(r),<br>VCANL(r)      | VTXD = VDD, RL = 0 (See Fig. 2)                                                | 2               | 0.5VDD        | 3                   | V        |  |

| Bus output voltage in standby                                                       | VstB                       | VTXD = VDD, RL = 0 (See Fig. 2)                                                | -0.1            |               | 0.1                 | V        |  |

| Dominant differential output voltage<br>Recessive differential output voltage       | VDIFF(d)(o)<br>VDIFF(r)(o) | VTXD = 0 V, 45 $\Omega$ < RL < 65 $\Omega$<br>VTXD = VDD, no load (See Fig. 2) | 1.5<br>- 50     | 1.8<br>0      | 3<br>50             | V<br>mV  |  |

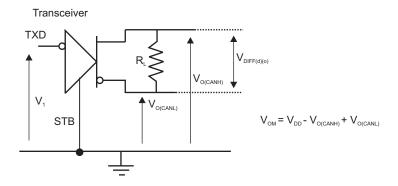

| Matching of dominant output voltage,<br>VDD - VO(CANH) - VO(CANL)                   | Vом                        | (See Fig. 4)                                                                   | - 100           | -40           | 150                 | mV       |  |

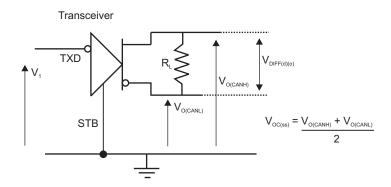

| Steady state common mode output voltage                                             | VOC(ss)                    | Vstb = 0V, RL = 60 $\Omega$ (See Fig. 5)                                       | 2               | 0.5VDD        | 3                   | V        |  |

#### NOTE:

<sup>1.</sup> Human Body Model (HBM).

<sup>1.</sup> When VIO is connected (HI-3001H), limits are referenced wrt VIO rather than  $\mbox{Vdd}$ .

## DC ELECTRICAL CHARACTERISTICS (cont.)

$VDD = 5V\pm5\%$ , Operating temperature range. Positive currents flow into the IC.

|                                                                                                                         |                                                    |                                                                                                                            | LIMITS                    |            |                        |                |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|------------------------|----------------|

| PARAMETER                                                                                                               | SYMBOL                                             | CONDITIONS                                                                                                                 | MIN                       | TYP        | MAX                    | UNIT           |

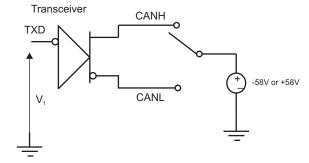

| Short-circuit steady-state output current                                                                               | IOS(ss)                                            | VCANH = +58V, VCANL open<br>VCANH = -58V, VCANL openV<br>VCANL = +58V, VCANH open<br>VCANL = -58V, VCANH open (See Fig. 6) | -20<br>-200<br>100<br>-20 |            | 20<br>100<br>200<br>20 | mA<br>mA<br>mA |

| RECEIVER                                                                                                                |                                                    |                                                                                                                            |                           |            |                        |                |

| Differential receiver threshold voltage Differential hysteresis voltage Differential hysteresis voltage in Standby mode | VTh(Rx)(diff)<br>VHys(Rx)(diff)<br>VHys(Stb)(diff) | - 12 V < VCANH, VCANL < + 12 V<br>- 12 V < VCANH, VCANL < + 12 V<br>- 12 V < VCANH, VCANL < + 12 V                         | 500<br>50<br>500          | 700<br>120 | 900<br>200<br>1150     | mV<br>mV<br>mV |

| Input leakage current, unpowered node                                                                                   | ICANH, ICANL                                       | V <sub>DD</sub> = V <sub>IO</sub> 0 V<br>V <sub>CANH</sub> = V <sub>CANL</sub> = 5V                                        | - 200                     |            | + 200                  | μΑ             |

| Differential input resistance                                                                                           | RIN(DIFF)                                          | VTXD = VDD<br>- 12 V < VCANH, VCANL < + 12 V                                                                               | 25                        | 50         | 100                    | kΩ             |

| Common mode input resistance                                                                                            | RIN(CM)                                            | VTXD = VDD<br>- 12 V < VCANH, VCANL < + 12 V                                                                               | 15                        | 30         | 45                     | kΩ             |

| Deviation between common mode input resistance between CANH and CANL                                                    | RIN(CM)(m)                                         | VCANH = VCANL                                                                                                              | - 3                       |            | + 3                    | %              |

### **AC ELECTRICAL CHARACTERISTICS**

$VDD = 5V \pm 5\%$ , Operating temperature range. Positive currents flow into the IC.

|                                                                                                              |                                              |                                                                 | LIMITS  |                      |                       |                      |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------|---------|----------------------|-----------------------|----------------------|

| PARAMETER                                                                                                    | SYMBOL                                       | CONDITIONS                                                      | MIN     | TYP                  | MAX                   | UNIT                 |

| Bit time<br>Bit rate                                                                                         | tBit<br>fBit                                 |                                                                 | 1<br>40 |                      | 25<br>1000            | μs<br>kHz            |

| Common mode input capacitance <sup>3</sup> Differential input capacitance <sup>3</sup>                       | CIN(CM)<br>CDIFF(CM)                         | VTXD = VDD, 1Mbit/s data rate<br>VTXD = VDD, 1Mbit/s data rate  |         | 20<br>10             |                       | pF<br>pF             |

| Delay TXD to bus active Delay TXD to bus inactive Delay bus active to RXD Delay bus inactive to RXD          | tdr(TXD)<br>tdf(TXD)<br>tdf(RXD)<br>tdr(RXD) | See Timing Diagrans                                             |         | 40<br>40<br>30<br>70 | 90<br>90<br>70<br>150 | ns<br>ns<br>ns<br>ns |

| Propagation delay TXD to RXD (recessive to dominant)<br>Propagation delay TXD to RXD (dominant to recessive) | tProp1<br>tProp2                             |                                                                 |         | 70<br>110            | 160<br>240            | ns<br>ns             |

| TXD permanent dominant time-out TXD permanent dominant timer reset time                                      | tdom<br>tRdom                                | VTXD = 0 V Rising edge on TXD while in permanent dominant state | 0.3     | 2                    | 6<br>1                | ms<br>µs             |

| Dominant time required on bus for wake up from standby                                                       | t <sub>wake</sub>                            |                                                                 | 0.5     | 3                    | 5                     | μs                   |

#### NOTES:

- All currents into the device pins are positive; all currents out of the device pins are negative.

All typicals are given for VDD = 5V, TA = 25°C.

- 3. Guaranteed by design but not tested.

## **Application and Test Information**

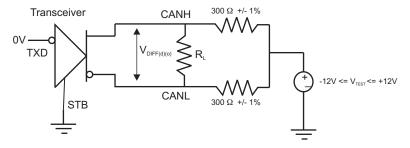

Figure 2. CAN Bus Driver Circuit

Figure 3. CAN Bus Driver (Dominant) Test Circuit

Figure 4. Driver Output Symmetry Test.

## **Application and Test Information**

Figure 5. Common Mode Output Voltage Test.

Figure 6. CAN Bus Driver Short-Circuit Test. (Note: V1 is a pulse from 0V to VDD with duty cycle of 99% such that permanent dominant time-out is avoided).

## **Application and Test Information**

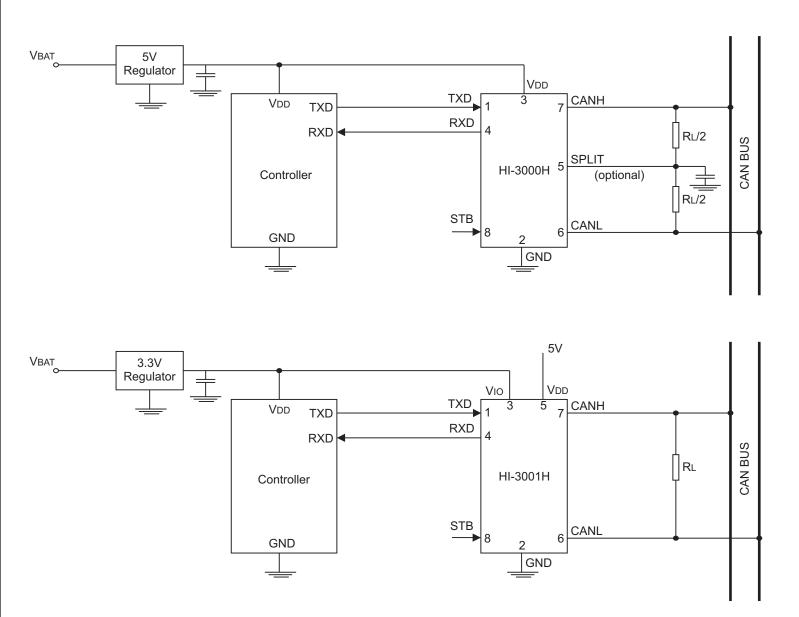

Figure 7. Typical Application Connections

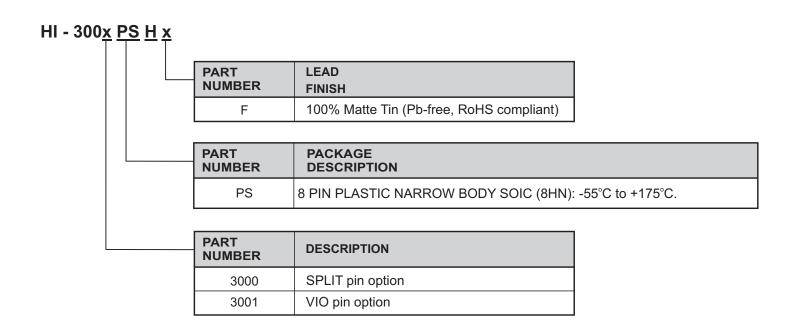

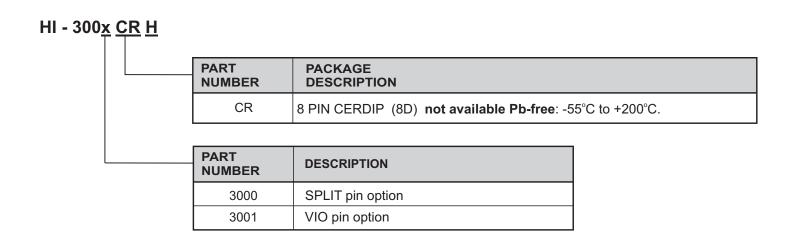

### **ORDERING INFORMATION**

## HI-3000H, HI-3001H

## **REVISION HISTORY**

| P/N     | Rev | Date     | Description of Change |

|---------|-----|----------|-----------------------|

| DS3000H | New | 12/05/12 | Initial Release       |

|         |     |          |                       |

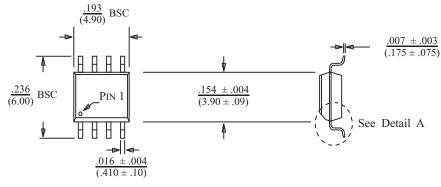

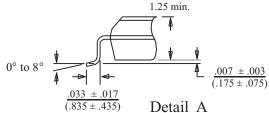

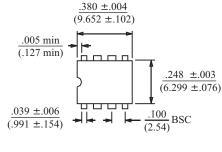

## **PACKAGE DIMENSIONS**

## 8-PIN PLASTIC SMALL OUTLINE (SOIC) - NB

(Narrow Body)

inches (millimeters)

Package Type: 8HN

BSC = "Basic Spacing between Centers" is theoretical true position dimension and has no tolerance. (JEDEC Standard 95)

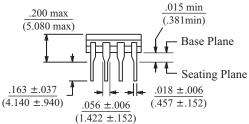

### **8-PIN CERDIP**

inches (millimeters)

Package Type: 8D

.314 ±.003 (7.976 ±.076) .010 ±.006 (.254 ±.152) .350 ±.030 (8.890 ±.762)

BSC = "Basic Spacing between Centers" is theoretical true position dimension and has no tolerance. (JEDEC Standard 95)