# **Detailed Specification - ICD**

# 1. Introduction

## 1.1 Scope

This version of the ICD is the version generated after qualification campaign closure.

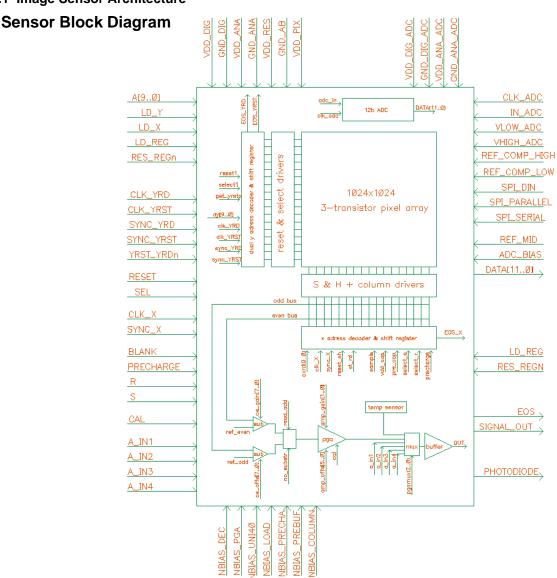

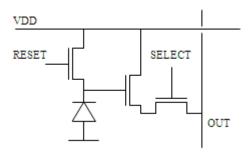

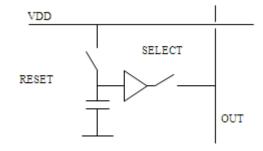

This specification details the ratings, physical, geometrical, electrical and electro-optical characteristics, test- and inspection-data for the High Accuracy Star Tracker (HAS) Version 2 CMOS Active Pixel image Sensor (CMOS APS).

The device described in this document is protected by US patent 6,225,670 and others.

# 1.2 Component Type Variants

A summary of the type variants of the basic CMOS image sensor is given in Table 1 on page 8. The complete list of detailed specifications for each type variant is given in Table 3 on page 9 for each type separately.

All specifications in Table 3 on page 9 are given at  $25 \pm 3^{\circ}$ C, under nominal clocking and bias conditions. Exceptions are noted in the 'remarks' field.

# 1.3 Maximum Rating

The maximum ratings which shall not be exceeded at any time during use or storage are as scheduled in Table 2 on page 9.

## 1.4 Physical Dimensions and Geometrical Information

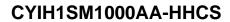

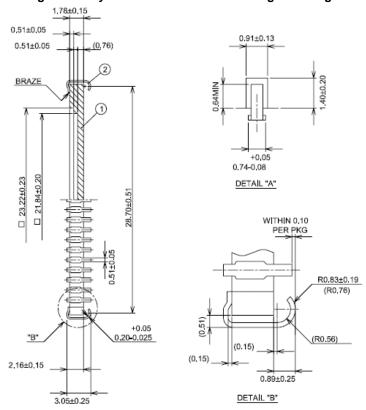

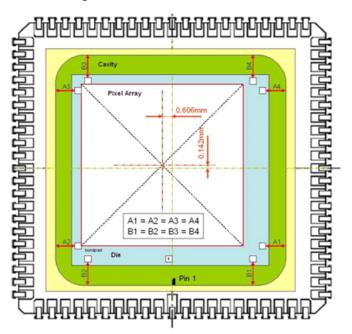

The physical dimensions of the assembled component are shown in Figure 2 on page 25. The geometrical information in Figure 4 on page 26 describes the position of the die in the package.

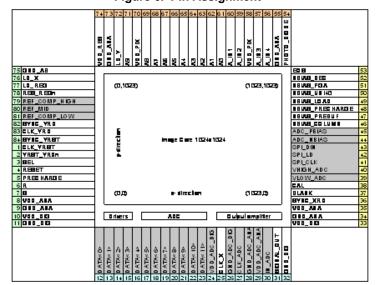

### 1.5 Pin Assignment

Figure 6 on page 27 contains the pin assignment. The figure contains a schematic drawing and a pin list. A detailed functional description of each pin can be found in "Pin List" on page 39.

#### 1.6 Soldering Instructions

Soldering is restricted to manual soldering only. No wave or reflow soldering is allowed. For the manual soldering, following restrictions are applicable:

- Solder 1 pin on each of the 4 sides of the sensor.

- Cool down period of min. 1 minute before soldering another pin on each of the 4 sides.

- Repeat soldering of 1 pin on each side, including a 1 minute cool down period.

# 1.7 Handling Precautions

The component is susceptible to damage by electro-static discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling. The following guidelines are applicable:

- Always manipulate the devices in an ESD controlled environment.

- Always store the devices in a shielded environment that protects against ESD damage (at least a non-ESD generating tray and a metal bag).

- Always wear a wrist strap when handling the devices and use ESD safe gloves.

- The HAS2 is classified as class 1A (JEDEC classification -[AD03]) device for ESD sensitivity.

# 1.8 Storage Information

The components must be stored in a dust-free and temperature, humidity and ESD controlled environment.

- Devices must always be stored in special ESD-safe trays such that the glass window is never touched.

- The trays are closed with EDS-safe rubber bands.

- The trays are sealed in an ESD-safe conductive foil in clean room conditions.

- For transport and storage outside a clean room the trays are packed in a second ESD-save bag that is sealed in clean room.

## 1.9 Procurement Requirements

The HAS2 image sensor can be procured at Cypress Semiconductor or its distributors, using the following references:

- Flight sensors: CYIH1SM1000AA-HHCS.

- Engineering sensors: CYIH1SM1000AA-HHCES.

The HAS sensor is subject to the standard European export regulations for dual use products.

A Certificate of Conformance will be issued upon request at no additional charge. The CoC will refer to this Detailed Specification.

Additional screening tests can be done upon request at additional cost.

The following data is by default delivered with FM sensors:

- Sensor calibration data

- Temperature calibration data

- Certificate of Conformance to this detailed specification

- Visual inspection report

- Bad pixel map

**Cypress Semiconductor Corporation** • 198 Champion Court • San Jose, CA 95134-1709 • Document Number: 001-54123 Rev. \*A Revised Septe

408-943-2600

[+] Feedback

# 2. Ordering Information

| Marketing Part Number | Description                    | Package     | Production    |

|-----------------------|--------------------------------|-------------|---------------|

| CYIH1SM1000AA-HHCS    | Space qualified (mono version) | 84 pin JLCC | In production |

| CYIH1SM1000AA-HHCES   | Standard Market (mono version) | 84 pin JLCC | Nov-09        |

# 3. Applicable Documents

The following documents form part of this specification and shall be read in conjunction with it:

| Nr.  | Reference                        | Title                                                                    | Issue     | Date           |

|------|----------------------------------|--------------------------------------------------------------------------|-----------|----------------|

| AD01 | ESCC Generic Specification 9020  | Charge Coupled Devices, Silicon, Photosensitive                          | 2 Draft F |                |

| AD02 | Cypress 001-06225 <sup>[1]</sup> | Electro-optical test methods for CMOS image sensors                      | E         | October, 2008  |

| AD03 | JESD22-A114-B                    | Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM) | В         | June, 2000     |

| AD04 | APS2-FVD-06-003                  | Process Identification Document for HAS2                                 | 2         | February, 2008 |

| AD05 | Cypress 001-49283                | Visual Inspection for FM devices                                         | 1         | January, 2008  |

| AD06 | Cypress 001-49280                | HAS2 FM Screening                                                        | 2         | June, 2009     |

# 4. Acronyms Used

For the purpose of this specification, the terms, definitions, abbreviations, symbols, and units specified in ESCC basic Specification 21300 shall apply. In addition, the following table contains terms that are specific to CMOS image sensors and are not listed in ESCC21300

| Abbreviation | Description                   |

|--------------|-------------------------------|

| ADC          | Analog to Digital Convertor   |

| APS          | Active Pixel Sensor           |

| CDS          | Correlated Double Sampling    |

| DNL          | Differential Non Linearity    |

| DR           | Destructive Readout           |

| DSNU         | Dark Signal Non Uniformity    |

| EPPL         | European Preferred Parts List |

| ESD          | Electro-Static Discharge      |

| FPN          | Fixed Pattern Noise           |

| HAS          | High Accuracy Startracker     |

| INL          | Integral Non Linearity        |

| MTF          | Modulated Transfer Function   |

| NDR          | Non Destructive Readout       |

| PRNU         | Pixel Response Non Uniformity |

| TBC          | To be Confirmed               |

| TBD          | To be Defined                 |

| RGA          | Residual Gas Analysis         |

### Note

Document Number: 001-54123 Rev. \*A Page 2 of 71

This specification will be superseded by the ESCC basic specification 25000 which is currently under development. The current reference is an internal Cypress procedure which is a confidential document.

The following formulas are applicable to convert % Vsat and mV/s into e- and e-/s:

$$FPN[e-] = \frac{FPN[\%Vsat]*\overline{Vsat}}{conversion\_gain}$$

$$Dark\_signal[e-/s] = \frac{Dark\_signal[V/s]}{conversion\_gain}$$

$$DSNU[e-] = \frac{DSNU[\%Vsat]*\overline{Vsat}}{conversion\_gain}$$

Other definitions:

$$ADC \ Quantization \ Noise = \frac{\cfrac{Ana \log Range}{ADC \ \text{Re } solution}}{\sqrt{ADC \ \text{Re } solution}}$$

■ Conversion gain for HAS: 14.8 µV/e-

■ Definition for Local measurements: 32 x 32 pixels

■ Definition for Global measurements: Full pixel array

## 5. Detailed Information

#### 5.1 Deviations from Generic Specification

Lot acceptance and screening are based on ESCC 9020 issue 2 draft F. section 5.9 on page 5 of this specification describes the lot acceptance and screening.

#### 5.2 Mechanical Requirements

#### 5.2.1 Dimension Check

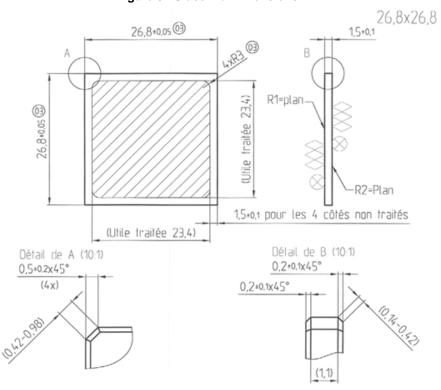

The dimensions of the components specified herein shall be checked. They shall comply with the specifications and the tolerances as indicated in Figure 2 on page 25.

#### 5.2.2 Geometrical Characteristics

The geometrical characteristics of the components specified herein shall be checked. They shall comply with the specifica-

tions and the tolerances as indicated in Figure 2 on page 25 and Figure 3 on page 26.

#### 5.2.3 Weight

The maximum weight of the components specified herein shall be as specified in Table 3 on page 9 - Mechanical Specifications, item 2.

#### 5.3 Materials and Finishes

The materials and finishes shall be as specified herein. Where a definite material is not specified, a material which will enable the components specified herein to meet the performance requirements of this specification shall be used.

#### 5.3.1 Case

The case shall be hermetically sealed and have a ceramic body and a glass window.

| Туре                                  | JLCC-84                   |

|---------------------------------------|---------------------------|

| Material                              | Black Alumina<br>BA-914   |

| Thermal expansion coefficient         | 7.6 x 10 <sup>-6 /K</sup> |

| Hermeticity                           | < 5·10-7 atms.<br>cm3/s   |

| Thermal resistance (Junction to case) | 3.633 °C/W                |

#### 5.3.2 Lead material and finish

| Lead material          | KOVAR            |

|------------------------|------------------|

| 1e Finish              | Nickel, min 2 μm |

| 2 <sup>nd</sup> Finish | Gold, min 1.5 μm |

#### 5.3.3 Window

The window material is a BK7G18 glass lid with anti-reflective coating applied on both sides.

The optical quality of the glass shall have the following specification:

See Table 3 on page 9 - glass window specification

The anti reflective coating shall have a reflection coefficient < 1.3% absolute and < 0.8% on average, over a bandwidth from 440 nm to 1100 nm.

#### 5.4 Marking

#### 5.4.1 General

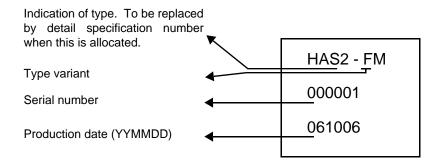

The marking Shall consist of a lead identification and traceability information.

#### 5.4.2 Lead Identification

An index to pin 1 shall be located on the top of the package in the position defined in Figure 2 on page 25. The pin numbering is counter clock-wise, when looking at the top-side of the component.

#### 5.4.3 Traceability Information

Each component shall be marked such that complete traceability can be maintained.

The component shall bear a number that is constituted as follows:

## 5.5 Electrical and Electro-optical Measurements

#### 5.5.1 Electrical and Electro-optical Measurements at Reference Temperature

The parameters to be measured to verify the electrical and electro-optical specifications are scheduled in Table 4 on page 14 and Table 13 on page 24. Unless otherwise specified, the measurements shall be performed at a environmental temperature of 22±3°C.

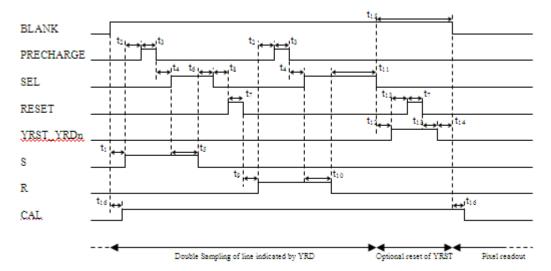

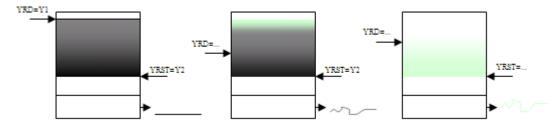

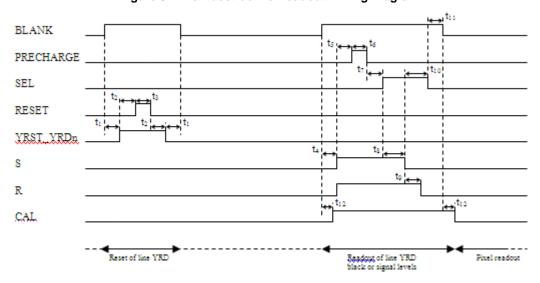

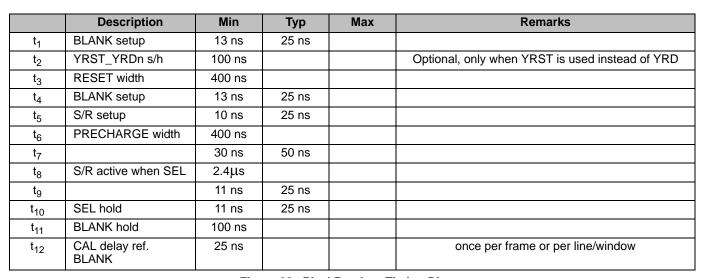

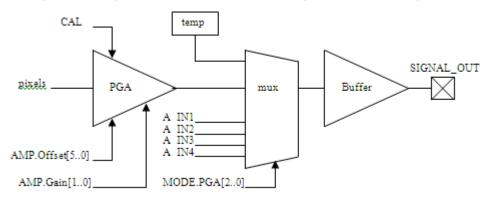

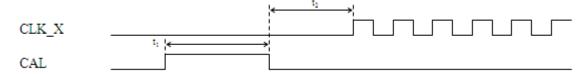

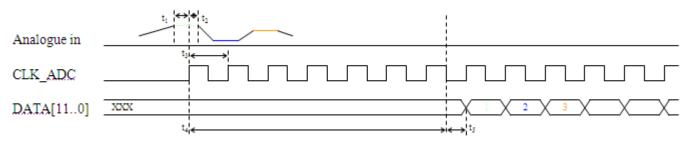

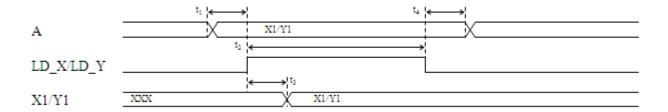

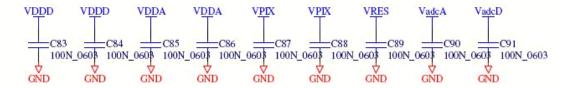

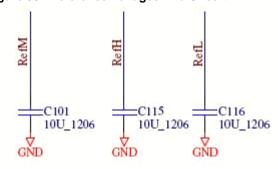

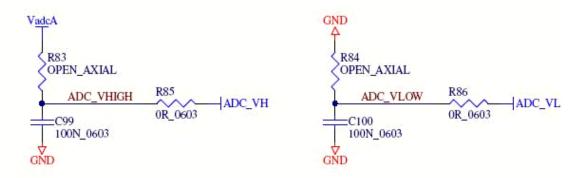

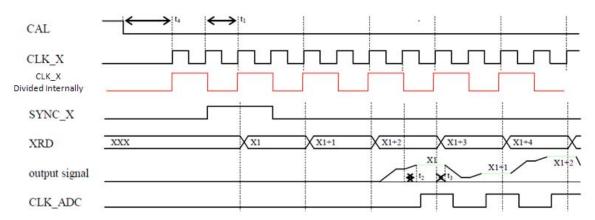

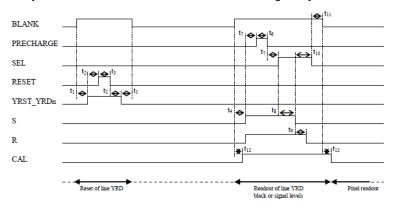

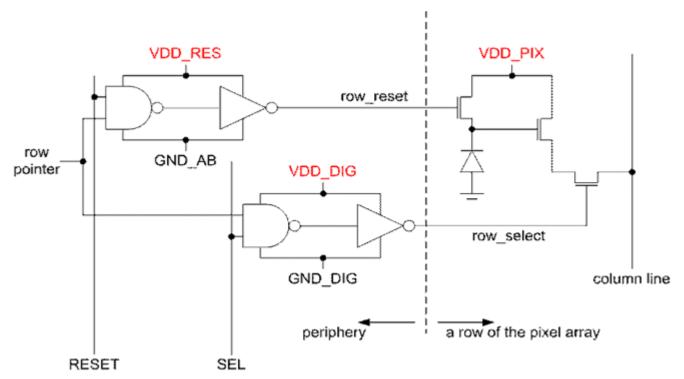

For all measurements the nominal power supply, bias and clocking conditions apply. The nominal power supply and bias conditions are given in Table 14 on page 24, the timing diagrams in Figure 35 on page 51 and Figure 37 on page 53.

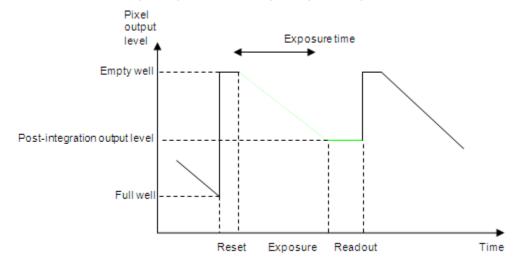

Remark: The given bias and power supply settings imply that the devices are measured in "soft- reset" condition.

# 5.5.2 Electrical and Electro-optical measurements at High and Low Temperature

The parameters to be measured to verify the electrical and electro-optical specifications are scheduled in Table 5 on page 15 and Table 6 on page 16. Unless otherwise specified, the measurements shall be performed at

-40 (-5 +0) °C and at +85 (+5 -0) °C.

## 5.5.3 Circuits for Electrical and Electro-optical Measurements

Circuits for performing the electro-optical tests in Table 4 on page 14 and Table 13 on page 24 are shown in Figure 48 on page 63 to Figure 51 on page 63.

#### 5.6 Burn-in Test

#### 5.6.1 Parameter Drift Values

The parameter drift values for power burn-in are specified in Table 7 on page 18 of this specification. Unless otherwise specified the measurements shall be conducted at a environmental temperature of 22±3°C and under nominal power supply, bias and timing conditions.

The parameter drift values shall not be exceeded. In addition to these drift value requirements, also the limit values of any parameter - as indicated in Table 4 on page 14 - shall not be exceeded.

Conditions for high temperature reverse bias burn-in

Not Applicable

#### 5.6.2 Conditions for Power Burn-in

The conditions for power burn-in shall be as specified in Table 10 on page 21 of this specification

# 5.6.3 Electrical Circuits for High Temperature Reverse Bias Burn-in

Not Applicable

#### 5.6.4 Electrical Circuits for Power Burn-in

Circuits to perform the power burn-in test are shown in Figure 48 on page 63 and next ones of this specification.

#### 5.7 Environmental and Endurance Tests

#### 5.7.1 Electrical and Electro-optical Measurements on Completion of Environmental Test

The parameters to be measured on completion of environmental tests are scheduled in Table 11 on page 21. Unless otherwise stated, the measurements shall be performed at a environmental temperature of 22±3°C. Measurements of dark current must be performed at 22±1°C and the actual environmental temperature must be reported with the test results.

## 5.7.2 Electrical and Electro-optical Measurements At Intermediate Point During Endurance Test

The parameters to be measured at intermediate points during endurance test of environmental tests are scheduled in Table 11 on page 21. Unless otherwise stated, the measurements shall be performed at an environmental temperature of 22±3°C

# 5.7.3 Electrical and electro-optical measurements on Completion of Endurance Test

The parameters to be measured on completion of endurance tests are scheduled in Table 11 on page 21. Unless otherwise stated, the measurements shall be performed at a environmental temperature of 22±3°C

#### 5.7.4 Conditions for Operating Life Test

The conditions for operating life tests shall be as specified in Table 10 on page 21 of this specification.

#### 5.7.5 Electrical Circuits for Operating Life Test

Circuits for performing the operating life test are shown in Figure 48 on page 63 and next ones of this specification.

#### 5.7.6 Conditions for High Temperature Storage Test

The temperature to be applied shall be the maximum storage temperature specified in Table 2 on page 9 of this specification.

#### 5.8 Total Dose Radiation Test

#### 5.8.1 Application

The total dose radiation test shall be performed in accordance with the requirements of ESCC Basic specification 22900.

#### 5.8.2 Parameter Drift Values

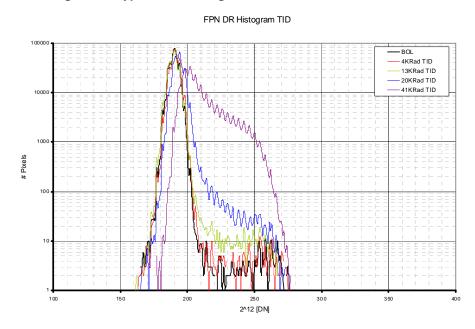

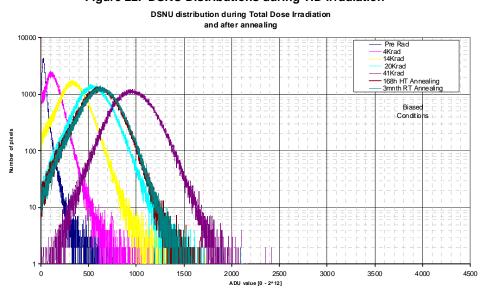

The allowable parameter drift values after total dose irradiation are listed in Table 8 on page 19. The parameters shown are valid after a total dose of 42KRad and 168h/100°C annealing.

#### 5.8.3 Bias conditions

Continuous bias shall be applied during irradiation testing as shown in Figure 48 on page 63 and next ones of this specification.

#### 5.8.4 Electrical and Electro-optical Measurements

The parameters to be measured, prior to, during and on completion of the irradiation are listed in Table 13 on page 24 of this specification. Only devices that meet the specification in Table 4 on page 14 of this specification shall be included in the test samples.

## 5.9 Lot Acceptance and Screening

This paragraph describes the Lot Acceptance Testing (LAT) and screening on the HAS FM devices. All tests on device level have to be performed on screened devices (see Table 5.9.6 on page 7).

### 5.9.1 Wafer Lot Acceptance

This is the acceptance of the silicon wafer lot. This has to be done on every wafer lot that will be used for the assembly of flight models.

| Test                         | Test method                | Number of devices | Test condition    | Test location |

|------------------------------|----------------------------|-------------------|-------------------|---------------|

| Wafer processing data review | PID                        | NA                | NA                | CY            |

| SEM                          | ESCC 21400                 | 4 naked dies      | NA                | Test house    |

| Total dose test              | ESCC 22900                 | 3 devices         | 42 krad : 1krad/h | ESTEC by CY   |

| Endurance test               | MIL-STD-883<br>Method 1005 | 6 devices         | 2000h at +125 C   | Test House    |

Before and after total dose test and endurance test:

- Electrical measurements before and after at high, low and room temperature. Conform Table 4 on page 14 and Table 5 on page 15, Table 6 on page 16 of this specification.

- Visual inspection before and after

- Detailed electro optical measurements before and after

#### 5.9.2 Glass Lot Acceptance

Transmission and reflectance curves that are delievered with each lot shall be compared with the specifications in Table, "Glass Lid Specification," on page 10

3 glass lid shall be chosen randomly from the lot and will be measured in detail. All obtained results will be compared with Figure 5 on page 27.

# 5.9.3 Package lot acceptance

5 packages shall be chosen randomly from the lot and will be measured in detail. All obtained results will be compared with Figure 2 on page 25.

A solderability test is covered in the assembly lot acceptance tests (Table 5.9.4).

# 5.9.4 Assembly Lot Acceptance

| Test                                      | Test method              | Number of devices | Test condition                           | Test location  |

|-------------------------------------------|--------------------------|-------------------|------------------------------------------|----------------|

| Special assembly house in process control |                          |                   |                                          | Assembly House |

| Bond strength test                        | MIL-STD-883 method 2011  | 2                 | D                                        | Assembly House |

| Assembly House Geometrical data review    | Review                   | All               |                                          | CY             |

| Solder ability                            | MIL-STD883, method 2003  | _                 | D                                        | Test House     |

| Terminal strength                         | MIL-STD 883, method 2004 | 3                 |                                          |                |

| Marking permanence                        | ESCC 24800               |                   |                                          |                |

| Geometrical measurements                  | PID                      | All               |                                          | CY             |

| Temperature cycling                       | MIL-STD 883, method 1010 | 5                 | Condition B<br>50 cycles<br>-55°C/+125°C | Test House     |

| Moisture resistance                       | JEDEC Std. Method A101-B | 1                 | 240h at 85°C/85%                         | Test House     |

| DPA:                                      |                          | •                 |                                          |                |

| Die shear test                            | MIL-STD-883 method 2019  |                   | N/A                                      | Test House     |

| Bond pull test                            | MIL-STD-883 method 2011  | 4                 | All wires                                | Test House     |

Before and after the following tests are done:

■ Electrical measurements conform Table 4 on page 14 of this specification

■ Detailed visual inspection

■ Fine leak test + Gross leak test

Fine- and gross-leak tests shall be performed using the following methods:

**Fine Leak test:** MIL-STD-883, Test Method 1014, Condition A **Gross Leak test:** MIL-STD-883, Test Method 1014, Condition C The required leak rate for fine leak testing is 5·10-7 atms. cm3/s

# 5.9.5 Periodic Testing

| Test                 | Test method              | Number of devices | Test condition                                                          | Test location |

|----------------------|--------------------------|-------------------|-------------------------------------------------------------------------|---------------|

| Mechanical Shock     | MIL-STD 883, method 2002 | 2                 | B - 5 shocks, 1500g<br>- 0,5ms - ½ sine,<br>6 axes                      | Test House    |

| Mechanical Vibration | MIL-STD 883, method 2007 | 2                 | A - 4 cycles, 20g 80<br>to 2000 Hz, 0,06<br>inch 20 to 80 Hz,<br>3 axes | Test House    |

| DPA:                 |                          |                   |                                                                         |               |

| Die shear test       | MIL-STD-883 method 2019  | _                 | N/A                                                                     | Test House    |

| Bond pull test       | MIL-STD-883 method 2011  | 2                 | All wires                                                               | Test House    |

Periodic testing is required every 2 years. Before and after the following tests are done:

■ Electrical measurements conform Table 4 on page 14.

■ Detailed visual inspection

■ Fine leak test + Gross leak test

Fine- and gross-leak tests shall be performed using the following methods:

**Fine Leak test:** MIL-STD-883, Test Method 1014, Condition A **Gross Leak test:** MIL-STD-883, Test Method 1014, Condition C The required leak rate for fine leak testing is 5-10 7 atms. cm3/s

# 5.9.6 Screening

| Nr. | Test                         | Test method             | Number of devices | Test condition                   | Test location |

|-----|------------------------------|-------------------------|-------------------|----------------------------------|---------------|

| 1   | HCRT Electrical measurements | 001-53958               | All               | HT +85°C<br>LT -40°C<br>RT +25°C | CY            |

| 2   | Visual inspection            | 001-49283 + ICD         | All               |                                  | CY            |

| 3   | Die placement measurements   | Cypress internal proc.  | All               |                                  | CY            |

| 4   | XRAY                         | ESCC 20900              | All               |                                  | Test House    |

| 5   | Stabilization bake           | MIL-STD-883 method 1008 | All               | 48h at 125°C                     | Test House    |

| 6   | Fine leak test               | MIL-STD-883 method 1014 | All               | A                                | Test House    |

| 7   | Gross leak test              | MIL-STD-883 method 1014 | All               | С                                | Test House    |

| 8   | Temperature cycling          | MIL-STD-883 method 1010 | All               | B - 10 cycles<br>-55°C +125°C    | Test House    |

| 9   | Biased Burn-in               | ICD                     | All               | 240h at +125°C.                  | CY            |

| 10  | Mobile Particle Detection    | MIL-STD-883 method 2020 | All               | Α                                | Test House    |

| 11  | Fine leak test               | MIL-STD-883 method 1014 | All               | Α                                | Test House    |

| 12  | Gross leak test              | MIL-STD-883 method 1014 | All               | С                                | Test House    |

| 13  | HCRT Electrical measurements | 001-53958               | All               | HT +85°C<br>LT -40°C<br>RT +25°C | CY            |

| 14  | Final Visual Inspection      | 001-49283 + ICD         | All               |                                  | CY            |

Page 7 of 71

# 6. Tables and Figures

# 6.1 Specification Tables

Table 1. Type Variant Summary

| HAS2 Type Variants                                     | Engineering samples (HHCES) | Flight model samples (HHCS) |

|--------------------------------------------------------|-----------------------------|-----------------------------|

| Optical Quality (See "Optical quality - Definitions" o | n page 70.)                 |                             |

| Dead pixels                                            | 100                         | 20                          |

| Bright pixels in FPN image                             | 50                          | 20                          |

| Bad pixels in PRNU image                               | 150                         | 50                          |

| Bad columns                                            | 5                           | 0                           |

| Bad rows                                               | 5                           | 0                           |

| Bright pixel clusters:                                 |                             |                             |

| 2 adjacent bright pixels                               | 25                          | 2                           |

| 4 or more adjacent bright pixels                       | 10                          | 0                           |

| DSNU defects @ 22 dec BOL                              | 1200                        | 1000                        |

| DSNU defects @ 22 dec EOL                              | 1500                        | 1250                        |

| Particle Contamination                                 |                             |                             |

| Fixed particles outside focal plane                    | N/A                         | N/A                         |

| Mobile particles > 20um                                | 0                           | 0                           |

| Fixed particles on focal plane > 20um                  | 0                           | 0                           |

| Mobile particles > 10um and < 20um                     | 20                          | 10                          |

| Fixed particles on focal plane > 10um and < 20um       |                             |                             |

| Particles < 10um                                       | N/A                         | N/A                         |

| Wafer lot acceptance (section 5.9.1 on page 5)         | NO                          | YES                         |

| Glass lot acceptance (section 5.9.2 on page 5)         | NO                          | YES                         |

| Assembly lot acceptance (Table 5.9.4 on page 6)        | NO                          | YES                         |

| Periodic testing (Table 5.9.5 on page 7)               | NO                          | YES                         |

| Screening (Table 5.9.6 on page 7)                      | NO                          | YES                         |

| Calibration data                                       | Optional                    | YES                         |

| Visual Inspection + particle mapping                   | Optional                    | YES                         |

**Table 2. Maximum Ratings**

| No | Characteristic                    | Min  | Тур | Max          | Unit | Remarks                                                                   |

|----|-----------------------------------|------|-----|--------------|------|---------------------------------------------------------------------------|

| 1  | Any supply voltage except VDD_RES | -0.5 | 3.3 | +7.0         | V    |                                                                           |

| 2  | Supply voltage at VDD_RES         | -0.5 | 3.3 | +5.0         | V    | 3.3V for normal operation; up to 5V for increased full well capacity.     |

| 3  | Voltage on any input terminal     | -0.5 | 3.3 | Vdd +<br>0.5 | V    |                                                                           |

| 4  | Soldering temperature             | NA   | NA  | 260          | °C   | Hand soldering only; See section 1.6 on page 1 for soldering instructions |

| 5  | Operating temperature             | -40  | NA  | +85          | °C   |                                                                           |

| 6  | Storage temperature               | -55  | NA  | +125         | °C   |                                                                           |

Table 3. Detailed Specification All Type Variants

| Gene | General Characteristics |     |               |     |        |                                     |  |  |  |

|------|-------------------------|-----|---------------|-----|--------|-------------------------------------|--|--|--|

| No   | Characteristic          | Min | Тур           | Max | Unit   | Remarks                             |  |  |  |

| 1    | Image sensor format     | N/A | 1024x<br>1024 | N/A | pixels |                                     |  |  |  |

| 2    | Pixel size              | N/A | 18            | N/A | μm     |                                     |  |  |  |

| 3    | ADC resolution          | N/A | 12            | N/A | bit    | 10 bit accuracy at 5 Msamples / sec |  |  |  |

| Silico | Silicon Particle Contamination Specification |     |     |     |      |                                      |  |  |  |

|--------|----------------------------------------------|-----|-----|-----|------|--------------------------------------|--|--|--|

| No     | Characteristic                               | Min | Тур | Max | Unit | Remarks                              |  |  |  |

| 1      | Optical quality:<br>Particle max size        | N/A | N/A | 20  | um   | See "Type Variant Summary" on page 8 |  |  |  |

| Mech | anical Specifications                                                        |             |        |            |      |                                                                                  |

|------|------------------------------------------------------------------------------|-------------|--------|------------|------|----------------------------------------------------------------------------------|

| No   | Characteristic                                                               | Min         | Тур    | Max        | Unit | Remarks                                                                          |

| 1a   | Flatness of image area                                                       | NA          | 7.4    | NA         | μm   | Peak-to-peak at 25 ± 3 °C<br>Specified by the foundry over<br>an entire 8" wafer |

| 1b   | Flatness of glass lid                                                        | NA          | 90     | 150        | μm   | Towards ceramic package                                                          |

| 2    | Mass                                                                         | 7.7         | 7.85   | 8.0        | g    |                                                                                  |

| 3    | Total thickness                                                              | 3.2         | 3.3    | 3.4        | mm   | Package + epoxy + glass lid                                                      |

| 4a   | Die position, X offset                                                       | NA          | NA     | 0.1        | mm   | Die in center of cavity                                                          |

| 4b   | Die position, Y offset                                                       | NA          | NA     | 0.1        | mm   | Die in center of cavity                                                          |

| 5    | Die position, parallelism vs window<br>Die position, parallelism vs backside | -0.1<br>0.1 | 0<br>0 | 0.1<br>0.1 | mm   |                                                                                  |

| 6    | Die position, Y tilt                                                         | -0.1        | 0      | 0.1        | 0    |                                                                                  |

| 7    | Die position, X tilt                                                         | -0.1        | 0      | 0.1        | 0    |                                                                                  |

| 8    | Die – window distance                                                        | 0.25        | 0.3    | 0.35       | mm   |                                                                                  |

Document Number: 001-54123 Rev. \*A Page 9 of 71

| Glas | s Lid Specification                                                               |                |                |                     |      |                                |

|------|-----------------------------------------------------------------------------------|----------------|----------------|---------------------|------|--------------------------------|

| No   | Characteristic                                                                    | Min            | Тур            | Max                 | Unit | Remarks                        |

| 1a   | XY size                                                                           | 26.7 x<br>26.7 | 26.8 x<br>26.8 | 26.9 x<br>26.9      | mm   |                                |

| 1b   | Thickness                                                                         | 1.4            | 1.5            | 1.6                 | mm   |                                |

| 2a   | Spectral range for optical coating of window                                      | 440            | NA             | 1100                | nm   |                                |

| 2b   | Reflection coefficient for window                                                 | NA             | <0.8           | <1.3                | %    | Over bandwidth indicated in 2a |

| 3    | Optical quality: Scratch max width Scratch max number Dig max size Dig max number | N/A            | N/A            | 10<br>5<br>60<br>25 | μm   |                                |

| Envi | ronmental Specification               |     |     |      |                                            |                                                                                                                                   |

|------|---------------------------------------|-----|-----|------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| No   | Characteristic                        | Min | Тур | Max  | Unit                                       | Remarks                                                                                                                           |

| 1    | Operating temperature                 | -40 | NA  | +85  | °C                                         |                                                                                                                                   |

| 2    | Storage temperature                   | -55 | NA  | +125 | °C                                         | Lower storage temperatures (to -80 deg C) have been tested and the device survives but this is not a fully qualified temperature. |

| 3    | Sensor total dose radiation tolerance | N/A | 42  | N/A  | krad<br>(Si)                               | Tested for functionality up to 300krad, 42 krad is guaranteed                                                                     |

| 4    | sensor SEL threshold with ADC enabled | NA  | NA  | >110 | MeV<br>cm <sup>3</sup><br>mg <sup>-1</sup> | Equivalent LET value                                                                                                              |

|    | rical Specification                                        | NA!  | T          | N    | 1111     | Damasila.                                                                      |

|----|------------------------------------------------------------|------|------------|------|----------|--------------------------------------------------------------------------------|

| No | Characteristic                                             | Min  | Тур        | Max  | Unit     | Remarks                                                                        |

| 1  | Total power supply current stand-by                        | 16   | 18.5       | 21   | mA       |                                                                                |

| 2  | Total power supply current, operational                    | 35   | 37         | 40   | mA       | ADC at 5MHz sampling rate Measured                                             |

| 3  | Power supply current to ADC, operational: analog + digital | 17   | 19         | 21   | mA       | ADC at 5MHz sampling rate Measured                                             |

| 4  | Power supply current to image core, operational            | 14   | 15.5       | 17   | mA       |                                                                                |

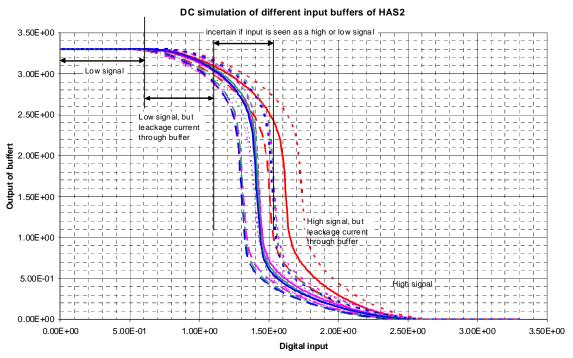

| 5  | Input impedance digital input                              | 3    | NA         | NA   | MΩ       |                                                                                |

| 6  | Input impedance ADC input                                  | 3    | NA         | NA   | MΩ       |                                                                                |

| 7  | Output amplifier voltage range                             | 2.2  | 2.45       | 2.6  | V        |                                                                                |

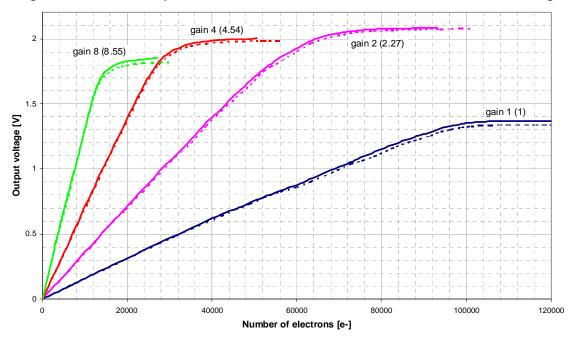

| 8  | Output amplifier gain setting 0                            | NA   | 1          | NA   | -        | Nominal 1 measured reference                                                   |

| 9  | Output amplifier gain setting 1                            | 1.9  | 2.1        | 2.3  | -        | Nominal 2 relative to setting 0                                                |

| 10 | Output amplifier gain setting 2                            | 3.8  | 4.1        | 4.4  | -        | Nominal 4 relative to setting 0                                                |

| 11 | Output amplifier gain setting 3                            | 7.2  | 7.7        | 8.2  | -        | Nominal 8 relative to setting 0                                                |

| 12 | Output amplifier offset setting 0                          | 0.86 | 0.93       | 1.0  | V        | 0 decodes to middle value                                                      |

| 13 | Output amplifier offset setting 31                         | 1.30 | 1.35       | 1.40 | V        |                                                                                |

| 14 | Output amplifier offset setting 32                         | 0.43 | 0.51       | 0.6  | V        |                                                                                |

| 15 | Output amplifier offset setting 63                         | 0.80 | 0.90       | 1.0  | V        |                                                                                |

| 16 | ADC ladder network resistance                              | NA   | 1.8        | NA   | kΩ       | Typical value                                                                  |

| 17 | ADC Differential non linearity                             | NA   | 7          | 11   | lsb      |                                                                                |

| 18 | ADC Integral non linearity                                 | NA   | 8          | 18   | Isb      |                                                                                |

| 19 | ADC set-up time                                            | 5    | NA         | NA   | ns       | Analog_in stable to CLK_ADC rising                                             |

| 20 | ADC hold time                                              | 10   | NA         | NA   | ns       | Analog_in stable after CLK_ADC rising edge                                     |

| 21 | ADC delay time                                             | NA   | NA         | 20   | ns       |                                                                                |

| 22 | ADC latency                                                | NA   | 6.5        | NA   | -        | Cycles of CLK_ADC                                                              |

| 23 | ADC ideal input range                                      | 0.85 | NA         | 2.0  | V        | VLOW_ADC to VHIGH_ADC                                                          |

| 24 | Saturation voltage output swing                            | 1.20 | 1.49       | NA   | V        | VDD_RES=3.3V                                                                   |

| 25 | Output range                                               | 0.8  | NA         | 2.1  | V        | Measured with PGA in unity gain, offset=0.8V, low is dark high is bright.      |

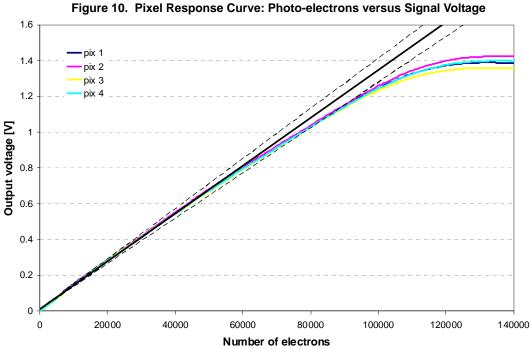

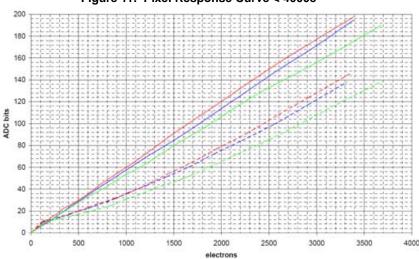

| 26 | Linear range of pixel signal swing                         | 40   | 50<br>0.75 | NA   | ke-<br>V | Measured within ±1%                                                            |

| 27 | Linear range                                               | 60   | 82         | NA   | ke-      | Measured within ±5%                                                            |

| 28 | Full well charge                                           | 90   | 100        | NA   | ke-      | Measured with VDD_RES=3.3V                                                     |

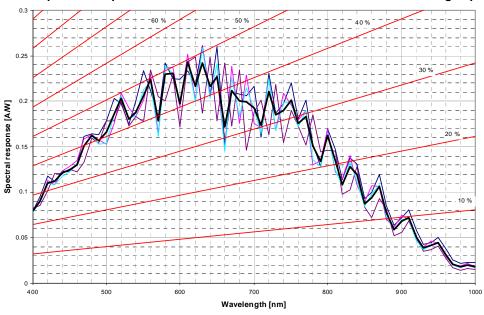

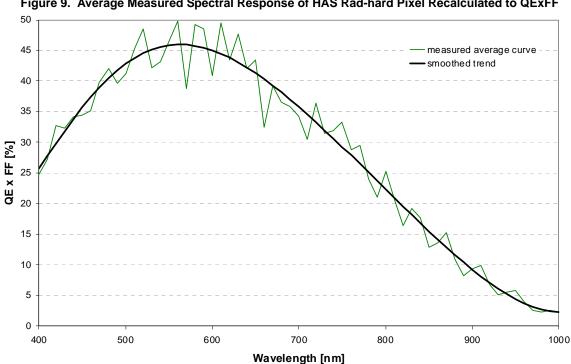

| 29 | Quantum efficiency x Fillfactor                            | NA   | 45         | NA   | %        | Measured between 500 nm and 650 nm. Refer to section 6.3.1 for complete curve. |

| 30 | Spectral response                                          | NA   | 33.3       | NA   | %        | Measured average over 400-900nm.                                               |

Document Number: 001-54123 Rev. \*A

| Elect | rical Specification                                                   |     |      |      |       |                                                                                      |

|-------|-----------------------------------------------------------------------|-----|------|------|-------|--------------------------------------------------------------------------------------|

| No    | Characteristic                                                        | Min | Тур  | Max  | Unit  | Remarks                                                                              |

| 31    | Charge to voltage conversion factor                                   | NA  | 16.9 | NA   | μV/e- | At pixel                                                                             |

| 32    | Charge to voltage conversion factor                                   | 13  | 14.8 | 15.6 | μV/e- | Measured at output SIGNAL_OUT, unity gain                                            |

| 33a   | Temporal noise (Soft Reset)                                           | NA  | 55   | 95   | e-    | Dark noise, with DR/DS, internal ADC                                                 |

| 33b   | Temporal noise (Hard Reset)                                           | N/A | 75   | 125  | e-    | Dark noise, with DR/DS, internal ADC                                                 |

| 33c   | Temporal noise (HTS Reset)                                            | NA  | 65   | 110  | e-    | Dark noise, with DR/DS, internal ADC                                                 |

| 34a   | Temporal noise (NDR Soft reset)                                       | NA  | 75   | 100  | e-    |                                                                                      |

| 34b   | Temporal noise (NDR Hard reset)                                       | NA  | 75   | 100  | e-    |                                                                                      |

| 34c   | Temporal noise (NDR HTS reset)                                        | NA  | 70   | 100  | e-    |                                                                                      |

| 35    | ADC quantization noise                                                | NA  | 7    | NA   | e-    |                                                                                      |

| 36a   | Local fixed pattern noise standard deviation (Hard reset)             | NA  | 110  | 160  | e-    | With DR/DS                                                                           |

| 36b   | Local fixed pattern noise standard deviation (Soft reset)             | NA  | 70   | 140  | e-    | With DR/DS                                                                           |

| 36c   | Local fixed pattern noise standard deviation (HTS reset)              | NA  | 95   | 140  | e-    | With DR/DS                                                                           |

| 37a   | Global fixed pattern noise standard deviation (Hard reset)            | NA  | 115  | 180  | e-    | With DR/DS                                                                           |

| 37b   | Global fixed pattern noise standard deviation (Soft reset)            | NA  | 90   | 140  | e-    | With DR/DS                                                                           |

| 37c   | Global fixed pattern noise standard deviation (HTS reset)             | NA  | 110  | 180  | e-    | With DR/DS                                                                           |

| 37d   | Global fixed pattern noise standard deviation (NDR, Soft reset)       | 14  | 15   | 18   | e-    | With NDR/CDS and external ADC                                                        |

| 37e   | Local Column fixed pattern noise standard deviation (NDR, Soft reset) | 14  | 15   | 18   | e-    | With NDR/CDS and external ADC                                                        |

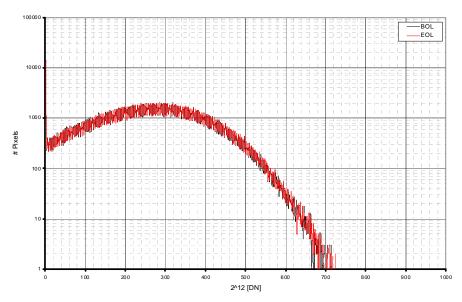

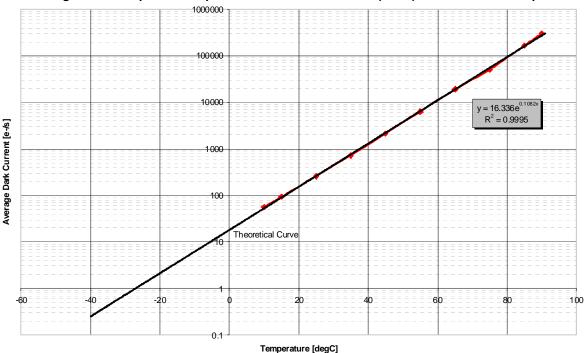

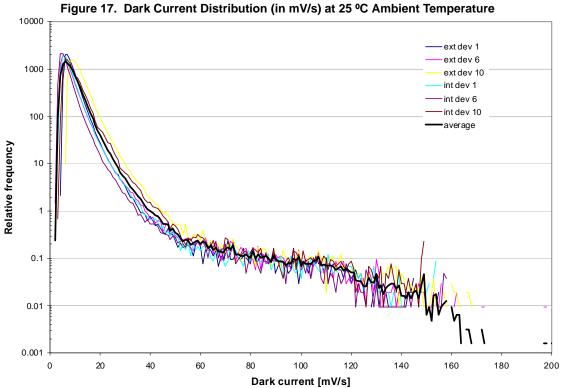

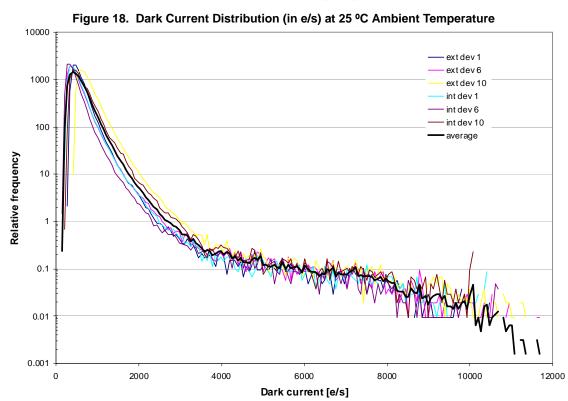

| 38    | Average dark signal                                                   | NA  | 190  | 400  | e-/s  | At 25 ± 2 °C die temp, BOL<br>see "Dark Current vs Temper<br>ature Model" on page 33 |

| 39    | Average dark signal                                                   | NA  | 5550 | 8730 | e-/s  | At 25 ± 2 °C die temp, EOL (25 krad)                                                 |

| 40    | Dark signal temperature dependency                                    | 5   | 5.8  | 8    | °C    | Sensor temperature increase for doubled average dark current.                        |

| 41    | Local dark signal non uniformity standard deviation                   | NA  | 260  | 400  | e-/s  | At 25 ± 2 °C die temp, BOL<br>96% of BOL average                                     |

| 42    | Global dark signal non uniformity standard deviation                  | N/A | 275  | 500  | e-/s  | At 25 ± 2 °C die temp, BOL<br>96% of BOL average                                     |

| 43    | Local photo response non uniformity, standard deviation               | NA  | 0.8  | 1.0  | %     | Of average response                                                                  |

| 44    | Global photo response non uniformity, standard deviation              | NA  | 1.8  | 5    | %     | Of average response                                                                  |

| 45    | MTF X direction                                                       | NA  | 0.35 | NA   | NA    | At Nyquist measured                                                                  |

| 46    | MTF Y direction                                                       | NA  | 0.35 | NA   | -     | At Nyquist measured                                                                  |

Document Number: 001-54123 Rev. \*A

| Elect | rical Specification                                          |     |       |      |       |                                                         |

|-------|--------------------------------------------------------------|-----|-------|------|-------|---------------------------------------------------------|

| No    | Characteristic                                               | Min | Тур   | Max  | Unit  | Remarks                                                 |

| 47    | Pixel to pixel crosstalk X direction                         | NA  | 9.8   | NA   | %     | Of total source signal – see section 6.3.6 for 2-D plot |

| 48    | Pixel to pixel crosstalk Y direction                         | NA  | 9.8   | NA   | %     | Of total Source signal – see section 6.3.6 for 2-D plot |

| 49    | Anti-blooming capability                                     | 200 | 1000  | NA   |       | Typical                                                 |

| 50    | Pixel rate                                                   | NA  | 5     | 10   | MHz   |                                                         |

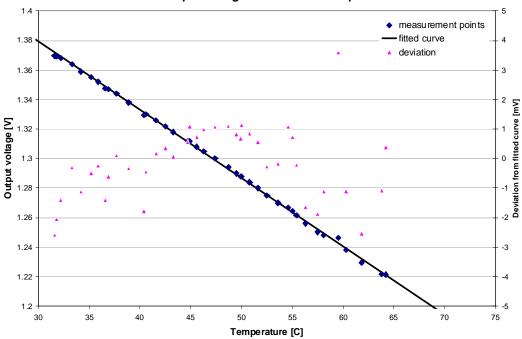

| 51    | Temperature sensor transfer curve                            | NA  | -4.64 | NA   | mV/°C | BOL                                                     |

| 52    | Temperature sensor output signal range, Min to Max (typical) | 800 | NA    | 1700 | mV    | BOL                                                     |

| 53    | Temperature sensor linearity                                 | NA  | 3     | NA   | mV    | BOL                                                     |

| 54    | Temperature sensor transfer curve                            | NA  | -4.64 | NA   | mV/°C | EOL                                                     |

| 55    | Temperature sensor output signal range, Min to Max (typical) | 800 | NA    | 1700 | NA    | EOL                                                     |

| 56a   | Image lag (Soft reset)                                       | NA  | 0.54  | NA   | -     | Soft reset                                              |

| 56b   | Image lag (Hard reset)                                       | NA  | -0.2  | NA   | -     | Hard reset                                              |

| 56c   | Image lag (HTS reset)                                        | NA  | -0.15 | NA   | -     | HTS reset                                               |

Table 4. Electrical and Electro-optical Measurements at Room Temperature

| No. | rical and Electro-optical Measurements  Characteristic    | Min  | Тур  | Max  | Unit | Remarks                                                     |

|-----|-----------------------------------------------------------|------|------|------|------|-------------------------------------------------------------|

| 1 1 | Total power supply current stand-by                       | 16   | 18.5 | 21   | mA   | Remarks                                                     |

| 2   | Total power supply current, operational                   | 35   | 37   | 40   | mA   | ADC at 5MHz sampling rate                                   |

| 3   | Power supply current to ADC, opera-                       | 17   | 19   | 21   | mA   | ADC at 5MHz sampling rate                                   |

| 3   | tional                                                    | 17   | 19   | 21   | MA   | ADC at SWIHZ Sampling rate                                  |

| 4   | Power supply current to image core, operational           | 14   | 15.5 | 17   | mA   |                                                             |

| 5   | Input impedance digital input                             | 3    | NA   | NA   | MΩ   |                                                             |

| 6   | Input impedance ADC input                                 | 3    | NA   | NA   | MΩ   |                                                             |

| 7   | Output impedance digital outputs                          | NA   | NA   | 400  | W    |                                                             |

| 8   | Output impedance analogue output                          | NA   | NA   | 1    | kΩ   |                                                             |

| 9   | Output amplifier voltage range                            | 2.2  | 2.45 | 2.6  | V    |                                                             |

| 10  | Output amplifier gain setting 0                           | NA   | 1    | NA   | -    | Nominal 1 measured reference                                |

| 11  | Output amplifier gain setting 1                           | 1.9  | 2.1  | 2.3  | -    | Nominal 2 relative to setting 0                             |

| 12  | Output amplifier gain setting 2                           | 3.8  | 4.1  | 4.4  | -    | Nominal 4 relative to setting 0                             |

| 13  | Output amplifier gain setting 3                           | 7.2  | 7.7  | 8.2  | -    | Nominal 8 relative to setting 0                             |

| 14  | Output amplifier offset setting 0                         | 0.86 | 0.93 | 1.0  | V    | 0 decodes to middle value                                   |

| 15  | Output amplifier offset setting 31                        | 1.30 | 1.35 | 1.40 | V    |                                                             |

| 16  | Output amplifier offset setting 32                        | 0.43 | 0.51 | 0.6  | V    |                                                             |

| 17  | Output amplifier offset setting 63                        | 0.80 | 0.90 | 1.0  | V    |                                                             |

| 18  | ADC Differential non linearity                            | N/A  | 7    | 11   | lsb  |                                                             |

| 19  | ADC Integral non linearity                                | N/A  | 8    | 18   | lsb  |                                                             |

| 20  | Saturation voltage output swing                           | 1.20 | 1.49 | NA   | V    | VDD_RES=3.3V                                                |

| 21  | Output range                                              | 0.8  | NA   | 2.1  | V    | PGA in unity gain, offset=0.8\ low is dark, high is bright. |

| 22a | Temporal noise (Soft reset)                               | NA   | 55   | 95   | e-   | Dark noise, with DR/DS, internal ADC                        |

| 22b | Temporal noise (Hard reset)                               | NA   | 75   | 125  | e-   | Dark noise, with DR/DS, internal ADC                        |

| 22c | Temporal noise (HTS reset)                                | NA   | 65   | 110  | e-   | Dark noise, with DR/DS, internal ADC                        |

| 23a | Temporal noise (NDR Soft reset)                           | NA   | 75   | 100  | e-   |                                                             |

| 23b | Temporal noise (NDR Hard reset)                           | NA   | 75   | 100  | e-   |                                                             |

| 23c | Temporal noise (NDR HTS reset)                            | NA   | 70   | 100  | e-   |                                                             |

| 24  | ADC quantization noise                                    | NA   | 7    | NA   | e-   |                                                             |

| 25a | Local fixed pattern noise standard deviation (Soft reset) | N/A  | 70   | 140  | e-   | With DR/DS                                                  |

| 25b | Local fixed pattern noise standard deviation (Hard reset) | NA   | 110  | 160  | e-   | With DR/DS                                                  |

| 25c | Local fixed pattern noise standard deviation (HTS reset)  | NA   | 95   | 140  | e-   | With DR/DS                                                  |

Document Number: 001-54123 Rev. \*A Page 14 of 71

| Elect | rical and Electro-optical Measurements                     | at Room | Temperat | ure 22°C |      |                       |

|-------|------------------------------------------------------------|---------|----------|----------|------|-----------------------|

| No.   | Characteristic                                             | Min     | Тур      | Max      | Unit | Remarks               |

| 26a   | Global fixed pattern noise standard deviation (Soft reset) | NA      | 90       | 140      | e-   | With DR/DS            |

| 26b   | Global fixed pattern noise standard deviation (Hard reset) | NA      | 115      | 180      | e-   | With DR/DS            |

| 26c   | Global fixed pattern noise standard deviation (HTS reset)  | NA      | 110      | 180      | e-   | With DR/DS            |

| 27    | Average dark signal                                        | NA      | 190      | 400      | e-/s | At 25 ± 2 °C die temp |

| 28    | Local dark signal non uniformity standard deviation        | NA      | 260      | 400      | e-/s | At 25 ± 2 °C          |

| 29    | Global dark signal non uniformity standard deviation       | NA      | 275      | 500      | e-/s | At 25 ± 2 °C          |

| 30    | Local photo response non uniformity, standard deviation    | NA      | 0.8      | 1.0      | %    | Of average response   |

| 31    | Global photo response non uniformity, standard deviation   | NA      | 1.8      | 5        | %    | Of average response   |

| 32a   | Image lag (Soft reset)                                     | NA      | 0.54     | NA       | -    |                       |

| 32b   | Image lag (Hard reset)                                     | NA      | -0.2     | NA       | -    |                       |

| 32c   | Image lag (HTS reset)                                      | NA      | -0.15    | NA       | -    |                       |

Table 5. Electrical and Electro-optical measurements at High Temperature

| Elect | Electrical and Electro-optical Measurements at High Temperature +85°C |      |      |      |      |                                 |  |  |  |  |

|-------|-----------------------------------------------------------------------|------|------|------|------|---------------------------------|--|--|--|--|

| No    | Characteristic                                                        | Min  | Тур  | Max  | Unit | Remarks                         |  |  |  |  |

| 1     | Total power supply current stand-by                                   | 17   | 20   | 23   | mA   |                                 |  |  |  |  |

| 2     | Total power supply current, operational                               | 35   | 38   | 41   | mA   | ADC at 5MHz sampling rate       |  |  |  |  |

| 3     | Power supply current to ADC, operational                              | 17   | 19   | 21   | mA   | ADC at 5MHz sampling rate       |  |  |  |  |

| 4     | Power supply current to image core, operational                       | 14   | 15.5 | 17   | mA   |                                 |  |  |  |  |

| 5     | Input impedance digital input                                         | 3    | NA   | NA   | MΩ   |                                 |  |  |  |  |

| 6     | Input impedance ADC input                                             | 3    | NA   | NA   | MΩ   |                                 |  |  |  |  |

| 7     | Output impedance digital outputs                                      | NA   | NA   | 400  | W    |                                 |  |  |  |  |

| 8     | Output impedance analogue output                                      | NA   | NA   | 1    | kΩ   |                                 |  |  |  |  |

| 9     | Output amplifier voltage range                                        | 2.2  | 2.45 | 2.6  | V    |                                 |  |  |  |  |

| 10    | Output amplifier gain setting 0                                       | NA   | 1    | NA   | -    | Nominal 1 measured reference    |  |  |  |  |

| 11    | Output amplifier gain setting 1                                       | 1.9  | 2.1  | 2.3  | -    | Nominal 2 relative to setting 0 |  |  |  |  |

| 12    | Output amplifier gain setting 2                                       | 3.7  | 4.0  | 4.3  | -    | Nominal 4 relative to setting 0 |  |  |  |  |

| 13    | Output amplifier gain setting 3                                       | 7.0  | 7.5  | 8.0  | -    | Nominal 8 relative to setting 0 |  |  |  |  |

| 14    | Output amplifier offset setting 0                                     | 0.89 | 0.94 | 1.0  | V    | 0 decodes to middle value       |  |  |  |  |

| 15    | Output amplifier offset setting 31                                    | 1.30 | 1.36 | 1.42 | V    |                                 |  |  |  |  |

| 16    | Output amplifier offset setting 32                                    | 0.43 | 0.53 | 0.63 | V    |                                 |  |  |  |  |

| 17    | Output amplifier offset setting 63                                    | 0.83 | 0.93 | 1.03 | V    |                                 |  |  |  |  |

| 18    | ADC Differential non linearity                                        | NA   | 8    | 11   | lsb  |                                 |  |  |  |  |

| 19    | ADC Integral non linearity                                            | NA   | 10   | 18   | lsb  |                                 |  |  |  |  |

Document Number: 001-54123 Rev. \*A Page 15 of 71

| Elect | rical and Electro-optical Measurements                     | at High | Temperatu | re +85°C |      |                                                              |

|-------|------------------------------------------------------------|---------|-----------|----------|------|--------------------------------------------------------------|

| No    | Characteristic                                             | Min     | Тур       | Max      | Unit | Remarks                                                      |

| 20    | Saturation voltage output swing                            | 1.20    | 1.52      | NA       | V    | VDD_RES=3.3V                                                 |

| 21    | Output range                                               | 0.8     | NA        | 2.1      | V    | PGA in unity gain, offset=0.8V, low is dark, high is bright. |

| 22a   | Temporal noise (Soft reset)                                | NA      | 66        | 110      | e-   | DR/DS                                                        |

| 22b   | Temporal noise (Hard reset)                                | NA      | 85        | 125      | e-   | DR/DS                                                        |

| 22c   | Temporal noise (HTS reset)                                 | NA      | 73        | 110      | e-   | DR/DS                                                        |

| 23a   | Temporal noise (NDR Soft reset)                            | NA      | 200       | 400      | e-   |                                                              |

| 23b   | Temporal noise (NDR Hard reset)                            | NA      | 170       | 300      | e-   |                                                              |

| 23c   | Temporal noise (NDR HTS reset)                             | NA      | 65        | 125      | e-   |                                                              |

| 24    | ADC quantization noise                                     | NA      | 7         | NA       | e-   |                                                              |

| 25a   | Local fixed pattern noise standard deviation (Soft reset)  | NA      | 82        | 160      | e-   | With DR/DS                                                   |

| 25b   | Local fixed pattern noise standard deviation (Hard reset)  | NA      | 95        | 160      | e-   | With DR/DS                                                   |

| 25c   | Local fixed pattern noise standard deviation (HTS reset)   | NA      | 100       | 160      | e-   | With DR/DS                                                   |

| 26a   | Global fixed pattern noise standard deviation (Soft reset) | NA      | 80        | 140      | e-   | With DR/DS                                                   |

| 26b   | Global fixed pattern noise standard deviation (Hard reset) | NA      | 97        | 160      | e-   | With DR/DS                                                   |

| 26c   | Global fixed pattern noise standard deviation (HTS reset)  | NA      | 115       | 300      | e-   | With DR/DS                                                   |

| 27    | Average dark signal                                        | NA      | 41000     | 60000    | e-/s | At +85 ± 2 °C die temp                                       |

| 28    | Local dark signal non uniformity standard deviation        | NA      | 2800      | 4000     | e-/s |                                                              |

| 29    | Global dark signal non uniformity standard deviation       | NA      | 3100      | 4500     | e-/s |                                                              |

| 30    | Local photo response non uniformity, standard deviation    | NA      | 0.74      | 1.0      | %    | Of average response                                          |

| 31    | Global photo response non uniformity, standard deviation   | NA      | 1.7       | 5        | %    | Of average response                                          |

| 32a   | Image lag (Soft reset)                                     | NA      | -0.13     | NA       | -    | Soft reset                                                   |

| 32b   | Image lag (Hard reset)                                     | NA      | -0.09     | NA       | -    | Hard reset                                                   |

| 32c   | Image lag (HTS reset)                                      | NA      | -0.12     | NA       | -    | HTS reset                                                    |

Table 6. Electrical and Electro-optical measurements at Low Temperature

| Elect | Electrical and Electro-optical Measurements at Low Temperature -40°C |     |      |     |      |                           |  |  |  |  |

|-------|----------------------------------------------------------------------|-----|------|-----|------|---------------------------|--|--|--|--|

| No    | Characteristic                                                       | Min | Тур  | Max | Unit | Remarks                   |  |  |  |  |

| 1     | Total power supply current stand-by                                  | 16  | 18   | 21  | mA   |                           |  |  |  |  |

| 2     | Total power supply current, operational                              | 35  | 37   | 40  | mA   | ADC at 5MHz sampling rate |  |  |  |  |

| 3     | Power supply current to ADC, operational                             | 17  | 19   | 21  | mA   | ADC at 5MHz sampling rate |  |  |  |  |

| 4     | Power supply current to image core, operational                      | 14  | 15.5 | 17  | mA   |                           |  |  |  |  |

| 5     | Input impedance digital input                                        | 3   | NA   | NA  | MΩ   |                           |  |  |  |  |

| 6     | Input impedance ADC input                                            | 3   | NA   | NA  | MΩ   |                           |  |  |  |  |

| 7     | Output impedance digital outputs                                     | NA  | NA   | 400 | W    |                           |  |  |  |  |

Document Number: 001-54123 Rev. \*A Page 16 of 71

| No  | trical and Electro-optical Measurements  Characteristic    |           |            |      | l lmit  | Domorko                                                     |

|-----|------------------------------------------------------------|-----------|------------|------|---------|-------------------------------------------------------------|

|     |                                                            | Min       | Typ        | Max  | Unit    | Remarks                                                     |

| 8   | Output impedance analogue output                           | NA<br>2.2 | NA<br>2.45 | 1    | kΩ<br>V |                                                             |

| 9   | Output amplifier voltage range                             | 2.2       |            | 2.6  |         | Name in al. 4                                               |

| 10  | Output amplifier gain setting 0                            | NA        | 1          | NA   | -       | Nominal 1 measured reference                                |

| 11  | Output amplifier gain setting 1                            | 1.9       | 2.1        | 2.3  | -       | Nominal 2 relative to setting 0                             |

| 12  | Output amplifier gain setting 2                            | 3.8       | 4.1        | 4.4  | -       | Nominal 4 relative to setting 0                             |

| 13  | Output amplifier gain setting 3                            | 7.2       | 7.7        | 8.2  | -       | Nominal 8 relative to setting 0                             |

| 14  | Output amplifier offset setting 0                          | 0.86      | 0.93       | 1.0  | V       | 0 decodes to middle value                                   |

| 15  | Output amplifier offset setting 31                         | 1.30      | 1.35       | 1.40 | V       |                                                             |

| 16  | Output amplifier offset setting 32                         | 0.43      | 0.51       | 0.6  | V       |                                                             |

| 17  | Output amplifier offset setting 63                         | 0.80      | 0.90       | 1.0  | V       |                                                             |

| 18  | ADC Differential non linearity                             | N/A       | 7          | 11   | lsb     |                                                             |

| 19  | ADC Integral non linearity                                 | N/A       | 11         | 18   | Isb     |                                                             |

| 20  | Saturation voltage output swing                            | 1.20      | 1.49       | NA   | V       | VDD_RES=3.3V                                                |

| 21  | Output range                                               | 0.8       | NA         | 2.1  | V       | PGA in unity gain, offset=0.8V low is dark, high is bright. |

| 22a | Temporal noise (Soft reset)                                | NA        | 59         | 100  | e-      | DR/DS                                                       |

| 22b | Temporal noise (Hard reset)                                | NA        | 77         | 125  | e-      | DR/DS                                                       |

| 22c | Temporal noise (HTS reset)                                 | NA        | 70         | 125  | e-      | DR/DS                                                       |

| 23a | Temporal noise (NDR Soft reset)                            | NA        | 80         | 125  | e-      |                                                             |

| 23b | Temporal noise (NDR Hard reset)                            | NA        | 80         | 125  | e-      |                                                             |

| 23c | Temporal noise (NDR HTS reset)                             | NA        | 75         | 125  | e-      |                                                             |

| 24  | ADC quantization noise                                     | NA        | 7          | NA   | e-      |                                                             |

| 25a | Local fixed pattern noise standard deviation (Soft reset)  | NA        | 70         | 140  | e-      | With DR/DS                                                  |

| 25b | Local fixed pattern noise standard deviation (Hard reset)  | NA        | 90         | 140  | e-      | With DR/DS                                                  |

| 25c | Local fixed pattern noise standard deviation (HTS reset)   | NA        | 100        | 160  | e-      | With DR/DS                                                  |

| 26a | Global fixed pattern noise standard deviation (Soft reset) | NA        | 70         | 140  | e-      | With DR/DS                                                  |

| 26b | Global fixed pattern noise standard deviation (Hard reset) | NA        | 95         | 140  | e-      | With DR/DS                                                  |

| 26c | Global fixed pattern noise standard deviation (HTS reset)  | NA        | 120        | 180  | e-      | With DR/DS                                                  |

| 27  | Average dark signal                                        | NA        | 3.3        | 10   | e-/s    |                                                             |

| 28  | Local dark signal non uniformity standard deviation        | NA        | 6          | 20   | e-/s    |                                                             |

| 29  | Global dark signal non uniformity standard deviation       | NA        | 8          | 30   | e-/s    |                                                             |

| 30  | Local photo response non uniformity, standard deviation    | NA        | 0.8        | 1.0  | %       | Of average response measured                                |

| 31  | Global photo response non uniformity, standard deviation   | NA        | 1.8        | 5    | %       | Of average response measured                                |

Document Number: 001-54123 Rev. \*A

| Elect | Electrical and Electro-optical Measurements at Low Temperature -40°C |     |      |     |      |            |  |  |

|-------|----------------------------------------------------------------------|-----|------|-----|------|------------|--|--|

| No    | Characteristic                                                       | Min | Тур  | Max | Unit | Remarks    |  |  |

| 32a   | Image lag                                                            | NA  | 0.6  | NA  | -    | Soft reset |  |  |

| 32b   | Image lag                                                            | NA  | 0.2  | NA  | -    | Hard reset |  |  |

| 32c   | Image lag                                                            | NA  | -1.2 | NA  | -    | HTS reset  |  |  |

Table 7. Parameter Drift Values for Burn In

| Elec | trical and Electro-optical Measurements                   | at Room Tempera | ture +22°C |      |                                                              |

|------|-----------------------------------------------------------|-----------------|------------|------|--------------------------------------------------------------|

| No   | Characteristic                                            | Typical Value   | Max Drift  | Unit | Remarks                                                      |

| 1    | Total power supply current stand-by                       | 18.5            | 2          | mA   |                                                              |

| 2    | Total power supply current, operational                   | 37              | 3          | mA   | ADC at 5MHz sampling rate                                    |

| 3    | Power supply current to ADC, operational                  | 19              | 2          | mA   | ADC at 5MHz sampling rate                                    |

| 4    | Power supply current to image core, operational           | 15.5            | 2          | mA   |                                                              |

| 5    | Output impedance digital outputs                          | NA              | 20         | W    |                                                              |

| 6    | Output impedance analogue output                          | NA              | 20         | W    |                                                              |

| 7    | Output amplifier voltage range                            | 2.45            | 0.3        | V    |                                                              |

| 8    | Output amplifier gain setting 0                           | 1               | N/A        | -    | Nominal 1<br>measured reference                              |

| 9    | Output amplifier gain setting 1                           | 2.1             | 0.2        | -    | Nominal 2 relative to setting 0                              |

| 10   | Output amplifier gain setting 2                           | 4.1             | 0.4        | -    | Nominal 4 relative to setting 0                              |

| 11   | Output amplifier gain setting 3                           | 7.7             | 0.6        | -    | Nominal 8 relative to setting 0                              |

| 12   | Output amplifier offset setting 0                         | 0.93            | 0.1        | V    | 0 decodes to middle value                                    |