## **THS8200-EP**

# All-Format Oversampled Component Video/PC Graphics D/A System With Three 11-Bit DACs, CGMS Data Insertion

## **Data Manual**

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Literature Number: SLES253

December 2009

www.ti.com

## **Contents**

| 1 | intro |                                                     |                    |                                                                               | _  |  |  |  |

|---|-------|-----------------------------------------------------|--------------------|-------------------------------------------------------------------------------|----|--|--|--|

|   | 1.1   |                                                     |                    |                                                                               |    |  |  |  |

| 2 | Overv |                                                     |                    |                                                                               |    |  |  |  |

|   | 2.1   | =                                                   |                    |                                                                               |    |  |  |  |

|   | 2.2   |                                                     | •                  | on                                                                            |    |  |  |  |

|   | 2.3   |                                                     |                    | ATION                                                                         |    |  |  |  |

| 3 |       |                                                     |                    | verview                                                                       |    |  |  |  |

|   | 3.1   |                                                     |                    | (AN)                                                                          |    |  |  |  |

|   |       | 3.1.1                                               |                    | ng Finite Impulse Responses Filter (IFIR)                                     |    |  |  |  |

|   |       | 3.1.2                                               |                    | ce Conversion (CSC)                                                           |    |  |  |  |

|   |       | 3.1.3                                               | -                  | Multiplier (CSM)                                                              |    |  |  |  |

|   |       | 3.1.4                                               |                    | ltiplexer (DIGMUX)                                                            |    |  |  |  |

|   |       | 3.1.5                                               |                    | ming Generator (DTG)                                                          |    |  |  |  |

|   |       | 3.1.6                                               |                    | nerator (CGEN)                                                                |    |  |  |  |

|   |       | 3.1.7                                               |                    | ver (CDRV)                                                                    |    |  |  |  |

|   |       | 3.1.8                                               |                    | nterface (I2CSLAVE)                                                           |    |  |  |  |

|   |       | 3.1.9                                               |                    | (TST)                                                                         |    |  |  |  |

|   |       | 3.1.10                                              |                    | erters (DAC)                                                                  |    |  |  |  |

| 4 |       |                                                     |                    | escription                                                                    |    |  |  |  |

|   | 4.1   |                                                     |                    | AN)                                                                           |    |  |  |  |

|   | 4.2   | •                                                   |                    | mats                                                                          |    |  |  |  |

|   | 4.3   |                                                     | -                  | CGEN)/Clock Driver (CDRV)                                                     |    |  |  |  |

|   | 4.4   |                                                     |                    | ersion (CSC)                                                                  |    |  |  |  |

|   | 4.5   |                                                     |                    | r (CSM)                                                                       |    |  |  |  |

|   |       | 4.5.1                                               |                    |                                                                               |    |  |  |  |

|   |       | 4.5.2                                               | _                  |                                                                               |    |  |  |  |

|   |       | 4.5.3                                               |                    | J                                                                             |    |  |  |  |

|   | 4.6   | Interpolating Finite Impulse Response Filter (IFIR) |                    |                                                                               |    |  |  |  |

|   | 4.7   |                                                     | _                  | nerator (DTG)                                                                 |    |  |  |  |

|   |       | 4.7.1                                               |                    | of Functionality                                                              |    |  |  |  |

|   |       | 4.7.2                                               | 4.7.2.1            | Description                                                                   |    |  |  |  |

|   |       |                                                     |                    | Predefined DTG Video Formats (Presets)                                        |    |  |  |  |

|   |       |                                                     |                    | Internal Synchronization                                                      |    |  |  |  |

|   |       |                                                     | 4.7.2.3            | Output Synchronization: Composite Sync                                        |    |  |  |  |

|   |       | 4.7.3                                               | 4.7.2.4            | Output Synchronization: Hsync/Vsync Outputs                                   | _  |  |  |  |

|   |       | 4.7.3                                               |                    | HDTV Mode                                                                     |    |  |  |  |

|   |       |                                                     | 4.7.3.1            | Active Video                                                                  |    |  |  |  |

|   |       |                                                     | 4.7.3.2            |                                                                               |    |  |  |  |

|   |       |                                                     | 4.7.3.3            | FULL NTSP (Full Normal Tri-Level Sync Pulse)                                  |    |  |  |  |

|   |       |                                                     | 4.7.3.4<br>4.7.3.5 | NTSP NTSP (Normal Tri-Level Sync Pulse/Normal Tri-Level Sync Pulse)           |    |  |  |  |

|   |       |                                                     | 4.7.3.6            | NTSP BTSP (Normal Tri-Level Sync Pulse/ Broad Pulse and Tri-Level Sync Pulse) | _  |  |  |  |

|   |       |                                                     | 4.7.3.7            | BTSP NTSP (Broad Pulse and Tri-Level Sync Pulse/Normal Tri-Level Sync Pulse)  |    |  |  |  |

|   |       |                                                     | 4.7.3.7            | Full BTSP (Full Broad Pulse and Tri-Level Sync Pulse)                         |    |  |  |  |

|   |       |                                                     | 4.7.3.8            | ruii DTOF (ruii DIOau Puise anu TII-Levei Sync Puise)                         | 43 |  |  |  |

www.ti.com SLES253-DECEMBER 2009

|   |      |         | 4.7.3.9                    | SDTV Mode                                                             | . 45        |

|---|------|---------|----------------------------|-----------------------------------------------------------------------|-------------|

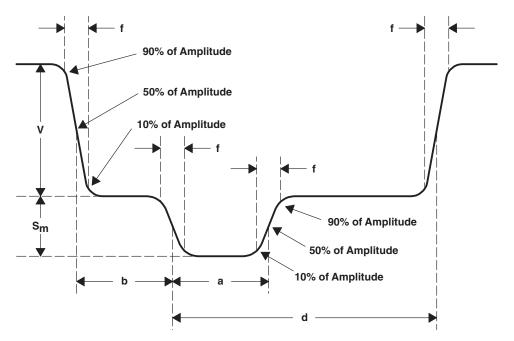

|   |      |         | 4.7.3.10                   | NEQ_NEQ (Negative Equalization Pulse/Negative Equalization Pulse)     | . 47        |

|   |      |         | 4.7.3.11                   | FULL_BSP (Full Broad Sync Pulse)                                      | . 47        |

|   |      |         | 4.7.3.12                   | BSP_BSP (Broad Sync Pulse/Broad Sync Pulse)                           | . <u>48</u> |

|   |      |         | 4.7.3.13                   | FULL_NSP (Full Normal Sync Pulse)                                     | . <u>48</u> |

|   |      |         | 4.7.3.14                   | NEQ_BSP (Negative Equalization Pulse/Broad Sync Pulse)                | . <u>49</u> |

|   |      |         | 4.7.3.15                   | BSP_NEQ (Broad Sync Pulse/Negative Equalization Pulse)                | <u>49</u>   |

|   |      |         | 4.7.3.16                   | FULL_NEQ (Full Negative Equalization Pulse)                           | . <u>50</u> |

|   |      |         | 4.7.3.17                   | NSP_ACTIVE (Normal Sync Pulse/Active Video)                           | . <u>50</u> |

|   |      |         | 4.7.3.18                   | ACTIVE_NEQ (Active Video/Negative Equalization Pulse)                 | . <u>51</u> |

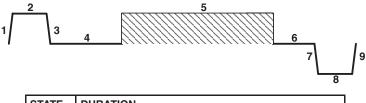

|   |      |         | 4.7.3.19                   | ACTIVE VIDEO                                                          | . <u>51</u> |

|   | 4.8  | D/A Co  | nversion                   |                                                                       | . 53        |

|   |      | 4.8.1   | RGB Out                    | put Without Sync Signal Insertion/General-Purpose Application DAC     | . <u>54</u> |

|   |      | 4.8.2   | SMPTE-0                    | Compatible RGB Output With Sync Signal Inserted on G (Green) Channel  | . <u>55</u> |

|   |      | 4.8.3   | SMPTE-0                    | Compatible Analog-Level Output With Sync Inserted on All RGB Channels | . <u>56</u> |

|   |      | 4.8.4   | SMPTE-0                    | Compatible YPbPr Output With Sync Signal Inserted on Y Channel Only   | . <u>57</u> |

|   |      | 4.8.5   | SMPTE-0                    | Compatible YPbPr Output With Sync Signal Inserted on All Channels     | <u>. 58</u> |

|   |      | 4.8.6   | Summary                    | of Supported Video Formats                                            | . <u>59</u> |

|   | 4.9  | Test Fu | unctions                   |                                                                       | . <u>59</u> |

|   | 4.10 | Power   | Down                       |                                                                       | . <u>59</u> |

|   | 4.11 | CGMS    | Insertion                  |                                                                       | . <u>59</u> |

|   | 4.12 |         |                            |                                                                       | _           |

| 5 |      | _       | -                          |                                                                       |             |

|   | 5.1  | -       | -                          | ons                                                                   |             |

|   |      | 5.1.1   | -                          | Control (Sub-Addresses 0x02-0x03)                                     |             |

|   |      | 5.1.2   | =                          | ace Conversion Control (Sub-Addresses 0x04-0x19)                      |             |

|   |      | 5.1.3   |                            | trol (Sub-Addresses 0x1A-0x1B)                                        |             |

|   |      | 5.1.4   |                            | h Control (Sub-Address 0x1C)                                          |             |

|   |      | 5.1.5   |                            | iming Generator Control, Part 1 (Sub-Addresses 0x1D-0x3C)             |             |

|   |      | 5.1.6   |                            | ntrol (Sub-Addresses 0x3D-0x40)                                       |             |

|   |      | 5.1.7   |                            | e/Multiplier Control (Sub-Addresses 0x41-0x4F)                        |             |

|   |      | 5.1.8   |                            | iming Generator Control, Part 2 (Sub-Addresses 0x50-0x82)             |             |

|   |      | 5.1.9   |                            | ontrol (Sub-Addresses 0x83-0x85)                                      |             |

|   | 5.2  |         |                            | Mode Line Type Definitions                                            |             |

|   |      | 5.2.1   |                            | 274P (1080P)                                                          |             |

|   |      | 5.2.2   |                            | erlaced (1080l)                                                       |             |

|   |      | 5.2.3   |                            | ogressive (720P)                                                      |             |

|   |      | 5.2.4   |                            | 5 Interlaced Mode                                                     |             |

|   |      | 5.2.5   |                            | 5 Progressive Mode                                                    |             |

| _ | A I  | 5.2.6   |                            | 5 Interlaced Mode                                                     |             |

| 6 |      |         |                            | on                                                                    |             |

|   | 6.1  |         | =                          | er Graphics Application                                               |             |

|   | 6.2  |         |                            | oPr/RGB Application                                                   | _           |

| 7 | 6.3  |         |                            | iming Modes tics                                                      | _           |

| • | 7.1  |         |                            | n Ratings                                                             |             |

|   | 7.1  | MUSUIU  | ı <del>c</del> ıvıaxıllıdl | n Naurige                                                             | . 00        |

SLES253-DECEMBER 2009 www.ti.com

| 7.2                    | Recomm                                                    | mended Operating Conditions                                                                  | 88        |  |  |  |  |  |  |  |

|------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

| 7.3                    | ELECTRICAL CHARACTERISTICS89                              |                                                                                              |           |  |  |  |  |  |  |  |

| 7.4 Power Requirements |                                                           |                                                                                              |           |  |  |  |  |  |  |  |

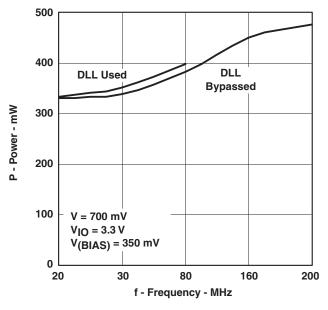

|                        | 7.4.1                                                     | Power for 700-mV DAC Output Compliance + 350-mV Bias at AVDD = 3.3 V,                        |           |  |  |  |  |  |  |  |

|                        |                                                           | DVDD = 1.8 V, VDD_IO = 3.3 V, VDD_DLL = 3.3 V, 1-MHz Tone on All Channels                    | <u>91</u> |  |  |  |  |  |  |  |

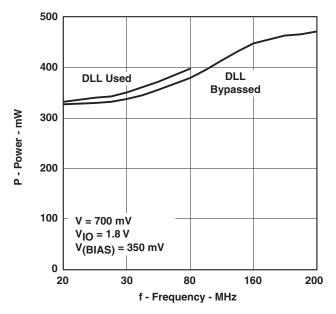

|                        | 7.4.2                                                     | Power for 700-mV DAC Output Compliance + 350-mV Bias at AVDD = 3.3 V,                        |           |  |  |  |  |  |  |  |

|                        |                                                           | DVDD = 1.8 V, VDD_IO = 1.8 V, VDD_DLL = 3.3 V, 1-MHz Tone on All Channels                    | <u>91</u> |  |  |  |  |  |  |  |

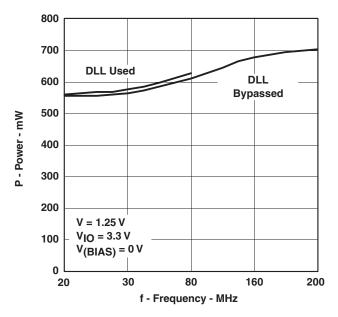

|                        | 7.4.3                                                     | Power for 1.25-V Output Compliance Without Bias at AVDD = 3.3 V,                             |           |  |  |  |  |  |  |  |

|                        |                                                           | DVDD = 1.8 V, VDD_IO = 3.3 V, VDD_DLL = 3.3 V, 1-MHz Tone on All Channels                    | 92        |  |  |  |  |  |  |  |

|                        | 7.4.4                                                     | Power for 1.25-V Output Compliance Without Bias at AVDD = 3.3 V,                             |           |  |  |  |  |  |  |  |

|                        |                                                           | DVDD = 1.8 V, VDD_IO = 1.8 V, VDD_DLL = 3.3 V, 1-MHz Tone on All Channels                    |           |  |  |  |  |  |  |  |

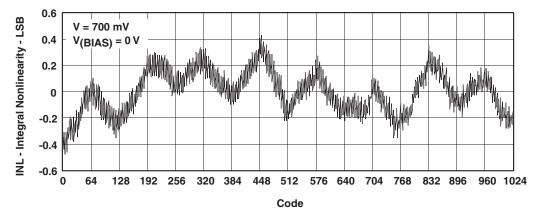

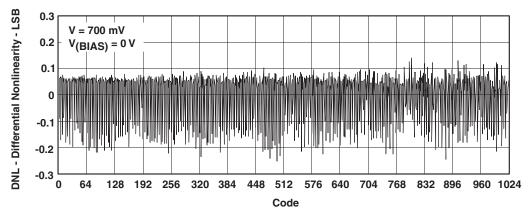

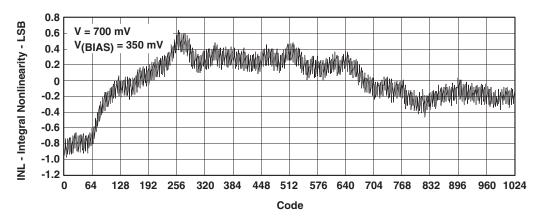

| 7.5                    | Nonline                                                   | arity                                                                                        | 94        |  |  |  |  |  |  |  |

|                        | 7.5.1                                                     | Differential Nonlinearity (DNL) and Integral Nonlinearity (INL) for 700 mV Without Bias      | <u>94</u> |  |  |  |  |  |  |  |

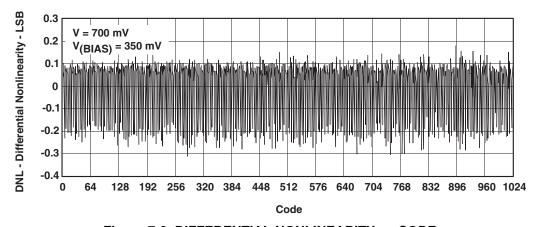

|                        | 7.5.2                                                     | Differential Nonlinearity (DNL) and Integral Nonlinearity (INL) for 700 mV + 350-mV Bias     | <u>95</u> |  |  |  |  |  |  |  |

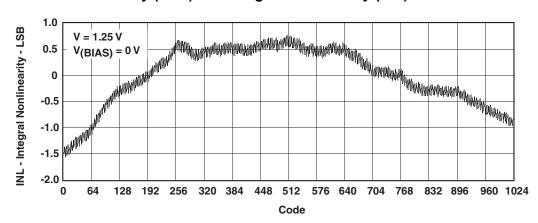

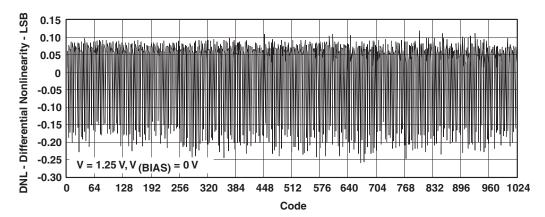

|                        | 7.5.3                                                     | Differential Nonlinearity (DNL) and Integral Nonlinearity (INL) for 1.25 V Without Bias      | <u>96</u> |  |  |  |  |  |  |  |

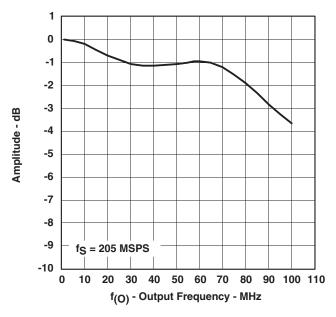

| 7.6                    | Analog                                                    | Output Bandwidth (sinx/x corrected) at f <sub>S</sub> = 205 MSPS                             | <u>97</u> |  |  |  |  |  |  |  |

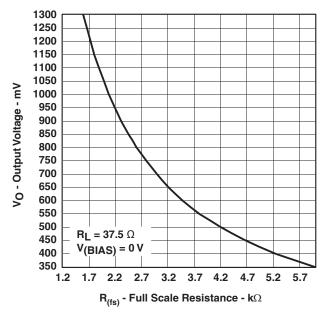

| 7.7                    | Output Compliance vs Full-Scale Adjustment Resistor Value |                                                                                              |           |  |  |  |  |  |  |  |

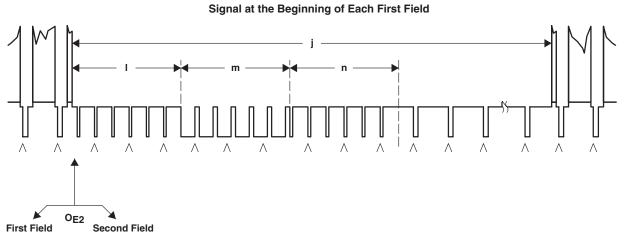

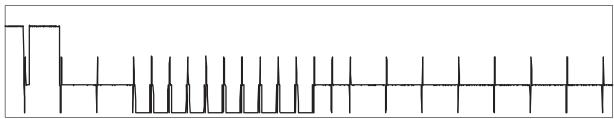

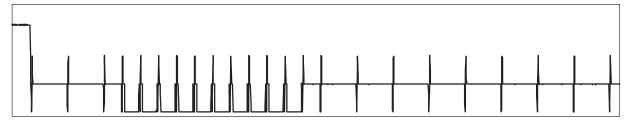

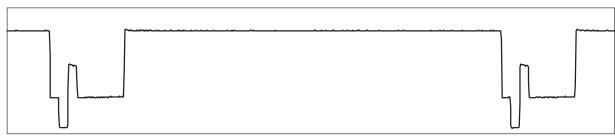

| 7.8                    | Vertical                                                  | Vertical Sync of the HDTV 1080I Format Preset in First and Second Field, and Horizontal Line |           |  |  |  |  |  |  |  |

|                        | Waveform Detail                                           |                                                                                              |           |  |  |  |  |  |  |  |

## List of Figures

| 3-1  | Functional Block Diagram                                                       | 14        |

|------|--------------------------------------------------------------------------------|-----------|

| 4-1  | 24-/30-Bit RGB or YCbCr Data Format                                            | 19        |

| 4-2  | 20-/16-Bit YCbCr 4:2:2 Data Format (16-Bit Operation Shown)                    | 20        |

| 4-3  | 16-Bit RGB 4:4:4 Data Format                                                   | 21        |

| 4-4  | 15-Bit RGB 4:4:4 Data Format                                                   | 22        |

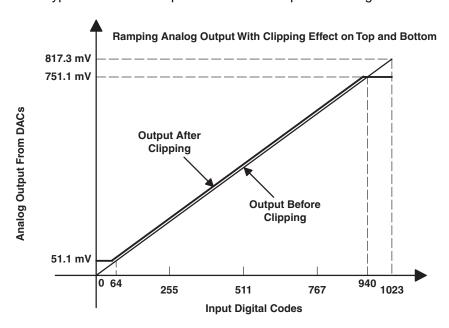

| 4-5  | Effect of Clipping on Analog Output                                            | 27        |

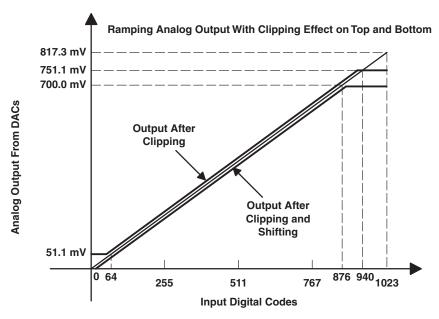

| 4-6  | Effect of Shifting on Clipped Analog Output                                    | 28        |

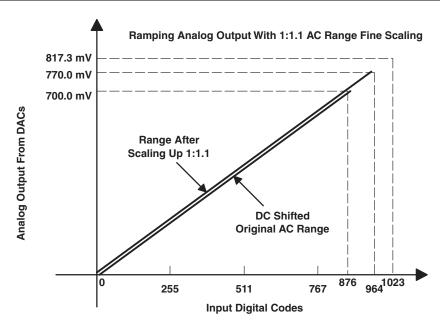

| 4-7  | Effect of Scaling the Analog Video Output                                      | 29        |

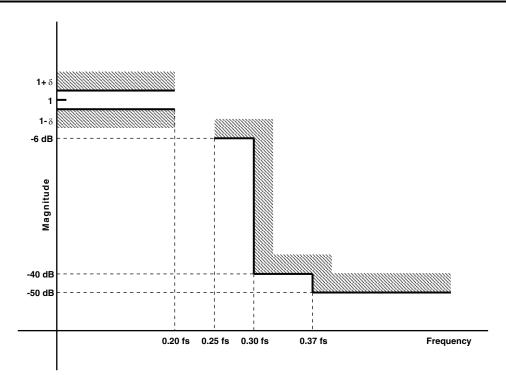

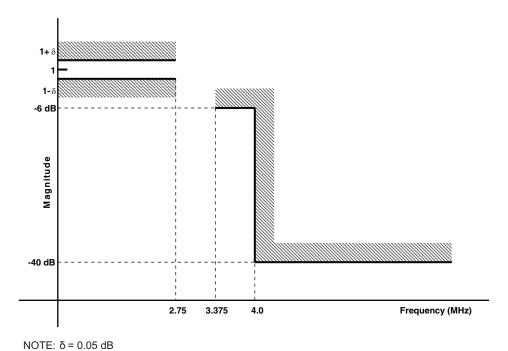

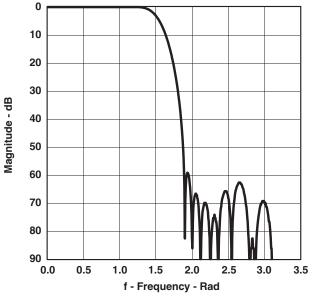

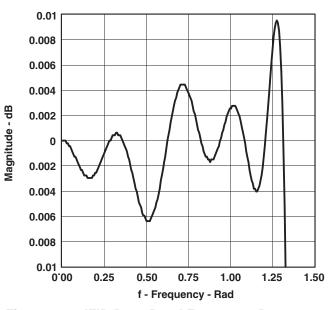

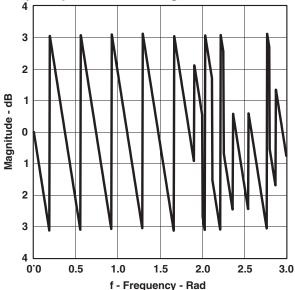

| 4-8  | P <sub>B</sub> and P <sub>R</sub> Filter Requirements Based on SMPTE 296M/274M | 30        |

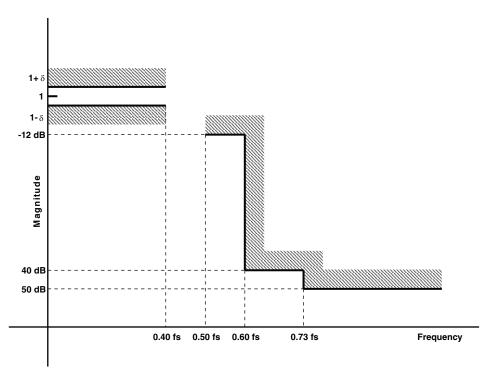

| 4-9  | Y and RGB Filter Requirements Based on SMPTE 296M/274M                         | 31        |

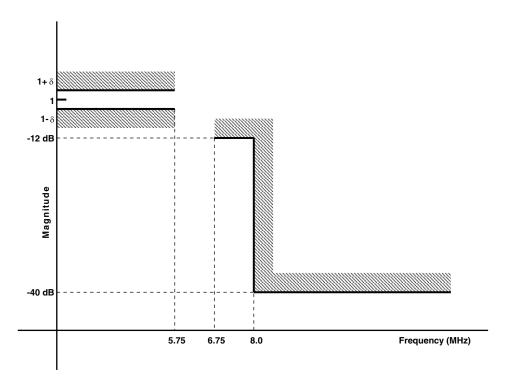

| 4-10 | Y and RGB Filter Requirements Based on ITU-R.BT601                             | <u>31</u> |

| 4-11 | Cb and Cr Filter Requirements Based on ITU-R.BT601                             | <u>31</u> |

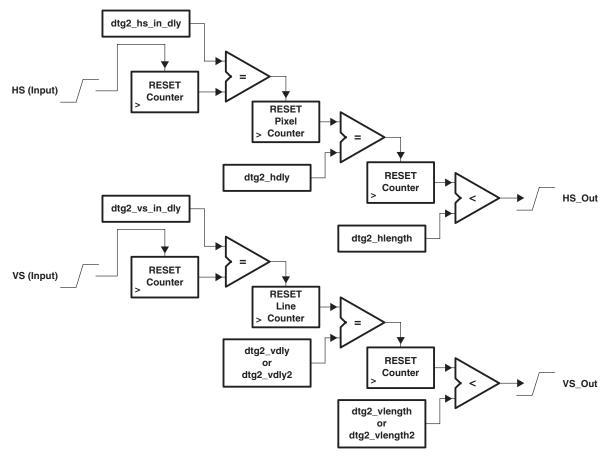

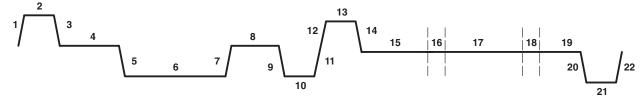

| 4-15 | THS8200 DTG VS/HS Output Generation                                            | 36        |

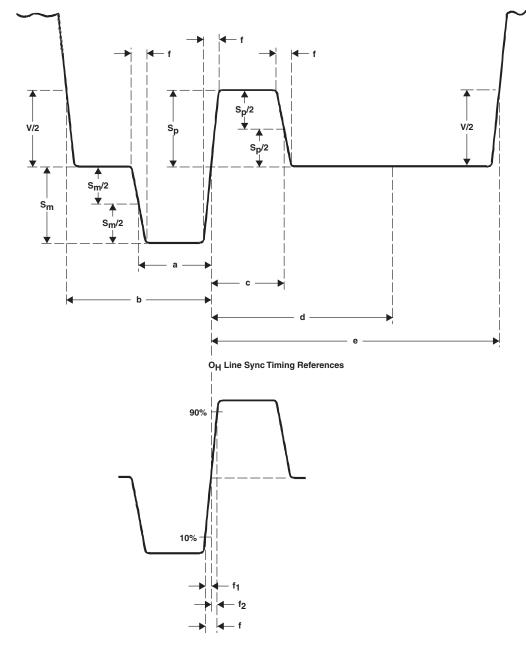

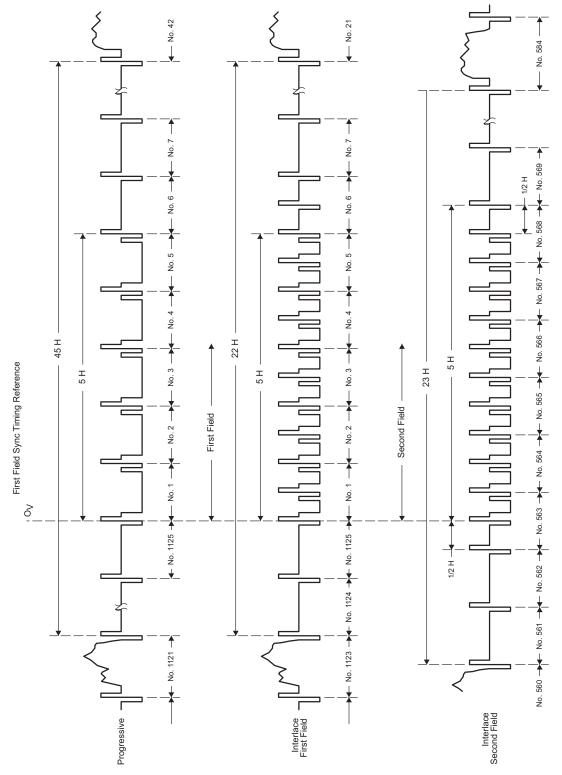

| 4-16 | Tri-Level Line-Synchronizing Signal Waveform                                   | 39        |

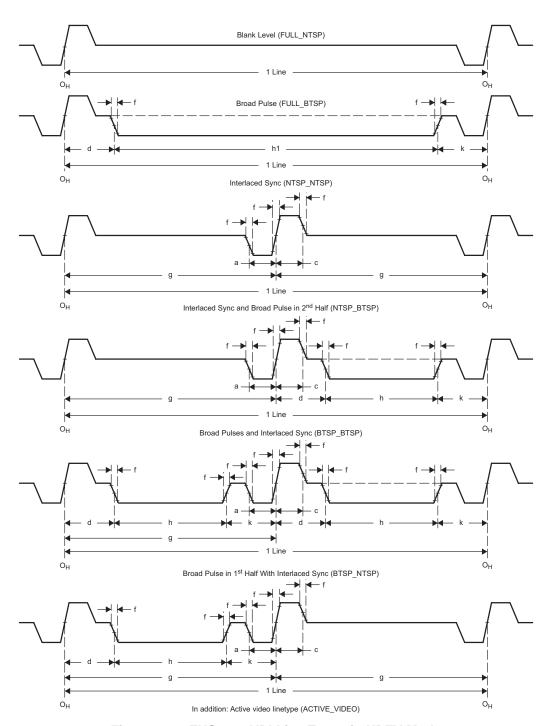

| 4-17 | THS8200 VBI Line Types in HDTV Mode                                            | 40        |

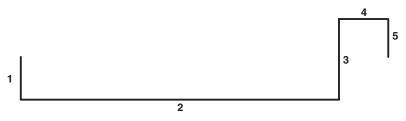

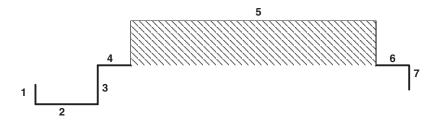

| 4-18 | HDTV Line Type ACTIVE_VIDEO                                                    | 40        |

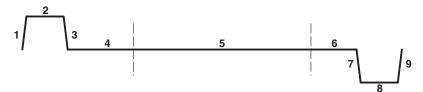

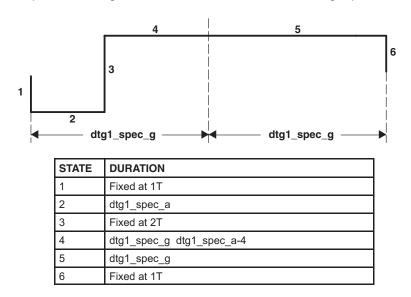

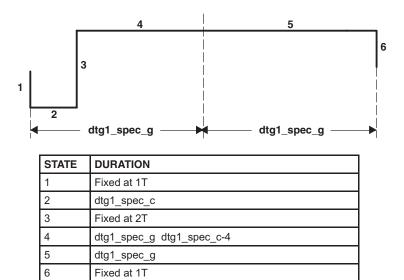

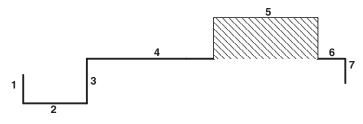

| 4-19 | HDTV Line Type FULL_NSTP                                                       | 41        |

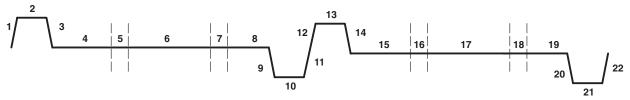

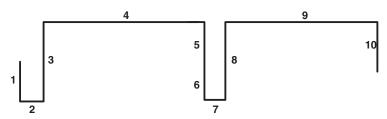

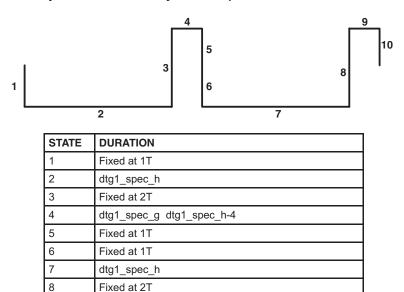

| 4-20 | HDTV Line Type NTSP_NTSP                                                       | 41        |

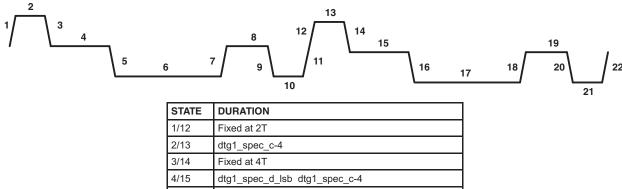

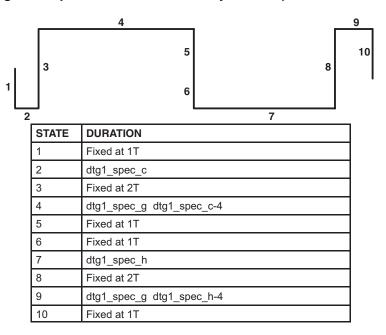

| 4-21 | HDTV Line Type BTSP_BTSP                                                       | 42        |

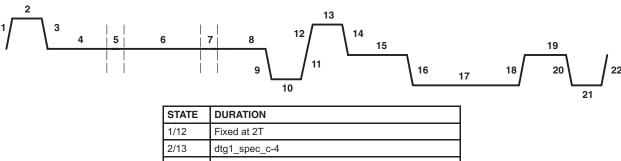

| 4-22 | HDTV Line Type NTSP_BTSP                                                       | 42        |

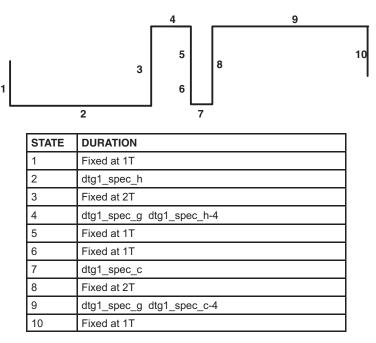

| 4-23 | HDTV Line Type BTSP_NTSP                                                       | 43        |

| 4-24 | HDTV Line Type FULL_BTSP                                                       | 43        |

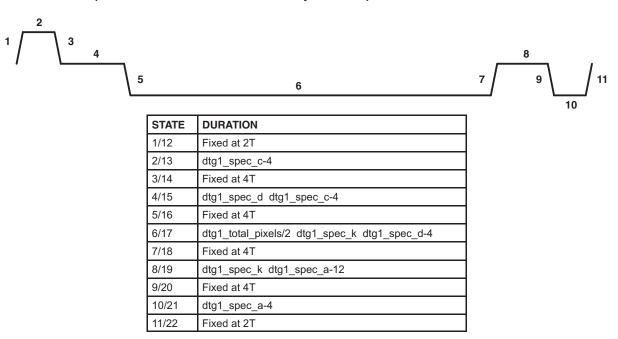

| 4-25 | Field/Frame Synchronizing Signal Waveform (1080I and 1080P Formats)            | 44        |

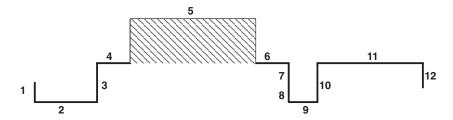

| 4-26 | Horizontal Synchronization Signal Waveform                                     | 46        |

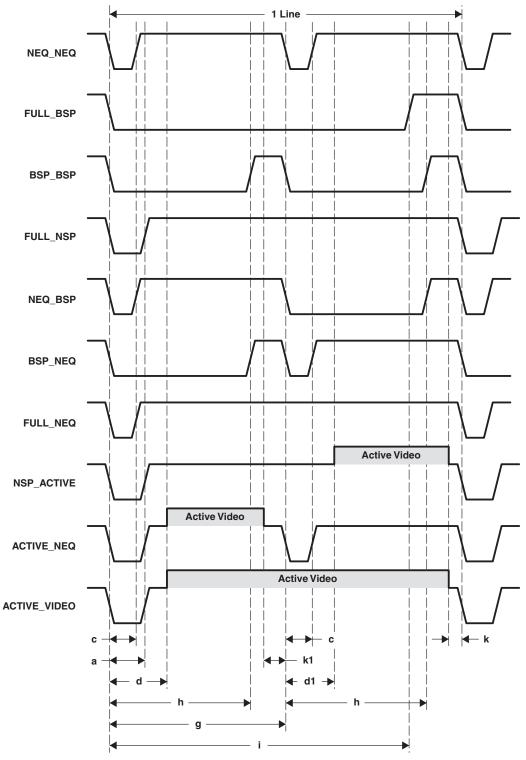

| 4-27 | THS8200 VBI Line Types in SDTV Mode                                            | 47        |

| 4-28 | SDTV Line Type NEQ_NEQ                                                         | 47        |

| 4-29 | SDTV Line Type FULL_BSP                                                        | 48        |

| 4-30 | SDTV Line Type BSP_BSP                                                         | 48        |

| 4-31 | SDTV Line Type FULL_NSP                                                        | 49        |

| 4-32 | SDTV Line Type NEQ_BSP                                                         | 49        |

| 4-33 | SDTV Line Type BSP_NEQ                                                         | <u>50</u> |

| 4-34 | SDTV Line Type FULL_NEQ                                                        | <u>50</u> |

| 4-35 | SDTV Line Type NSP_ACTIVE                                                      | <u>50</u> |

| 4-36 | SDTV Line Type ACTIVE_NEQ                                                      | <u>51</u> |

| 4-37 | SDTV Line Type ACTIVE_VIDEO                                                    | <u>51</u> |

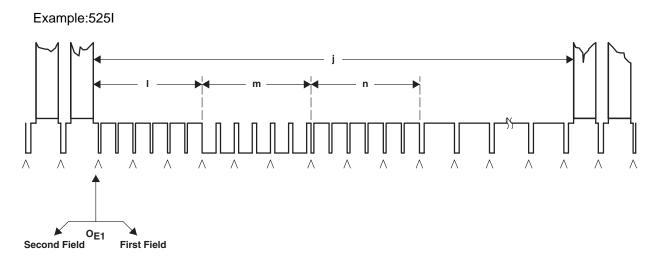

| 4-38 | Field/Frame Synchronizing Signal Waveform (525I Format)                        | 52        |

| 4-39 | RGB Without Sync Insertion or Composite Video Output                           | <u>54</u> |

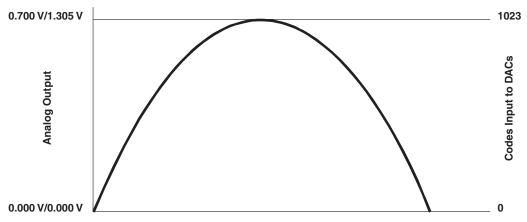

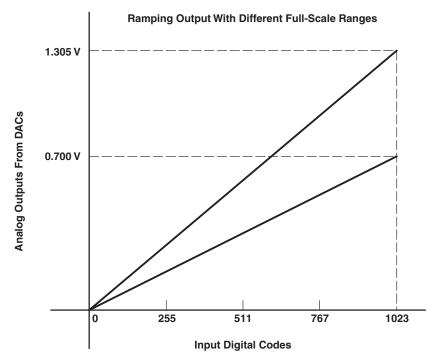

| 4-40 | Ramping Output With Different Full-Scale Ranges                                | <u>55</u> |

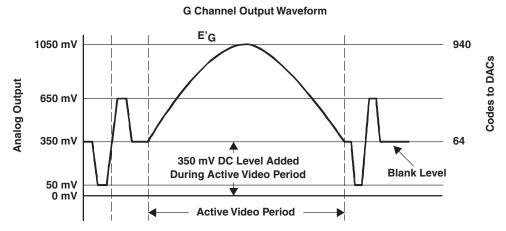

| 4-41 | G-Channel Output Waveform                                                      | 56        |

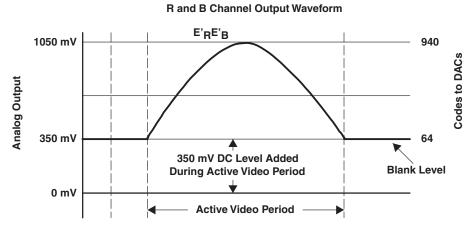

| 4-42 | R- and B-Channel Output Waveform                                               | <u>56</u> |

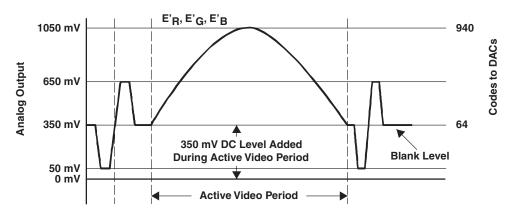

| 4-43 | R-, G-, and B-Channel Output Waveform                                          | <u>57</u> |

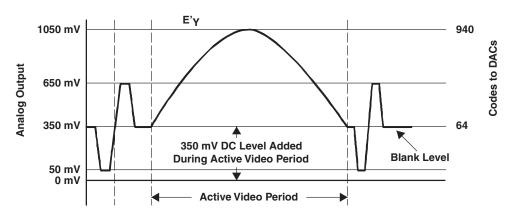

| 4-44 | Y-Channel Output Waveform                                                      | <u>57</u> |

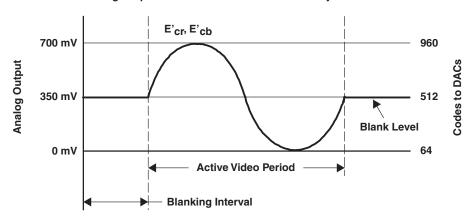

| 4-45 | Analog Output of Cr and Cb Channels Without Sync Insertion                     | <u>58</u> |

| 4-46 | Analog Output of Cr and Cb Channels With Sync Insertion                        | 58        |

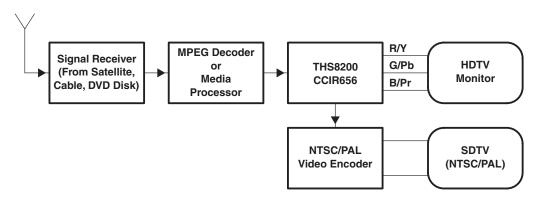

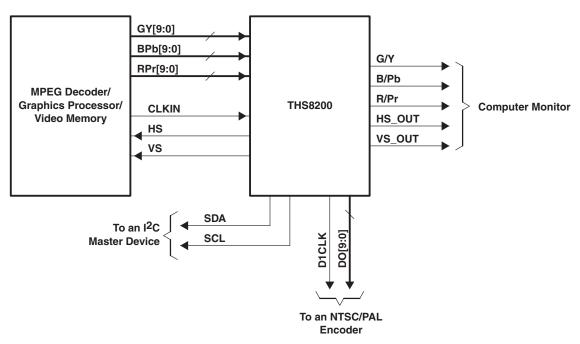

| 6-1  | Typical Video Application                                                      | 85        |

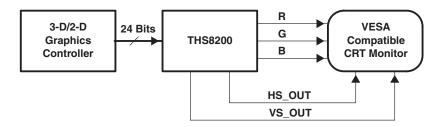

| 6-2  | Computer Graphics Application                                                  | <u>85</u> |

### **THS8200-EP**

| SLES25 | 3-DECEMBER 2009 www.ti.                  | .com      |

|--------|------------------------------------------|-----------|

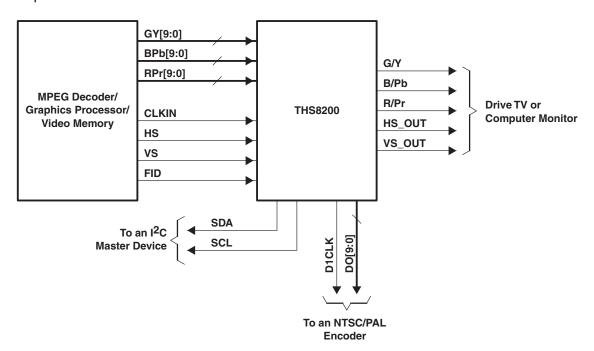

| 6-3    | Slave Operation Mode of THS8200          | 86        |

| 6-4    | Master Operation Mode of THS8200         | 87        |

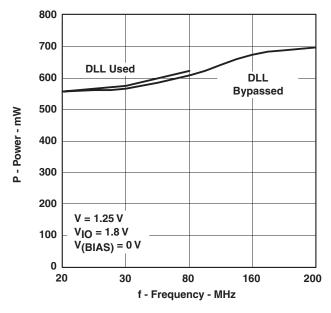

| 7-1    | POWER vs FREQUENCY                       | 91        |

| 7-2    | POWER vs FREQUENCY                       | 92        |

| 7-3    | POWER vs FREQUENCY                       |           |

| 7-4    | POWER vs FREQUENCY                       | 94        |

| 7-5    | INTEGRAL NONLINEARITY vs CODE            | 95        |

| 7-6    | DIFFERENTIAL NONLINEARITY vs CODE        | <u>95</u> |

| 7-7    | INTEGRAL NONLINEARITY vs CODE            | 95        |

| 7-8    | DIFFERENTIAL NONLINEARITY vs CODE        | 96        |

| 7-9    | INTEGRAL NONLINEARITY vs CODE            | 96        |

| 7-10   | DIFFERENTIAL NONLINEARITY vs CODE        | 97        |

| 7-11   | AMPLITUDE vs OUTPUT FREQUENCY            | 97        |

| 7-12   | OUTPLIT VOLTAGE VS EULL-SCALE RESISTANCE | 97        |

www.ti.com SLES253-DECEMBER 2009

## **List of Tables**

| 2-1 | TERMINAL FUNCTIONS      | <u>12</u> |

|-----|-------------------------|-----------|

| 4-1 | Supported Input Formats | <u>18</u> |

TEXAS INSTRUMENTS

SLES253-DECEMBER 2009 www.ti.com

www.ti.com SLES253-DECEMBER 2009

# All-Format Oversampled Component Video/PC Graphics D/A System With Three 11-Bit DACs, CGMS Data Insertion

Check for Samples: THS8200-EP

#### 1 Introduction

#### 1.1 Features

- Three 11-Bit 205-MSPS D/A Converters With Integrated Bi-Level/Tri-Level Sync Insertion

- Support for All ATSC Video Formats (Including 1080P) and PC Graphics Formats (Up to UXGA at 75 Hz)

#### **INPUT**

- Flexible 10/15/16/20/24/30-Bit Digital Video Input Interface With Support for YCbCr or RGB Data, Either 4:4:4 or 4:2:2 Sampled

- Video Synchronization Via Hsync, Vsync Dedicated Inputs or Via Extraction of Embedded SAV/EAV Codes According to ITU-R.BT601 (SDTV) or SMPTE274M/SMPTE296M (HDTV)

- Glueless Interface to TI DVI 1.0 (With HDCP)

Receivers. Can Receive Video-Over-DVI

Formats According to the EIA-861 Specification

and Convert to YPbPr/RGB Component

Formats With Separate Syncs or Embedded

Composite Sync

#### **VIDEO PROCESSING**

- Programmable Clip/Shift/Multiply Function for Operation With Full-Range or ITU-R.BT601 Video Range Input Data

- Programmable Digital Fine-Gain Controller on Each Analog Output Channel, for Accurate Channel Matching and Programmable White-Balance Control

- Built-In 4:2:2 to 4:4:4 Video Interpolation Filter

- Built-In 2x Oversampling SDTV/HDTV Interpolation Filter for Improved Video Frequency Characteristic

- Fully Programmable Digital Color Space Conversion Circuit

- Fully Programmable Display Timing Generator to Supply All SDTV and HDTV Composite Sync Ttiming Formats, Progressive and Interlaced

- Fully Programmable Hsync/Vsync Outputs

- Vertical Blanking Interval (VBI) Override or Data Pass-Thru for VBI Data Transparency

- Programmable CGMS Data Generation and Insertion

OUTPUT

- Digital

- ITU-R BT.656 Digital Video Output Port

- Analog

- Analog Component Output from Software-Switchable 700-mV/1.3-V Compliant Output DACs at 37.5-Ω load

- Programmable Video/Sync Ratio (7:3 or 10:4)

- Programmable Video Pedestal GENERAL

- Built-In Video Color Bar Test Pattern Generator

- Fast Mode I<sup>2</sup>C Control Interface

- Configurable Master or Slave Timing Mode

- Configuration Modes Allow the Device to Act as a Master Timing Source for Requesting Data from, e.g., the Video Frame Buffer. Alternatively, the Device Can Slave to an External Timing Master (Master Mode Only Available for PC Graphics Output Modes).

- DAC and Chip Powerdown Modes

- Low-Power 1.8-/3.3-V Operation

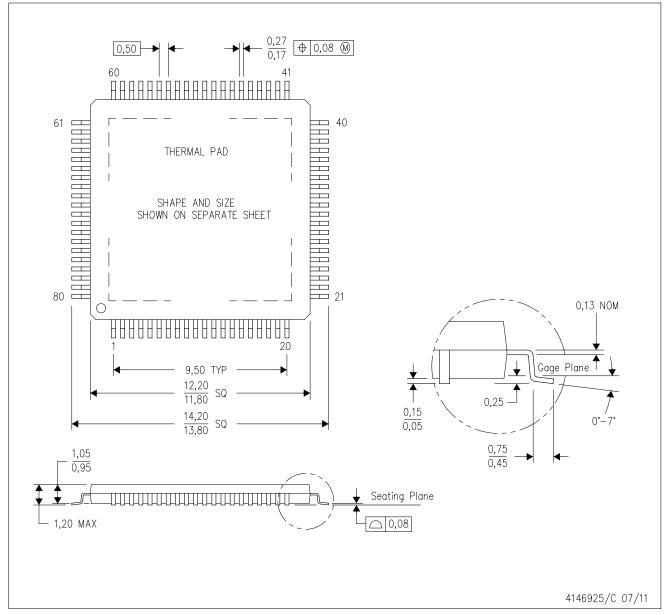

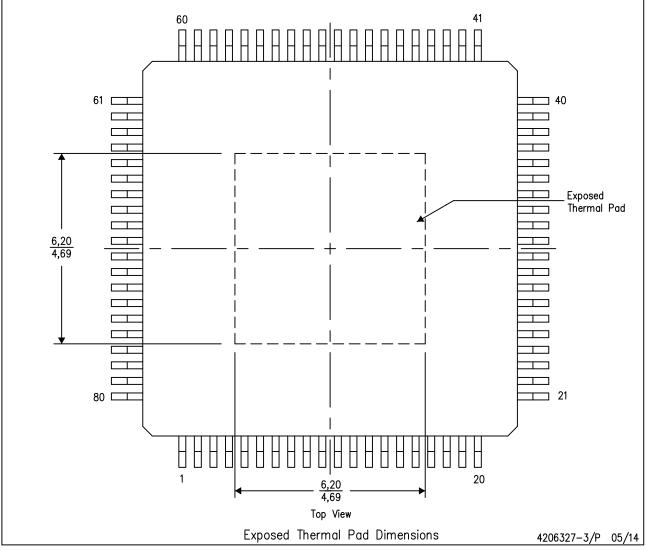

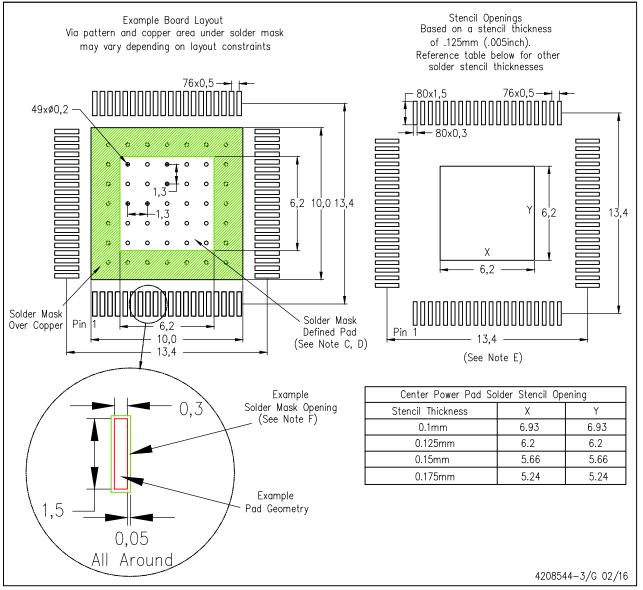

- 80-pin PowerPAD™ Plastic Quad Flatpack Package with Efficient Heat Dissipation and Small Physical Size APPLICATIONS

- DVD Players

- Digital-TV/Interactive-TV/Internet Set-Top Boxes

- Personal Video Recorders

- HDTV Display or Projection Systems

- Digital Video Systems

Instruments semiconductor products ar PowerPAD is a trademark of Texas Instruments.

#### 2 Overview

#### 2.1 Description

THS8200 is a complete video back-end D/A solution for DVD players, personal video recorders and set-top boxes, or any system requiring the conversion of digital component video signals into the analog domain.

THS8200 can accept a variety of digital input formats, in both 4:4:4 and 4:2:2 formats, over a 3x10-bit, 2x10-bit or 1x10-bit interface. The device synchronizes to incoming video data either through dedicated Hsync/Vsync inputs or through extraction of the sync information from embedded sync (SAV/EAV) codes inside the video stream. Alternatively, when configured for generating PC graphics output, THS8200 also provides a master timing mode in which it requests video data from an external (memory) source.

THS8200 contains a display timing generator that is completely programmable for all standard and nonstandard video formats up to the maximum supported pixel clock of 205 MSPS. Therefore, the device supports all component video and PC graphics (VESA) formats. A fully-programmable 3x3 matrixing operation is included for color space conversion. All video formats, up to the HDTV 1080I and 720P formats, can also be internally 2x oversampled. Oversampling relaxes the need for sharp external analog reconstruction filters behind the DAC and improves the video frequency characteristic.

The output compliance range can be set via external adjustment resistors and there is a choice of two settings, in order to accommodate without hardware changes both component video/PC graphics (700 mV) and composite video (1.3 V) outputs. An internal programmable clip/shift/multiply function on the video data assures standards-compliant video output ranges for either full 10-bit or reduced ITU-R.BT601 style video input. In order to avoid nonlinearities after scaling of the video range, the DACs are internally of 11-bit resolution. Furthermore, a bi- or tri-level sync with programmable amplitude (in order to support both 700/300-mV and 714/286-mV video/sync ratios) can be inserted either on the green/luma channel only or on all three output channels. This sync insertion is generated from additional current sources in the DACs such that the full DAC resolution remains available for the video range. This preserves 100% of the DAC's 11-bit dynamic range for video data.

THS8200 optionally supports the pass-through of ancillary data embedded in the input video stream or can insert ancillary data into the 525P analog component output according to the CGMS data specification.

#### 2.2 Ordering Information

| T <sub>A</sub> | PACKAGE | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|---------|-----------------------|------------------|

| -40°C to 85°C  | PFP     | THS8200IPFPEP         | THS8200IEP       |

SLES253-DECEMBER 2009 www.ti.com

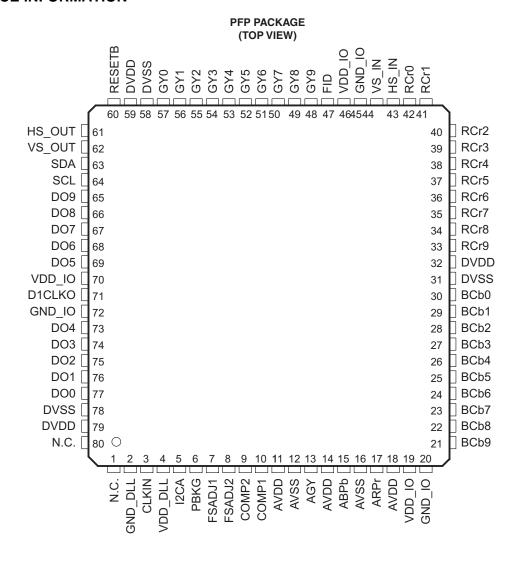

#### 2.3 **DEVICE INFORMATION**

#### **Table 2-1. TERMINAL FUNCTIONS**

| TERMINAL           |                    | (1)                | DEGODIDATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|--------------------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME               | NO.                | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ABPb               | 15                 | 0                  | Analog output of DAC2. See AGY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| ARPr               | 17                 | 0                  | Analog output of DAC3. See AGY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| AG Y               | 13                 | 0                  | Analog output of DAC1. With the proper setting of FSADJ <n>, this output is capable of driving 1.3-V full scale into a 37.5-Ω load.</n>                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| AVDD               | 11, 14, 18         | PWR                | Analog power supply, nominal 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| AVSS               | 12, 16             | PWR                | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| BCb[9:0]           | 21 - 30            | I                  | 10-bit video data input port. All 10 bits or the 8 MSB of this port can be connected to the video data source. In 30-bit mode, the B data of RGB, or the Cb data of YCbCr, should be connected to this port. In 10-bit input mode, this port is unused. In 20-bit input mode, this port is used for CbCr input data.                                                                                                                                                                                     |  |  |  |

| CLKIN              | 3                  | I                  | Main clock input. Video input data on the GY[9:0]/BCb[9:0]/RCr[9:0] ports should be synchronized to CLKIN. Depending on the input data format, CLKIN is supplied to THS8200 at 1x or 2x the pixel clock frequency.                                                                                                                                                                                                                                                                                       |  |  |  |

| COMP1              | 10                 | Р                  | Compensation pin for the internal reference amplifier. A 0.1-µF capacitor should be connected between COMP1 and analog power supply AVDD.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| COMP2              | 9                  | Р                  | Compensation pin for the internal reference amplifier. A 0.1-µF capacitor should be connected between COMP2 and analog power supply AVDD.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| D1CLKO             | 71                 | 0                  | Video ITU-R.BT656-compliant clock output. This clock output is off by default and should be activated via an $\rm I^2C$ register setting.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DO[9:5]<br>DO[4:0] | 65 - 69<br>73 - 77 | 0                  | ITU-R.BT656 compliant video data output port. Only available when ITU-R.BT656 input format is used. Can be used to connect to external PAL/NTSC video encoder. This port is o by default and should be activated via an I <sup>2</sup> C register setting.                                                                                                                                                                                                                                               |  |  |  |

| DVDD               | 32, 59, 79         | PWR                | Digital core power, nominal 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| DVSS               | 31, 58, 78         | PWR                | Digital core ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| FID                | 47                 | I                  | Field identification signal for interlaced video formats. In slave timing mode, this is an input from the video data source. In master timing mode this signal is unused, as only progressive-scan VESA formats are supported in master mode.                                                                                                                                                                                                                                                            |  |  |  |

| FSADJ1             | 7                  | Р                  | Full scale adjustment control 1. A resistor should be connected between FSADJ1 and analog ground AGND to control the full-scale output current of the DAC output channels. Via the data_fsadj $\rm I^2C$ programming register, the user can select between two full-scale ranges, determined by FSADJ1 or FSADJ2. For 700-mV video output (1 Vpp including sync), the nominal value is 2.99 k $\Omega$ ; for 1.0-Vpp video output (1.3 Vpp including sync) output the nominal value is 2.08 k $\Omega$ . |  |  |  |

| FSADJ2             | 8                  | Р                  | Full scale adjustment control 2. See FSADJ1.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| GND_DLL            | 2                  | PWR                | Ground of clock doubler. Should be connected to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| GND_IO             | 20, 45, 72         | PWR                | I/O ring ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| GY[9:0]            | 48 - 57            | I                  | 10-bit video data input port. All 10 bits or the 8 MSB of this port can be connected to the video data source. The G data of RGB or the Y data of YCbCr should be connected to this port. Port used in 10-bit mode for CbYCrY video input data; in 20-bit input mode for Y data.                                                                                                                                                                                                                         |  |  |  |

| HS_IN              | 43                 | I/O                | Horizontal source synchronization. In slave timing mode, this is an input from the video data source. In master timing mode, this is an output to the video data source with programmable timing and polarity, serving as a horizontal data qualification signal to the video source.                                                                                                                                                                                                                    |  |  |  |

| HS_OUT             | 61                 | 0                  | Horizontal sync output (to display). Irrespective of slave/master timing mode configuration, this is always an output with timing generated by the DTG.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 12CA               | 5                  | I                  | I <sup>2</sup> C device address LSB selection                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| N.C.               | 1, 80              | I                  | Manufacturing test input. Must be tied to GND for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| PBKG (VSS)         | 6                  | PWR                | Substrate ground. Should be connected to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RCr[9:0]           | 33 - 42            | I                  | 10-bit video data input port. All 10-bits or the 8 MSB of this port can be connected to the video data source. In 30-bit mode, the R data of RGB or the Cr data of YCbCr should be connected to this port. In the 10- /20-bit input mode, this port is unused. For some input formats this port is unused.                                                                                                                                                                                               |  |  |  |

| RESETB             | 60                 | I                  | Software reset pin (active low). The minimum reset duration is 200 ns.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

SLES253-DECEMBER 2009 www.ti.com

## **TERMINAL FUNCTIONS (continued)**

| TERMINAL |            | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                       |  |  |

|----------|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO.        | 1/0\               | DESCRIPTION                                                                                                                                                                                                                                                                       |  |  |

| SCL      | 64         | В                  | Serial clock line of I <sup>2</sup> C bus interface. Open-collector. Maximum specified clock speed is 400 kHz (fast I <sup>2</sup> C).                                                                                                                                            |  |  |

| SDA      | 63         | В                  | Serial data line of I <sup>2</sup> C bus interface. Open-collector.                                                                                                                                                                                                               |  |  |

| VDD_DLL  | 4          | PWR                | Power supply of clock doubler, nominal 1.8 V                                                                                                                                                                                                                                      |  |  |

| VDD_IO   | 19, 46, 70 | PWR                | I/O ring power, 1.8 V or 3.3 V nominal                                                                                                                                                                                                                                            |  |  |

| VS_IN    | 44         | I/O                | Vertical source synchronization. In slave timing mode, this is an input from the video data source. In master timing mode, this is an output to the video data source with programmable timing and polarity, serving as a vertical data qualification signal to the video source. |  |  |

| VS_OUT   | 62         | 0                  | Vertical sync output (to display). Irrespective of slave/master timing mode configuration, this is always an output with timing generated by the DTG.                                                                                                                             |  |  |

# TEXAS INSTRUMENTS

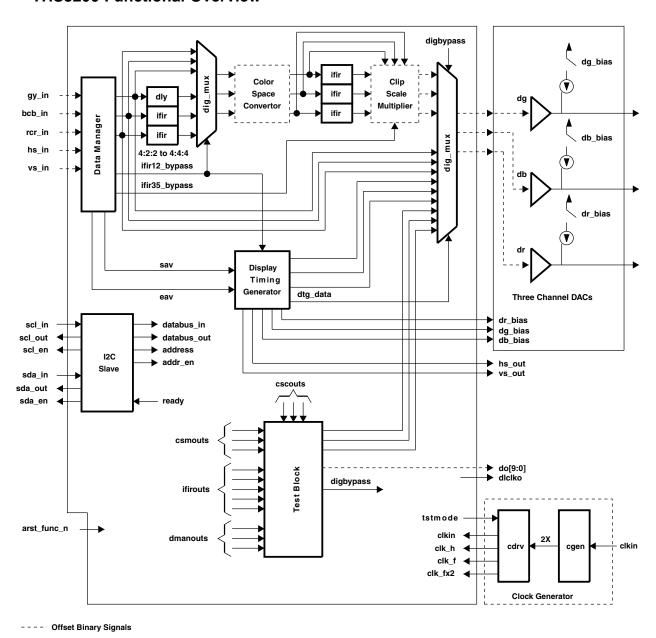

#### 3 THS8200 Functional Overview

Figure 3-1. Functional Block Diagram

www.ti.com SLES253 – DECEMBER 2009

#### 3.1 Data Manager (DMAN)

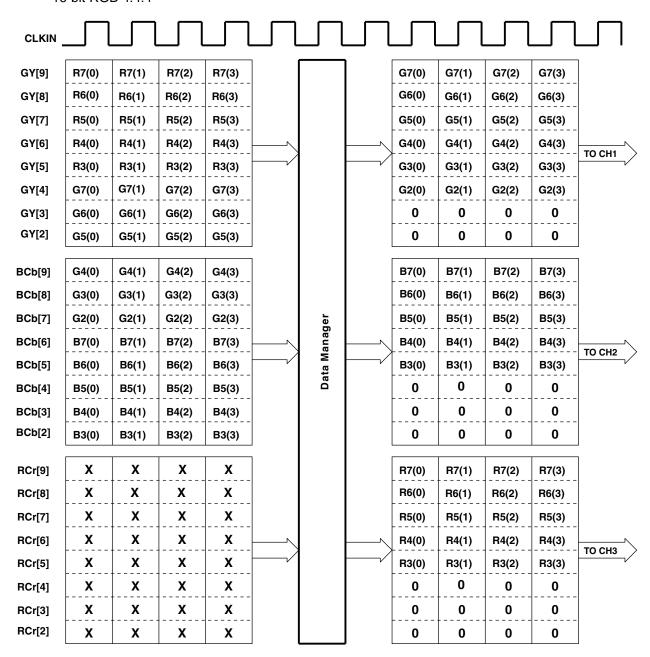

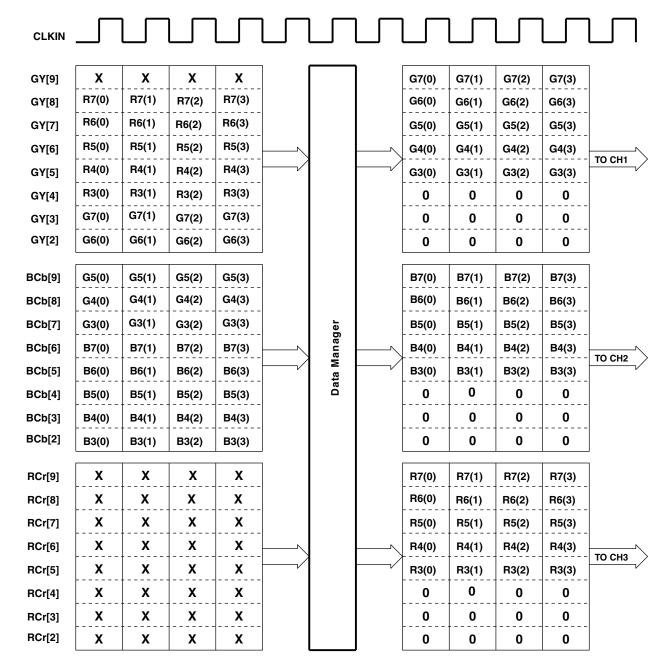

The data manager is the block that transforms the selected input video data format present on the chip input bus(es) to an internal 10-bit three-channel representation. Supported input formats include 10-/8-bit ITU-R.BT656 with embedded sync codes, 15-/16- or 24-/30-bit RGB with external sync, 20-/16-bit SMPTE274M/296M with embedded sync codes, as well as 20-/16-bit YCbCr 4:2:2 with external sync. The user can optionally include a 4:2:2 to 4:4:4 interpolation on the color data path. When a format with embedded sync is selected, DMAN also extracts H(Hsync), V(Vsync), F(FieldID) identifiers from the ITU-R.BT656 (SDTV) or SMPTE274M/296M (HDTV) data stream for internal synchronization of the DTG. Alternatively, the device synchronizes to HS\_IN, VS\_IN, FID inputs.

#### 3.1.1 Interpolating Finite Impulse Responses Filter (IFIR)

The interpolating FIR is used to upsample the input data by 2x. In the THS82000 there are five IFIRs. The first two are used only when the input data is in 4:2:2 format for conversion to a 4:4:4 internal representation on both color difference channels. The last three IFIRs are used to upsample the internal data to the DACs on all three channels in case 2x video interpolation is enabled. By 2x oversampling the video data, the requirements for the analog reconstruction filter at the DAC outputs are relaxed so it can be built with fewer components, thereby also improving the overall video frequency characteristic (less group delay variation). All of the IFIRs can be bypassed or switched in by programming the appropriate  $I^2C$  registers. The coefficients of all IFIRs are fixed.

#### 3.1.2 Color-Space Conversion (CSC)

The color-space converter block is used to convert input video data in one type of color space to output video data in another color space (e.g., RGB to YCbCr, or vice versa). This block contains a 3x3 matrix multiplier/adder and a 3x1 adder. All multiplier and adder coefficients can be programmed via the I<sup>2</sup>C interface to support any linear matrixing+offset operation on the video data.

#### 3.1.3 Clip/Shift/Multiplier (CSM)

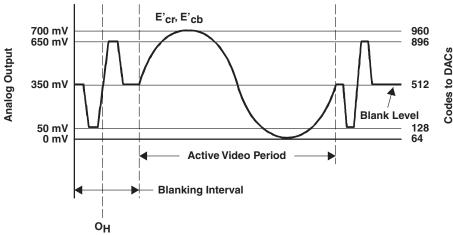

The clip-shift-multiply block optionally clips the input code range at a programmed low/high code, shifts the input video data downwards, and multiplies the input by a programmable coefficient in the range 0–1.999. This allows for operation with a reduced input code range such as prescribed in the ITU-R.BT601 recommendation. Each channel can be independently programmed to accommodate different digital ranges for each of the three input channels. For example, for standard video signals the Y channel has a digital input range of 64–940, whereas the two other channels have an input range of 64–960. All three channels must have a DAC output range of 0–700 mV, so normally the analog voltage corresponding to 1 LSB would have to change to account for the different digital inputs. This might cause matching errors. Therefore in the THS8200 the DAC LSB does not change; rather LSB conversion is done by scaling the digital inputs to the DAC's full input range. Furthermore, the CSM output is 11 bits wide and is sent to the 11-bit DACs. The extra bit of resolution resolves nonlinearities introduced by the scaling process. The clipping function can be switched off to allow for super-white/super-black excursions.

#### 3.1.4 Digital Multiplexer (DIGMUX)

This multiplexer in front of the DACs can select between video signals at 1x or 2x the pixel clock rate. It is also used to switch in blanking/sync level data generated by the display timing generator (DTG) block and test pattern data (e.g., color bars, I<sup>2</sup>C-controlled DAC levels) or to perform data insertion (CGMS) during vertical blanking.

#### 3.1.5 Display Timing Generator (DTG)

The display timing generator is responsible for the generation of the correct frame format including all sync, equalization and serration pulses. In master timing mode, the DTG is synchronized to external synchronization inputs, either from the dedicated device terminals HS\_IN, VS\_IN, and FID or is synchronized to the identifiers extracted from the input data stream, as selected by the DMAN mode. In master timing mode, the DTG generates the required field/frame format based on the externally applied pixel clock input.

When active data is not being passed to the DACs, i.e., during the horizontal/vertical blanking intervals, the DTG generates the correct digital words for blank, sync levels and other level excursions, such as preand post-serration pulses and equalization pulses.

Horizontal timings, as well as amplitudes of negative and positive sync, HDTV broad pulses and SDTV pre- and post-equalization and serration pulses, are all I<sup>2</sup>C-programmable to accommodate, e.g., the generation of both EIA.770-1 (10:4 video/sync ratio) and EIA.770-2 (7:3 video/sync ratio) compliant analog component video outputs, and to support nonstandard video timing formats.

In addition or as an alternative to the composite sync inserted on green/luma channel or all analog outputs, output video timing can be carried via dedicated Hsync/Vsync output signals as well. The position, duration and polarity of Hsync and Vsync outputs are fully programmable in order to support, for example, the centering of the active video window within the picture frame.

The DTG also controls the data multiplexer in the DIGMUX block. DIGMUX can be programmed to pass device input data only on active video lines (inserting DTG-generated blanking level during blanking intervals). Alternatively, the DTG can pass device input data also during some VBI lines (ancillary data in the input stream is passed transparently on some VBI lines). Finally, the device can also generate its own ancillary data and insert it into the analog outputs according to the CGMS data format for the 525P video format.

#### 3.1.6 Clock Generator (CGEN)

The clock generator is an analog delay-locked loop (DLL) based circuit and provides a 2x clock from the CLKIN input. The 2x clock is used by the CDRV block for 2x video interpolation. Some video formats also require a 1/2 rate clock used for 4:2:2 to 4:4:4 conversion.

#### 3.1.7 Clock Driver (CDRV)

The clock drive block generates all on-chip clocks. Its inputs are control signals from the digital logic, the original CLKIN, and the 2x clock from CGEN. Outputs include a half-rate clock, full-rate clock, and a 2x full-rate clock. The clocks are used for both optional on-chip interpolation processes: 4:2:2 to 4:4:4 interpolation and 1x to 2x video oversampling.

#### 3.1.8 FC Host Interface (I2CSLAVE)

The  $I^2C$  interface controls and programs the internal  $I^2C$  registers. The THS8200  $I^2C$  interface implementation supports the fast  $I^2C$  specification (SCL: 400 kHz) and allows the writing and reading of registers. An auto-increment addressing feature simplifies block register programming. The  $I^2C$  interface works without a clock present on CLKIN.

#### 3.1.9 Test Block (TST)

The test block controls all the test functions of the THS8200. In addition to manufacturing test modes, this block contains several user test modes including a DAC internal ramp generator and a 75% SMPTE video color bar generator.

www.ti.com SLES253-DECEMBER 2009

#### 3.1.10 D/A Converters (DAC)

THS8200 contains three DACs operating at up to 205 MSPS and with an internal resolution of 11 bits. Each DAC contains an integrated video sync inserter. The sync(s) is (are) inserted by means of additional current source circuits either on the green/luma (Y) channel only or on all the DAC output channels, in order to be compliant with both consumer (EIA, sync-on-G/Y) as well as professional (SMPTE, sync-on-all) standards.

The DAC speed supports all ATSC formats, including 1080P, as well as all PC graphics (VESA) formats up to UXGA at 75 Hz (202.5 MSPS).

#### 4 Detailed Functional Description

#### 4.1 Data Manager (DMAN)

**Table 4-1. Supported Input Formats**

|                                                   | INPUT INTERFACE  |           |                       | TIMING CONTROL   |                  | SYNCHRONIZATION    |                  |        |       |

|---------------------------------------------------|------------------|-----------|-----------------------|------------------|------------------|--------------------|------------------|--------|-------|

|                                                   | 30 BIT           | 20 BIT    | 10 BIT <sup>(1)</sup> | 16 BIT           | 15 BIT           | EMBEDDED<br>TIMING | DEDICATED TIMING | MASTER | SLAVE |

| [PRESET]<br>HDTV-SMPTE296M<br>progressive (720P)  | X (4:4:4)        | X (4:2:2) |                       |                  |                  | Х                  | Х                |        | Х     |

| [PRESET]<br>HDTV-SMPTE274M<br>progressive (1080P) | X (4:4:4)        | X (4:2:2) |                       |                  |                  | Х                  | x                |        | Х     |

| [PRESET]<br>HDTV-SMPTE274M<br>progressive (1080I) | X (4:4:4)        | X (4:2:2) |                       |                  |                  | Х                  | x                |        |       |

| [GENERIC] HDTV                                    | X (4:4:4)        | X (4:2:2) |                       |                  |                  | X                  | X                |        | Х     |

| [PRESET]<br>SDTV-ITU.1358 (525P)                  | X (4:4:4)        | X (4:2:2) | X <sup>(2)</sup>      |                  |                  | X                  | X <sup>(3)</sup> |        | X     |

| [PRESET]<br>SDTV-ITU-R.BT470<br>(525I)            | X (4:4:4)        | X (4:2:2) | X <sup>(4)</sup>      |                  |                  | Х                  | X <sup>(3)</sup> |        | Х     |

| [PRESET]<br>SDTV-ITU-R.BT470<br>(625i)            | X (4:4:4)        | X (4:2:2) | X <sup>(4)</sup>      |                  |                  | Х                  | X <sup>(3)</sup> |        | Х     |

| [GENERIC] SDTV                                    | X (4:4:4)        | X (4:2:2) |                       |                  |                  | X                  | X                |        | X     |

| [PRESET] VESA                                     | X <sup>(5)</sup> |           |                       | X <sup>(5)</sup> | X <sup>(5)</sup> |                    | X                | Х      | Х     |

<sup>(1)</sup> When the device is configured to receive data over a 10-bit interface, the ITU-R.BT656 output bus on the THS8200 can be enabled via an I<sup>2</sup>C register bit to send the received data to an external device. In other DMAN modes, this output should remain off (data\_tristate656 register).

- (2) SMPTE293M-compliant

- (3) Dedicated timing not supported with 10-bit interface.

- (4) ITU-R.BT656-compliant

- (5) Because PC graphics data is normally only 8 bits wide, only 3x8 bits (8 MSBs of each bus) are used. Color space converter bypass is required for modes with pixel clock > 150 MSPS.

Table 4-1 summarizes all supported video mode configurations.

Each video mode is characterized by three attributes:

- **Input Interface**: Data is accepted over 10-, 20- or 30-bit interface (or 8- ,16-, 24-bit interface for 8-bit data when using 8 MSBs of each input data bus and connecting 2 LSBs to ground). This selection is controlled by the dman\_cntl register.

- Timing control: Video timing is either embedded in the data stream or supplied via dedicated timing signals. In the latter case additional Hsync (HS\_IN), Vsync (VS\_IN) and FieldID (FID) input signals are required to synchronize the video data source and THS8200 in the case of slave timing mode. This selection is controlled by the dtg2\_embedded\_timing register.

- **Synchronization**: Video timing either is supplied to the device (slave) or the THS8200 requests video data from the source (master). This selection is controlled by the chip\_ms register.

#### NOTE

Device operation with combinations of settings for the dman\_cntl, dtg2\_embedded\_timing and chip\_ms registers that result in operating modes not marked in Table 4-1 is not assured. See detailed register map description for actual register settings.

www.ti.com SLES253-DECEMBER 2009

Furthermore, Table 4-1 shows for which modes presets are defined. When in a preset video mode, the line-type/breakpoint-pairs that define the frame format (see Display Timing Generator, Section 4.7) are preprogrammed. Therefore the user does not need to define the table with line type/breakpoint settings, nor does the field and frame size need to be programmed. However, when in preset mode, the horizontal parameters (all dtg1\_spec\_x registers for the line types used by the preset setting, and dtg1\_total\_pixels registers) still need to be programmed. Presets are available for most popular DTV video formats. Alternatively, generic modes for SDTV, HDTV or VESA can be selected, which allow full programmability of the field/frame sizes and DTG parameters.

#### Note from the table that:

- If embedded timing is used, the device is always in slave mode, because the data stream supplied to THS8200 contains the video timing information.

- Master operation is only supported for PC graphics (VESA) formats.

- In HDTV modes with embedded timing, data is supplied to the device over a 20-bit interface, as defined in SMPTE274/296M.

- In SDTV modes with embedded timing, data is supplied to the device over a 10-bit interface. When the

video format is interlaced, this interface is known as ITU-R.BT656 (525I, 625I). When the video format

is progressive, only 525P is supported with embedded timing. The 625P interface can be supported

with dedicated timing, using the SDTV generic mode.

- In generic modes with dedicated timing, both 20 bits (4:2:2) and 30 bits (4:4:4) are supported.

- In PC graphics modes (VESA generic), input data is either over the 30-bit interface or over the 16-/15-bit interface and always has dedicated timing. Note that the 16-bit interface is not equivalent to a 2×8-bit version of the 20-bit interface; see Section 4.2, Input Interface Formats, for details.

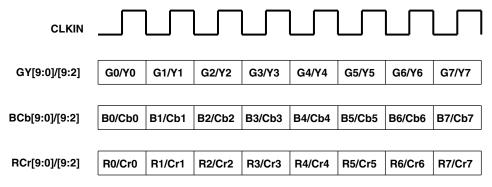

#### 4.2 Input Interface Formats

The following figures define the input video format for each input mode, as selected by the data\_dman\_cntl register setting. Video data is always clocked in at the rising edge of CLKIN.

#### NOTE

For 8-bit operation with 10-bit input buses, connect only the 8 MSBs of each input bus used, and tie the 2 LSBs to ground.

30-bit YCbCr/RGB 4:4:4

Figure 4-1. 24-/30-Bit RGB or YCbCr Data Format

20-bit YCbCr 4:2:2

CLKIN is equal to the  $1 \times$  pixel clock. The pixel clock equals the rate of the Y input and is  $2 \times$  the rate of the 2 other channels in this input format where Cb and Cr are multiplexed onto the same input bus.

SLES253-DECEMBER 2009 www.ti.com

Figure 4-2. 20-/16-Bit YCbCr 4:2:2 Data Format (16-Bit Operation Shown)

When dedicated timing is used in this mode, there is a fixed relationship between the first active period of HS\_IN (i.e., the first CLKIN rising edge seeing HS\_IN active) and a Cb color component assumed present during that clock period on the bus receiving CbCr samples. When embedded timing is used in this mode, the SAV/EAV structure also unambiguously defines the CbCr sequence, according to SMPTE274M/296M for HDTV.

#### NOTE

The figure shows the case when only 8 bits of each 10-bit input bus are used.

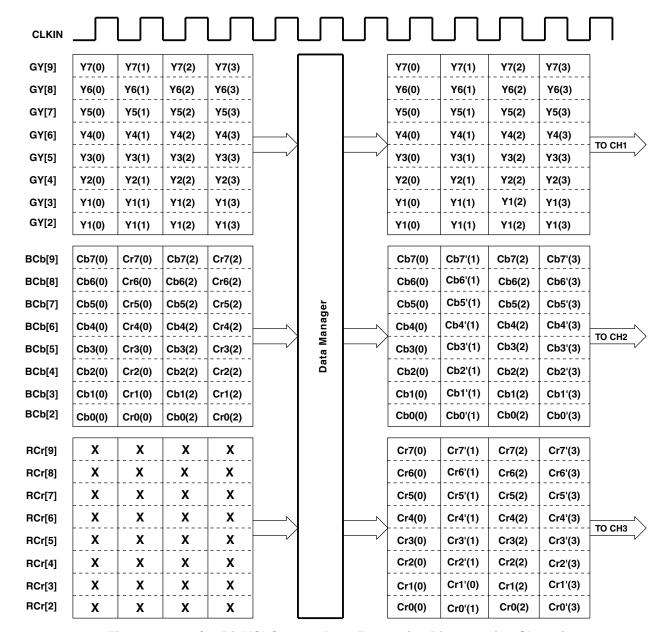

10-bit YCbCr 4:2:2 (ITU mode)

CLKIN is equal to 2x the pixel clock since all components are multiplexed on a single 10-bit bus with a 4-multiple sequence: CbYCrY. Therefore the pixel clock (i.e., the Y input rate) is 1/2 of CLKIN and the Cb and Cr rate are 1/4 of CLKIN.

When dedicated timing is used in this mode, there is a fixed relationship between the first active period

SLES253-DECEMBER 2009 www.ti.com

of HS\_IN (i.e. the first CLKIN rising edge seeing HS active) and a Cb color component assumed present during that clock period on the input bus. When embedded timing is used in this mode, the SAV/EAV structure also unambiguously defines the CbCr sequence, according to ITU-R.BT656 (for 625I and 525I) and SMPTE293M (for 525P).

16-bit RGB 4:4:4

Figure 4-3. 16-Bit RGB 4:4:4 Data Format

CLKIN is equal to 1x the pixel clock. This format is only supported in VESA mode and can be used for PC graphics applications that do not require full 8-bit resolution on each color component.

15-bit RGB 4:4:4

SLES253-DECEMBER 2009 www.ti.com

Figure 4-4. 15-Bit RGB 4:4:4 Data Format

CLKIN is equal to 1x the pixel clock. This format is only supported in VESA mode and can be used for PC graphics applications that do not require full 8-bit resolution on each color component.

#### 4.3 Clock Generator (CGEN)/Clock Driver (CDRV)

The clock generator/clock driver blocks generate all on-chip clocks for 4:2:2 to 4:4:4 and 2x video oversampling. The DMAN setting controls whether the input data is 4:2:2 or 4:4:4 sampled, and whether a 30-, 20- or 10-bit interface is used. This selection affects the clock input frequency assumed to be present on CLKIN.

30-bit 4:4:4: 1x pixel clock, 4:2:2 to 4:4:4 interpolation should be bypassed. Optional 2x oversampling is available for formats with pixel clock up to 80 MHz.

www.ti.com SLES253 – DECEMBER 2009

• 20-bit 4:2:2: 1x pixel clock. 4:2:2 to 4:4:4 interpolation should be switched in, and is available for formats with pixel clock up to 150 MHz. Optional 2x oversampling available for formats with pixel clock up to 80 MHz.

• 10-bit 4:2:2 (ITU): 1/2x pixel clock. 4:2:2 to 4:4:4 interpolation should be switched in, and is available for formats with pixel clock up to 150 MHz. Optional 2x oversampling is available for formats with pixel clock up to 80 MHz.

The internal DLL (delay-locked loop) generates the higher clock frequencies. The user should program the input frequency range selection register, dll\_freq\_sel, according to the frequency present on CLK\_IN when using either or both interpolation/oversampling stages.

The 4:2:2 to 4:4:4 stage is switched in or bypassed, depending on the setting of data\_ifir12\_bypass register (interpolation only on chroma channels). This feature should only be used with YCbCr 4:2:2 input. The THS8200 can perform color space conversion to RGB depending on the CSC setting. The dtg2\_rgbmode\_on register should be set corresponding to the color space representation of the DAC output.

The 2x oversampling stage is switched in or bypassed, depending on the setting of data\_ifir35\_bypass register.

The user should not enable the 2x oversampling stage when the CLK\_IN frequency exceeds 80 MHz, as is the case for the higher PC graphics formats and 1080P HDTV. In this case the DLL should be bypassed using the vesa\_clk register to disable the 2x frequency generation. As explained in the detailed register map description for this register, it is still possible to support 20-bit 4:2:2 input in this mode (e.g., for 1080P).

A second bypass mode operation exists for the DLL, enabled by the dll\_bypass register. When this bypass mode is active, the CLKIN input is assumed to be 2x pixel frequency. This mode is meant only for test purposes as it does not correspond to any mode in the supported input formats table.

SLES253-DECEMBER 2009 www.ti.com

#### 4.4 Color Space Conversion (CSC)

THS8200 contains a fully-programmable 3x3 multiply/add and 3x1 adder block that can be switched in for all video formats up to a pixel clock frequency of 150 MHz. Color space conversion is thus available for all DTV modes, including 1080P and VESA modes up to SXGA at 75 Hz (135 MSPS). The operation is done after optional 4:2:2 to 4:4:4 conversion, and thus on the 1x pixel clock video data prior to optional 2x video oversampling. The CSC block can be switched in or bypassed depending on the setting of register csc\_bypass.

Each of the nine floating point multiplier coefficients of the 3x3 multiply/add is represented as the combination of a 6-bit signed binary integer part, and a 10-bit fractional part. The integer part is a signed magnitude representation with the MSB as the sign bit. The fractional part is a magnitude representation; see the following example.

The register nomenclature is: csc\_<r,g,b> <i,f>c<1,2,3> where:

- <r,g,b> identifies which input channel is multiplied by this coefficient (r = red/Cr, g = green/Y, b = blue/Cb input).

- <i,f> identifies the integer (i) or fractional (f) part of the coefficient.

- <1,2,3> identifies the output channel from the color space converter: 1 = Yd/Gd, 2 = Cb/Bd, 3 = Cr/Rd.

For the offset values, a value of 1/4 of the desired digital offset needs to be programmed in the individual offset register, so a typical offset of 512 (offset over 1/2 of the video range) requires programming a value of 128 decimal into the offset<1,2,3> registers, where again <1,2,3> defines the output channel affected, with similar convention as shown previously.

Saturation logic can be switched in to avoid over- and underflow on the result after color space conversion using the csc uof cntl register.

We next show an example of how to program the CSC. This also explains the numeric data formats.

CSC configuration example: HDTV RGB to HDTV YCbCr

The formulas for RGB to YCbCr conversion are:

- Yd = 0.2126\*Rd + 0.7152\*Gd + 0.0722\*Bd

- Cb = -0.1172\*Rd 0.3942\*Gd + 0.5114\*Bd + 512

- Cr = 0.5114\*Rd 0.4646\*Gd 0.0468\*Bd + 512

To program the red coefficient of channel 1 (Y) with the value of 0.2126 the following must be done:

- 1. Realize that this is a positive value so the sign bit of the integer part is 0 (bit 5 of csc\_ric1 = 0).

- 2. Note that there is no integer portion of the coefficient (bit 4-bit 0 = 00000).

- 3. The binary representation of the fractional part can be constructed directly from the binary equivalent of the fractional part multiplied by 1024 (0.2126 × 1024 = 217.7), rounded to the nearest integer (218) and represented as a binary 10-bit number (00 1101 1010).

Using the above method all the registers for the CSC blocks can be programmed with the correct value for RGB to YCbCr conversion. Below is a complete list of register values for the above conversion.

| 0.2126 → csc_ric1 = 00 0000                | csc_rfc1 = 00 1101 1010 |

|--------------------------------------------|-------------------------|

| $0.7152 \rightarrow csc\_gic1 = 00\ 0000$  | csc_gfc1 = 10 1101 1100 |

| 0.0722 → csc_bic1 = 00 0000                | csc_bfc1 = 00 0100 1010 |

| -0.1172 → csc_ric2 = 10 0000               | csc_rfc2 = 00 0111 1000 |

| $-0.3942 \rightarrow csc\_gic2 = 10\ 0000$ | csc_gfc2 = 01 1001 0100 |

| 0.5114 → csc_bic2 = 00 0000                | csc_bfc2 = 10 0000 1100 |

| $0.5114 \rightarrow csc\_ric3 = 00\ 0000$  | csc_rfc3 = 10 0000 1100 |

| $-0.4646 \rightarrow csc\_gic3 = 10\ 0000$ | csc_gfc3 = 01 1101 1100 |

| $-0.0468 \rightarrow csc\_bic3 = 10\ 0000$ | csc_bfc3 = 00 0011 0000 |

SLES253-DECEMBER 2009

For the offsets necessary in the second and third equation the csc\_offset<n> registers need to be programmed. We need to add 512 to the Cb and Cr channels. The value to be programmed is 1/4 of this offset in a signed magnitude representation, thus 128 or csc\_offset2 = csc\_offset3 = 00 1000 0000.

Packing these individual registers into the I<sup>2</sup>C register map, the programmed values are:

| SUBADDRESS | REGISTER NAME | VALUE     |

|------------|---------------|-----------|

| 0x04       | csc_r11       | 0000 0000 |

| 0x05       | csc_r12       | 1101 1010 |

| 0x06       | csc_r21       | 1000 0000 |

| 0x07       | csc_r22       | 0111 1000 |

| 0x08       | csc_r31       | 0000 0010 |

| 0x09       | csc_r32       | 0000 1100 |

| 0x0A       | csc_g11       | 0000 0010 |

| 0x0B       | csc_g12       | 1101 1100 |

| 0x0C       | csc_g21       | 1000 0001 |

| 0x0D       | csc_g22       | 1001 0100 |

| 0x0E       | csc_g31       | 1000 0001 |

| 0x0F       | csc_g32       | 1101 1100 |

| 0x10       | csc_b11       | 0000 0000 |

| 0x11       | csc_b12       | 0100 1010 |

| 0x12       | csc_b21       | 0000 0010 |

| 0x13       | csc_b22       | 0000 1100 |

| 0x14       | csc_b31       | 1000 0000 |

| 0x15       | csc_b32       | 0011 0000 |

| 0x16       | csc_offs1     | 0000 0000 |

| 0x17       | csc_offs12    | 0000 1000 |

| 0x18       | csc_offs23    | 0000 0010 |

| 0x19       | csc_offs3     | 0000 0000 |

CSC configuration example: HDTV YCbCr to HDTV RGB

- Gd = -0.4577\*Cr + Yd 0.1831\*Cb + 328 (= 0.6408\*128\*4)

- Bd = 0\*Cr + Yd + 1.8142\* Cb 929 (= -1.8142\*128\*4)

- Rd = 1.5396\* Cr + Yd + 0\*Cb 788 (= -1.5396\*128\*4)

Submit Documentation Feedback Product Folder Link(s): THS8200-EP

In a similar manner, it can be calculated that the programming array is in this case:

| SUBADDRESS | REGISTER NAME | VALUE     |

|------------|---------------|-----------|

| 0x04       | csc_r11       | 1000 0001 |

| 0x05       | csc_r12       | 1101 0101 |

| 0x06       | csc_r21       | 0000 0000 |

| 0x07       | csc_r22       | 0000 0000 |

| 0x08       | csc_r31       | 0000 0110 |

| 0x09       | csc_r32       | 0010 1001 |

| 0x0A       | csc_g11       | 0000 0100 |

| 0x0B       | csc_g12       | 0000 0000 |

| 0x0C       | csc_g21       | 0000 0100 |

| 0x0D       | csc_g22       | 1000 0000 |

| 0x0E       | csc_g31       | 0000 0100 |

| 0x0F       | csc_g32       | 0000 0000 |

| 0x10       | csc_b11       | 1000 0000 |

| 0x11       | csc_b12       | 1011 1011 |

| 0x12       | csc_b21       | 0000 0111 |

| 0x13       | csc_b22       | 0100 0010 |

| 0x14       | csc_b31       | 0000 0000 |

| 0x15       | csc_b32       | 0000 0000 |

| 0x16       | csc_offs1     | 0001 0100 |

| 0x17       | csc_offs12    | 1010 1110 |

| 0x18       | csc_offs23    | 1000 1011 |

| 0x19       | csc_offs3     | 0001 0100 |

#### 4.5 Clip/Scale/Multiplier (CSM)

There are limits on the code range of the video data if sampled according to ITU or SMPTE standards. In other words, the full 10-bit range [0:1023] is not used to represent video pixels. For example, typically 64 decimal is the lowest code allowed to represent a video signal and corresponds to the blanking level. Similarly for Y, typically the maximum code is 940 decimal. Excursions outside this range can be the result of digital video processing.