# Dual DMOS Full Bridge Motor Driver With Serial Port Control and Dual Regulators

#### **Features and Benefits**

- 3.3/5 V switching regulator

- 1 to 2.5 V configurable linear regulator output

- Dual DMOS full bridge: drive two DC motors or a single stepper motor

- ±1.5 A, 50 V output rating per bridge

- 4-bit microstepping capability

- Serial port control

- Configurable mixed, fast, and slow current decay

- Synchronous rectification for low power dissipation

- Internal UVLO and thermal shutdown circuitry

- Crossover-current protection

- OCP protection

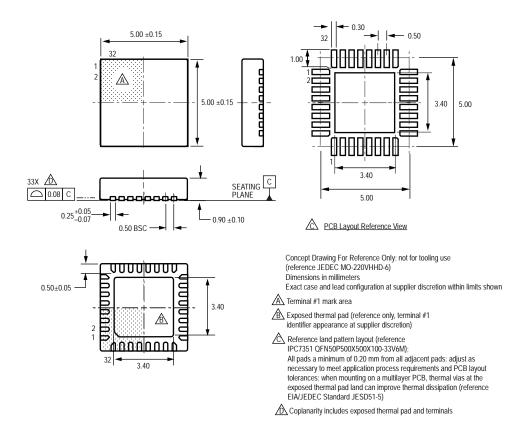

# Package: 32-contact QFN (suffix ET)

### **Description**

Designed to provide the motor driver and power supply requirements for printers and office automation equipment. This integrated power IC incorporates two high current, high performance, full bridge outputs, capable of 1.5 A at 50 V. Additionally two power supply rails are provided for microprocessor or DSP supplies. A switching buck regulator steps the supply down to a low voltage output that is adjustable from 3.3 to 5 V. This voltage can be used to supply external 5 V rails, it also feeds back into the part and supplies the integrated linear regulator which is adjustable from 1 to 2.5 V.

The A3998 serial port provides flexible configuration for the dual full bridge motor driver. Two full bridges can be programmed to control one stepper motor or two DC motors. Both bridges have integrated fixed off-time PWM control with programmable decay mode selection.

The A3998 is supplied in a low profile, 32-contact QFN,  $5 \times 5$  mm, 0.90 mm nominal height, with exposed thermal pad (suffix ET). The package is lead (Pb) free with 100% matte-tin leadframe plating.

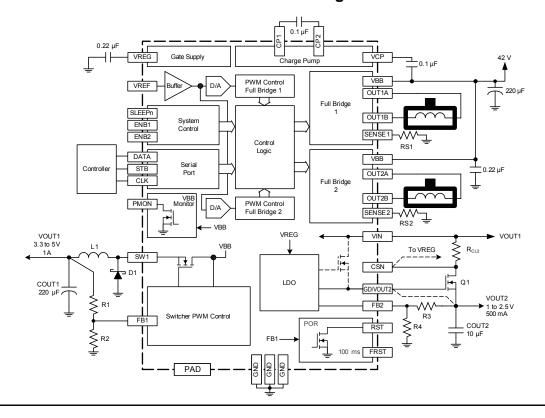

# **Functional Block Diagram**

### **Selection Guide**

| Part Number  | Packing*                   |

|--------------|----------------------------|

| A3998SETTR-T | 1500 pieces per 7-in. reel |

<sup>\*</sup>Contact Allegro<sup>™</sup> for additional packing options

## **Absolute Maximum Ratings\***

| Characteristic                | Symbol               | Notes                         | Rating      | Unit |

|-------------------------------|----------------------|-------------------------------|-------------|------|

| Load Supply Voltage           | V <sub>BB</sub>      |                               | 50          | V    |

| Outrot Comment                |                      | Motor, DC                     | 1.5         | Α    |

| Output Current                | l <sub>OUT</sub>     | Pulsed, t <sub>W</sub> < 1 μs | 6           | Α    |

| Octobe Welfers                | .,                   | DC                            | 0.52        | V    |

| Sense Voltage                 | V <sub>SENSE</sub>   | t <sub>W</sub> < 1 μs         | 2.5         | V    |

| SW1 Pin Voltage               | V <sub>SW</sub>      |                               | –1 to 50    | V    |

| Logic Pins Voltage Range      | V <sub>IO</sub>      |                               | -0.3 to 5.5 | V    |

| VIN Pin Voltage               | V <sub>IN</sub>      |                               | -0.3 to 6   | V    |

| FB Pins Voltage Range         | V <sub>FB</sub>      |                               | -0.3 to 5.5 | V    |

| VREF Pin Voltage Range        | V <sub>REF</sub>     |                               | -0.3 to 5.5 | V    |

| PMON, RST Pins Voltage Range  | V <sub>RST</sub>     |                               | -0.3 to 5.5 | V    |

| VREG Pin Voltage Range        | V <sub>REG</sub>     |                               | -0.3 to 8   | V    |

| Operating Ambient Temperature | T <sub>A</sub>       | S temperature range           | -20 to 85   | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                               | 150         | °C   |

| Storage Temperature           | T <sub>stg</sub>     |                               | -55 to 150  | °C   |

### Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic                             | Symbol | Test Conditions*                                               | Value | Unit |

|--------------------------------------------|--------|----------------------------------------------------------------|-------|------|

| Package Thermal Resistance                 |        | 4-layer PCB based on JEDEC standard                            | 30    | °C/W |

| Package Thermal Resistance $R_{\theta JA}$ |        | Estimated, on 2-layer PCB with 1 in.2 of copper area each side | 55    | °C/W |

<sup>\*</sup>Additional thermal information available on the Allegro website

#### **Table of Contents**

| Table of Contents                     |   |                                         |    |

|---------------------------------------|---|-----------------------------------------|----|

| Specifications                        | 2 | PWM Control Mode                        | 9  |

| Pin-out Diagram and Terminal List     | 2 | Phase Control                           | 10 |

| Thermal Characteristics               |   | Enable Logic                            | 10 |

| Terminal List                         | 3 | Fast Decay Time                         | 10 |

| Terrimar List                         | 3 | PWM Blank Timer                         | 10 |

| Electrical Characteristics            | 4 | Synchronous Rectification               | 10 |

| Functional Description                | 7 | Protection                              | 11 |

| Voltage Regulators                    | 7 | Power-On Reset                          | 11 |

| Switching Regulator                   | 7 | Application Information                 | 16 |

| Linear Regulator                      | 8 | PCB Layout                              | 16 |

| Serial Port                           | 8 | Switcher                                | 16 |

| Serial Port Writing                   | 8 | Motor Driver                            | 16 |

| Configuration Register                | 9 | Thermal Considerations                  | 16 |

| Motor Driver                          | 9 | Switching Regulator Component Selection | 16 |

| Full Bridge Output Current Regulation | 9 | Package Outline Drawing                 | 19 |

| Fixed Off-Time                        | 9 |                                         |    |

|                                       |   |                                         |    |

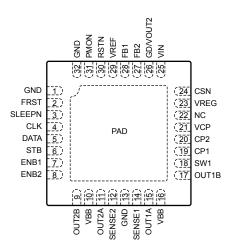

# **Pin-out Diagram**

#### **Terminal List Table**

| Number  | Name   | Function                          | Number | Name     | Function                       |

|---------|--------|-----------------------------------|--------|----------|--------------------------------|

| 1,13,32 | GND    | Ground                            | 18     | SW1      | DC to DC switch output         |

| 2       | FRST   | Control logic input               | 19     | CP1      | Charge pump capacitor terminal |

| 3       | SLEEPN | Control logic input, active low   | 20     | CP2      | Charge pump capacitor terminal |

| 4       | CLK    | Control logic input               | 21     | VCP      | Reservoir capacitor terminal   |

| 5       | DATA   | Control logic input               | 22     | NC       | No connect                     |

| 6       | STB    | Control logic input               | 23     | VREG     | Gate supply                    |

| 7       | ENB1   | Control logic input               | 24     | CSN      | Current Sense/Reg select       |

| 8       | ENB2   | Control logic input               | 25     | VIN      | Logic supply/ LDO supply       |

| 9       | OUT2B  | DMOS full bridge 2, output B      | 26     | GD/VOUT2 | Gate drive output / VOUT2      |

| 10, 16  | VBB    | Motor and switcher supply voltage | 27     | FB2      | Feedback for VOUT2             |

| 11      | OUT2A  | DMOS full bridge 2, output A      | 28     | FB1      | Feedback for VOUT1             |

| 12      | SENSE2 | Sense resistor terminal, bridge 2 | 29     | VREF     | Analog input                   |

| 14      | SENSE1 | Sense resistor terminal, bridge 1 | 30     | RSTN     | Reset flag output              |

| 15      | OUT1A  | DMOS full bridge 1, output A      | 31     | PMON     | Power monitor flag output      |

| 17      | OUT1B  | DMOS full bridge 1, output B      | _      | PAD      | Exposed thermal pad            |

# A3998

## ELECTRICAL CHARACTERISTICS<sup>1,2</sup> Valid at T<sub>J</sub> = 25°C, V<sub>BB</sub> = 50 V; unless otherwise specified

| Characteristics                                        | Symbol                | Test Conditions                                                                                    | Min.                   | Typ. <sup>3</sup> | Max.                  | Unit |

|--------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------|------------------------|-------------------|-----------------------|------|

| Load Supply Voltage Range                              | V <sub>BB</sub>       | Operating                                                                                          | 9                      | _                 | 50                    | V    |

| Bridge Output On Besisters                             | _                     | Source driver, I <sub>OUT</sub> = -1.5 A                                                           | _                      | 0.5               | _                     | Ω    |

| Bridge Output On-Resistance                            | R <sub>DS(on)RG</sub> | Sink driver, I <sub>OUT</sub> = 1.5 A                                                              | _                      | 0.5               | _                     | Ω    |

| VBB Pins Supply Current                                | I <sub>BB</sub>       | V <sub>REG</sub> regulated, I <sub>OUT</sub> = 0 mA, outputs on,<br>PWM = 50 kHz, Duty Cycle = 50% | -                      | 5                 | 10                    | mA   |

|                                                        | I <sub>BBS</sub>      | Standby mode, regulator active                                                                     | _                      | _                 | 5                     | mA   |

| VIN Pin Supply Current                                 | I <sub>IN</sub>       |                                                                                                    | _                      | 5                 | 8                     | mA   |

| Control Logic                                          |                       |                                                                                                    |                        |                   |                       |      |

| Logic Inputs Voltage Range                             | V <sub>IO</sub>       | Operating                                                                                          | 3                      | _                 | 5.5                   | V    |

| Logic Input Voltage                                    | V <sub>IO(1)</sub>    |                                                                                                    | V <sub>DD</sub> × 0.55 | _                 | _                     | V    |

| Logic Input Voltage                                    | V <sub>IO(0)</sub>    |                                                                                                    | _                      | _                 | V <sub>DD</sub> ×0.27 | V    |

| Logic Pins Input Current (Except ENB1,ENB2, FRST pins) | I <sub>IO</sub>       | V <sub>IN</sub> = 0 to 5 V                                                                         | -20                    | <1.0              | 20                    | μΑ   |

| ENB1,ENB2, FRST Pins Input Current                     | I <sub>IO(1)</sub>    | V <sub>IN</sub> = 3.3 V                                                                            | _                      | 66                | 100                   | μΑ   |

| ENDT,ENDZ, FROT FINS INput Current                     | I <sub>IO(0)</sub>    | V <sub>IN</sub> = 0.8 V                                                                            | _                      | 16                | 40                    | μΑ   |

| Input Hysteresis                                       | V <sub>IOHYS</sub>    |                                                                                                    | 200                    | _                 | 700                   | mV   |

|                                                        |                       | PWM change to source on                                                                            | 350                    | 550               | 1000                  | ns   |

| Propagation Dolay Time                                 | t <sub>pd</sub>       | PWM change to source off                                                                           | 35                     | _                 | 250                   | ns   |

| Propagation Delay Time                                 |                       | PWM change to sink on                                                                              | 350                    | 550               | 1000                  | ns   |

|                                                        |                       | PWM change to sink off                                                                             | 35                     | _                 | 250                   | ns   |

| Crossover Delay                                        | t <sub>COD</sub>      |                                                                                                    | 300                    | 425               | 1000                  | ns   |

| Supply Monitor                                         |                       |                                                                                                    |                        |                   |                       |      |

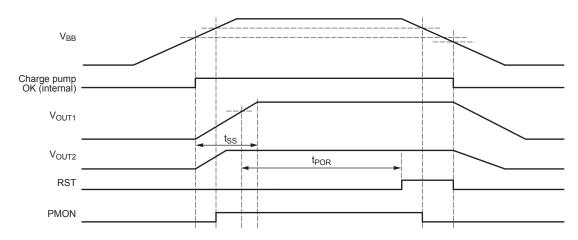

| Reset Timer                                            | t <sub>POR</sub>      |                                                                                                    | 70                     | 100               | 130                   | ms   |

| RSTN and PMON Pins Output<br>Voltage                   | V <sub>RST</sub>      | I <sub>OUT</sub> = 1 mA                                                                            | -                      | -                 | 0.5                   | V    |

| RSTN and PMON Pins Output<br>Leakage Current           | I <sub>leakage</sub>  | V <sub>OUT</sub> = 5 V                                                                             | -                      | -                 | 1                     | μΑ   |

| Power Monitor Threshold                                | V <sub>PM(th)</sub>   | PMON pin, V <sub>BB</sub> falling                                                                  | 12                     | 13                | 14                    | V    |

| Power Monitor Hysteresis                               | V <sub>PMHYS</sub>    |                                                                                                    | _                      | 2                 | _                     | V    |

| Protection Circuits                                    |                       |                                                                                                    |                        |                   |                       |      |

| VIN Pin UVLO Threshold                                 | V <sub>INUV(th)</sub> | V <sub>IN</sub> rising                                                                             | _                      | 2.8               | 3                     | V    |

| VIN Pin UVLO Hysteresis                                | V <sub>INUVHYS</sub>  |                                                                                                    | _                      | 100               | _                     | mV   |

| VBB Pins UVLO Threshold                                | V <sub>BBUV(th)</sub> | V <sub>BB</sub> rising                                                                             | 6.6                    | 7.1               | 7.6                   | V    |

| VBB Pins UVLO Hysteresis                               | V <sub>BBUVHYS</sub>  |                                                                                                    | 0.7                    | 0.9               | 1.1                   | V    |

| FB1 Pin UVLO Threshold                                 | V <sub>FBUV(th)</sub> | V <sub>FB</sub> falling                                                                            | 698                    | 735               | 772                   | mV   |

| FB1 Pin UVLO Hysteresis                                | V <sub>FBUVHYS</sub>  |                                                                                                    | _                      | 100               | _                     | mV   |

| Thermal Shutdown Temperature                           | T <sub>JSD</sub>      |                                                                                                    | 155                    | 165               | 175                   | °C   |

| Thermal Shutdown Hysteresis                            | T <sub>JSDHYS</sub>   |                                                                                                    | _                      | 20                | _                     | °C   |

Continued on the next page...

# **ELECTRICAL CHARACTERISTICS**<sup>1,2</sup> (continued) Valid at $T_J = 25$ °C, $V_{BB} = 50$ V; unless otherwise specified

| Characteristics                          | Symbol                | Test Conditions                                                         | Min.                  | Typ. <sup>3</sup> | Max. | Unit |

|------------------------------------------|-----------------------|-------------------------------------------------------------------------|-----------------------|-------------------|------|------|

| DC to DC Converter                       |                       |                                                                         |                       |                   |      |      |

| Feedback Voltage Regulation <sup>4</sup> | V <sub>FB1</sub>      | Does not include Cycle Skipping mode (V = 9 to 50 V, I = 100 mA to 1 A) | 0.98                  | 1                 | 1.02 | V    |

| G G                                      | 151                   | Cycle Skipping mode                                                     | 0.95                  | 1                 | 1.05 | V    |

| Feedback Input Bias Current              | I <sub>FB1</sub>      |                                                                         | -400                  | -                 | 100  | nA   |

| Soft Start Duration                      | t <sub>SS</sub>       | V <sub>BB</sub> = 9 V                                                   | 5                     | 10                | 15   | ms   |

| Current Limit                            | I <sub>CLREG</sub>    | V <sub>FB</sub> > 400 mV                                                | 1.5                   | -                 | 2.7  | А    |

| Current Limit                            | I <sub>CLFB</sub>     | V <sub>FB</sub> < 400 mV                                                | .5                    | -                 | 1.2  | Α    |

| Fixed Off-time                           | t <sub>OFF</sub>      | V <sub>OUT</sub>                                                        | _                     | 4                 | -    | μs   |

| Buck Switch On-Resistance                | R <sub>DS(on)SW</sub> | I = 1 A, T <sub>J</sub> = 25°C                                          | _                     | 0.6               | -    | Ω    |

| Low Drop-Out Regulator                   |                       |                                                                         |                       |                   |      |      |

| Feedback Voltage                         | V <sub>FB2</sub>      | I = 0 to 500 mA                                                         | .98                   | 1                 | 1.02 | V    |

| Internal Current Limit                   | I <sub>CL2</sub>      | CSN connected to VREG                                                   | 525                   | -                 | 750  | mA   |

| External Current Limit Threshold         | V <sub>CL2</sub>      | CSN connected to sense resistor                                         | 180                   | 200               | 220  | mV   |

| VIN Pin Voltage Range                    | V <sub>IN</sub>       |                                                                         | V <sub>OUT</sub> +0.6 | _                 | 5.5  | V    |

| Control Circuit                          |                       |                                                                         |                       |                   |      |      |

| VREF Pin Input Voltage Range             | V <sub>REFRNG</sub>   | Operating                                                               | 0.0                   | -                 | 2.6  | V    |

| Reference Input Current                  | I <sub>REF</sub>      | V <sub>REF</sub> = 2.0, V <sub>BB</sub> = 0 to 50 V                     | _                     | -                 | ±1   | μA   |

| Transconductance Error <sup>5</sup>      | Cm                    | V <sub>REF</sub> = 2.0, DAC = 15                                        | -4                    | _                 | 4    | %    |

| Transconductance Errors                  | Gm <sub>ERR</sub>     | V <sub>REF</sub> = 2.0, DAC = 3                                         | -10                   | _                 | 10   | %    |

| Internal Oscillator Frequency            | f <sub>osc</sub>      |                                                                         | 3.4                   | 4                 | 4.6  | MHz  |

<sup>&</sup>lt;sup>1</sup>Negative current is defined as coming out of (sourcing) the specified device pin.

<sup>&</sup>lt;sup>2</sup>Specified limits are tested at a single temperature and assured over the range 0°C to 125°C by design and characterization.

<sup>&</sup>lt;sup>3</sup>Typical data is for design information only.

<sup>4</sup>Average value of V<sub>OUT</sub> relative to target. 5Gm<sub>ERR</sub> =[(V<sub>REF</sub> × Current\_Ratio / 5) – V<sub>SENSE</sub>] / (V<sub>REF</sub> × Current\_Ratio / 5).

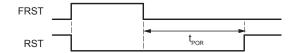

### **Normal Power-up Timing Diagram**

# **RST Function Timing with FRST Input**

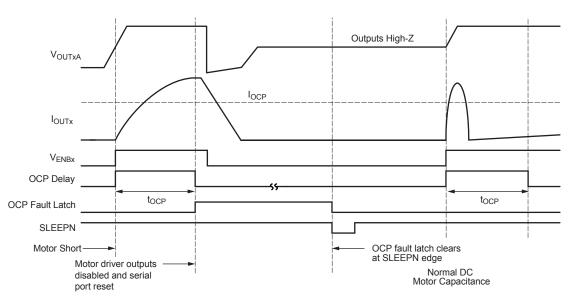

## **Overcurrent Protection (OCP) Timing Diagram**

# **Functional Description**

# Voltage Regulators

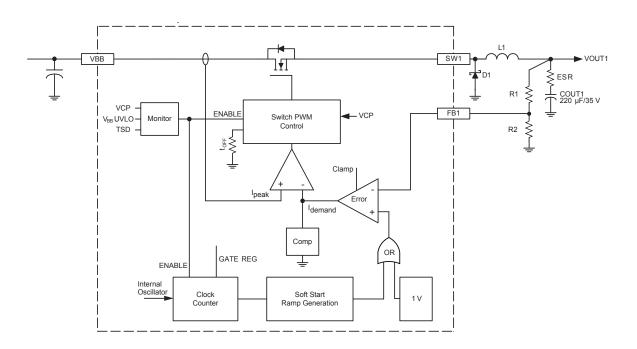

#### **Switching Regulator**

An adjustable fixed off-time, peak current controlled buck regulator is used to provide external voltage to microprocessors or DSPs. The switcher output is fed back into the device and provides low voltage logic supply for the IC, improving overall efficiency. The regulator can operate in both continuous and discontinuous modes. An internal blanking circuit filters out transients due to the reverse recovery of the external clamp diode.

The switching regulator fixed off-time of approximately 4  $\mu s$  is appropriate for the  $V_{OUT1}$  range from 3.3 to 5 V.

**Light Load Regulation** The switching regulator enters Cycle Skipping mode at light load conditions to maintain reasonable voltage regulation. As the output current decreases, there remains some energy that is stored during the power switch minimum on-time. The stored energy is transferred to the output capacitor and the output voltage begins to increase. To prevent energy

in the inductor from pumping the supply voltage up, the A3998 can skip PWM cycles. Cycle skipping mode can be activated any time there is discontinuous current in the inductor.

**Soft Start** An internal ramp generator and counter allow the output to ramp-up slowly. This limits the maximum demand on the external power supply by controlling the inrush current required to charge the external capacitor and any DC load at start-up. Internally, the ramp is set to 10 ms nominal rise time.

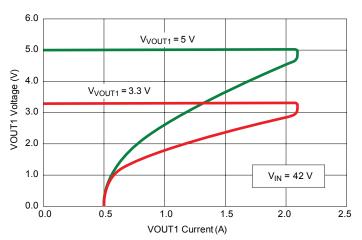

**Shorted Load** The regulator incorporates an overcurrent limit to handle shorted load conditions at the regulator output. For low output voltages at power-up, and in the case of a short, the off-time is extended to prevent loss of control of the current limit due to the minimum on-time of the switcher.

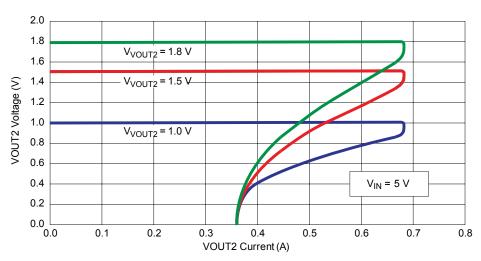

The overcurrent limit has a foldback feature to reduce the current limit when the output is overloaded (see figure 2). The voltage at the feedback pin (FB) is monitored to determine which current limit level to use. As the feedback voltage rises above approximately 400 mV, the foldback circuit is disabled.

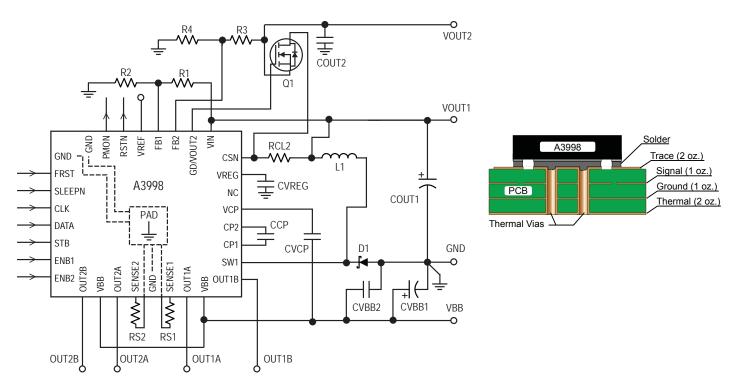

Figure 1. Implementation of switcher circuit; see table 3 for external component specifications.

#### **Linear Regulator**

An adjustable voltage rail from 1 to 2.5 V is integrated into the device. The switcher output is fed back into the device through the VIN pin and supplies the integrated linear pass element. To reduce power dissipation in the A3998, the linear regulator can be configured to drive the gate of an external N-channel FET. Using the external FET significantly reduces power dissipation in the IC and can allow the device to operate in high ambient temperature environments.

The regulator has two configurations: Internal mode and External mode. External mode is used to minimize power dissipation. In External mode current is limited by selection of the sense resistor, RCL. Internal mode is selected by connecting pin CSN to the

Figure 2. Switcher current limit with foldback

VREG pin. Both internal and external configurations are current limited.

Internal Configuration When the internal pass element is configured the internal current limit is fixed at I<sub>CL2</sub>. The regulator has overcurrent protection with foldback. Figure 3 shows the I•V characteristic of the linear regulator.

**External Configuration** When the external pass element is configured the current is adjustable by selecting the value of a current limit resistor R<sub>CL2</sub>. When the voltage across the resistor equals V<sub>CL2</sub> the regulator enters current limit and will fold back according to the waveform shown in figure 3. To calculate the current limit use the formula below:

$$V_{\rm CL2} / I_{\rm LIM} = R_{\rm CL} \tag{1}$$

where I<sub>LIM</sub> is the target current limit.

### **Serial Port**

#### Serial Port Writing

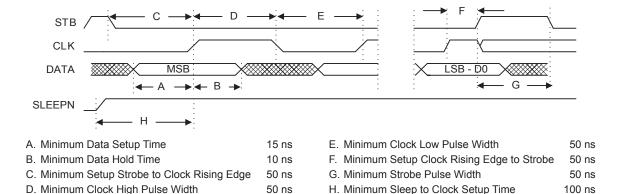

The serial port is accessed for writing only, using the STB (Strobe), CLK (clock), DATA and SLEEPN pins. Addressing consists of word selection bits (D15:D14) followed by the bit values for each parameter in the word. Timing requirements are shown in figure 4.

Figure 3. Linear current limit with foldback

#### **Configuration Register**

A configuration register supporting four 16-bit words can be set using the serial port.

The Configuration register is volatile memory accessed through the serial port. The bit descriptions are shown in table 1. At a power-on reset (POR), the bits are set to their default values, all zeros with the exception of the MSB of the fixed off-time parameters, which are set to one.

#### **Motor Driver**

#### **Full Bridge Output Current Regulation**

Maximum load current is regulated by an Internal PWM mode, fixed off-time current control circuit. When the outputs of the DMOS full bridges are turned on, current increases in the motor winding until it reaches a value given by:

$$I_{\text{TRIP}} = V_{\text{REF}} \times \text{Current Ratio} / (5 \times R_{\text{S}})$$

(2)

where  $R_S$  is the value of the sense resistor RS, and the Current Ratio is as shown in table 2.

At the trip point, the sense comparator resets the source enable latch, turning off the source driver. At this point, load inductance causes the current to recirculate for the serial port programmed fixed off-time period. The current path during recirculation is determined by the configuration of slow/mixed decay mode and the synchronous rectification control bits.

#### **Fixed Off-Time**

The PWM timer is programmable via the serial port to provide fixed off-time PWM signals to the A3998 internal control block.

Five bits (word 0/1, D6:D2) are available for each full bridge to adjust the fixed off-time, t<sub>OFF</sub>, when Internal PWM current control mode is selected.

The off-time is defined by the following equation:

$$t_{\text{OFF}} = (1 + N) \times T_{\text{OSC}} \times 8 - T_{\text{OSC}}$$

(3)

where N is the word value, from 0 to 31, and T<sub>OSC</sub> is the period of the internal oscillator.

For example, given the internal oscillator frequency,  $f_{OSC}$ , of 4 MHz (typ) ( $T_{OSC}$  = 250 ns), the fixed off-time is adjustable from 2 to 64  $\mu$ s in increments of 2  $\mu$ s.

#### **PWM Control Mode**

The selection of Internal or External PWM control mode for each full bridge is made in the Configuration register.

- Selection of Internal control mode (word 2, D0 and D7) sets the Internal PWM Decay Mode (Mixed or Slow), and allows the configuration of Fixed Off-Time and Fast Decay Time. In Mixed Decay mode, during the first portion of the off-time period, the A3998 operates in Fast Decay mode, until the Fast Decay time count is reached. The rest of the fixed off-time period the A3998 operates in Slow Decay mode. If the Fast Decay Time duration is longer than the Fixed Off-Time duration, the device effectively operates in Fast Decay mode throughout the period.

- Selection of External control mode (word 2, D1 and D8) sets the External PWM Decay Mode (Fast or Slow). In this mode, a chopping signal on the Enable pins (ENBx) are used to provide external PWM current control.

Figure 4. Serial Port Timing Diagram

#### **Phase Control**

This setting sets the relative states of the full-bridge outputs. This determines if the device operates in the forward or reverse (relative) direction:

| Serial Port<br>Configuration Bit<br>(Word 2) |         | Phase |      |

|----------------------------------------------|---------|-------|------|

| D2/D9                                        | State   | OUTA  | OUTB |

| 0                                            | Reverse | Low   | High |

| 1                                            | Forward | High  | Low  |

#### **Enable Logic**

The ENB1 and ENB2 input terminals are provided for external PWM control of the two full bridges. When ENBx is set to logic high, output on the corresponding full bridge is enabled. When set to logic low, the bridge output is chopped.

#### **Fast Decay Time**

Four bits (word 0/1, D10:D7) are available for each full bridge to set the Fast Decay portion, t<sub>FD</sub>, of the fixed off-time when Internal PWM control, Mixed Decay mode is selected.

The Fast Decay portion is defined by:

$$t_{\rm FD} = (1+N) \times T_{\rm OSC} \times 8 - T_{\rm OSC} \tag{4}$$

where N is the word value, from 0 to 15.

For example, given the internal oscillator frequency,  $f_{OSC}$ , of 4 MHz (typ) ( $T_{OSC}$  = 250 ns), the fixed off-time is adjustable from 2 to 32  $\mu$ s in increments of 2  $\mu$ s. For  $t_{FD}$  >  $t_{OFF}$ , the device effectively operates in Fast Decay mode.

#### **PWM Blank Timer**

When a source driver turns on, a current spike occurs due to the reverse recovery currents of the clamp diodes and/or switching transients related to distributed capacitance in the load. To prevent this current spike from erroneously resetting the source enable latch, the sense comparator is blanked.

The programmable blanking function is enabled while the blank timer runs, which is after the off-time counter expires. When the Enable (ENBx) signal is chopped, or the Phase setting in the the Configuration register is changed, a PWM-off cycle is initiated and the blank timer is reset.

**Blank Time** Two bits (word 0/1, D1:D0) are available for each full bridge to set the current sense comparator blank time when any output driver is switched on. The settings are according to the following table (T<sub>OSC</sub> is the period of the internal oscillator):

| Serial Port Configuration Bit<br>(Word 0/1) |    | Blank Time            |

|---------------------------------------------|----|-----------------------|

| D1                                          | D0 |                       |

| 0                                           | 0  | 4 × T <sub>OSC</sub>  |

| 0                                           | 1  | 6 × T <sub>OSC</sub>  |

| 1                                           | 0  | 12 × T <sub>OSC</sub> |

| 1                                           | 1  | $24 \times T_{OSC}$   |

For example, given the internal oscillator frequency,  $f_{OSC}$ , of 4 MHz (typ) ( $T_{OSC}$  = 250 ns), the blank time is adjustable from 1 to 6  $\mu$ s.

#### Synchronous Rectification

When a PWM-off cycle is triggered, either by an Enable chop command or an Internal PWM control mode Fixed Off-Time cycle, the load current recirculates according to the decay mode selected by the Configuration register settings. After a short crossover delay, the synchronous rectification feature turns-on the appropriate MOSFET (or pair of MOSFETs, for the Mixed Decay portion of the off-time) during the current decay and effectively shorts-out the body diodes with the low  $R_{\rm DS(on)}$  driver. This lowers power dissipation significantly and can eliminate the requirement for external Schottky diodes.

Synchronous rectification can be configured in active mode or passive mode via the serial port (word 0/1, D11):

- Active mode prevents reversal of load current by turning-off synchronous rectification when a zero current level is detected.

- Passive mode allows reversal of current, but turns-off synchronous rectification if the load current inversion ramps up to the I<sub>TRIP</sub> current limit (see equation 1).

**SLEEPN Pin** Active low input signal to reset serial port Configuration register and enter Standby mode. During Standby mode, the regulators can still operate.

# Dual DMOS Full Bridge Motor Driver With Serial Port Control and Dual Regulators

#### **Protection**

**Switching Regulator** The buck switch is disabled under the following fault conditions:

- $V_{BB} < V_{BBUV(th)}$

- $\bullet V_{CP} < V_{BB} + 5 V$

- · Thermal shutdown fault

**Thermal Protection** A thermal shutdown circuit turns-off all drivers and disables the switching regulator in the event of a fault due to excessive junction temperature. The serial port Configuration register is not reset.

Shutdown occurs when the junction temperature reaches T<sub>JSD</sub>, 165°C (typ). Thermal shutdown has a hysteresis, T<sub>JSDHYS</sub>, of approximately 20°C (typ). The outputs of the device remain disabled until the fault condition is removed.

**PMON Pin** Open drain output, logic high indicates  $V_{BB}$  is above the UVLO threshold.

**Undervoltage Lockout** At power-up, and in the event of low  $V_{\rm IN}$ , the UVLO circuit disables the drivers and the serial port Configuration register is reset to the default, POR state.

**OCP** When an overcurrent event is detected, the serial port Configuration register is reset to the default (POR) state. This

fault is latched and can only be reset by cycling the power to the A3998 (power-on reset, POR) or by cycling Standby mode (via the SLEEPN pin).

Note: An overcurrent fault event will not be generated during a shorted load condition if the blank time is programmed shorter than the  $t_{\rm OCP}$ . In this case, the overcurrent protection is still active, however, the internal current control circuit will operate as normal and terminate the source driver on-state upon completion of the blank time, before the OCP can trip the fault line and reset the serial port.

## **Power-On Reset**

FRST Pin Active high input signal forces reset (POR).

**RSTN Pin** An open drain output, RSTN will be low if either of following conditions are true:

- $V_{FB1} < V_{FBUV(th)}$

- · FRST high

If neither of the conditions are true, there will be a 100 ms delay before RSTN goes high. (See RST Function with FRST Input timing diagram.)

**Table 1. Configuration Register Bit Map**

| Bit #  | Function                                                                 | Reset (POR) Value |

|--------|--------------------------------------------------------------------------|-------------------|

| Word 0 |                                                                          | '                 |

| D0     | Bridge 1 Blank Time LSB                                                  | 0                 |

| D1     | Bridge 1 Blank Time MSB                                                  | 0                 |

| D2     | Bridge 1 Off Time LSB                                                    | 0                 |

| D3     | Bridge 1 Off Time Bit 1                                                  | 0                 |

| D4     | Bridge 1 Off Time Bit 2                                                  | 0                 |

| D5     | Bridge 1 Off Time Bit 3                                                  | 0                 |

| D6     | Bridge 1 Off Time MSB                                                    | 1                 |

| D7     | Bridge 1 Fast Decay LSB                                                  | 0                 |

| D8     | Bridge 1 Fast Decay Bit 1                                                | 0                 |

| D9     | Bridge 1 Fast Decay Bit 2                                                | 0                 |

| D10    | Bridge 1 Fast Decay MSB                                                  | 0                 |

| D11    | Bridge 1 Synchronous Rectification Control: 0 = Active 1 = Passive       | 0                 |

| D12    | Unused                                                                   | 0                 |

| D13    | Unused                                                                   | -                 |

| D14    | Word Select 0 = 0                                                        | -                 |

| D15    | Word Select 1 = 0                                                        | -                 |

| Word 1 |                                                                          |                   |

| D0     | Bridge 2 Blank Time LSB                                                  | 0                 |

| D1     | Bridge 2 Blank Time MSB                                                  | 0                 |

| D2     | Bridge 2 Off Time LSB                                                    | 0                 |

| D3     | Bridge 2 Off Time Bit 1                                                  | 0                 |

| D4     | Bridge 2 Off Time Bit 2                                                  | 0                 |

| D5     | Bridge 2 Off Time Bit 3                                                  | 0                 |

| D6     | Bridge 2 Off Time MSB                                                    | 1                 |

| D7     | Bridge 2 Fast Decay LSB                                                  | 0                 |

| D8     | Bridge 2 Fast Decay Bit 1                                                | 0                 |

| D9     | Bridge 2 Fast Decay Bit2                                                 | 0                 |

| D10    | Bridge 2 Fast Decay MSB                                                  | 0                 |

| D11    | Bridge 2 Synchronous Rectification Control:<br>0 = Active<br>1 = Passive | 0                 |

| D12    | Unused                                                                   | 0                 |

| D13    | Unused                                                                   | -                 |

| D14    | Word Select 0 = 1                                                        | -                 |

| D15    | Word Select 1 = 0                                                        | _                 |

Continued on the next page...

**Table 1. Configuration Register Bit Map (continued)**

| Bit #  | Function                                                                            | Reset (POR) Value |

|--------|-------------------------------------------------------------------------------------|-------------------|

| Word 2 |                                                                                     |                   |

| D0     | Bridge 2 Internal PWM Mode: 0 = Mixed decay mode 1 = Slow decay mode                | 0                 |

| D1     | Bridge 2 External PWM Mode (ENB2 chopping): 0 = Fast decay mode 1 = Slow decay mode | 0                 |

| D2     | Bridge 2 Phase                                                                      | 0                 |

| D3     | Bridge 2 DAC LSB (Current Ratio bit)                                                | 0                 |

| D4     | Bridge 2 DAC Bit 2 (Current Ratio bit)                                              | 0                 |

| D5     | Bridge 2 DAC Bit 3 (Current Ratio bit)                                              | 0                 |

| D6     | Bridge 2 DAC Bit 4 (Current Ratio bit)                                              | 0                 |

| D7     | Bridge 1 Internal PWM Mode: 0 = Mixed decay mode 1 = Slow decay mode                | 0                 |

| D8     | Bridge 1 External PWM Mode (ENB1 chopping): 0 = Fast decay mode 1 = Slow decay mode | 0                 |

| D9     | Bridge 1 Phase                                                                      | 0                 |

| D10    | Bridge 1 DAC LSB (Current Ratio bit)                                                | 0                 |

| D11    | Bridge 1 DAC Bit 2 (Current Ratio bit)                                              | 0                 |

| D12    | Bridge 1 DAC Bit 3 (Current Ratio bit)                                              | 0                 |

| D13    | Bridge 1 DAC Bit 4 (Current Ratio bit)                                              | 0                 |

| D14    | Word Select 0 = 0                                                                   | _                 |

| D15    | Word Select 1 = 1                                                                   | _                 |

Continued on the next page...

**Table 1. Configuration Register Bit Map (continued)**

| Bit #  | Function                                                                                                        | Reset (POR) Value |

|--------|-----------------------------------------------------------------------------------------------------------------|-------------------|

| Word 3 |                                                                                                                 |                   |

| D0     | Thermal Monitor:<br>0 = Normal function<br>$1 = \text{RSTN} = \text{thermal analog output}, \ V = K \times T_J$ | 0                 |

| D1     | Charge Pump: 0 = Normal Operation 1 = Disable Charge Pump                                                       | 0                 |

| D2     | Reserved For Test                                                                                               | 0                 |

| D3     | Reserved For Test                                                                                               | 0                 |

| D4     | Reserved For Test                                                                                               | 0                 |

| D5     | Reserved For Test                                                                                               | 0                 |

| D6     | Reserved For Test                                                                                               | 0                 |

| D7     | Reserved For Test                                                                                               | 0                 |

| D8     | Reserved For Test                                                                                               | 0                 |

| D9     | Reserved For Test                                                                                               | 0                 |

| D10    | Reserved For Test                                                                                               | 0                 |

| D11    | Reserved For Test                                                                                               | 0                 |

| D12    | Reserved For Test                                                                                               | 0                 |

| D13    | Reserved For Test                                                                                               | 0                 |

| D14    | Word Select 0 = 1                                                                                               | _                 |

| D15    | Word Select 1 = 1                                                                                               | _                 |

Table 2. Current Ratio Configuration\*

| DAC Bit 4 | DAC Bit 3 | DAC Bit 2 | DAC LSB | Current Ratio (%) |

|-----------|-----------|-----------|---------|-------------------|

| 1         | 1         | 1         | 1       | 100.0             |

| 1         | 1         | 1         | 0       | 95.65             |

| 1         | 1         | 0         | 1       | 91.30             |

| 1         | 1         | 0         | 0       | 86.95             |

| 1         | 0         | 1         | 1       | 82.61             |

| 1         | 0         | 1         | 0       | 78.26             |

| 1         | 0         | 0         | 1       | 73.91             |

| 1         | 0         | 0         | 0       | 69.56             |

| 0         | 1         | 1         | 1       | 60.87             |

| 0         | 1         | 1         | 0       | 52.17             |

| 0         | 1         | 0         | 1       | 43.48             |

| 0         | 1         | 0         | 0       | 34.78             |

| 0         | 0         | 1         | 1       | 26.08             |

| 0         | 0         | 1         | 0       | 17.39             |

| 0         | 0         | 0         | 1       | 0                 |

| 0         | 0         | 0         | 0       | Disabled          |

<sup>\*</sup>Internal PWM control mode selected

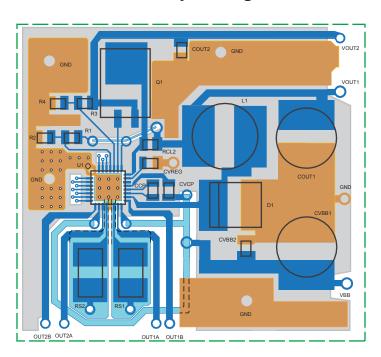

# **Application Information**

## **PCB Layout**

#### **Switcher**

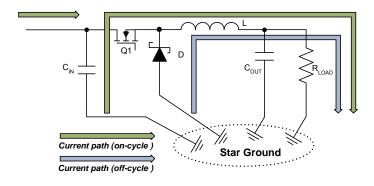

The board layout has a significant impact on the performance of the device. It is important to isolate high current ground returns, in order to minimize ground bounce that could produce reference errors in the device. The method used to isolate power ground from noise sensitive circuitry is a star ground. This approach makes sure the high current components such as the input capacitor, output capacitor, and diode have very low impedance paths to each other. Figure 5 illustrates the technique. The ground from each of the components should be very close to each other and be connected on the same surface as the components. Internal ground planes should not be used for the star ground connection, because vias add impedance to the current path. In order to further reduce noise effects on the PCB, noise sensitive traces should not be connected to internal ground planes.

The feedback network from the switcher output should have an independent ground trace that goes directly to the exposed pad underneath the device. The exposed pad should be connected to internal ground planes and to any exposed copper used for heat dissipation. If the grounds from the device also are connected directly to the exposed pad, the ground reference from the feedback network will be less susceptible to noise injection or ground bounce.

Figure 5. Star Ground Connection

To reduce radiated emissions from the high frequency switching nodes it is important to have an internal ground plane directly under the LX node. The plane should not be broken directly under the switching path because the lowest impedance path for radiated emissions is back to the star ground using the ground plane directly under the signal trace. If another trace does break the return path, the energy will have to find another path, which is through radiated emissions or through stray eddy currents.

#### **Motor Driver**

In order to use PWM current control, a low-value resistor is placed between the LSSx pin and ground for current sensing purposes. To minimize ground-trace IR drops in sensing the output current level, the current sensing resistor should have an independent ground return to the star ground point. This trace should be as short as possible. For low-value sense resistors, the IR drops in the PCB can be significant, and should be taken into account. When selecting a value for the sense resistor be sure not to exceed the maximum voltage on the SENSEx pin of ±500 mV at maximum load. During overcurrent events, this rating may be exceeded for short durations.

#### Thermal Considerations

The PCB should have a thick ground plane. For optimum electrical and thermal performance, the A3998 must be soldered directly onto the board. On the underside of the A3998 package is an exposed pad, which provides a path for enhanced thermal dissipation. The thermal pad must be soldered directly to an exposed surface on the PCB in order to achieve optimal thermal conduction. Thermal vias are used to transfer heat to other layers of the PCB. The load supply pin, VBB, should be decoupled with an electrolytic capacitor (typically 100  $\mu F$ ) in parallel with a lower valued ceramic capacitor placed as close as practicable to the device

#### **Switching Regulator Component Selection**

External component recommended values are provided in table 3.

**V<sub>OUT1</sub>** The regulator requires an external clamping diode, D1, inductor, L1, and filter capacitor, COUT1 (see figure 1).

The output voltage is determined by an external resistive voltage divider, according to the following formula:

$$V_{\text{OUT1}} = V_{\text{FB1}} \times (1 + R1 / R2)$$

(5)

# **PCB Layout Diagram**

# Dual DMOS Full Bridge Motor Driver With Serial Port Control and Dual Regulators

The total resistance from  $V_{OUT1}$  to FB1 to GND should be less than 10 k $\Omega$ .

**D1** The Schottky catch diode should be rated to handle 1.2 times the maximum load current. The voltage rating should be higher than the maximum input voltage expected during any operating condition. The duty cycle for high input voltages can be very close to 100%.

**L1** The inductor must be rated to handle the total load current and the value chosen must keep the ripple current to a reasonable value. The ripple current,  $I_R$ , can be calculated by:

$$I_{R} = V_{L(OFF)} \times (t_{OFF} / L)$$

(6)

where

$$V_{\text{L(OFF)}} = V_{\text{OUT1}} + V_{\text{f}} + I_{\text{av}} \times R_{\text{L}}$$

(7)

The switching frequency can then be estimated by:

$$f_{\text{PWM}} = 1 / (t_{\text{ON}} + t_{\text{OFF}})$$

where

$$t_{ON} = I_R \times L / V_{L(ON)}$$

and

$$V_{L(ON)} = V_{BB} - I_{av} \times R_{DS(on)} - I_{av} \times R_{L} - V_{OUT1}$$

(10)

Higher inductor values can be chosen to lower the ripple current. This may be an option if it is required to increase the total maximum current available that can be drawn from the switching regulator. The maximum total current available is:

$$I_{\text{LOAD(max)}} = I_{\text{CL}}(\text{min}) - I_{\text{R}} / 2 \tag{11}$$

Where I<sub>CL</sub>(min) is from the Electrical Characteristics table.

**COUT1** The output capacitor main consideration is voltage ripple on the output. For electrolytic output capacitors, a low ESR type is recommended. The peak to peak output ripple is simply:

$$I_{\text{R(pp)}} = I_{\text{R}} \times \text{ESR}$$

(12)

Note that the ripple current can be decreased by increasing the inductor value. The minimum voltage rating of the capacitor is 10 V, however, because ESR decreases with voltage, the most cost effective choice may be a higher rated voltage.

(9) V<sub>OUT2</sub> This output requires a 10 μF ceramic output capacitor, COUT2.

**Table 3. Recommended Components**

| Configuration   |                  | Component |                                             |                           |  |

|-----------------|------------------|-----------|---------------------------------------------|---------------------------|--|

| Output          | f <sub>PWM</sub> | Symbol    | Description                                 | Representative Component  |  |

| V <sub>OL</sub> | JT1x             |           |                                             |                           |  |

|                 |                  | L1        | 68 µH                                       | 3BSumida RCH1216BNP-680K  |  |

|                 |                  | COUT1     | 220 μF / 25 V, ESR = 72 mΩ                  | Rubycon ZL 25ZL220M8x11.5 |  |

| 5 V / 1 A       | 220 kHz          | D1        | 60 V / 3 A Schottky diode                   | NSQ03A06                  |  |

|                 |                  | R1        | 2 kΩ                                        |                           |  |

|                 |                  | R2        | 499 Ω                                       |                           |  |

| 3.3V/1A         |                  | L1        | 68 µH                                       | 4BSumida RCH1216BNP-680K  |  |

|                 | 230 kHz          | COUT1     | 220 μF / 25 V, ESR = 72 mΩ                  | Rubycon ZL 25ZL220M8x11.5 |  |

|                 |                  | D1        | 60 V / 3 A Schottky diode                   | Vishay SS36               |  |

|                 |                  | R1        | 2 kΩ                                        |                           |  |

|                 |                  | R2        | 866 Ω                                       |                           |  |

| V <sub>OL</sub> | JT2x             |           |                                             |                           |  |

|                 |                  | Q1        | External MOSFET - C <sub>gs</sub> < 1000 pF |                           |  |

|                 |                  | RSx       | Sense resistor                              |                           |  |

|                 |                  | COUT2     | 10 μF /10 V X5R                             |                           |  |

|                 |                  | R3, R4    |                                             |                           |  |

(8)

# Package ET, 32-Pin QFN

# A3998 Dual DMOS Full Bridge Motor Driver With Serial Port Control and Dual Regulators

Copyright ©2011-2013, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com