# **Silicon PNP Power Transistor**

### **Application:**

Intented for use in power linear and switching applications

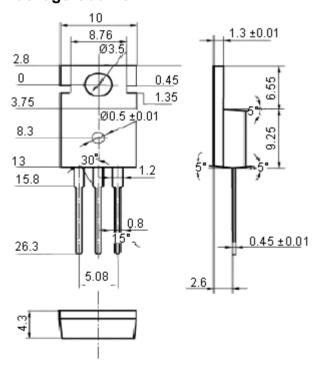

Fig. 1 Simplified Outline (TO-220C) and Symbol

### **Pinning**

| Pin | Description                           |  |

|-----|---------------------------------------|--|

| 1   | Emitter                               |  |

| 2   | Collector; connected to mounting base |  |

| 3   | Base                                  |  |

### Absolute Maximum Ratings $(T_a = 25^{\circ}C)$

| Symbol           | Parameter                   | Conditions            | Value      | Unit |

|------------------|-----------------------------|-----------------------|------------|------|

| $V_{CBO}$        | Collector - base voltage    | Open emitter          | -100       | V    |

| $V_{CEO}$        | Collector - emitter voltage | Open base             | -100       | V    |

| V <sub>EBO</sub> | Emitter - base voltage      | Open collector        | -5         | V    |

| I <sub>C</sub>   | Collector current           | -                     | -15        | Α    |

| I <sub>B</sub>   | Base current                | -                     | -5         | Α    |

| P <sub>C</sub>   | Collector power dissipation | T <sub>C</sub> ≤ 25°C | 90         | W    |

| T <sub>j</sub>   | Junction temperature        | -                     | 150        | °C   |

| T <sub>stg</sub> | Storage temperature         | -                     | -65 to 150 | °C   |

#### **Thermal Characteristics**

| Symbol              | Parameter                           | Maximum | Unit |

|---------------------|-------------------------------------|---------|------|

| R <sub>th j-c</sub> | Thermal resistance junction to case | 1.4     | °C/W |

## **Characteristics** ( $T_j = 25^{\circ}C$ Unless Otherwise Specified)

| Symbol                 | Parameter                              | Conditions                                      | Minimum | Typical | Maximum | Unit |

|------------------------|----------------------------------------|-------------------------------------------------|---------|---------|---------|------|

| V <sub>CEO (SUS)</sub> | Collector - emitter sustaining voltage | $I_{\rm C} = -0.1  \text{A};  I_{\rm B} = 0$    | -100    | -       | -       | V    |

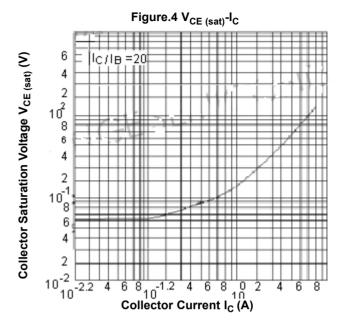

| V <sub>CEsat-1</sub>   | Collector - emitter saturation voltage | I <sub>C</sub> = -5 A; I <sub>B</sub> = 0.5 A   | -       | -       | -1      | V    |

| V <sub>CEsat-2</sub>   | Collector - emitter saturation voltage | I <sub>C</sub> = -10 A; I <sub>B</sub> = -2.5 A | -       | -       | -3      | V    |

www.element14.com www.farnell.com www.newark.com

# **Silicon PNP Power Transistor**

## **Characteristics** ( $T_j = 25^{\circ}C$ Unless Otherwise Specified)

| Symbol             | Parameter                         | Conditions                                                            | Minimum | Typical | Maximum    | Unit |

|--------------------|-----------------------------------|-----------------------------------------------------------------------|---------|---------|------------|------|

| V <sub>BEsat</sub> | Base - emitter saturation voltage | I <sub>C</sub> = -10 A; I <sub>B</sub> = -2.5 A                       | -       | -       | -2.5       | V    |

| V <sub>BE</sub>    | Base - emitter voltage            | I <sub>C</sub> = -5 A; V <sub>CE</sub> = -4 V                         | -       | -       | -1.5       | V    |

| I <sub>CBO</sub>   | Collector cut-off current         | $V_{CB} = -100 \text{ V}; I_{E} = 0$<br>$T_{C} = 150^{\circ}\text{C}$ | -       | -       | -0.5<br>-5 | mA   |

| I <sub>CEO</sub>   | Collector cut-off current         | $V_{CE} = -50 \text{ V}; I_{B} = 0$                                   | -       | -       | -1         | mA   |

| I <sub>EBO</sub>   | Emitter cut-off current           | V <sub>EB</sub> = -5 V; I <sub>C</sub> = 0                            | -       | -       | -1         | mA   |

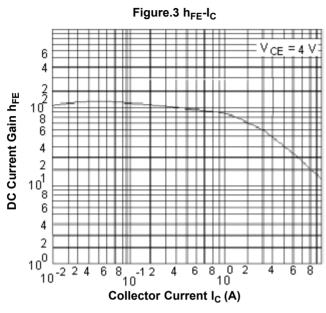

| h <sub>FE-1</sub>  | DC current gain                   | I <sub>C</sub> = -0.5 A; V <sub>CE</sub> = -4 V                       | 40      | -       | 250        | -    |

| h <sub>FE-2</sub>  | DC current gain                   | I <sub>C</sub> = -5 A; V <sub>CE</sub> = -4 V                         | 15      | -       | 150        | -    |

| h <sub>FE-3</sub>  | DC current gain                   | I <sub>C</sub> = -10 A; V <sub>CE</sub> = -4 V                        | 5       | -       | -          | -    |

| f <sub>T</sub>     | Transition frequency              | I <sub>C</sub> = -0.5 A; V <sub>CE</sub> = -4 V                       | 3       | -       | -          | MHz  |

### **Package Outline**

Dimensions: Millimetres

Fig. 2 Outline Dimensions (Unindicated Tolerance: ±0.1 mm)

## **Silicon PNP Power Transistor**

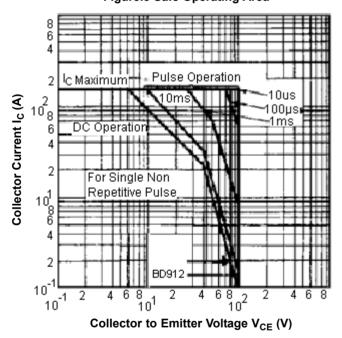

Figure.5 Safe Operating Area

#### **Part Number Table**

| Description                  | Part Number |  |  |

|------------------------------|-------------|--|--|

| Silicon PNP Power Transistor | BD912       |  |  |

Important Notice: This data sheet and its contents (the "Information") belong to the members of the Premier Farnell group of companies (the "Group") or are licensed to it. No licence is granted for the use of it other than for information purposes in connection with the products to which it relates. No licence of any intellectual property rights is granted. The Information is subject to change without notice and replaces all data sheets previously supplied. The Information supplied is believed to be accurate but the Group assumes no responsibility for its accuracy or completeness, any error in or omission from it or for any use made of it. Users of this data sheet should check for themselves the Information and the suitability of the products for their purpose and not make any assumptions based on information included or omitted. Liability for loss or damage resulting from any reliance on the Information or use of it (including liability resulting from negligence or where the Group was aware of the possibility of such loss or damage arising) is excluded. This will not operate to limit or restrict the Group's liability for death or personal injury resulting from its negligence. Multicomp is the registered trademark of the Group. © Premier Farnell plc 2011.