# 24-35 GHz GaAs MMIC High Power SPDT Reflective PIN Switch

#### AP640R7-00

#### **Features**

- Broad Bandwidth

- Low Loss, < 1.5 dB

- High Isolation, > 28 dB

- Return Loss, < -12 dB

- Fast Switching Speed, < 4 ns</p>

- High Power Handling, 40 dBm Peak, 36 dBm CW

### **Description**

Alpha's high power, single pole, double throw PIN diode switch is a robust, high performance switch. It is ideal for low loss, high isolation applications, particularly where broad bandwidths and high power handling is required. The chip uses Alpha's proven PIN diode technology, and is based upon MBE layers for the highest uniformity and repeatability. The diodes employ surface passivation to ensure a rugged, reliable part with through-substrate via holes and gold-based backside metallization to facilitate an epoxy die attach process. The GaAs MMIC employs a specialized high power PIN diode in each arm and an on-chip bias network. Chips are measured on a 100% basis at 24, 28, 31 and 35 GHz for insertion loss, isolation, input and output return losses, and also at DC for diode breakdown voltage and turn on voltage.

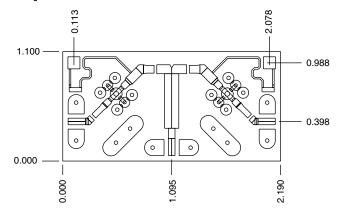

### **Chip Outline**

Dimensions indicated in mm. All pads are  $\geq 0.07$  mm wide. Chip thickness = 0.1 mm.

## **Absolute Maximum Ratings**

| Characteristic        | Value                     |  |

|-----------------------|---------------------------|--|

| Operating Temperature | -55°C to +125°C           |  |

| Storage Temperature   | mperature -65°C to +150°C |  |

| DC Reverse Bias       | -100 V (-20 mA)           |  |

| DC Forward Bias       | +2.6 V (100 mA)           |  |

| P <sub>IN</sub>       | 15 W                      |  |

## **Electrical Specifications at 25°C**

| Parameter                                         | Condition              | Symbol            | Min. | Typ. <sup>2</sup> | Max. | Unit |

|---------------------------------------------------|------------------------|-------------------|------|-------------------|------|------|

| Insertion Loss                                    | F = 24, 28, 31, 35 GHz | IL                |      | 1.2               | 1.5  | dB   |

| Isolation                                         | F = 24, 28, 31, 35 GHz | ISO               | 28   | 30                |      | dB   |

| Input Return Loss                                 | F = 24, 28, 31, 35 GHz | RL <sub>I</sub>   |      | 16                | 12   | dB   |

| Output Return Loss (Insertion State)              | F = 24, 28, 31, 35 GHz | RLO               |      | 17                | 14   | dB   |

| Leakage Current                                   | V = -50 V              | I <sub>DD</sub>   |      | 2                 | 20   | μΑ   |

| Switching Speed <sup>1</sup>                      |                        |                   |      | 4                 |      | ns   |

| Output Power at 1 dB Compression <sup>1</sup>     | F = 35 GHz             | P <sub>1 dB</sub> |      | 36                |      | dBm  |

| Two-Tone Input Third-Order Intercept <sup>1</sup> | F = 28 GHz             | IIP3              | 40   |                   |      | dBm  |

<sup>1.</sup> Not measured on a 100% basis.

<sup>2.</sup> Typical represents the median parameter value across the specified frequency range for the median chip.

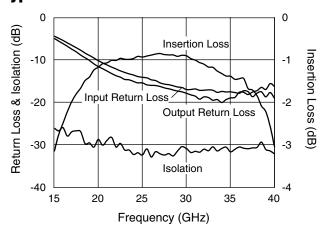

### **Typical Performance Data**

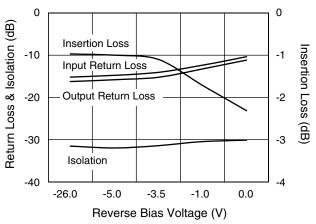

Performance vs. Frequency Bias Conditions:  $I_F = 20 \text{ mA}$ ,  $V_R = -3.5 \text{ V}$

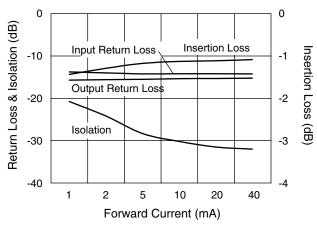

Performance vs. DC Bias F = 28 GHz, Reverse Voltage = -3.5 V

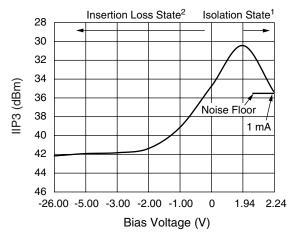

Performance vs. DC Bias F = 28 GHz, Forward Current = 20 mA

Two-Tone Input Third-Order Intercept @ 28 GHz

- 1. Isolation arms are biased with 10 mA (1.25 V) where IIP3 is below the noise floor.

- 2. Insertion loss arms are biased with -5 V where IIP3 is below the noise floor.

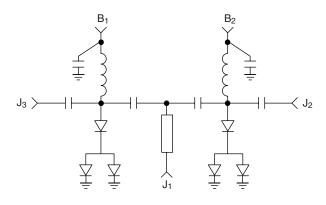

### **Truth Table**

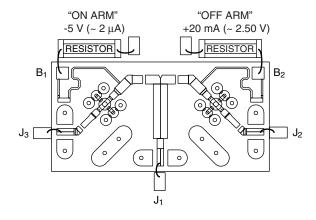

| B <sub>1</sub> | B <sub>2</sub> | J <sub>1</sub> –J <sub>2</sub> |

|----------------|----------------|--------------------------------|

| +20 mA         | -5 V           | Insertion Loss                 |

| -5 V           | +20 mA         | Isolation                      |

### **Circuit Schematic**

# **Bias Arrangement**