# DATA SHEET

| Part No.         | MN5B02UC        |

|------------------|-----------------|

| Package Code No. | TQFP048-P-0707B |

SEMICONDUCTOR COMPANY MATSUSHITA ELECTRIC INDUSTRIAL CO., LTD.

# **Panasonic**

## MN5B02UC

# Contents

| ■ Overview                             | 3  |

|----------------------------------------|----|

| ■ Features                             | 3  |

| ■ Applications                         | 3  |

| ■ Package                              | 3  |

| ■ Block Diagram                        |    |

| ■ Pin Arrangement                      | 5  |

| ■ Pin Descriptions                     |    |

| ■ Absolute Maximum Ratings             |    |

| ■ Recommended Operating Range          |    |

| ■ Input/output capacitance             | 8  |

| ■ Electrical Characteristics           | 9  |

| ■ Clock Generator (PLL) Characteristic | 10 |

MN5B02UC Panasonic

# MN5B02UC

## ICs for audio common use

#### Overview

• The MN5B02UC performs digital signal processing for 5.1-channel and 2-channel audio signals output from DVD, CD, MD, MP3, and other decoders to generate 3D playback with remarkable presence for output to stereo headphones.

• It offers 3 setting modes (Music, Cinema, Voice), allowing 3D effects to be configured to fit individual sources.

#### ■ Features

- 3D sound effect settings: Music, Cinema, Voice, (Down mix (3D sound effect: OFF))

- Sampling frequency: 48 kHz / 44.1 kHz

- Audio serial input: 5.1-ch. (L, C, R, LS, RS, LFE) / 2-ch. (L, R)

- Audio serial output: 2-ch. (L, R)

- External memory: Not necessary

- Microcontroller interface (Serial): Control register settings

- Parallel interface: Control register settings

- Internal operating frequency: Approx. 50 MHz (with external clock)

- External clock: 512 fs / 256 fs

- Power save mode: PLL clock stopped

- Power supply: 3.3 V (External I/O), 1.5 V (Internal circuit)

#### Applications

• Audio equipment, Portable DVD player, Headphone etc.

#### Package

• 48-pin TQFP (7 mm × 7 mm)

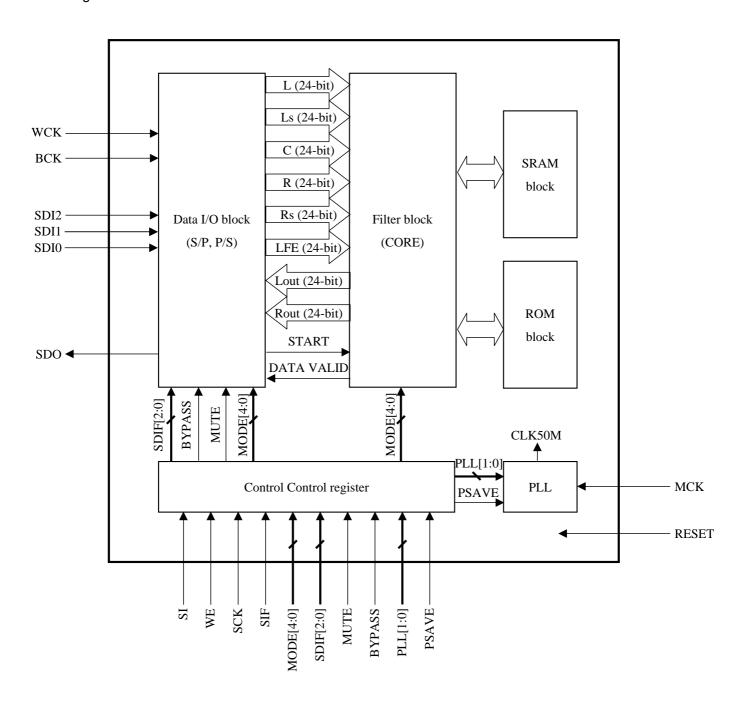

#### ■ Block Diagram

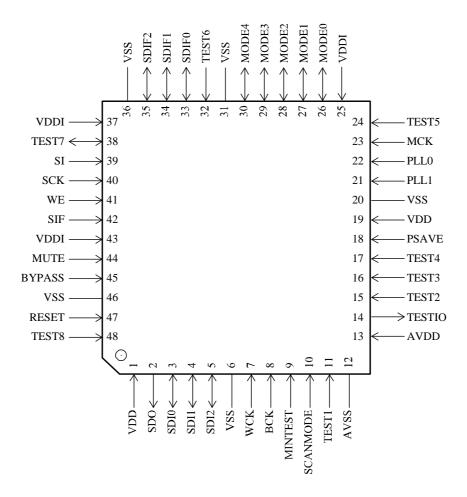

#### ■ Pin Arrangement

Note) All supply pins (VDD, VSS, VDDI, AVDD, AVSS) must be fixed. Connect MINTEST pin VSS.

# ■ Pin Descriptions

| Block                            | Pin<br>No. | Symbol           | I/O | Description                                                           |

|----------------------------------|------------|------------------|-----|-----------------------------------------------------------------------|

|                                  | 7          | WCK              | I   | Word clock for audio data input                                       |

|                                  | 8          | BCK              | I   | Bit clock for audio data I/O                                          |

| Audio output                     | 3          | SDI0             | I   | Audio data serial input (L, R)                                        |

|                                  | 4          | SDI1             | I   | Audio data serial input (LS, RS)                                      |

|                                  | 5          | SDI2             | I   | Audio data serial input (C, LFE)                                      |

| Audio output                     | 2          | SDO              | О   | Audio data serial output (L, R)                                       |

|                                  | 40         | SCK              | I   | Serial data I/O clock                                                 |

| Serial microcontroller interface | 39         | SI               | I   | Control register data input                                           |

|                                  | 41         | WE               | I   | Write enable (low active)                                             |

|                                  | 42         | SIF              | I   | Serial (low) / parallel (high) interface selection                    |

|                                  | 30         | MODE4            | I   |                                                                       |

|                                  | 29         | MODE3            | I   | Operating mode setting • 3D sound effect (Music, Cinema, Voice, (Down |

|                                  | 28         | MODE2            | I   | mix)) • Number of input channels                                      |

|                                  | 27         | MODE1            | I   | Sampling frequency                                                    |

|                                  | 26         | MODE0            | I   |                                                                       |

|                                  | 35         | SDIF2            | I   |                                                                       |

| Parallel interface               | 34         | SDIF1            | I   | Audio data I/O format setting                                         |

|                                  | 33         | SDIF0            | I   |                                                                       |

|                                  | 44         | MUTE             | I   | L, R output signal mute setting (high: mute ON)                       |

|                                  | 45         | BYPASS           | I   | L, R input bypass output setting (high: bypass ON)                    |

|                                  | 18         | PSAVE            | I   | Power save pin (low: PLL clock stopped)                               |

|                                  | 21         | PLL1             | I   |                                                                       |

|                                  | 22         | PLL0             | I   | PLL clock selection pin                                               |

| PLL                              | 23         | MCK              | I   | Operating clock input pin                                             |

| Reset                            | 47         | RESET            | I   | System reset (low: reset ON)                                          |

|                                  | 1          | V <sub>DD</sub>  | _   | +3.3 V external supply voltage                                        |

|                                  |            | V <sub>DD</sub>  | _   | +3.3 V external supply voltage                                        |

| D 1                              | 25         | V <sub>DDI</sub> | _   | +1.5 V internal supply voltage                                        |

| Power supply                     |            | V <sub>DDI</sub> | _   | +1.5 V internal supply voltage                                        |

|                                  |            | V <sub>DDI</sub> | _   | +1.5 V internal supply voltage                                        |

|                                  | 13         | $AV_{DD}$        | _   | +3.3 V external supply voltage (PLL)                                  |

**Panasonic**

# ■ Pin Descriptions (continued)

| Block  | Pin<br>No. | Symbol          | I/O | Description                  |

|--------|------------|-----------------|-----|------------------------------|

|        |            | V <sub>SS</sub> | _   | Ground                       |

| Ground | 20         | $V_{SS}$        |     | Ground                       |

|        | 31         | $V_{SS}$        |     | Ground                       |

|        | 36         | $V_{SS}$        | _   | Ground                       |

|        | 46         | $V_{SS}$        | _   | Ground                       |

|        | 12         | $AV_{SS}$       | _   | Ground (PLL)                 |

|        | 9          | MINTEST         | I   | Test pin (Connect to ground) |

|        | 10         | SCANMODE        | I   | Test pin (Connect to ground) |

|        | 11         | TEST1           | I   | Test pin (Connect to ground) |

|        | 14         | TESTIO          | О   | Test pin (Not connected)     |

|        | 15         | TEST2           | I   | Test pin (Connect to ground) |

| Test   | 16         | TEST3           | I   | Test pin (Connect to ground) |

|        | 17         | TEST4           | I   | Test pin (Connect to ground) |

|        | 24         | TEST5           | I   | Test pin (Connect to ground) |

|        | 32         | TEST6           | I   | Test pin (Connect to ground) |

|        | 38         | TEST7           | I/O | Test pin (Not connected)     |

|        | 48         | TEST8           | I   | Test pin (Connect to ground) |

## $\blacksquare \ \, \text{Absolute Maximum Ratings} \quad \, V_{SS} = AV_{SS} = \, 0 \, \, V$

|     | Parameter                  | Parameter |                                                       | Rating                                             | Unit                                                               |               |   |  |

|-----|----------------------------|-----------|-------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|---------------|---|--|

| A1  | External supply voltage *  |           | E                                                     |                                                    | $V_{\mathrm{DD}}$                                                  | - 0.3 to +4.6 | V |  |

| A2  |                            |           | $AV_{DD}$                                             | - 0.3 to +4.6                                      | V                                                                  |               |   |  |

| A3  | Internal supply voltag     | ge *      | $V_{\mathrm{DDI}}$                                    | - 0.3 to +2.0                                      | V                                                                  |               |   |  |

| A4  |                            |           | ·                                                     |                                                    | $V_{\rm I} = -0.3 \text{ to } V_{\rm DD} + 0.3 \text{ (max. 4.6)}$ |               | V |  |

| A5  | Input voltage              |           | $V_{IA}$                                              | $-0.3 \text{ to AV}_{DD} + 0.3 \text{ (max. 4.6)}$ | v                                                                  |               |   |  |

| A6  | Output voltage             |           | $V_{\rm O}$ = $-0.3$ to $V_{\rm DD} + 0.3$ (max. 4.6) |                                                    | V                                                                  |               |   |  |

| A7  | Outmut ourment             | TYPE-HL2  | т                                                     | ±6                                                 | A                                                                  |               |   |  |

| A8  | Output current             | TYPE-HL4  | $I_{O}$                                               | ±12                                                | mA                                                                 |               |   |  |

| A9  | Input current power supply |           | $I_{V}$                                               | ±70 / pin                                          | mA                                                                 |               |   |  |

| A10 | Power dissipation          |           | $P_{D}$                                               | 410                                                | mW                                                                 |               |   |  |

| A11 | A11 Operating temperature  |           | $T_{\mathrm{opr}}$                                    | -30 to +85                                         | °C                                                                 |               |   |  |

| A12 | Storage temperature        |           | $T_{stg}$                                             | -50 to +150                                        | °C                                                                 |               |   |  |

Note) 1. TYPE-HL2: BCK, SDI0 to SDI2, MODE0 to MODE4, SDIF0 to SDIF2 TYPE-HL4: SDO

- 2. The max. and min. limits define the range within which the chip is safe. However the chip is not guaranteed to operate at the boundary conditions.

- 3. All power supply pins are connected directly to each power units or ground.

- 4. MINTEST pin are connected to  $\boldsymbol{V}_{\text{SS}}$  .

- 5.\*: In case of either  $V_{DD}$  or  $V_{DDI}$  is off, output turn out unfixed condition by flow-through current. There is no regulations connected with power on/off  $(V_{DD}$ ,  $V_{DDI})$  sequence. But please power on  $(V_{DD}$ ,  $V_{DDI})$  at the same time.

## $\blacksquare$ Recommended Operating Range $V_{SS} = AV_{SS} = 0 V$

| Parameter |                          | Symbol           | Conditions |      | Unit |      |       |

|-----------|--------------------------|------------------|------------|------|------|------|-------|

|           | Parameter                |                  | Conditions | Min  | Тур  | Max  | Offic |

| B1        | External complex voltage | $V_{DD}$         |            | 3.0  | 3.3  | 3.6  | V     |

| B2        | External supply voltage  | AV <sub>DD</sub> |            | 3.0  | 3.3  | 3.6  | V     |

| В3        | Internal supply voltage  | V <sub>DDI</sub> |            | 1.35 | 1.5  | 1.65 | V     |

| B4        | Ambient temperature      | T <sub>a</sub>   |            | -30  |      | 85   | °C    |

| В5        | Input rise time          | t <sub>r</sub>   |            | 0    |      | 80   | ns    |

| В6        | Input fall time          | $r_{\rm f}$      |            | 0    |      | 80   | ns    |

#### ■ Input/output capacitance

| Parameter |                 | Cymhal           | Conditions                                                            | Limits |     |     | Lloit |

|-----------|-----------------|------------------|-----------------------------------------------------------------------|--------|-----|-----|-------|

|           |                 | Symbol           | Conditions                                                            | Min    | Тур | Max | Unit  |

| C1        | Input terminal  | C <sub>IN</sub>  |                                                                       |        | 5   | 7   | pF    |

| C2        | Output terminal | C <sub>OUT</sub> | $V_{DD} = V_{DDI} = AV_{DD} = V_I = 0 V,$<br>$f = 1 MHz, T_a = 25$ °C |        | 5   | 7   | pF    |

| С3        | I/O terminal    | C <sub>IO</sub>  |                                                                       |        | 5   | 7   | pF    |

#### ■ Electrical Characteristics

$V_{DD} = 3.0 \ V \ to \ 3.6 \ V, \ AV_{DD} = 3.0 \ V \ to \ 3.6 \ V, \ V_{DDI} = 1.35 \ V \ to \ 1.65 \ V, \ V_{SS} = 0 \ V, \ AV_{SS} = 0 \ V, \ f_{TEST} = 56 \ MHz, \ T_a = -30 ^{\circ}C \ to \ +85 ^{\circ}C$

| Parameter |                             | Cymhal             | Conditions                                                                                                                                                                                                                                                                                                    |                       | Limits   |                     | Lloit |

|-----------|-----------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|---------------------|-------|

|           | Parameter                   | Symbol             | Conditions                                                                                                                                                                                                                                                                                                    | Min                   | Тур      | Max                 | Unit  |

| D1        | Static supply current       | $I_{ m DDS}$       | $\begin{aligned} &V_{I} \text{ (pull up)} = \text{Open,} \\ &V_{I} \text{ (pull down)} = \text{Open,} \\ &\text{Input pins and bi-directional pins} \\ &\text{in the Hi-Z state are} \\ &\text{simultaneously connected to} \\ &\text{either } V_{DD} \text{ or } V_{SS} \text{ input levels.} \end{aligned}$ |                       |          | 20                  | mA    |

| D2        | Operating power consumption | $P_{\mathrm{DDO}}$ | $\begin{split} &V_{I}=V_{DD} \text{ or } V_{SS} \text{ , } f=56 \text{ MHz,} \\ &V_{DD}=3.3 \text{ V, } AV_{DD}=3.3 \text{ V,} \\ &V_{DDI}=1.5 \text{ V,} \\ &External \text{ load}=65 \text{ pF output} \\ &\text{open} \end{split}$                                                                         |                       | 85       | 170                 | mW    |

| Input     | LVCMOS level: SI, WE, MCI   | K, PLL0, F         | PLL1, SCK, SIF, WCK, MUTE, PS                                                                                                                                                                                                                                                                                 | SAVE, BYPAS           | SS, RESE | T, BCK              |       |

| D3        | Input voltage high level    | $V_{IH}$           |                                                                                                                                                                                                                                                                                                               | $V_{DD} \times 0.7$   |          | V <sub>DD</sub>     | V     |

| D4        | Input voltage low level     | V <sub>IL</sub>    |                                                                                                                                                                                                                                                                                                               | 0                     |          | $V_{DD} \times 0.3$ | V     |

| D5        | Input leakage current       | $I_{LI}$           | $V_{\rm I} = V_{\rm DD}$ or $V_{\rm SS}$                                                                                                                                                                                                                                                                      |                       |          | ±5                  | μΑ    |

| Input     | LVCMOS level with pull-dow  | n resistor         | : MINTEST, TEST1 to TEST6, SC                                                                                                                                                                                                                                                                                 | CANMODE, T            | EST8     |                     |       |

| D6        | Input voltage high level    | $V_{IH}$           |                                                                                                                                                                                                                                                                                                               | $V_{DD} \times 0.7$   |          | V <sub>DD</sub>     | V     |

| D7        | Input voltage low level     | $V_{IL}$           |                                                                                                                                                                                                                                                                                                               | 0                     |          | $V_{DD} \times 0.3$ | V     |

| D8        | Pull-down resistor          | $R_{IL}$           | $V_{\rm I} = V_{\rm DD}$                                                                                                                                                                                                                                                                                      | 10                    | 30       | 90                  | kΩ    |

| D9        | Input leakage current       | I <sub>LIL</sub>   | $V_{I} = V_{SS}$                                                                                                                                                                                                                                                                                              |                       |          | ±10                 | μΑ    |

| Outpu     | ut pushpull: SDO            | •                  |                                                                                                                                                                                                                                                                                                               |                       |          |                     |       |

| D10       | Output voltage high level   | V <sub>OH</sub>    | $I_{OH} = -4.0 \text{ mA}, V_I = V_{DD} \text{ or } V_{SS}$                                                                                                                                                                                                                                                   | V <sub>DD</sub> - 0.6 |          |                     | V     |

| D11       | Output voltage low level    | V <sub>OL</sub>    | $I_{OL} = 4.0 \text{ mA}, V_{I} = V_{DD} \text{ or } V_{SS}$                                                                                                                                                                                                                                                  |                       |          | 0.4                 | V     |

| Input/    | output LVCMOS level: SDI0   | to SDI2, I         | MODE0 to MODE4, SDIF0 to SDI                                                                                                                                                                                                                                                                                  | F2                    |          |                     |       |

| D12       | Input voltage high level    | V <sub>IH</sub>    |                                                                                                                                                                                                                                                                                                               | $V_{DD} \times 0.7$   |          | V <sub>DD</sub>     | V     |

| D13       | Input voltage low level     | V <sub>IL</sub>    |                                                                                                                                                                                                                                                                                                               | 0                     |          | $V_{DD} \times 0.3$ | V     |

| D14       | Output voltage high level   | V <sub>OH</sub>    | $I_{OH} = -2.0 \text{ mA}, V_I = V_{DD} \text{ or } V_{SS}$                                                                                                                                                                                                                                                   | $V_{DD} - 0.6$        |          |                     | V     |

| D15       | Output voltage low level    | V <sub>OL</sub>    | $I_{OL} = 2.0 \text{ mA}, V_I = V_{DD} \text{ or } V_{SS}$                                                                                                                                                                                                                                                    |                       |          | 0.4                 | V     |

| D16       | Output leakage current      | $I_{LO}$           | $V_{O} = \text{Hi-Z}, V_{I} = V_{DD} \text{ or } V_{SS}$ , $V_{O} = V_{DD} \text{ or } V_{SS}$                                                                                                                                                                                                                |                       |          | ±5                  | μΑ    |

MN5B02UC Panasonic

#### ■ Electrical Characteristics (continued)

$V_{DD} = 3.0 \text{ V}$  to 3.6 V,  $AV_{DD} = 3.0 \text{ V}$  to 3.6 V,  $V_{DDI} = 1.35 \text{ V}$  to 1.65 V,  $V_{SS} = 0 \text{ V}$ ,  $AV_{SS} = 0 \text{ V}$ ,  $f_{TEST} = 56 \text{ MHz}$ ,  $T_a = -30 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$

| Parameter |                                                          | Symbol            | Conditions                                                            |                     | Unit |                     |       |

|-----------|----------------------------------------------------------|-------------------|-----------------------------------------------------------------------|---------------------|------|---------------------|-------|

|           |                                                          | Symbol            | Conditions                                                            | Min                 | Тур  | Max                 | Offic |

| Input/    | Input/output LVCMOS level with pull-down resistor: TEST7 |                   |                                                                       |                     |      |                     |       |

| D17       | Input voltage high level                                 | $V_{\mathrm{IH}}$ |                                                                       | $V_{DD} \times 0.7$ |      | $V_{\mathrm{DD}}$   | V     |

| D18       | Input voltage low level                                  | V <sub>IL</sub>   |                                                                       | 0                   |      | $V_{DD} \times 0.3$ | V     |

| D19       | Output voltage high level                                | V <sub>OH</sub>   | $I_{OH} = -2.0 \text{ mA}, V_I = V_{DD} \text{ or } V_{SS}$           | $V_{DD} - 0.6$      |      |                     | V     |

| D20       | Output voltage low level                                 | V <sub>OL</sub>   | $I_{OL} = 2.0 \text{ mA}, V_{I} = V_{DD} \text{ or } V_{SS}$          |                     |      | 0.4                 | V     |

| D21       | Pull-down resistor                                       | $R_{\rm IL}$      | $V_{I} = V_{DD}$                                                      | 10                  | 30   | 90                  | kΩ    |

| D22       | Output leakage current                                   | $I_{LOL}$         | $V_O = Pull-down,$<br>$V_I = V_{DD} \text{ or } V_{SS}, V_O = V_{SS}$ |                     |      | ±10                 | μΑ    |

#### ■ Clock Generator (PLL) Characteristic

$V_{DD} = 3.3 \text{ V}, \text{ AV}_{DD} = 3.3 \text{ V}, \text{ V}_{DDI} = 1.50 \text{ V}, \text{ V}_{SS} = 0 \text{ V}, \text{ AV}_{SS} = 0 \text{ V}, \text{ T}_a = 25^{\circ}\text{C}$

| Parameter |                  | Cymbol            | Conditions |     | - Unit |     |       |  |

|-----------|------------------|-------------------|------------|-----|--------|-----|-------|--|

|           | Parameter        | Symbol Conditions |            | Min | Тур    | Max | Offic |  |

| E1        | Input frequency  | $f_{IN1}$         |            |     | 25     |     | MHz   |  |

| E2        | Output frequency | F <sub>OUT1</sub> | ×4         |     | 100    |     | MHz   |  |

| E3        | Input frequency  | $f_{IN2}$         |            |     | 12.5   |     | MHz   |  |

| E4        | Output frequency | F <sub>OUT2</sub> | ×8         |     | 100    |     | MHz   |  |

| E5        | Input frequency  | f <sub>IN3</sub>  |            |     | 19     |     | MHz   |  |

| E6        | Output frequency | F <sub>OUT3</sub> | ×6         |     | 114    |     | MHz   |  |

Note) Pin name: TESTIO a0nalog bi-direction pin

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products, and no license is granted under any intellectual property right or other right owned by our company or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd. Industrial Co., Ltd.