## MIC3002

### FOM Management IC with Internal Calibration

#### General Description

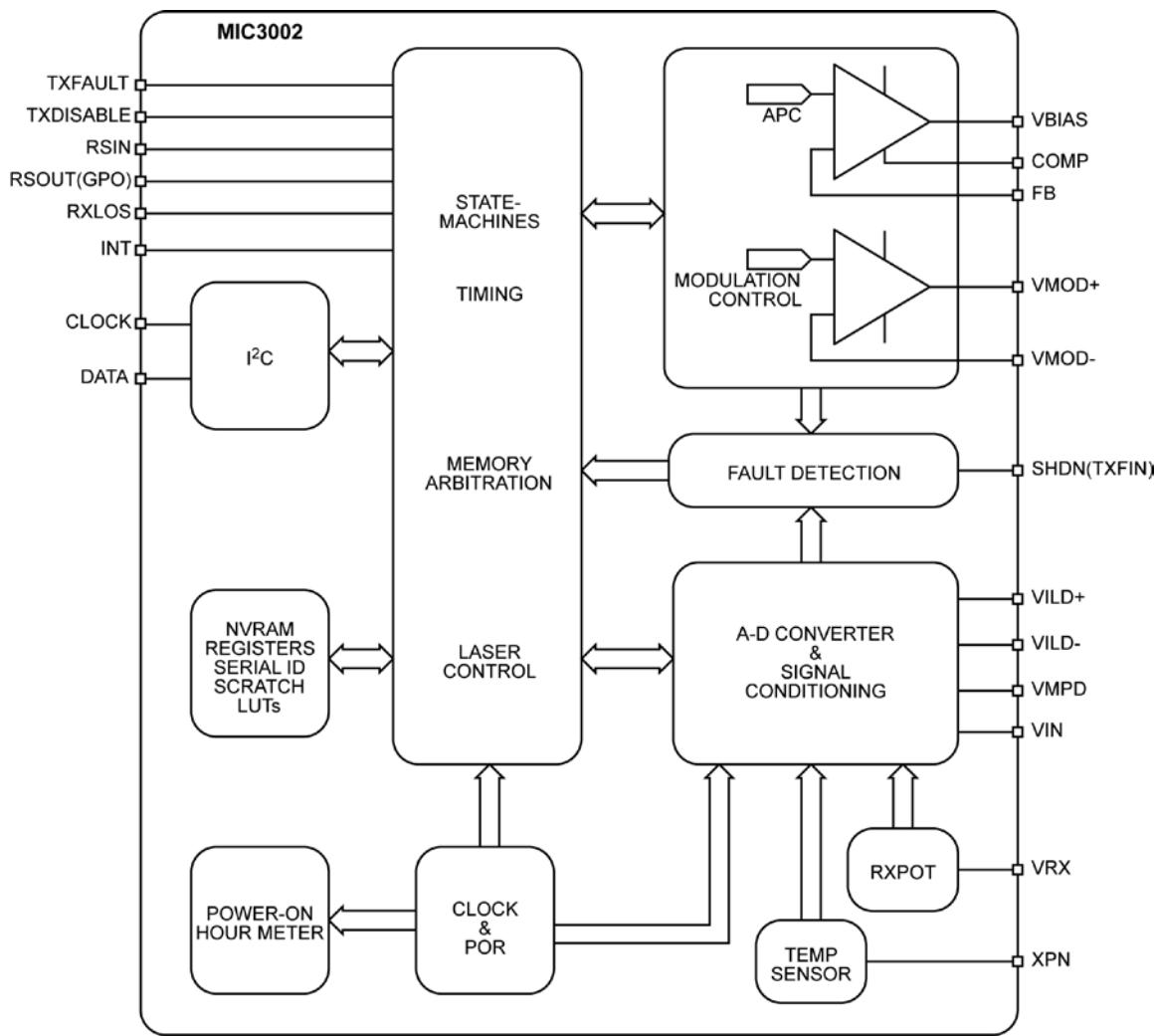

The MIC3002 is a fiber optic module controller which enables the implementation of sophisticated, hot-pluggable fiber optic transceivers with intelligent laser control and an internally calibrated Digital Diagnostic Monitoring Interface per SFF-8472. It essentially integrates all non-datapath functions of an SFP transceiver into a tiny (4mm x 4mm) QFN package. It also works well as a microcontroller peripheral in transponders or 10Gbps transceivers.

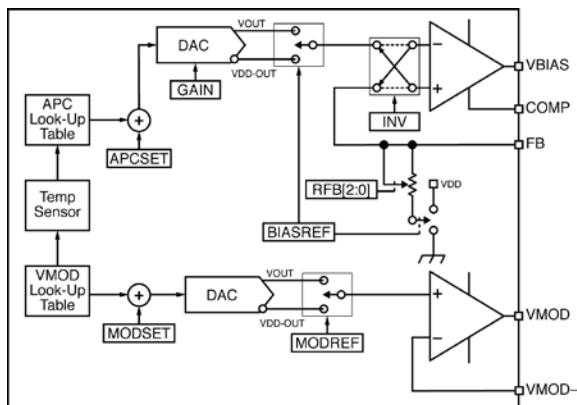

A highly configurable automatic power control (APC) circuit controls laser bias. Bias and modulation are temperature compensated using dual DACs, an on-chip temperature sensor, and NVRAM look-up tables. A programmable internal feedback resistor provides a wide dynamic range for the APC. Controlled laser turn-on facilitates hot plugging.

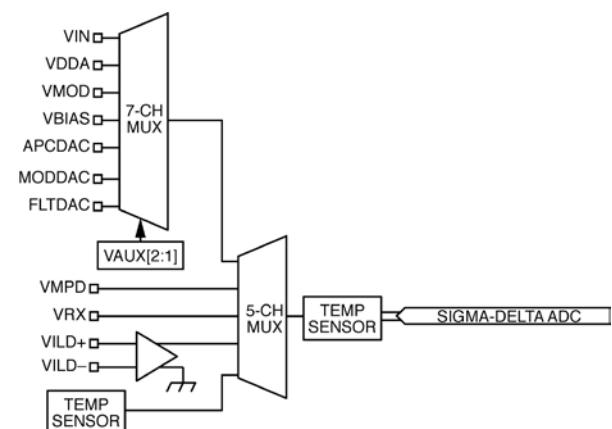

An analog-to-digital converter converts the measured temperature, voltage, bias current, transmit power, and received power from analog to digital. An EEPOT provides front-end adjustment of RX power. Each parameter is compared against user-programmed warning and alarm thresholds. Analog comparators and DACs provide high-speed monitoring of received power and critical laser operating parameters. Data can be reported as either internally calibrated or externally calibrated.

An interrupt output, power-on hour meter, and data-ready bits add user friendliness beyond SFF-8472. The interrupt output and data-ready bits reduce overhead in the host system. The power-on hour meter logs operating hours using an internal real-time clock and stores the result in NVRAM.

In addition to the features listed above which are already implemented in the previous controller MIC3001, the MIC3002 features an extensive temperature range, options to mask alarms and warnings interrupt and TXFAULT, and ability to support up to four chips with the same address on the serial interface.

Communication with the MIC3002 is via an industry standard 2-wire serial interface. Nonvolatile memory is provided for serial ID, configuration, and separate OEM and user scratchpad spaces. Two-level password protection guards against data corruption.

#### Features

- Extensive temperature range

- Alarms and Warnings interrupt and TXFAULT masks

- Capability to support up to four chips on the serial interface

- LUT to compensate for chip-FOM case temperature difference

- APC or constant-current laser bias

- Turbo mode for APC loop start-up and shorter laser turn on time

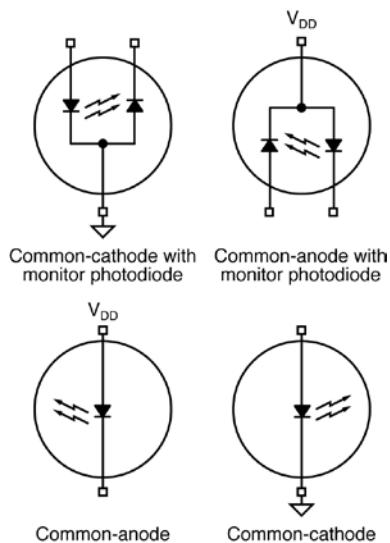

- Supports multiple laser types and bias circuit topologies

- Integrated digital temperature sensor

- Temperature compensation of modulation, bias, and fault levels via NVRAM look-up tables

- NVRAM to support GBIC/SFP serial ID function

- User writable EEPROM scratchpad

- Diagnostic monitoring interface per SFF-8472

- Monitors and reports critical parameters: temperature, bias current, TX and RX optical power, and supply voltage

- S/W control and monitoring of TXFAULT, RXLOS, RATESELECT, and TXDISABLE

- Internal or external calibration

- EEPOT for adjusting RX power measurement

- Power-on hour meter

- Interrupt capability

- Extensive test and calibration features

- 2-wire SMBus-compatible serial interface

- SFP/SFP+ MSA and SFF-8472 compliant

- 3.0V to 3.6V power supply range

- 5V-tolerant I/O

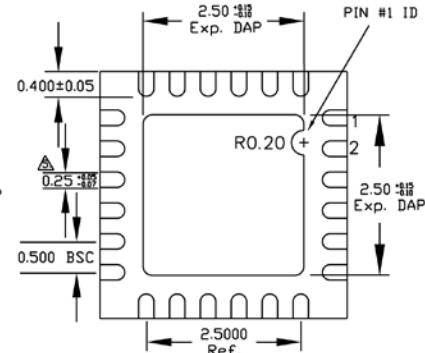

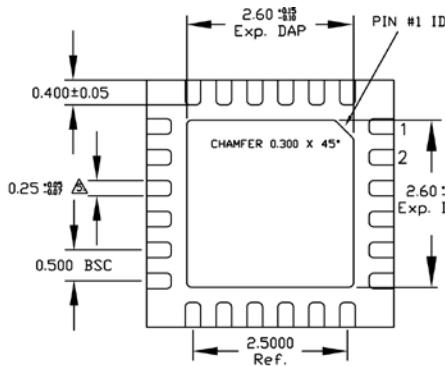

- Available in (4mm x 4mm) 24-pin QFN package

#### Applications

- SFP/SFP+ optical transceivers

- SONET/SDH transceivers and transponders

- Fibre Channel transceivers

- 10Gbps transceivers

- Free space optical communications

- Proprietary optical links

## Ordering Information

| Part Number                 | Package Type | Junction Temp. Range | Package Marking                         | Lead Finish       |

|-----------------------------|--------------|----------------------|-----------------------------------------|-------------------|

| MIC3002BML                  | 24-pin QFN   | –45°C to +105°C      | 3002                                    | Sn-Pb             |

| MIC3002BMLTR <sup>(1)</sup> | 24-pin QFN   | –45°C to +105°C      | 3002                                    | Sn-Pb             |

| MIC3002GML                  | 24-pin QFN   | –45°C to +105°C      | 3002<br>with Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

| MIC3002GMLTR <sup>(1)</sup> | 24-pin QFN   | –45°C to +105°C      | 3002<br>with Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

1. Note:

2. Tape and Reel.

## Contents

|                                                    |    |

|----------------------------------------------------|----|

| Pin Configuration.....                             | 7  |

| Pin Description .....                              | 7  |

| Absolute Maximum Ratings .....                     | 9  |

| Operating Ratings .....                            | 9  |

| Electrical Characteristics.....                    | 9  |

| Timing Diagram.....                                | 14 |

| Address Map .....                                  | 15 |

| Block Diagram .....                                | 18 |

| Analog-to-Digital Converter/Signal Monitoring..... | 18 |

| Temperature Reading Compensation.....              | 19 |

| Alarms and Warnings Interrupt Source Masking ..... | 20 |

| Alarms and Warnings as TXFAULT Source .....        | 21 |

| Alarms and Warnings Latch.....                     | 21 |

| SMBus Multipart Support .....                      | 21 |

| Calibration Modes .....                            | 22 |

| A/ External Calibration.....                       | 22 |

| Voltage.....                                       | 22 |

| Temperature .....                                  | 22 |

| Bias Current.....                                  | 22 |

| TX Power .....                                     | 22 |

| RX Power.....                                      | 23 |

| B/ Internal Calibration .....                      | 23 |

| Temperature Offset.....                            | 25 |

| C/ ADC Result Registers Reading.....               | 25 |

| RXPOT .....                                        | 25 |

| Laser Diode Bias Control .....                     | 25 |

| Laser Modulation Control .....                     | 26 |

| Power ON and Laser Start-Up .....                  | 27 |

| Fault Comparators .....                            | 28 |

| SHDN and TXFIN.....                                | 29 |

| Temperature Measurement.....                       | 29 |

| Diode Faults .....                                 | 29 |

| Temperature Compensation .....                     | 29 |

| Alarms and Warning Flags .....                     | 32 |

| Control and Status I/O.....                        | 32 |

| System Timing.....                                 | 34 |

| Warm Resets.....                                   | 36 |

| Power-On Hour Meter .....                          | 36 |

| Test and Calibration Features .....                | 37 |

| Serial Port Operation.....                         | 38 |

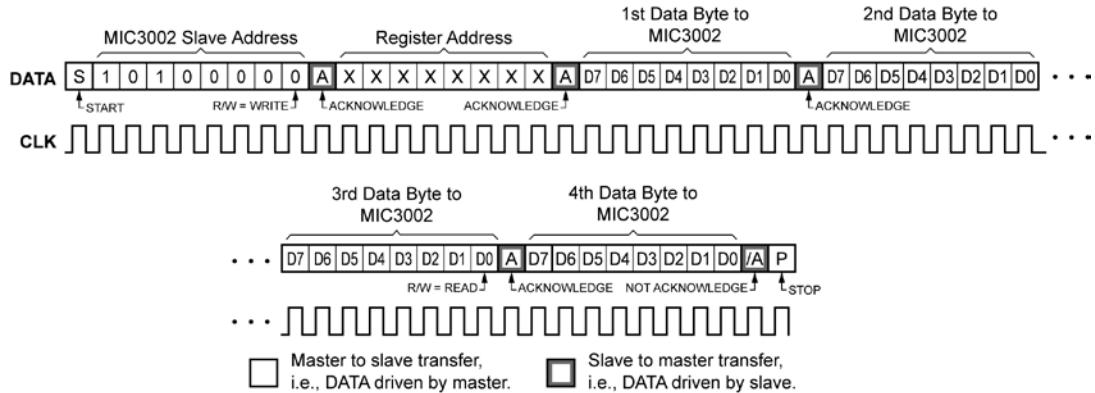

| Page Writes.....                                   | 38 |

| Acknowledge Polling.....                           | 39 |

| Write Protection and Data Security .....           | 39 |

| OEM Password.....                                  | 39 |

| User Password.....                                 | 39 |

---

|                                                            |    |

|------------------------------------------------------------|----|

| Detailed Register Descriptions.....                        | 40 |

| Alarm Threshold Registers.....                             | 40 |

| Warning Threshold Registers.....                           | 43 |

| ADC Result Registers .....                                 | 45 |

| Alarm Flags .....                                          | 48 |

| Warning Flags .....                                        | 49 |

| Warning Status Register 0 (WARN0).....                     | 49 |

| Warning Status Register 1 (WARN1).....                     | 49 |

| OEM Password Entry (OEMPW) .....                           | 50 |

| USER Password Setting (USRPWSET) .....                     | 50 |

| USER Password (USRPW).....                                 | 51 |

| Power-On Hours .....                                       | 51 |

| Data Ready Flags (DATARDY).....                            | 51 |

| USER Control Register (USRCTL) .....                       | 52 |

| OEM Configuration Register 0 (OEMCFG0).....                | 52 |

| OEM Configuration Register 1 (OEMCFG1).....                | 53 |

| OEM Configuration Register 2 (OEMCFG2).....                | 54 |

| APC Setpoint x .....                                       | 54 |

| Modulation Setpoint x .....                                | 54 |

| I <sub>BIAS</sub> Fault Threshold (IBFLT).....             | 55 |

| Transmit Power Fault Threshold (TXFLT) .....               | 55 |

| Loss-Of-Signal Threshold (LOSFLT) .....                    | 55 |

| Fault Suppression Timer (FLTTMR) .....                     | 55 |

| Fault Mask (FLTMSK) .....                                  | 56 |

| OEM Password Setting (OEMPWSET) .....                      | 56 |

| OEM Calibration 0 (OEMCAL0) .....                          | 57 |

| OEM Calibration 1 (OEMCAL1) .....                          | 57 |

| OEM Calibration 1 (LUT Index).....                         | 58 |

| OEM Configuration 3 (OEMCFG3) .....                        | 58 |

| BIAS DAC Setting (APCDAC) Current VBIAS Setting.....       | 58 |

| Modulation DAC Setting (MODDAC) Current VMOD Setting ..... | 59 |

| OEM Readback Register (OEMRD) .....                        | 59 |

| Signal Detect Threshold (LOSFLTn).....                     | 59 |

| RX EEPROM Tap Selection (RXPOT) .....                      | 60 |

| OEM Configuration 4 (OEMCFG4) .....                        | 60 |

| OEM Configuration 5 (OEMCFG5) .....                        | 61 |

| OEM Configuration 6 (OEMCFG6) .....                        | 62 |

| Power-On Hour Meter Data (POHDATA) .....                   | 62 |

| OEM Scratchpad Registers (SCRATCHn).....                   | 63 |

| RX Power Look-up Table (RXLUTn).....                       | 63 |

| Calibration Constants (CALn) .....                         | 63 |

| Manufacturer ID Register .....                             | 64 |

| Device ID Register .....                                   | 64 |

| Package Information .....                                  | 65 |

## List of Figures

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| Figure 1. MIC3002 Block Diagram .....                                   | 18 |

| Figure 2. Analog-to-Digital Converter Block Diagram .....               | 18 |

| Figure 3. Internal Calibration RX Power Linear Approximation .....      | 25 |

| Figure 4. RXPOT Block Diagram .....                                     | 25 |

| Figure 5. MIC3002 APC and Modulation Control Block Diagram .....        | 26 |

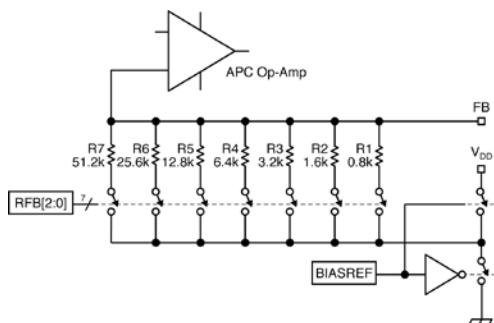

| Figure 6. Programmable Feedback Resistor .....                          | 26 |

| Figure 7. Transmitter Configurations Supported by MIC3002 .....         | 26 |

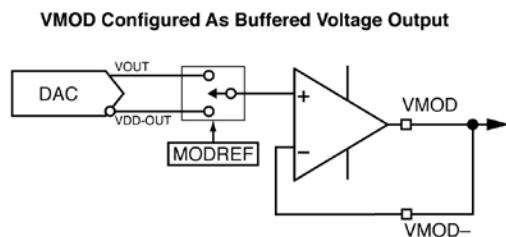

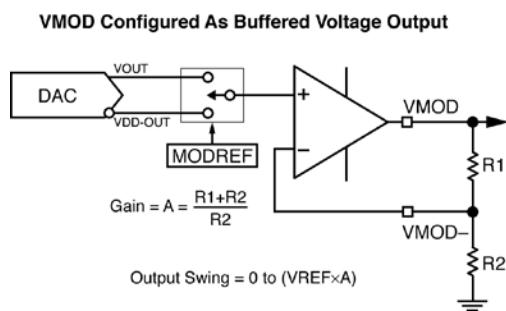

| Figure 8. V <sub>MOD</sub> Configured as Voltage Output with Gain ..... | 27 |

| Figure 9. MIC3002 Power-ON Timing.....                                  | 28 |

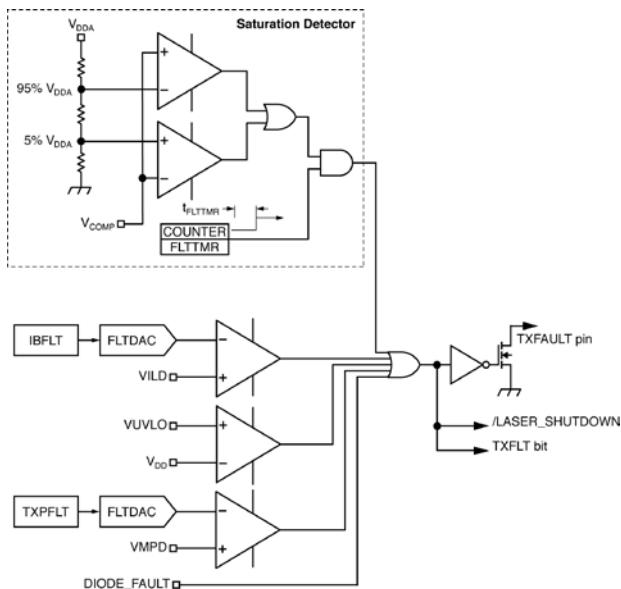

| Figure 10. Fault Comparator Logic .....                                 | 28 |

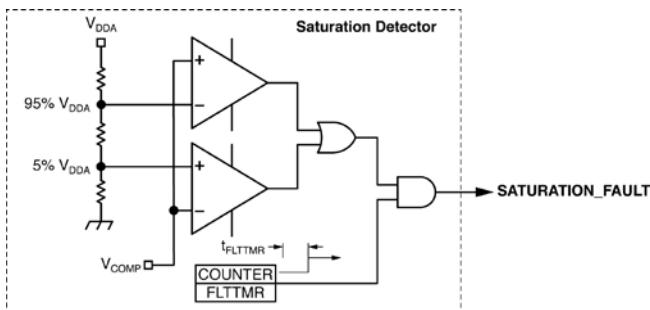

| Figure 11. Saturation Detector.....                                     | 29 |

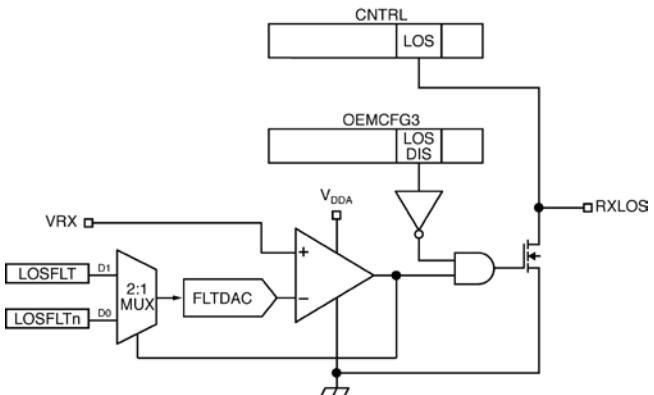

| Figure 12. RXLOS Comparator Logic .....                                 | 29 |

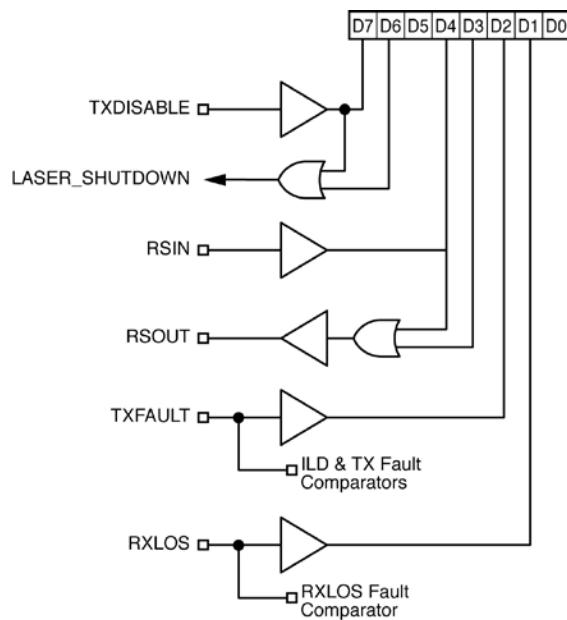

| Figure 13. Control and Status I/O Logic.....                            | 33 |

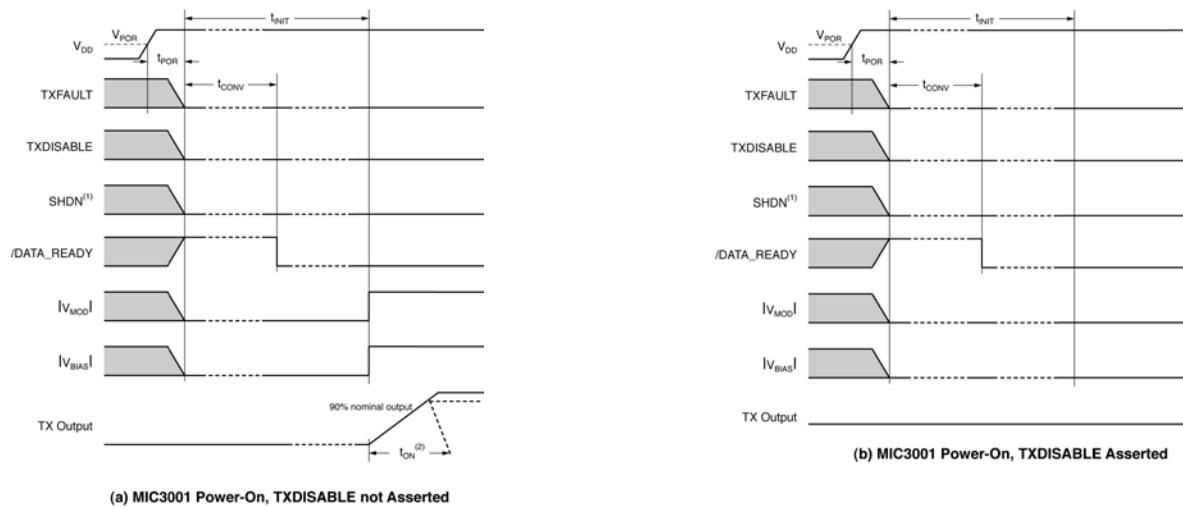

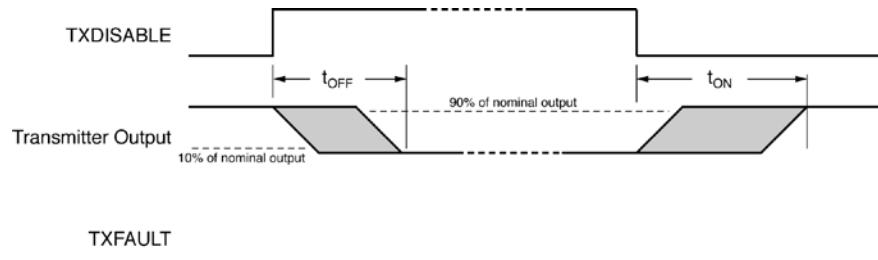

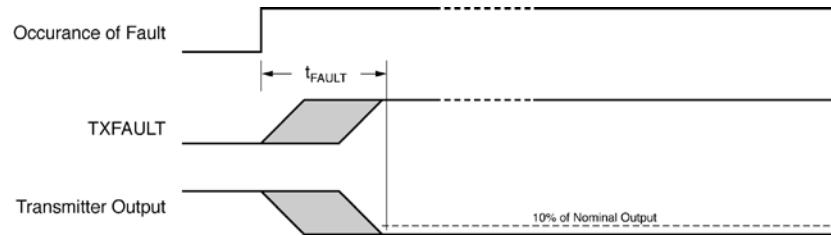

| Figure 14. Transmitter ON-OFF Timing .....                              | 34 |

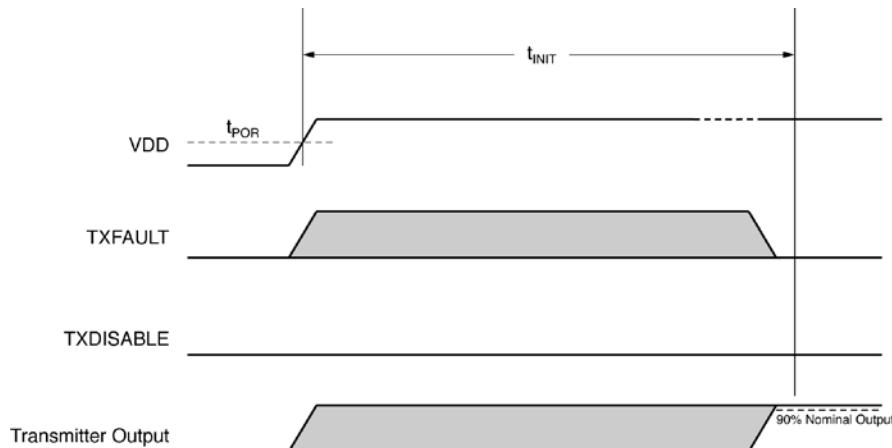

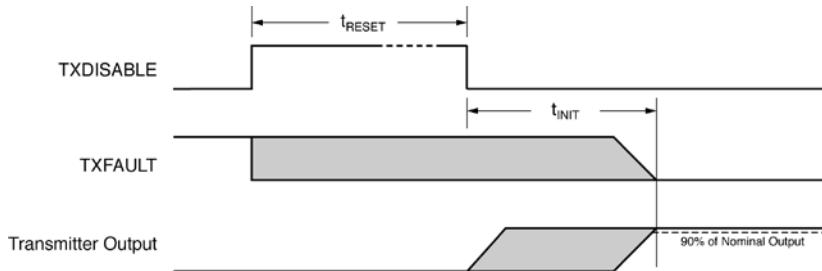

| Figure 15. Initialization Timing with TXDISABLE Asserted.....           | 34 |

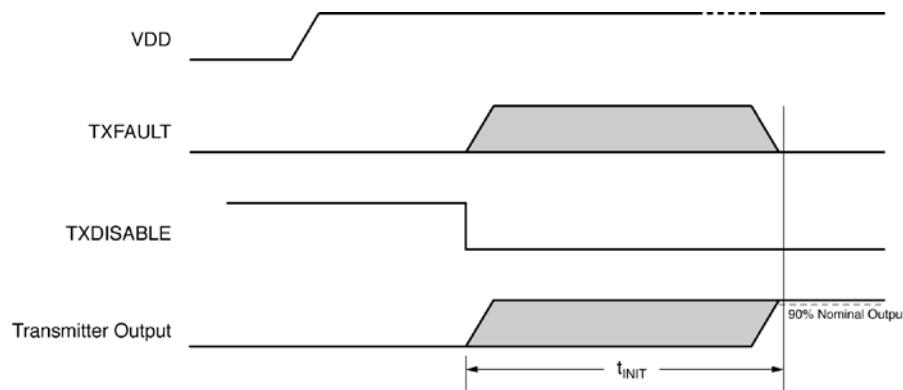

| Figure 16. Initialization Timing with TXDISABLE Not Asserted.....       | 34 |

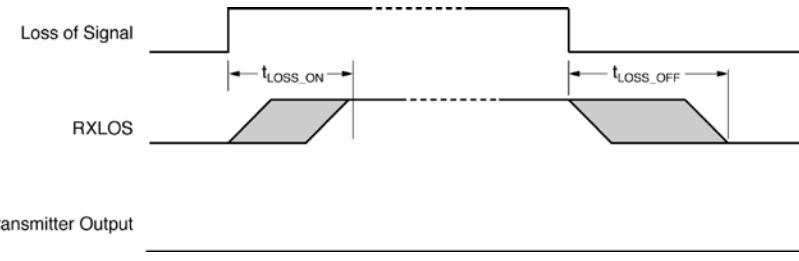

| Figure 17. Loss-of-Signal (LOS) Timing .....                            | 35 |

| Figure 18. Transmit Fault Timing .....                                  | 28 |

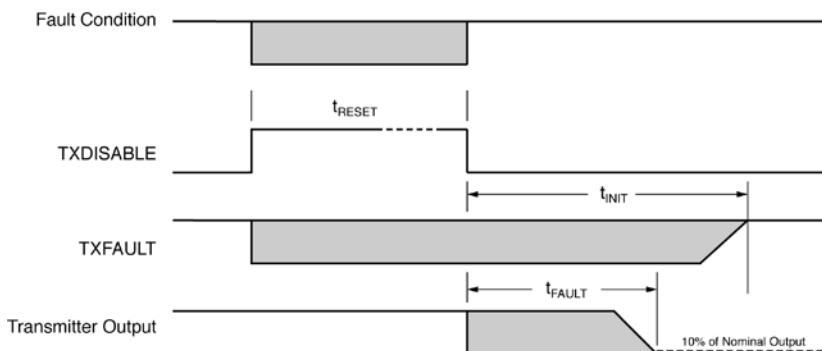

| Figure 19. Successfully Clearing a Fault Condition .....                | 36 |

| Figure 20. Unsuccessful Attempt to Clear a Fault .....                  | 36 |

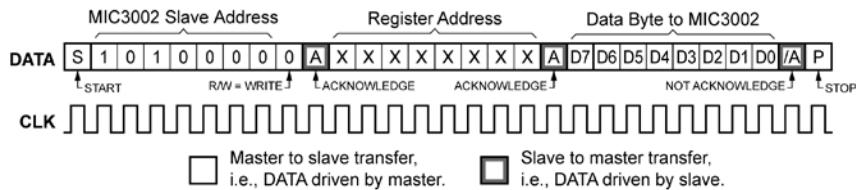

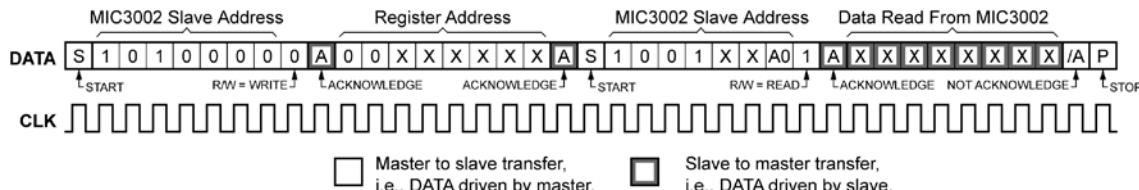

| Figure 21. Write Byte Protocol .....                                    | 38 |

| Figure 22. Read Byte Protocol .....                                     | 38 |

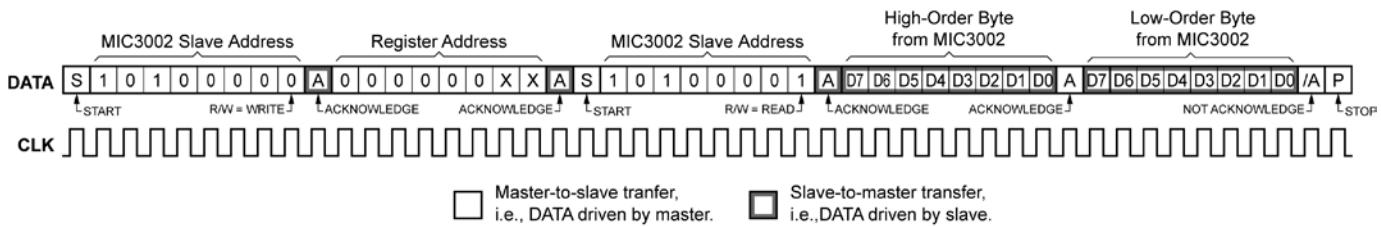

| Figure 23. Read_Word Protocol.....                                      | 38 |

| Figure 24. Four-Byte Page_White Protocol .....                          | 39 |

## List of Tables

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| Table 1. MIC3002 Address Map, Serial Address = A0 <sub>h</sub> .....                | 15 |

| Table 2. MIC3002 Address Map, Serial Address = A2 <sub>h</sub> .....                | 15 |

| Table 3. Temperature Compensation Tables, Serial Address = A4 <sub>h</sub> .....    | 16 |

| Table 4. OEM Configuration Registers, Serial Address = A6 <sub>h</sub> .....        | 17 |

| Table 5. A/D Input Signal Ranges and Resolutions.....                               | 19 |

| Table 6. V <sub>AUX</sub> Input Signal Ranges and Resolutions .....                 | 19 |

| Table 7. LUT for Temperature Reading Compensation.....                              | 20 |

| Table 8. Alarms Interrupt Sources Masking Bits.....                                 | 20 |

| Table 9. Warnings Interrupt Sources Masking Bits.....                               | 21 |

| Table 10. LSB Values of Offset Coefficients.....                                    | 23 |

| Table 11. Internal Calibration Coefficient Memory Map – Part I .....                | 24 |

| Table 12. Internal Calibration Coefficient Memory Map – Part II .....               | 24 |

| Table 13. Shutdown State of SHDN vs. Configuration Bits .....                       | 27 |

| Table 14. Shutdown State of V <sub>BIAS</sub> vs. Configuration Bits.....           | 27 |

| Table 15. Shutdown State of V <sub>MOD</sub> vs. Configuration Bits.....            | 27 |

| Table 16. Temperature Compensation Look-up Tables .....                             | 30 |

| Table 17. APC Temperature Compensation Look-Up Table .....                          | 31 |

| Table 18. V <sub>MOD</sub> Temperature Compensation Look-Up Table.....              | 31 |

| Table 19. I <sub>BIAS</sub> Comparator Temperature Compensation Look-Up Table ..... | 31 |

| Table 20. BIAS Current High Alarm Temperature Compensation Table .....              | 31 |

| Table 22. MIC3002 Events.....                                                       | 33 |

| Table 23. Power-On Hour Meter Result Format .....                                   | 36 |

| Table 24. Test and Diagnostic Features .....                                        | 37 |

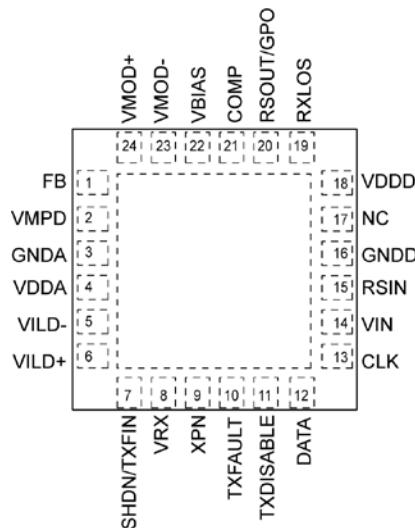

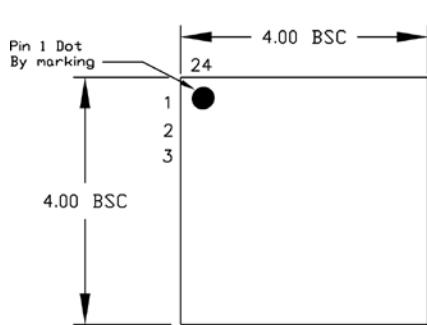

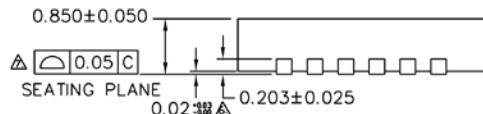

## Pin Configuration

24-Pin QFN

## Pin Description

| Pin Number | Pin Name   | Pin Function                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | FB         | Analog Input. Feedback voltage for the APC loop op-amp. Polarity and scale are programmable via the APC configuration bits. Connect to $V_{BIAS}$ if APC is not used.                                                                                                                                                                                                                          |

| 2          | VMPD       | Analog Input. Multiplexed A/D converter input for monitoring transmitted optical power via a monitor photodiode. In most applications, VMPD will be connected directly to FB. The input range is 0 - $V_{REF}$ or 0 - $V_{REF}/4$ depending on the setting of the APC configuration bits                                                                                                       |

| 3          | GNDA       | Ground return for analog functions.                                                                                                                                                                                                                                                                                                                                                            |

| 4          | VDDA       | Power supply input for analog functions.                                                                                                                                                                                                                                                                                                                                                       |

| 5          | VILD-      | Analog Input. Reference terminal for the multiplexed pseudo-differential A/D converter inputs for monitoring laser bias current via a sense resistor (VILD+ is the sensing input). Tie to $V_{DD}$ or GND to reference the voltage sensed on VILD+ to $V_{DD}$ or GND, respectively. Limited common-mode voltage range, see "Applications Information" section for more details.               |

| 6          | VILD+      | Analog Input. Multiplexed A/D input for monitoring laser bias current via a sense resistor (signal input); accommodates inputs referenced to $V_{DD}$ or GND (see pin 5 description). Limited common-mode voltage range, see "Applications Information" section for more details.                                                                                                              |

| 7          | SHDN/TXFIN | Digital output/Input; programmable polarity. When used as shutdown output (SHDN), OEMCFG3-2 set to 0, SHDN is asserted at the detection of a fault condition if OEMCFG4-7 is set to 0. If the latter bit is set to 1, a fault condition will not assert SHDN. When programmed as TXFIN, it is an input for external fault signals to be ORed with the internal fault sources to drive TXFAULT. |

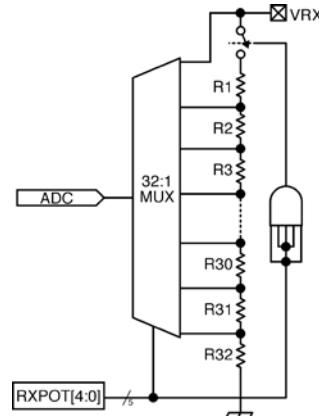

| 8          | VRX        | Analog Input. Multiplexed A/D converter input for monitoring received optical power. The input range is 0 to $V_{REF}$ . A 5-bit programmable EEPROM on this pin provides for coarse calibration and ranging of the RX power measurement.                                                                                                                                                      |

| 9          | XPN        | Analog Input/Output. Optional connection to an external PN junction for sensing temperature at a remote location. The Zone bit in OEMCFG1 determines whether temperature is measured using the on-chip sensor or the remote PN junction.                                                                                                                                                       |

| 10         | TXFAULT    | Digital Output; Open-Drain, programmable polarity. If OEMCFG5-4 is set to 0, a high level indicates a hardware fault impeding transmitter operation. The state of this pin is always reflected in the TXFLT bit.                                                                                                                                                                               |

## Pin Description

| Pin Number | Pin Name  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | TXDISABLE | Digital Input; Active High. The transmitter is disabled when this line is high or the STXDIS bit is set. The state of this input is always reflected in the TXDIS bit.                                                                                                                                                                                                                                                                                                                                                |

| 12         | DATA      | Digital I/O; Open-drain. Bi-directional serial data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13         | CLK       | Digital Input; Serial clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14         | VIN/INT   | If bit 4 (IE) in USRCTL register is set to 0 (default), this pin is configured as analog input. If IE bit is set to 1, this pin is configured as open-drain output. Analog Input: Multiplexed A/D input for monitoring supply voltage. 0V to 5.5V input range. Open-drain output: outputs the internally generated interrupt signal /INT.                                                                                                                                                                             |

| 15         | RSIN      | Digital Input; Rate Select Input; ORed with rate select bit to determine the state of the RSOUT pin. The state of this pin is always reflected in the RSEL bit.                                                                                                                                                                                                                                                                                                                                                       |

| 16         | GNDD      | Ground return for digital functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 17         | NC        | No connection. This pin is used for test purposes and must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18         | VDDD      | Power supply input for digital functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19         | RXLOS     | Digital Output; programmable polarity Open-Drain. Indicates the loss of the received signal as indicated by a level of received optical power below the programmed RXLOS comparator threshold; may be wire-ORed with external signals. Normal operation is indicated by a Low level when OEMCFG6-3 is set to 0 and a high level when OEMCFG6-3 is set to 1. RXLOS is de-asserted when VRX > LOSFLTn. The LOS bit reflects the state of RXLOS whether driven by the MIC3002 or an external circuit.                    |

| 20         | RS0/GPO   | Digital Output. Open-Drain or push-pull. When used as rate select output, it represents the receiver rate select as per SFF. This output is controlled by the SRSEL bit ORed with RSIN input and is open drain only. When used as a general-purpose, non-volatile output, it is controlled by the GPO configuration bits in OEMCFG3.                                                                                                                                                                                  |

| 21         | COMP      | Analog Output, compensation terminal. Connect a capacitor between this pin and GNDA or VDDA with appropriate value to tune the APC loop time constant to a desirable value.                                                                                                                                                                                                                                                                                                                                           |

| 22         | VBIAS     | Analog Output. Buffered DAC output capable of sourcing or sinking up to 10mA under control of the APC function to drive an external transistor for laser diode D.C. bias. The output and feedback polarity are programmable to accommodate either a NPN or a PNP transistor to drive a common-anode or common-cathode laser diode.                                                                                                                                                                                    |

| 23         | VMOD-     | Analog Input. Inverting terminal of VMOD buffer op-amp. Connect to VMOD+ (gain = 1) or feedback resistors network to set a different gain                                                                                                                                                                                                                                                                                                                                                                             |

| 24         | VMOD+     | Analog Output. Buffered DAC output to set the modulation current on the laser driver IC. Operates with either a 0– V <sub>REF</sub> or a (V <sub>DD</sub> –V <sub>REF</sub> ) – V <sub>DD</sub> output swing so as to generate either a ground-referenced or a V <sub>DD</sub> referenced programmed voltage. A simple external circuit can be used to generate a programmable current for those drivers that require a current rather than a voltage input. See “Applications Information” section for more details. |

**Absolute Maximum Ratings<sup>(1)</sup>**

|                                                                  |                         |

|------------------------------------------------------------------|-------------------------|

| Power Supply Voltage, $V_{DD}$ .....                             | +3.8V                   |

| Voltage on CLK, DATA, TXFAULT, VIN, RXLOS,<br>DISABLE, RSIN..... | -0.3V to +6.0V          |

| Voltage On Any Other Pin .....                                   | -0.3V to $V_{DD}$ +0.3V |

| Power Dissipation, $T_A = 85^\circ\text{C}$ .....                | 1.5W                    |

| Junction Temperature ( $T_J$ ) .....                             | 150°C                   |

| Storage Temperature ( $T_S$ ) .....                              | -65°C to +150°C         |

| ESD Ratings <sup>(3)</sup>                                       |                         |

| Human Body Model.....                                            | 2kV                     |

| Machine Model .....                                              | 300V                    |

| Soldering (20sec) .....                                          | 260°C                   |

**Operating Ratings<sup>(2)</sup>**

|                                                           |                 |

|-----------------------------------------------------------|-----------------|

| Power Supply Voltage, $V_{DDA}/V_{DDD}$ .....             | +3.0V to +3.6V  |

| Ambient Temperature Range ( $T_A$ ) ...                   | -40°C to +105°C |

| Package Thermal Resistance<br>QFN ( $\theta_{JA}$ ) ..... | 43°C/W          |

**Electrical Characteristics**

For typical values,  $T_A = 25^\circ\text{C}$ ,  $V_{DDA} = V_{DDD} = +3.3\text{V}$ , unless otherwise noted. **Bold** values are guaranteed for  $+3.0\text{V} \leq (V_{DDA} = V_{DDD}) \leq 3.6\text{V}$ ,  $T_{(\min)} \leq T_A \leq T_{(\max)}$ <sup>(8)</sup>

| Symbol                          | Parameter                         | Condition                                                                                                                       | Min   | Typ   | Max   | Units |

|---------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| <b>Power Supply</b>             |                                   |                                                                                                                                 |       |       |       |       |

| $I_{DD}$                        | Supply Current                    | CLK = DATA = $V_{DDD} = V_{DDA}$ ;<br>TXDISABLE low; all DACs at full-scale; all A/D inputs at full-scale; all other pins open. | 2.3   | 3.5   | mA    |       |

|                                 |                                   | CLK = DATA = $V_{DDD} = V_{DDA}$ ;<br>TXDISABLE high; FLTDAC at full-scale; all A/D inputs at full-scale; all other pins open.  | 2.3   | 3.5   | mA    |       |

| $V_{POR}$                       | Power-on Reset Voltage            | All registers reset to default values;<br>A/D conversions initiated.                                                            | 2.9   | 2.98  | V     |       |

| $V_{UVLO}$                      | Under-Voltage Lockout Threshold   | Note 5                                                                                                                          | 2.5   | 2.73  | V     |       |

| $V_{HYST}$                      | Power-on Reset Hysteresis Voltage |                                                                                                                                 | 170   |       | mV    |       |

| $t_{POR}$                       | Power-on Reset Time               | $V_{DD} > V_{POR}$ <sup>(4)</sup>                                                                                               | 50    |       | μs    |       |

| $V_{REF}$                       | Reference Voltage                 |                                                                                                                                 | 1.210 | 1.225 | 1.240 | V     |

| $\Delta V_{REF}/\Delta V_{DDA}$ | Voltage Reference Line Regulation |                                                                                                                                 | 1.7   |       | mV/V  |       |

**Temperature-to-Digital Converter Characteristics**

|              |                                         |                                                         |         |         |    |

|--------------|-----------------------------------------|---------------------------------------------------------|---------|---------|----|

|              | Local Temperature Measurement<br>Error  | -40°C $\leq T_A \leq +105^\circ\text{C}$ <sup>(6)</sup> | $\pm 1$ | $\pm 3$ | °C |

|              | Remote Temperature<br>Measurement Error | -40°C $\leq T_A \leq +105^\circ\text{C}$ <sup>(6)</sup> | $\pm 1$ | $\pm 3$ | °C |

| $t_{CONV}$   | Conversion Time                         | Note 4                                                  |         | 60      | ms |

| $t_{SAMPLE}$ | Sample Period                           |                                                         |         | 100     | ms |

**Remote Temperature Input, XPN**

|       |                                          |                                     |   |     |     |    |

|-------|------------------------------------------|-------------------------------------|---|-----|-----|----|

| $I_F$ | Current to External Diode <sup>(4)</sup> | XPN at high level, clamped to 0.6V. |   | 192 | 400 | μA |

|       |                                          | XPN at low level, clamped to 0.6V.  | 7 | 12  |     | μA |

**Voltage-to-Digital Converter Characteristics (V<sub>RX</sub>, V<sub>AUX</sub>, V<sub>BIAS</sub>, V<sub>MPD</sub>, V<sub>ILD±</sub>)**

| Symbol              | Parameter                 | Condition                                      | Min | Typ | Max  | Units |

|---------------------|---------------------------|------------------------------------------------|-----|-----|------|-------|

|                     | Voltage Measurement Error | -40°C ≤ T <sub>A</sub> ≤ +105°C <sup>(6)</sup> |     | ±1  | ±2.0 | %fs   |

| t <sub>CONV</sub>   | Conversion Time           | Note 4                                         |     |     | 10   | ms    |

| t <sub>SAMPLE</sub> | Sample Period             | Note 4                                         |     |     | 100  | ms    |

**Voltage Input, V<sub>IN</sub> (Pin 14 used as an ADC Input)**

|                   |                     |                                                                              |      |    |     |    |

|-------------------|---------------------|------------------------------------------------------------------------------|------|----|-----|----|

| V <sub>IN</sub>   | Input Voltage Range | -0.3 ≤ V <sub>DD</sub> ≤ 3.6V                                                | GNDA |    | 5.5 | V  |

| I <sub>LEAK</sub> | Input Current       | V <sub>IN</sub> = V <sub>DD</sub> or GND; V <sub>AUX</sub> = V <sub>IN</sub> |      | 55 |     | μA |

| C <sub>IN</sub>   | Input Capacitance   |                                                                              |      | 10 |     | pF |

**Digital-to-Voltage Converter Characteristics (V<sub>MOD</sub>, V<sub>BIAS</sub>)**

|                   |                                  |                                                |  |      |     |     |

|-------------------|----------------------------------|------------------------------------------------|--|------|-----|-----|

|                   | Accuracy                         | -40°C ≤ T <sub>A</sub> ≤ +105°C <sup>(6)</sup> |  | ±1   | 2.0 | %fs |

| t <sub>CONV</sub> | Conversion Time                  | Note 4                                         |  |      | 20  | ms  |

| DNL               | Differential Non-linearity Error | Note 4                                         |  | ±0.5 | ±1  | LSB |

**Bias Current Sense Inputs, V<sub>ILD+</sub>, V<sub>ILD-</sub>**

|                  |                                                                                    |                                                |   |      |                     |    |

|------------------|------------------------------------------------------------------------------------|------------------------------------------------|---|------|---------------------|----|

| V <sub>ILD</sub> | Differential Input Signal Range,  V <sub>ILD+</sub> - V <sub>ILD-</sub>            |                                                | 0 |      | V <sub>REF</sub> /4 | mV |

| I <sub>IN+</sub> | V <sub>ILD+</sub> input current                                                    |                                                |   |      | ±1                  | μA |

| I <sub>IN-</sub> | V <sub>ILD-</sub> input current<br> V <sub>ILD+</sub> - V <sub>ILD-</sub>   = 0.3V | V <sub>ILD-</sub> referred to V <sub>DDA</sub> |   | +150 |                     | μA |

|                  |                                                                                    | V <sub>ILD-</sub> referred to GND              |   | -150 |                     | μA |

| C <sub>IN</sub>  | Input Capacitance                                                                  |                                                |   | 10   |                     | pF |

**APC Op Amp, FB, V<sub>BIAS</sub>, COMP**

|                    |                                                             |                                                        |                         |       |                  |       |

|--------------------|-------------------------------------------------------------|--------------------------------------------------------|-------------------------|-------|------------------|-------|

| GBW                | Gain Bandwidth Product                                      | C <sub>COMP</sub> = 20pF; Gain = 1                     |                         | 1     |                  | MHz   |

| TC <sub>VOS</sub>  | Input Offset Voltage Temperature Coefficient <sup>(4)</sup> |                                                        |                         | 1     |                  | μV/°C |

| V <sub>OUT</sub>   | Output Voltage Swing                                        | I <sub>OUT</sub> = 10mA, SRCE bit = 1                  | GNDA                    |       | 1.25             | V     |

|                    |                                                             | I <sub>OUT</sub> = -10mA, SRCE bit = 0                 | V <sub>DDA</sub> - 1.25 |       | V <sub>DDA</sub> | V     |

| I <sub>SC</sub>    | Output Short-Circuit Current                                |                                                        |                         | 55    |                  | mA    |

| t <sub>SC</sub>    | Short Circuit Withstand Time                                | T <sub>J</sub> ≤ 150°C <sup>(4)</sup>                  |                         |       |                  | sec   |

| PSRR               | Power Supply Rejection Ratio                                | C <sub>COMP</sub> = 20pF; Gain = 1, to GND             |                         | 55    |                  | dB    |

|                    |                                                             | C <sub>COMP</sub> = 20pF; Gain = 1, to V <sub>DD</sub> |                         | 40    |                  |       |

| A <sub>MIN</sub>   | Minimum Stable Gain                                         | C <sub>COMP</sub> = 20pF, Note 4                       |                         |       | 1                | V/V   |

| ΔV/Δt              | Slew Rate                                                   | C <sub>COMP</sub> = 20pF; Gain = 1                     |                         | 3     |                  | V/μs  |

| ΔRFB               | Internal Feedback Resistor Tolerance                        |                                                        |                         | ±20   |                  | %     |

| ΔRFB/Δt            | Internal Feedback Resistor Temperature Coefficient          |                                                        |                         | 25    |                  | ppm/C |

| I <sub>START</sub> | Laser Start-up Current Magnitude                            | START = 01 <sub>h</sub>                                |                         | 0.375 |                  | mA    |

|                    |                                                             | START = 02 <sub>h</sub>                                |                         | 0.750 |                  | mA    |

|                    |                                                             | START = 04 <sub>h</sub>                                |                         | 1.500 |                  | mA    |

|                    |                                                             | START = 08 <sub>h</sub>                                |                         | 3.000 |                  | mA    |

| C <sub>IN</sub>    | Pin Capacitance                                             |                                                        |                         | 10    |                  | pF    |

## Electrical Characteristics

| Symbol                                                                   | Parameter                                       | Condition                                              | Min     | Typ  | Max                  | Units |

|--------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------|---------|------|----------------------|-------|

| <b>V<sub>MOD</sub> Buffer Op-Amp, V<sub>MOD+</sub>, V<sub>MOD-</sub></b> |                                                 |                                                        |         |      |                      |       |

| GBW                                                                      | Gain Bandwidth                                  | C <sub>COMP</sub> = 20pF; Gain = 1                     |         | 1    |                      | MHz   |

| T <sub>C<sub>VOS</sub></sub>                                             | Input Offset Voltage<br>Temperature Coefficient |                                                        |         | 1    |                      | µV/°C |

| I <sub>BIAS</sub>                                                        | V <sub>MOD-</sub> Input Current                 |                                                        |         | ±0.1 | ±1                   | µA    |

| V <sub>OUT</sub>                                                         | Output Voltage Swing                            | I <sub>OUT</sub> = ±1mA                                | GNDA+75 |      | V <sub>DDA</sub> -75 | mV    |

| I <sub>SC</sub>                                                          | Output Short-Circuit Current                    |                                                        |         | 35   |                      | mA    |

| t <sub>SC</sub>                                                          | Short Circuit Withstand Time                    | T <sub>J</sub> ≤ 150°C <sup>(4)</sup>                  |         |      |                      | sec   |

| PSRR                                                                     | Power Supply Rejection Ratio                    | C <sub>COMP</sub> = 20pF; Gain = 1, to GND             |         | 65   |                      | dB    |

|                                                                          |                                                 | C <sub>COMP</sub> = 20pF; Gain = 1, to V <sub>DD</sub> |         | 44   |                      | dB    |

| A <sub>MIN</sub>                                                         | Minimum Stable Gain                             | C <sub>COMP</sub> = 20pF                               |         |      | 1                    | V/V   |

| ΔV/ΔT                                                                    | Slew Rate                                       | C <sub>COMP</sub> = 20pF; Gain = 1                     |         | 1    |                      | V/µs  |

| C <sub>IN</sub>                                                          | Pin Capacitance                                 |                                                        |         | 10   |                      | pF    |

### Control and Status I/O, TXDISABLE, TXFAULT, RSIN, RSOUT(GPO), SHDN(TXFIN), RXLOS, /INT

|                   |                                               |                       |     |                       |    |

|-------------------|-----------------------------------------------|-----------------------|-----|-----------------------|----|

| V <sub>IL</sub>   | Low Input Voltage                             |                       |     | 0.8                   | V  |

| V <sub>IH</sub>   | High Input Voltage                            |                       | 2.0 |                       | V  |

| V <sub>OL</sub>   | Low Output Voltage                            | I <sub>OL</sub> ≤ 3mA |     | 0.3                   | V  |

| V <sub>OH</sub>   | High Output Voltage<br>(applies to SHDN only) | I <sub>OH</sub> ≤ 3mA |     | V <sub>DDA</sub> -0.3 | V  |

| I <sub>LEAK</sub> | Input Current                                 |                       |     | ±1                    | µA |

| C <sub>IN</sub>   | Input Capacitance                             |                       | 10  |                       | pF |

### Transmit Optical Power Input, V<sub>MPD</sub>

|                   |                     |           |                                    |    |                  |    |

|-------------------|---------------------|-----------|------------------------------------|----|------------------|----|

| V <sub>IN</sub>   | Input Voltage Range | Note 4    | GNDA                               |    | V <sub>DDA</sub> | V  |

| V <sub>RX</sub>   | Input Signal Range  | BIASREF=0 |                                    |    | V <sub>REF</sub> | V  |

|                   |                     | BIASREF=1 | V <sub>DDA</sub> -V <sub>REF</sub> |    | V <sub>DDA</sub> | V  |

| C <sub>IN</sub>   | Input Capacitance   | Note 4    |                                    | 10 |                  | pF |

| I <sub>LEAK</sub> | Input Current       |           |                                    | ±1 | µA               |    |

### Received Optical Power Input, VRX, RXPOT

|                                      |                                               |                              |      |     |                  |       |

|--------------------------------------|-----------------------------------------------|------------------------------|------|-----|------------------|-------|

|                                      | Input Voltage Range                           | Note 4                       | GNDA |     | V <sub>DDA</sub> | V     |

| V <sub>RX</sub>                      | Valid Input Signal Range<br>(ADC Input Range) |                              | 0    |     | V <sub>REF</sub> | V     |

| R <sub>RXPOT(32)</sub>               | End-to-End Resistance                         | RXPOT = 1F <sub>h</sub>      |      | 32  |                  | KΩ    |

| ΔRXPOT                               | Resistor Tolerance                            |                              |      | ±20 |                  | %     |

| ΔRXPOT/ΔT                            | Resistor Temperature<br>Coefficient           |                              |      | 25  |                  | ppm/C |

| ΔV <sub>RX</sub> /V <sub>RXPOT</sub> | Divider Ratio Accuracy                        | 00 ≤ RXPOT ≤ 1F <sub>h</sub> | -5   |     | +5               | %     |

| I <sub>LEAK</sub>                    | Input Current                                 | RXPOT = 0 (disconnected)     |      | ±1  | µA               |       |

| C <sub>IN</sub>                      | Input Capacitance                             | Note 4                       |      | 10  |                  | pF    |

| I <sub>LEAK</sub>                    | Input Current                                 |                              |      | ±1  | µA               |       |

## Electrical Characteristics

| Symbol                                                                           | Parameter                                              | Condition                                                                                                         | Min           | Typ | Max          | Units         |

|----------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------|-----|--------------|---------------|

| <b>Control and Status I/O Timing, TXFAULT, TXDISABLE, RSIN, RSOUT, and RXLOS</b> |                                                        |                                                                                                                   |               |     |              |               |

| $t_{OFF}$                                                                        | TXDISABLE Assert Time                                  | From input asserted to optical output at 10% of nominal, $C_{COMP} = 10\text{nF}$ .                               |               |     | <b>10</b>    | $\mu\text{s}$ |

| $t_{ON}$                                                                         | TXDISABLE De-assert Time                               | From input de-asserted to optical output at 90% of nominal, $C_{COMP} = 10\text{nF}$ .                            |               |     | <b>1</b>     | ms            |

| $t_{INIT}$                                                                       | Initialization Time                                    | From power on or transmitter enabled to optical output at 90% of nominal and TX_FAULT de-asserted. <sup>(4)</sup> |               |     | <b>300</b>   | ms            |

| $t_{INIT2}$                                                                      | Power-on Initialization Time                           | From power on to APC loop-enabled.                                                                                |               |     | <b>200</b>   | ms            |

| $t_{FAULT}$                                                                      | TXFAULT Assert Time                                    | From fault condition to TXFAULT assertion. <sup>(4)</sup>                                                         |               |     | 95           | $\mu\text{s}$ |

| $t_{RESET}$                                                                      | Fault Reset Time                                       | Length of time TXDISABLE must be asserted to reset fault condition.                                               | <b>10</b>     |     |              | $\mu\text{s}$ |

| $t_{LOSS\_ON}$                                                                   | RXLOS Assert Time                                      | From loss of signal to RXLOS asserted.                                                                            |               |     | 95           | $\mu\text{s}$ |

| $t_{LOSS\_OFF}$                                                                  | RXLOS De-assert Time                                   | From signal acquisition to LOS de-asserted.                                                                       |               |     | <b>100</b>   | $\mu\text{s}$ |

| $t_{DATA}$                                                                       | Analog Parameter Data Ready                            | From power on to valid analog parameter data available. <sup>(4)</sup>                                            |               |     | <b>400</b>   | ms            |

| $t_{PROP\_IN}$                                                                   | TXFAULT, TXDISABLE, RXLOS, RSIN Input Propagation Time | Time from input change to corresponding internal register bit set or cleared. <sup>(4)</sup>                      |               |     | <b>1</b>     | $\mu\text{s}$ |

| $t_{PROP\_OUT}$                                                                  | TXFAULT, RSOUT, /INT Output Propagation Time           | From an internal register bit set or cleared to corresponding output change. <sup>(4)</sup>                       |               |     | <b>1</b>     | $\mu\text{s}$ |

| <b>Fault Comparators</b>                                                         |                                                        |                                                                                                                   |               |     |              |               |

| $\phi_{FLTTMR}$                                                                  | Fault Suppression Timer Clock Period                   | Note 4                                                                                                            | <b>0.475</b>  | 0.5 | <b>0.525</b> | ms            |

|                                                                                  | Accuracy                                               |                                                                                                                   | -3            |     | +3           | %/F.S.        |

| $t_{REJECT}$                                                                     | Glitch Rejection                                       | Maximum length pulse that will not cause output to change state. <sup>(4)</sup>                                   | 4.5           |     |              | $\mu\text{s}$ |

| $V_{SAT}$                                                                        | Saturation Detection Threshold                         | High level                                                                                                        |               | 95  |              | %VDDA         |

|                                                                                  |                                                        | Low level                                                                                                         |               | 5   |              | %VDDA         |

| <b>Power-On Hour Meter</b>                                                       |                                                        |                                                                                                                   |               |     |              |               |

|                                                                                  | Timebase Accuracy                                      | $0^\circ\text{C} \leq T_A \leq +70^\circ\text{C}$ <sup>(4)</sup>                                                  | <b>+5</b>     |     | <b>-5</b>    | %             |

|                                                                                  |                                                        | $-40^\circ\text{C} \leq T_A \leq +105^\circ\text{C}$                                                              | <b>+10</b>    |     | <b>-10</b>   | %             |

|                                                                                  | Resolution                                             | Note 4                                                                                                            |               | 10  |              | hours         |

| <b>Non-Volatile (FLASH) Memory</b>                                               |                                                        |                                                                                                                   |               |     |              |               |

| $t_{WR}$                                                                         | Write Cycle Time <sup>(7)</sup>                        | From STOP of a one to four-byte write transaction. <sup>(4)</sup>                                                 |               |     | <b>13</b>    | ms            |

|                                                                                  | Data Retention                                         |                                                                                                                   | <b>100</b>    |     |              | years         |

| Endurance                                                                        | Minimum Permitted Number Write Cycles                  |                                                                                                                   | <b>10,000</b> |     |              | cycles        |

**Serial Data I/O Pin, Data**

| Symbol     | Parameter          | Condition             | Min        | Typ | Max        | Units         |

|------------|--------------------|-----------------------|------------|-----|------------|---------------|

| $V_{OL}$   | Low Output Voltage | $I_{OL} = 3\text{mA}$ |            |     | <b>0.4</b> | V             |

|            |                    | $I_{OL} = 6\text{mA}$ |            |     | <b>0.6</b> | V             |

| $V_{IL}$   | Low Input Voltage  |                       |            |     | <b>0.8</b> | V             |

| $V_{IH}$   | High Input Voltage |                       | <b>2.1</b> |     |            | V             |

| $I_{LEAK}$ | Input Current      |                       |            |     | <b>±1</b>  | $\mu\text{A}$ |

| $C_{IN}$   | Input Capacitance  | Note 4                |            | 10  |            | pF            |

**Serial Clock Input, CLK**

|            |                    |                                            |            |    |            |               |

|------------|--------------------|--------------------------------------------|------------|----|------------|---------------|

| $V_{IL}$   | Low Input Voltage  | $2.7\text{V} \leq V_{DD} \leq 3.6\text{V}$ |            |    | <b>0.8</b> | V             |

| $V_{IH}$   | High Input Voltage | $2.7\text{V} \leq V_{DD} \leq 3.6\text{V}$ | <b>2.1</b> |    |            | V             |

| $I_{LEAK}$ | Input Current      |                                            |            |    | <b>±1</b>  | $\mu\text{A}$ |

| $C_{IN}$   | Input Capacitance  | Note 4                                     |            | 10 |            | pF            |

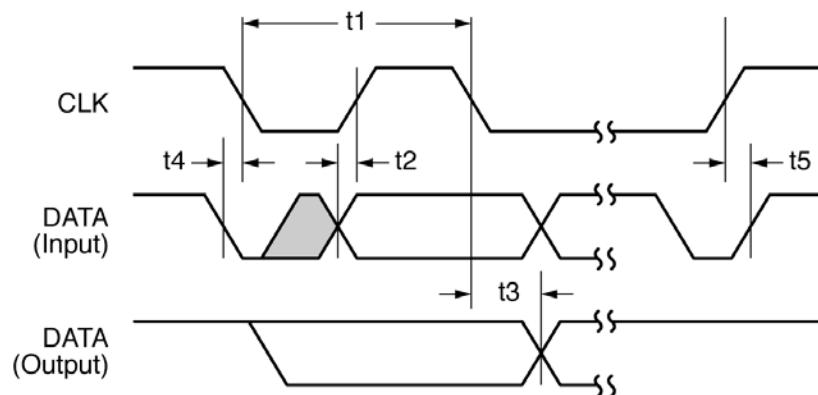

**Serial Interface Timing<sup>(4)</sup>**

|            |                                    |                                                                                                        |            |  |            |               |

|------------|------------------------------------|--------------------------------------------------------------------------------------------------------|------------|--|------------|---------------|

| $t_1$      | CLK (clock) Period                 |                                                                                                        | <b>2.5</b> |  |            | $\mu\text{s}$ |

| $t_2$      | Data In Setup Time to CLK High     |                                                                                                        | <b>100</b> |  |            | ns            |

| $t_3$      | Data Out Stable After CLK Low      |                                                                                                        | <b>300</b> |  |            | ns            |

| $t_4$      | Data Low Setup Time to CLK Low     | Start Condition                                                                                        | <b>100</b> |  |            | ns            |

| $t_5$      | Data High Hold Time After CLK High | Stop Condition                                                                                         | <b>100</b> |  |            | ns            |

| $t_{DATA}$ | Data Ready Time                    | From power on to completion of one set of ADC conversions; analog data available via serial interface. |            |  | <b>400</b> | ms            |

**Notes:**

1. Exceeding the absolute maximum rating may damage the device.

2. The device is not guaranteed to function outside its operating rating.

3. Devices are ESD sensitive. Handling precautions recommended.

4. Guaranteed by designing and/or testing of related parameters. Not 100% tested in production.

5. The MIC3000 will attempt to enter its shutdown state when  $V_{DD}$  falls below  $V_{UVLO}$ . This operation requires time to complete. If the supply voltage falls too rapidly, the operation may not be completed.

6. Does not include quantization error.

7. The MIC3002 will not respond to serial bus transactions during an EEPROM write-cycle. The host will receive a NACK during  $t_{WR}$ .

8. Final test on outgoing product is performed at  $T_A = +25^\circ\text{C}$ .

## Timing Diagram

**Serial Interface Timing**

## Address Map

| Address(s) | Field Size (Bytes) | Name                         | Description                                                       |

|------------|--------------------|------------------------------|-------------------------------------------------------------------|

| 0 – 95     | 96                 | Serial ID defined by SEP MSA | G-P NVRAM; R/W under valid OEM password.                          |

| 96 – 127   | 32                 | Vendor Specific              | Vendor specific EEPROM                                            |

| 128 – 255  | 128                | Reserved                     | Reserved for future use. G-P NVRAM; R/W under valid OEM password. |

Table 1. MIC3002 Address Map, Serial Address = A0<sub>h</sub>

| Address(s) |         | Field Size (Bytes) | Name                        | Description                                                                                                                                                        |

|------------|---------|--------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HEX        | DEC     |                    |                             |                                                                                                                                                                    |

| 00-27      | 0-39    | 40                 | Alarm and Warning Threshold | High/low limits for warning and alarms; writeable using OEM p/w; read-only otherwise.                                                                              |

| 28-37      | 40-55   | 16                 | Reserved                    | Reserved – do not write; reads undefined.                                                                                                                          |

| 38-5B      | 56-91   | 36                 | Calibration Constants       | Numerical constants for external calibration; writeable using OEM p/w; read-only otherwise.                                                                        |

| 5C-5E      | 92-94   | 3                  | Reserved                    | Reserved – do not write; reads undefined.                                                                                                                          |

| 5F         | 95      | 1                  | Checksum                    | G-P NVRAM; writeable using OEM p/w; ready only otherwise.                                                                                                          |

| 60-69      | 96-105  | 10                 | Analog Data                 | Real time analog parameter data.                                                                                                                                   |

| 6A-6D      | 106-109 | 4                  | Reserved                    | Reserved – do not write; reads undefined.                                                                                                                          |

| 6E         | 110     | 1                  | Control/Status Bits         | Control and status bits.                                                                                                                                           |

| 6F         | 111     | 1                  | Reserved                    | Reserved – do not write; reads undefined.                                                                                                                          |

| 70-71      | 112-113 | 2                  | Alarm Flags                 | Alarm status bits; read only.                                                                                                                                      |

| 72-73      | 114-115 | 2                  | Reserved                    | Reserved – do not write; reads undefined.                                                                                                                          |

| 74-75      | 116-117 | 2                  | Warning Flags               | Warning status bits; read only.                                                                                                                                    |

| 76-77      | 118-119 | 2                  | Reserved                    | Reserved – do not write; reads undefined.                                                                                                                          |

| 78-7E      | 120-126 | 7                  | OEMPW                       | OEM password entry field. The OEM password location can be selected to be 78-7B (120-123) or 7B-7E (123-126) by setting the bit OEMCFG5 bit 2 to 0 (default) or 1. |

| 7F         | 127     | 1                  | Vendor Specific             | Vendor specific. Reserved – do not write; reads undefined.                                                                                                         |

| 80-DD      | 128-221 | 94                 | User Scratchpad             | User writeable EEPROM. G-P NVRAM; R/W using any valid password.                                                                                                    |

| DE         | 222     | 1                  | ALT_USRCTL                  | Alternate location for USRCTL register. Set bit OEMCFG6-2 to 1 to select this location. Can be used as a scratch pad if not selected.                              |

| DF-F5      | 223-245 | 23                 | User Scratchpad             | User writeable EEPROM. G-P NVRAM; R/W using any valid password.                                                                                                    |

| F6         | 246     | 1                  | USRPWSET                    | User password setting; read/write using any p/w; returns zero otherwise.                                                                                           |

| F7         | 247     | 1                  | USRPW                       | User password register                                                                                                                                             |

| F8-F9      | 248-249 | 2                  | Alarms Masks                | Bit =1: corresponding alarm not masked<br>Bit = 0: corresponding alarm masked                                                                                      |

| FA-FB      | 250-251 | 2                  | Warnings Masks              | Bit =1: corresponding warning not masked<br>Bit = 0: corresponding warning masked                                                                                  |

| FC-FE      | 252-254 | 3                  | Reserved                    | Reserved – do not write; reads undefined.                                                                                                                          |

| FF         | 255     | 1                  | USRCTL                      | End-user control and status bits If ALT-USRCTL is not selected. Can be used as a scratch pad if not selected.                                                      |

Table 2. MIC3002 Address Map, Serial Address = A2<sub>h</sub>

| Address(s) |         | Field Size (Bytes) | Name     | Description                                                                                                                         |

|------------|---------|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| HEX        | DEC     |                    |          |                                                                                                                                     |

| 00-3F      | 0-63    | 64                 | BIASLUT1 | Bias temperature compensation L.U.T. first 64 entries. Additional 12 entries are located in A6: 90-9B.                              |

| 40-7F      | 64-127  | 64                 | MODLUT1  | Modulation temperature compensation L.U.T. first 64 entries. Additional 12 entries are located in A6: A0-AB.                        |

| 80-BF      | 128-191 | 64                 | IFTLUT1  | Bias current fault threshold temperature compensation L.U.T. first 64 entries. Additional 12 entries are located in A6: B0-BB.      |

| C0-FF      | 192-255 | 64                 | HATLUT1  | Bias current high alarm threshold temperature compensation L.U.T. first 64 entries. Additional 12 entries are located in A6: C0-CB. |

Table 3. Temperature Compensation Tables, Serial Address = A4<sub>h</sub>

| Address(s) |       | Field Size (Bytes) | Name     | Description                                                                       |

|------------|-------|--------------------|----------|-----------------------------------------------------------------------------------|

| HEX        | DEC   |                    |          |                                                                                   |

| 00         | 0     | 1                  | OEMCFG0  | OEM configuration register 0                                                      |

| 01         | 1     | 1                  | OEMCFG1  | OEM configuration register 1                                                      |

| 02         | 2     | 1                  | OEMCFG2  | OEM configuration register 2                                                      |

| 03         | 3     | 1                  | APCSET0  | APC setpoint register 0                                                           |

| 04         | 4     | 1                  | APCSET1  | APC setpoint register 1                                                           |

| 05         | 5     | 1                  | APCSET2  | APC setpoint register 2                                                           |

| 06         | 6     | 1                  | MODSET0  | Modulation setpoint register 0                                                    |

| 07         | 7     | 1                  | IBFLT    | Bias current fault-comparator threshold. This register is temperature compensated |

| 08         | 8     | 1                  | TXPFLT   | TX power fault threshold                                                          |

| 09         | 9     | 1                  | LOSFLT   | RX LOS fault-comparator threshold                                                 |

| 0A         | 10    | 1                  | FLTTMR   | Fault comparator timer setting                                                    |

| 0B         | 11    | 1                  | FLTMSK   | Fault source mask bits                                                            |

| 0C-0F      | 12-15 | 4                  | OEMPWSET | Password for access to OEM areas                                                  |

| 10         | 16    | 1                  | OEMCAL0  | OEM calibration register 0                                                        |

| 11         | 17    | 1                  | OEMCAL1  | OEM calibration register 1                                                        |

| 12         | 18    | 1                  | LUTINDX  | Look-up table index read-back                                                     |

| 13         | 19    | 1                  | OEMCFG3  | OEM configuration register 3                                                      |

| 14         | 20    | 1                  | APCDAC   | Reads back current APC DAC value (setpoint+offset)                                |

| 15         | 21    | 1                  | MODDAC   | Reads back current modulation DAC value (setpoint+offset)                         |

| 16         | 22    | 1                  | OEMREAD  | Reads back OEM calibration data                                                   |

| 17         | 23    | 1                  | LOSFLTN  | LOS De-assert threshold                                                           |

| 18         | 24    | 1                  | RXPOT    | RXPOT tap selection                                                               |

| 19         | 25    | 1                  | OEMCFG4  | OEM configuration register 4                                                      |

| 1A         | 26    | 1                  | OEMCFG5  | OEM configuration register 5                                                      |

| 1B         | 27    | 1                  | OEMCFG6  | OEM configuration register 6                                                      |

| 1C-1D      | 28-29 | 2                  | SCRATCH  | Reserved – do not write; reads undefined.                                         |

| 1E         | 30    | 1                  | MODSET 1 | Modulation setpoint register 1                                                    |

| 1F         | 31    | 1                  | MODSET 2 | Modulation setpoint register 2                                                    |

|       |         |     |                  |                                                                                                                 |

|-------|---------|-----|------------------|-----------------------------------------------------------------------------------------------------------------|

| 20-27 | 32-39   | 8   | POHDATA          | Power-on hour meter scratchpad                                                                                  |

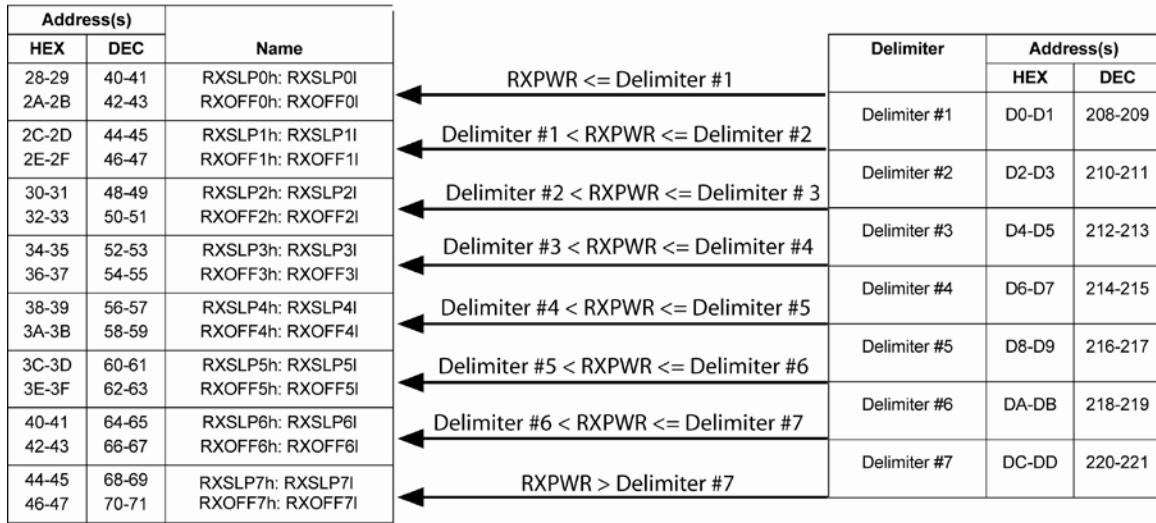

| 28-47 | 40-71   | 32  | RXLUT            | RX power calibration look-up table. Eight sets of slope and offset                                              |

| 48-57 | 72-87   | 16  | CALCOEF          | Slope and offset coefficients used for Temperature, Voltage, Bias, and TXPOWER internal calibration             |

| 58-5F | 88-95   | 8   | SCRATCH          | OEM scratchpad area                                                                                             |

| 60-86 | 96-134  | 39  | TCTRLUT          | LUT to temperature-compensate temperature results and/or temperature to be used by parameters compensation LUT. |

| 87-8F | 135-143 | 9   | SCRATCH          | OEM scratchpad area.                                                                                            |

| 90-9B | 144-155 | 12  | BIASLUT2         | Bias temperature compensation L.U.T. additional 12 entries.                                                     |

| 9C-9F | 156-159 | 4   | SCRATCH          | OEM scratchpad area                                                                                             |

| A0-AB | 160-171 | 12  | MODLUT2          | Modulation temperature compensation L.U.T. additional 12 entries.                                               |

| AC-AF | 172-175 | 14  | SCRATCH          | OEM scratchpad area.                                                                                            |

| B0-BB | 176-187 | 12  | IFTLUT2          | Bias current fault threshold temperature compensation L.U.T. additional 12 entries.                             |