May 2008

# FAN2103 — TinyBuck™ 3A, 24V Input, Integrated Synchronous Buck Regulator

#### **Features**

- 3A Output Current

- Over 95% Efficiency

- Fully Synchronous Operation with Integrated Schottky Diode on Low-side MOSFET Boosts Efficiency

- Programmable Frequency Operation (200KHz to 600KHz)

- Power-good Signal

- Accepts Ceramic Capacitors on Output

- External Compensation for Flexible Design

- Wide Input Range: 3V to 24V

- Output Voltage Range: 0.8V to 90%V<sub>IN</sub>

- Input Under-voltage Lockout

- Programmable Over-current Limit

- Under-voltage, Over-voltage, and Thermal Protections

- 5x6mm, 25-pin, 3-pad MLP

## **Applications**

- Graphics Cards

- Battery-powered Equipment

- Set-top Boxes

- Point-of-load Regulation

- Servers

# Description

The FAN2103 TinyBuck™ is an easy-to-use, cost- and space-efficient, 3A synchronous buck solution. It enables designers to solve high current requirements in a small area with minimal external components.

External compensation, programmable switching frequency, and current limit features allow for design optimization and flexibility.

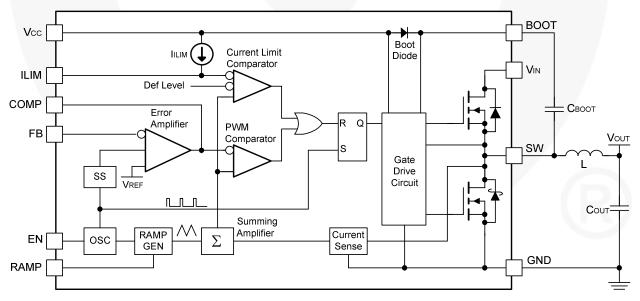

The summing current mode modulator uses lossless current sensing for current feedback and over-current, and includes voltage feedforward.

Fairchild's advanced BiCMOS power process, combined with low R<sub>DS(ON)</sub> internal MOSFETs and a thermally efficient MLP package provide the ability to dissipate high power in a small package.

Output over-voltage, under-voltage, and thermal shutdown protections plus power-good, help protect the devices from damage during fault conditions.

## **Related Application Notes**

AN-5067 – PCB Land Pattern Design and Surface Mount Guidelines for MLP Packages

## **Ordering Information**

| Part Number | Operating<br>Temperature Range | Package                                    | Eco Status | Packing<br>Method |

|-------------|--------------------------------|--------------------------------------------|------------|-------------------|

| FAN2103MPX  | -10°C to 85°C                  | 25-Pin Molded Leadless Package (MLP) 5x6mm | Green      | Tape and Reel     |

| FAN2103EMPX | -40°C to 85°C                  | 25-Pin Molded Leadless Package (MLP) 5x6mm | Green      | Tape and Reel     |

For Fairchild's definition of "green" please visit: <a href="http://www.fairchildsemi.com/company/green/rohs\_green.html">http://www.fairchildsemi.com/company/green/rohs\_green.html</a>.

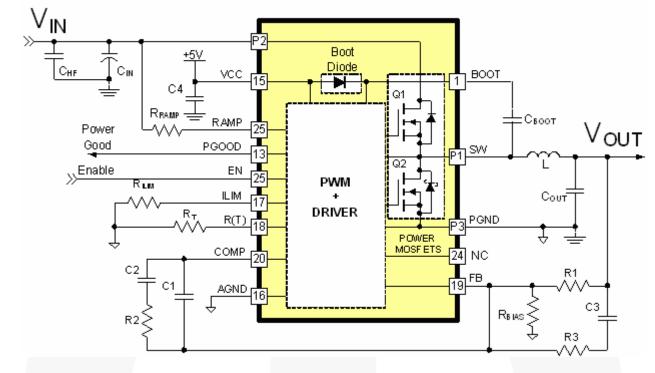

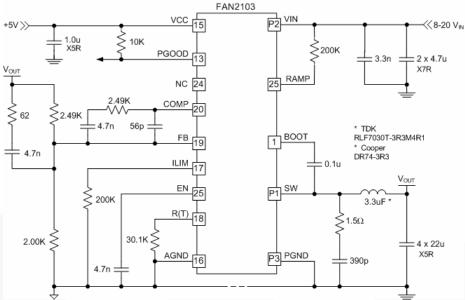

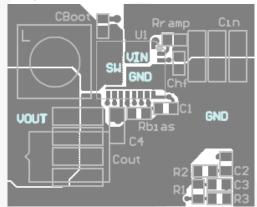

# **Typical Application Diagram**

Figure 1. Typical Application

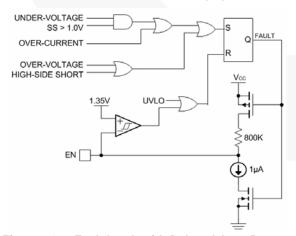

# **Block Diagram**

Figure 2. Block Diagram

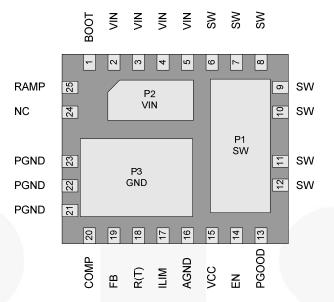

# **Pin Configuration**

Figure 3. MLP 5x6mm Pin Configuration (Bottom View)

# **Pin Definitions**

| Pin       | Name  | Description                                                                                                                                                                                                                                                                |  |  |  |

|-----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P1, 6-12  | SW    | Switching Node.                                                                                                                                                                                                                                                            |  |  |  |

| P2, 2-5   | VIN   | Power Input Voltage. Connect to the main input power source.                                                                                                                                                                                                               |  |  |  |

| P3, 21-23 | PGND  | Power Ground. Power return and Q2 source.                                                                                                                                                                                                                                  |  |  |  |

| 1         | воот  | <b>High-side Drive BOOT Voltage</b> . Connect through capacitor ( $C_{\text{BOOT}}$ ) to SW. The IC includes an internal synchronous bootstrap diode to recharge the capacitor on this pin to $V_{\text{CC}}$ when SW is LOW.                                              |  |  |  |

| 13        | PGOOD | <b>Power-Good Flag</b> . An open-drain output that pulls LOW when FB is outside a ±10% range of the reference when EN is HIGH. PGOOD does not assert HIGH until the fault latch is enabled.                                                                                |  |  |  |

| 14        | EN    | NABLE. Enables operation when pulled to logic HIGH or left open. Toggling EN resets the egulator after a latched fault condition. This input has an internal pull-up when the IC is incitioning normally. When a latched fault occurs, EN is discharged by a current sink. |  |  |  |

| 15        | VCC   | nput Bias Supply for IC. The IC's logic and analog circuitry are powered from this pin.                                                                                                                                                                                    |  |  |  |

| 16        | AGND  | nalog Ground. The signal ground for the IC. All internal control voltages are referred to his pin. Tie this pin to the ground island/plane through the lowest impedance connection.                                                                                        |  |  |  |

| 17        | ILIM  | <b>Current Limit</b> . A resistor (R <sub>ILIM</sub> ) from this pin to AGND can be used to program the current-mit trip threshold lower than the default setting.                                                                                                         |  |  |  |

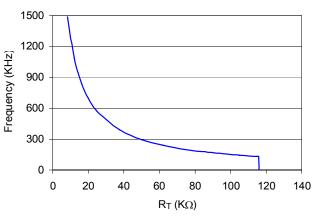

| 18        | R(T)  | <b>Oscillator Frequency</b> . A resistor (R <sub>T</sub> ) from this pin to AGND sets the PWM switching frequency.                                                                                                                                                         |  |  |  |

| 19        | FB    | Output Voltage Feedback. Connect through a resistor divider to the output voltage.                                                                                                                                                                                         |  |  |  |

| 20        | COMP  | Compensation. Error amplifier output. Connect the external compensation network between this pin and FB.                                                                                                                                                                   |  |  |  |

| 24        | NC    | No Connect. This pin is not used.                                                                                                                                                                                                                                          |  |  |  |

| 25        | RAMP  | Ramp Amplitude. A resistor (R <sub>RAMP</sub> ) connected from this pin to VIN sets the ramp amplitude and provides voltage feedforward functionality.                                                                                                                     |  |  |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Parameter      | Conditions                        | Min. | Max.                 | Unit  |

|----------------|-----------------------------------|------|----------------------|-------|

| VIN to PGND    |                                   |      | 28                   | V     |

| VCC to AGND    | AGND = PGND                       |      | 6                    | V     |

| BOOT to PGND   |                                   |      | 35                   | V     |

| BOOT to SW     |                                   | -0.3 | 6.0                  | V     |

| SW to PGND     | Transient (t < 20ns, f < 600KHz)  | -5   | 30                   | V     |

| All other pins |                                   | -0.3 | V <sub>CC</sub> +0.3 | V     |

| ESD            | Human Body Model, JESD22-A114     | 2    |                      | kV    |

| ESD            | Charged Device Model, JESD22-C101 | 2    |                      | NV NV |

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol          | Parameter            | Conditions  | Min. | Тур. | Max. | Unit |

|-----------------|----------------------|-------------|------|------|------|------|

| V <sub>CC</sub> | Bias Voltage         | VCC to AGND | 4.5  | 5.0  | 5.5  | V    |

| $V_{IN}$        | Supply Voltage       | VIN to PGND | 3    |      | 24   | V    |

| TA              | Ambient Temperature  | FAN2103M    | -10  |      | +85  | °C   |

| IA              | Ambient Temperature  | FAN2103EM   | -40  |      | +85  | °C   |

| TJ              | Junction Temperature |             |      |      | +125 | °C   |

## **Thermal Information**

| Symbol            | Parameter                                        |         | Min. | Тур.              | Max.               | Unit |

|-------------------|--------------------------------------------------|---------|------|-------------------|--------------------|------|

| T <sub>STG</sub>  | Storage Temperature                              |         | -65  |                   | +150               | °C   |

| TL                | Lead Soldering Temperature, 10 Seconds           |         |      |                   | +300               | °C   |

| T <sub>VP</sub>   | Vapor Phase, 60 Seconds                          |         |      |                   | +215               | °C   |

| Tı                | Infrared, 15 Seconds                             |         |      |                   | +220               | °C   |

|                   |                                                  |         |      | 4                 |                    | °C/W |

| $\theta_{\sf JC}$ | Thermal Resistance: Junction-to-Case             | P2 (Q1) |      | 7                 |                    | °C/W |

|                   | P3                                               |         |      | 4                 |                    | °C/W |

| Өл-РСВ            | Thermal Resistance: Junction-to-Mounting Surface |         |      | 35 <sup>(1)</sup> |                    | °C/W |

| P <sub>D</sub>    | Power Dissipation, T <sub>A</sub> = 25°C         |         |      |                   | 2.8 <sup>(1)</sup> | W    |

#### Note:

1. Typical thermal resistance when mounted on a four-layer, two-ounce PCB, as shown in Figure 25. Actual results are dependent on mounting method and surface related to the design.

# **Electrical Specifications**

Recommended operating conditions are the result of using the circuit shown in Figure 1 unless otherwise noted.

| Parameter                             | Conditions                                                    | Min. | Тур. | Max. | Unit              |

|---------------------------------------|---------------------------------------------------------------|------|------|------|-------------------|

| Power Supplies                        |                                                               | 4    | •    | -1   |                   |

| V <sub>CC</sub> Current               | SW = Open, FB = 0.7V, $V_{CC}$ = 5V, $f_{SW}$ = 600KHz        |      | 8    | 12   | mA                |

|                                       | Shutdown: EN = 0, V <sub>CC</sub> = 5V                        |      | 7    | 10   | μΑ                |

| V INA Threshold                       | Rising V <sub>CC</sub>                                        | 4.1  | 4.3  | 4.5  | V                 |

| V <sub>CC</sub> UVLO Threshold        | Hysteresis                                                    |      | 300  |      | mV                |

| Oscillator                            |                                                               | •    |      |      |                   |

| -                                     | $R_T = 50K\Omega$                                             | 255  | 300  | 345  | KHz               |

| Frequency                             | $R_T = 24K\Omega$                                             | 540  | 600  | 660  | KHz               |

| Minimum On-Time <sup>(2)</sup>        |                                                               |      | 50   | 65   | ns                |

| Ramp Amplitude, pk–pk                 | $16V_{IN}$ , $1.8V_{OUT}$ , $R_T = 30KΩ$ , $R_{RAMP} = 200KΩ$ |      | 0.53 |      | V                 |

| Minimum Off-Time <sup>(2)</sup>       |                                                               |      | 100  | 150  | ns                |

| Reference                             |                                                               |      | •    |      |                   |

| 5.6                                   | FAN2103M, 25°C                                                | 794  | 800  | 806  | mV                |

| Reference Voltage (V <sub>FB</sub> )  | FAN2103EM, 25°C                                               | 795  | 800  | 805  | mV                |

| T O #i-it                             | FAN2103M, -10 to +85°C                                        |      | 50   |      | PPM               |

| Temperature Coefficient               | FAN2103EM, -40 to +85°C                                       |      | 70   |      | PPM               |

| Error Amplifier                       |                                                               | 1    |      | •    |                   |

| DC Gain <sup>(2)</sup>                |                                                               | 80   | 85   |      | dB                |

| Gain Bandwidth Product <sup>(2)</sup> | V <sub>CC</sub> = 5V                                          | 12   | 15   |      | MHz               |

| Output Voltage (V <sub>COMP</sub> )   |                                                               | 0.4  |      | 3.2  | V                 |

| Output Current, Sourcing              | V <sub>CC</sub> = 5V, V <sub>COMP</sub> = 2.2V                | 1.5  | 2.2  |      | mA                |

| Output Current, Sinking               | V <sub>CC</sub> = 5V, V <sub>COMP</sub> = 1.2V                | 0.8  | 1.2  |      | mA                |

| FB Bias Current                       | V <sub>FB</sub> = 0.8V, 25°C                                  | -850 | -650 | -450 | nA                |

| Protection and Shutdown               |                                                               |      |      |      |                   |

| Current Limit                         | R <sub>ILIM</sub> open                                        | 3.8  | 5.0  | 7.0  | Α                 |

| I <sub>LIM</sub> Current              | 25°C, V <sub>CC</sub> = 5V                                    | 9    | 10   | 11   | μΑ                |

| Over-Temperature Shutdown             | Internal IC Temperature                                       |      | +160 |      | °C                |

| Over-Temperature Hysteresis           | Internal IC Temperature                                       |      | +30  |      | °C                |

| Over-Voltage Threshold                | 2 Consecutive Clock Cycles                                    | 110  | 115  | 120  | %V <sub>OUT</sub> |

| Under-Voltage Shutdown                | 16 Consecutive Clock Cycles                                   | 68   | 73   | 78   | %V <sub>OUT</sub> |

| Fault Discharge Threshold             | Measured at FB Pin                                            |      | 250  |      | mV                |

| Fault Discharge Hysteresis            | Measured at FB Pin (V <sub>FB</sub> ~500mV)                   |      | 250  |      | mV                |

| Soft-Start                            |                                                               |      |      |      |                   |

| V <sub>OUT</sub> to Regulation (T0.8) | Fraguency = 600KH=                                            |      | 5.3  |      | ms                |

| Fault Enable/SSOK (T1.0)              | Frequency = 600KHz                                            |      | 6.7  |      | ms                |

#### Note:

2. Specifications guaranteed by design and characterization; not production tested.

# **Electrical Specifications** (Continued)

Recommended operating conditions are the result of using the circuit shown in Figure 1 unless otherwise noted.

| Parameter                       | Conditions             | Min. | Тур. | Max. | Unit              |

|---------------------------------|------------------------|------|------|------|-------------------|

| Control Functions               | •                      | ·    |      |      |                   |

| EN Threshold, Rising            |                        |      | 1.35 | 2.00 | V                 |

| EN Hysteresis                   |                        |      | 250  |      | mV                |

| EN Pull-up Resistance           |                        |      | 800  |      | ΚΩ                |

| EN Discharge Current            | Auto-restart Mode      |      | 1    |      | μΑ                |

| FB OK Drive Resistance          |                        |      |      | 800  | Ω                 |

| PGOOD Threshold                 | FB < V <sub>REF</sub>  | -14  | -11  | -8   | %V <sub>REF</sub> |

| (Compared to V <sub>REF</sub> ) | FB > V <sub>REF</sub>  | +7   | +10  | +13  | %V <sub>REF</sub> |

| PGOOD Output Low                | I <sub>OUT</sub> ≤ 2mA | -/   |      | 0.4  | V                 |

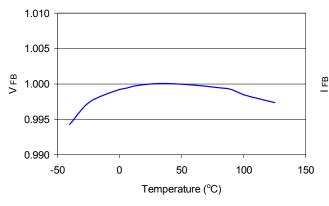

# **Typical Characteristics**

1.10

1.00

0.90

0.80

-50

0

50

100

150

Temperature (°C)

Figure 4. Reference Voltage (V<sub>FB</sub>) vs. Temperature, Normalized

Figure 5. Reference Bias Current (I<sub>FB</sub>) vs. Temperature, Normalized

Figure 6. Frequency vs. R<sub>T</sub>

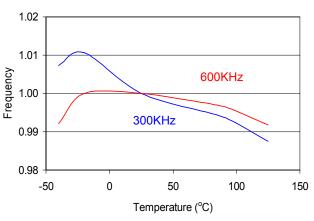

Figure 7. Frequency vs. Temperature, Normalized

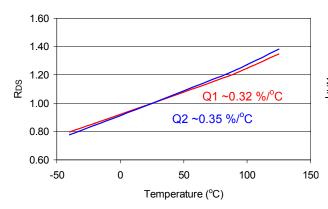

Figure 8.  $R_{DS}$  vs. Temperature, Normalized  $(V_{CC} = V_{GS} = 5V)$

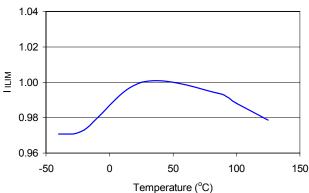

Figure 9. I<sub>LIM</sub> Current (I<sub>ILIM</sub>) vs. Temperature, Normalized

## **Application Circuit**

Figure 10. Application Circuit: 1.8 Vout, 500KHz

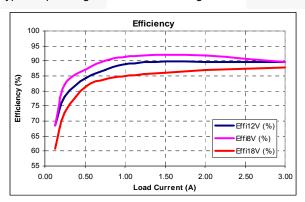

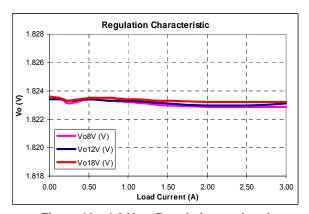

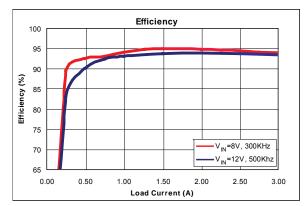

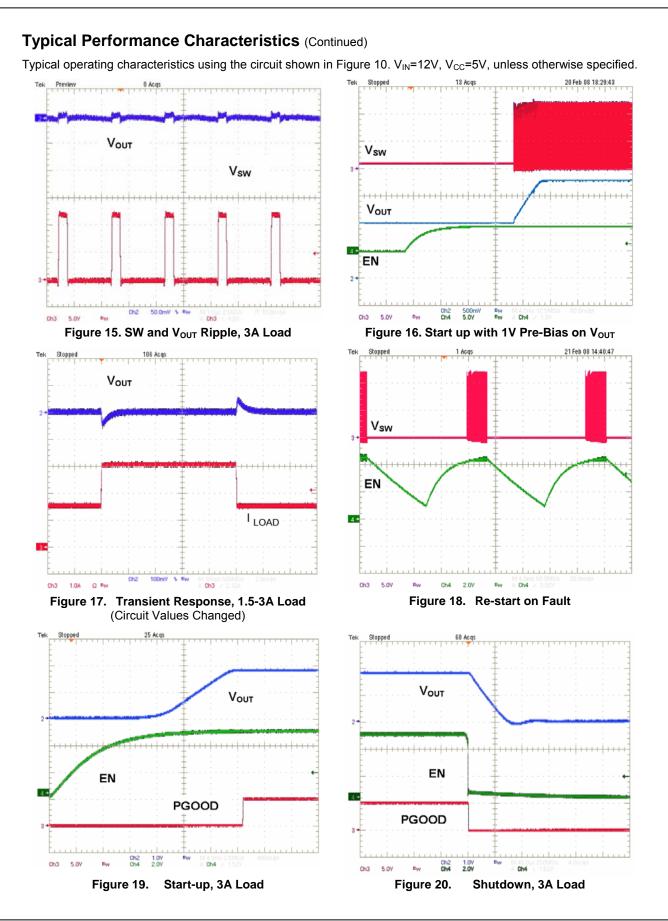

# **Typical Performance Characteristics**

Typical operating characteristics using the circuit shown in Figure 10. V<sub>IN</sub>=16V, V<sub>CC</sub>=5V, unless otherwise specified.

1.0 0.9 Loss12V (W) 0.8 Loss8V (W) 0.7 0.6 Loss (W) 0.5 0.4 0.2 0.0 0.00 0.50 1.00 1.50 2.00 2.50 3.00 Load Current (A)

Figure 11. 1.8 V<sub>OUT</sub> Efficiency Over V<sub>IN</sub> vs. Load

Figure 13.  $1.8 V_{OUT}$  Regulation vs. Load

Figure 12. 1.8 V<sub>OUT</sub> Dissipation Over V<sub>IN</sub> vs. Load

Figure 14. 3.3 V<sub>OUT</sub> Efficiency vs. Load (Circuit Values Changed)

## **Circuit Description**

#### Initialization

Once  $V_{CC}$  exceeds the UVLO threshold and EN is HIGH, the IC checks for an open or shorted FB pin before releasing the internal soft-start ramp (SS).

If R1 is open (as shown in Figure 1), the error amplifier output (COMP) is forced LOW and no pulses are generated. After the SS ramp times out (T1.0), an undervoltage latched fault occurs.

If the parallel combination of R1 and  $R_{\text{BIAS}}$  is  $\leq 1 K \Omega,$  the internal SS ramp is not released and the regulator does not start.

#### Soft-Start

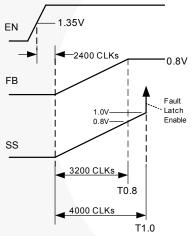

Once internal SS ramp has charged to 0.8V (T0.8), the output voltage is in regulation. Until SS ramp reaches 1.0V (T1.0), the "Fault Latch" is inhibited.

To avoid skipping the soft-start cycle, it is necessary to apply  $V_{\text{IN}}$  before  $V_{\text{CC}}$  reaches its UVLO threshold.

Soft-start time is a function of oscillator frequency.

Figure 21. Soft-Start Timing Diagram

The regulator does not allow the low-side MOSFET to operate in full synchronous rectification mode until internal SS ramp reaches 95% of  $V_{\text{REF}}$  (~0.76V). This helps the regulator start against pre-biased outputs (as shown in Figure 16) and ensures that inductor current does not "ratchet" up during the soft-start cycle.

$\mbox{V}_{\mbox{\footnotesize CC}}$  UVLO or toggling the EN pin discharges the SS and resets the IC.

#### **Bias Supply**

The FAN2103 requires a 5V supply rail to bias the IC and provide gate-drive energy and controller power. Connect a  $\geq 1.0 \mu f$  X5R or X7R decoupling capacitor between VCC and PGND. Whenever the EN pin is pulled up to V<sub>CC</sub>, the 5V supply connected to V<sub>CC</sub> should be turned ON after V<sub>IN</sub> comes up. If the power supply is turned ON using EN pin with an external control after V<sub>CC</sub> and V<sub>IN</sub> come up, the V<sub>CC</sub> and V<sub>IN</sub> power sequencing is not relevant.

Since  $V_{CC}$  is used to drive the internal MOSFET gates, supply current is frequency and voltage dependent. Approximate  $V_{CC}$  current ( $I_{CC}$ ) can be calculated using:

$$I_{CC(mA)} = 4.58 + \left[ \left( \frac{V_{CC} - 5}{227} + 0.013 \right) \bullet (f - 128) \right] \tag{1}$$

where frequency (f) is expressed in KHz.

Setting the Output Voltage

The output voltage of the regulator can be set from 0.8V to  $\sim\!\!80\%$  of  $V_{\text{IN}}$  by an external resistor divider (R1 and R<sub>BIAS</sub> in Figure 1).

The internal reference is 0.8V with 650nA, sourced from the FB pin to ensure that if the pin is open, the regulator does not start.

The external resistor divider is calculated using:

$$\frac{0.8V}{R_{BIAS}} = \frac{V_{OUT} - 0.8V}{R1} + 650nA$$

(2)

Connect R<sub>BIAS</sub> between FB and AGND.

## **Setting the Frequency**

Oscillator frequency is determined by an external resistor,  $R_T$  connected between the R(T) pin and AGND:

$$f_{(KHz)} = \frac{10^6}{(65 \cdot R_T) + 135} \tag{3}$$

where  $R_T$  is expressed in  $K\Omega$ .

$$R_{T(K\Omega)} = \frac{(10^6 / f) - 135}{65} \tag{4}$$

where frequency (f) is expressed in KHz.

The regulator does not start if R<sub>T</sub> is left open.

## **Calculating the Inductor Value**

Typically the inductor is set for a ripple current ( $\Delta I_L$ ) of 10% to 35% of the maximum DC load. Regulators requiring fast transient response use a value on the high side of this range, while regulators that require very low output ripple and/or use high-ESR capacitors restrict allowable ripple current:

$$\Delta IL = \frac{V_{OUT} \bullet (1 - D)}{L \bullet f} \tag{5}$$

where f is the oscillator frequency and:

$$L = \frac{V_{OUT} \bullet (1 - D)}{\Delta I L \bullet f} \tag{6}$$

## **Setting the Ramp Resistor Value**

The internal ramp voltage excursion ( $\Delta V_{RAMP}$ ) during  $t_{ON}$  should be set to 0.6V.  $R_{RAMP}$  is approximately:

$$R_{RAMP(K\Omega)} = \frac{(V_{IN} - 1.8) \bullet V_{OUT}}{18x10^{-6} \bullet V_{IN} \bullet f} - 2$$

(7)

where frequency (f) is expressed in KHz.

## **Setting the Current Limit**

There are two levels of current-limit thresholds in FAN2103. The first level of protection is through an internal default limit set at the factory to limit output current beyond normal usage levels. The second level of protection is a flexible one to be set externally by the user. Current-limit protection is enabled whenever the lower of the two thresholds is reached. The FAN2103 uses its internal low-side MOSFET for current-sensing. The current-limit threshold voltage (VILIM) is compared to the voltage drop across the low-side MOSFET, sampled at the end of each PWM off-time/cycle. The internal default threshold (with ILIM open) is temperature compensated.

The  $10\mu A$  current sourced from the ILIM pin can be used to establish a lower, temperature–dependent, current-limit threshold by connecting an external resistor ( $R_{ILIM}$ ) to AGND:

$$R_{ILIM(K\Omega)} = 10.4 \bullet K_{T} \bullet (I_{OUT} - \frac{\Delta IL}{2}) + 142.5$$

(8)

where:

$I_{OUT}$  = desired current limit set point in Amps,  $K_T$  = the normalized temperature coefficient of the low-side MOSFET (Q2) from Figure 8.

After 16 consecutive, pulse-by-pulse, current-limit cycles, the fault latch is set and the regulator shuts down. Cycling  $V_{CC}$  or EN restores operation after a normal soft-start cycle (refer to Auto-Restart section).

The over-current protection fault latch is active during the soft-start cycle. Use a 1% resistor for  $R_{\text{ILIM}}$ .

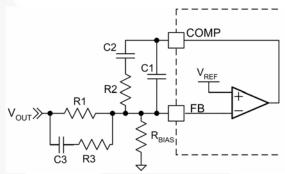

#### **Loop Compensation**

The loop is compensated using a feedback network around the error amplifier. Figure 22 shows a complete Type-3 compensation network. Type-2 compensation eliminates R3 and C3.

Figure 22. Compensation Network

Because the FAN2103 employs summing current-mode architecture, Type-2 compensation can be used for many applications. For applications that require wide loop bandwidth and/or use very low-ESR output capacitors, Type-3 compensation may be required.

$R_{RAMP}$  provides feedforward compensation for changes in  $V_{IN}$ . With a fixed  $R_{RAMP}$  value, the modulator gain increases as  $V_{IN}$  is reduced, which could make it difficult to compensate the loop. For designs with low input voltages (3V to 6.5V), it is recommended that a separate  $R_{RAMP}$  and the compensation component values are used as compared to designs with  $V_{IN}$  between 6.5V and 24V.

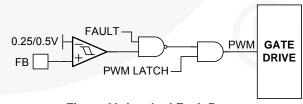

#### **Protection**

The converter output is monitored and protected against extreme overload, short-circuit, over-voltage, and under-voltage conditions.

An internal "Fault Latch" is set for any fault intended to shut down the IC. When the fault latch is set, the IC discharges  $V_{\text{OUT}}$  by enhancing the low-side MOSFET until FB<0.25V. The MOSFET is not turned on again unless FB>0.5V. This behavior discharges the output without causing undershoot (negative output voltage).

Figure 23. Latched Fault Response

#### **Under-Voltage Shutdown**

If FB remains below the under-voltage threshold for 16 consecutive clock cycles, the fault latch is set and the converter shuts down. This fault is prevented from setting the fault latch during soft-start.

## **Over-Voltage Protection / Shutdown**

If FB exceeds 115% • V<sub>REF</sub> for two consecutive clock cycles, the fault latch is set and shutdown occurs.

A shorted high-side MOSFET condition is detected when SW voltage exceeds ~0.7V while the low-side MOSFET is fully enhanced. The fault latch is set immediately upon detection.

The two fault protection circuits above are active all the time, including during soft-start.

#### **Auto-Restart**

After a fault, EN is discharged with  $1\mu A$  to a 1.1V threshold before the  $800 K\Omega$  pull-up is restored. A new soft-start cycle begins when EN charges above 1.35V.

Depending on the external circuit, the FAN2103 can be provisioned to remain latched-off or automatically restart after a fault.

Table 1. Fault / Restart Provisioning

| EN pin                                                      | Controller / Restart State                                           |

|-------------------------------------------------------------|----------------------------------------------------------------------|

| Pull to GND                                                 | OFF (disabled)                                                       |

| V <sub>CC</sub> No restart – latched OFF (after V comes up) |                                                                      |

| Open                                                        | Immediate restart after fault                                        |

| Cap to GND                                                  | New soft-start cycle after:<br>t <sub>DELAY</sub> (ms) = 3.9 • C(nf) |

With EN left open, restart is immediate.

If auto-restart is not desired, tie the EN pin to the VCC pin or pull it high after  $V_{CC}$  comes up with a logic gate to keep the 1µA current sink from discharging EN to 1.1V.

Figure 24. Fault Latch with Delayed Auto-Restart

#### **Over-Temperature Protection**

FAN2103 incorporates an over-temperature protection circuit that sets the fault latch when a die temperature of about 160°C is reached. The IC is allowed to restart when the die temperature falls below 130°C.

## Power Good (PGOOD) Signal

PGOOD is an open-drain output that asserts LOW when  $V_{OUT}$  is out of regulation, as measured at the FB pin (thresholds are specified in the Electrical Specifications section). PGOOD does not assert HIGH until the fault latch is enabled (T1.0).

#### **PCB** Layout

Figure 25. Recommended PCB Layout

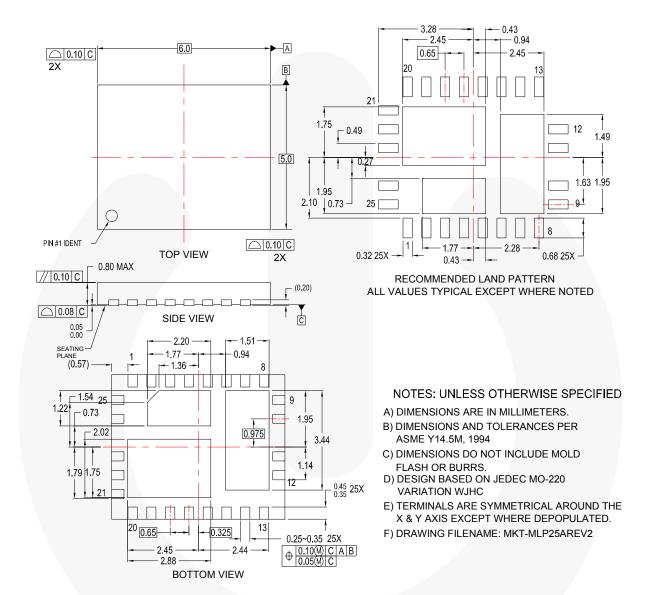

## **Physical Dimensions**

Figure 26. 5x6mm Molded Leadless Package (MLP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

ACEx<sup>®</sup> Build it Now™ CorePLUS™ CorePOWER™ CROSSVOL™ CTL™

Current Transfer Logic™ EcoSPARK®

EfficentMax™ EZSWITCH™ \*

Fairchild®

Fairchild Semiconductor® FACT Quiet Series™ FACT®

FAST® FastvCore™ FlashWriter®\* FPS™ F-PFS™ FRFET®

Global Power Resources

Green FPS™ Green FPS™e-Series™

GTO™ IntelliMAX™ ISOPLANAR™ MegaBuck™

MICROCOUPLER™ MicroFET™ MicroPak™

MillerDrive™ MotionMax™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR® PDP SPM™ Power-SPM™ PowerTrench®

Programmable Active Droop™ QFET®

QSTM

Quiet Series™ RapidConfigure™

Saving our world, 1mW at a time™

SmartMax™ SMART START™

SPM<sup>®</sup>

STEALTH™ SuperFET™ SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS™

SyncFET™ SYSTEM ®

The Power Franchise® p wer

TinyBoost™ TinyBuck™ TinýLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ uSerDes™

UHC Ultra FRFET™ UniFET™ VCX™ VisualMax™

\* EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- 1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support, which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                               |

|--------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | This datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 134