# SIEMENS

---

## ICs for Communications

ISDN Subscriber Access Controller for Terminals

ISAC<sup>®</sup>-S TE

PSB 2186

**PEB 2186**

**Revision History: 10.94**

Previous Releases: **11.88; 3.89; 12.89; 02.95**

| Page | Subjects (changes since last revision)                                         |

|------|--------------------------------------------------------------------------------|

|      | The present documentation is an editorial update of the Technical Manual 12.89 |

## **Data Classification**

### **Maximum Ratings**

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

### **Characteristics**

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25^\circ\text{C}$  and the given supply voltage.

### **Operating Range**

In the operating range the functions given in the circuit description are fulfilled.

For detailed technical information about “**Processing Guidelines**” and “**Quality Assurance**” for ICs, see our “**Product Overview**”.

## **Edition 10.94**

This edition was realized using the software system FrameMaker®

**Published by Siemens AG, Breech Belittler, Marketing-Communication,

Banisters 73, D-81541 Munching.**

© Siemens AG 1994. All Rights Reserved.

As far as patents or other rights of third parties are concerned, liability is only assumed for components per se, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery, and prices please contact the Offices of Semiconductor Group in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the type in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

---

| <b>Table of Contents</b> |                                           | <b>Page</b> |

|--------------------------|-------------------------------------------|-------------|

| <b>1</b>                 | <b>Features</b>                           | 8           |

| 1.1                      | Pin Definitions and Functions             | 11          |

| 1.2                      | Logic Symbol                              | 14          |

| 1.3                      | Functional Block Diagram                  | 15          |

| 1.4                      | System Integration                        | 16          |

| 1.4.1                    | ISDN Applications                         | 16          |

| 1.4.2                    | Microprocessor Environment                | 19          |

| <b>2</b>                 | <b>Functional Description</b>             | 21          |

| 2.1                      | General Functions and Device Architecture | 21          |

| 2.2                      | Interface and Operating Modes             | 22          |

| 2.3                      | IOM®-2 Mode Functions                     | 24          |

| 2.3.1                    | Basic IOM®-2 Frame Structure              | 24          |

| 2.3.2                    | IOM®-2 Interface Connections              | 26          |

| 2.3.3                    | mP Access to B and IC Channels            | 30          |

| 2.3.4                    | MONITOR Channel Handling                  | 36          |

| 2.3.5                    | C/I-Channel Handling                      | 40          |

| 2.3.6                    | TIC-Bus Access                            | 41          |

| 2.4                      | Layer-1 Functions for the S/T Interface   | 44          |

| 2.4.1                    | S/T Interface                             | 46          |

| 2.4.2                    | Analog Functions                          | 47          |

| 2.4.3                    | S/T-Interface Circuitry                   | 48          |

| 2.4.4                    | S/T Interface Pre-Filter Compensation     | 49          |

| 2.4.5                    | Receiver Functions                        | 50          |

| 2.4.5.1                  | Receive Signal Oversampling               | 50          |

| 2.4.5.2                  | Adaptive Receiver Characteristics         | 51          |

| 2.4.5.3                  | Level Detection Power Down                | 52          |

| 2.4.6                    | Timing Recovery                           | 52          |

| 2.4.7                    | Activation/Deactivation                   | 53          |

| 2.4.7.1                  | FAinfA_1fr                                | 53          |

| 2.4.7.2                  | FAinfB_1fr                                | 54          |

| 2.4.7.3                  | FAinfD_1fr                                | 54          |

| 2.4.7.4                  | FAinfA_kfr                                | 55          |

| 2.4.7.5                  | FAinfB_kfr                                | 55          |

---

| <b>Table of Contents</b>                                                 | <b>Page</b> |

|--------------------------------------------------------------------------|-------------|

| 2.4.7.6 FAinfD_kfr .....                                                 | 56          |

| 2.4.7.7 FAregain .....                                                   | 56          |

| 2.4.8 D-Channel Access .....                                             | 57          |

| 2.4.9 S- and Q-Channel Access .....                                      | 58          |

| 2.5 Terminal Specific Functions .....                                    | 60          |

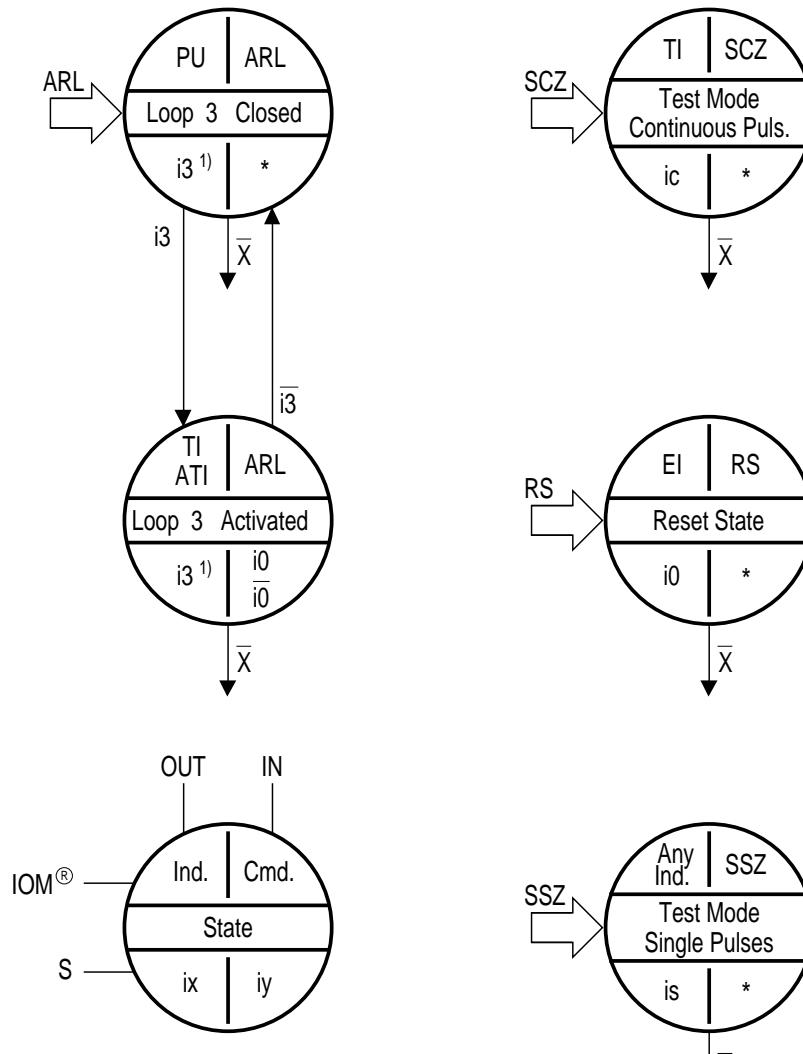

| 2.6 Test Functions .....                                                 | 62          |

| 2.7 Layer-2 Functions for the ISDN-Basic Access .....                    | 63          |

| 2.7.1 Message Transfer Modes .....                                       | 64          |

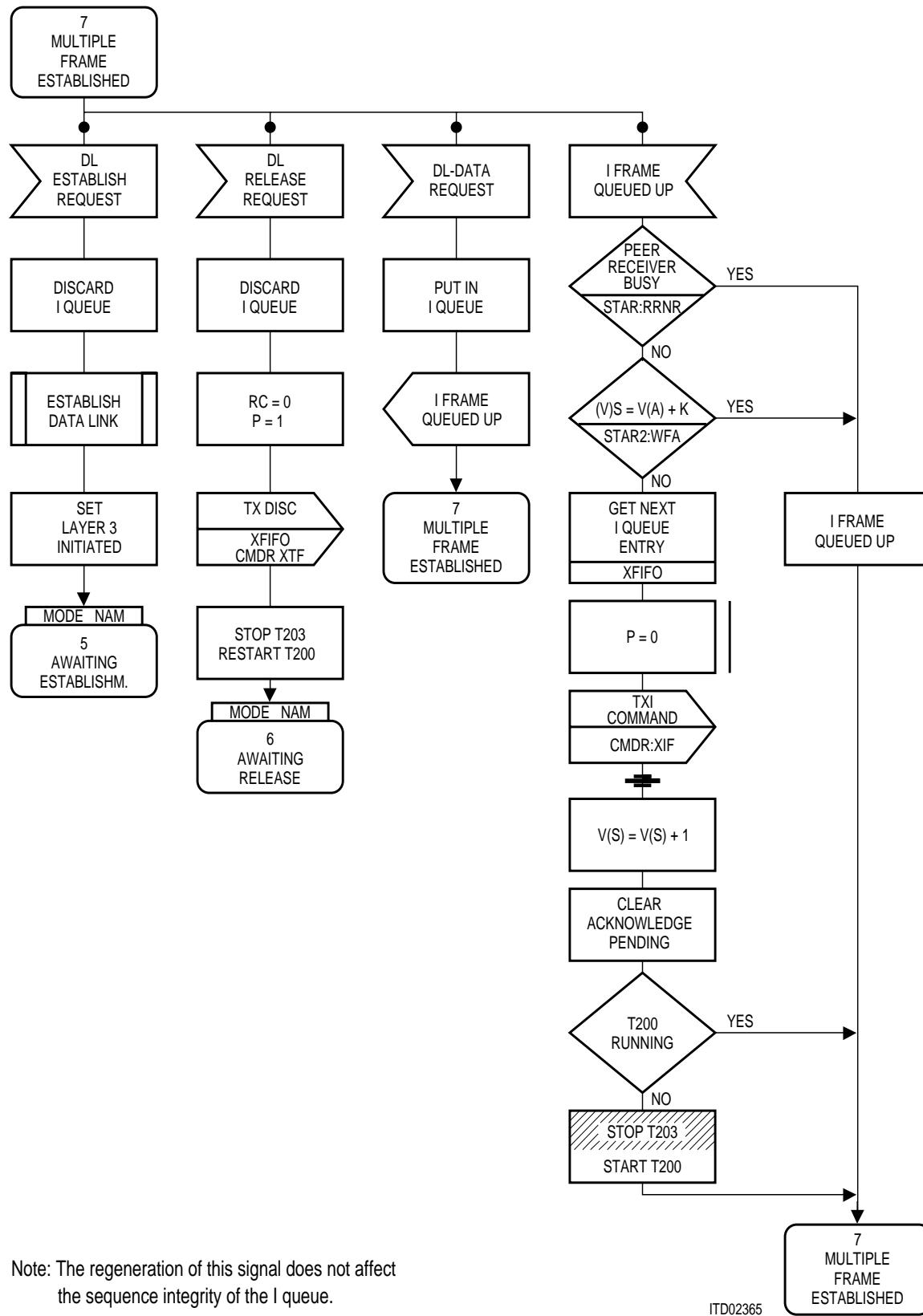

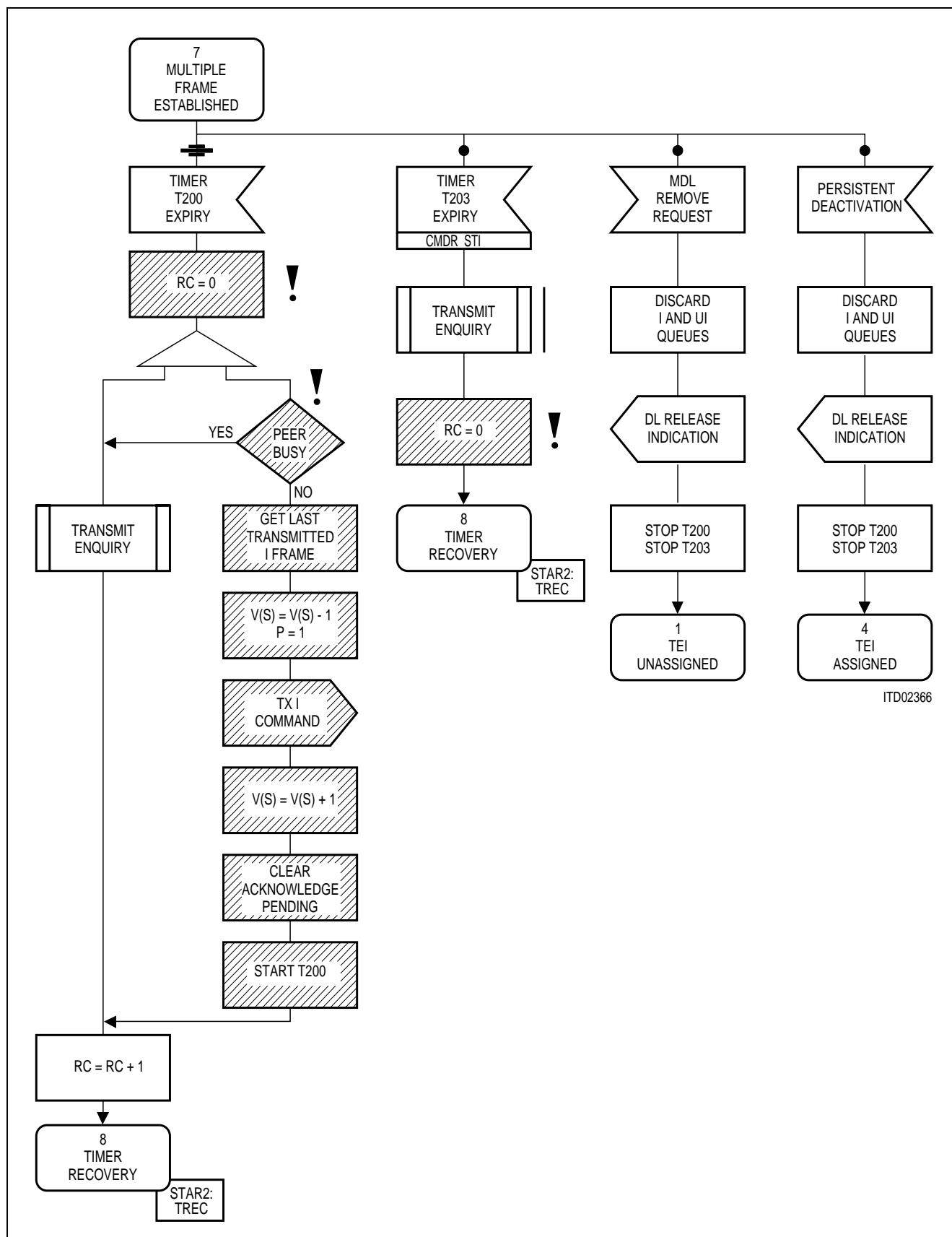

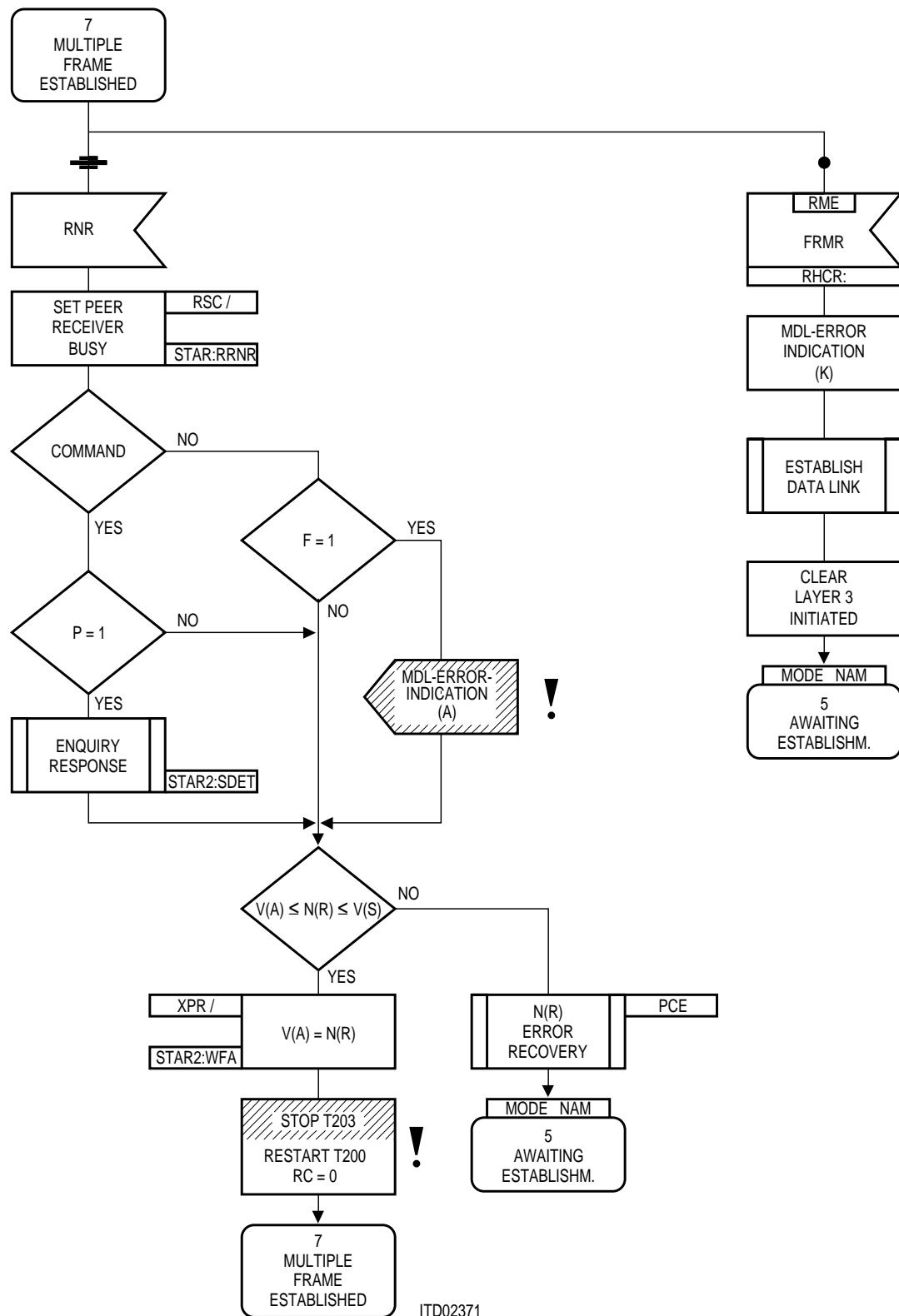

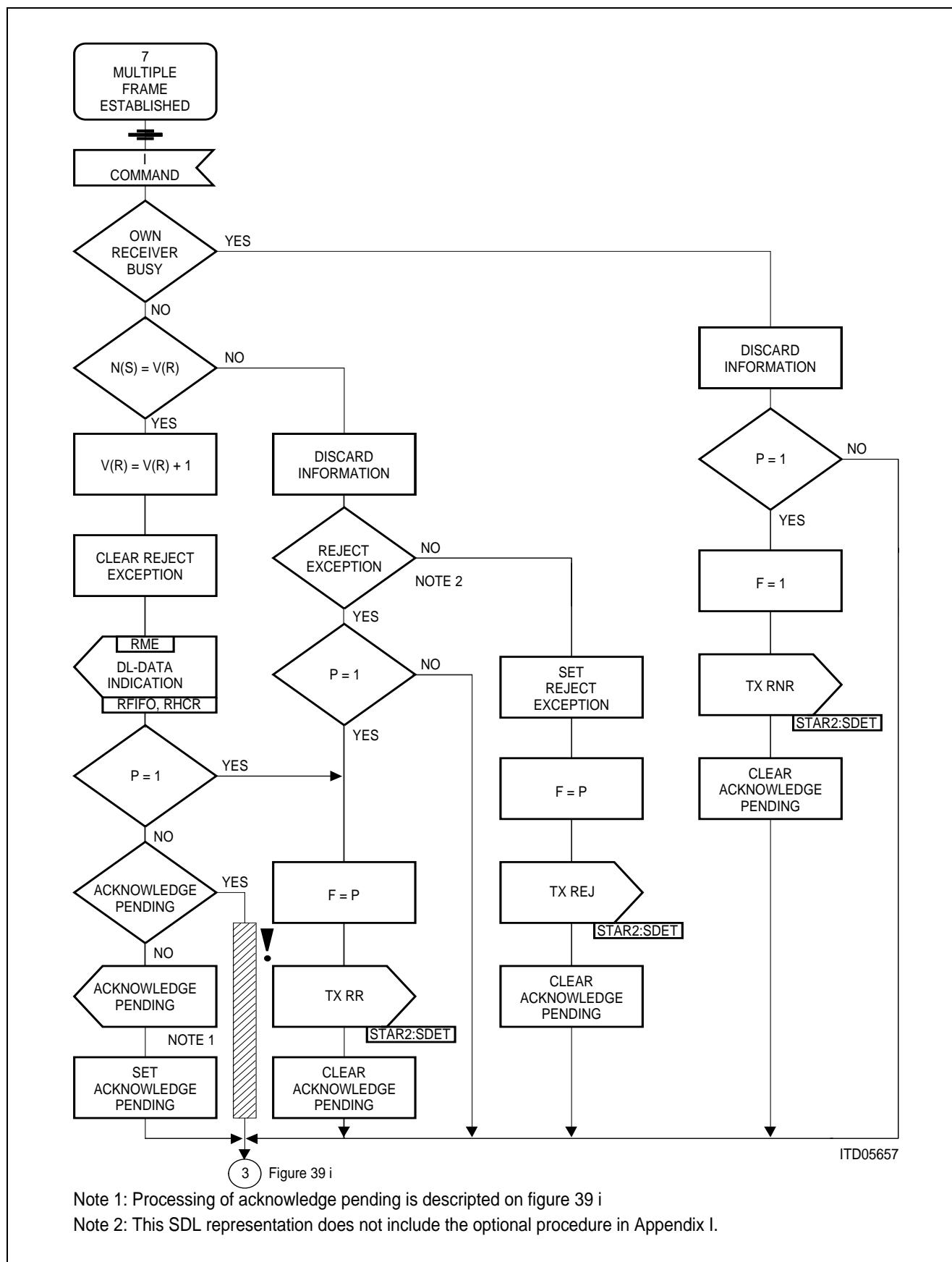

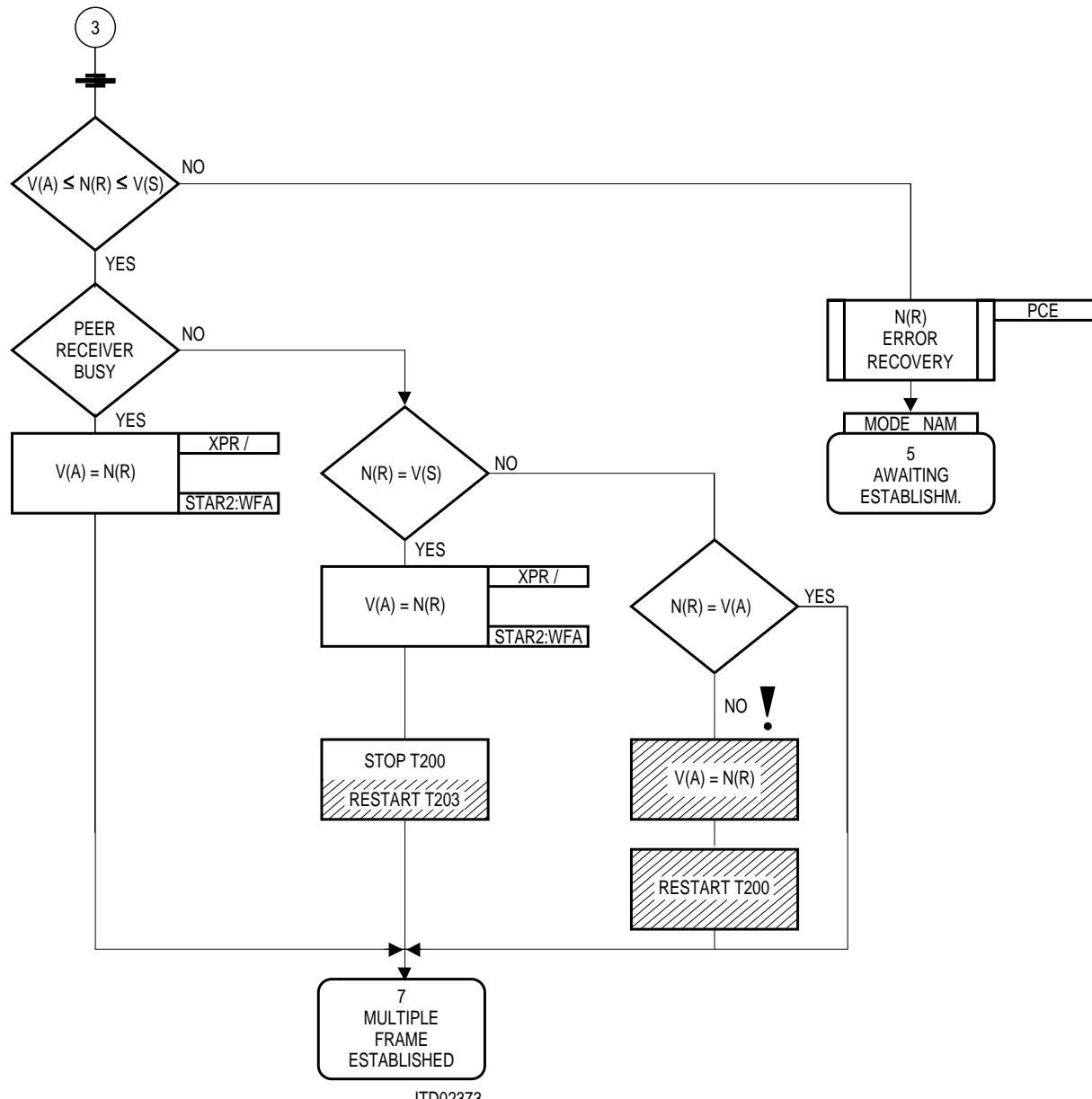

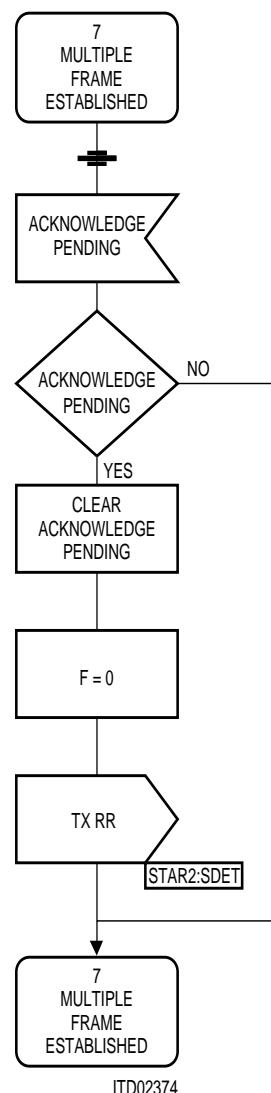

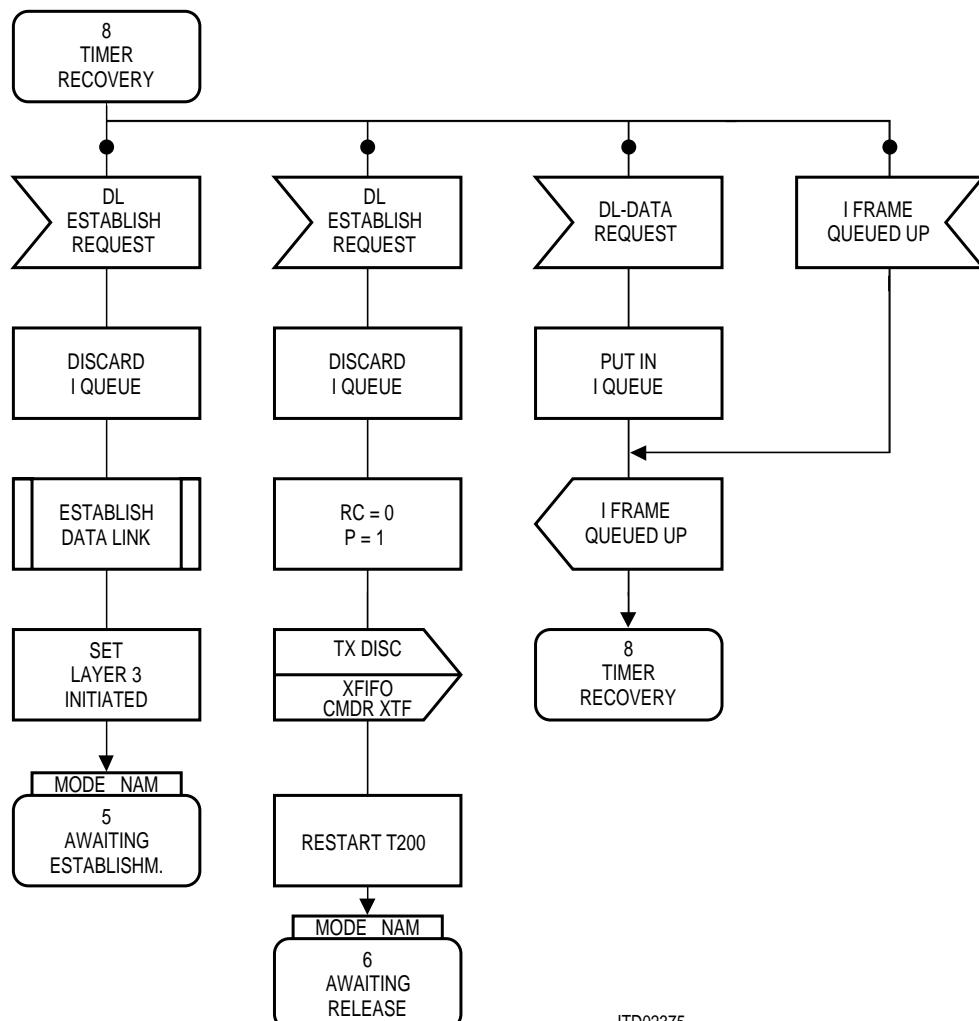

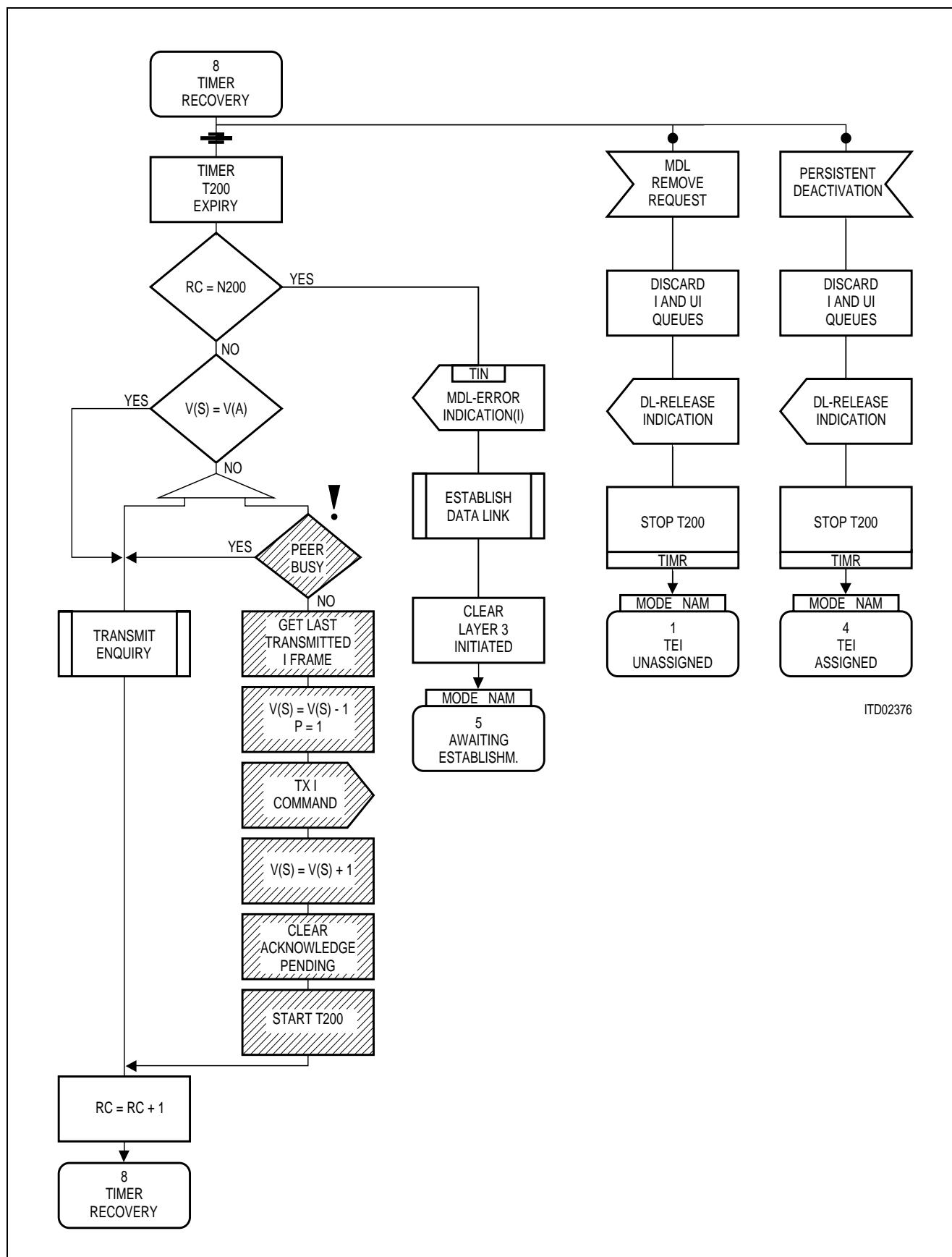

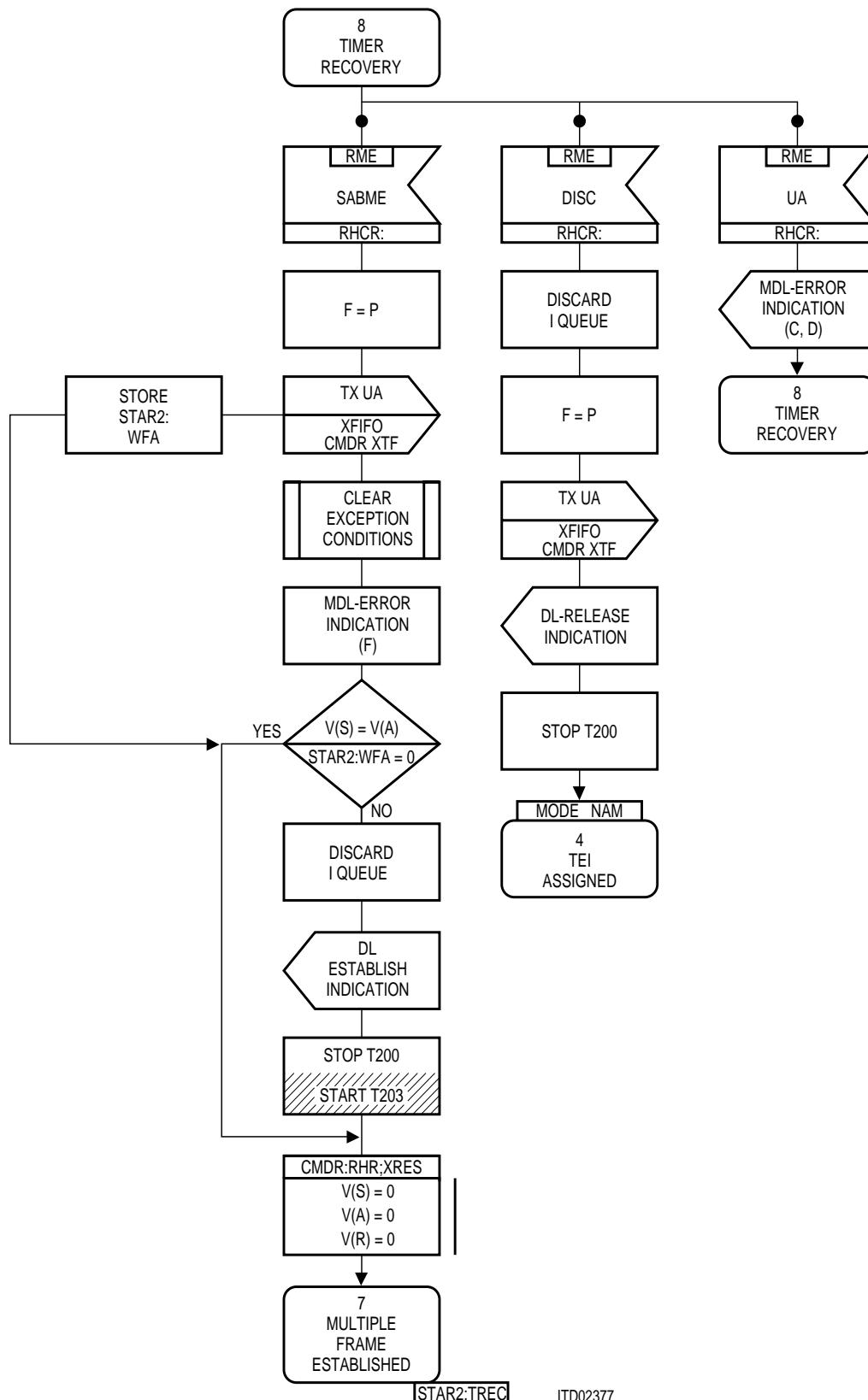

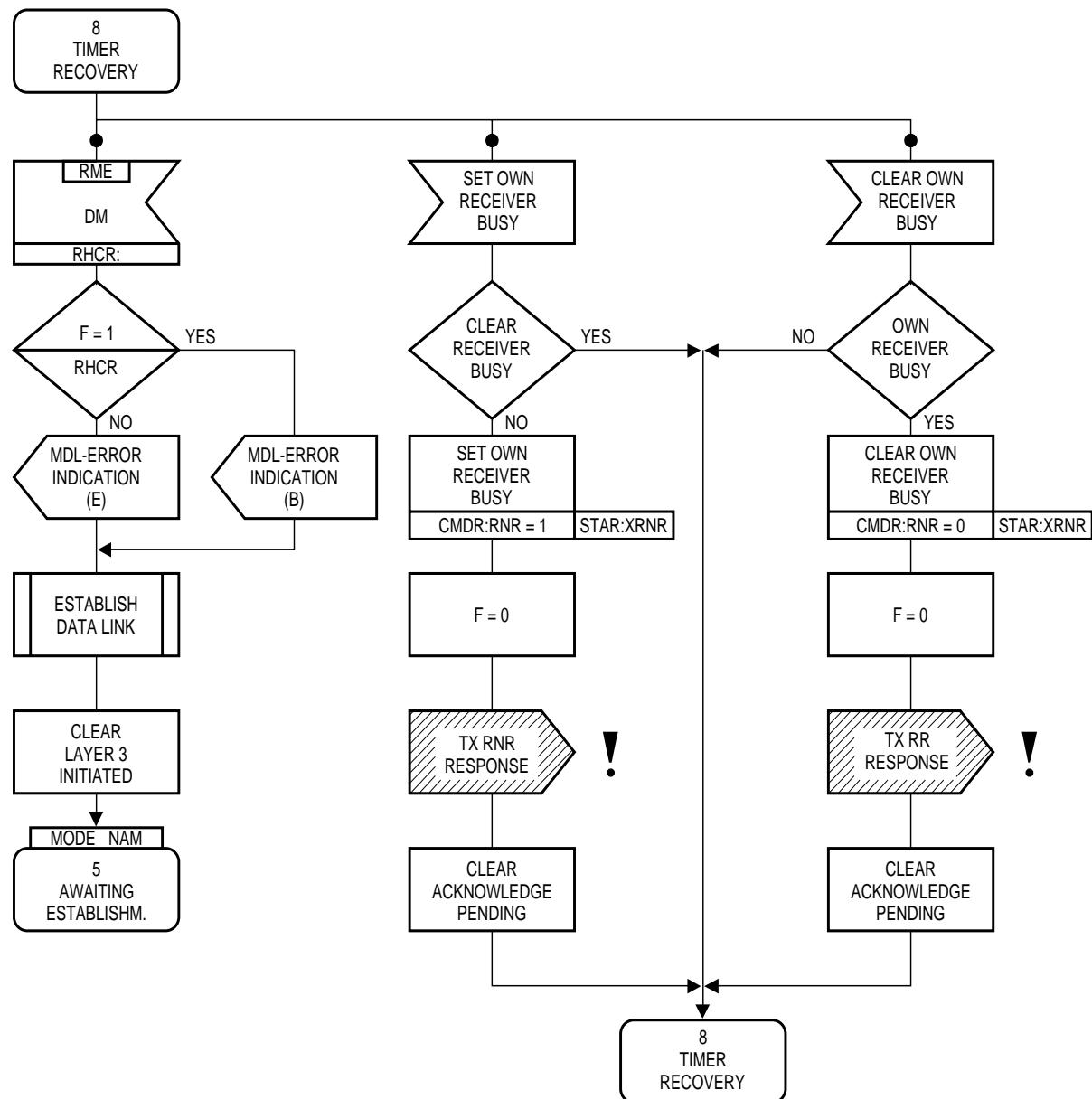

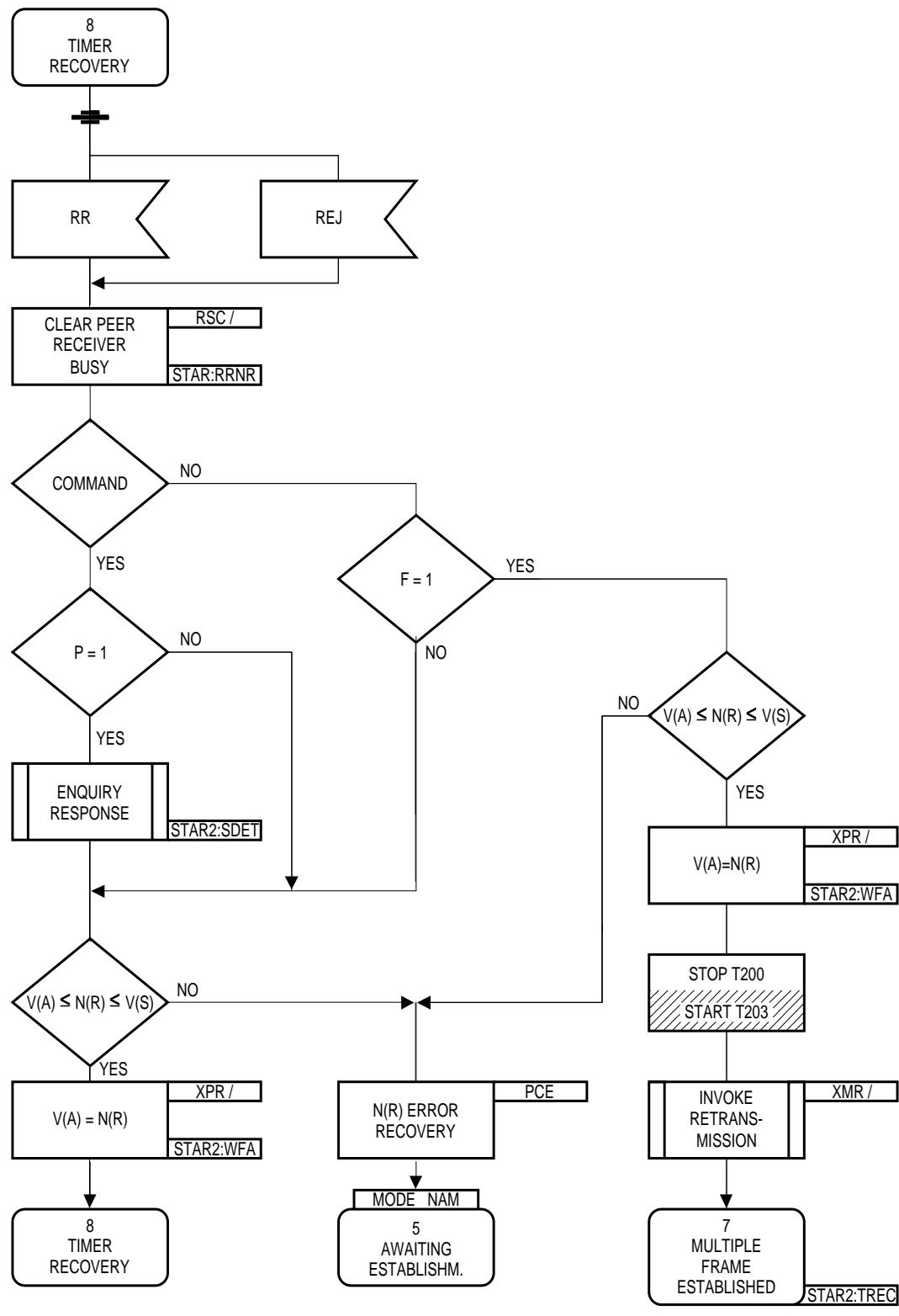

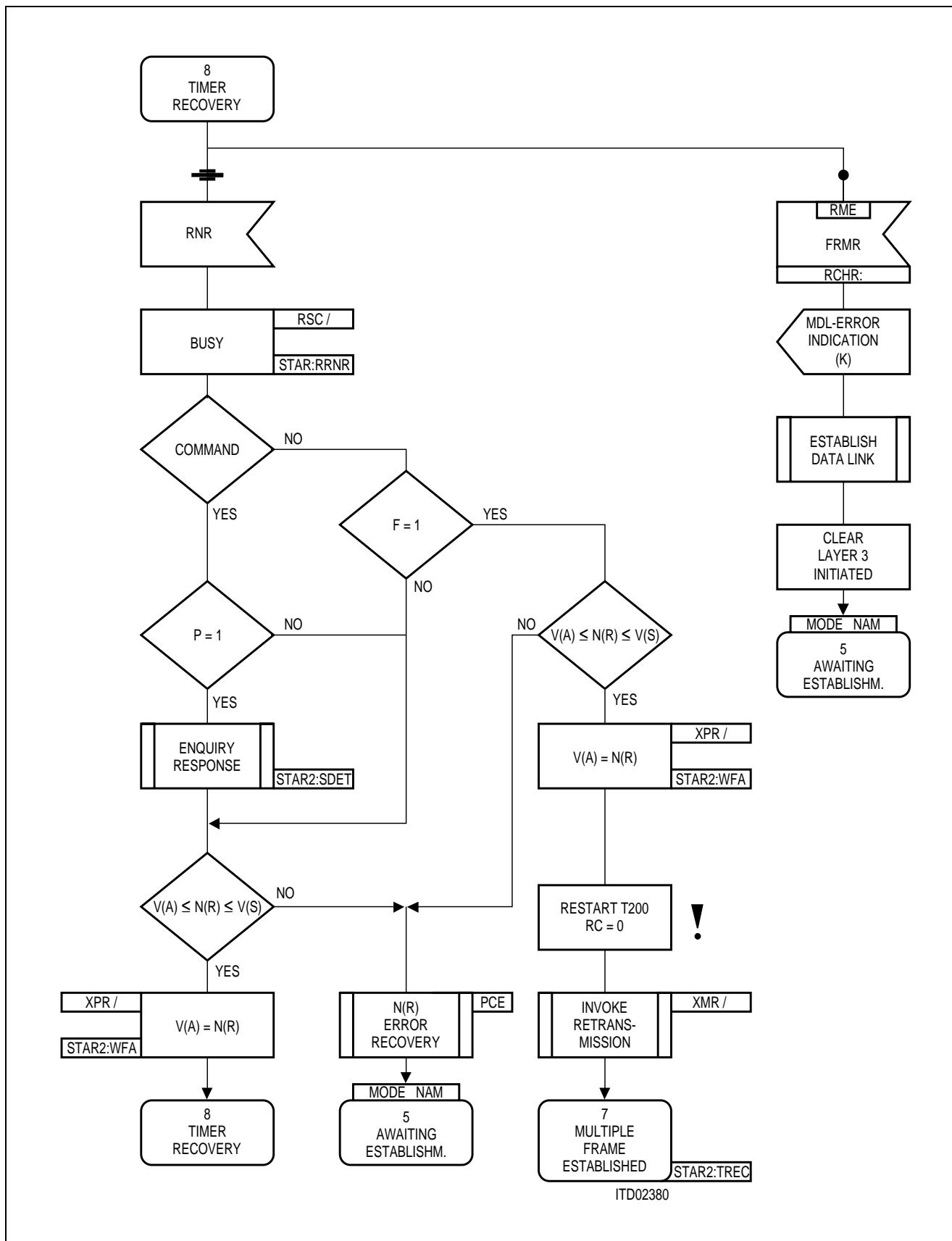

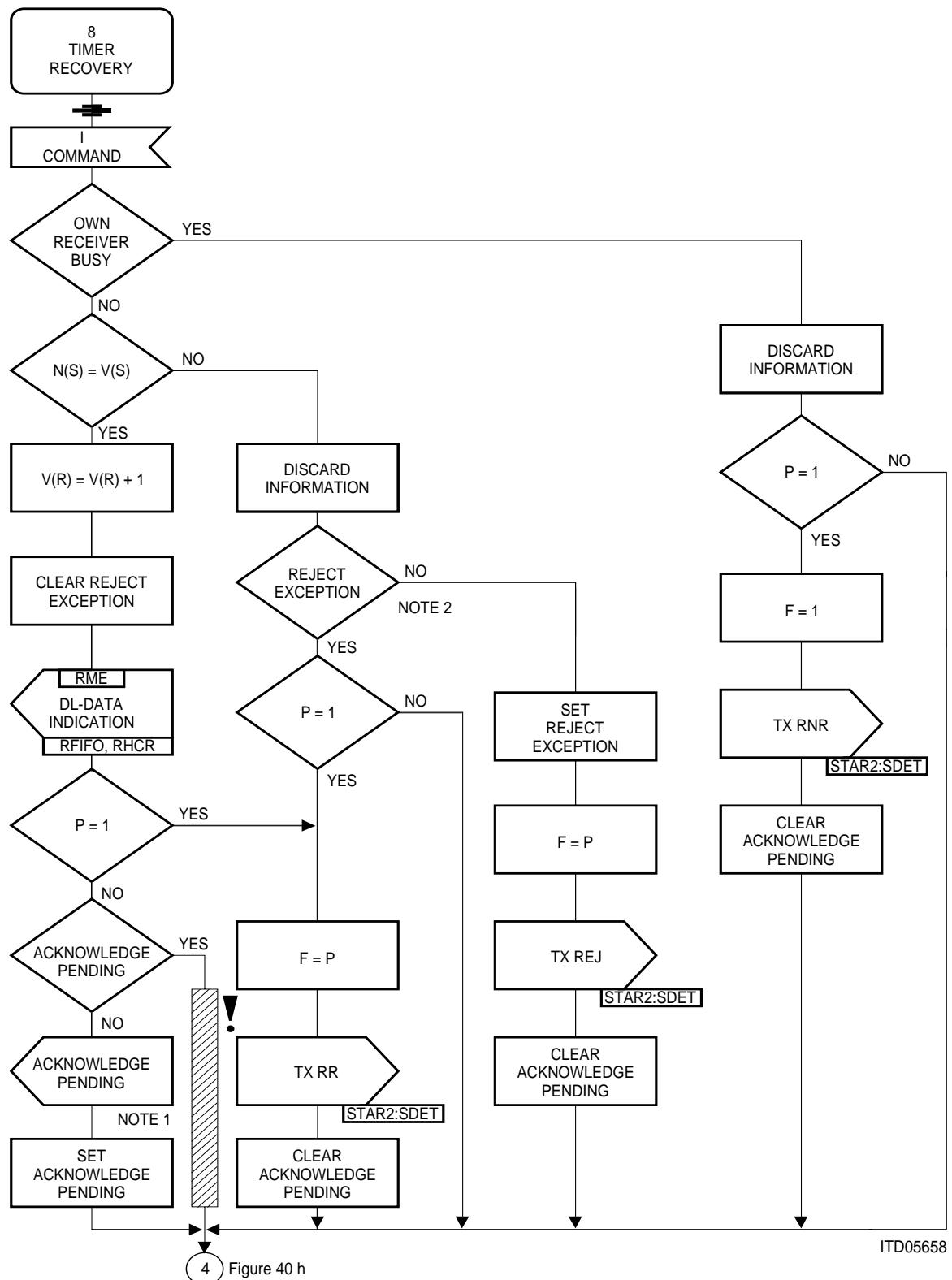

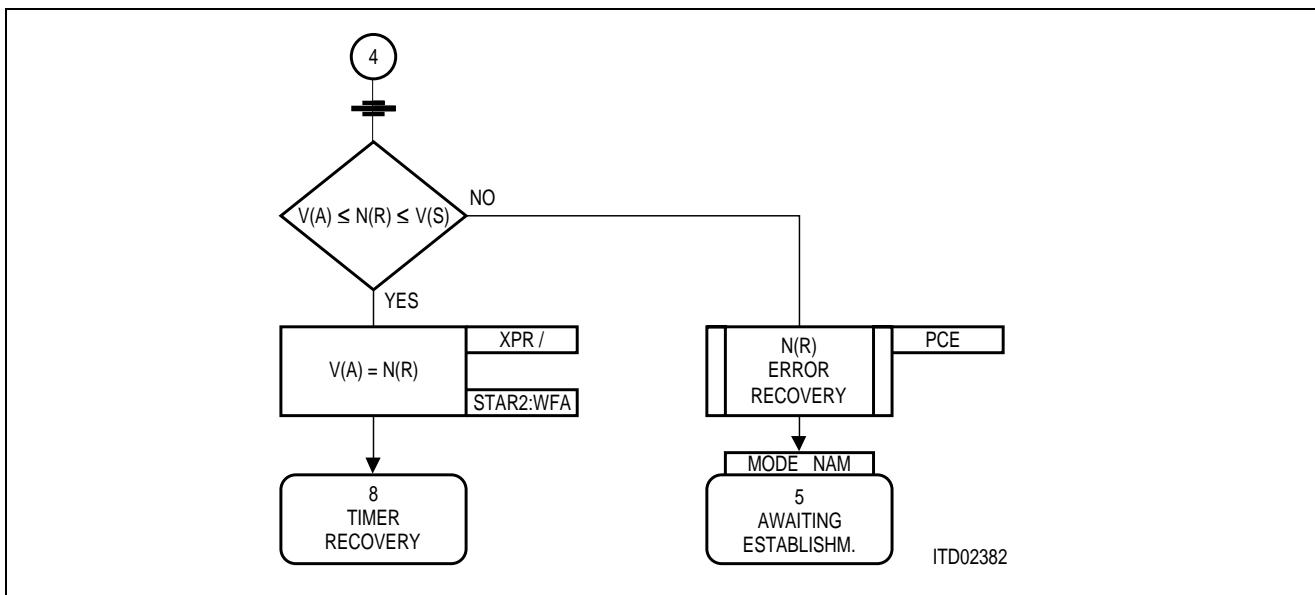

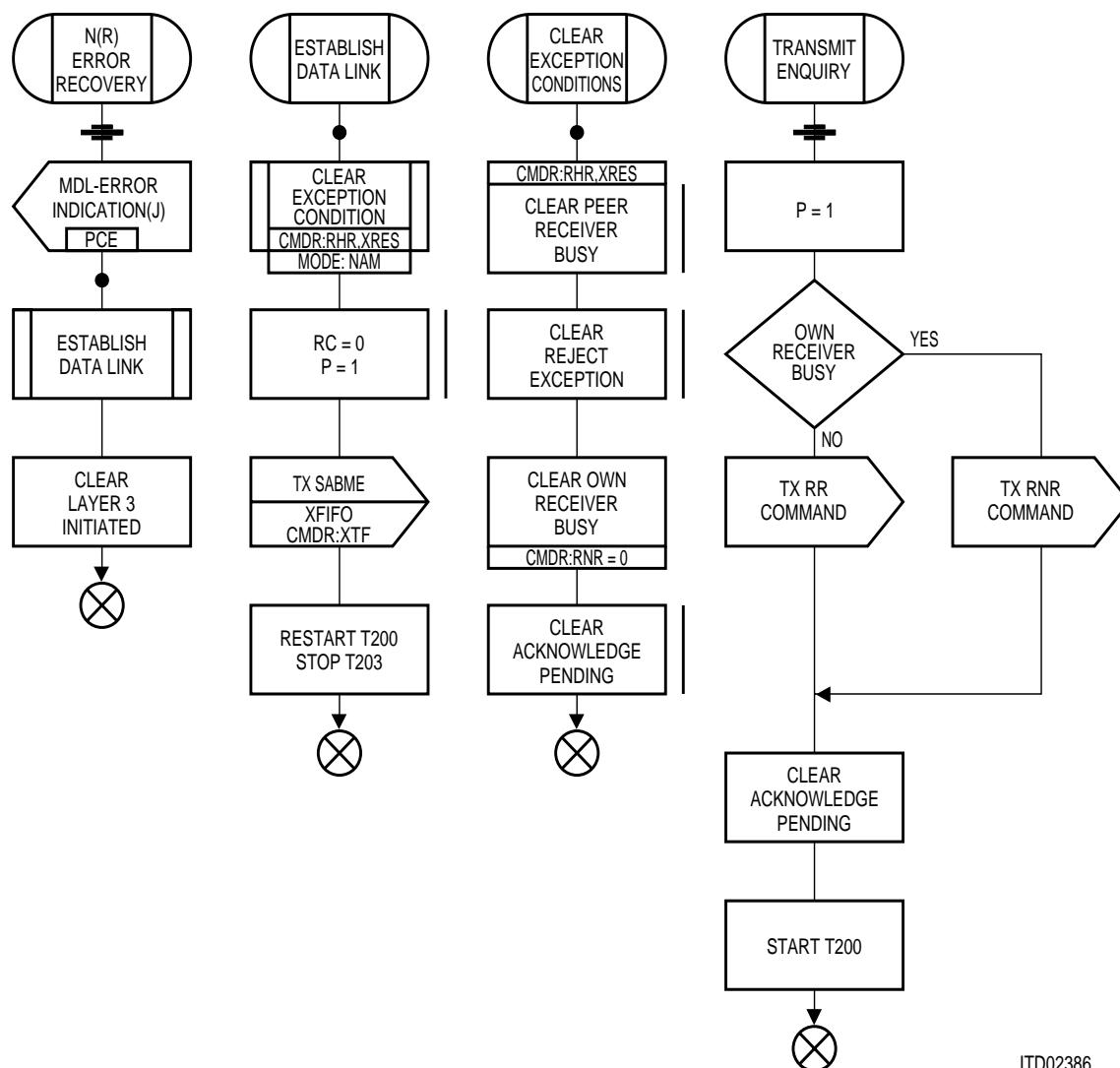

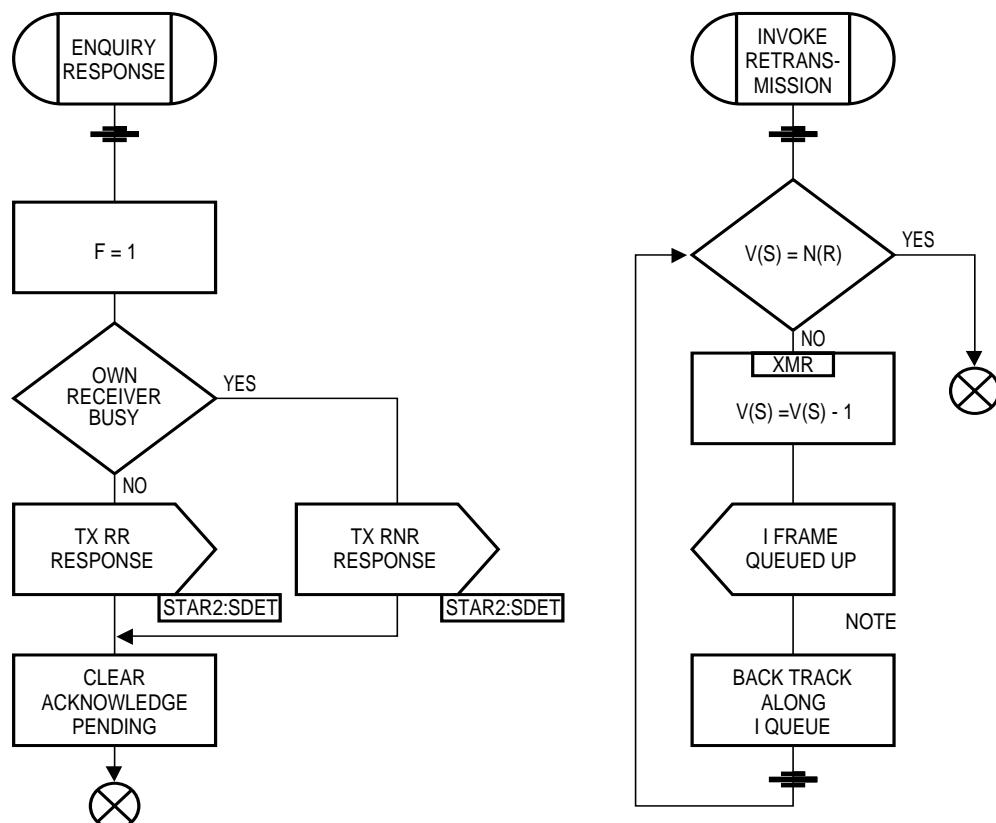

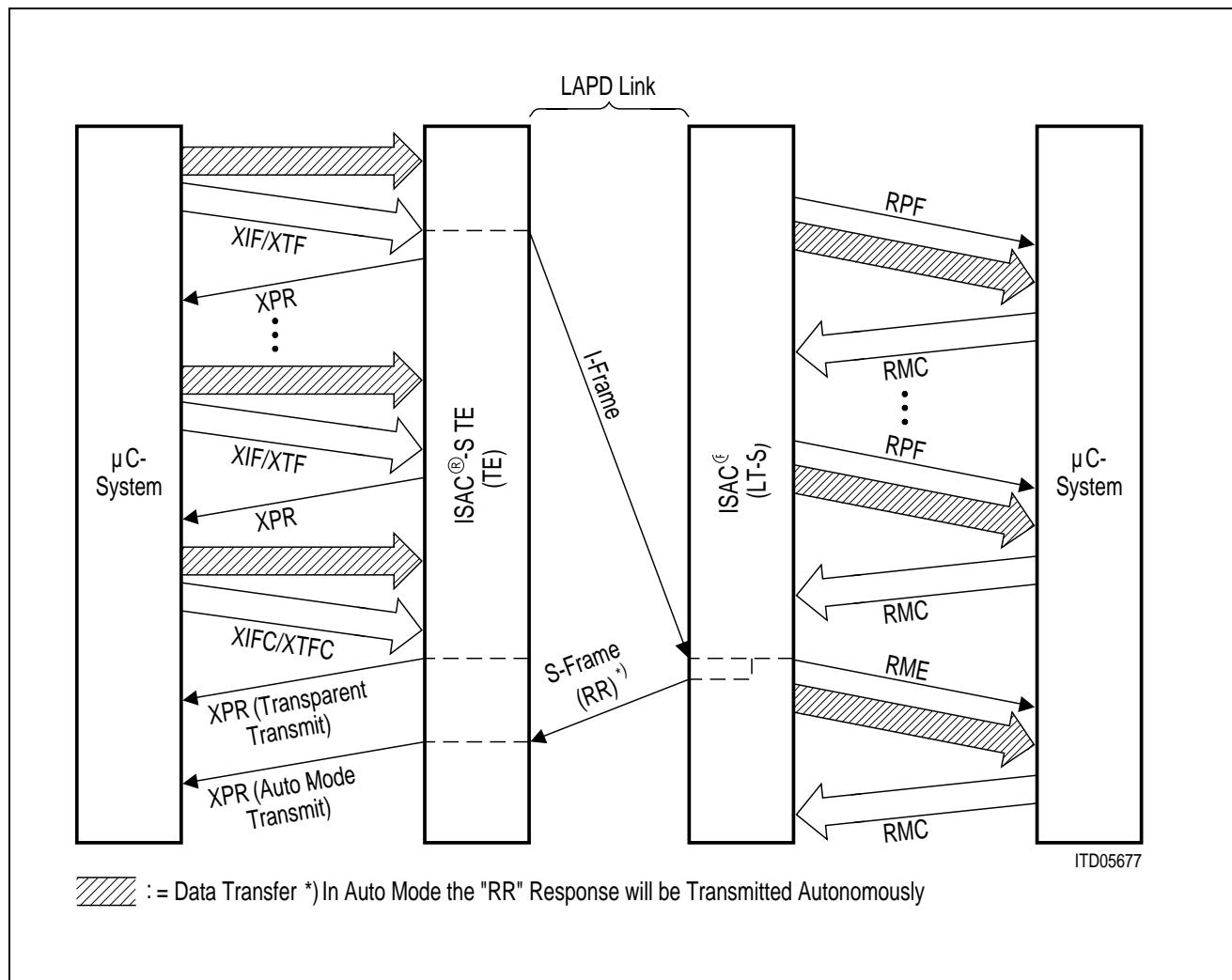

| 2.7.2 Protocol Operations (auto-mode) .....                              | 66          |

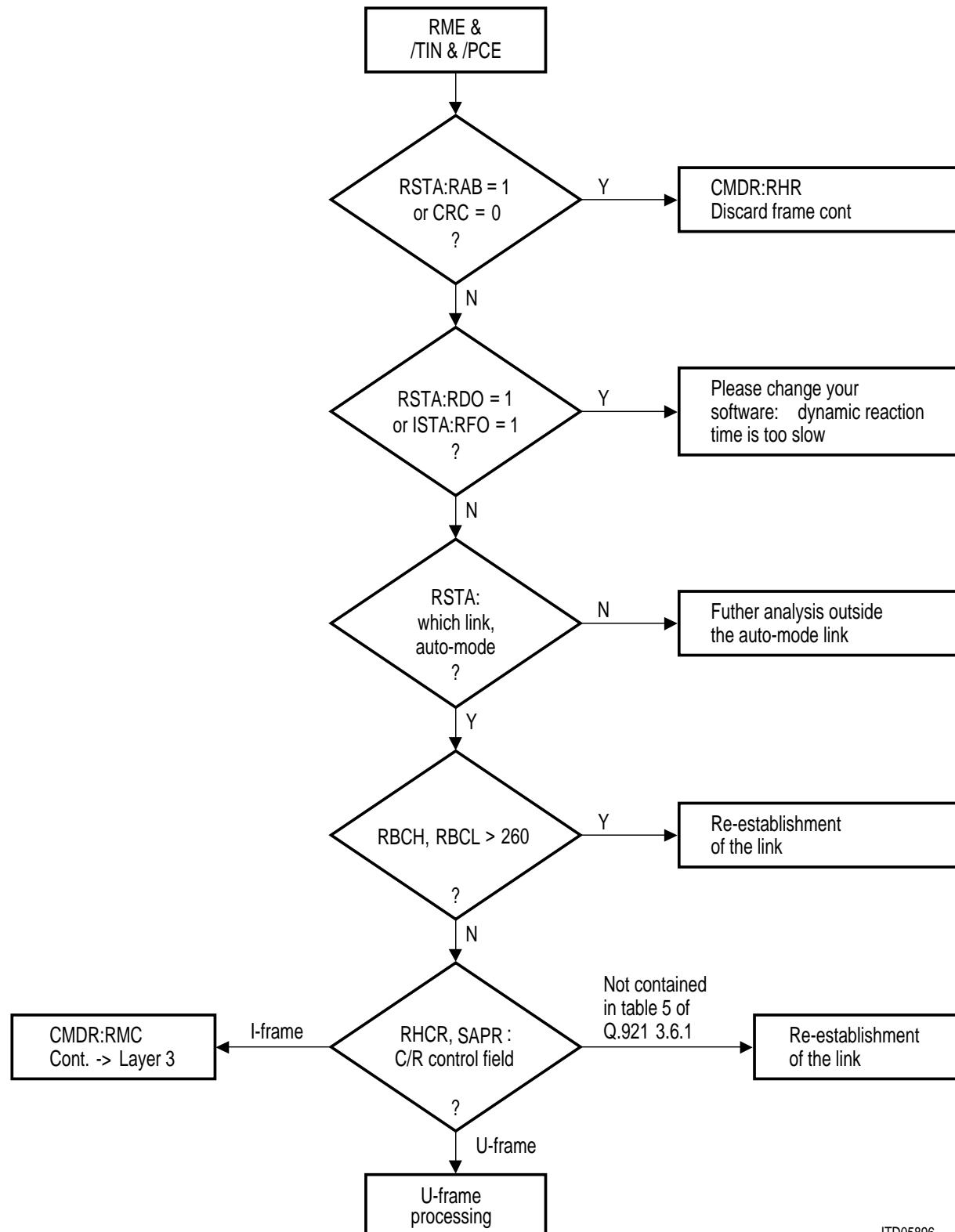

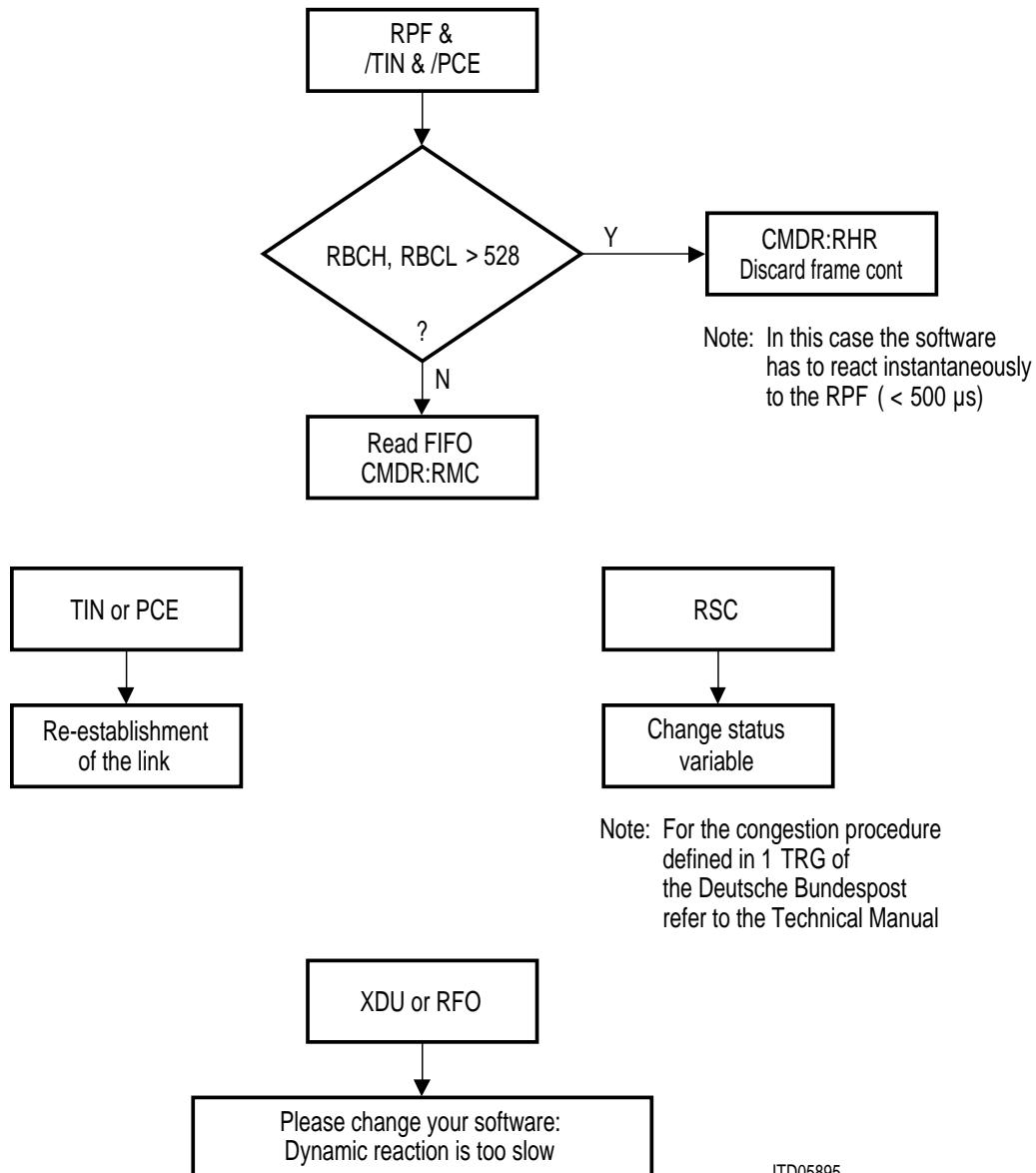

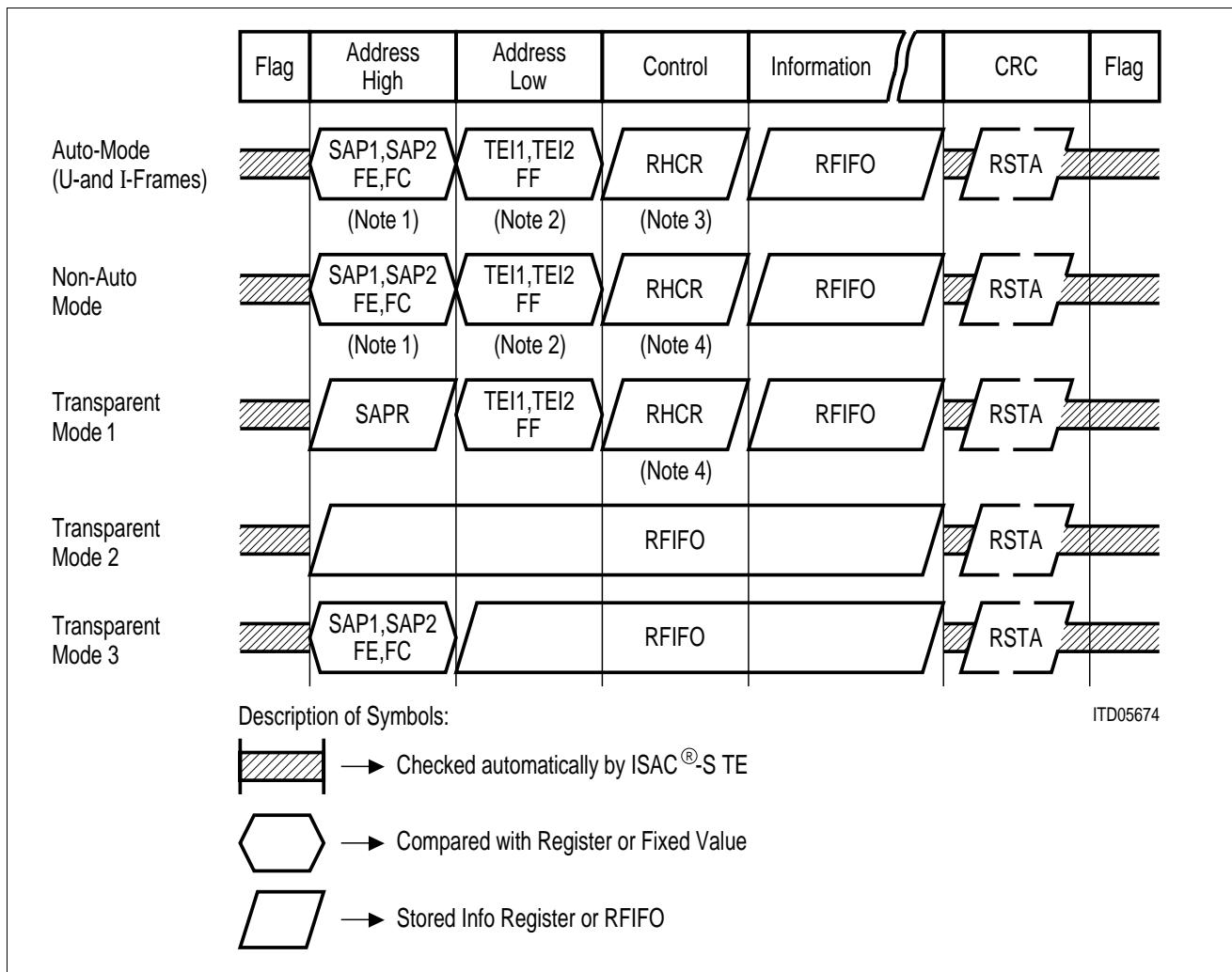

| 2.7.3 Reception of Frames .....                                          | 67          |

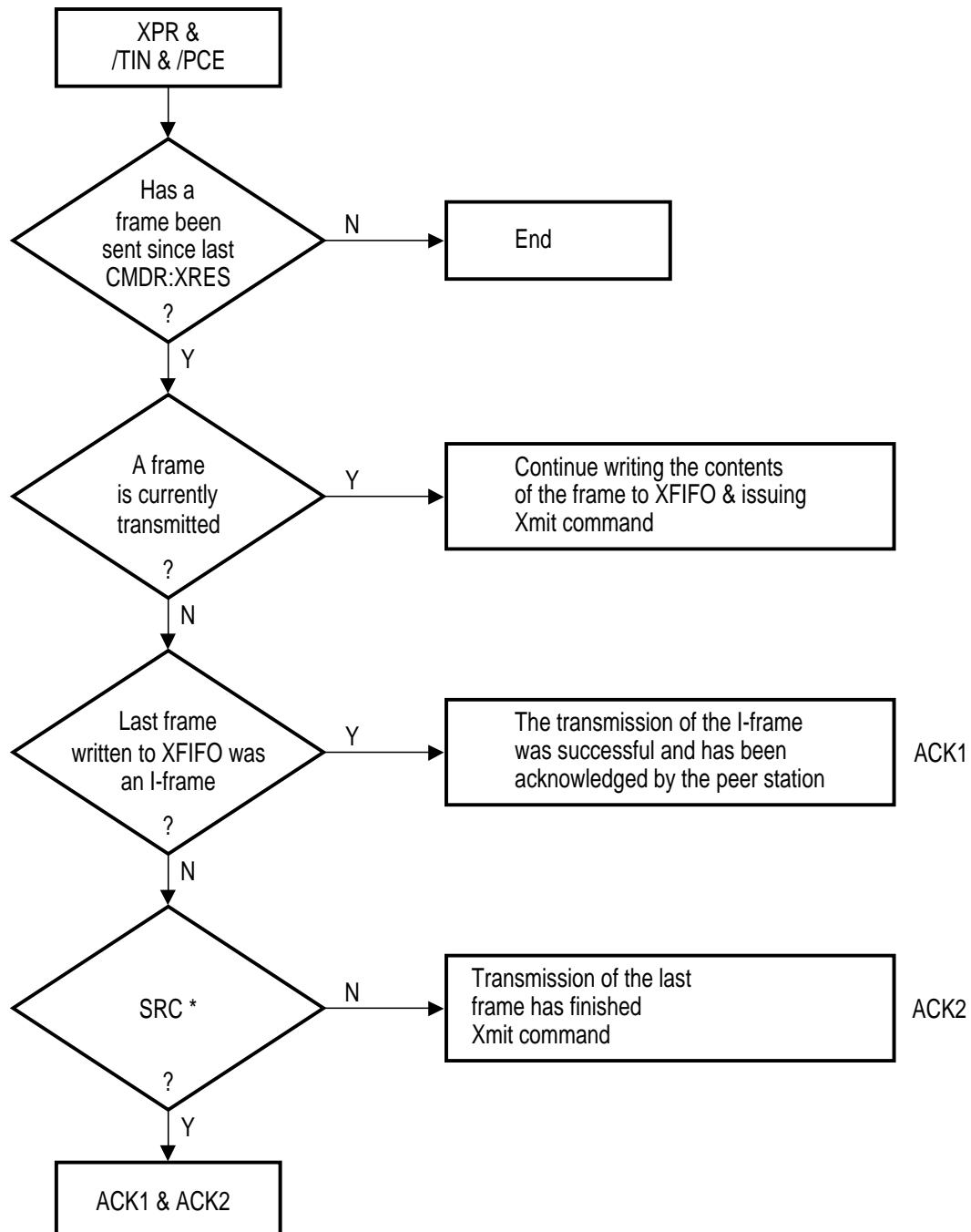

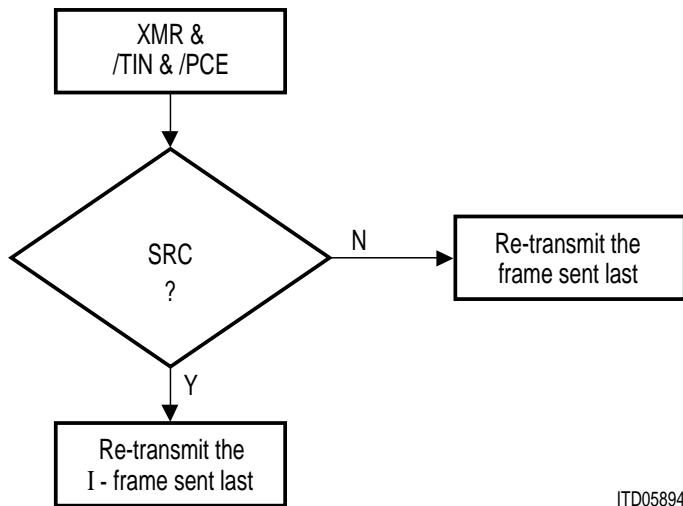

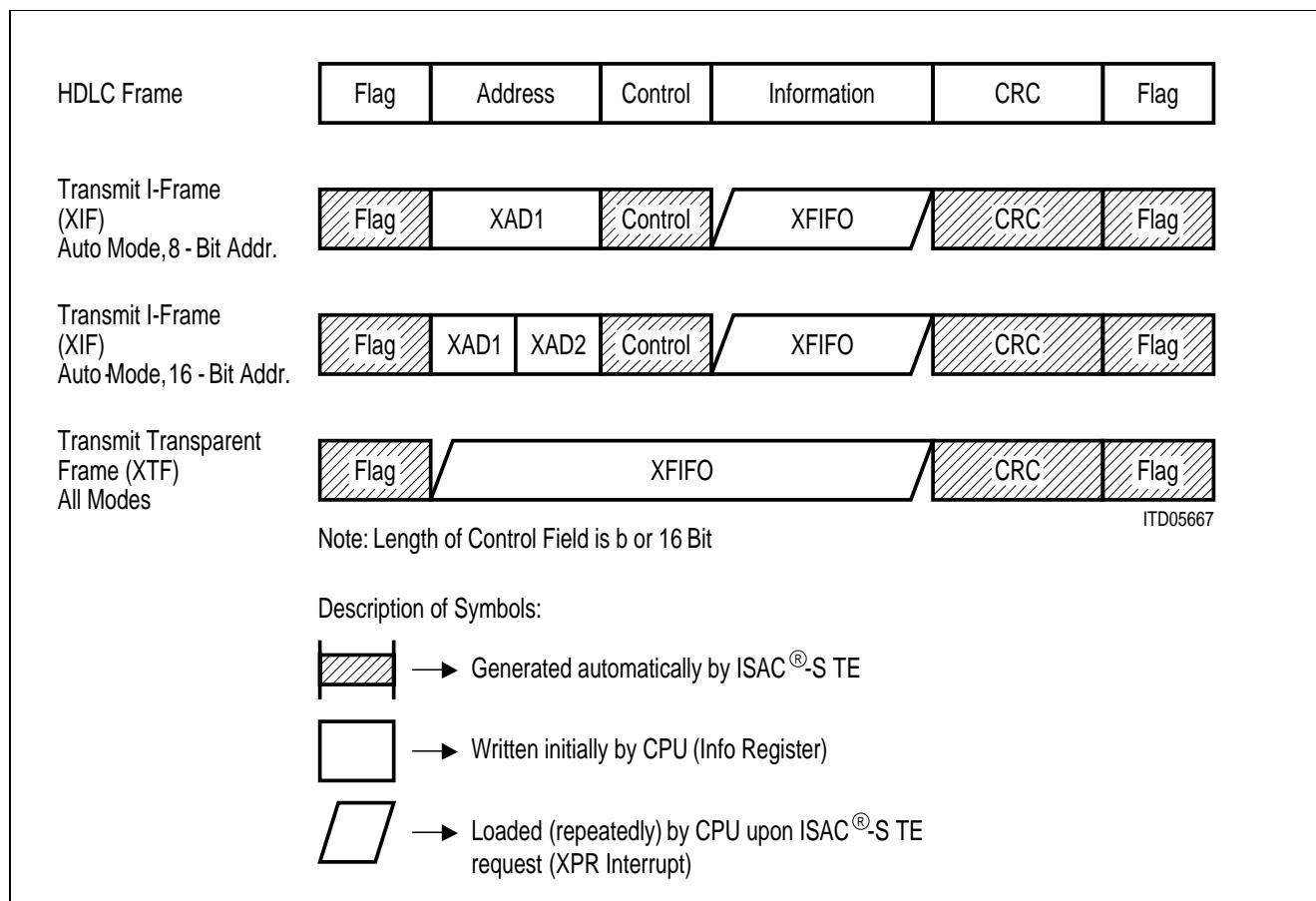

| 2.7.4 Transmission of Frames .....                                       | 71          |

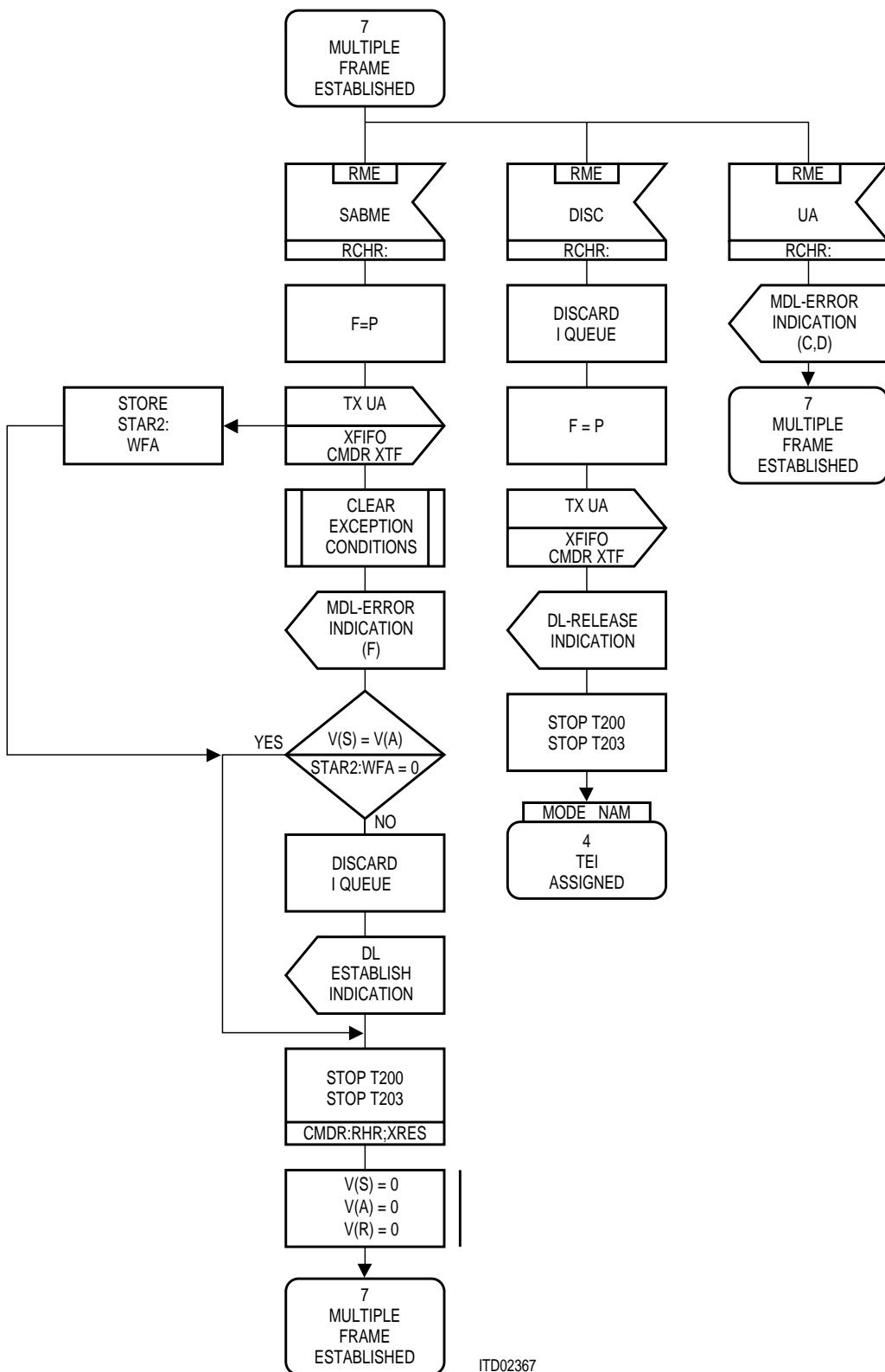

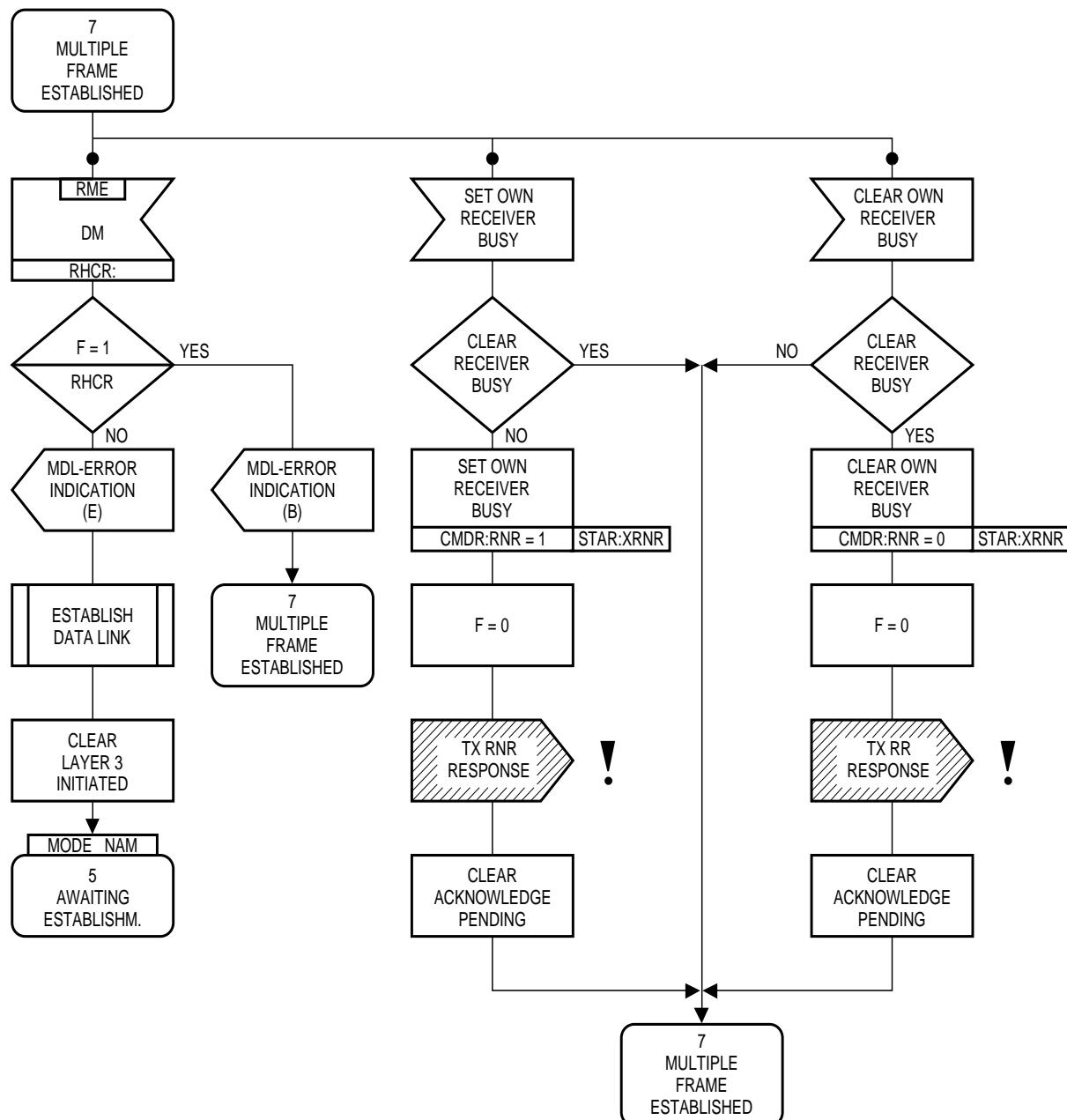

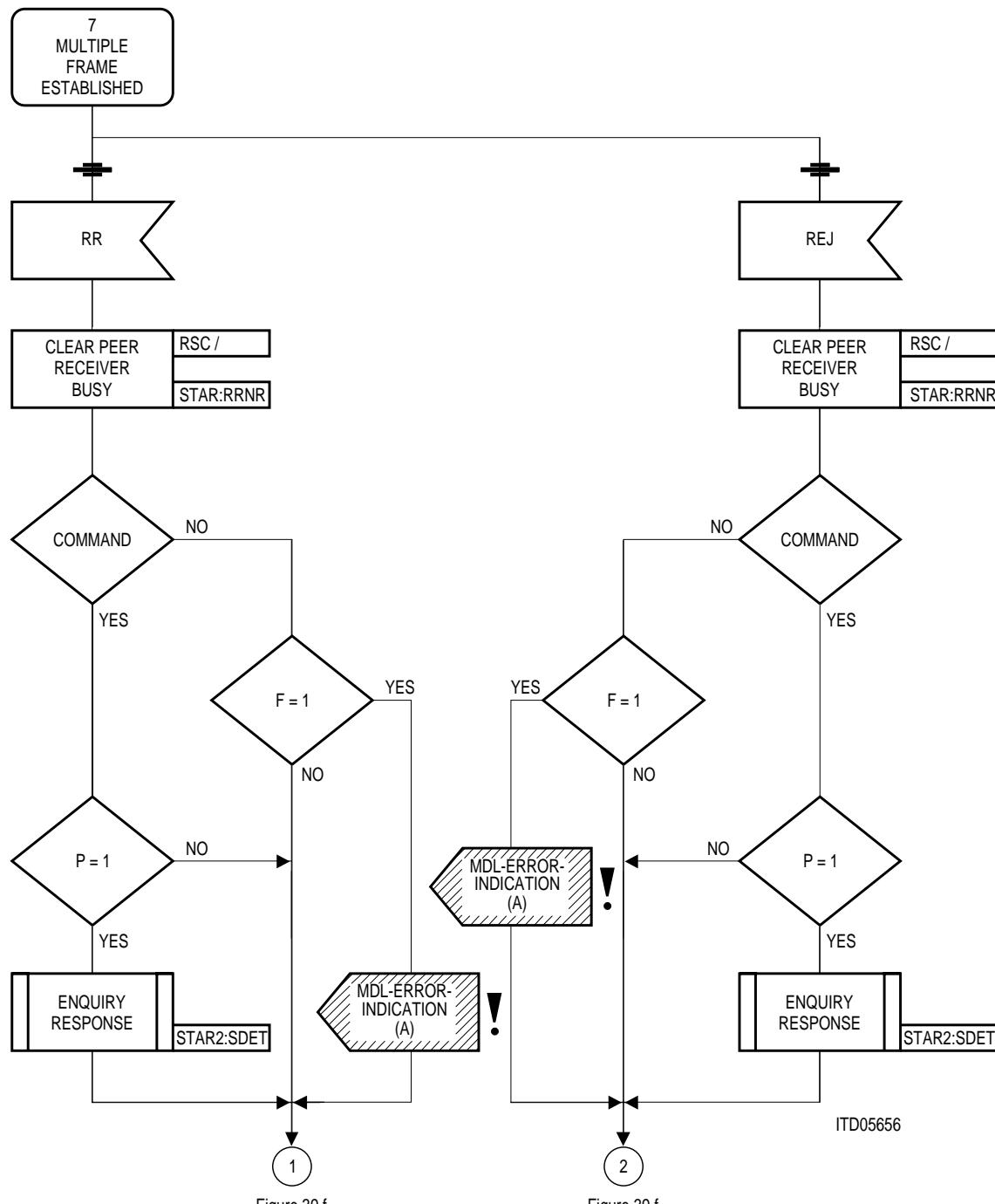

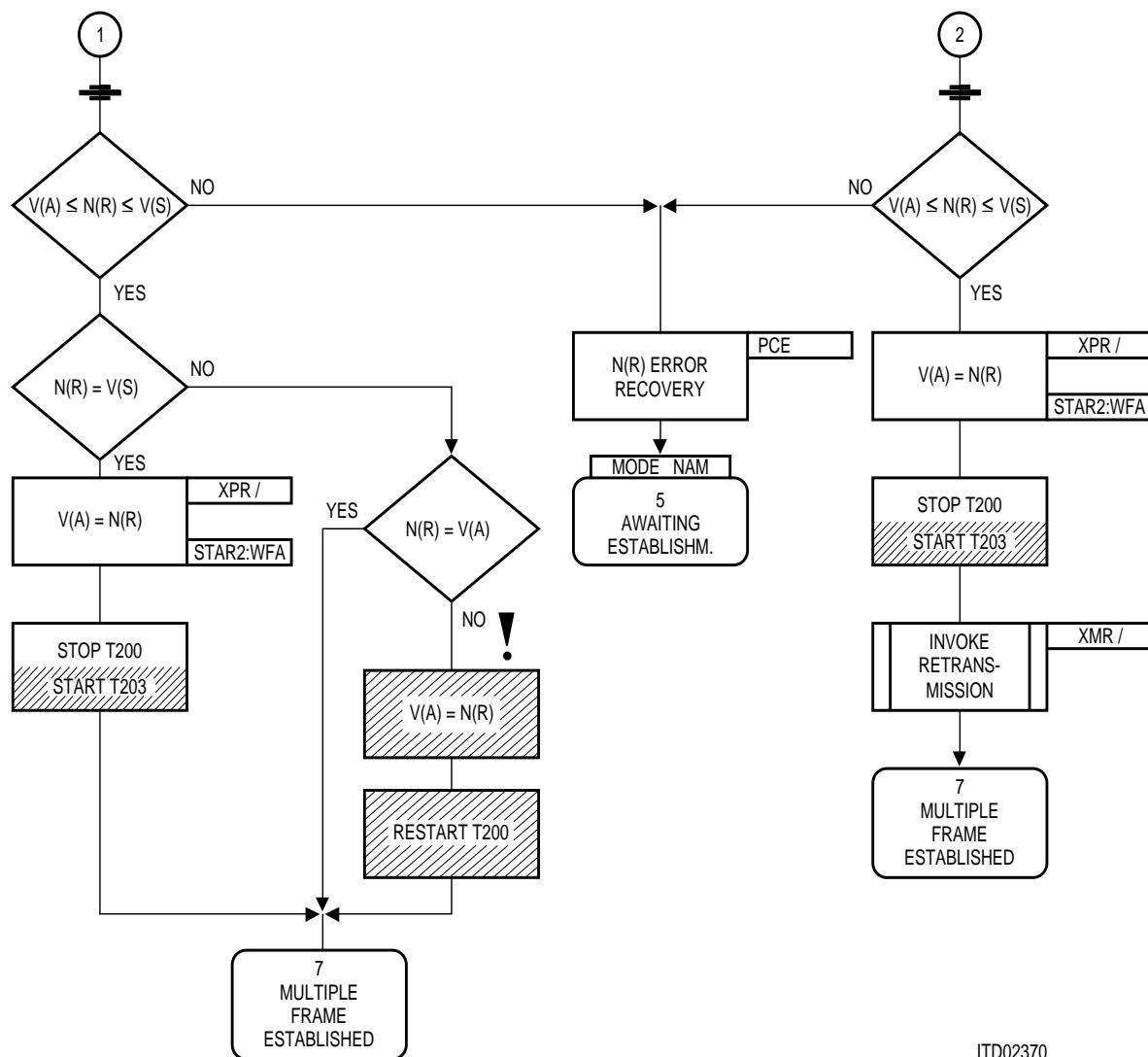

| 2.7.5 Documentation of the Auto Mode .....                               | 74          |

| 2.7.5.1 Legend of the Auto-Mode Documentation .....                      | 74          |

| 2.7.5.2 Additional General Considerations when Using the Auto Mode ..... | 77          |

| 2.7.5.3 Dealing With Error Conditions in Auto Mode .....                 | 78          |

| <b>3 Operational Description</b> .....                                   | 115         |

| 3.1 Microprocessor Interface Operation .....                             | 115         |

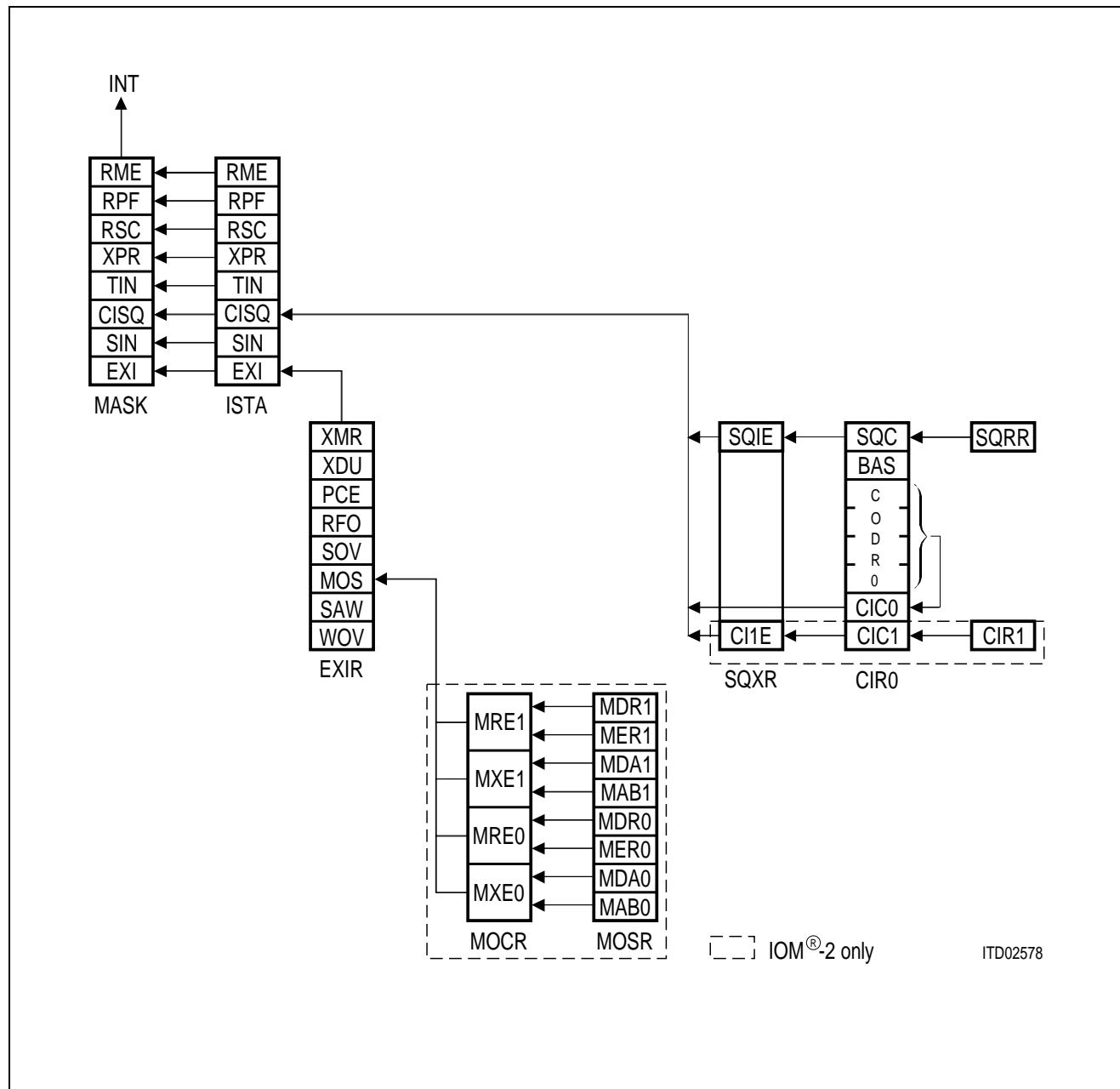

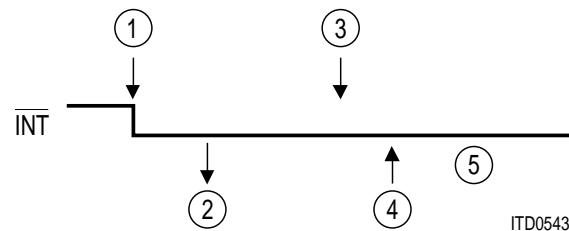

| 3.2 Interrupt Structure and Logic .....                                  | 117         |

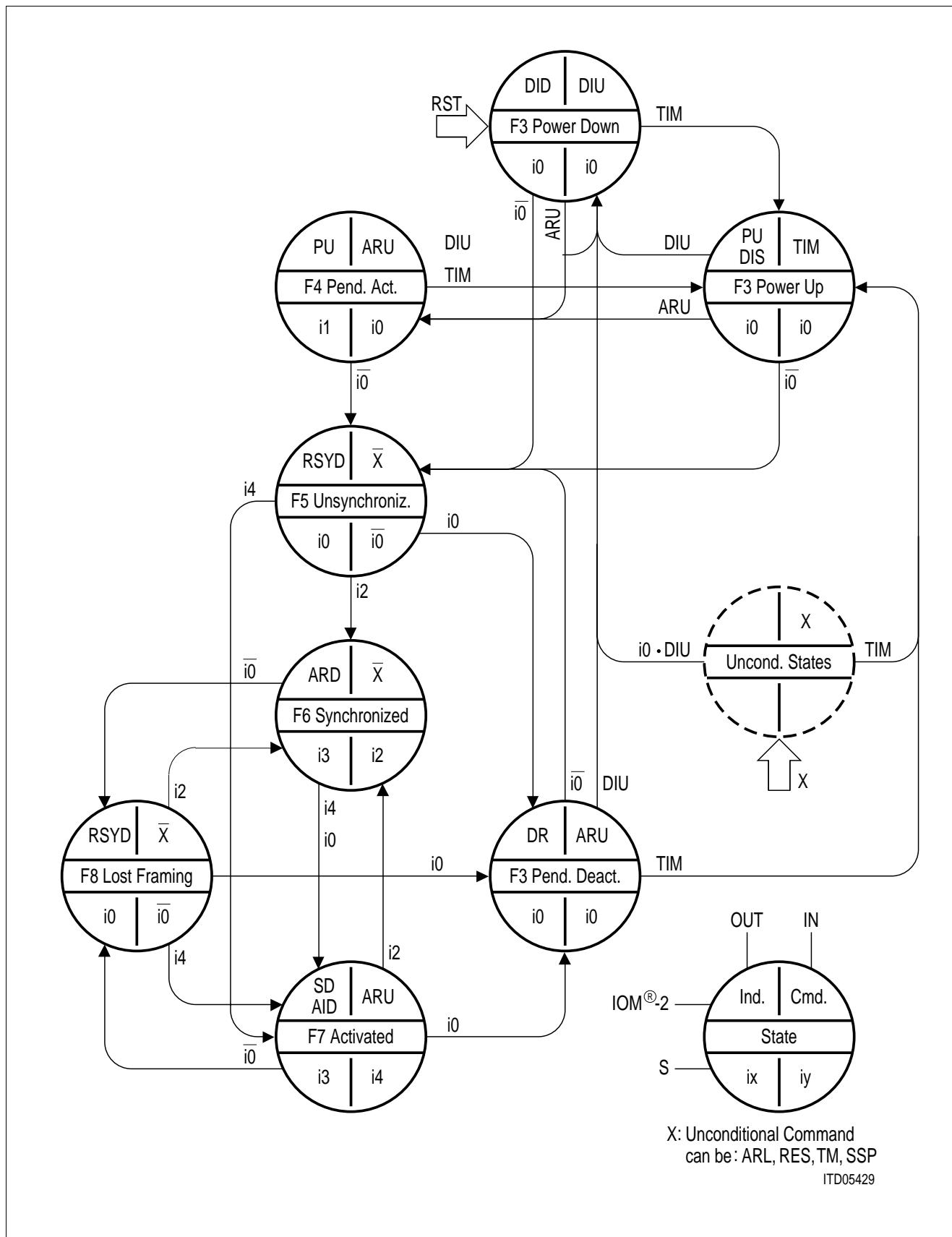

| 3.3 Control of Layer 1 .....                                             | 121         |

| 3.3.1 Activation/Deactivation of IOM® Interface .....                    | 121         |

| 3.3.2 Activation/Deactivation of S/T Interface .....                     | 124         |

| 3.3.2.1 Layer-1 Command/Indication Codes and State Diagrams .....        | 125         |

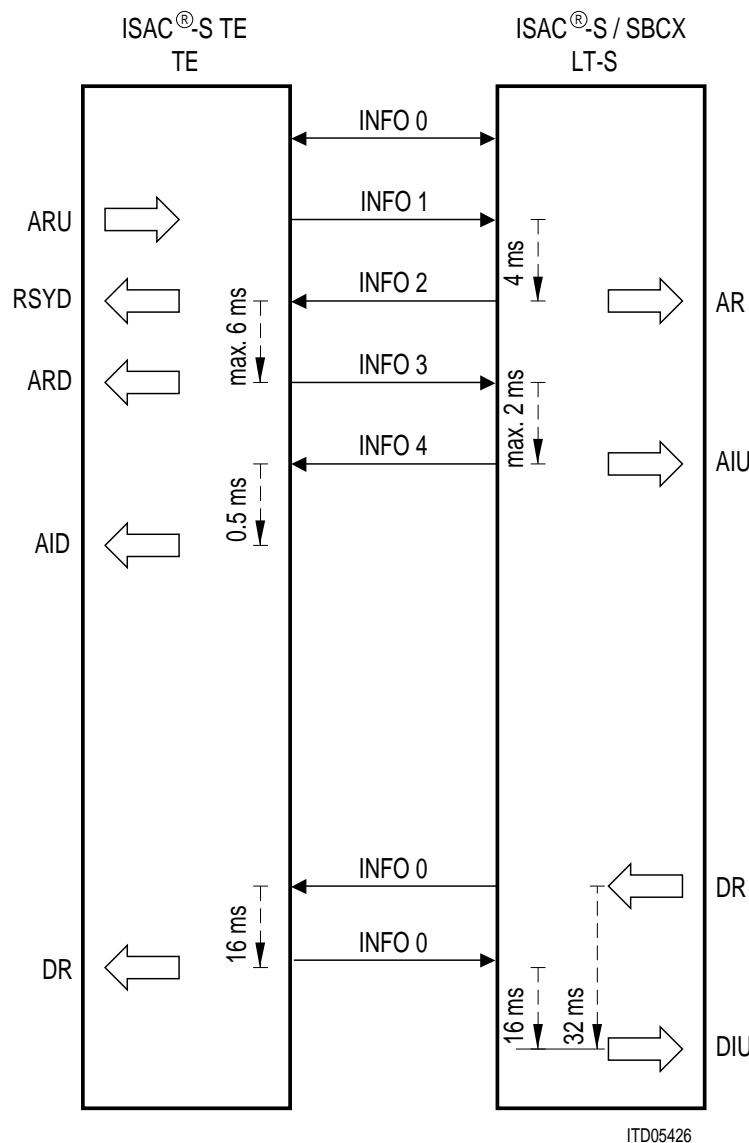

| 3.3.3 Example of Activation/Deactivation .....                           | 131         |

| 3.4 Control of Layer-2 Data Transfer .....                               | 132         |

| 3.4.1 HDLC-Frame Reception .....                                         | 135         |

| 3.4.2 HDLC-Frame Transmission .....                                      | 137         |

| 3.5 Reset .....                                                          | 138         |

| 3.6 Initialization .....                                                 | 140         |

| <b>4 Detailed Register Description</b> .....                             | 142         |

| 4.1 HDLC Operation and Status Registers .....                            | 146         |

| 4.1.1 Receive FIFO RFIFO Read Address 00-1FH .....                       | 146         |

| 4.1.2 Transmit FIFO XFIFO Write Address 00-1FH .....                     | 146         |

| 4.1.3 Interrupt Status Register ISTA Read Address 20H .....              | 146         |

---

| <b>Table of Contents</b>                                                  | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| 4.1.4 Mask Register MASK Write Address 20H .....                          | 147         |

| 4.1.5 Status Register STAR Read Address 21H .....                         | 148         |

| 4.1.6 Command Register CMDR Write Address 21H .....                       | 149         |

| 4.1.7 Mode Register MODE Read/Write Address 22H .....                     | 150         |

| 4.1.8 Timer Register TIMR Read/Write Address 23H .....                    | 152         |

| 4.1.9 Extended Interrupt Register EXIR Read Address 24H .....             | 154         |

| 4.1.10 Transmit Address 1 XAD1 Write Address 24H .....                    | 155         |

| 4.1.11 Receive Frame Byte Count Low RBCL Read Address 25H .....           | 156         |

| 4.1.12 Transmit Address 2 XAD2 Write Address 25H .....                    | 156         |

| 4.1.13 Received SAPI Register SAPR Read Address 26H .....                 | 156         |

| 4.1.14 SAPI1 Register SAP1 Write Address 26H .....                        | 157         |

| 4.1.15 Receive Status Register RSTA Read Address 27H .....                | 157         |

| 4.1.16 SAPI2 Register SAP2 Write Address 27H .....                        | 159         |

| 4.1.17 TEI1 Register 1 TEI1 Write Address 28H .....                       | 159         |

| 4.1.18 Receive HDLC Control Register RHCR Read Address 29H .....          | 160         |

| 4.1.19 TEI2 Register TEI2 Write Address 29H .....                         | 161         |

| 4.1.20 Receive Frame Byte Count High RBCH Read Address 2AH .....          | 161         |

| 4.1.21 Status Register 2 STAR2 Read/Write Address 2BH .....               | 162         |

| 4.2 Special Purpose Registers: IOM®-2 Mode .....                          | 163         |

| 4.2.1 Serial Port Control Register SPCR Read/Write Address 30H .....      | 163         |

| 4.2.2 Command/Indication Receive 0 CIR0 Read Address 31H .....            | 164         |

| 4.2.3 Command/Indication Transmit 0 CIX0 Write Address 31H .....          | 165         |

| 4.2.4 MONITOR Receive Channel 0 MOR0 Read Address 32H .....               | 166         |

| 4.2.5 MONITOR Transmit Channel 0 MOX0 Write Address 32H .....             | 166         |

| 4.2.6 Command/Indication Receive 1 CIR1 Read Address 33H .....            | 166         |

| 4.2.7 Command/Indication Transmit 1 CIX1 Write Address 33H .....          | 166         |

| 4.2.8 MONITOR Receive Channel 1 MOR1 Read Address 34H .....               | 167         |

| 4.2.9 MONITOR Transmit Channel 1 MOX1 Write Address 34H .....             | 167         |

| 4.2.10 Channel Register 1 C1R Read/Write Address 35H .....                | 167         |

| 4.2.11 Channel Register 2 C2R Read/Write Address 36H .....                | 167         |

| 4.2.12 B1-Channel Register B1CR Read Address 37H .....                    | 168         |

| 4.2.13 Synchronous Transfer Control Register STCR Write Address 37H ..... | 168         |

| 4.2.14 B2-Channel Register B2CR Read Address 38H .....                    | 169         |

---

| <b>Table of Contents</b>                                                   | <b>Page</b> |

|----------------------------------------------------------------------------|-------------|

| 4.2.15 Additional Feature Register 1 ADF1 Write Address 38H . . . . .      | 170         |

| 4.2.16 Additional Feature Register 2 ADF2 Read/Write Address 39H . . . . . | 171         |

| 4.2.17 MONITOR Status Register MOSR Read Address 3AH . . . . .             | 172         |

| 4.2.18 MONITOR Control Register MOCR Write Address 3AH . . . . .           | 172         |

| 4.2.19 S-, Q-Channel Receive Register SQRR Read Address 3BH . . . . .      | 173         |

| 4.2.20 S, Q Channel Transmit Register SQXR Write Address 3BH . . . . .     | 174         |

| <b>5 Electrical Characteristics</b> . . . . .                              | 176         |

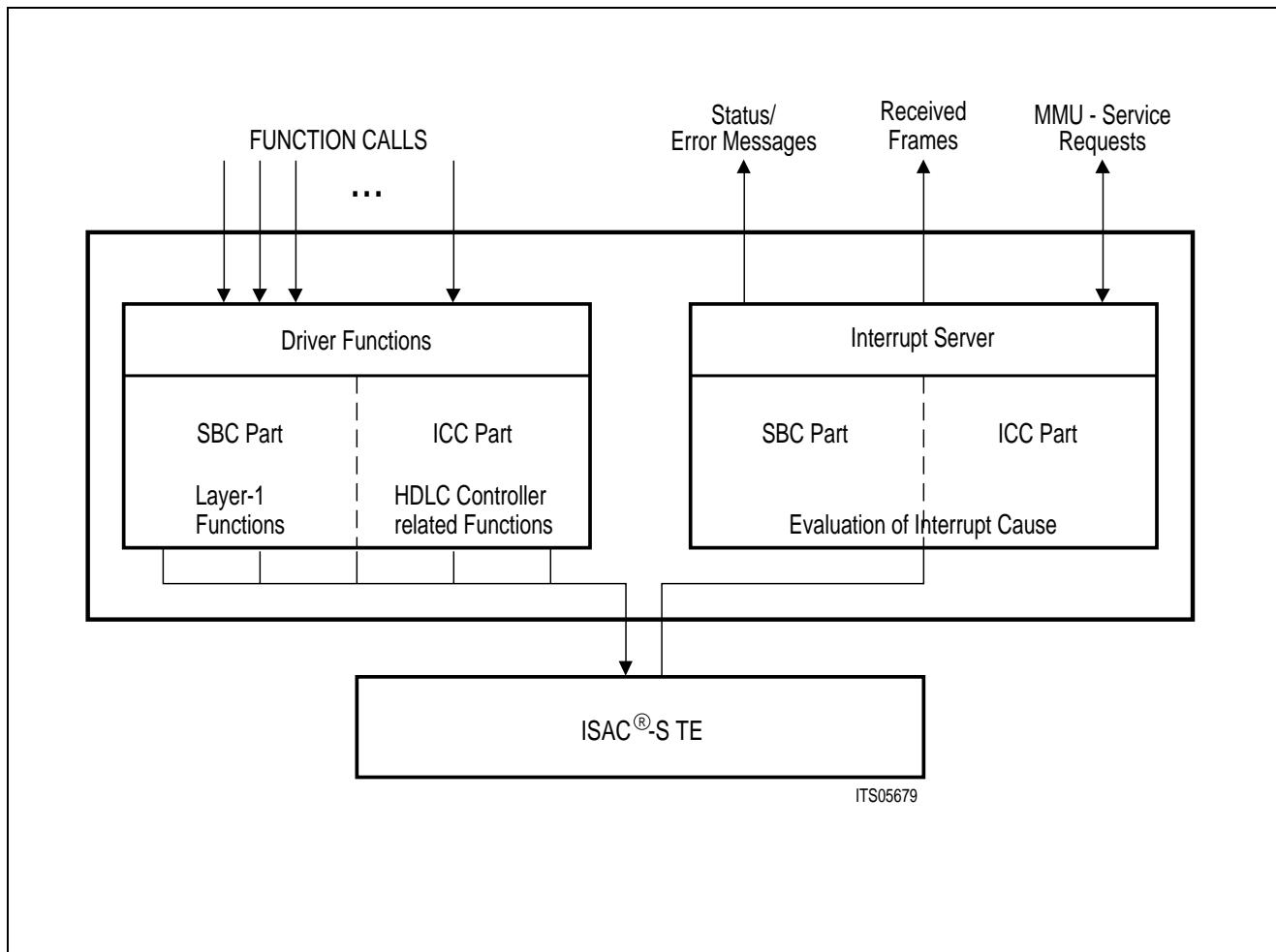

| <b>6 ISAC®-S TE Low Level Controller</b> . . . . .                         | 192         |

| 6.1 Architecture and Functions . . . . .                                   | 192         |

| 6.2 Summary of LLC Functions . . . . .                                     | 194         |

| 6.2.1 Layer-1 Related Functions . . . . .                                  | 194         |

| 6.2.2 HDLC-Controller Related Functions . . . . .                          | 194         |

| 6.2.3 External Functions . . . . .                                         | 195         |

| 6.3 LLC-Code Elements . . . . .                                            | 197         |

| 6.3.1 Structures . . . . .                                                 | 197         |

| 6.3.2 Definitions and Naming Conventions . . . . .                         | 198         |

| 6.3.2.1 Type Definitions . . . . .                                         | 198         |

| 6.3.2.2 Macro Definitions . . . . .                                        | 199         |

| 6.4 Interrupts . . . . .                                                   | 200         |

| 6.5 LLC-Routine Reference . . . . .                                        | 201         |

| 6.5.1 ISAC®-S TE Layer-1 Functions: The SBC Part . . . . .                 | 201         |

| 6.5.2 ISAC®-S TE HDLC-Controller Related Functions: The ICC Part . . . . . | 202         |

| 6.6 Listing of Driver Routines . . . . .                                   | 205         |

| <b>7 Package Outlines</b> . . . . .                                        | 237         |

IOM®<sup>TM</sup>, IOM®-1, IOM®-2, SICOFI®<sup>TM</sup>, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI®<sup>TM</sup>, ARCOFI®<sup>TM</sup>, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, IPAT®-2, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®-P, QUAT®-S are registered trademarks of Siemens AG.

MUSAC<sup>TM</sup>-A, FALC<sup>TM</sup> 54, IWE<sup>TM</sup>, SARE<sup>TM</sup>, UTPT<sup>TM</sup>, ASM<sup>TM</sup>, ASP<sup>TM</sup> are trademarks of Siemens AG.

Purchase of Siemens I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C-system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. Copyright Philips 1983.

## **Introduction**

The PSB 2186 ISAC®-S TE implements the four-wire S/T interface used to link voice/data terminals to an ISDN.

The PSB 2186 combines the functions of the S-Bus Interface Circuit (SBC: PEB 2080) and the ISDN Communications Controller (ICC: PEB 2070) on one chip.

The component switches B- and D-channels between the S/T and the ISDN Oriented Modular (IOM®) interfaces, the latter being a standard backplane interface for the ISDN-basic access.

The device provides all electrical and logical functions of the S/T interface, such as: activation/deactivation, mode dependent timing recovery and D-channel access and priority control.

The HDLC packets of the ISDN D-channel are handled by the ISAC-S which interfaces them to the associated microcontroller. In one of its operating modes the device offers high level support of layer-2 functions of the LAPD protocol.

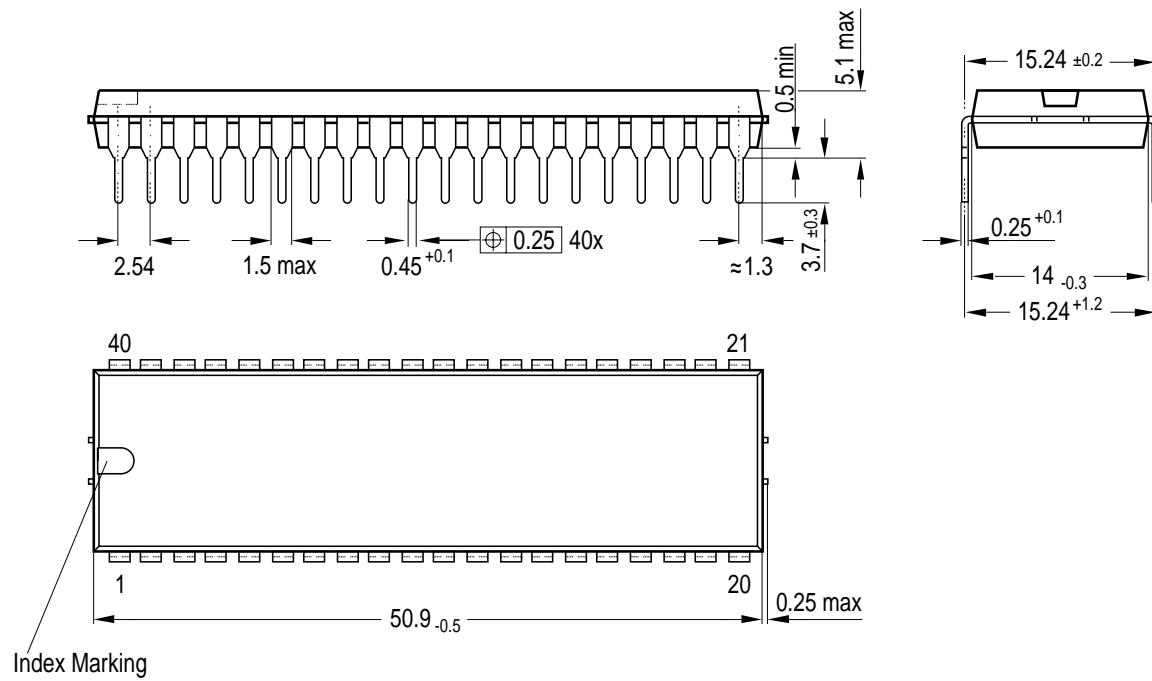

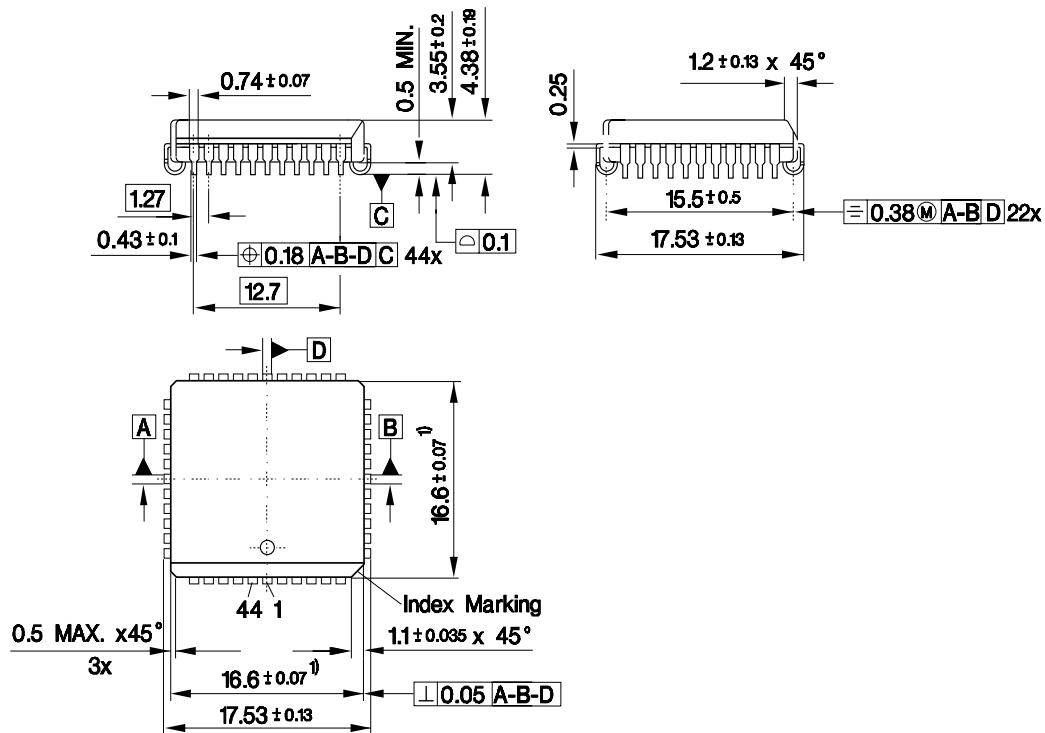

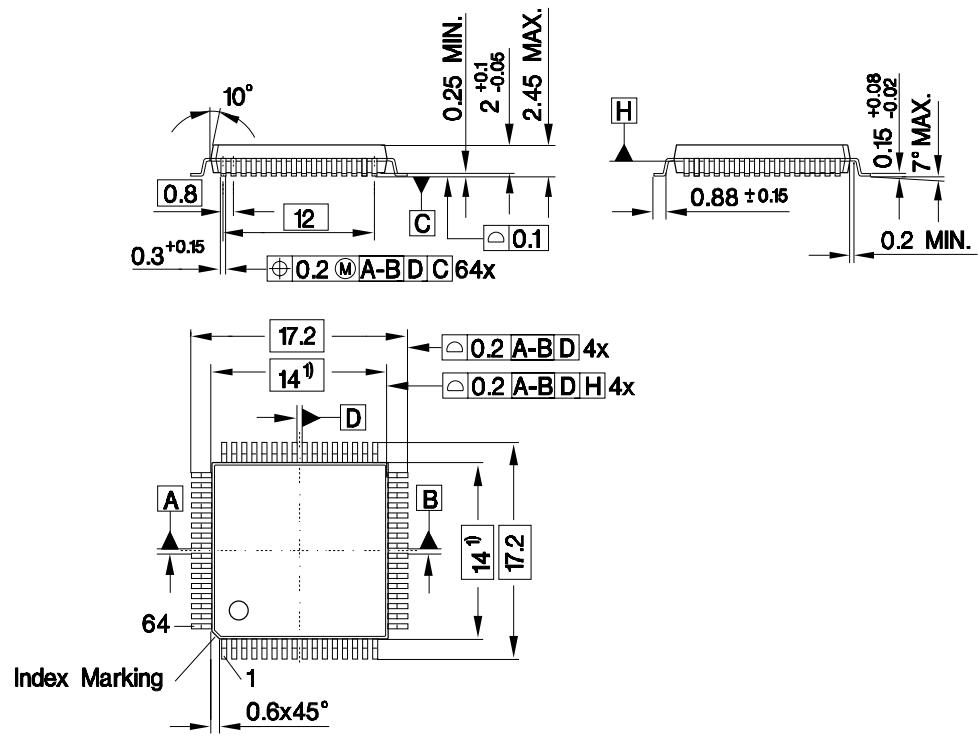

The ISAC-S is a CMOS device, available in a P-DIP-40, P-LCC-44, P-MQFP-64 package. It operates from a single + 5 V supply and features a power-down state with very low power consumption.

## ISDN Subscriber Access Controller for Terminals (ISAC®-S TE)

PSB 2186

### Preliminary Data

CMOS IC

#### 1 Features

Terminal IOM®-2 terminal specific version of the PEB 2086:

- Pin and software compatible to PEB 2086

- Compatible to PEB 2085 (Symmetrical Receiver)

- Full duplex 2B+D S/T interface transceiver according to CCITT I.430

- Conversion of the frame structure between the S/T interface and IOM-2

- Receive timing recovery

- D-channel access control

- Activation and deactivation procedures with automatic wake-up from power-down state

- Access to S and Q bits of S/T interface

- Adaptively switched receive thresholds

- Support of LAPD protocol

- FIFO buffer (2 x 64 bytes) for efficient transfer of D-channel packets

- 8-bit microprocessor interface, multiplexed or non-multiplexed

- Serial interface: IOM-2 interface including bit clock and strobe signal

- Implementation of IOM-2 MONITOR and C/I-channel protocol to control peripheral devices

- Microprocessor access to B- and intercommunication-channels

- Watchdog timer

- Advanced CMOS technology

- Low power consumption: standby: 8 mW; active: 80 mW

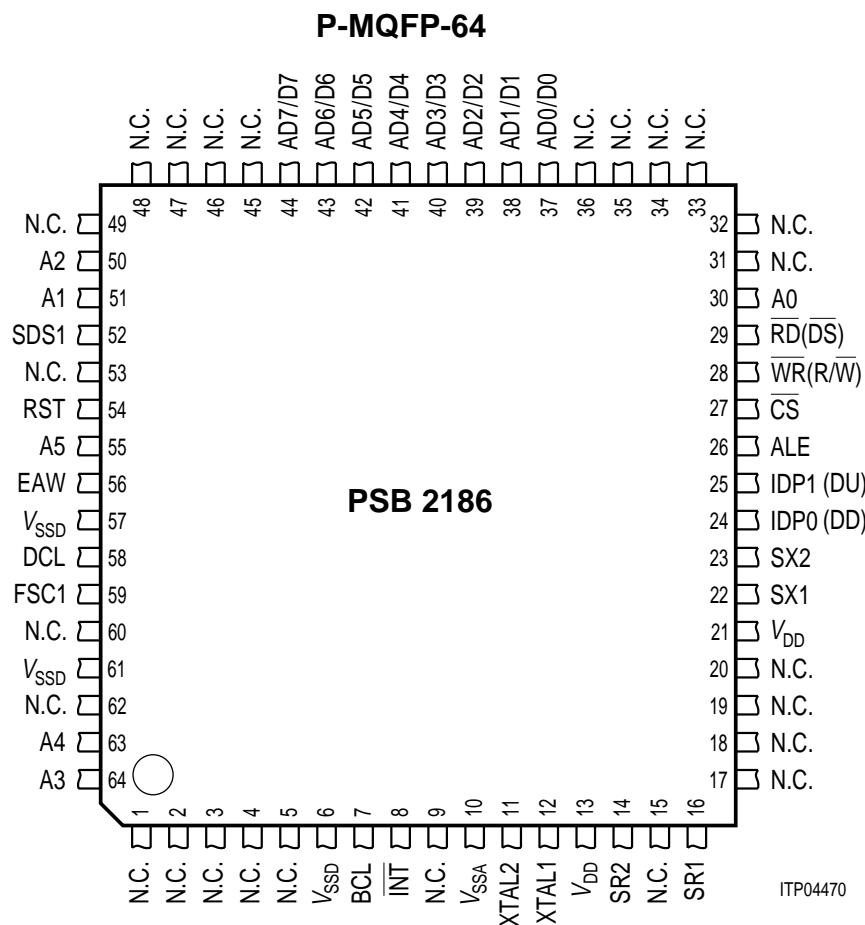

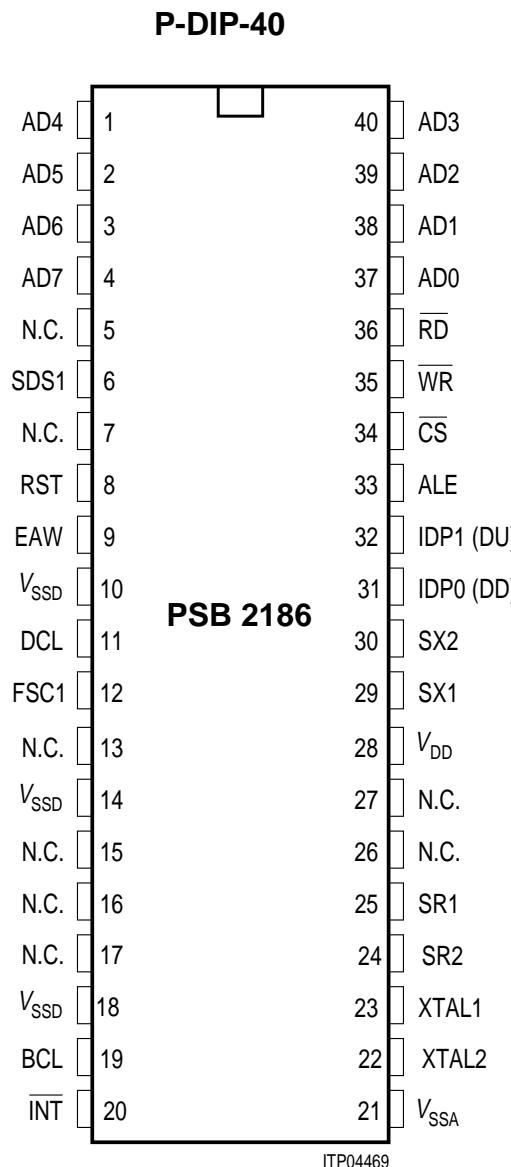

P-MQFP-64

P-LCC-44

P-DIP-40

| Type      | Ordering Code | Package         |

|-----------|---------------|-----------------|

| PSB 2186H | Q67100-H6412  | P-MQFP-64 (SMD) |

| PSB 2186N | Q67100-H6390  | P-LCC-44 (SMD)  |

| PSB 2186P | Q67100-H6389  | P-DIP-40        |

The PSB 2186, ISAC-S TE is software compatible to the PEB 2085, ISAC-S.

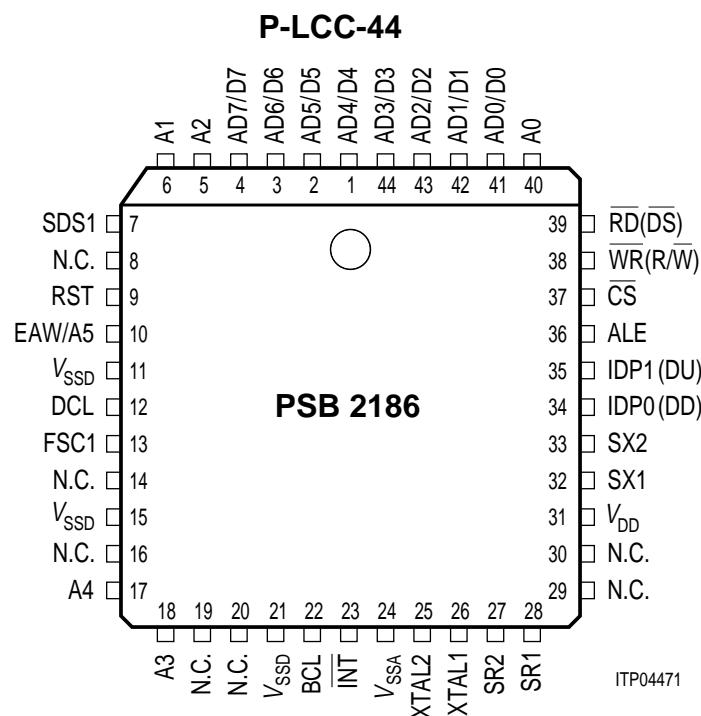

**Pin Configuration**

(top view)

**Pin Configuration

(top view)**

## 1.1 Pin Definitions and Functions

| Pin No.<br>P-DIP-40 | Pin No.<br>P-MQFP-64 | Pin No.<br>P-LCC-44 | Symbol | Input (I)<br>Output (O)<br>Open<br>Drain (OD) | Function                                                                                                                                                            |

|---------------------|----------------------|---------------------|--------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37                  | 37                   | 41                  | AD0/D0 | I/O                                           | <b>Multiplexed Bus Mode:</b><br>Address/data bus transfers addresses from the µP system to the ISAC-S TE and data between the µP system and the ISAC-S TE.          |

| 38                  | 38                   | 42                  | AD1/D1 | I/O                                           |                                                                                                                                                                     |

| 39                  | 39                   | 43                  | AD2/D2 | I/O                                           |                                                                                                                                                                     |

| 40                  | 40                   | 44                  | AD3/D3 | I/O                                           |                                                                                                                                                                     |

| 1                   | 41                   | 1                   | AD4/D4 | I/O                                           |                                                                                                                                                                     |

| 2                   | 42                   | 2                   | AD5/D5 | I/O                                           |                                                                                                                                                                     |

| 3                   | 43                   | 3                   | AD6/D6 | I/O                                           | <b>Non-Multiplexed Bus Mode:</b><br>Data bus. Transfers data between the µP system and the ISAC-S TE.                                                               |

| 4                   | 44                   | 4                   | AD7/D7 | I/O                                           |                                                                                                                                                                     |

| 34                  | 27                   | 37                  | CS     | I                                             | <b>Chip Select:</b> A “Low” on this line selects the ISAC-S TE for a read/write operation.                                                                          |

| –                   | 28                   | 38                  | R/W    | I                                             | <b>Read/Write:</b> When “High” identifies a valid µP access as a read operation. When “Low”, identifies a valid µP access as a write operation (Motorola bus mode). |

| 35                  | 28                   | 38                  | WR     | I                                             | <b>Write:</b> This signal indicates a write operation (Intel bus mode).                                                                                             |

| –                   | 29                   | 39                  | DS     | I                                             | <b>Data Strobe:</b> The rising edge marks the end of a valid read or write operation (Motorola bus mode).                                                           |

| 36                  | 29                   | 39                  | RD     | I                                             | <b>Read:</b> This signal indicates a read operation (Intel bus mode).                                                                                               |

| 20                  | 8                    | 23                  | INT    | OD                                            | <b>Interrupt Request:</b> The signal is activated when the ISAC-S TE requests an interrupt. It is an open drain output.                                             |

## 1.1 Pin Definitions and Functions (cont'd)

| Pin No.<br>P-DIP-40 | Pin No.<br>P-MQFP-64 | Pin No.<br>P-LCC-44 | Symbol | Input (I)<br>Output (O)<br>Open<br>Drain (OD) | Function                                                                                                                                                                                                                                 |

|---------------------|----------------------|---------------------|--------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33                  | 26                   | 36                  | ALE    | I                                             | <b>Address Latch Enable:</b> A high on this line indicates an address on the address/data bus (multiplexed bus type only). ALE also selects the microprocessor interface type (multiplexed or non-multiplexed) P-LCC and P-MQFP only.    |

| 8                   | 54                   | 9                   | RST    | I/O                                           | <b>Reset:</b> A “High” on this input forces the ISAC-S TE into reset state. The minimum pulse length is four DCL-clock periods or four ms. If the terminal specific functions are enabled, the ISAC-S TE may also supply a reset signal. |

| 12                  | 59                   | 13                  | FSC1   | O (I)                                         | <b>Frame Sync 1:</b> Frame sync output. “High” during channel 0 on the IOM-2 interface. FSC1 becomes Input if Test Mode is programmed (ADF1).                                                                                            |

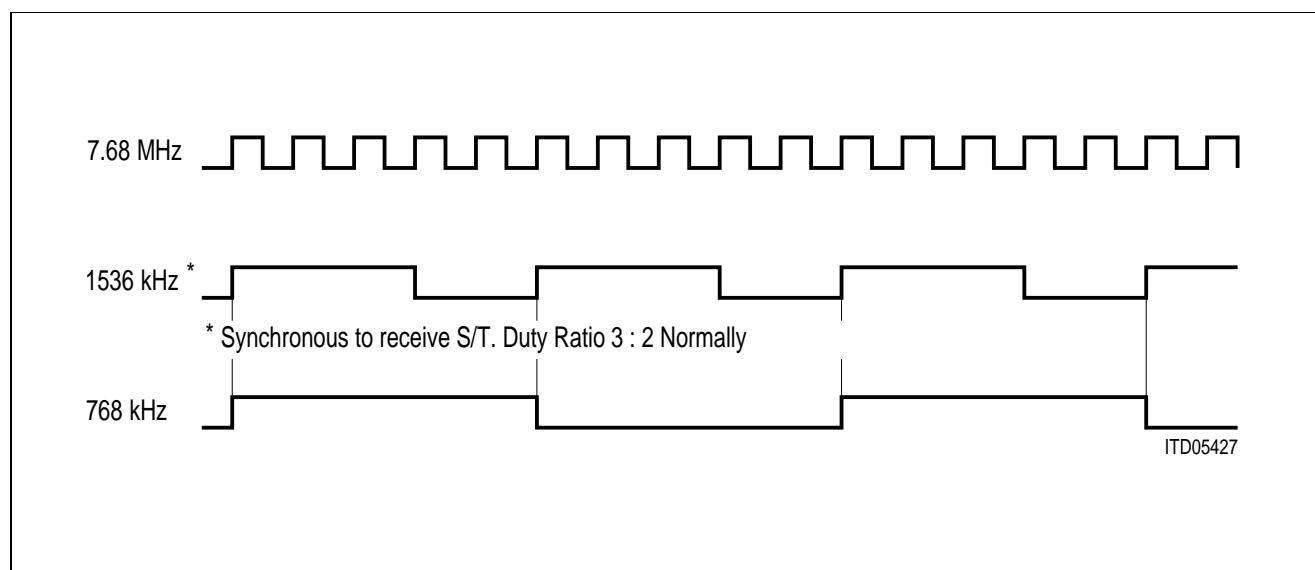

| 11                  | 58                   | 12                  | DCL    | O (I)                                         | <b>Data Clock:</b> Clock of frequency equal to twice the data rate on the IOM-interface Clock output 1536-kHz IOM-2 mode DCL becomes Input if Test Mode is programmed (ADF1).                                                            |

| —                   | 30                   | 40                  | A0     | I                                             | Address Bit 0                                                                                                                                                                                                                            |

| —                   | 51                   | 6                   | A1     | I                                             | Address Bit 1                                                                                                                                                                                                                            |

| —                   | 50                   | 5                   | A2     | I                                             | Address Bit 2(Non-multiplexed)                                                                                                                                                                                                           |

| —                   | 64                   | 18                  | A3     | I                                             | Address Bit 3bus mode)                                                                                                                                                                                                                   |

| —                   | 63                   | 17                  | A4     | I                                             | Address Bit 4                                                                                                                                                                                                                            |

| —                   | 55                   | 10                  | A5     | I                                             | Address Bit 5                                                                                                                                                                                                                            |

## 1.1 Pin Definitions and Functions (cont'd)

| Pin No.<br>P-DIP-40 | Pin No.<br>P-MQFP-64 | Pin No.<br>P-LCC-44 | Symbol    | Input (I)<br>Output (O)<br>Open<br>Drain (OD) | Function                                                                                                                                                                                                                                      |

|---------------------|----------------------|---------------------|-----------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9                   | 56                   | 10                  | EAW       | I                                             | <b>External Awake</b> (terminal specific function). If a falling edge on this input is detected, the ISAC-S TE generates an interrupt and, if enabled, a reset pulse.                                                                         |

| 6                   | 52                   | 7                   | SDS1      | O                                             | <b>Serial Data Strobe 1.</b><br>A programmable strobe signal, selecting either one or two B- or IC-channels on IOM-2 interface, is supplied via this line. After reset, SDS1 takes on its function only after a write access to SPCR is made. |

| 19                  | 7                    | 22                  | BCL       | O                                             | <b>Bit Clock:</b> Clock of frequency 768 kHz, IOM-2 mode.                                                                                                                                                                                     |

| 10, 14, 18          | 57, 6, 61            | 11, 15, 21          | $V_{SSD}$ | —                                             | Digital ground                                                                                                                                                                                                                                |

| 21                  | 10                   | 24                  | $V_{SSA}$ | —                                             | Analog ground                                                                                                                                                                                                                                 |

| 28                  | 13, 21               | 31                  | $V_{DD}$  | —                                             | Power supply (5 V $\pm$ 5 %)                                                                                                                                                                                                                  |

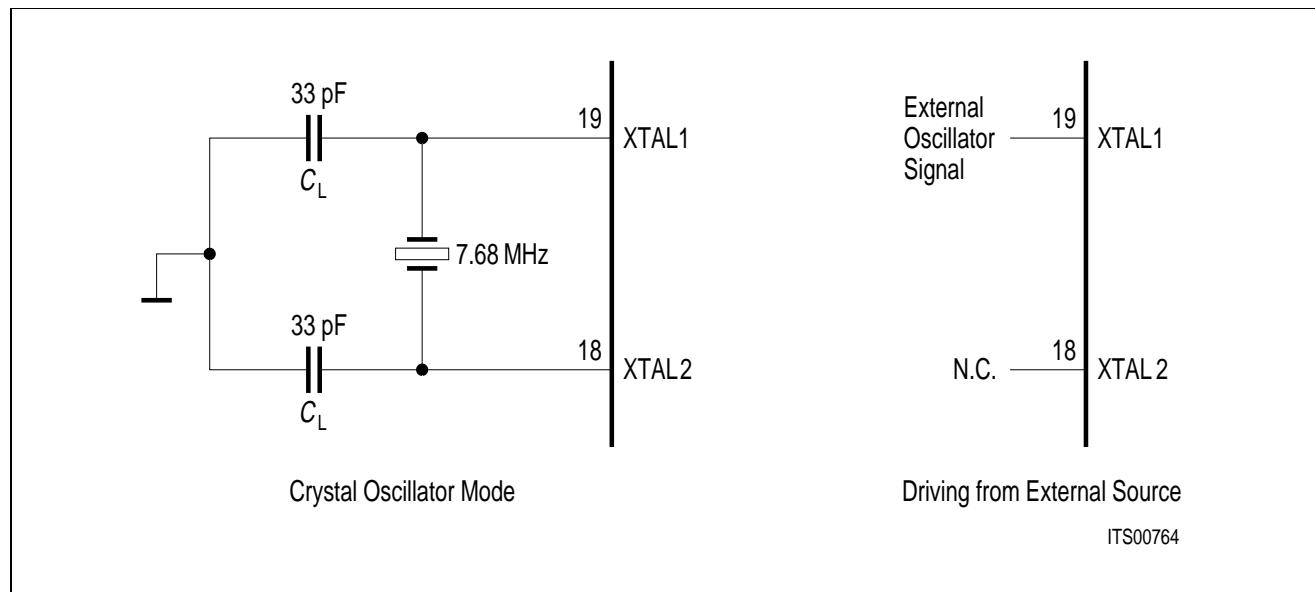

| 23                  | 12                   | 26                  | XTAL1     | I                                             | Connection for crystal or external clock input                                                                                                                                                                                                |

| 22                  | 11                   | 25                  | XTAL2     | O                                             | Connection for external crystal.<br>Left unconnected if external clock is used.                                                                                                                                                               |

| 24                  | 14                   | 27                  | SR2       | I                                             | <b>S-Bus Receiver Input</b>                                                                                                                                                                                                                   |

| 25                  | 16                   | 28                  | SR1       | I                                             | <b>S-Bus Receiver Input</b>                                                                                                                                                                                                                   |

| 29                  | 22                   | 32                  | SX1       | O                                             | <b>S-Bus Transmitter Output</b> (positive)                                                                                                                                                                                                    |

| 30                  | 23                   | 33                  | SX2       | O                                             | <b>S-Bus Transmitter Output</b> (negative)                                                                                                                                                                                                    |

| 31                  | 24                   | 34                  | IDP0(DD)  | I/O                                           | <b>IOM-Data Port 0 (DD)</b>                                                                                                                                                                                                                   |

| 32                  | 25                   | 35                  | IDP1(DU)  | I/O                                           | <b>IOM-Data Port 1 (DU)</b><br>Open drain without internal pull-up resistor or push-pull (ADF2:ODS)                                                                                                                                           |

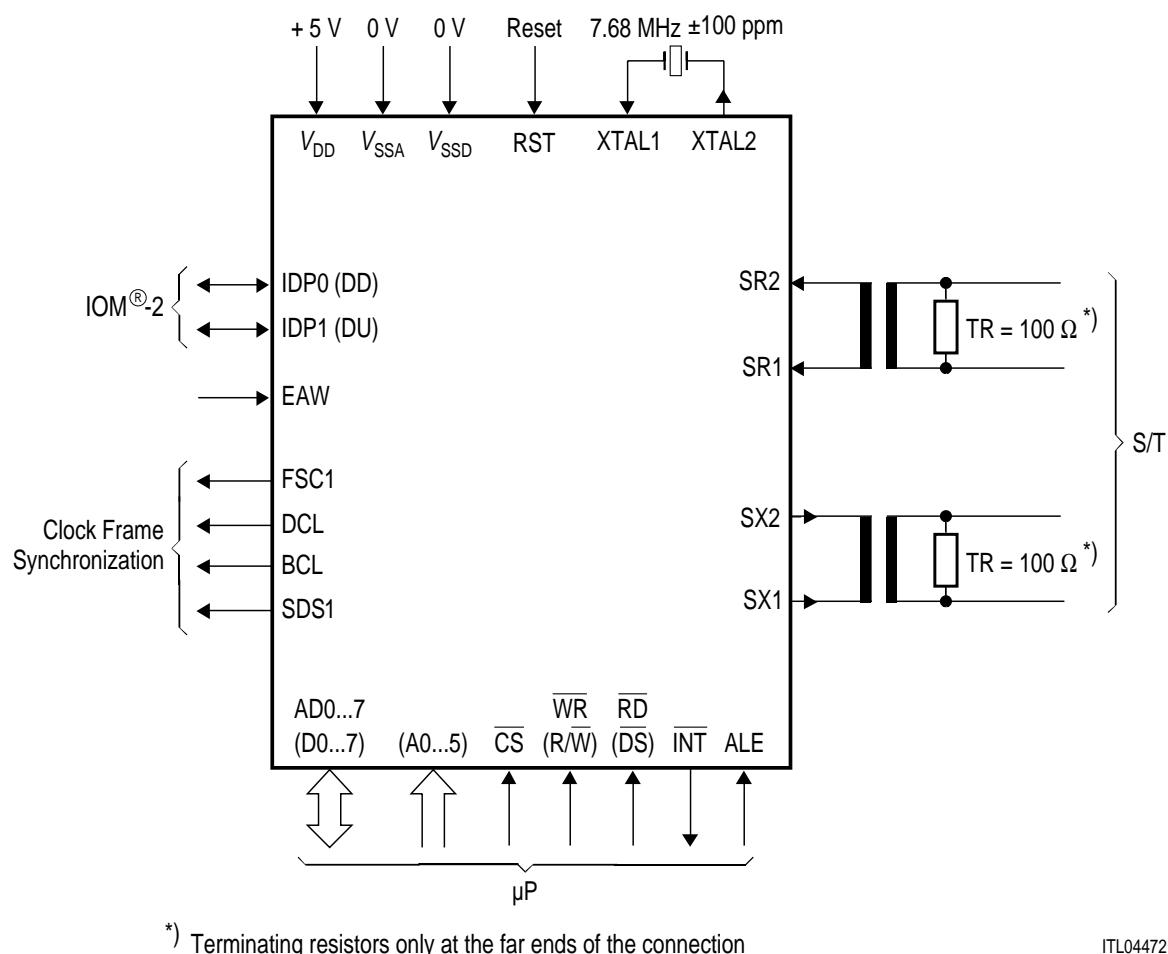

## 1.2 Logic Symbol

ITL04472

**Figure 1**

Logic Symbol of the ISAC®-S TE PSB 2186

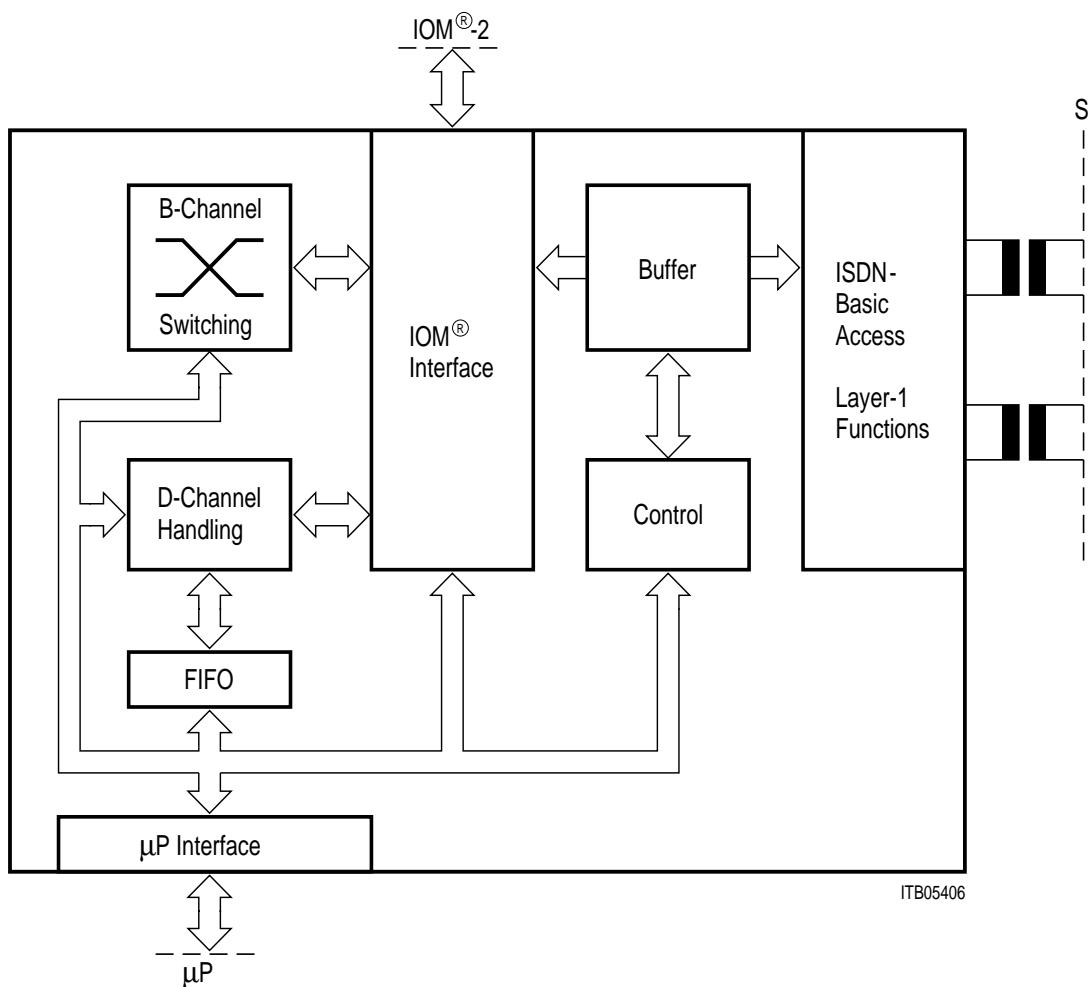

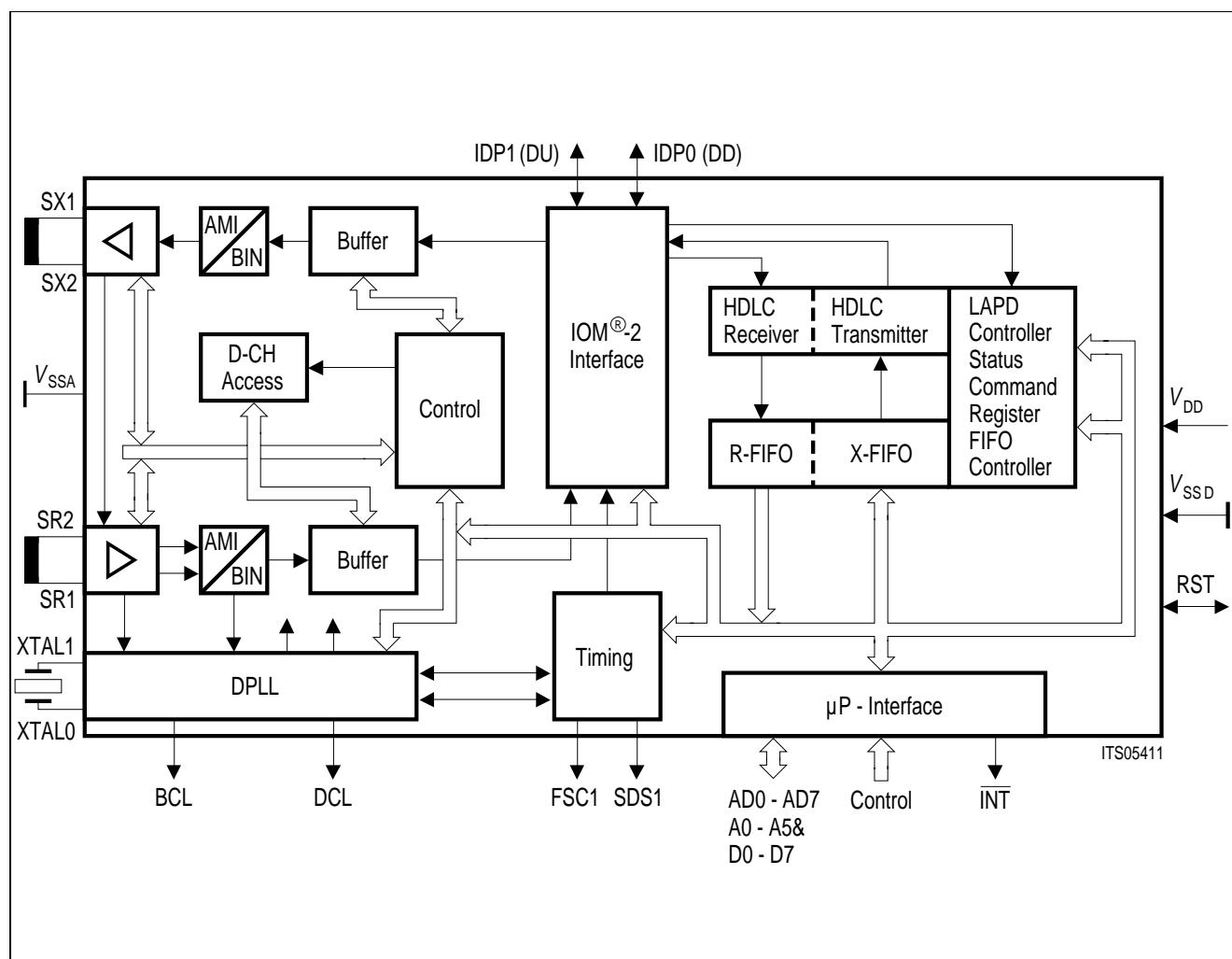

## 1.3 Functional Block Diagram

**Figure 2**

**Block Diagram of the ISAC®-S TE**

## 1.4 System Integration

### 1.4.1 ISDN Applications

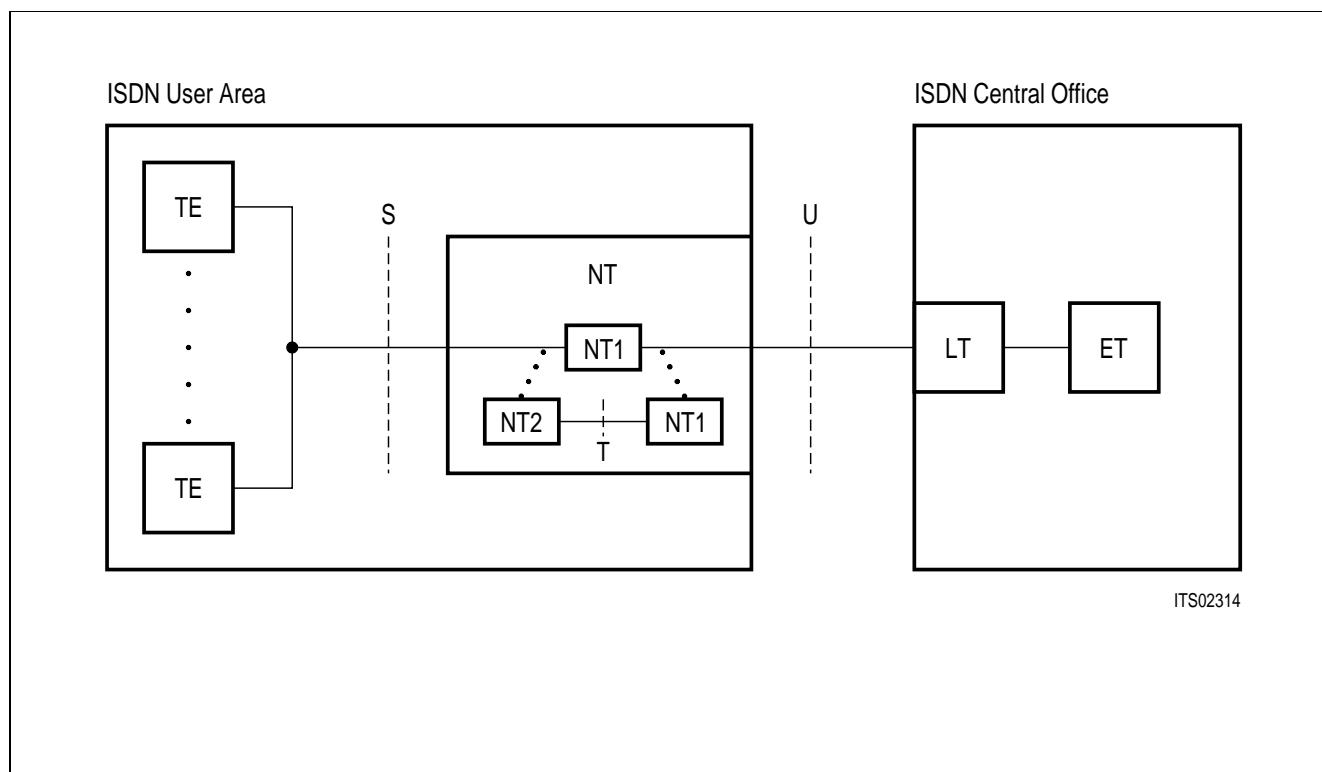

The reference model for the ISDN-basic access according to CCITT I series recommendations consists of

- an exchange and trunk line termination in the central office (ET, LT)

- a remote network termination in the user area (NT)

- a two-wire loop (U interface) between NT and LT

- a four-wire link (S interface) which connects subscriber terminals and the NT in the user area as depicted in **figure 3**.

**Figure 3**

**ISDN-Basic Subscriber Access Architecture**

The NT equipment serves as a converter between the U interface at the exchange and the S interface at the user premises. The NT may consist of either an NT1 only or an NT1 together with an NT2 connected via the T interface which is physically identical to the S interface. The NT1 is a direct transformation between layer 1 of S and layer 1 of U. NT2 may include higher level functions like multiplexing and switching as in a PBX.

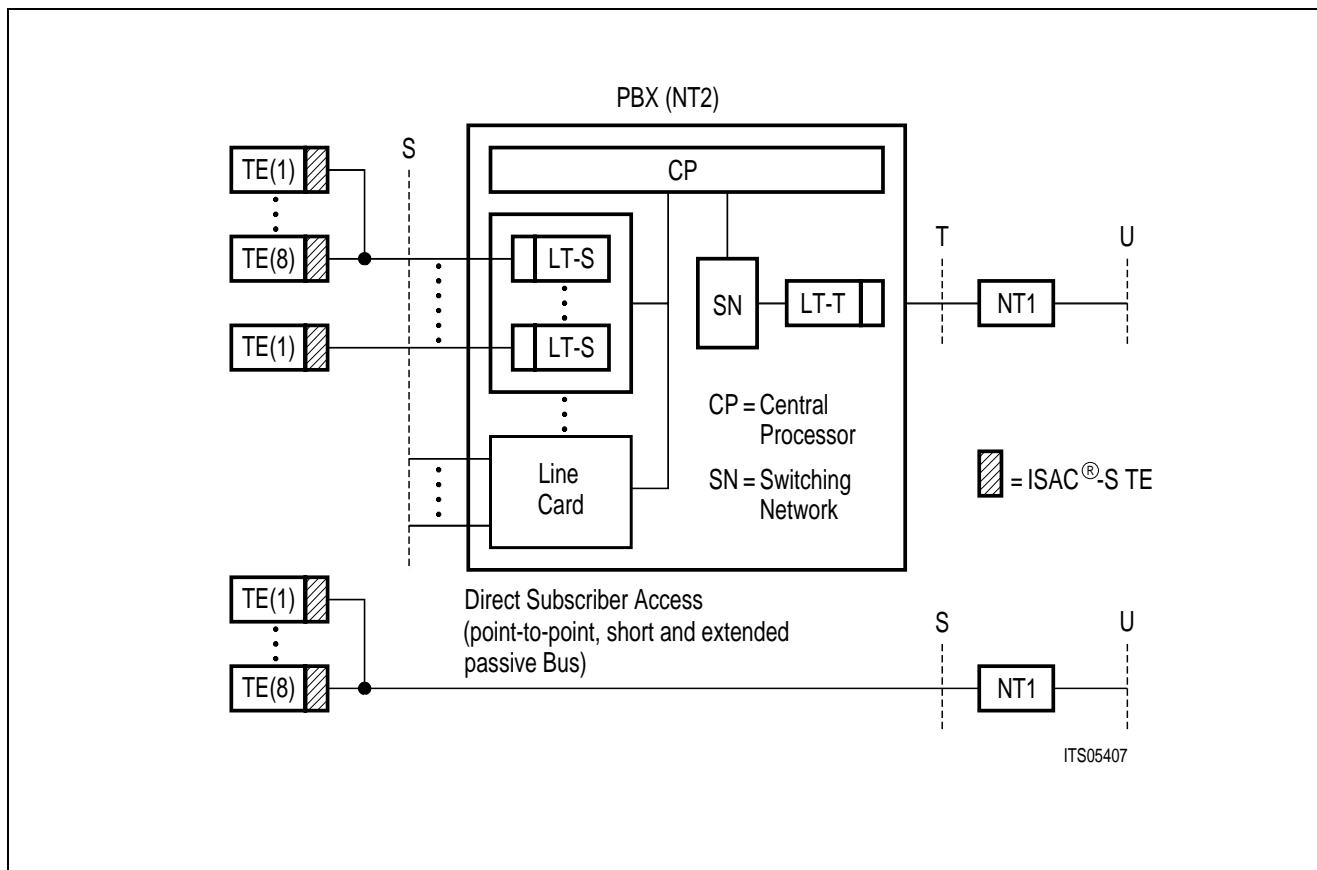

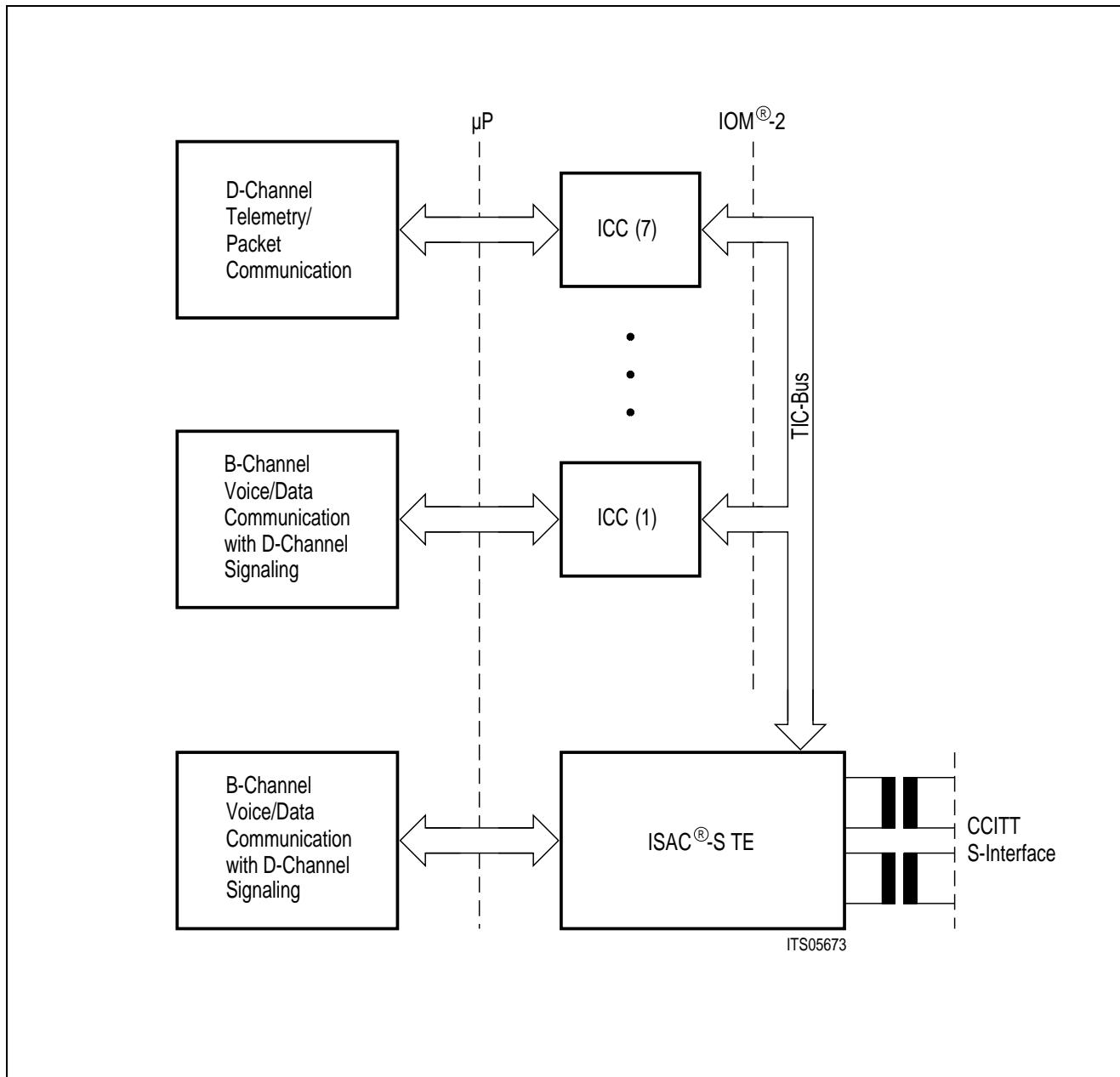

The ISAC-S TE is designed for the user area of the ISDN-basic access, especially for subscriber terminal equipment with S interfaces. **Figure 4** illustrates the application of the ISAC-S TE.

**Figure 4**

**Applications of the ISAC®-S TE (ISDN-Basic Access)**

### Terminal Applications

The concept of the ISDN basic access is based on two circuit-switched 64 kbit/s B channels and a message oriented 16 kbit/s D channel for packetized data, signaling and telemetry information.

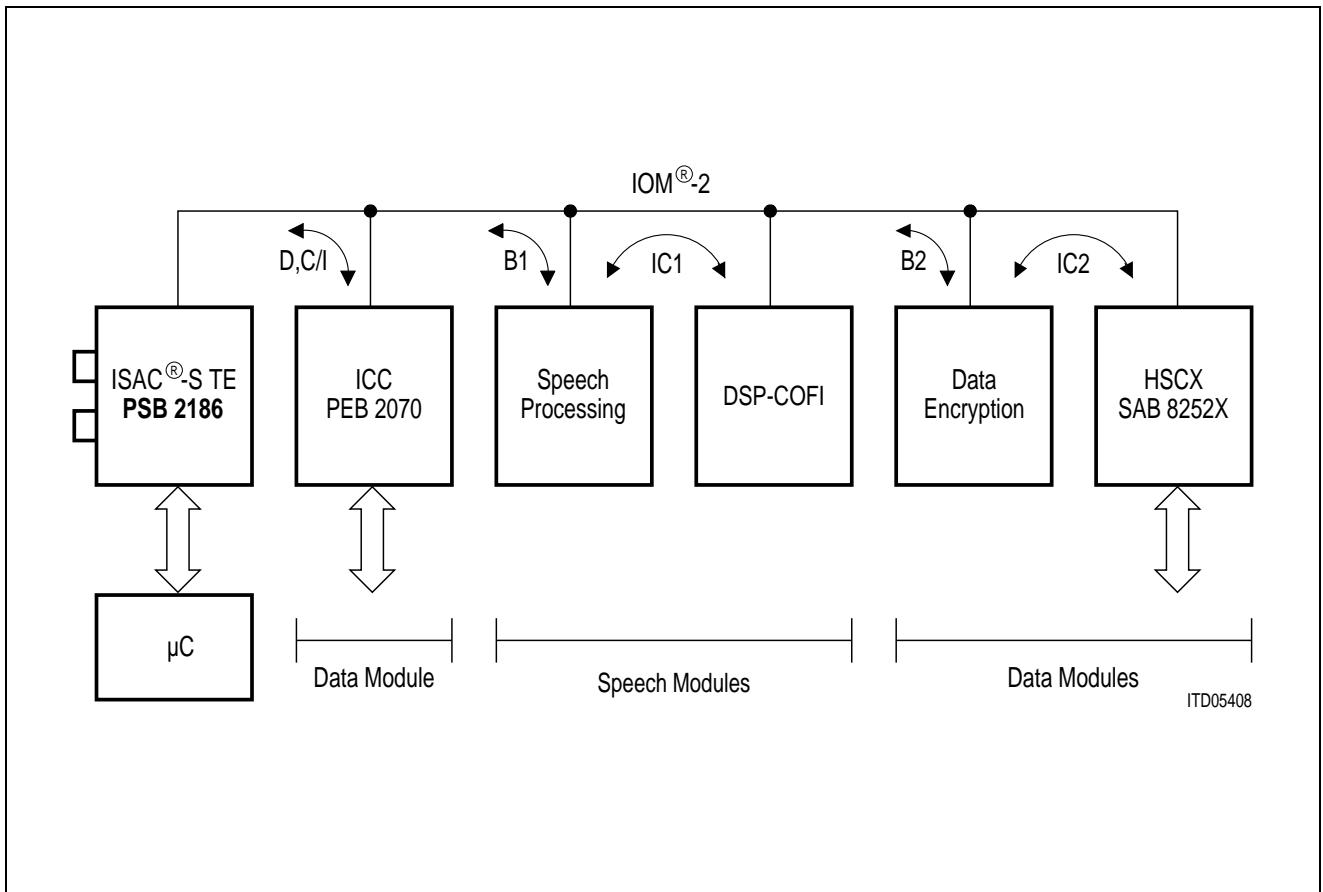

**Figure 5** shows an example of an integrated **multifunctional ISDN-S** terminal using the ISAC-S TE. The ISAC-S TE provides the interface to the bus and separates the B- and D channels.

The D channel, containing signaling data and packet switched data, is processed by the LAPD controller contained in the ISAC-S TE and routed via a parallel  $\mu$ P interface to the terminal processor. The high level support of the LAPD protocol which is implemented by the ISAC-S TE allows the use of a low cost processor in cost sensitive applications.

The IOM-2 interface generated by the ISAC-S TE is used to connect different voice/data (V/D) application modules:

- sources/sinks for the D channel

- sources/sinks for the B1- and B2 channels.

**Figure 5**

**Example of an ISDN®-S TE Voice/Data Terminal**

Up to eight D-channel components (ICC: ISDN Communication Controller PEB 2070) may be connected to the D- and C/I (Command/Indication) channels (TIC-bus). The ISAC-S TE and ICC handle contention autonomously.

Data transfers between the ISAC-S TE and the voice/data modules are done with the help of the IOM-MONITOR channel protocol. Each V/D module can be accessed by an individual address. The same protocol enables the control of IOM-terminal modules and the allocation of intercommunication channels inside the terminal. Two intercommunication channels IC1 and IC2 allow a  $2 \times 64$  kbit/s transfer rate between voice/data modules.

In the example above (**figure 5**), one ICC is used for data packets in the D channel. A voice processor is connected to a programmable digital signal processing codec filter via IC1 and a data encryption module to a data device via IC2. B1 is used for voice communication, B2 for data communication.

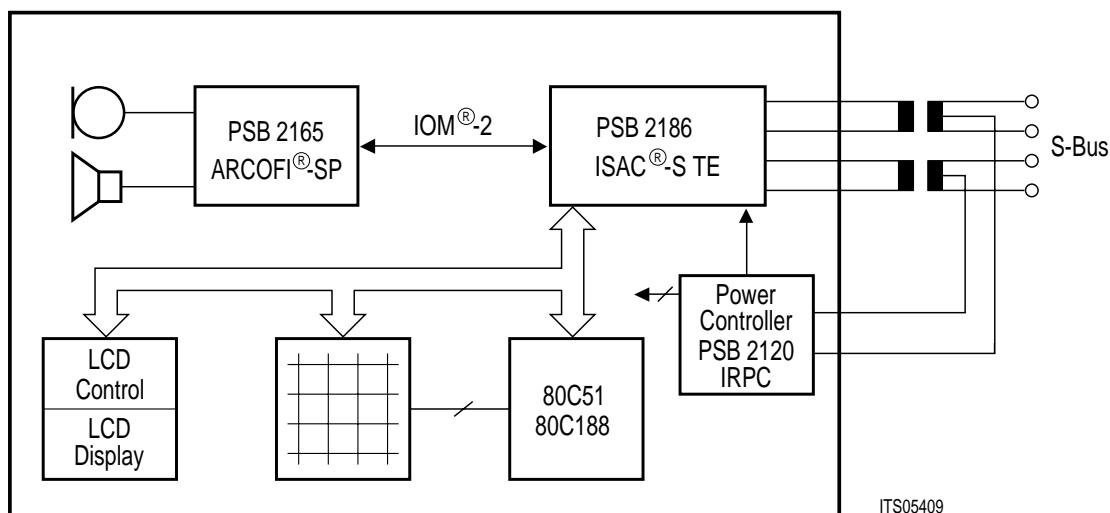

**Figure 6** shows the implementation of a ISDN feature phone using the ISAC-S TE and the Audio Ringing Codec Filter featuring speakerphone (PSB 2165, ARCOFI®-SP).

**Figure 6**

**ISDN-Feature Telephone**

## 1.4.2 Microprocessor Environment

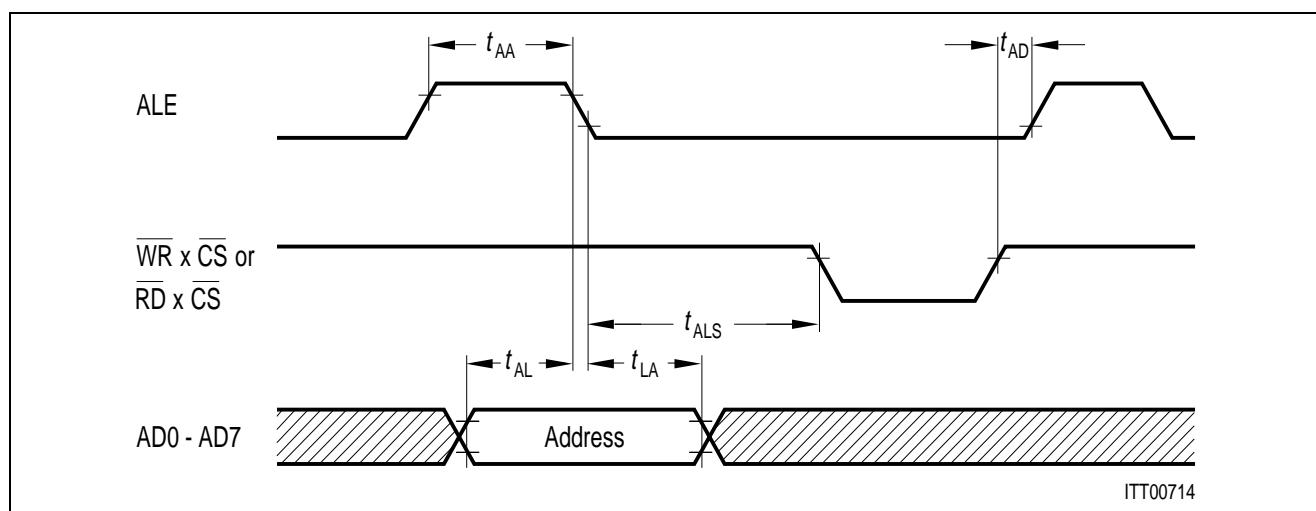

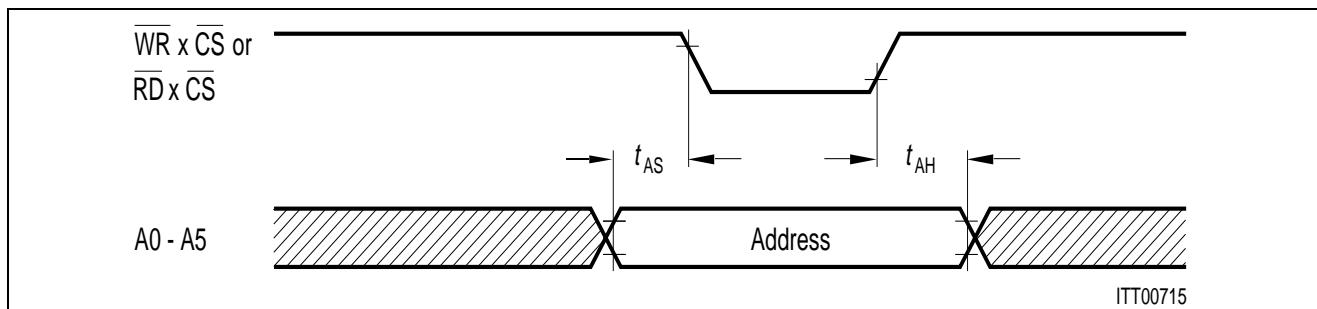

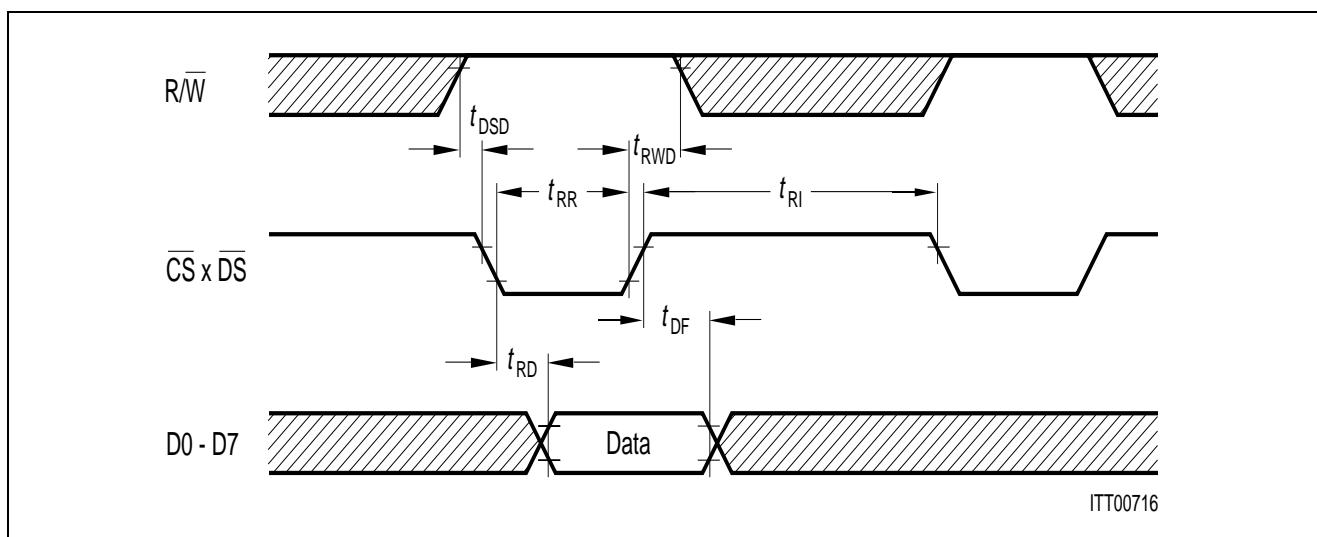

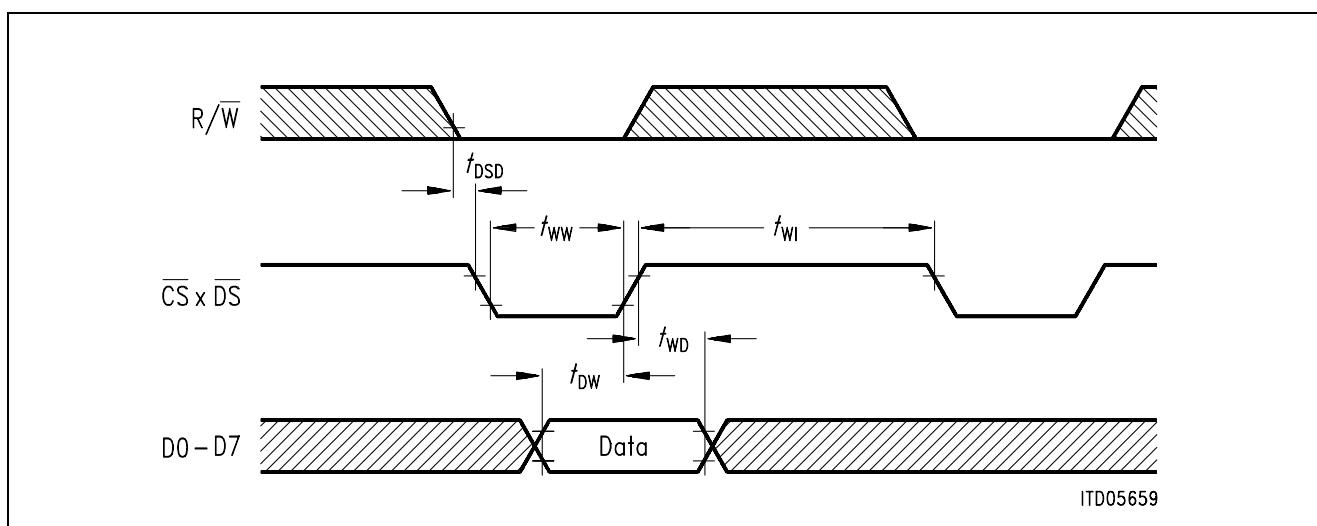

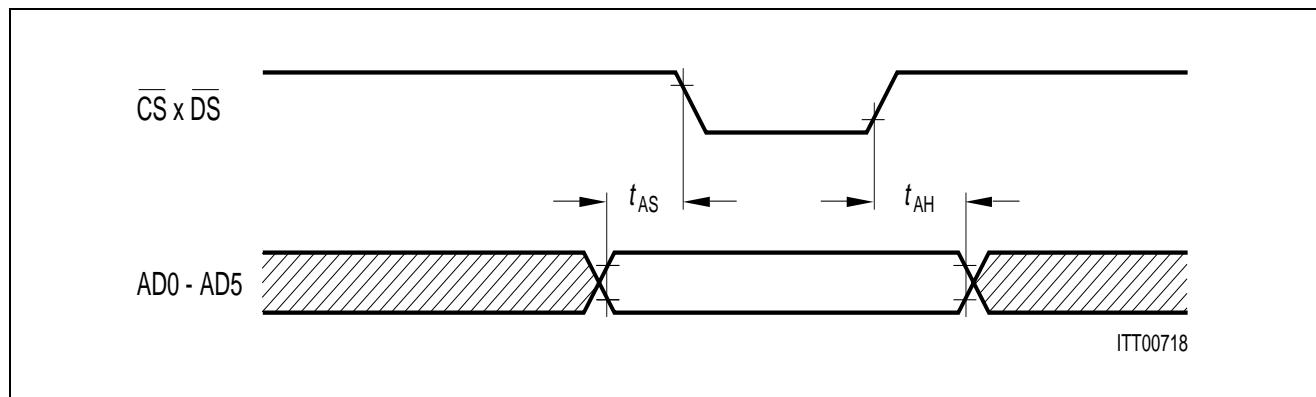

The ISAC-S TE is especially suitable for cost-sensitive applications with single-chip microcontrollers (e.g. 8048, 8031, 8051). However, due to its programmable micro-processor interface and non-critical bus timing, it fits perfectly into almost any 8-bit microprocessor system environment. The microcontroller interface can be selected to be either of the Motorola type (with control signals  $\overline{CS}$ ,  $\overline{R/W}$ ,  $\overline{DS}$ ) of the Siemens/Intel non-multiplexed bus type (with control signals  $\overline{CS}$ ,  $\overline{WR}$ ,  $\overline{RD}$ ) or of the Siemens/Intel multiplexed address/data bus type ( $\overline{CS}$ ,  $\overline{WR}$ ,  $\overline{RD}$ , ALE).

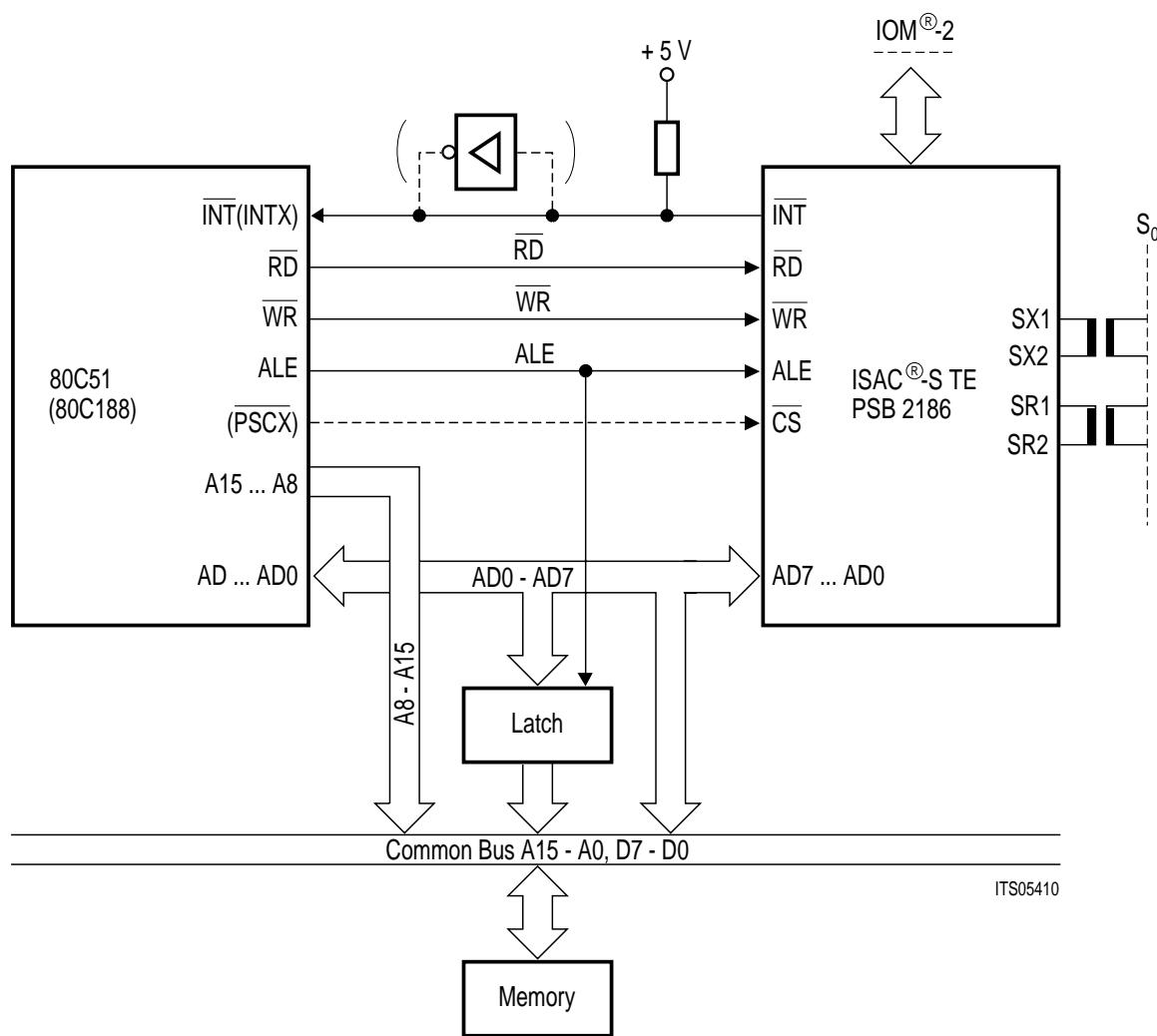

An example how to connect the ISAC-S TE to a Siemens/Intel microcontroller is shown in **figure 7**.

**Figure 7**

Connecting the ISAC®-S TE to Siemens/Intel Microcontroller

## 2 Functional Description

### 2.1 General Functions and Device Architecture

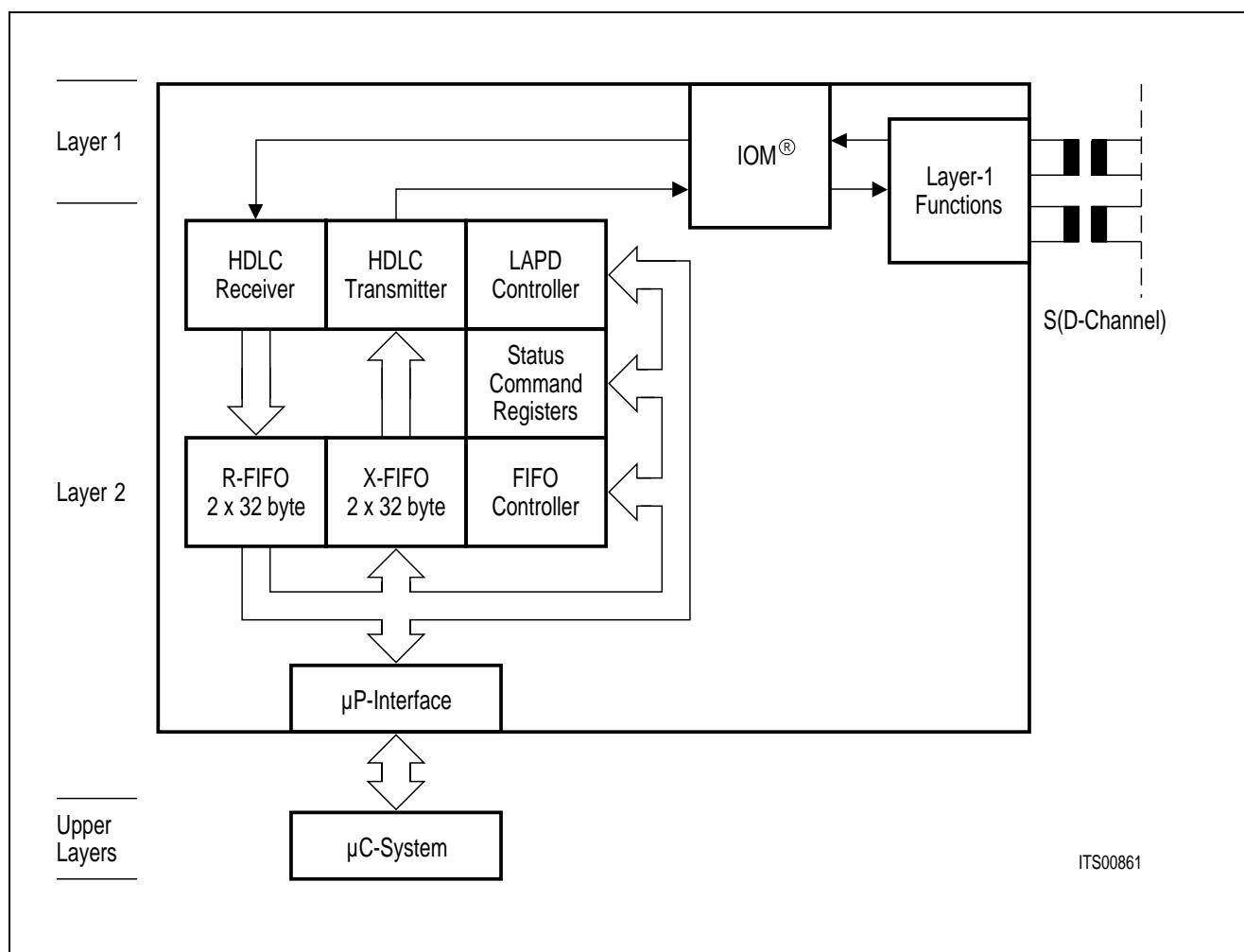

The functional block diagram of the ISAC-S TE is shown in **figure 8**.

The left-hand side of the diagram contains the layer-1 functions, according to CCITT I series recommendations:

- S-bus transmitter and receiver

- timing recovery and synchronization by means of digital PLL circuitry

- activation/deactivation

- access to S and Q channels

- handling of D channel

- test loops

- send single/continuous AMI pulses (diagnostics).

**Figure 8**

Architecture of the ISAC®-S TE

The right-hand side consists of:

- the serial interface logic for the IOM-2 interfaces, with B-channel switching capabilities

- the logic necessary to handle the D-channel messages (layer 2).

The latter consists of an HDLC receiver and an HDLC transmitter together with 64-byte deep FIFO's for efficient transfer of the messages to/from the user's CPU.

In a special HDLC-controller operating mode, the auto mode, the ISAC-S TE processes protocol handshakes (I- and S frames) of the LAPD (Link Access Procedure on the D channel) autonomously.

Control and monitor functions as well as data transfers between the user's CPU and the D- and B channels are performed by the 8-bit parallel  $\mu$ P-interface logic.

The IOM interface allows interaction between layer-1 and layer-2 functions. It implements D-channel collision resolution for connecting other layer-2 devices to the IOM interface (TIC bus), and the C/I and MONITOR channel protocols (IOM-2) to control peripheral devices.

The timing unit is responsible for the system clock and frame synchronization.

## 2.2 Interface and Operating Modes

The ISAC-S TE is configurable for the following application:

- ISDN terminals → TE mode

### IOM®-2 Interface Mode (ADF2:IMS=1)

In this mode the IOM interface has the enhanced functionality of IOM-2. B-channel interfacing is performed directly via the IOM-2 interface.

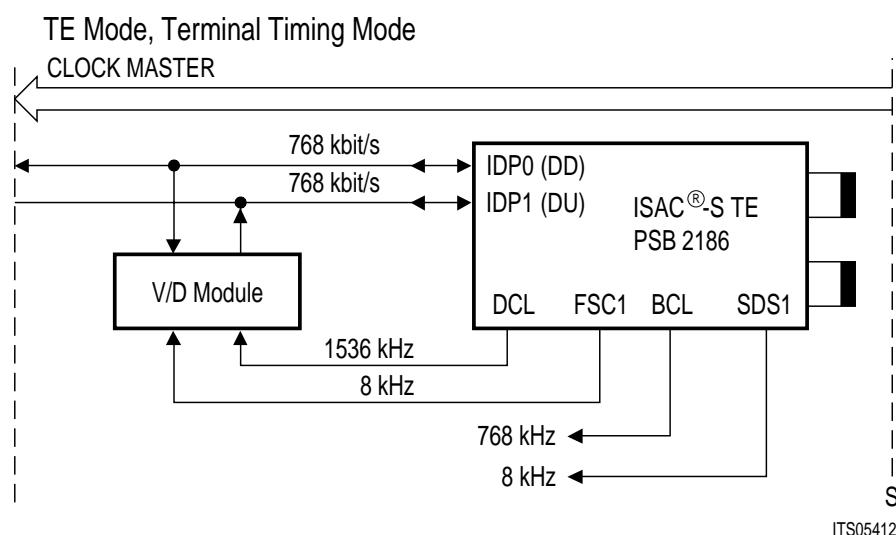

The ISAC-S TE supports the IOM-2 terminal mode frame structure (3 channels) according to **figure 11 (see chapter 2.3.1)**.

The operating mode is shown in **table 1**.

**Table 1**

**Operating Mode and Functions of Specific Pins of the ISAC®-S PSB 2186 in IOM®-2 Mode**

| Pin No.<br>P-DIP-40-2  | 11          | 12       | 19         |

|------------------------|-------------|----------|------------|

| Pin No.<br>P-LCC-44-1  | 12          | 13       | 22         |

| Pin No.<br>P-MQFP-64-1 | 58          | 59       | 7          |

| Application            | DCL         | FSC1     | BCL        |

| TE                     | o:1536 kHz* | o:8 kHz* | o:768 kHz* |

\*) synchronized to the S/T interface      o:output

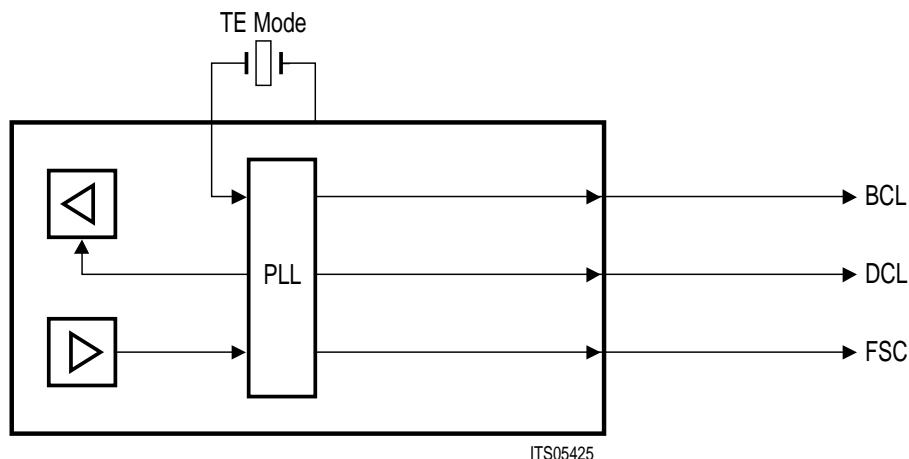

The operating mode in relation to the timing recovery is illustrated in **figure 9**.

**Figure 9**

**Operating Modes of ISAC®-S TE (IOM®-2)**

## 2.3 IOM®-2 Mode Functions

### 2.3.1 Basic IOM®-2 Frame Structure

The IOM-2 is a generalization and enhancement of the IOM-1. While the basic frame structure is very similar, IOM-2 offers further capacity for the transfer of maintenance information. In terminal applications, the IOM-2 constitutes a powerful backplane bus offering intercommunication and sophisticated control capabilities for peripheral modules.

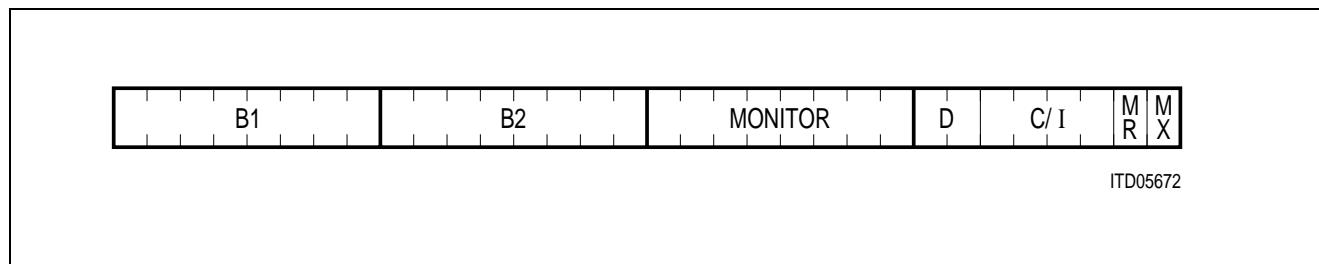

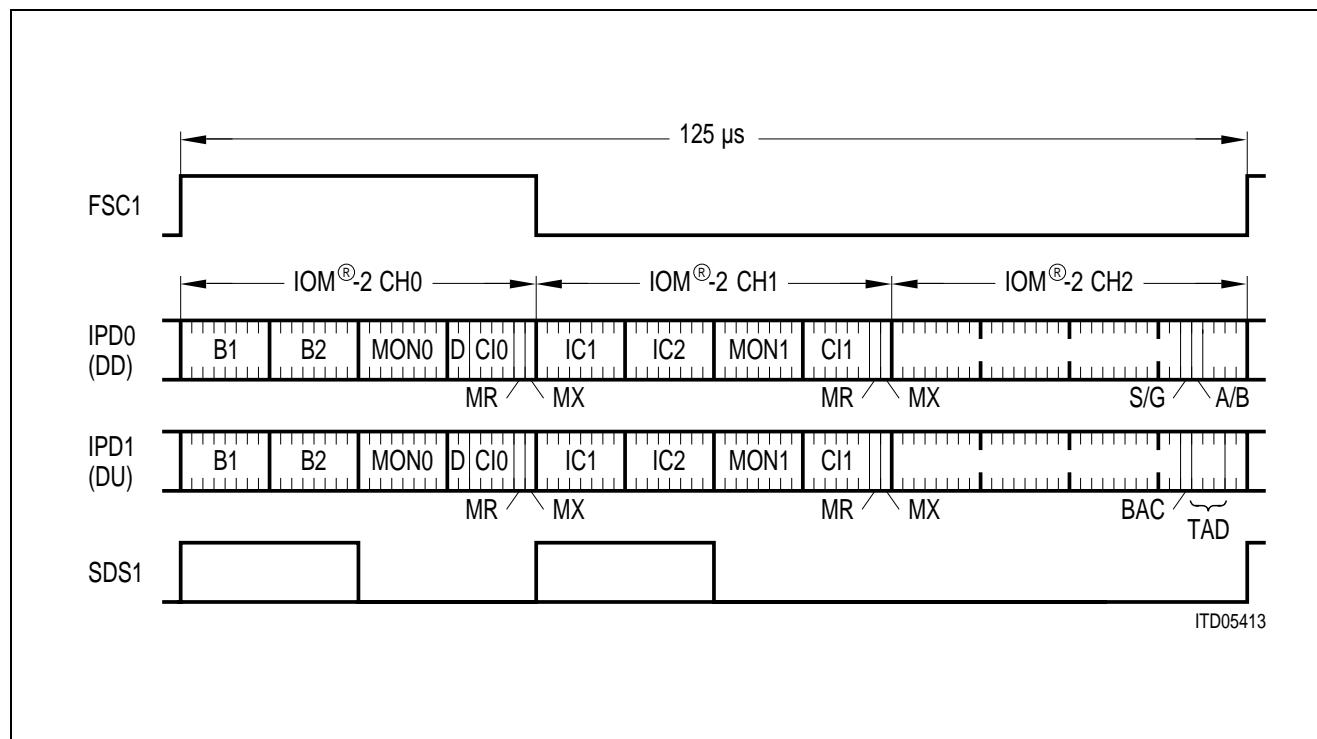

The channel structure of the IOM-2 is depicted in **figure 10**.

**Figure 10**

**Channel Structure of IOM®-2**

- The 64-kbit/s channels, B1 and B2, are conveyed in the first two octets.

- The third octet (monitor channel) is used for transferring maintenance information between the layer-1 functional blocks (SBCX, IECQ) and the layer-2 controller (**see chapter 2.3.4**).

- The fourth octet (control channel) contains

- two bits for the 16-kbit/s D channel

- four command/indication bits for controlling activation/deactivation and for additional control functions

- two bits MR and MX for supporting the handling of the MONITOR channel.

## IOM®-2 TE Frame Structure

The frame is composed of three channels (**figure 11**):

- Channel 0 contains 144 kbit/s (for 2B+D) plus MONITOR and command/indication channels for the layer-1 device.

- Channel 1 contains two 64-kbit/s intercommunication channels plus MONITOR and command/indication channels for other IOM-2 devices.

- Channel 2 is used for IOM-bus arbitration (access to the TIC bus). Only the command/indication bits are used in channel 2. **See section 2.3.6** for details.

**Figure 11**

**Definition of IOM®-2 Channels in Terminal Timing Mode**

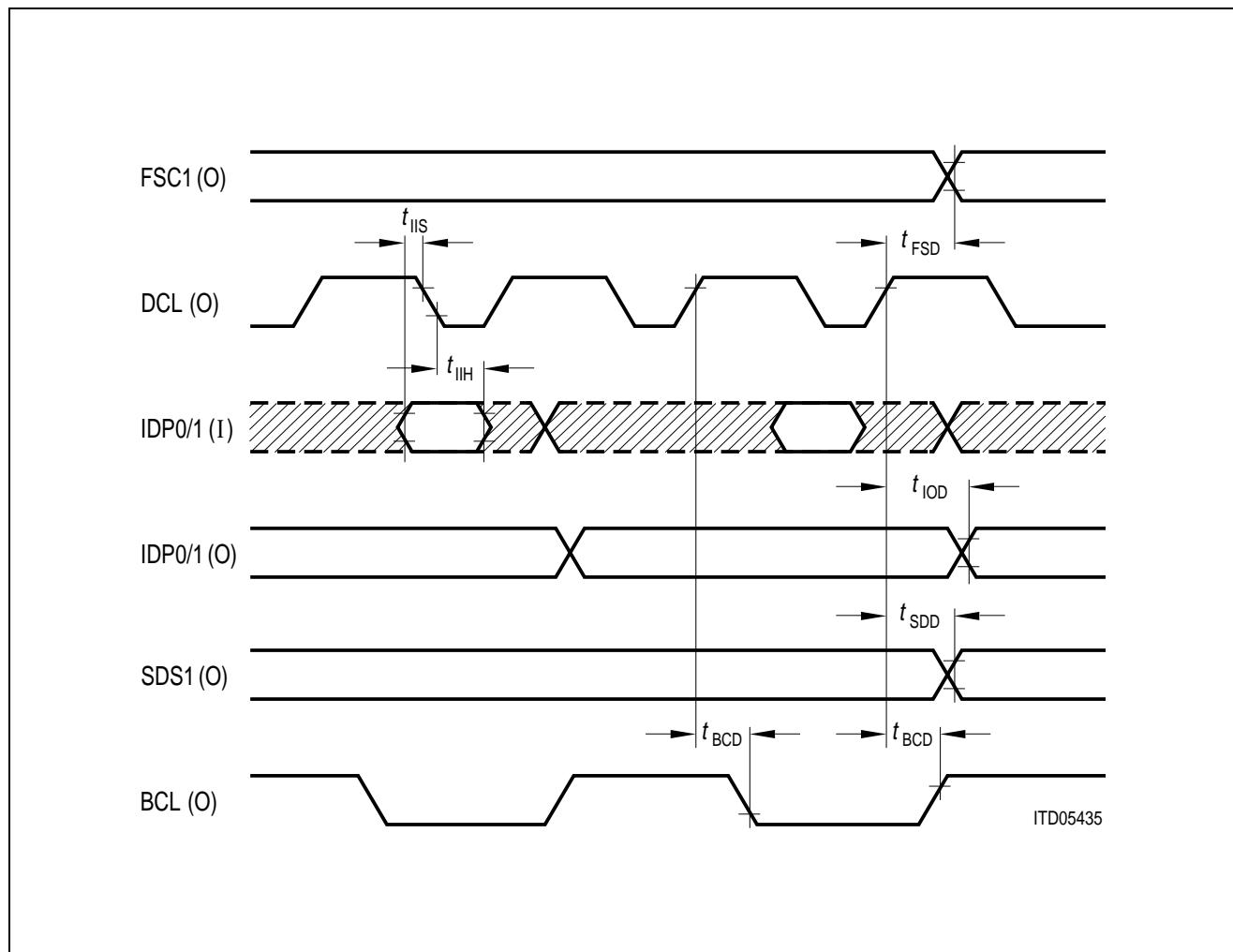

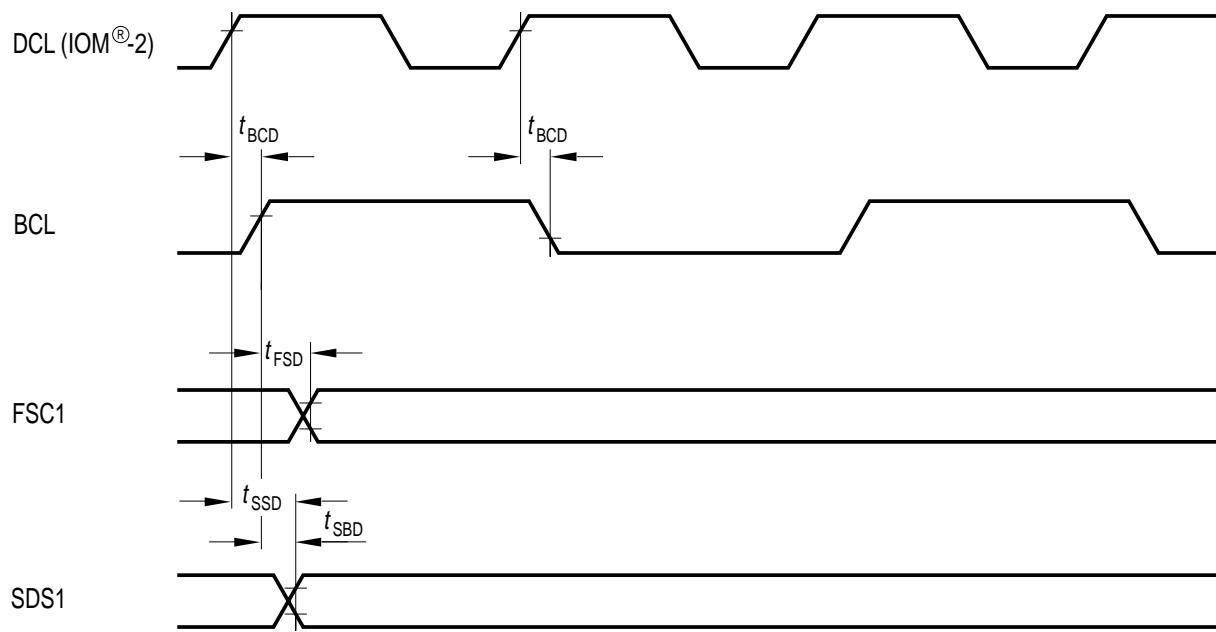

The IOM-2 signals are:

IDP0, 1 : 768 kbit/s

DCL : 1536-kHz output

FSC1 : 8-kHz output.

In addition, to support standard combos/data devices the following signals are generated as outputs:

BCL : 768-kHz bit clock

SDS1 : 8-kHz programmable data strobe signal for selecting one or both B/IC channel(s).

### **2.3.2 IOM®-2 Interface Connections**

#### **Output Driver Selection**

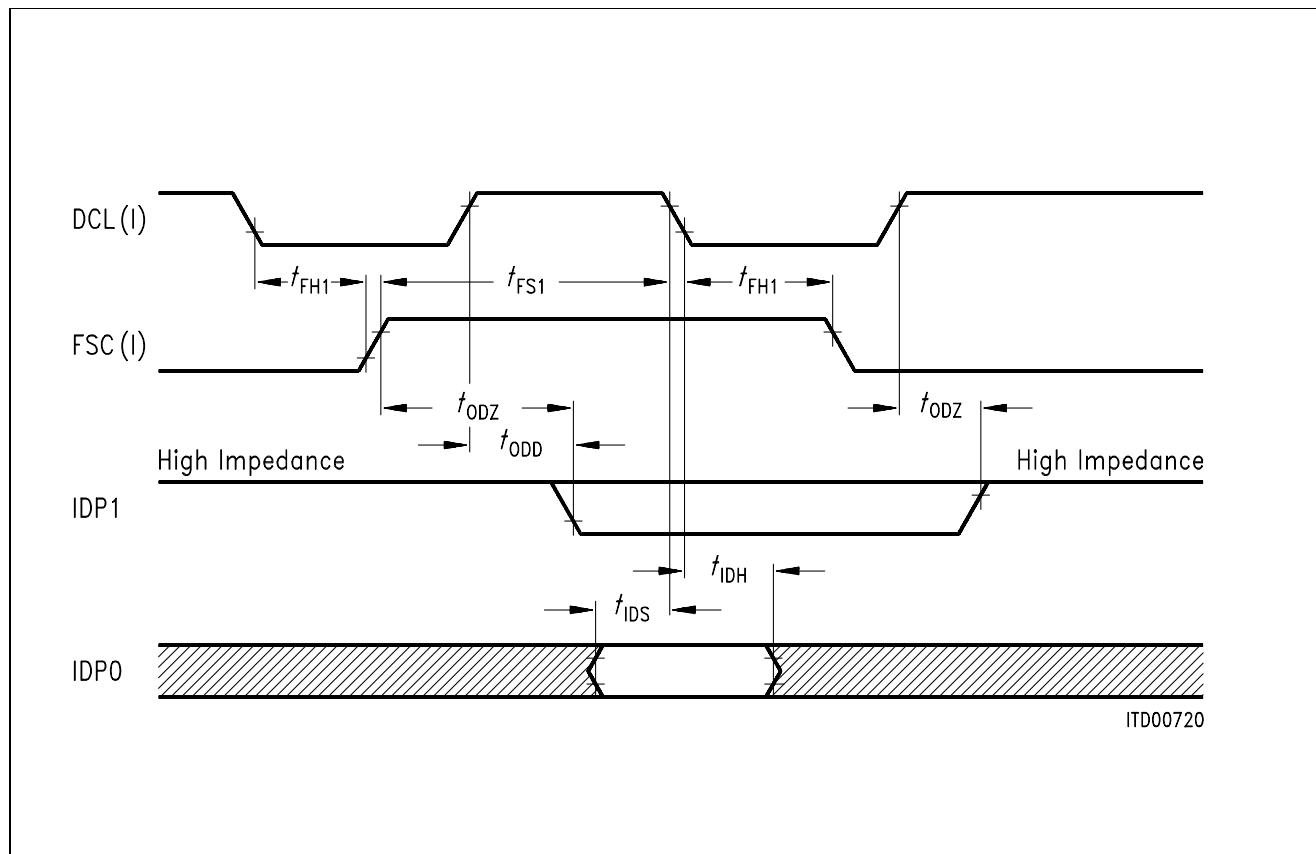

The type of the IOM output is selectable via bit ODS (ADF2 register). Thus when inactive (not transmitting) IDP0, 1 are either high impedance (ODS=1) or open drain "1" (ODS=0).

Normally the IOM-2 interface is operated in the "open drain" mode (ODS=0) in order to take advantage of the bus capability. In this case pull-up resistors (1 k $\Omega$  – 5 k $\Omega$ ) are required on IDP0 and IDP1.

#### **IOM® OFF Function**

In IOM-2 terminal mode (SPCR:SPM=0) the IOM interface can be switched off for external devices via IOF bit in ADF1 register. If IOF=1, the interface is switched off i.e. DCL, FSC1, IDP0/1 and BCL are high impedance.

#### **IOM® Direction Control**

For test applications, the direction of IDP0(DD) and IDP1(DU) can be reversed during certain time-slots within the IOM-2 frame. This is performed via the IDC bit in the SQXR register. For normal operation SQXR:IDC should be set to "0".

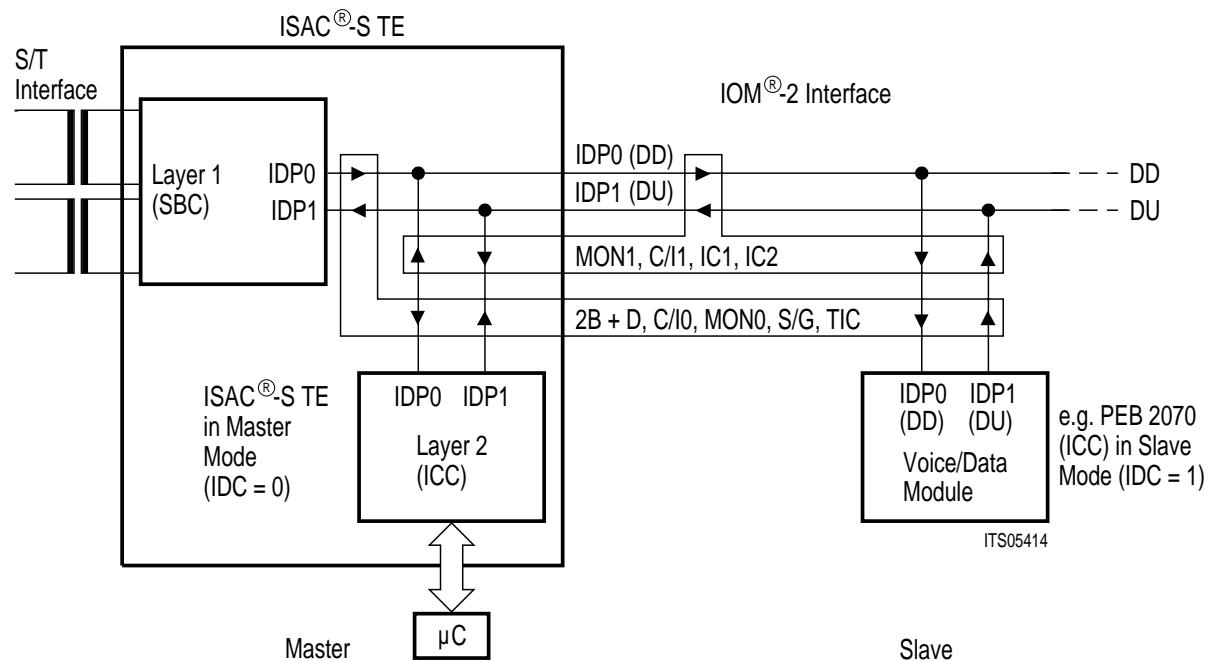

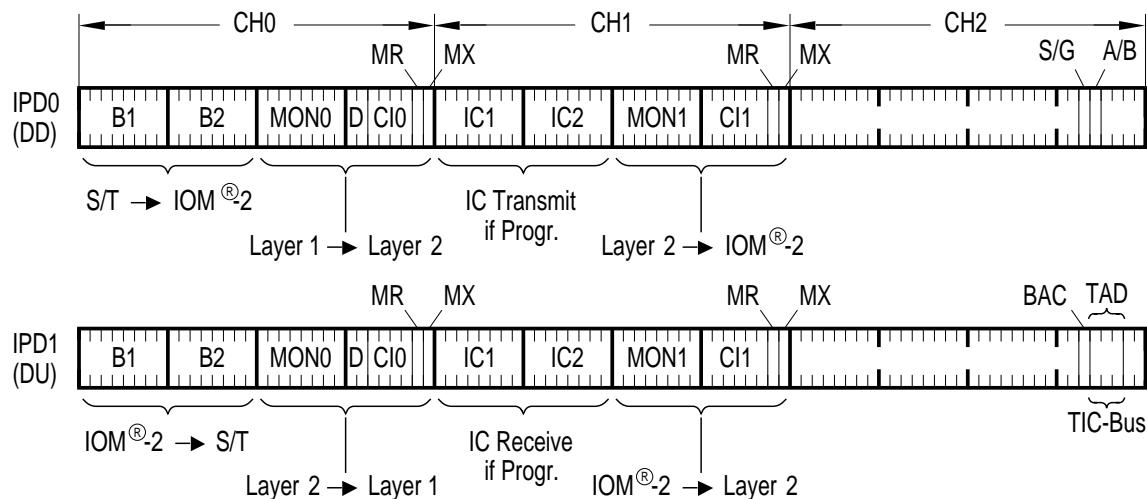

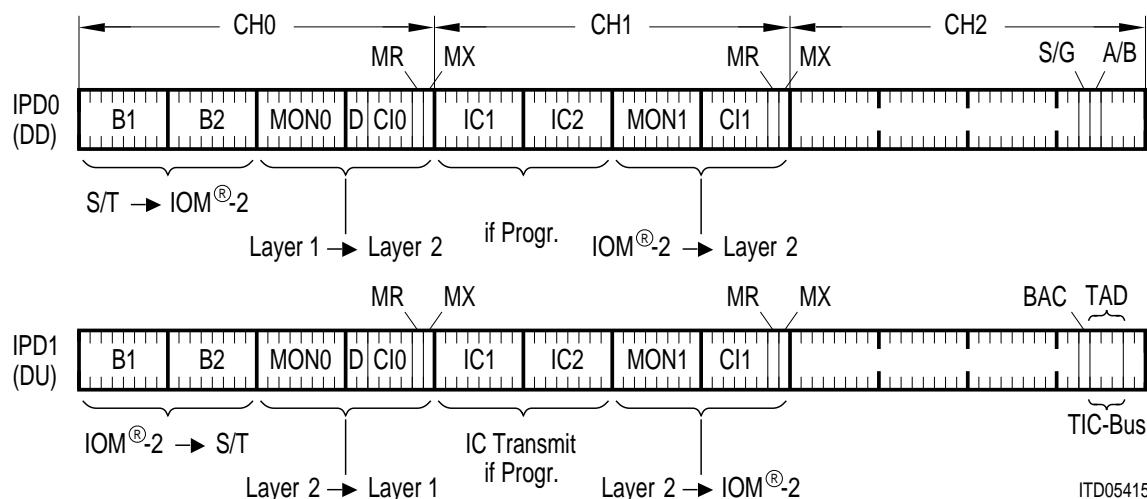

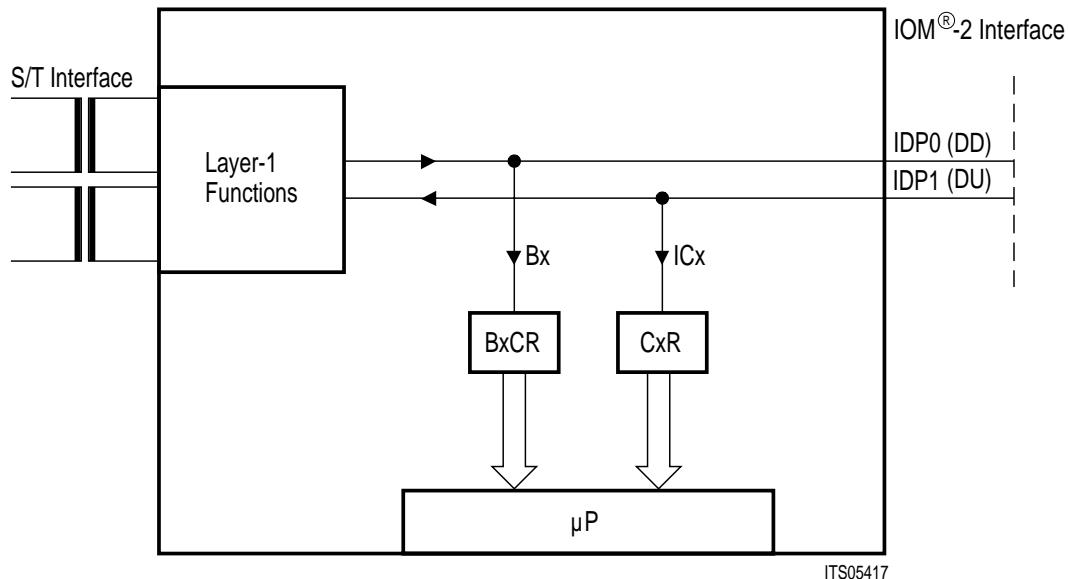

### IOM® Data Ports in Terminal Mode

In this case the IOM has the 12-byte frame structure consisting of channels 0, 1 and 2 (**see figure 11**):

- IDP0 carries the 2B+D channels from the S/T interface, and the MONITOR 0 and C/I 0 channels coming from the S/T controller;

- IDP1 carries the MONITOR 0 and C/I 0 channels to the layer-1.

Channel 1 of the IOM interface is used for internal communication in terminal applications. Two cases have to be distinguished, according to whether the ISAC-S TE is operated as a master device (communication with slave devices via MONITOR 1 and C/I 1), or as a slave device (communication with one master via MONITOR 1 and C/I 1).

If IDC is set to "0" (master mode):

- IDP0 carries the MONITOR 1 and C/I 1 channels as output to peripheral (voice/data) devices;

- IDP0 carries the IC channels as output to other devices, if programmed ( $C_{\times}C1 - 0 = 01$  in register SPCR).

If IDC is set to "1" (slave mode):

- IDP1 carries the MONITOR 1 and C/I 1 channels as output to a master device;

- IDP0 carries the IC channels as output to other devices, if programmed ( $C_{\times}C1 - 0 = 01$  in register SPCR).

If required (cf. DIM2-0, MODE register), bit 5 of the last byte in channel 2 on IDP0 is used to indicate the S-bus state (stop/go bit) and bits 2 to 5 of the last byte are used for TIC-bus access arbitration (**see chapter 2.3.6**).

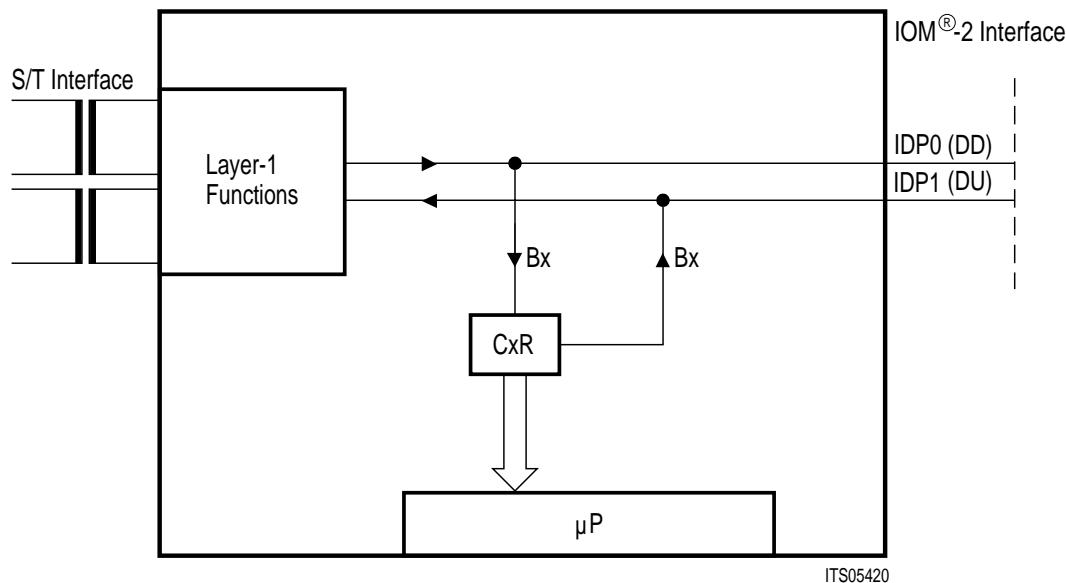

**Figure 12** shows the connection in a multifunctional terminal with the ISAC-S TE as a master (**figure 12b**) and an ICC as a slave device.

**Figure 12a**

**IOM® Data Ports 0, 1 in Terminal Mode (SPCR:SPM=0)**

**(a) Master Mode (IDC = 0)****(b) Slave Mode (IDC = 1)****Figure 12b**

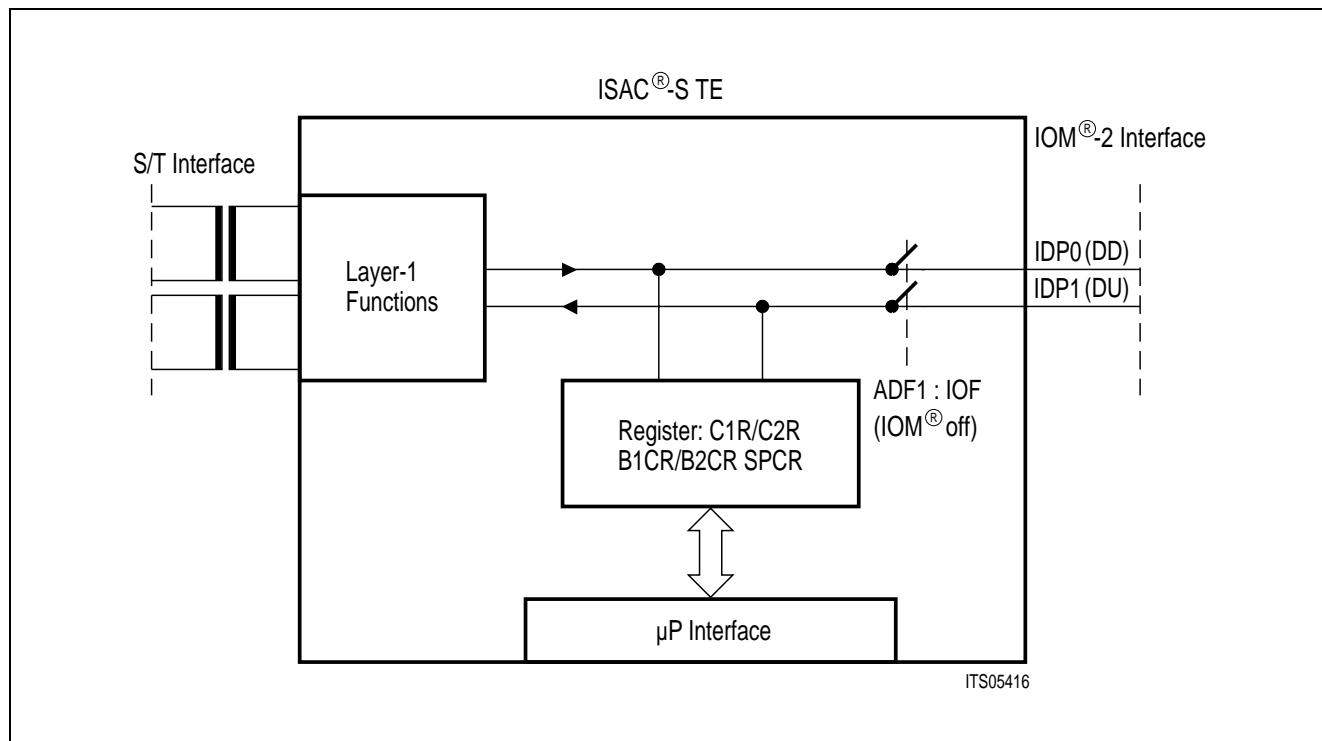

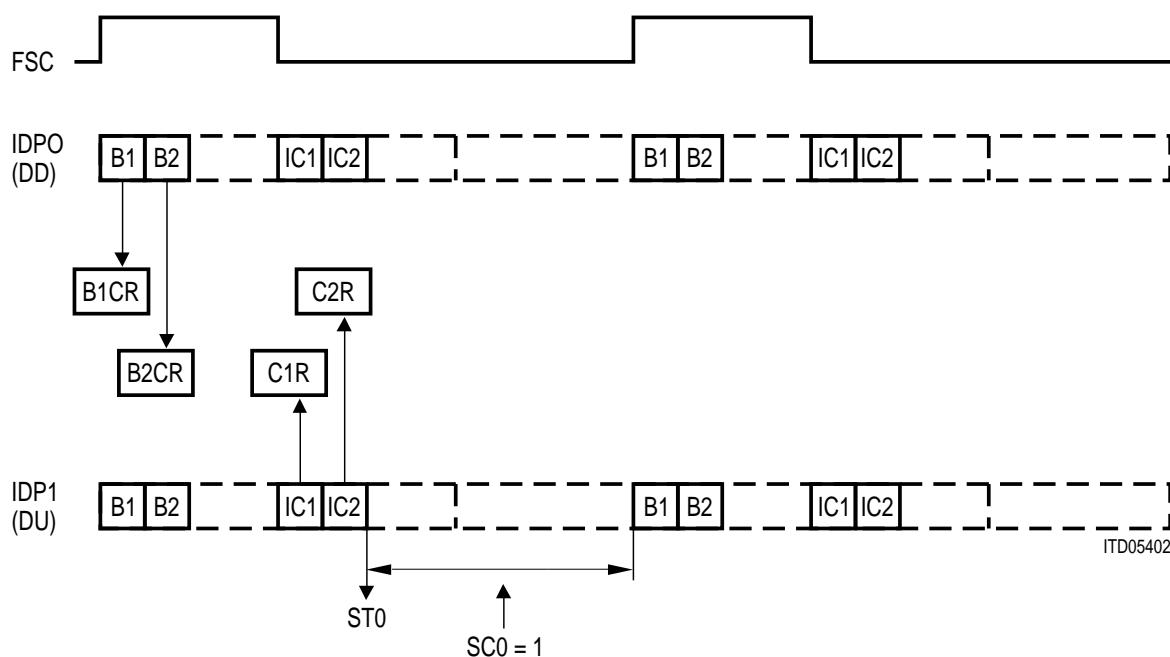

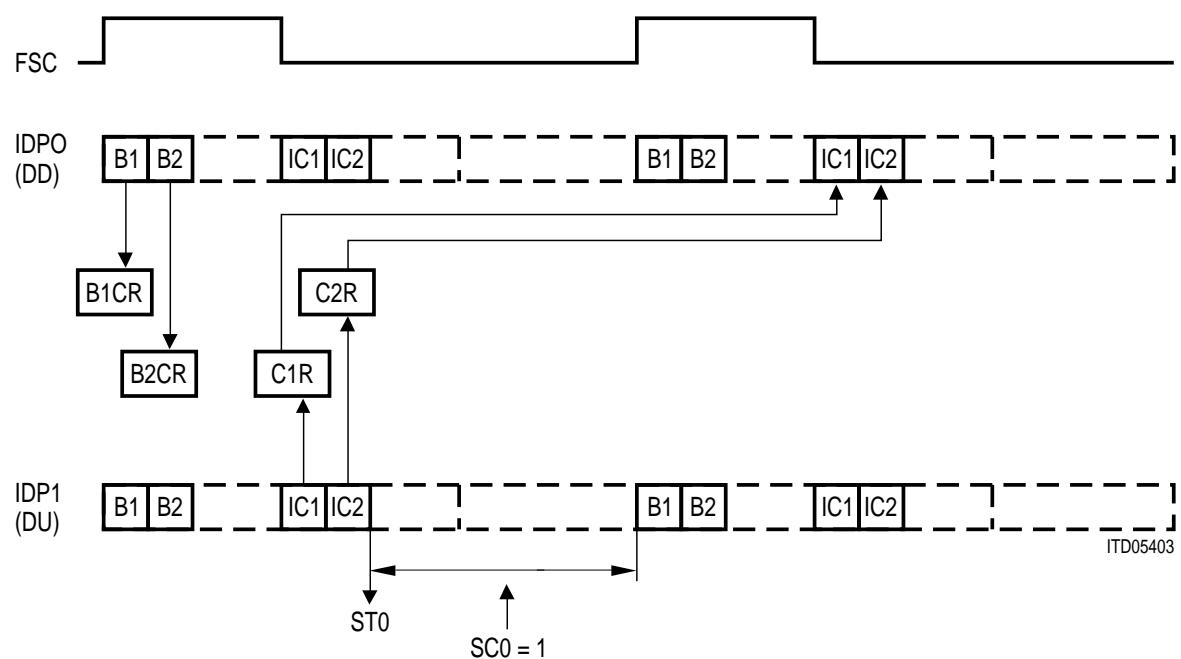

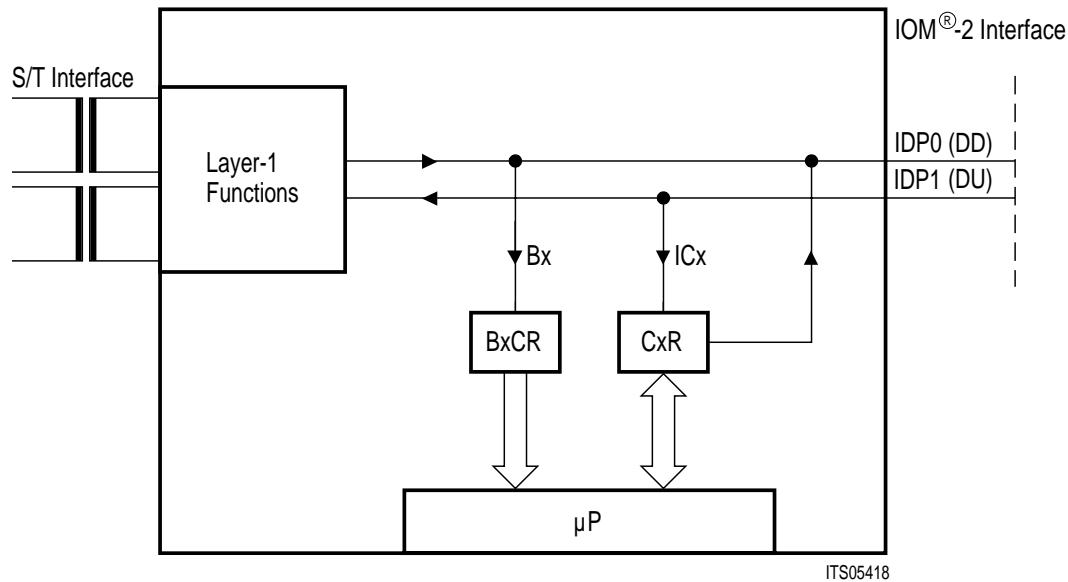

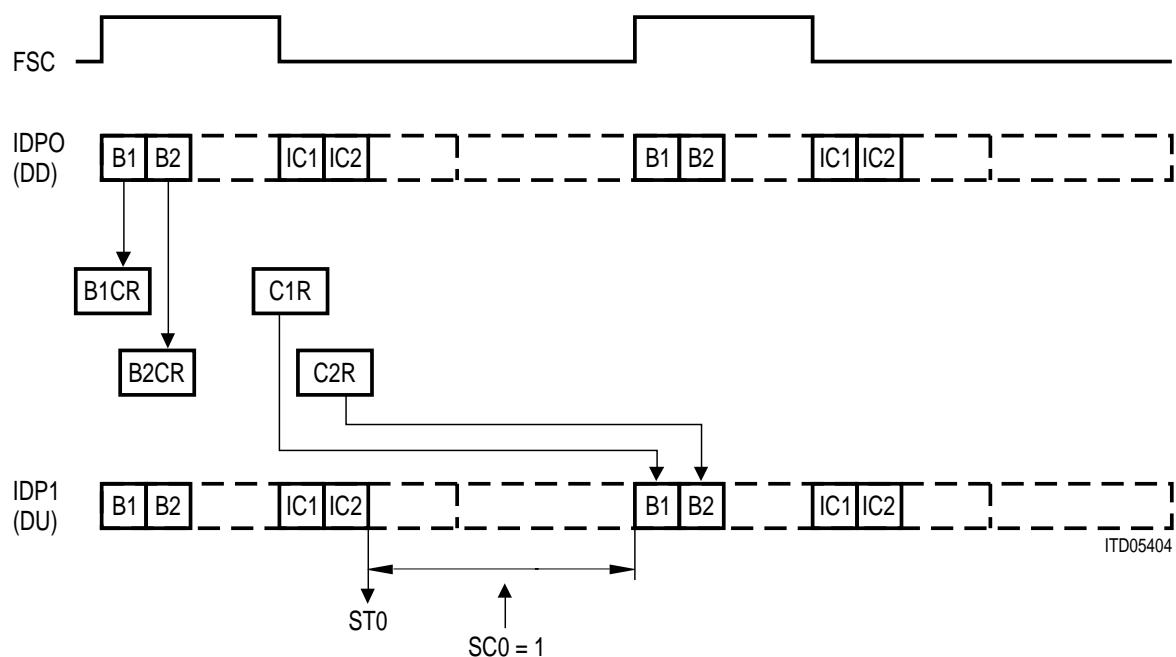

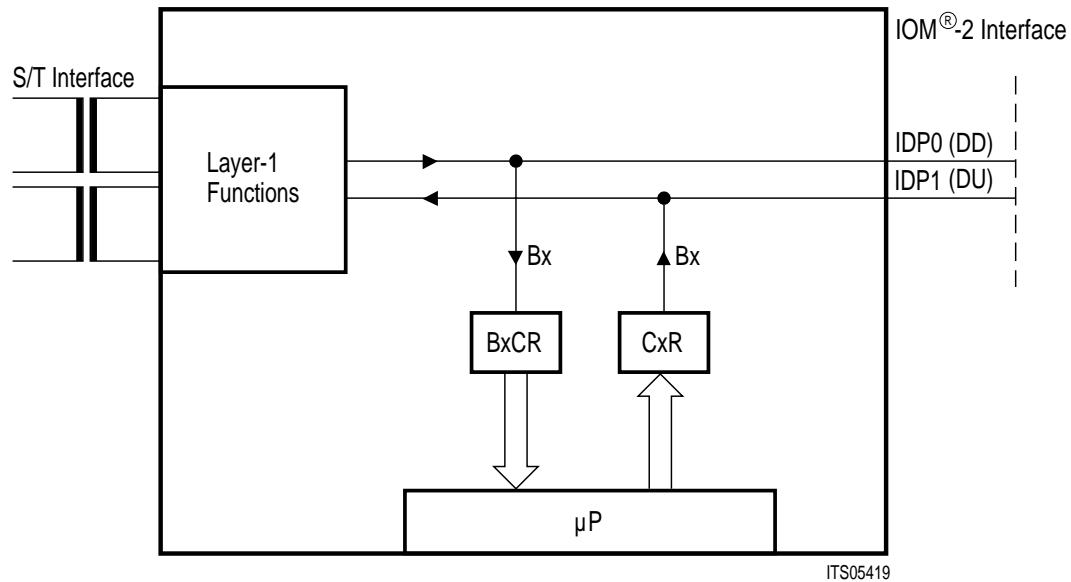

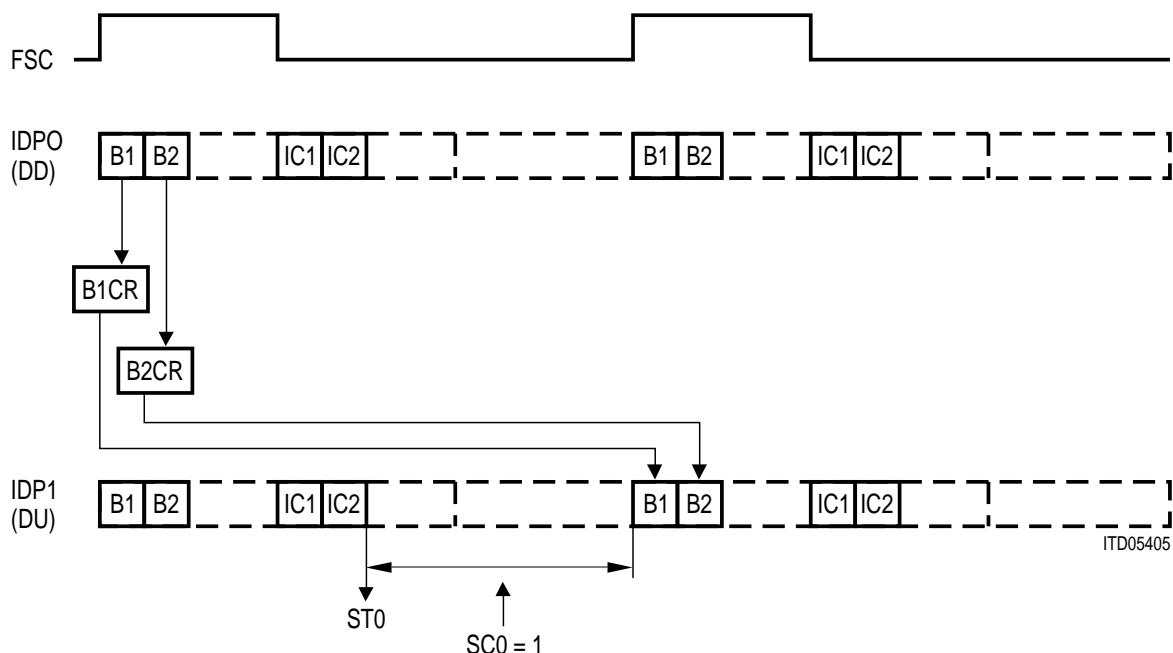

### 2.3.3 $\mu$ P Access to B and IC Channels

The microprocessor can access the B and IC (intercommunication) channels at the IOM-2 interface by reading the B1CR/B2CR or by reading and writing the C1R/C2R registers. Furthermore it is possible to loop back the B channels from/to the S/T interface or to loop back the IC channels from/to the IOM-2 interface without  $\mu$ P intervention.

These access and switching functions are selected with the channel connect bits (Cx<sub>C1</sub>, Cx<sub>C0</sub>) in the SPCR register (**table 2, figure 13**).

External B-channel sources (voice/data modules) connected to the IOM-2 interface can be disconnected with the IOM off function (ADF1:IOF) in order to not disturb the B-channel access (**see figure 13**).

If the B-channel access is used for transferring 64-kbit/s voice/data information directly from the  $\mu$ P port to the ISDN S/T interface, the access can be synchronized to the IOM interface by means of a synchronous transfer interrupt programmed in the STCR register.

**Table 2**

$\mu$ P Access to B/IC Channels (IOM®-2)

| Cx <sub>C1</sub> | Cx <sub>C0</sub> | C <sub>x</sub> R | C <sub>x</sub> R | B <sub>x</sub> CR | Output to IOM-2 | Applications                                                                                                                   |

|------------------|------------------|------------------|------------------|-------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|

|                  |                  | Read             | Write            | Read              |                 |                                                                                                                                |

| 0                | 0                | IC <sub>x</sub>  | —                | B <sub>x</sub>    | —               | B <sub>x</sub> monitoring, IC <sub>x</sub> monitoring                                                                          |

| 0                | 1                | IC <sub>x</sub>  | IC <sub>x</sub>  | B <sub>x</sub>    | IC <sub>x</sub> | B <sub>x</sub> monitoring, IC <sub>x</sub> looping from/to IOM-2                                                               |

| 1                | 0                | —                | B <sub>x</sub>   | B <sub>x</sub>    | B <sub>x</sub>  | B <sub>x</sub> access from/to S <sub>0</sub> ;<br>transmission of a constant value in B <sub>x</sub> channel to S <sub>0</sub> |

| 1                | 1                | B <sub>x</sub>   | B <sub>x</sub>   | —                 | B <sub>x</sub>  | B <sub>x</sub> looping from S <sub>0</sub> ;<br>transmission of a variable pattern in B <sub>x</sub> channel to S <sub>0</sub> |

**Note:** x=1 for channel 1 or 2 for channel 2

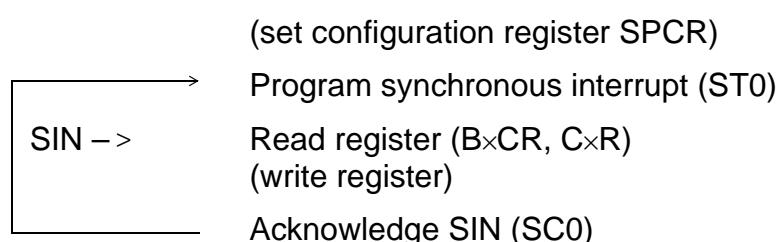

The general sequence of operations to access the B/IC channels is:

**Figure 13**

**Principle of B/IC-Channel Access**

**Figure 14**

**Access to B and IC Channels in IOM®-2 Terminal Mode**

**(a) SPCR:C<sub>x</sub>C1, C<sub>x</sub>C0 = 00**

**B<sub>x</sub> monitoring, IC<sub>x</sub> monitoring (SQXR:IDC=0)**

**(b) SPCR:C<sub>x</sub>C1, C<sub>x</sub>C0 = 01**

**B<sub>x</sub> monitoring, IC<sub>x</sub> looping (SQXR:IDC=0)**

**(c) SPCR:CxC1, CxC0 = 10**

**Bx access from/to S/T**

**transmission of constant value to S/T**

**(d) SPCR:C<sub>x</sub>C1, C<sub>x</sub>C0 = 11**

**B<sub>x</sub> looping from/to S/T**

**transmission of variable pattern to S/T**

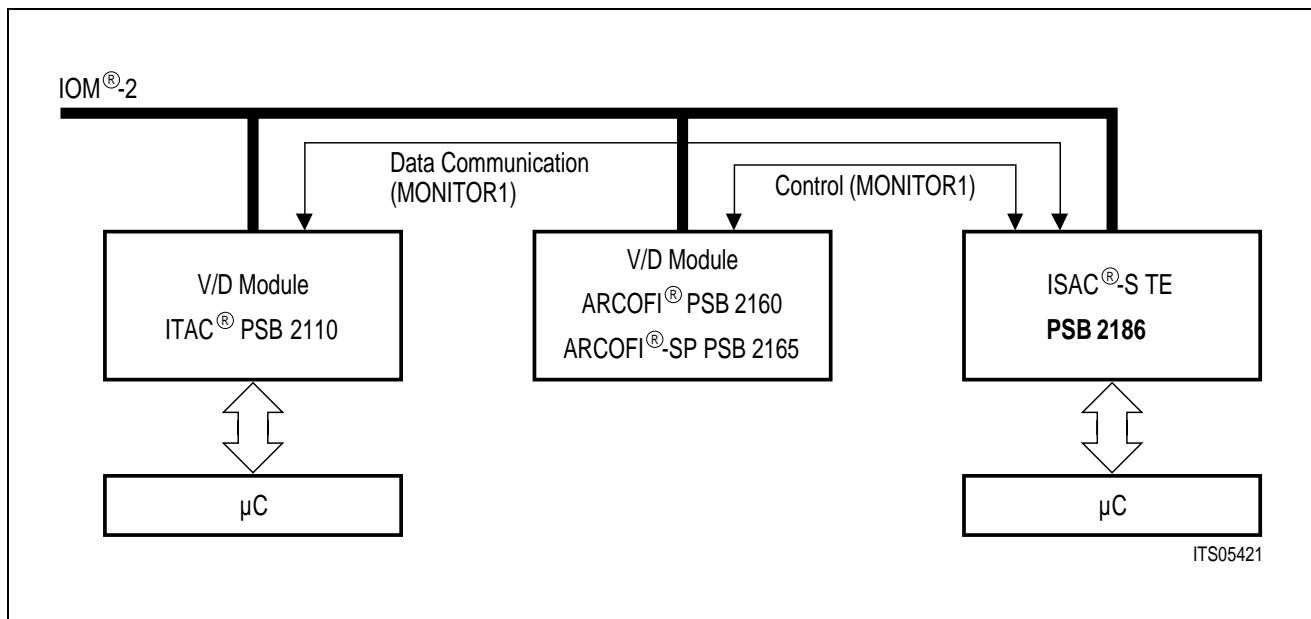

### 2.3.4 MONITOR Channel Handling

In IOM-2 mode, the MONITOR channel protocol is a handshake protocol used for high speed information exchange between the ISAC-S TE and other devices, in MONITOR channel "0" or "1" (**see figure 11**). In the non-TE mode, only one MONITOR channel is available ("MONITOR channel 0").

The MONITOR channel protocol is necessary:

- For programming and controlling devices attached to the IOM. Examples of such devices are: layer-1 transceivers (using MONITOR channel 0), and peripheral V/D modules that do not need a parallel microcontroller interface (MONITOR channel 1), such as the Audio Ringing Codec Filter PSB 2165.

- For data exchange between two microcontroller systems attached to two different devices on one IOM-2 backplane. Use of the MONITOR channel avoids the necessity of a dedicated serial communication path between the two systems. This greatly simplifies the system design of terminal equipment (**figure 17**).

**Note:** There is normally no necessity for monitor channel operations over "MONITOR channel 0" since the internal layer-1 part of the ISAC-S TE does not support this function. The implemented MONITOR handler can however be used with external layer-1 transceivers in case only the ICC part of the ISAC-S TE is used (ADF1:TEM).

**Figure 15**

**Examples of MONITOR Channel Applications in IOM®-2 TE Mode**

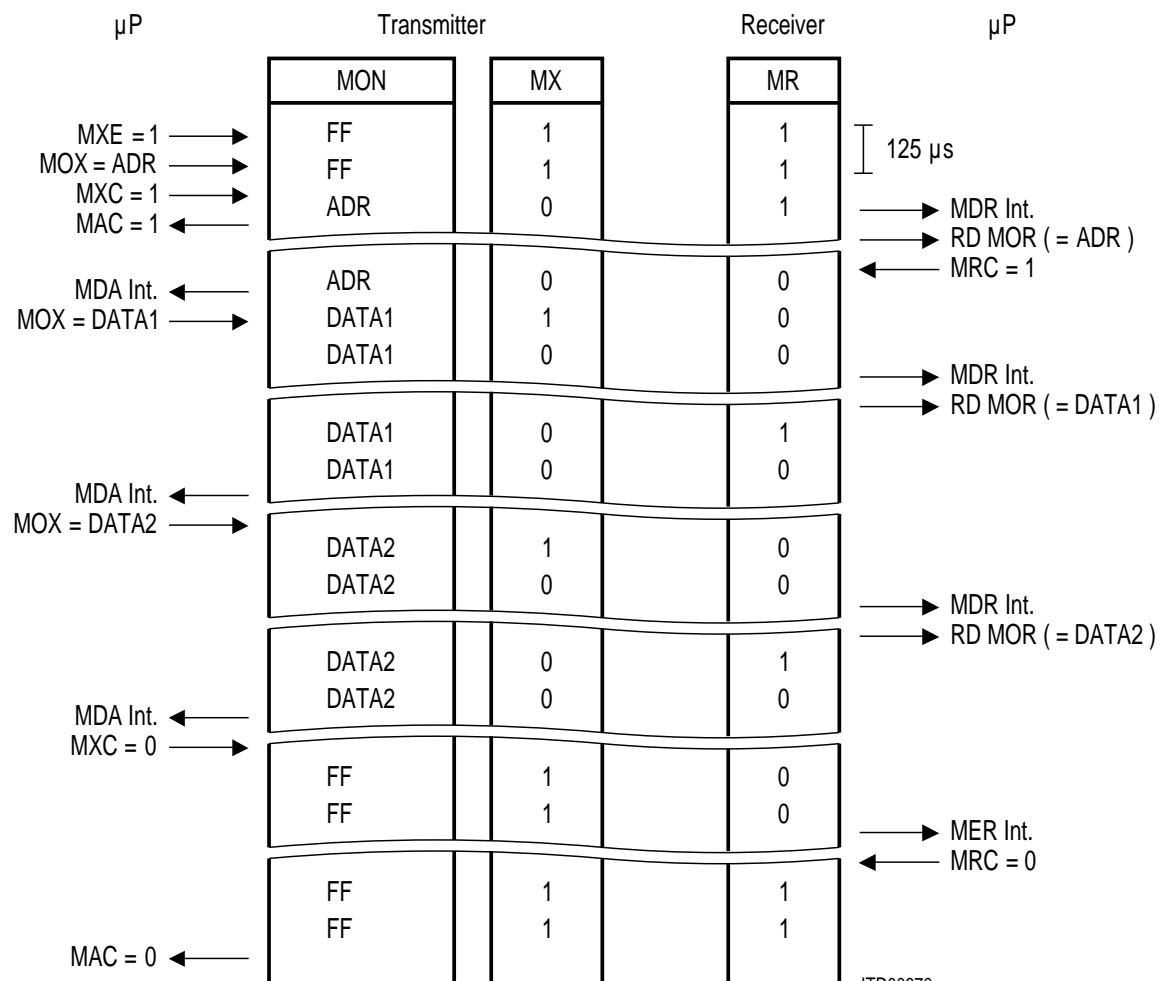

The MONITOR channel operates on an asynchronous basis. While data transfers on the bus take place synchronized to frame sync, the flow of data is controlled by a handshake procedure using the MONITOR Channel Receive (MR0 or 1) and MONITOR Channel Transmit (MX0 or 1) bits. For example: data is placed onto the MONITOR channel and the MX bit is activated. This data will be transmitted repeatedly once per 8-kHz frame until the transfer is acknowledged via the MR bit.

The microprocessor may either enforce a "1" (idle) in MR, MX by setting the control bit MRC1, 0 or MXC1, 0 to "0" (MONITOR Control Register MOCR), or enable the control of these bits internally by the ISAC-S TE according to the MONITOR channel protocol. Thus, before a data exchange can begin, the control bit MRC(1, 0) or MXC(1, 0) should be set to "1" by the microprocessor.

The MONITOR channel protocol is illustrated in **figure 16**. Since the protocol is identical in MONITOR channel 0 and MONITOR channel 1 (available in TE mode only), the index 0 or 1 has been left out in the illustration.

The relevant status bits are:

- MONITOR Channel Data Received MDR (MDR0, MDR1)

- MONITOR Channel End of Reception MER (MER0, MER1)

for the **reception** of MONITOR data, and

- MONITOR Channel Data Acknowledged MDA (MDA0, MDA1)

- MONITOR Channel Data Abort MAB (MAB0, MAB1)

for the **transmission** of MONITOR data (register: MOSR)

In addition, the status bit:

MONITOR Channel Active MAC (MAC0, MAC1)

indicates whether a transmission is in progress (register: STAR).

**Figure 16**

MONITOR Channel Protocol (IOM®-2)

---

Before starting a transmission, the microprocessor should verify that the transmitter is inactive, i.e. that a possible previous transmission has been terminated. This is indicated by a "0" in the MONITOR Channel Active MAC status bit.

After having written the MONITOR Data Transmit (MOX) register, the microprocessor sets the MONITOR Transmit Control bit MXC to "1". This enables the MX bit to go active (0), indicating the presence of valid MONITOR data (contents of MOX) in the corresponding frame. As a result, the receiving device stores the MONITOR byte in its MONITOR Receive MOR register and generates an MDR interrupt status.

Alerted by the MDR interrupt, the microprocessor reads the MONITOR Receive (MOR) register. When it is ready to accept data (e.g. based on the value in MOR, which in a point-to-multipoint application might be the address of the destination device), it sets the MR control bit MRC to "1" to enable the receiver to store succeeding MONITOR channel bytes and acknowledge them according to the MONITOR channel protocol. In addition, it enables other MONITOR channel interrupts by setting MONITOR Interrupt Enable to "1".

As a result, the first MONITOR byte is acknowledged by the receiving device setting the MR bit to "0". This causes a MONITOR Data Acknowledge MDA-interrupt status at the transmitter.

A new MONITOR data byte can now be written by the microprocessor in MOX. The MX bit is still in the active (0) state. The transmitter indicates a new byte in the MONITOR channel by returning the MX bit active after sending it once in the inactive state. As a result, the receiver stores the MONITOR byte in MOR and generates a new MDR-interrupt status. When the microprocessor has read the MOR register, the receiver acknowledges the data by returning the MR bit active after sending it once in the inactive state. This in turn causes the transmitter to generate an MDA-interrupt status.

This "MDA interrupt – write data – MDR interrupt – read data – MDA interrupt" handshake is repeated as long as the transmitter has data to send. Note that the MONITOR channel protocol imposes no maximum reaction times to the microprocessor.

When the last byte has been acknowledged by the receiver (MDA-interrupt status), the microprocessor sets the MONITOR Transmit Control bit MXC to "0". This enforces an inactive ("1") state in the MX bit. Two frames of MX inactive signifies the end of a message. Thus, a MONITOR Channel End of Reception MER-interrupt status is generated by the receiver when the MX bit is received in the inactive state in two consecutive frames. As a result, the microprocessor sets the MR control bit MRC to 0, which in turn enforces an inactive state in the MR bit. This marks the end of the transmission, making the MONITOR Channel Active MAC bit return to "0".

During a transmission process, it is possible for the receiver to ask a transmission to be aborted by sending an inactive MR bit value in two consecutive frames. This is effected by the microprocessor writing the MR control bit MRC to "0". An aborted transmission is indicated by a MONITOR Channel Data Abort MAB-interrupt status at the transmitter.

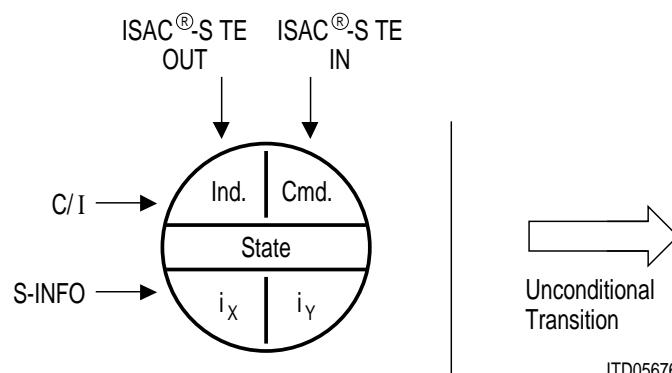

### 2.3.5 C/I-Channel Handling

The command/indication channel carries real-time status information between the ISAC-S TE and another device connected to the IOM.

- 1) One C/I channel (called C/I0) conveys the commands and indications between the layer-1 and the layer-2 parts of the ISAC-S TE. It can be accessed by an external layer-2 device e.g. to control the layer-1 activation/deactivation procedures. C/I0 channel access may be arbitrated via the TIC bus access protocol. In this case the arbitration is done in C/I channel 2 (**see figure 11**).

The C/I0 channel is accessed via register CIR0 (in receive direction, layer-1 to layer-2) and register CIX0 (in transmit direction, layer-2 to layer-1). The C/I0 code is four bits long.

A listing and explanation of the layer-1 C/I codes can be found in **chapter 3.4**.

In the receive direction, the code from layer-1 is continuously monitored, with an interrupt being generated anytime a change occurs (ISTA:CISQ). A new code must be found in two consecutive IOM frames to be considered valid and to trigger a C/I code change interrupt status (double last look criterion).

In the transmit direction, the code written in CIX0 is continuously transmitted in C/I0.

- 2) A second C/I channel (called C/I1) can be used to convey real time status information between the ISAC-S TE and various non-layer-1 peripheral devices e.g. PSB 2160 ARCOFI. The channel consists of six bits in each direction (**see figure 11**).

The C/I1 channel is accessed via registers CIR1 and CIX1. A change in the received C/I1 code is indicated by an interrupt status without double last look criterion.

**Figure 17**

**Applications of TIC Bus in IOM®-2 Bus Configuration**

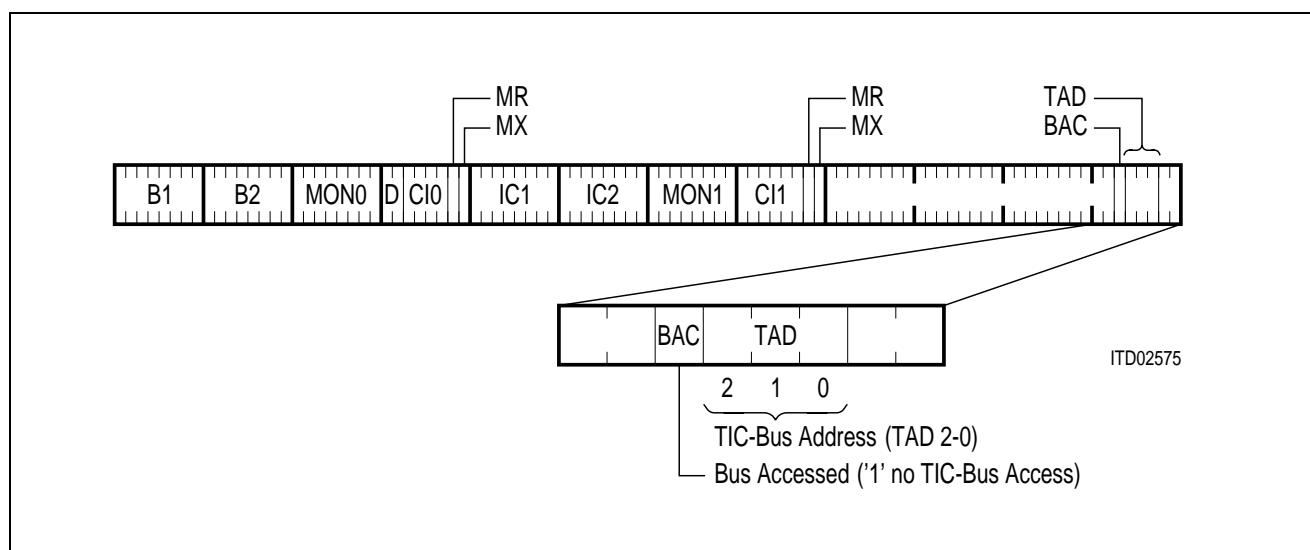

### 2.3.6 TIC-Bus Access

In IOM-2 interface mode the TIC-bus capability is only available in TE mode. The arbitration mechanism implemented in the last octet of IOM channel 2 of the IOM allows the access of external communication controllers (up to 7) to the layer-1 functions provided in the ISAC-S TE and to the D channel. (TIC bus; **see figure 17**). To this effect the outputs of the controllers (ICC:ISDN Communication Controller PEB 2070) are wired-or-and connected to pin IDP1. The inputs of the ICCs are connected to pin IDP0. External pull-up resistors on IDP0/1 are required. The arbitration mechanism must be activated by setting MODE:DIM2-0=001 (**see chapter 4.1.7**).

An access request to the TIC bus may either be generated by software ( $\mu$ P access to the C/I

channel) or by the ISAC-S TE itself (transmission of an HDLC frame). A software access request to the bus is effected by setting the BAC bit (CIX0 register) to "1".

In the case of an access request, the ISAC-S TE checks the Bus Accessed-bit (bit 5 of IDP1 last octet of CH2, **see figure 18**) for the status "bus free", which is indicated by a logical "1". If the bus is free, the ISAC-S TE transmits its individual TIC-bus address programmed in the STCR register. The TIC bus is occupied by the device which sends its address error-free. If more than one device attempt to seize the bus simultaneously, the one with the lowest address values wins.

**Figure 18**

**Structure of Last Octet of CH2 on IDP1 (DU)**

When the TIC bus is seized by the ISAC-S TE, the bus is identified to other devices as occupied via the IDP1 C/I Bus Accessed-bit state "0" until the access request is withdrawn. After a successful bus access, the ISAC-S TE is automatically set into a lower priority class, that is, a new bus access cannot be performed until the status "bus free" is indicated in two successive frames.

If none of the devices connected to the IOM interface request access to the D- and C/I channels, the TIC-bus address 7 will be present. The device with this address will therefore have access, by default, to the D and C/I channels.

**Note:** Bit BAC (CIX0 register) should be reset by the  $\mu$ P when access to the C/I channels is no more requested, to grant other devices access to the D- and C/I channels.

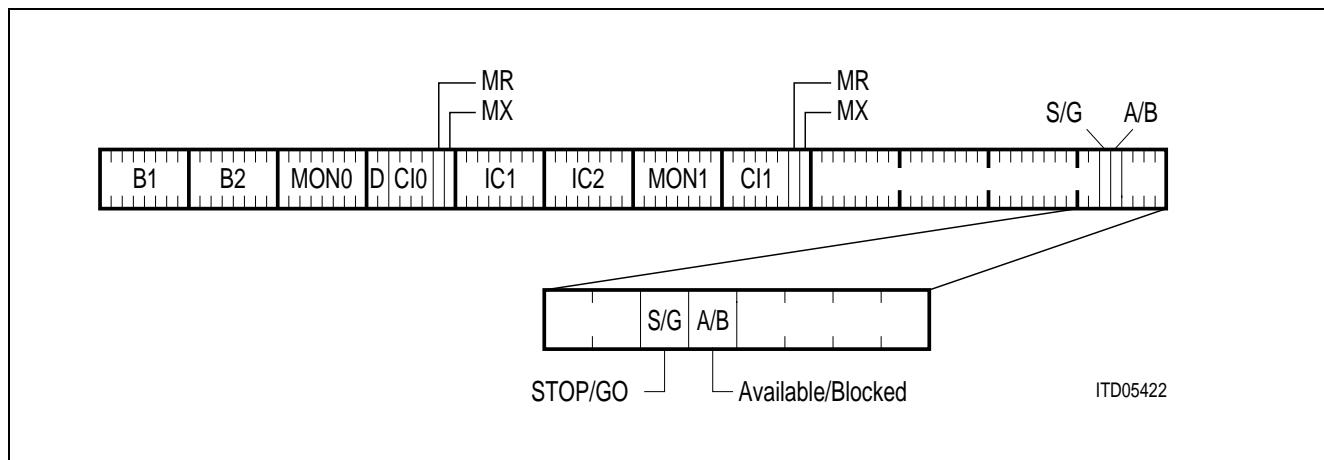

The availability of the S/T interface D channel is indicated in bit 5 "Stop/Go" (S/G) of the IDP0 last octet of C/I channel (**figure 19**).

S/G = 1 : stop

S/G = 0 : go

**Figure 19**

**Structure of Last Octet of CH2 on IDP0 (DD)**

The stop/go bit is available to other layer-2 devices connected to the IOM to determine if they can access the S/T bus D channel.

The available busy bit is not influenced by the ISAC-S TE.

## 2.4 Layer-1 Functions for the S/T Interface

- line transceiver functions for the S/T interface according to the electrical specifications of CCITT I.430;

- conversion of the frame structure between IOM and S/T interface;

- conversion from/to binary to/from pseudo-ternary code;

- level detect;

- S/T-timing generation using IOM timing synchronous to system, or vice versa;

- D-channel access control and priority handling;

- activation/deactivation procedures, triggered by primitives received over the IOM C/I channel or by INFO's received from the line;

- frame alignment;

- execution of test loops.

For a block diagram, **see figure 8**.

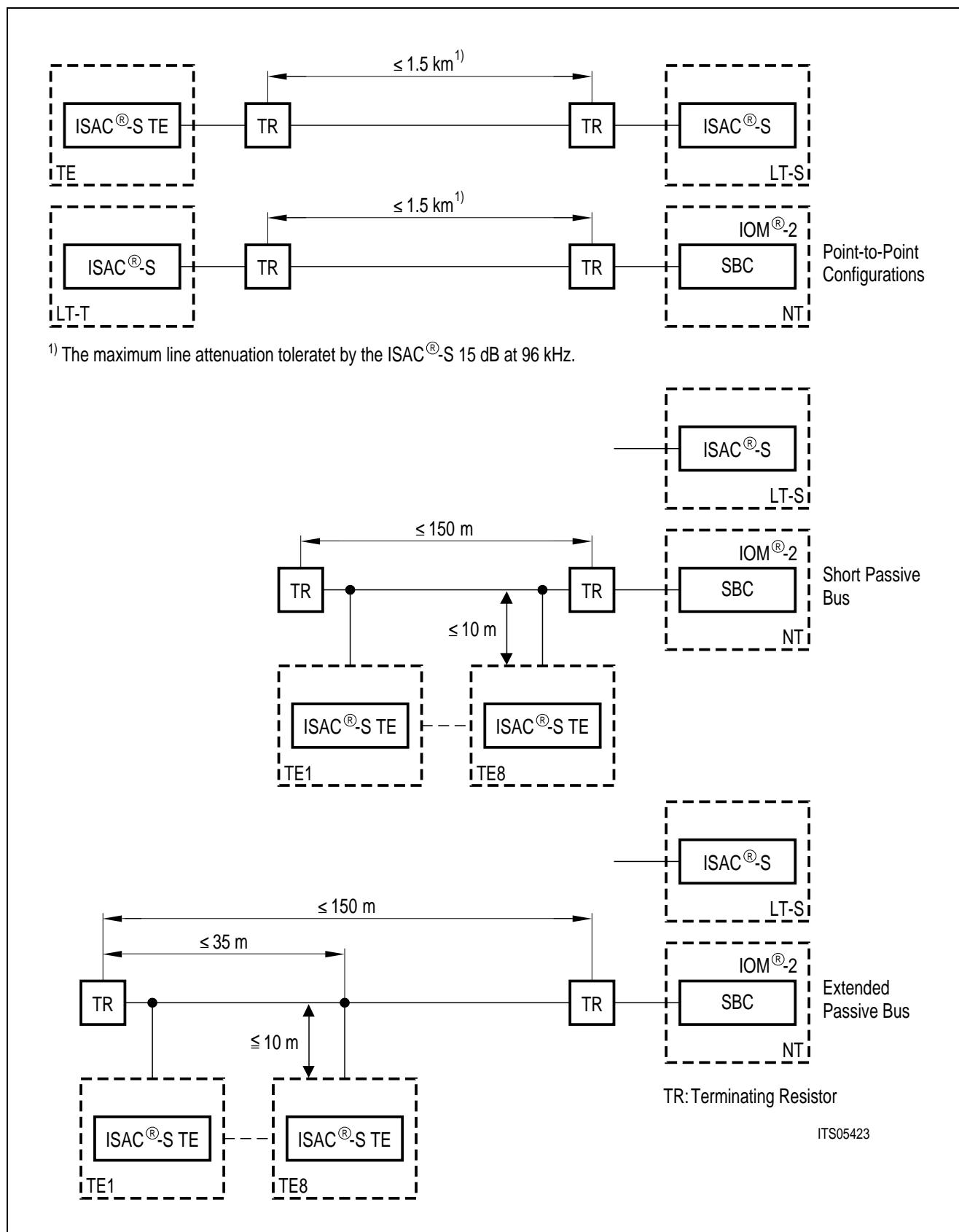

The wiring configurations in user premises, in which the ISAC-S TE can be used are illustrated in **figure 20**.

**Figure 20**

Wiring Configurations in User Premises

## 2.4.1 S/T Interface

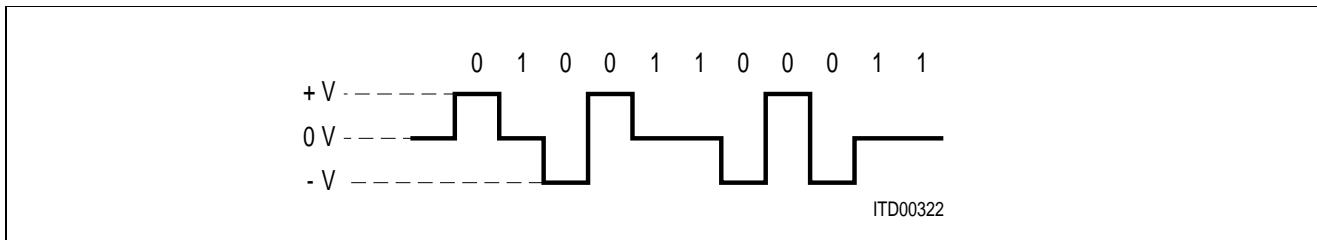

According to CCITT recommendation I.430 pseudo-ternary encoding with 100% pulse width is used on the S/T interface. A logical "1" corresponds to a neutral level (no current), whereas logical "0" 's are encoded as alternating positive and negative pulses. An example is shown in **figure 21**.

**Figure 21**

**S/T-Interface Line Code**

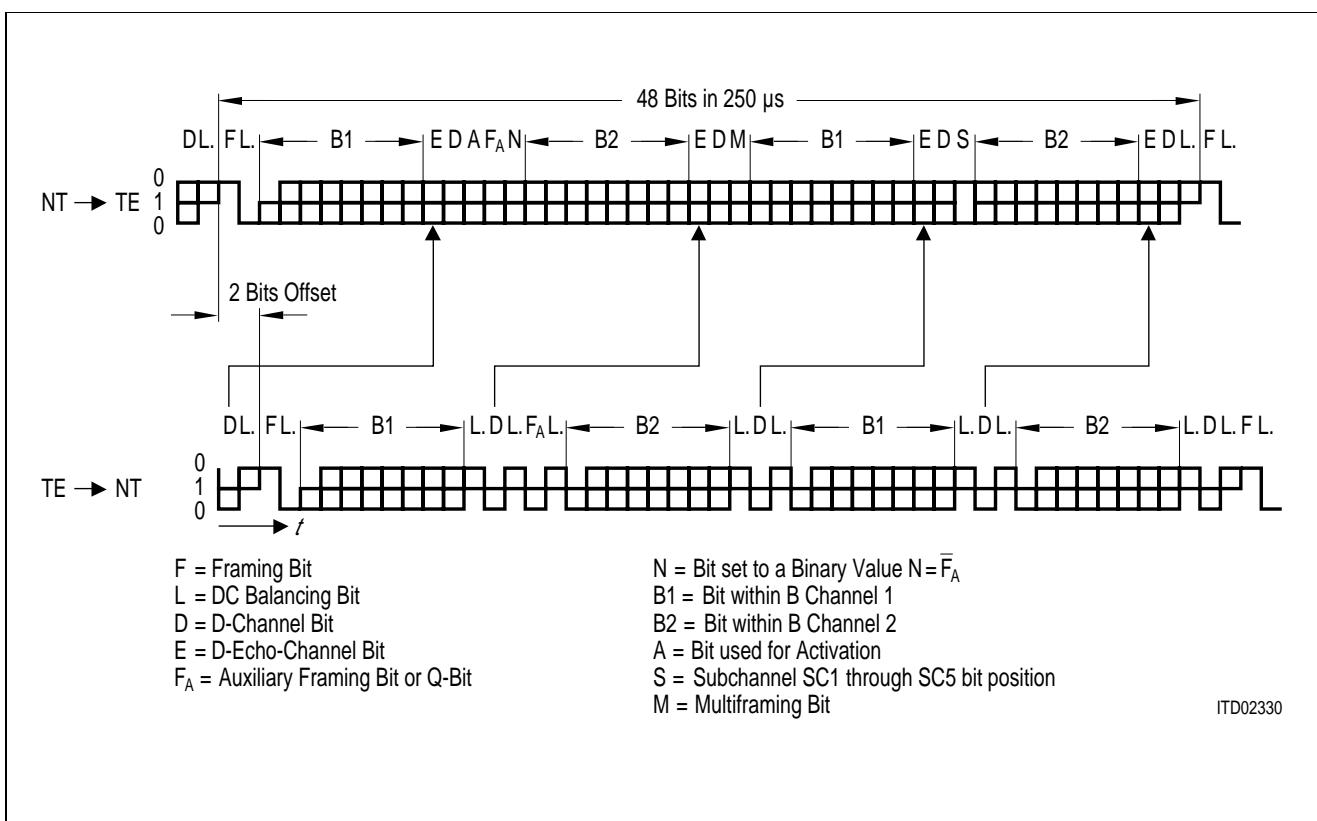

One frame consists of 48 bits, at a nominal bit rate of 192 kbit/s. Thus each frame carries two octets of B1, two octets of B2, and four D bits, according to the B1+B2+D structure defined for the ISDN-basic access (total useful data rate: 144 kbit/s). Frame begin is marked using a code violation (no mark inversion). The frame structures (from network to subscriber, and subscriber to network) are shown in **figure 22**.

**Figure 22**

**Frame Structure at Reference Points S and T (CCITT I.430)**

**Note:** Dots demarcate those parts of the frame that are independently DC-balanced.

## 2.4.2 Analog Functions

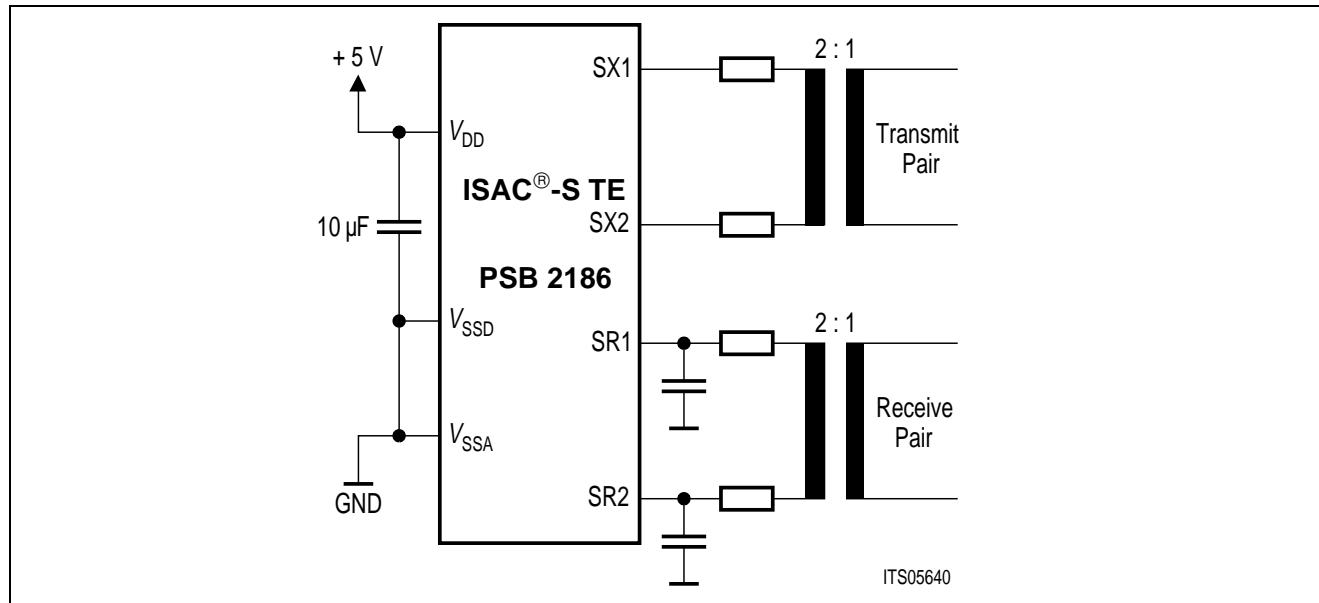

For both receive and transmit direction, a 2:1 transformer is used to connect the ISAC-S TE transceiver to the 4 wire S/T interface. The corrections are shown in **figure 23**.

**Figure 23**

**ISAC-S TE External S-Interface Circuitry**

The full-bauded pseudo-ternary pulse shaping is achieved with the integrated transmitter which is realized as a current limited voltage source. A voltage of 2.1 V is delivered between SX1-SX2, which yields a current of 7.5 mA over  $280 \Omega$ .

The receiver is designed as a threshold detector with adaptively switched threshold levels. Pin SR1 delivers 2.5 V as an output, which is the virtual ground of the input signal on pin SR2.

The external transformer of ratio 2:1 is needed in both receive and transmit direction to provide for isolation and transform voltage levels according to CCITT recommendations.

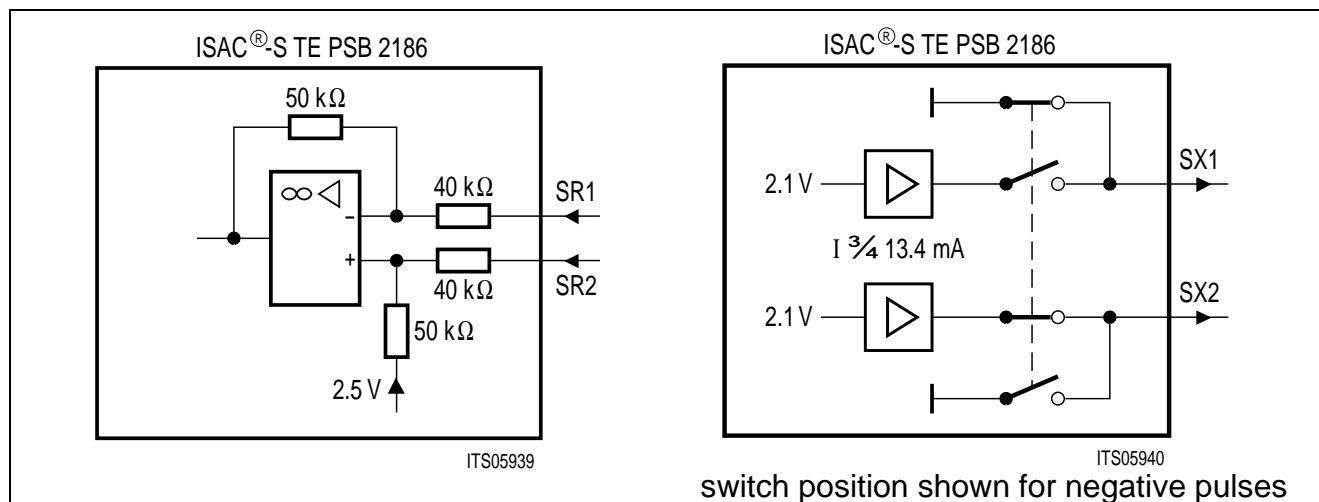

The equivalent circuits of the integrated receiver and transmitter are shown in **figure 24**.

**Figure 24**

**Equivalent Internal Circuits of Receiver and Transmitter Stages**

## Symmetrical S-Bus Receiver

The S-bus receiver of the PSB 2186 is a symmetrical one. This results in a simplification of the external circuitry and PCB layout to meet the I.430 receiver input impedance specification.

### 2.4.3 S/T-Interface Circuitry

In order to comply to the physical requirements of CCITT recommendation I.430 and considering the national requirements concerning overvoltage protection and electromagnetic compatibility (EMC), the ISAC-S TE needs some additional circuitry.

Useful hints how to design such interface circuitry are contained on the Application Note "S/T-interface circuitry using the PEB 2080 SBC or PEB 2085 ISAC-S (12/89)".

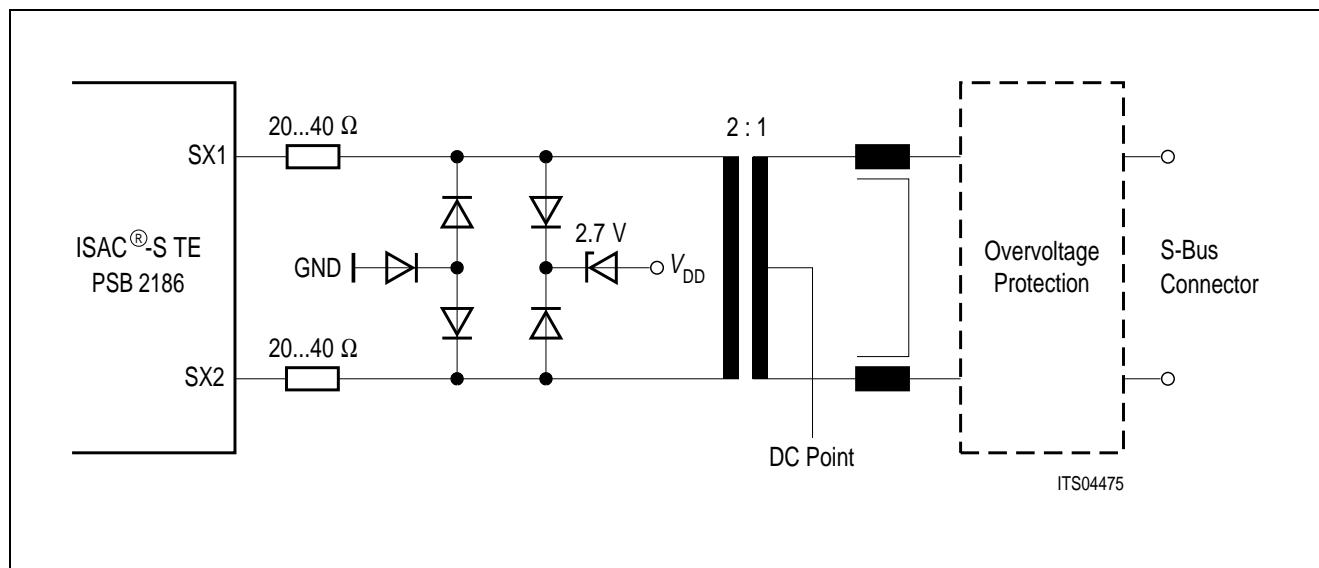

The transmitter of the PSB 2186 ISAC-S TE is identical to that of both the PEB 2080 SBC and PEB 2085/ISAC-S, hence, the line interface circuitry should be the same (**figure 25**). The external resistors (20 ... 40  $\Omega$ ) are required in order to adjust the output voltage to the pulse mask (nominal 750 mV according to CCITT I.430, to be tested with the command "SSZ") on the one hand and in order to meet the output impedance of minimum 20  $\Omega$  (transmission of a binary zero according to CCITT I.430, to be tested with the command "SCZ") on the other hand.

**Figure 25**

External Transmitter Circuitry

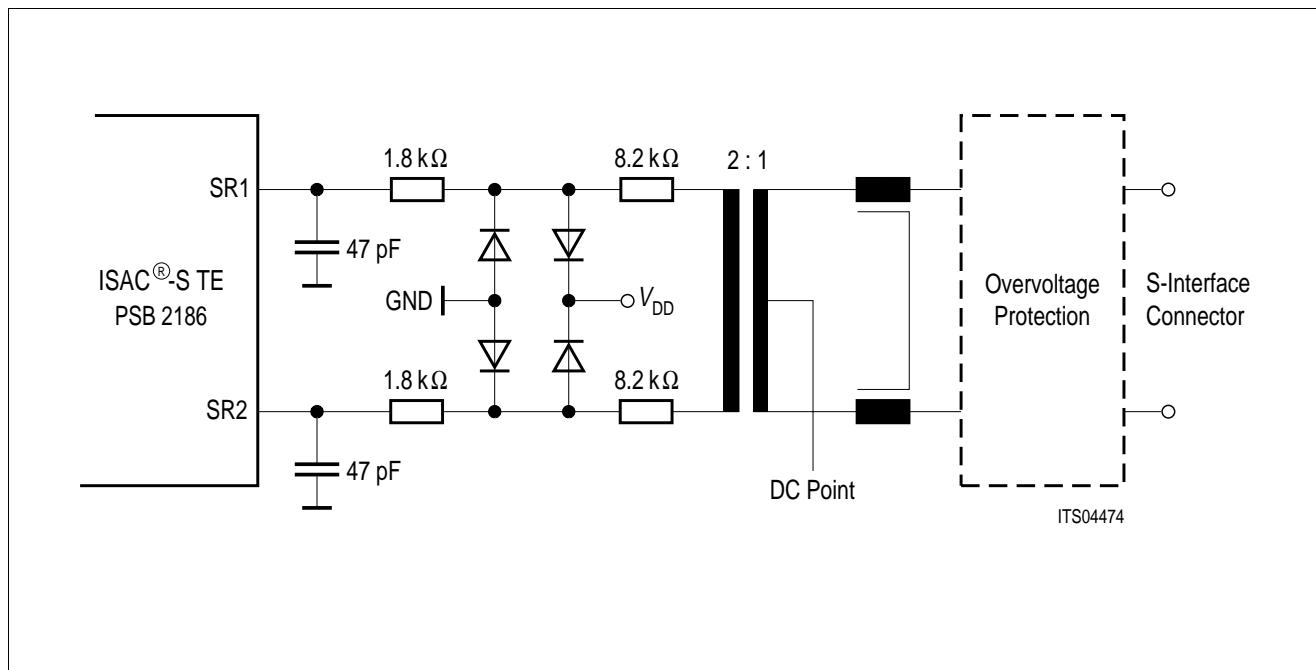

The receiver of the PSB 2186 ISAC-S TE is symmetrical as opposed to both PEB 2080 SBC and PEB 2085 ISAC-S. Thus two resistors of 10 k $\Omega$  must be placed in series to the receiver inputs.

In order to protect the ISAC-S inputs and comply to impedance requirements performed without power supply (96-kHz test), the 10 k $\Omega$  tester is split-up.

A 1.8 k $\Omega$  resistor protects the device inputs, while the 8.2 k $\Omega$  resistors limit the maximum current in impedance tests.

**Figure 26**

**External Receiver Circuity**

#### 2.4.4 S/T Interface Pre-Filter Compensation

To compensate for the extra delay introduced into the received signal by a filter, the sampling of the receive signal can be delayed by programming bits TEM and PFS in the ADF1 register as shown in **table 3**. Note that setting TEM to "1" and PFS to "0" has the effect of completely disabling layer-1 functions, for test purposes (**see section 2.6**).

**Table 3**

**TEM/PFS Function Table**

| TEM | PFS | Effect                               |

|-----|-----|--------------------------------------|

| 0   | 0   | No pre-filter (0 delay)              |

| 0   | 1   | Pre-filter delay compensation 520 ns |

| 1   | 1   | Pre-filter delay compensation 910 ns |

| 1   | 0   | Test mode (layer-1 disabled)         |

This delay compensation might be necessary in order to comply with the "total phase deviation input to output" requirement of CCITT recommendation I.430 which specifies a phase deviation in the range of – 7% to + 15% of a bit period.

## 2.4.5 Receiver Functions

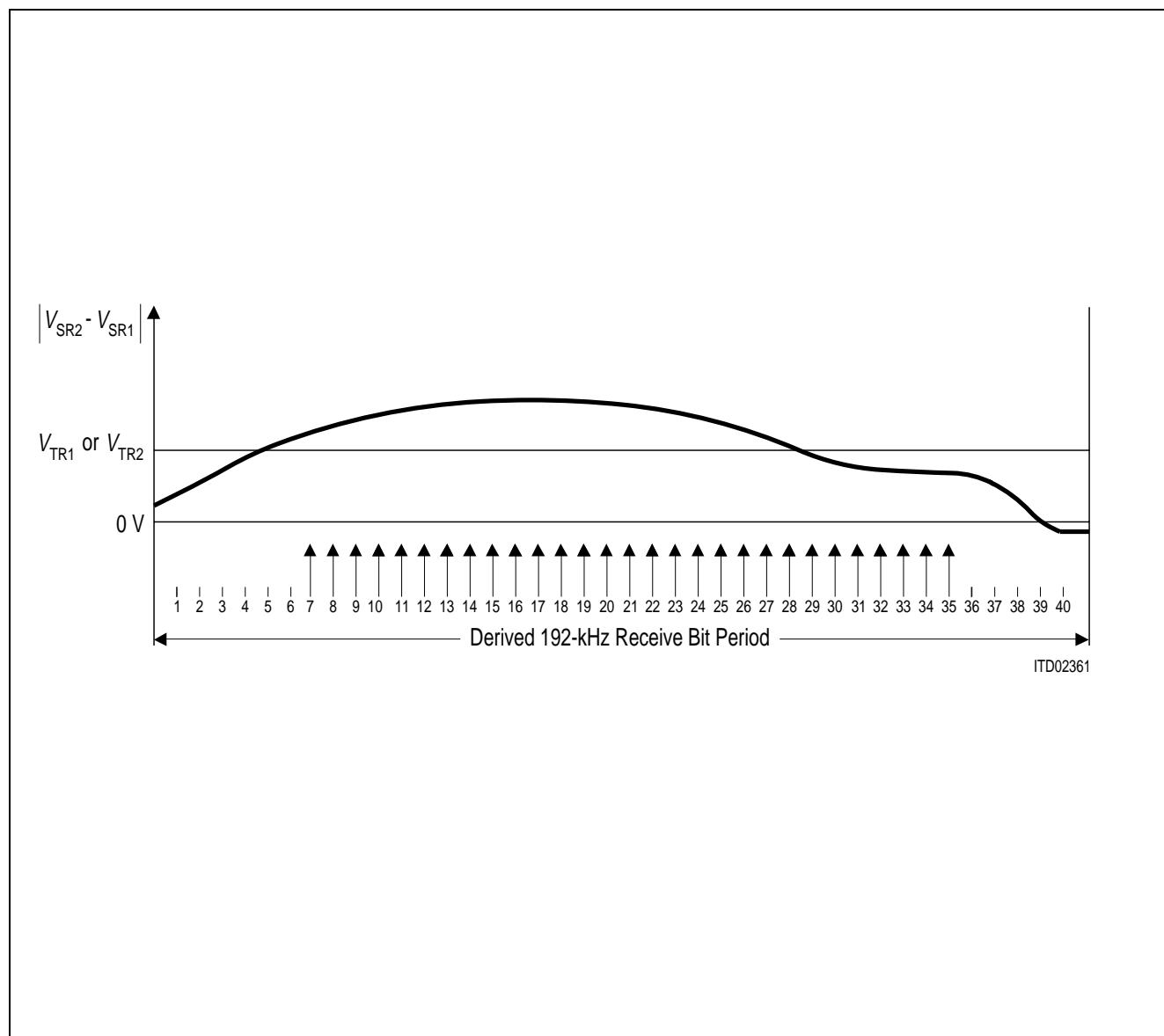

### 2.4.5.1 Receive Signal Oversampling

In order to additionally reduce the bit error rate in severe conditions, the ISAC-S TE performs oversampling of the received signal and uses majority decision logic.

As illustrated in **figure 27**, each received bit is sampled 29 times at 7.68-MHz clock intervals inside the estimated bit window. The samples obtained are compared against a threshold VTR1 or VTR2 (**see section: Adaptive Receiver Characteristics**).

If at least 16 samples have an amplitude exceeding the selected threshold, a logical "0" is considered to be detected, otherwise a logical "1" (no signal) is considered detected.

**Figure 27**

**S/T-Receive Signal Oversampling**

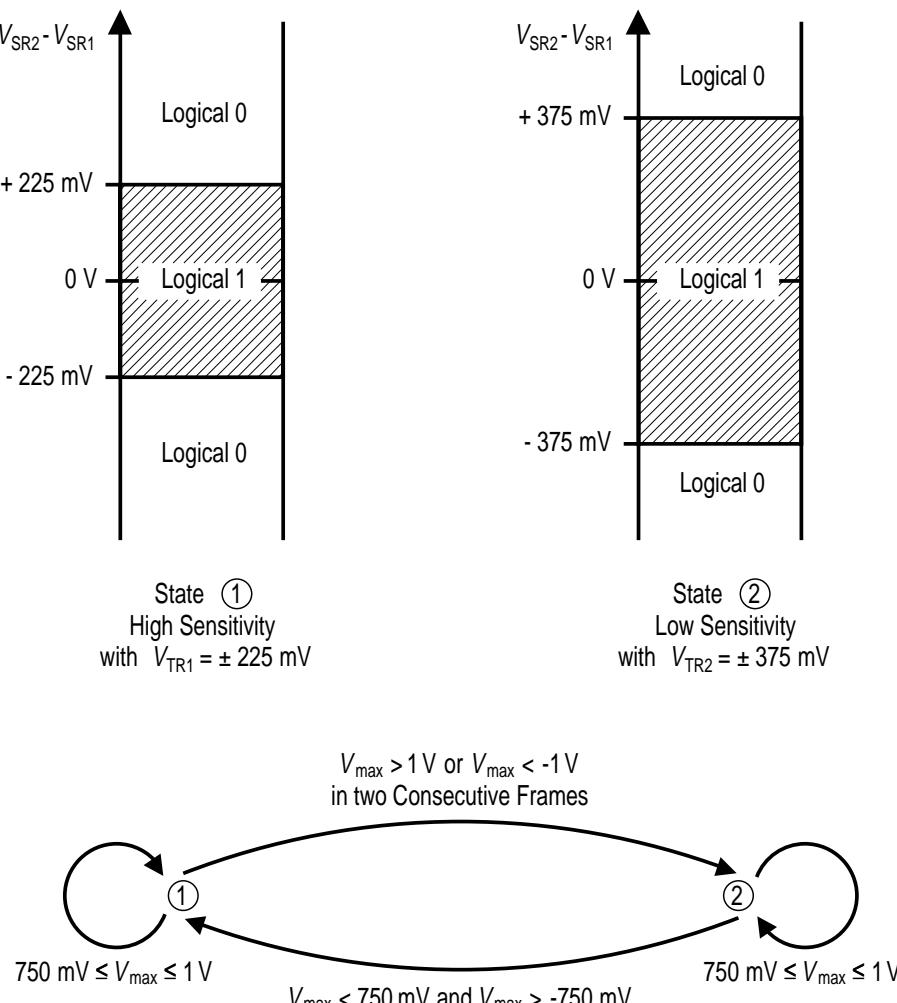

### 2.4.5.2 Adaptive Receiver Characteristics

The integrated receiver uses an adaptively switched threshold detector. The detector controls the switching of the receiver between two sensitivity levels. The hysteresis characteristics of the receiver are shown in **figure 28**.

$V_{SR2} - V_{SR1}$  = Input Voltage

$V_{TR1} \cdot V_{TR2}$  = Threshold Voltages of the Receiver Threshold Detector

$V_{\max}$  = Maximum Value of  $V_{SR2} - V_{SR1}$  during one Frame

ITD00774

**Figure 28**

**Switching of the Receiver between High Sensitivity and Low Sensitivity**

### 2.4.5.3 Level Detection Power Down

In power down state, (see chapter 3.3.1) only an analog level detector is active. All clocks, including the IOM interface, are stopped. The data lines are "high", whereas the clocks are "low".

An activation initiated from the exchange side (Info 2 on S bus detected) will have the consequence that a clock signal is provided automatically.

From the terminal side an activation must be started by setting and resetting the SPU bit in the SPCR register (see chapter 4).

### 2.4.6 Timing Recovery

The transmit and receive bit clocks are derived, with the help of the DPLL, from the S-interface receive data stream. The received signal is sampled several times inside the derived receive clock period, and a majority logic is used to additionally reduce bit error rate in severe conditions (see chapter 2.4.5). The transmit frame is shifted by two bits with respect to the received frame.

The output clocks (DCL, FSC1 etc.) are synchronous to the S-interface timing.

**Figure 29**

**Clock System of the ISAC®-S TE in TE Mode**

## 2.4.7 Activation/Deactivation

An incorporated finite state machine controls ISDN layer-1 activation/deactivation according to CCITT (see chapter 3.4).

### Loss of Synchronization / Resynchronization

The following section describes the behaviour of the PSB 2186 in respect to the CTS test procedures for frame alignment.

#### Setting of the ISAC-S TE

The ISAC-S TE needs to be programmed for multiframe operation with the Q-bits set to '1'.

STAR2: MULT = 0

SQXR:SQX1-4 = 1111B (xFH)

#### 2.4.7.1 FAinfA\_1fr

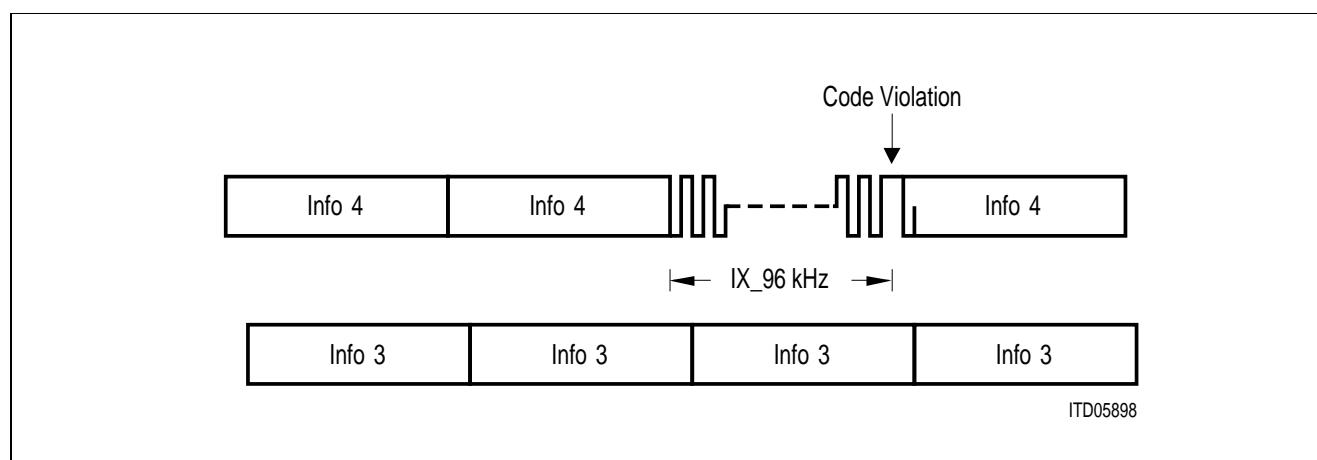

This test checks if no loss of frame alignment occurs upon a receipt of one bad frame. The pattern for the bad frame is defined as IX\_96 kHz. This pattern was revised so that a code violation is generated at the begin of the next info 4 frame.

| Device        | Settings | Result | Comments |

|---------------|----------|--------|----------|

| PSB 2186 V1.1 | none     | Pass   |          |

### 2.4.7.2 FAinfB\_1fr

This test uses a frame which has no framing and balancing bit.

| Device        | Settings | Result | Comments |

|---------------|----------|--------|----------|

| PSB 2186 V1.1 | none     | Pass   |          |

### 2.4.7.3 FAinfD\_1fr

This test uses a frame which remains at binary '1' until the first code violation in bit 16. Since it is specified, that a terminal should mirror the received  $F_A$ -bit in the transmitted  $F_A$ -bit, a frame is generated by the IUT which will not generate a second code violation. The pattern for a correct i3\_BASIC frame states that the  $F_A$ -bit may have any value.

| Device        | Settings | Result | Comments |

|---------------|----------|--------|----------|

| PSB 2186 V1.1 | none     | Pass   |          |

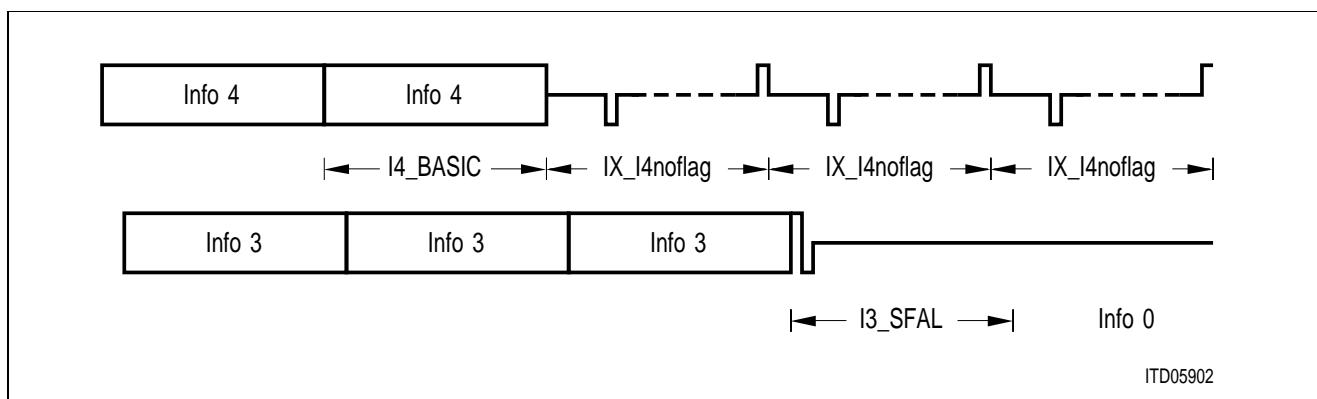

#### 2.4.7.4 FAinfA\_kfr

This test uses a number of IX\_96 kHz frames to check the loss of synchronization.

| Device        | Settings | Result | Comments |

|---------------|----------|--------|----------|

| PSB 2186 V1.1 | $n = 2$  | Pass   |          |

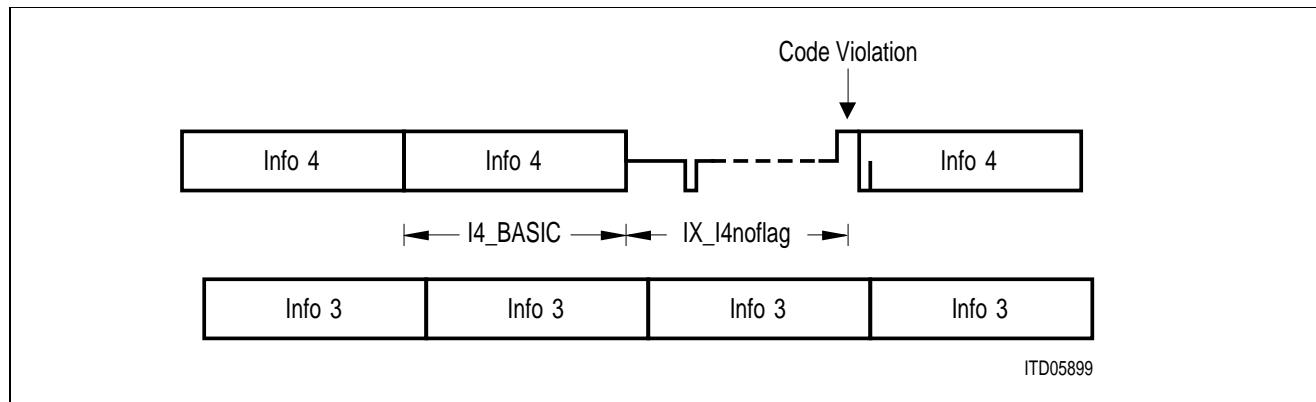

#### 2.4.7.5 FAinfB\_kfr

This test uses a number of IX\_I4noflag frames to check the loss of synchronization.

| Device        | Settings | Result | Comments |

|---------------|----------|--------|----------|

| PSB 2186 V1.1 | $n = 2$  | Pass   |          |

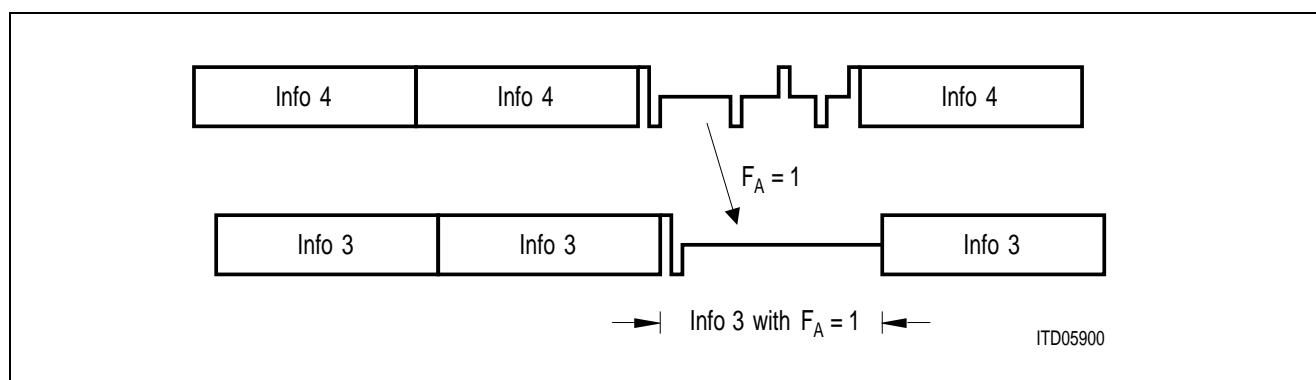

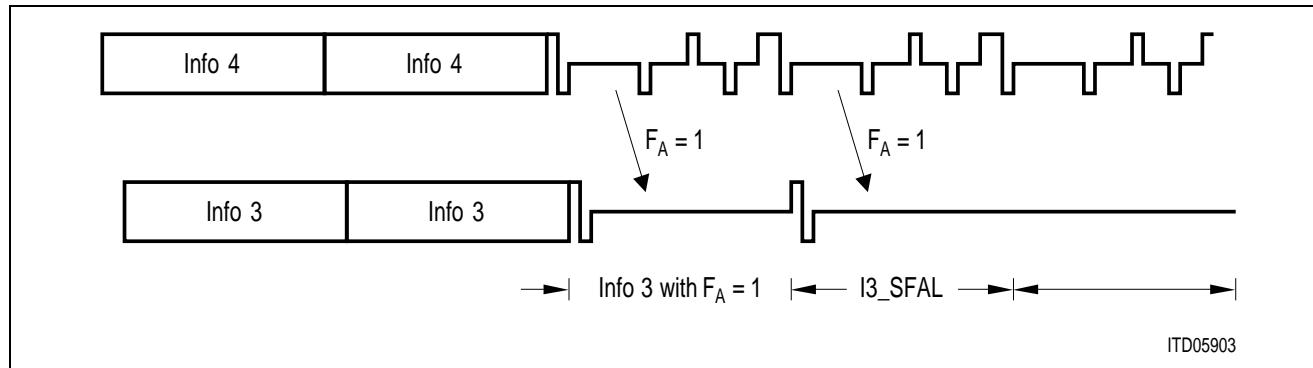

#### 2.4.7.6 FAinfD\_kfr

This test uses a number of IX\_I4voil16 frames to check the loss of synchronization. The first Info 3 frame with the  $F_A$ -bit set to one looks like a i3\_SFAL frame but it is a correct info 3 frame since the receiver stays synchronous (see **FAinfD\_1fr**).

| Device        | Settings | Result | Comments |

|---------------|----------|--------|----------|

| PSB 2186 V1.1 | $n = 2$  | Pass   |          |

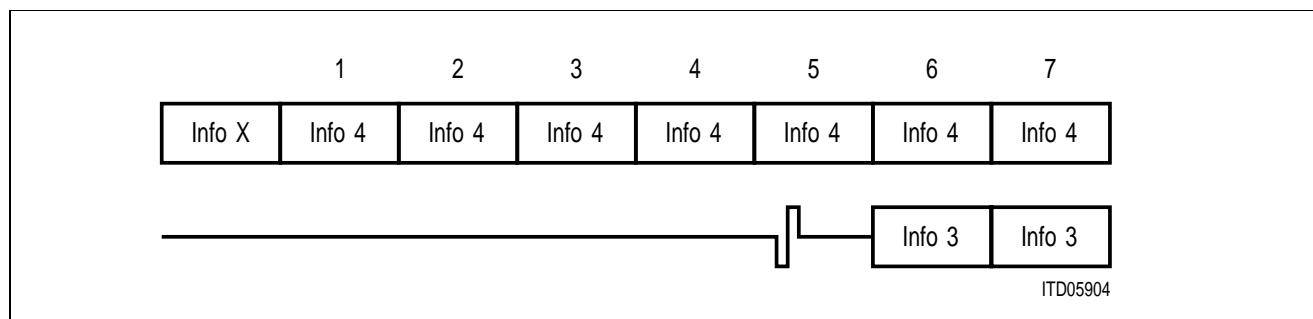

#### 2.4.7.7 FAregain

This test uses I4\_BASIC frames to regain the frame alignment. The protocol tester evaluates the difference between sending the first info 4 frame until a complete info 3 frame has been received. This period is considered as 'm+1'. 'm' must be specified before the test is started.

The PSB 2186 achieves synchronization after 5 or 6 frames. The actual value depends on internal timing conditions which can not be influenced from extern. This is a result of changes that were made to handle the iXvoil16 test case correctly. The info 4 pattern generates the second code violation at the position of the  $F_A$ -bit. Around that bit position, the state machine changes its states. As a result of that overlap, the info 3 frame is transmitted after 5 frames or one frame later.

| Device        | Settings       | Result | Comments |

|---------------|----------------|--------|----------|

| PSB 2186 V1.1 | $m = 5$ or $6$ | Pass   |          |

## 2.4.8 D-Channel Access

The D channel is submitted to the D-channel access procedure according to CCITT recommendation I.430.

The D-channel access procedure according to CCITT I.430 including priority management is fully implemented in the ISAC-S:

If collision detection is programmed (MODE:DIM2-0), a collision is detected if either an echo bit of "0" is recognized and a D bit of "1" was generated, or an echo bit of "1" is recognized and a D bit of "0" was generated. When this occurs, D-channel transmission is immediately stopped, and the echo channel is monitored to enable a subsequent D-channel access to be attempted.

### Stop/Go Bit

As the collision resolution is performed by the layer-1 part of the device, an information about the D-channel status ("ready" or "busy") must be sent back to the layer-2 part to control HDLC transmission. For this goal a Stop/Go (S/G) bit is transmitted over the IOM interface to the layer-2 device.

The S/G bit is transmitted in bit 90 of an IOM-2 frame (12-byte structure) (**see figure 19**).

A logical "1" of the S/G bit indicates a collision on the S bus. By sending the S/G bit a logical "0" to the layer-2 controller in anticipation of the S bus D channel "ready"-state, the first valid 0 bits will emerge from the layer-1 part at exactly that moment an access is becoming possible.

### Selection of D-Channel Access Mode

For proper operation of the D-channel access procedure, the ISAC-S TE must be programmed via the MODE (**see chapter 4.1.7**) register to evaluate the stop/go bit. This is achieved by setting MODE:DIM2-0 to 001 or 011.

### Selection of the Priority Class

The priority class (priority 8 or priority 10) is selected by transferring the appropriate activation command via the Command/Indicate (C/I) channel of the IOM interface to the layer-1 controller. If the activation of the S interface is initiated by a TE, the priority class is selected implicitly by the choice of the activation command. If the S-Interface is activated from the NT, an activation command selecting the desired priority class should be programmed at the TE on reception of the activation indication (AI8). In the activated state, the priority class may be changed whenever required simply by programming the respective activation request command (AR8 or AR10). The following table summarizes the C/I codes used for setting the priority classes:

**Table 4**

**Priority Commands/Indications**

| Command (upstream)                         | Abbr. | Code | Remarks                                          |

|--------------------------------------------|-------|------|--------------------------------------------------|

| Activate request, set priority 8           | AR8   | 1000 | Activation command: Set D-channel priority to 8  |

| Activate request, set priority 10          | AR10  | 1001 | Activation command: Set D-channel priority to 10 |

| Indication (downstream)                    | Abbr. | Code | Remarks                                          |

| Activate indication with priority class 8  | AI8   | 1100 | Info 4 received: D-channel priority is 8 or 9    |

| Activate indication with priority class 10 | AI10  | 1101 | Info 4 received: D-channel priority is 10 or 11  |

#### 2.4.9 S- and Q-Channel Access

Access to the received/transmitted S- or Q channel is provided via registers. As specified by CCITT I.430, the Q bit is transmitted from TE to NT in the position normally occupied by the auxiliary framing bit ( $F_A$ ) in one frame out of 5, whereas the S bit is transmitted from NT to TE in a spare bit, **see figure 22**.

The functions provided by the ISAC-S are:

- Synchronization to the received 20 frame multiframe by means of the received M bit pattern. Synchronization is achieved when the M bit has been correctly received during 20 consecutive frames starting from frame number 1 (**table 5**).

- When synchronization is achieved, the four received S bits in frames 1, 6, 11 and 16 are stored as SQR1 to SQR4 in the SQRR register if the complete M bit multiframe pattern was correctly received in the corresponding multiframe. A change in any of the received four bits (SQR1, 2, 3 or 4) is indicated by an interrupt (CISQ in ISTA and SQC in CIR0).

- When an M bit is observed to have a value different from that expected, the synchronization is considered lost. The SQR bits are not updated until synchronization is regained. The synchronization state is constantly indicated by the SYN bit in the SQRR register.

- When synchronization with the received multiframe is achieved, the four bits SQX1 to SQX4 stored in the SQXR register are transmitted as the four Q bits ( $F_A$ -bit position) in frames 1, 6, 11 and 16 respectively (starting from frame number one). Otherwise the bit transmitted is a mirror of the received  $F_A$ -bit. At loss of synchronization (mismatch in M bit) the mirroring is resumed starting with the next  $F_A$ -bit.

- The S/T multiframe synchronization can be disabled in the STAR2 register (MULT bit).

**Table 5****S- and Q-Bit Position Identification and Multiframe Structure****S- and Q-Channel Structure**

| Frame Number | NT-to-TE<br>F <sub>A</sub> -Bit<br>Position | NT-to-TE<br>M Bit | NT-to-TE<br>S Bit | TE-to-NT<br>F <sub>A</sub> -Bit<br>Position |

|--------------|---------------------------------------------|-------------------|-------------------|---------------------------------------------|

| 1            | ONE                                         | ONE               | S1                | Q1                                          |

| 2            | ZERO                                        | ZERO              | ZERO              | ZERO                                        |

| 3            | ZERO                                        | ZERO              | ZERO              | ZERO                                        |

| 4            | ZERO                                        | ZERO              | ZERO              | ZERO                                        |

| 5            | ZERO                                        | ZERO              | ZERO              | ZERO                                        |

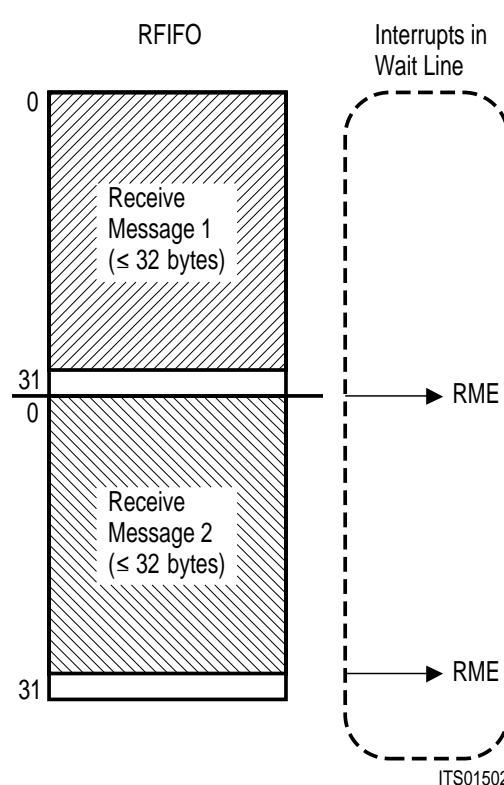

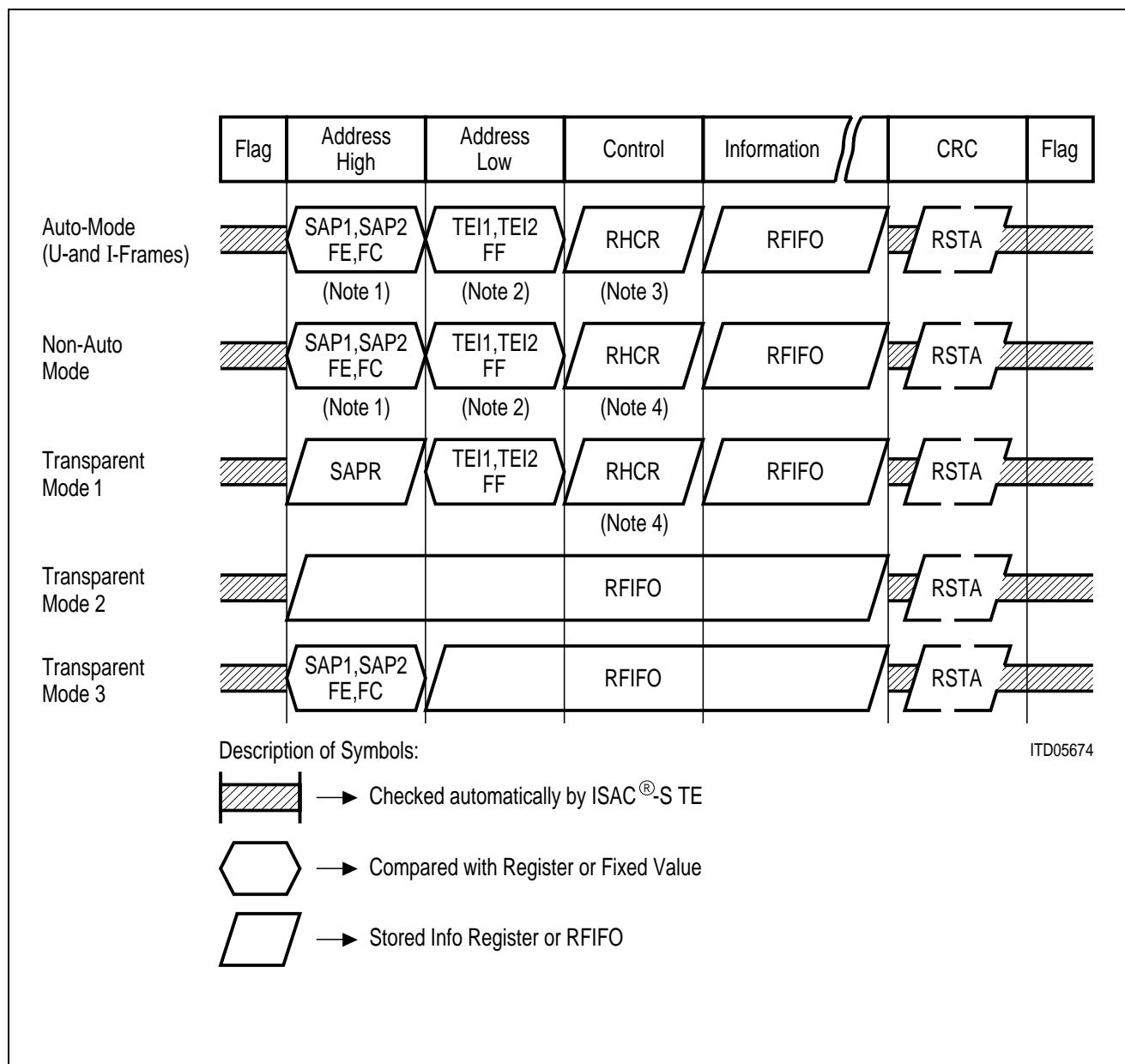

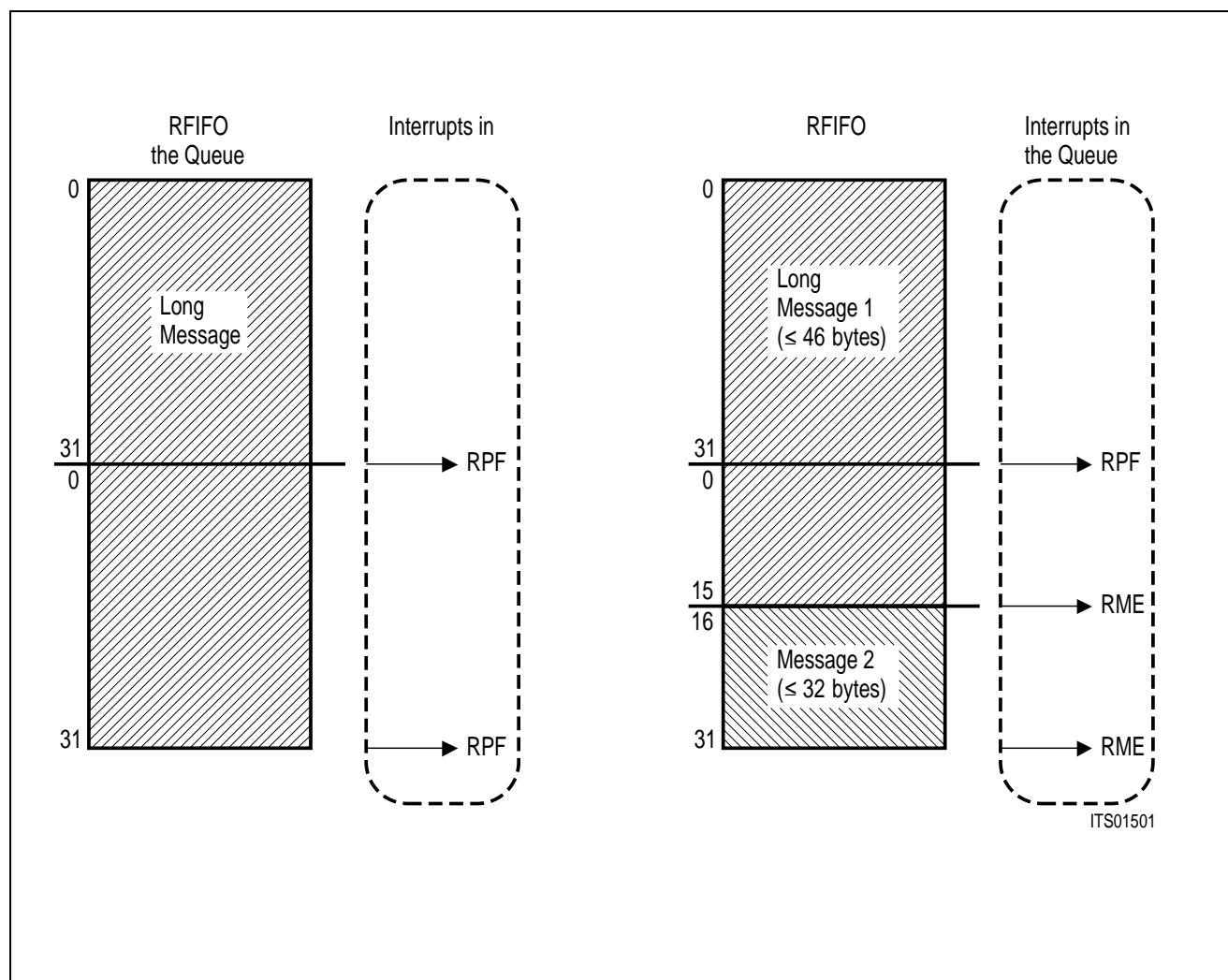

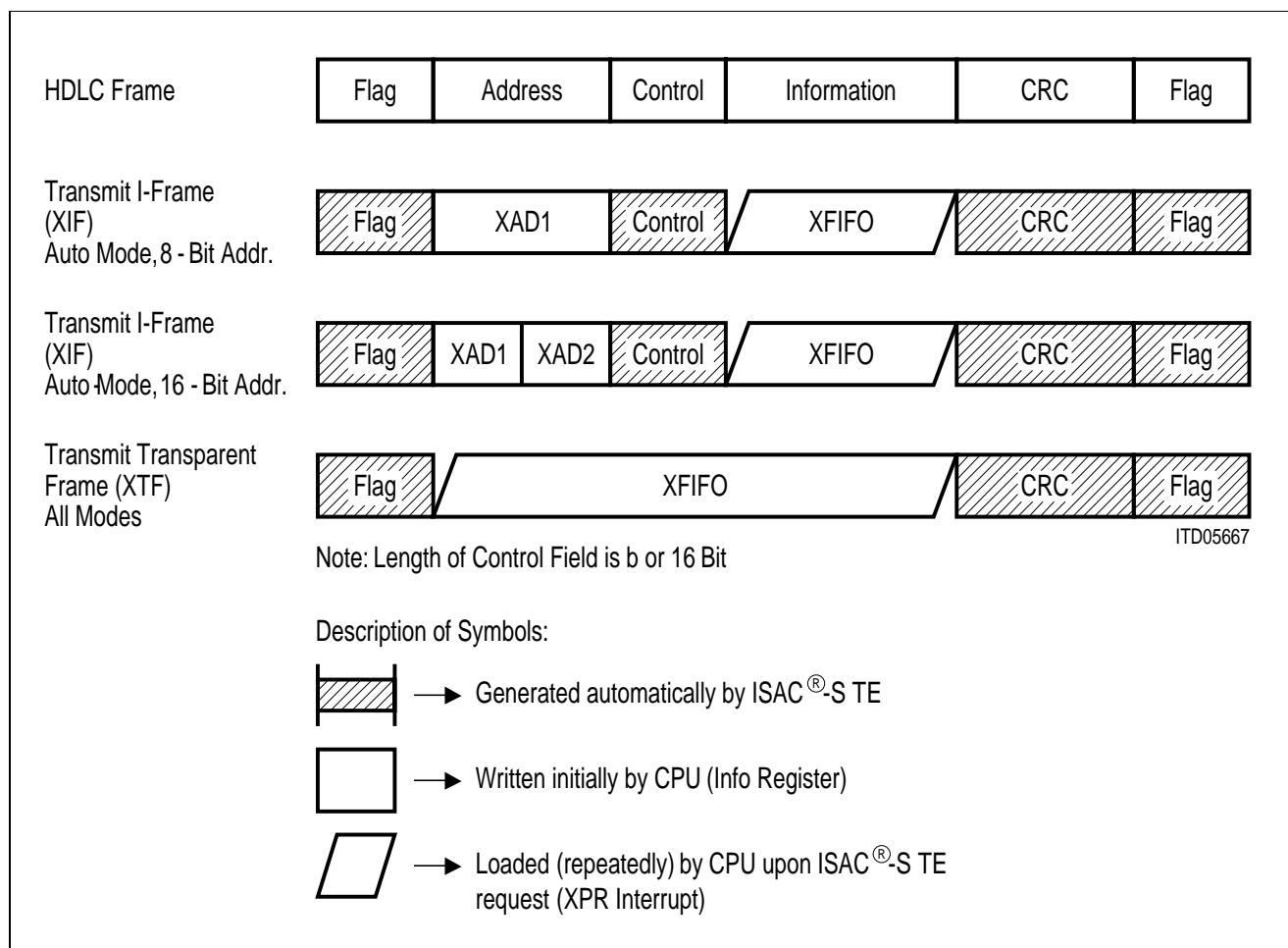

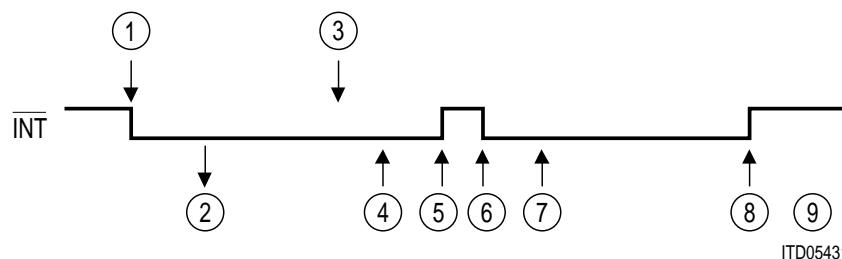

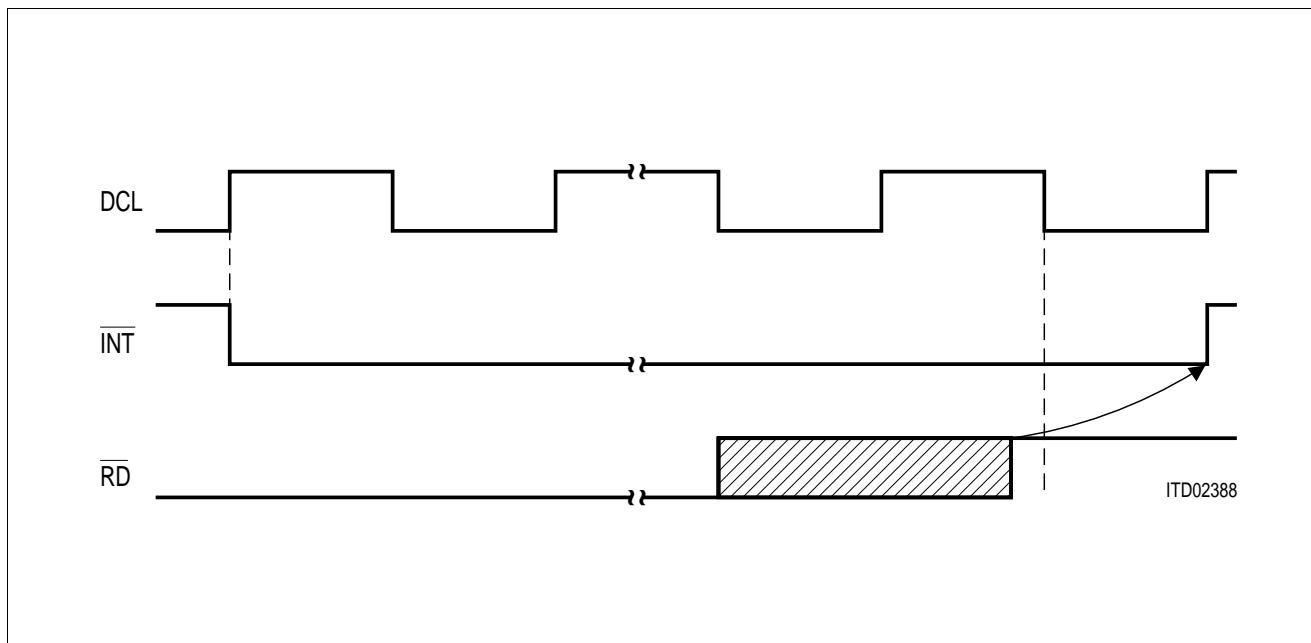

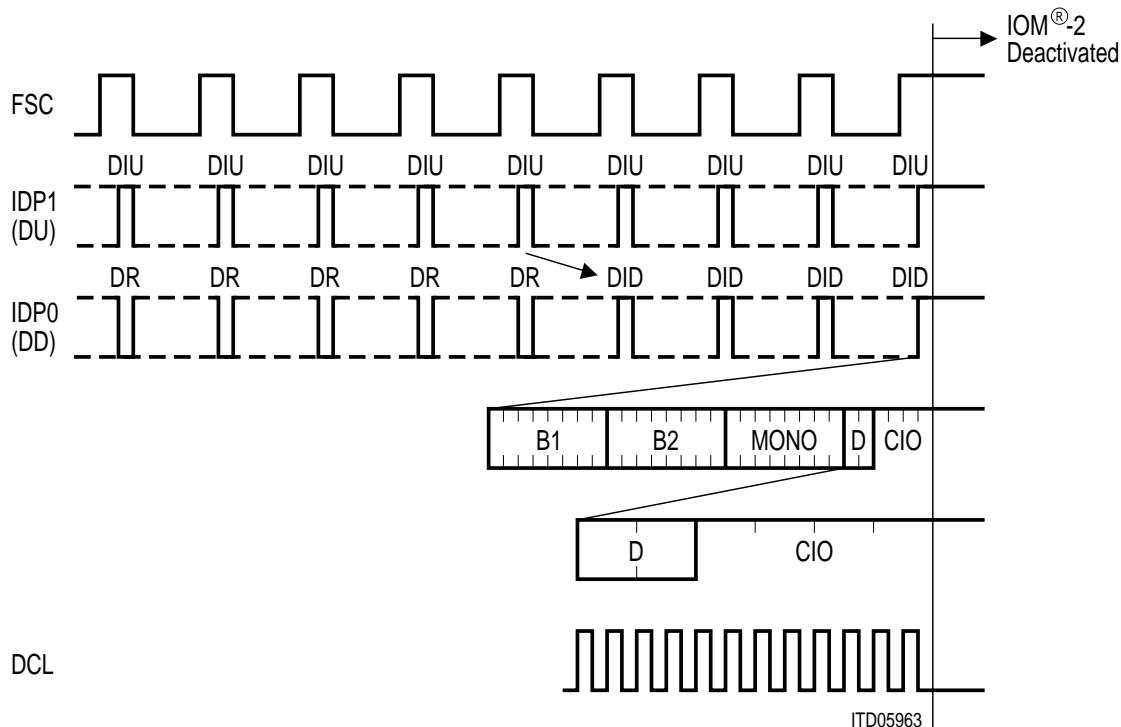

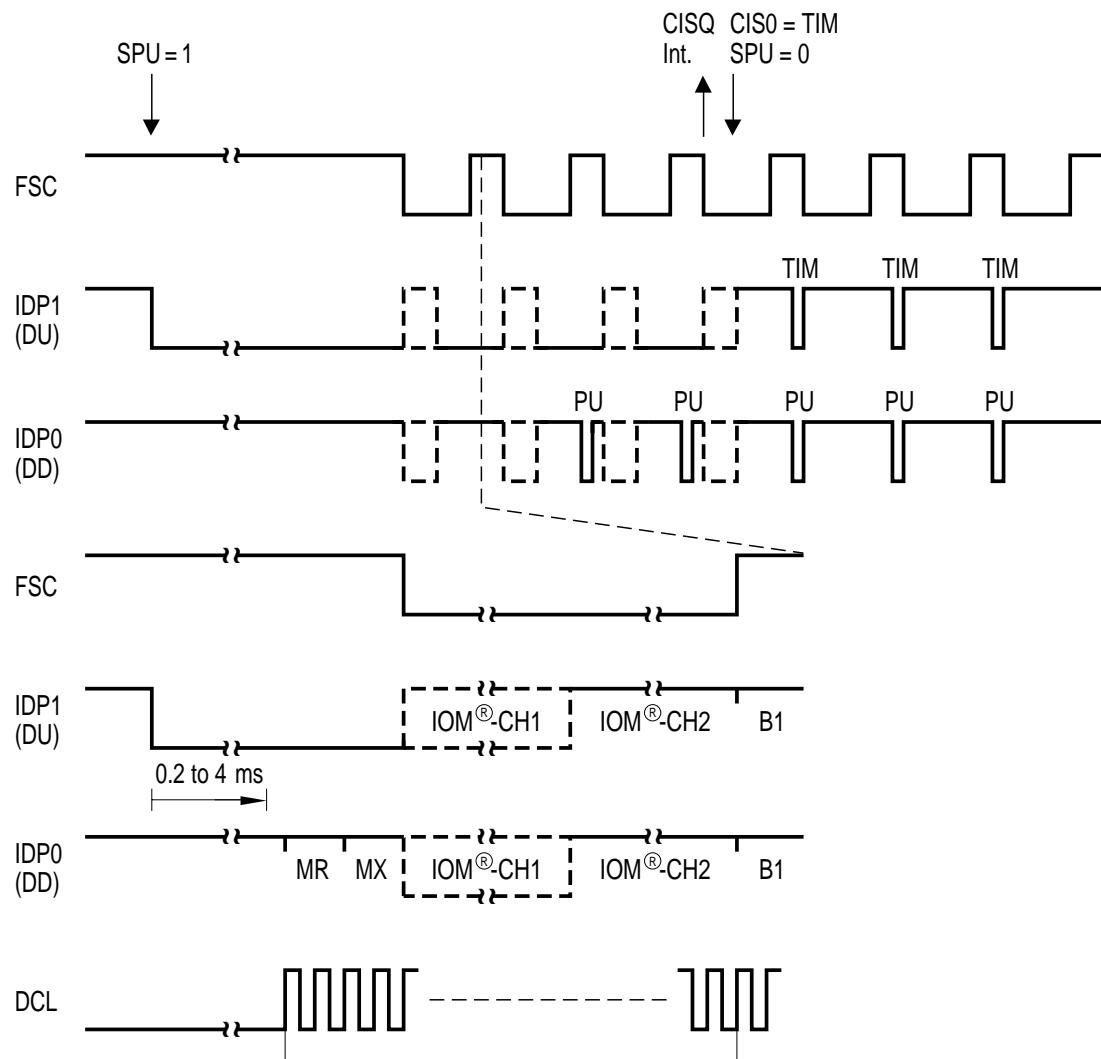

| 6            | ONE                                         | ZERO              | S2                | Q2                                          |