# CMOS 16-Bit Microcontrollers TMP95CS54F

## Outline and Features

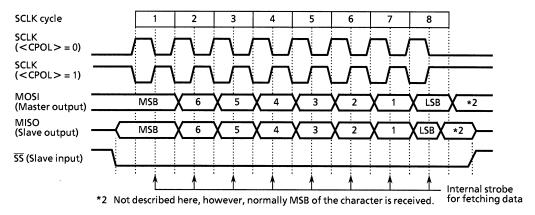

The TMP95CS54 is a high-speed 16-bit microcontroller designed for the control of various mid- to large-scale equipment.

The TMP95CS54 comes in a 100-pin flat package.

Listed below are the features of the TMP95CS54.

- (1) High-speed 16-bit CPU (900/H CPU)

- Instruction mnemonics are upward-compatible with the TLCS-90/900

- 16 Mbytes of linear address space

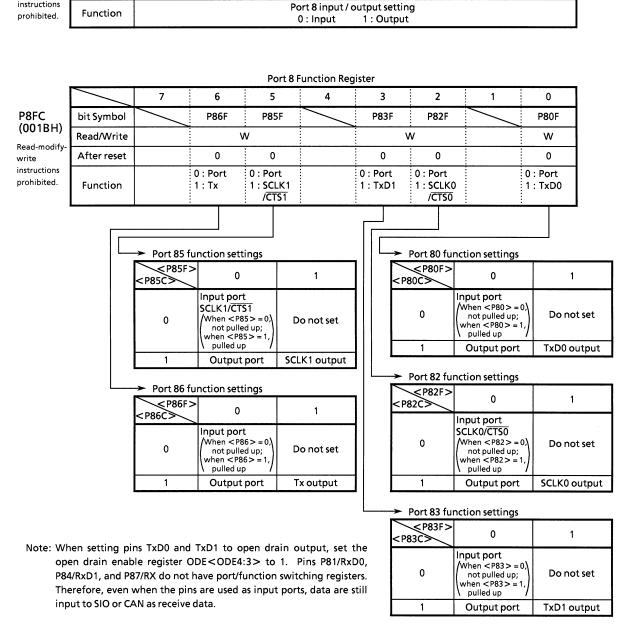

- General-purpose registers and register banks

- 16-bit multiplication and division instructions; bit transfer and arithmetic instructions

- Micro DMA: Four-channels (667 ns/2 bytes at 24 MHz)

- (2) Minimum instruction execution time: 167 ns (at 24 MHz)

- (3) Built-in RAM: 2 Kbytes Built-in ROM: 64 Kbyte

#### **RESTRICTIONS ON PRODUCT USE**

030619EBP

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

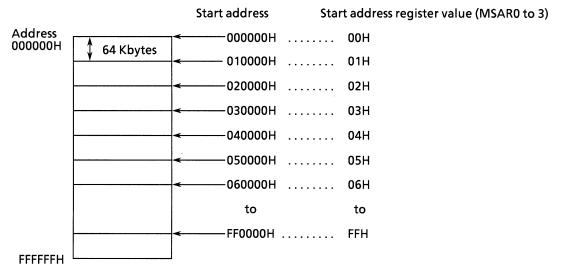

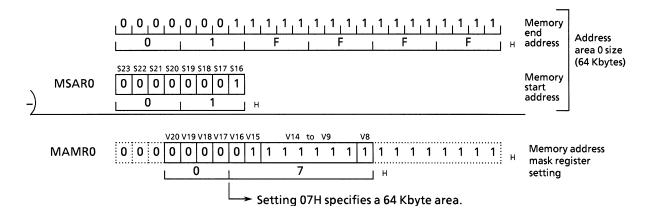

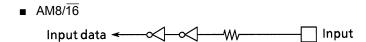

- (4) External memory expansion

- Expandable up to 16 Mbytes (shared program/data area)

- External data bus width select pin  $(AM8/\overline{16})$

- Can simultaneously support 8/16-bit width external data bus  $\cdots$  Dynamic data bus sizing

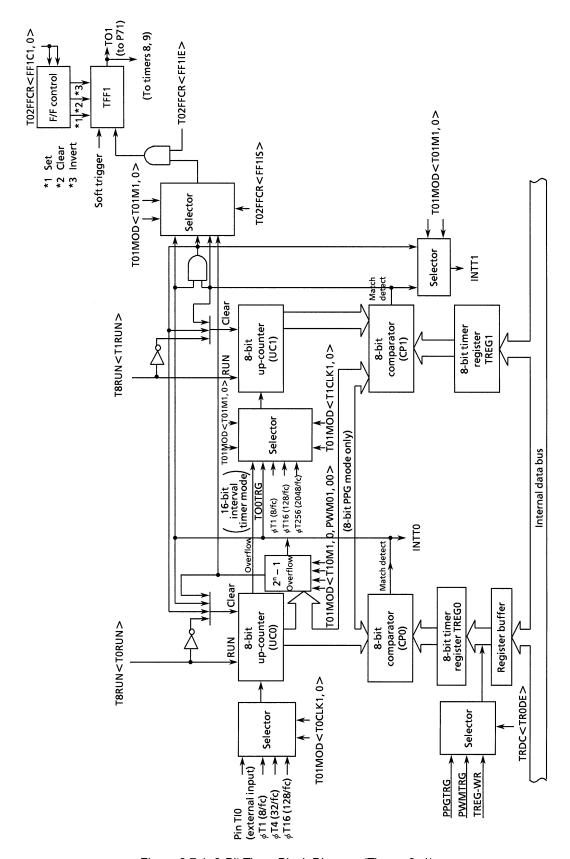

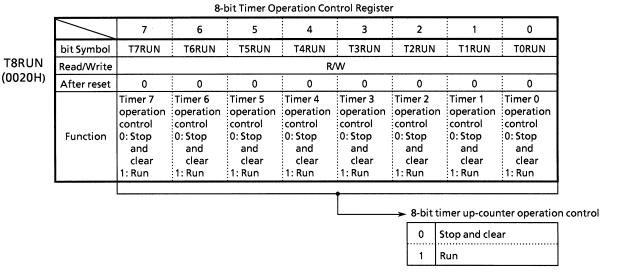

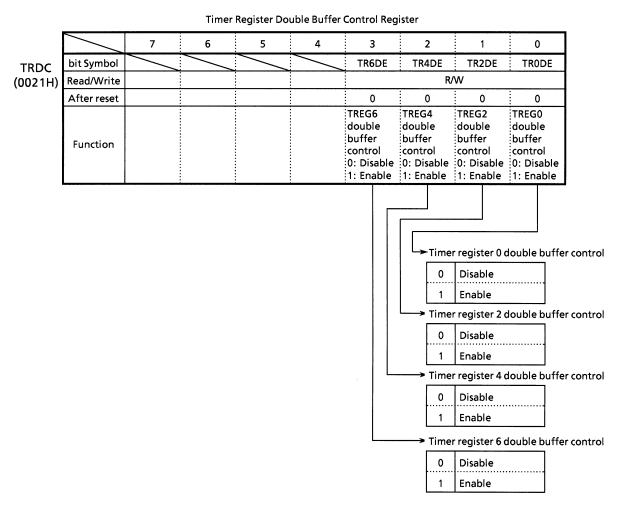

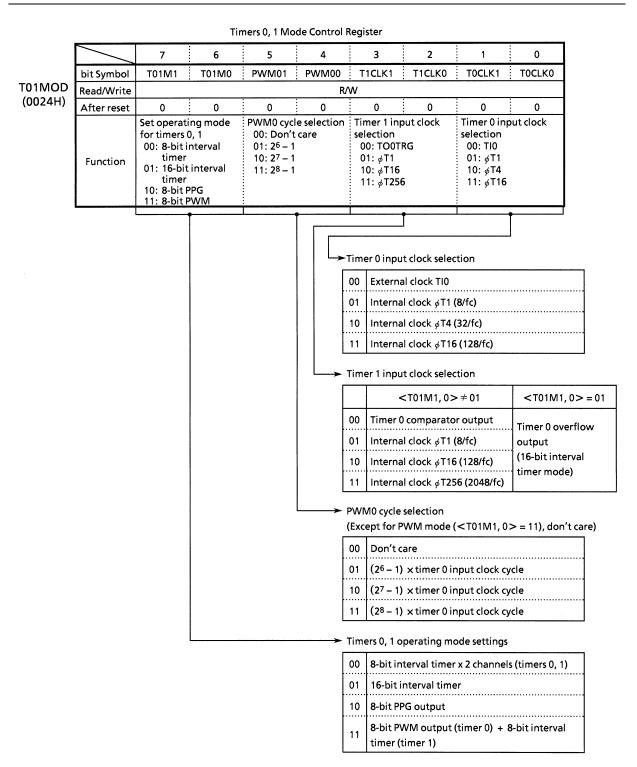

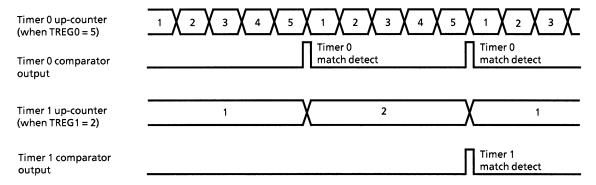

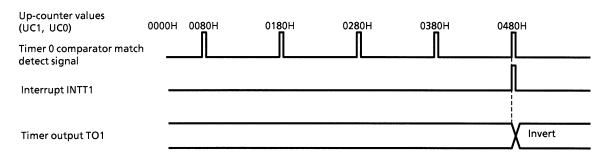

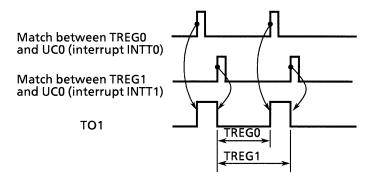

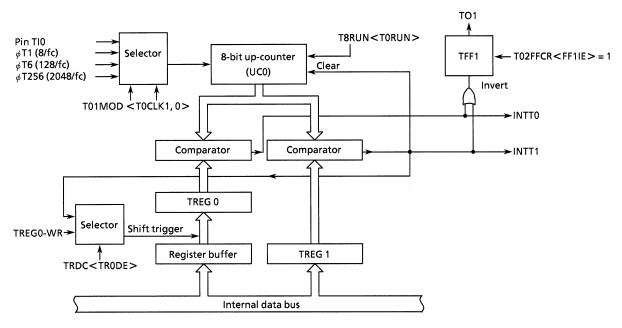

- (5) 8-bit timers: 8 channels

- With event counter function: 2 channels

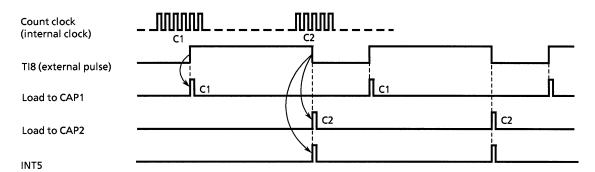

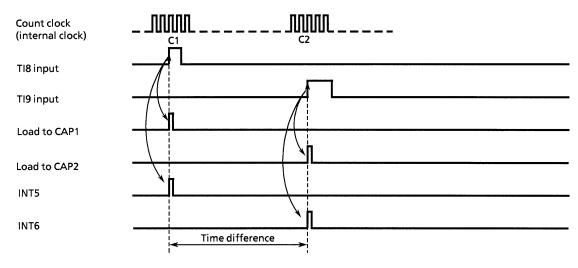

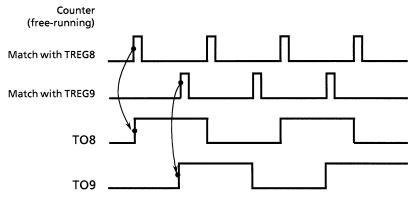

- (6) 16-bit timer/event counter: 2 channels

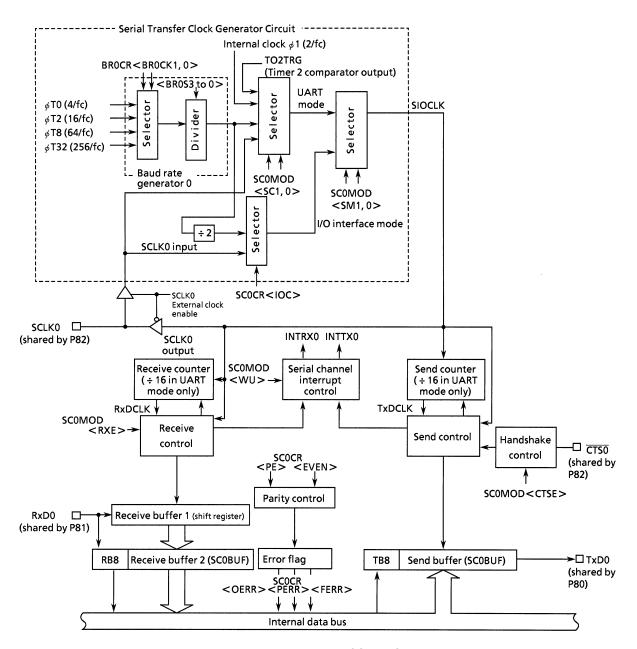

- (7) General-purpose serial interface : 2 channels

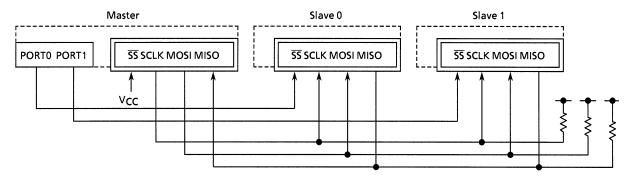

- (8) Serial Expansion Interface: 1 channel

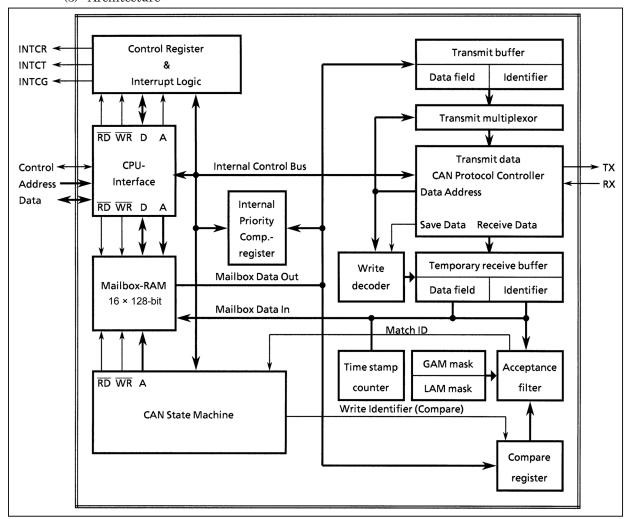

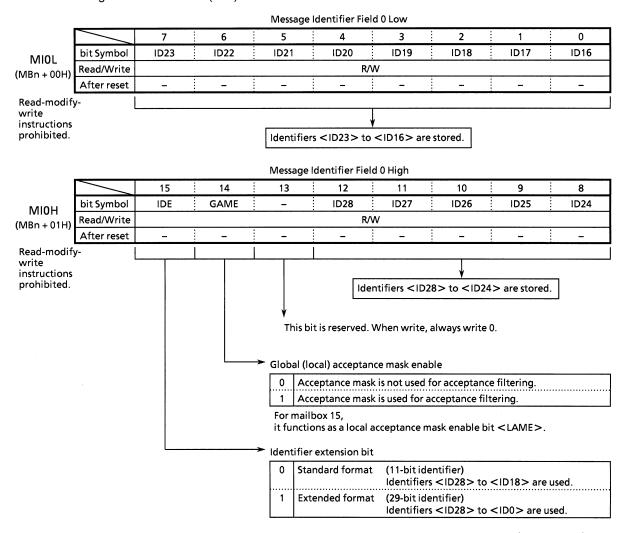

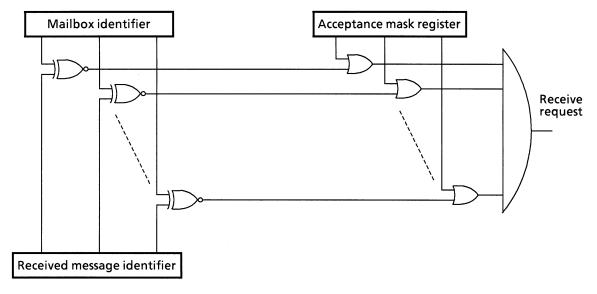

- (9) CAN Controller: 1 channel

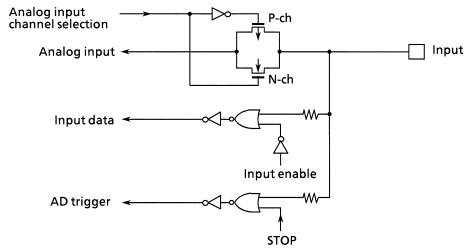

- (10) 10-bit AD converter: 8 channels

- (11) Watchdog timer

- (12) Bus width/wait controller: 4 blocks

- (13) Interrupts: 47 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 28 internal interrupts: Seven selectable priority levels

- 10 external interrupts: Seven selectable priority levels

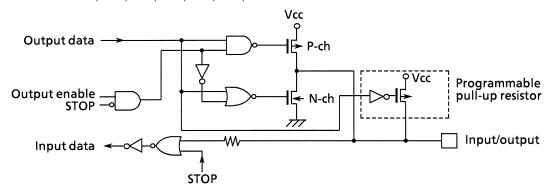

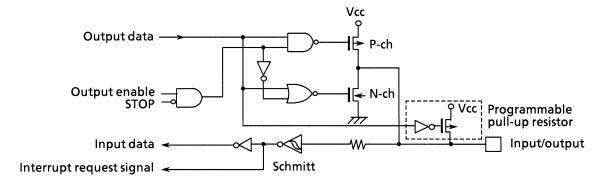

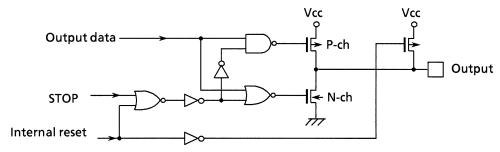

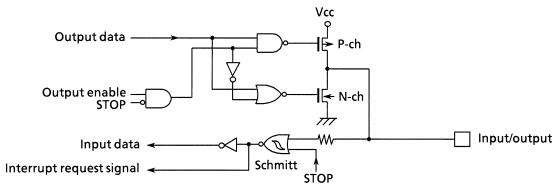

- (14) Input/output ports: 81 pins

- (15) Standby mode

- Four HALT modes: RUN, IDLE2, IDLE1, STOP

- (16) Operating voltage

- $V_{CC} = 4.7 \text{ to } 5.3 \text{ V}$

- (17) Package

- P-LQFP100-1414-0.50D

95CS54-2 2005-05-10

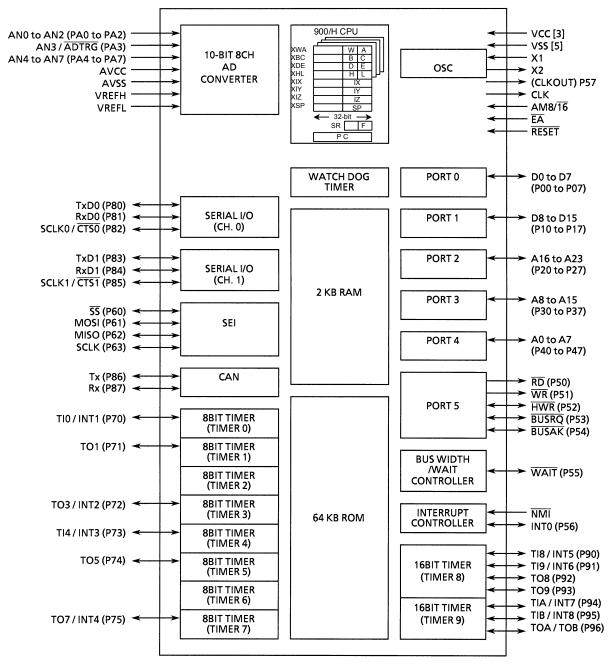

Note: After a reset, functions in parentheses ( ) are selected for the shared pins.

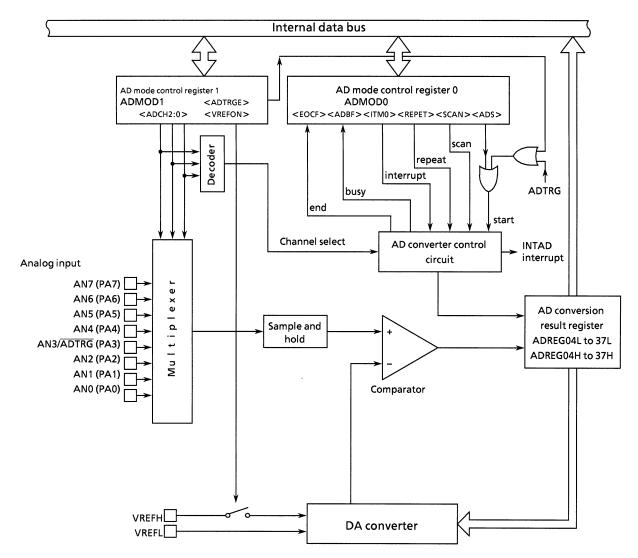

Figure 1.1 TMP95CS54 Block Diagram

# 2. Pin Assignment and Pin Functions

This section shows the TMP95CS54 pin assignment, and the names and an outline of the functions of the input/output pins.

## 2.1 Pin Assignment Diagram

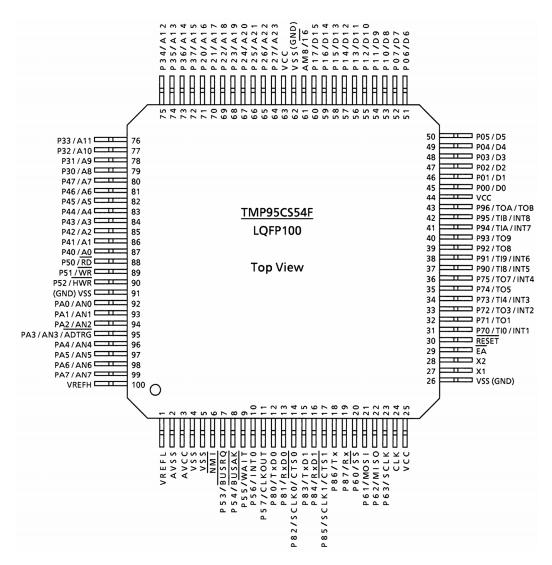

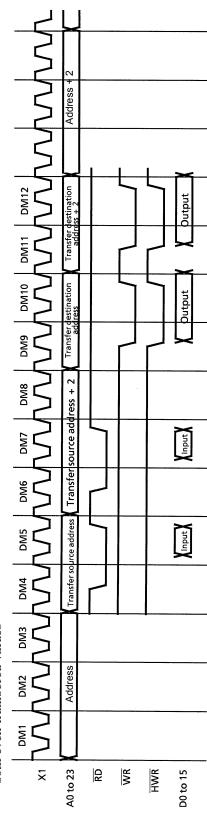

Figure 2.1.1 is the pin assignment diagram for the TMP95CS54.

Figure 2.1.1 Pin Assignment Diagram (100-Pin LQFP)

## 2.2 Pin Names and Functions

Table 2.2.1 shows the names and functions of the input/output pins.

Table 2.2.1 Pin Names and Functions (1/4)

| Pin Name         | Number<br>of Pins | Input/Output | Function                                                            |  |  |  |  |

|------------------|-------------------|--------------|---------------------------------------------------------------------|--|--|--|--|

| P00 to P07       | 8                 | Input/output | Port 0: I/O port. Input or output specifiable in units of bits      |  |  |  |  |

| / D0 to D7       |                   | Input/output | Data: Data bus 0 to 7                                               |  |  |  |  |

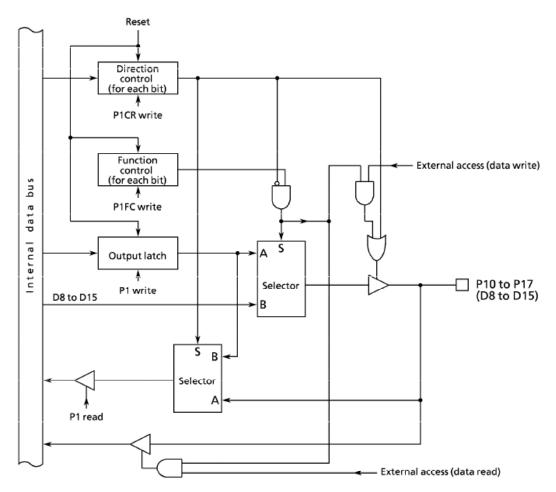

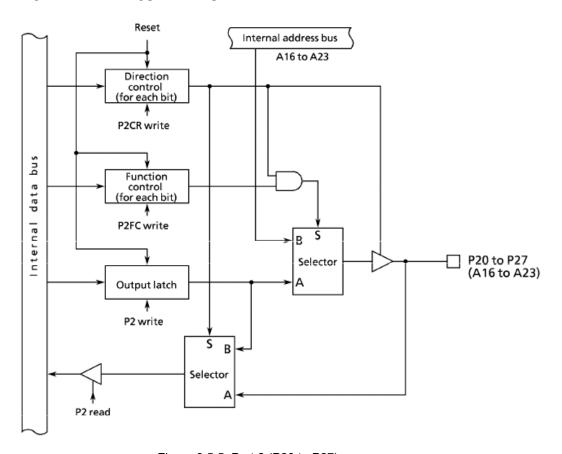

| P10 to P17       | 8                 | Input/output | Port 1: I/O port. Input or output specifiable in units of bits      |  |  |  |  |

| / D8 to D15      |                   | Input/output | Data: Data bus 8 to 15                                              |  |  |  |  |

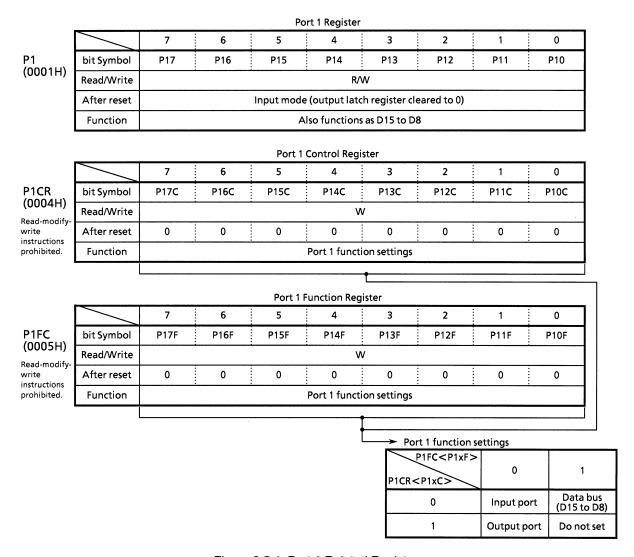

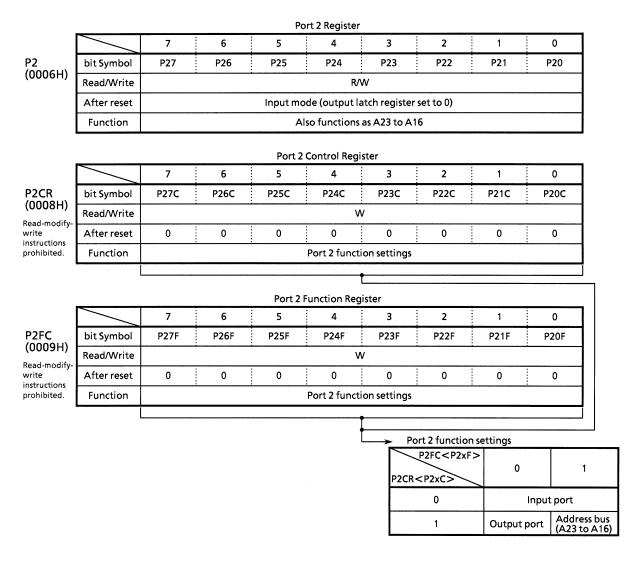

| P20 to P27       | 8                 | Input/output | Port 2: I/O port. Input or output specifiable in units of bits      |  |  |  |  |

| / A16 to A23     |                   | Output       | Address: Address bus 16 to 23                                       |  |  |  |  |

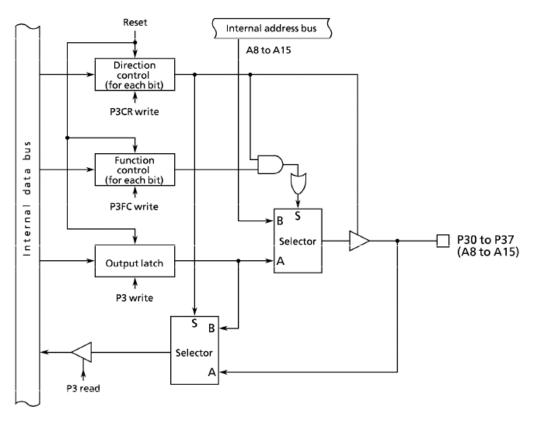

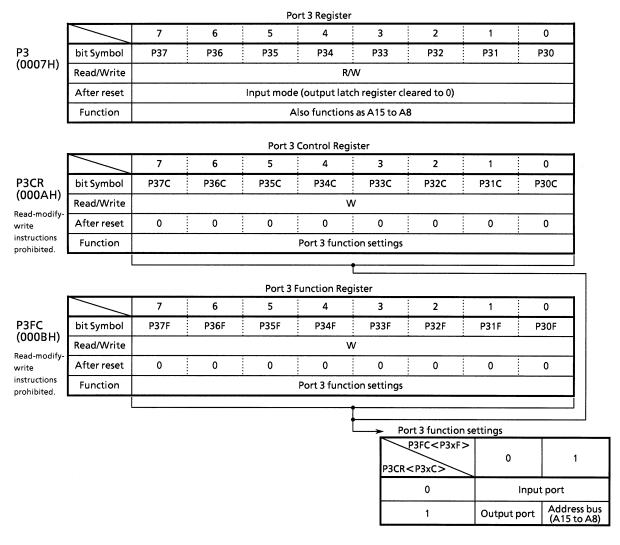

| P30 to P37       | 8                 | Input/output | Port 3: I/O port. Input or output specifiable in units of bits      |  |  |  |  |

| / A8 to A15      |                   | Output       | Address: Address bus 8 to 15                                        |  |  |  |  |

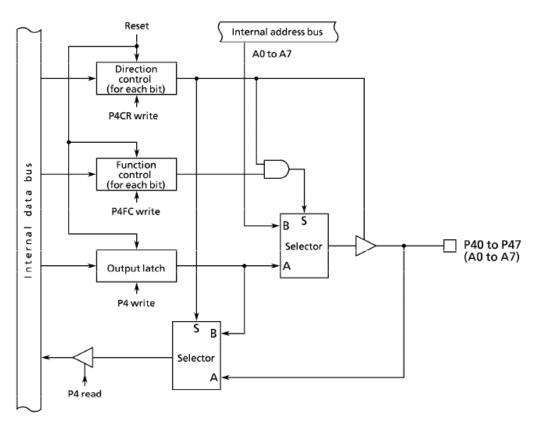

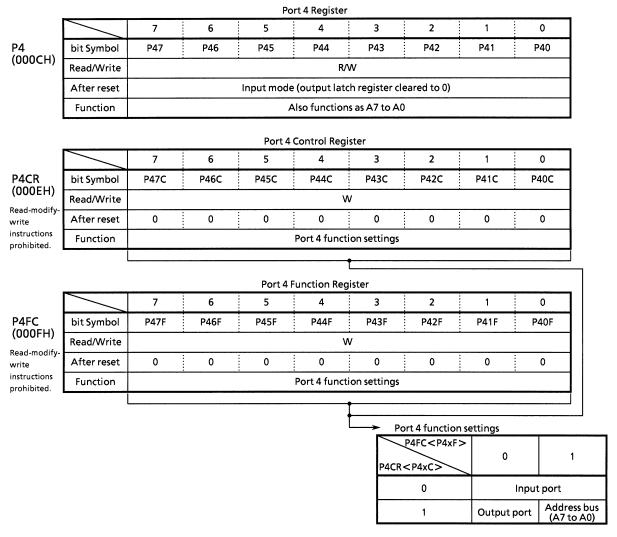

| P40 to P47       | 8                 | Input/output | Port 4: I/O port. Input or output specifiable in units of bits      |  |  |  |  |

| / A0 to A7       |                   | Output       | Address: Address bus 0 to 7                                         |  |  |  |  |

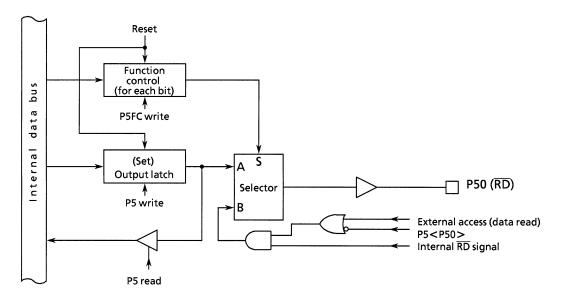

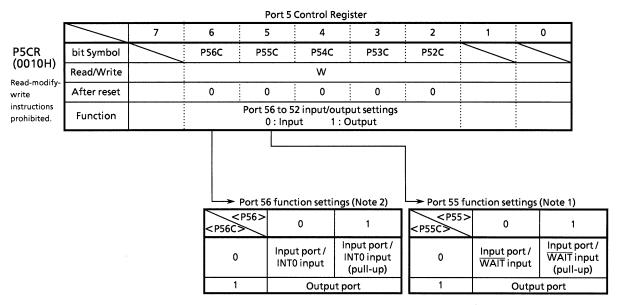

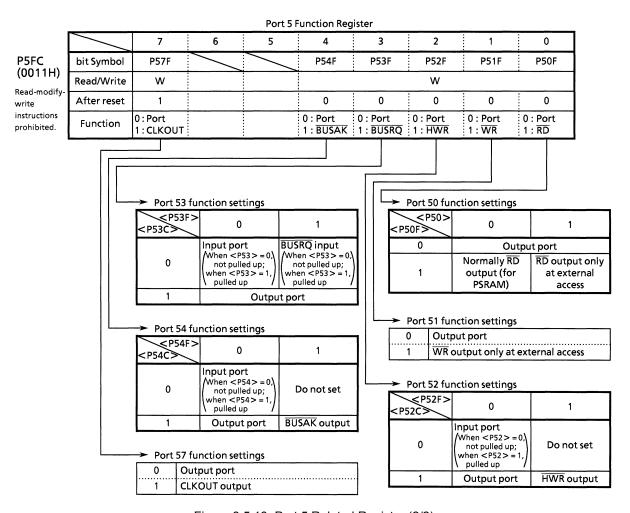

| P50              | 1                 | Output       | Port 50: Output-only port                                           |  |  |  |  |

| /RD              |                   | Output       | Read: Outputs strobe signal to read external memory (setting P5     |  |  |  |  |

|                  |                   |              | <P50> = 0 and P5FC $<$ P50F> = 1 outputs strobe signal at all read  |  |  |  |  |

|                  |                   |              | timings)                                                            |  |  |  |  |

| P51              | 1                 | Output       | Port 51: Output-only port.                                          |  |  |  |  |

| /WR              |                   | Output       | Write: Outputs strobe signal to write data on pins D0 to D7         |  |  |  |  |

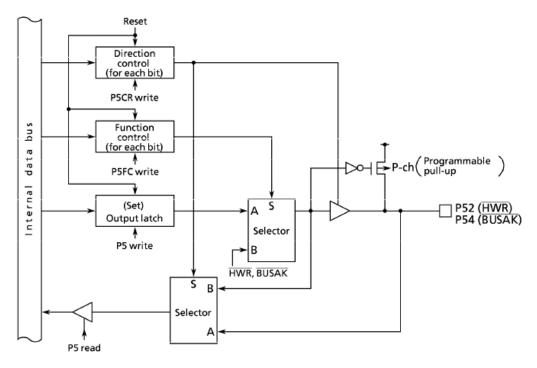

| P52              | 1                 | Input/output | Port 52: I/O port (with built-in pull-up resistor)                  |  |  |  |  |

| / <del>HWR</del> |                   | Output       | Upper write: Outputs strobe signal to write data on pins D8 to D15  |  |  |  |  |

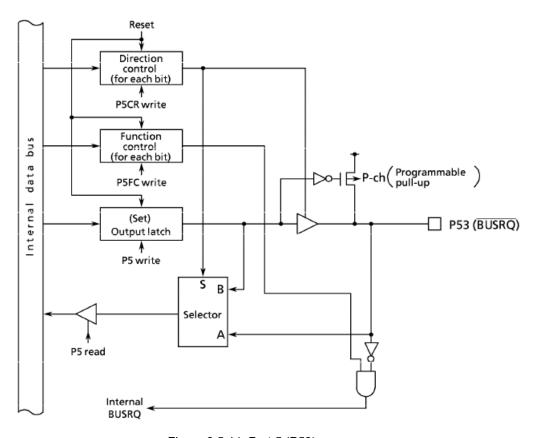

| P53              | 1                 | Input/output | Port 53: I/O port (with built-in pull-up resistor)                  |  |  |  |  |

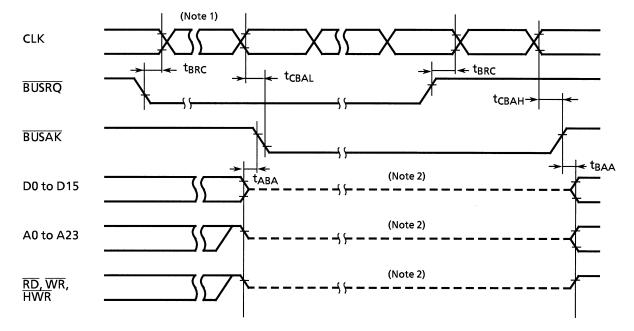

| / BUSRQ          |                   | Input        | Bus request: Input pin to request external bus release              |  |  |  |  |

| P54              | 1                 | Input/output | Port 54: I/O port (with built-in pull-up resistor)                  |  |  |  |  |

| /BUSAK           |                   | Output       | Bus acknowledge: Output pin to acknowledge that CPU received        |  |  |  |  |

|                  |                   |              | BUSRQ and released external bus.                                    |  |  |  |  |

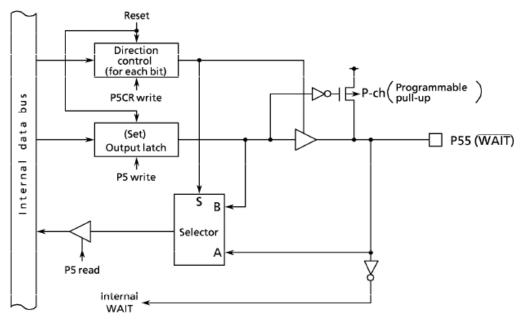

| P55              | 1                 | Input/output | Port 55: I/O port (with built-in pull up resistor)                  |  |  |  |  |

| /WAIT            |                   | Input        | Wait: Bus wait request pin for CPU (Effective when 1 WAIT + N mode, |  |  |  |  |

|                  |                   |              | or 0 + NWAIT mode. Set using bus width/wait control register.)      |  |  |  |  |

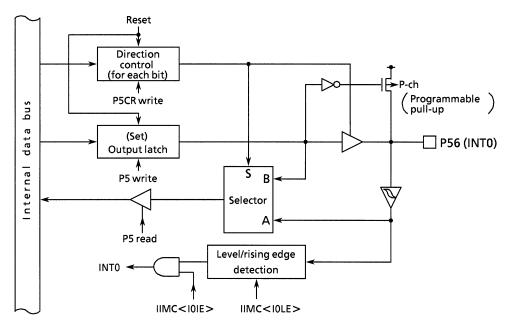

| P56              | 1                 | Input/output | Port 56: I/O port (with built-in pull-up resistor)                  |  |  |  |  |

| /INTO            |                   | Input        | Interrupt request pin 0: Interrupt request pin with programmable    |  |  |  |  |

|                  |                   |              | level/rising edge.                                                  |  |  |  |  |

Table 2.2.1 Pin Names and Functions (2/4)

| Pin Name        | Number<br>of Pins | Input/Output | Function                                                   |

|-----------------|-------------------|--------------|------------------------------------------------------------|

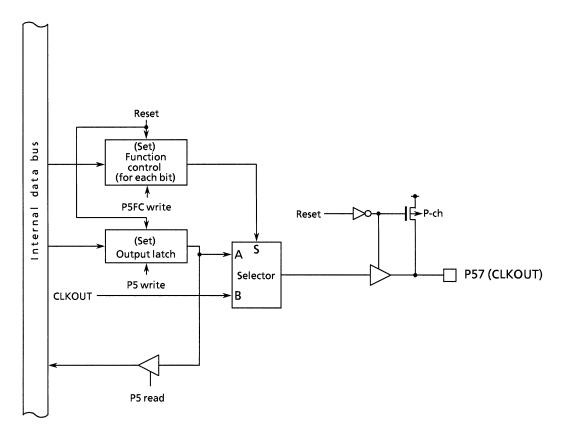

| P57             | 1                 | Output       | Port 57: Output-only port (with built-in pull-up resistor) |

| / CLKOUT        |                   | Output       | CLKOUT output: Outputs external clock divided by 6.        |

|                 |                   |              | Pulled up during reset.                                    |

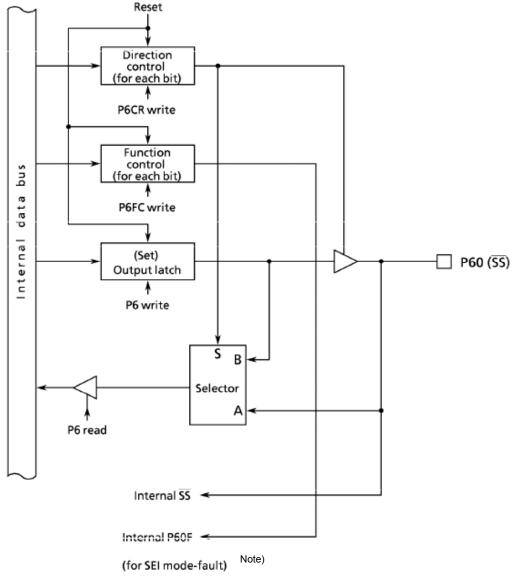

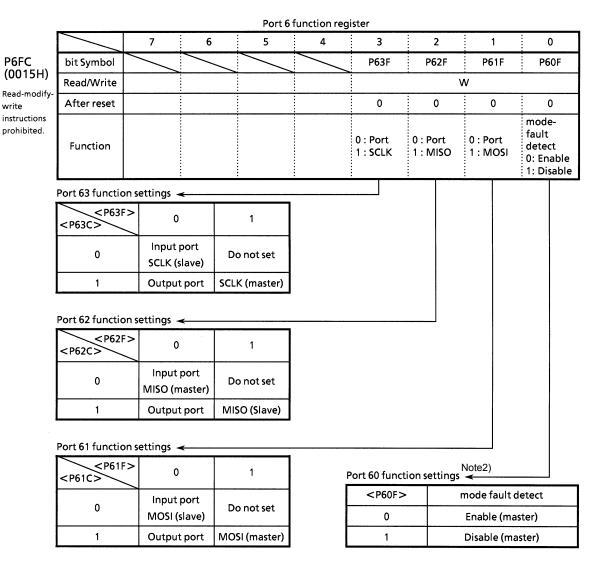

| P60             | 1                 | Input/output | Port 60: I/O port                                          |

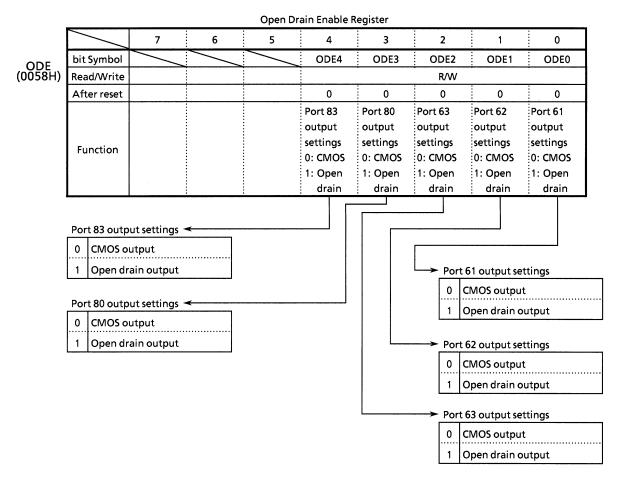

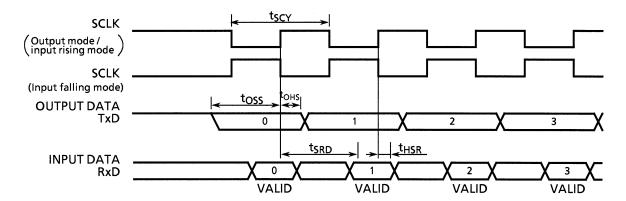

| / <del>SS</del> |                   | Input        | SEI slave select input                                     |

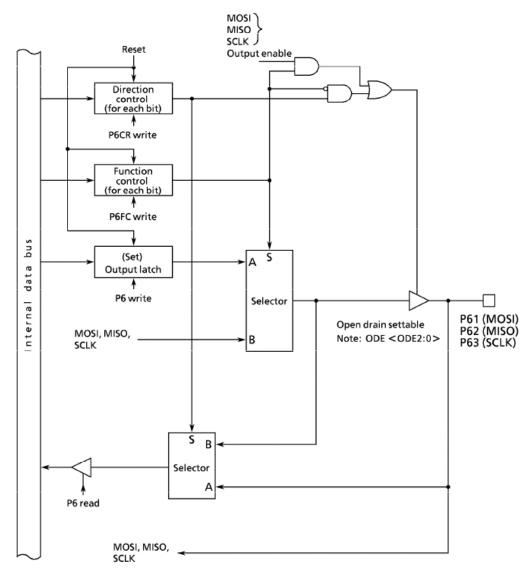

| P61             | 1                 | Input/output | Port 61: I/O port                                          |

| / MOSI          |                   | Input/output | SEI master output, slave input                             |

| P62             | 1                 | Input/output | Port 62: I/O port                                          |

| / MISO          |                   | Input/output | SEI master input, slave output                             |

| P63             | 1                 | Input/output | Port 63: I/O port                                          |

| / SCLK          |                   | Input/output | SEI clock input/output                                     |

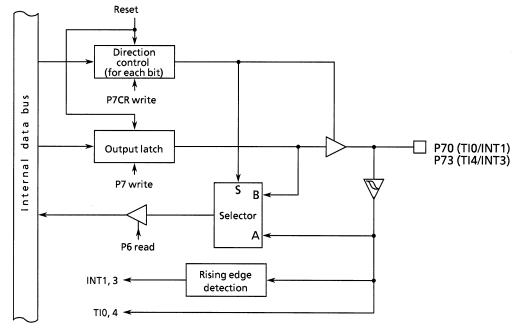

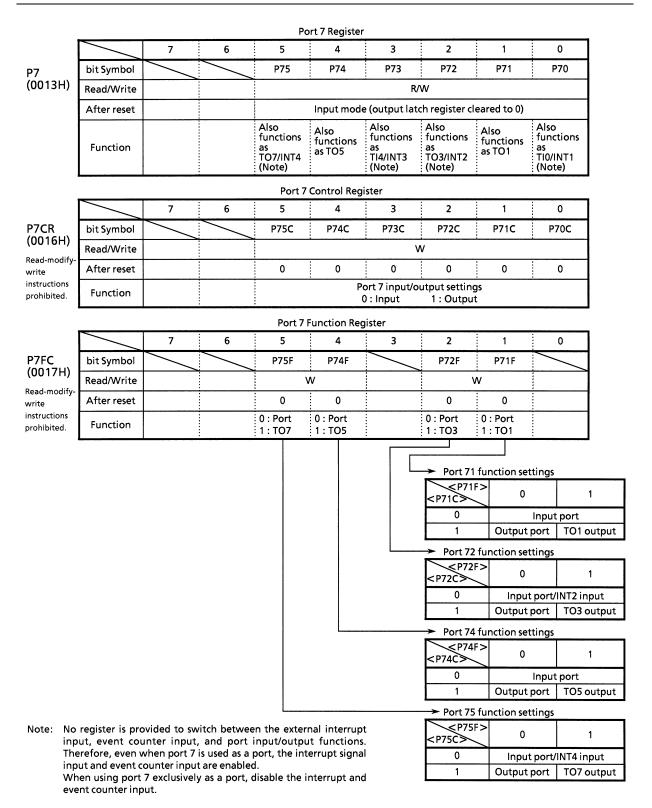

| P70             | 1                 | Input/output | Port 70: I/O port                                          |

| /TI0            |                   | Input        | Timer input 0: Input pin for timer 0                       |

| /INT1           |                   | Input        | Interrupt request pin 1: Rising-edge interrupt request pin |

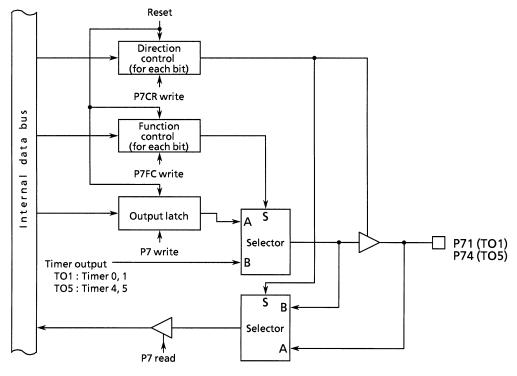

| P71             | 1                 | Input/output | Port 71: I/O port.                                         |

| /TO1            |                   | Output       | Timer output 1: Output pin for timer 0 or 1                |

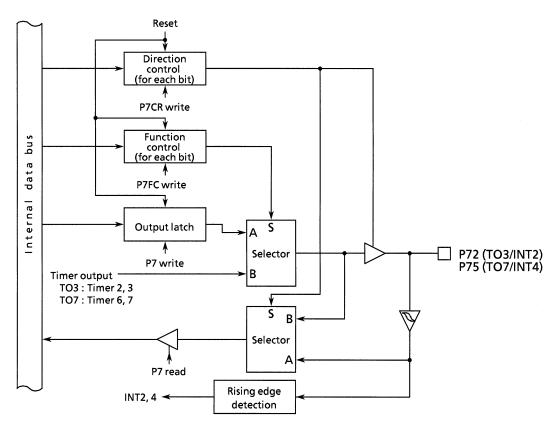

| P72             | 1                 | Input/output | Port 72: I/O port                                          |

| /TO3            | :                 | Output       | Timer output 3: Output pin for timer 2 or 3                |

| /INT2           |                   | Input        | Interrupt request pin 2: Rising-edge interrupt request pin |

| P73             | 1                 | Input/output | Port 73: I/O port                                          |

| /TI4            |                   | Input        | Timer input 4: Input pin for timer 4                       |

| /INT3           |                   | Input        | Interrupt request pin 3: Rising-edge interrupt request pin |

| P74             | 1                 | Input/output | Port 74: I/O port                                          |

| /TO5            |                   | Output       | Timer output 5: Output pin for timer 4 or 5                |

| P75             | 1                 | Input/output | Port 75: I/O port                                          |

| /TO7            |                   | Output       | Timer output 7: Output pin for timer 6 or 7                |

| /INT4           |                   | Input        | Interrupt request pin 4: Rising-edge interrupt request pin |

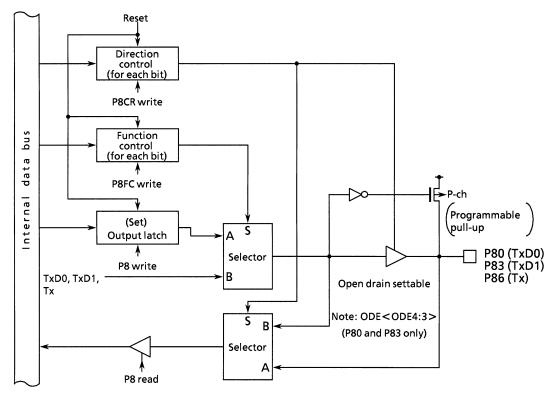

| P80             | 1                 | Input/output | Port 80: I/O port (with built-in pull-up resistor)         |

| /TxD0           |                   | Output       | Serial transmission data 0                                 |

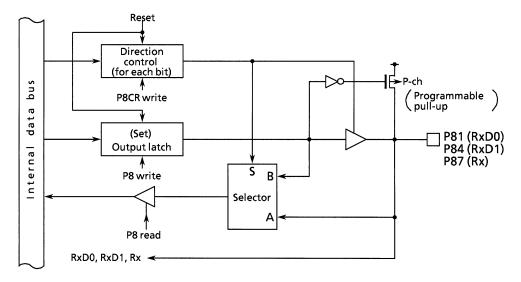

| P81             | 1                 | Input/output | Port 81: I/O port (with built-in pull-up resistor)         |

| /RxD0           |                   | Input        | Serial receive data 0                                      |

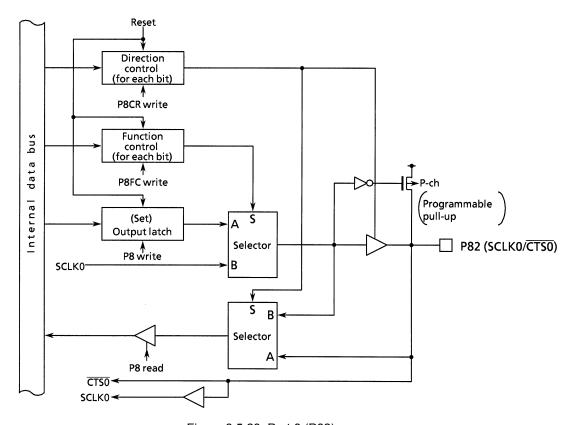

| P82             | 1                 | Input/output | Port 82: I/O port (with built-in pull-up resistor)         |

| /SCLK0          |                   | Input/output | Serial clock input/output 0                                |

| / CTSO          |                   | Input        | Serial data ready to send 0 (Clear-to-send)                |

Table 2.2.1 Pin Names and Functions (3/4)

| Pin Name    | Number<br>of Pins | Input/Output | Function                                                                             |  |  |  |  |

|-------------|-------------------|--------------|--------------------------------------------------------------------------------------|--|--|--|--|

| P83         | 1                 | Input/output | Port 83: I/O port (with built-in pull-up resistor)                                   |  |  |  |  |

| /TxD1       |                   | Output       | Serial transmission data 1                                                           |  |  |  |  |

| P84         | 1                 | Input/output | Port 84: I/O port (with built-in pull-up resistor)                                   |  |  |  |  |

| /RxD1       |                   | Input        | Serial receive data 1                                                                |  |  |  |  |

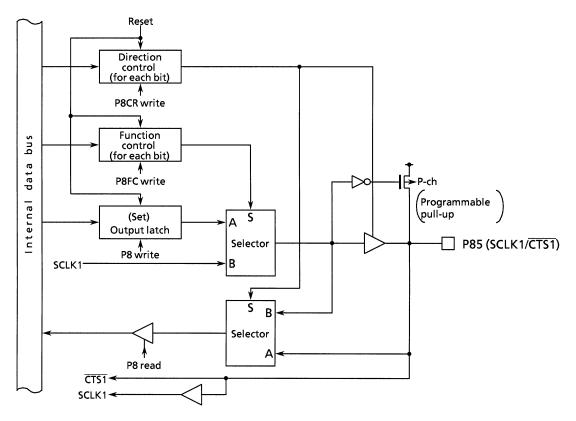

| P85         | 1                 | Input/output | Port 85: I/O port (with built-in pull-up resistor)                                   |  |  |  |  |

| /SCLK1      |                   | Input/output | Serial clock input/output 1                                                          |  |  |  |  |

| / CTS1      |                   | Input        | Serial data ready to send 1 (Clear-to-send)                                          |  |  |  |  |

| P86         | 1                 | Input/output | Port 86: I/O port (with built-in pull-up resistor)                                   |  |  |  |  |

| /Tx         |                   | Output       | CAN transmission data                                                                |  |  |  |  |

| P87         | 1                 | Input/output | Port 87: I/O port (with built-in pull-up resistor)                                   |  |  |  |  |

| /Rx         |                   | Input        | CAN receive data                                                                     |  |  |  |  |

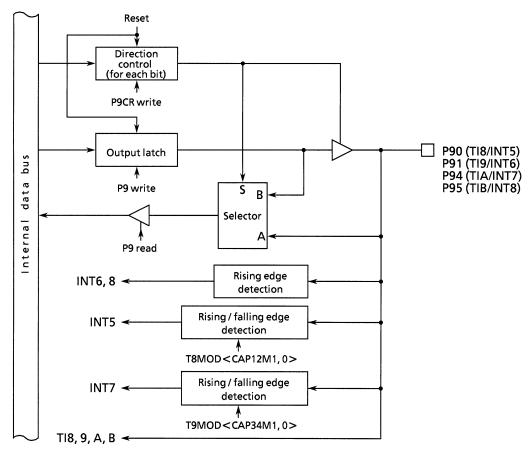

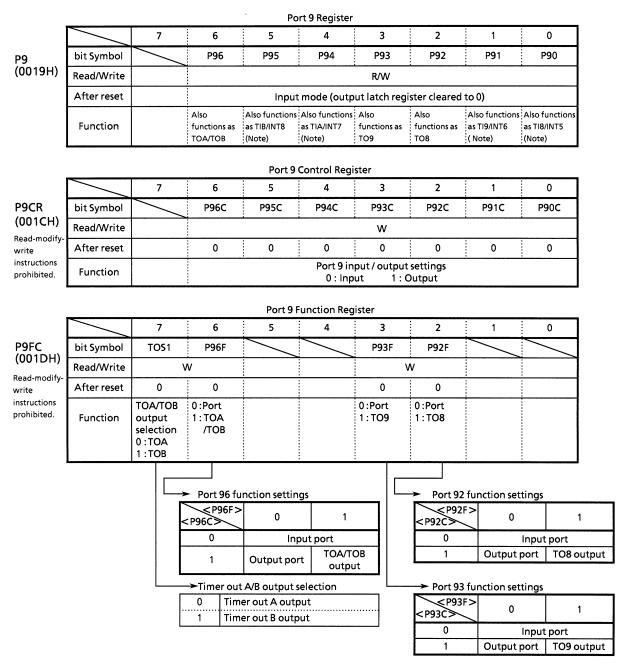

| P90         | 1                 | Input/output | Port 90: I/O port                                                                    |  |  |  |  |

| /TI8        |                   | Input        | Timer input 8: Input pin for timer 8                                                 |  |  |  |  |

| /INT5       |                   | Input        | Interrupt request pin 5: Interrupt request pin with programmable                     |  |  |  |  |

|             |                   |              | rising/falling edge                                                                  |  |  |  |  |

| P91         | 1                 | Input/output | Port 91: I/O port                                                                    |  |  |  |  |

| /TI9        |                   | Input        | Timer input 9: Input pin for timer 8                                                 |  |  |  |  |

| /INT6       |                   | Input        | Interrupt request pin 6: Rising edge interrupt request pin                           |  |  |  |  |

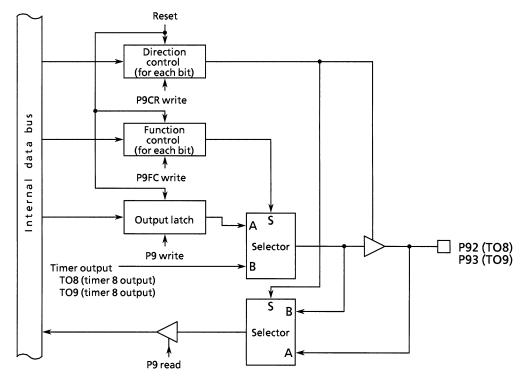

| P92         | 1                 | Input/output | Port 92: I/O port                                                                    |  |  |  |  |

| /TO8        |                   | Output       | Timer output 8: Output pin for timer 8                                               |  |  |  |  |

| P93         | 1                 | Input/output | Port 93: I/O port                                                                    |  |  |  |  |

| /TO9        |                   | Output       | Timer output 9: Output pin for timer 8                                               |  |  |  |  |

| P94         | 1                 | Input/output | Port 94: I/O port                                                                    |  |  |  |  |

| /TIA        |                   | Input        | Timer input A: Input pin for timer 9                                                 |  |  |  |  |

| /INT7       |                   | Input        | Interrupt request pin 7: Interrupt request pin with programmable rising/falling edge |  |  |  |  |

| P95         | 1                 | Input/output | Port 95: I/O port                                                                    |  |  |  |  |

| /TIB        |                   | Input        | Timer input B: Input pin for timer 9                                                 |  |  |  |  |

| /INT8       |                   | Input        | Interrupt request pin 8: Rising edge interrupt request pin                           |  |  |  |  |

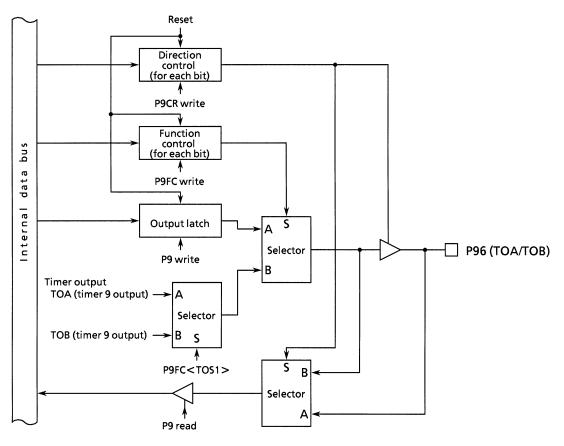

| P96         | 1                 | Input/output | Port 96: I/O port                                                                    |  |  |  |  |

| /TOA        |                   | Output       | Timer output A: Output pin for timer 9                                               |  |  |  |  |

| /TOB        |                   | Output       | Timer output B: Output pin for timer 9                                               |  |  |  |  |

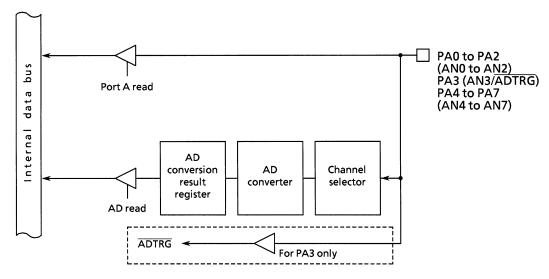

| PA0 to PA2  | 3                 | Input        | Port A0 to A2: Input-only port                                                       |  |  |  |  |

| /AN0 to AN2 |                   | Input        | Analog input 0 to 2: AD converter input pins                                         |  |  |  |  |

| PA3         | 1                 | Input        | Port A3: Input-only port                                                             |  |  |  |  |

| /AN3        |                   | Input        | Analog input 3: AD converter input pin                                               |  |  |  |  |

| / ADTRG     |                   | Input        | External start trigger                                                               |  |  |  |  |

Table 2.2.1 Pin Names and Functions (4/4)

| Pin Name           | Number<br>of Pins | Input/Output | Function                                                          |

|--------------------|-------------------|--------------|-------------------------------------------------------------------|

| PA4 to PA7         | 4                 | Input        | Port A4 to A7: Input-only port                                    |

| / AN4 to AN7       |                   | Input        | Analog input 4 to 7: AD converter input pins                      |

| ЙМÏ                | 1                 | Input        | Non-maskable interrupt request pin: Interrupt request pin with    |

|                    |                   |              | programmable falling edge or both falling and rising edge         |

| CLK                | 1                 | Output       | Clock output: Outputs external clock divided by 4.                |

|                    |                   |              | Pulled up during reset.                                           |

| ĒĀ                 | 1                 | Input        | External access: Connect to VCC.                                  |

| AM8/ <del>16</del> | 1                 | Input        | Address mode: External data bus width select pin                  |

|                    |                   |              | Connect this pin to VCC. Data bus width at external access can be |

|                    |                   |              | set by bus width/wait control register.                           |

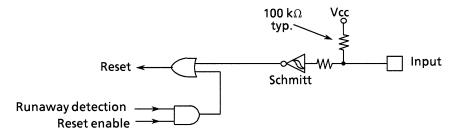

| RESET              | 1                 | Input        | Reset: Initializes TMP95CS54 (with built-in pull-up resistor)     |

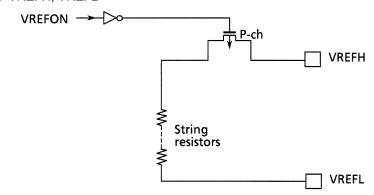

| VREFH              | 1                 | Input        | Reference voltage input pin for AD converter (high)               |

| VREFL              | 1                 | Input        | Reference voltage input pin for AD converter (low)                |

| AVCC               | 1                 |              | Power supply pin for AD converter: Connect to power supply        |

| AVSS               | 1                 |              | GND pin for AD converter: Connect to GND                          |

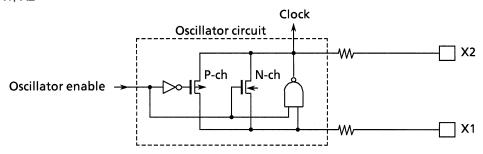

| X1/X2              | 2                 | Input/output | Oscillator connecting pin                                         |

| VCC                | 3                 |              | Power supply pin: Connect all VCC pins to power supply            |

| VSS                | 5                 |              | GND pin: Connect all VSS pins to GND (0 V)                        |

Note: Disconnect the pull-up resistors from pins other than  $\overline{\text{RESET}}$  pin by software.

P57 and CLK pin are pulled-up only during reset.

## 3. Operation

The following is a block-by-block description of the functions and basic operation of the TMP95CS54.

Notes and restrictions for each block are outlined in "7, Use Precautions and Restrictions" at the end of this manual.

## 3.1 CPU

TMP95CS54 incorporates a high-performance 16-bit CPU (900/H-CPU). For CPU operation, see the section dealing with the TLCS-900/H CPU.

The following describes the unique functions of the CPU used in the TMP95CS54; these functions are not covered in the TLCS-900/H CPU section.

#### 3.1.1 Reset

When resetting the TMP95CS54 microcontroller, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the RESET input to low level for at least 10 system clocks (ten states: 0.83 µs at 24 MHz).

When the reset is accepted, the CPU:

Sets as follows the program counter (PC) in accordance with the reset vector stored at address FFFF00H - FFFF02H:

```

PC (7:0) ← value at FFFF00H address

PC (15:8) ← value at FFFF01H address

PC (23:16) ← value at FFFF02H address

```

- Sets the stack pointer (XSP) to 100H.

- Sets bits <IFF2:0> of the status register (SR) to 111 (sets the interrupt level mask register to level 7).

- Sets the <MAX> bit of the status register to 1 (MAX mode).

(Note: As this product does not support a MIN mode, do not write 0 to <MAX>.)

- Clears bits <RFP2:0> of the status register to 000 (sets the register bank to 0).

When reset is released, the CPU starts executing instructions in accordance with the program counter settings. CPU internal registers not mentioned above do not change when the reset is released.

When the reset is accepted, the CPU sets internal I/O, ports, and other pins as follows.

- Initializes the internal I/O registers.

- Sets the port pins, including the pins that also act as internal I/O, to general-purpose

input or output port mode.

- Pulls up the CLK pin to high level.

(Note: During reset, do not reduce the external voltage level as this can cause malfunction.)

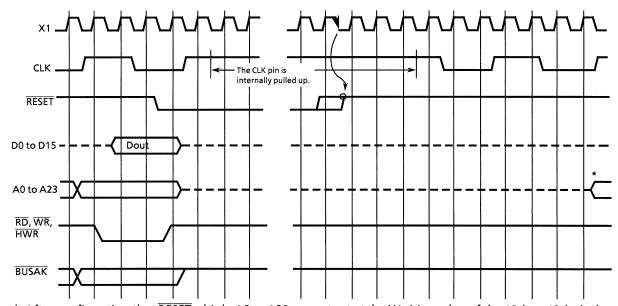

Figure 3.1.1 shows an example of the basic timing of the reset operation.

Figure 3.1.1 TMP95CS54 Reset Timing Example

## 3.1.2 External data bus width selection (AM8/ $\overline{16}$ Pin)

Connect the input pin to VCC. After a reset, this pin accesses ROM by the internal 16-bit bus.

The data bus width for an external access depends on the setting in the <B0BUS>, <B1BUS>, <B2BUS>, <B3BUS> or <BEXBUS> bit of the bus width/wait control registers. To access the 16-bit bus, set port 1 to D8 to D15.

<sup>\*</sup> After confirmation that RESET = high, A0 to A23 are output at the X1 rising edge of the 10th or 12th clock.

## 3.2 Memory Map

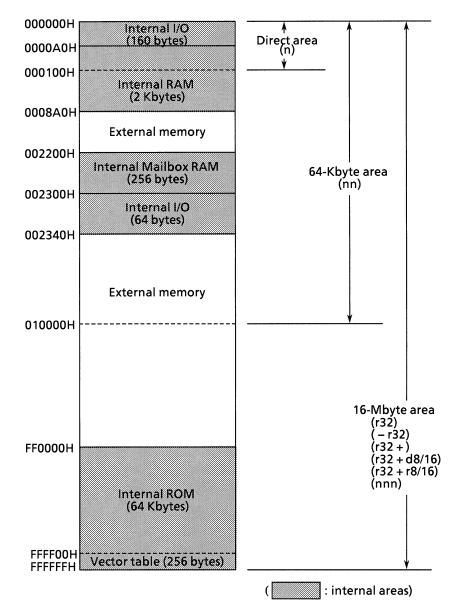

Figure 3.2.1 shows the memory map and the access widths for the CPU addressing modes.

Figure 3.2.1 TMP95CS54 Memory Map

## 3.3 Interrupts

Interrupts are controlled by the CPU interrupt mask register <IFF2:0> (bits 14 to 12 of the status register) and by the built-in interrupt controller.

The TMP95CS54 has a total of 47 interrupts divided into the following five types:

Interrupts generated by CPU: 9

• Software interrupts: 8

• Illegal instruction: 1

Internal interrupts: 28

• Internal I/O interrupts: 24

• Micro DMA transfer end interrupts: 4

External interrupts: 10

• Interrupts from external pins (NMI, INT0 to INT8)

A (fixed) individual interrupt vector number is assigned to each interrupt.

One of seven (variable) priority levels can be assigned to each maskable interrupt. The priority level of non-maskable interrupts is fixed at 7, the highest level.

When an interrupt is generated, the interrupt controller sends the priority of that interrupt to the CPU. If multiple interrupts are generated simultaneously, the interrupt controller sends the interrupt with the highest priority to the CPU. (The highest priority possible is level 7, used for non-maskable interrupts.)

The CPU compares the priority level of the interrupt with the value of the CPU interrupt mask register <IFF2:0>. If the priority level of the interrupt is higher than the value of the interrupt mask register, the CPU accepts the interrupt. However, software interrupts and illegal instruction interrupts generated by the CPU are processed without comparison with the <IFF2:0> value.

The interrupt mask register <IFF2:0> value can be updated using the value of the EI instruction (executing EI num sets the content of <IFF2:0> to num). For example, specifying EI 3 enables the acceptance of maskable interrupts whose priority level set in the interrupt controller is 3 or higher, and enables the acceptance of non-maskable interrupts. However, if EI or EI 0 is specified, maskable interrupts with a priority level of 1 or higher and non-maskable interrupts are accepted (operationally identical to "EI 1").

Operationally, the DI instruction (<IFF2:0> is 7) is identical to the EI 7 instruction, but as the priority level of maskable interrupts is 0 to 6, the DI instruction is used to disable maskable interrupts. The EI instruction is valid immediately after execution begins. (With the TLCS-90, the EI instruction is valid after execution of the instruction following the EI instruction.)

In addition to the general-purpose interrupt processing mode described above, the TLCS-900/H interrupts also have a micro DMA processing mode.

Because the CPU transfers data (byte transfer, word transfer, or 4-byte transfer) automatically in micro DMA mode, this mode can be used for speeding up interrupt processing, such as transferring data to I/O.

The TMP95CS54 also has a micro DMA soft start function for requesting micro DMA processing by software rather than by interrupt.

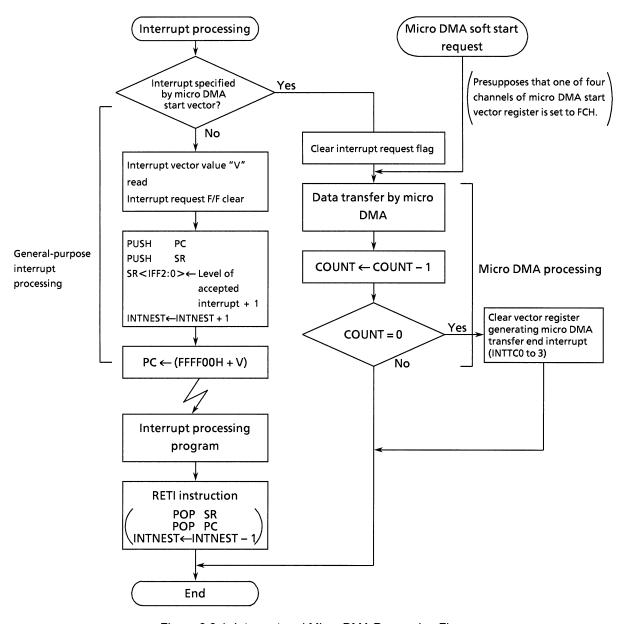

Figure 3.3.1 shows the overall interrupt processing flow.

Figure 3.3.1 Interrupt and Micro DMA Processing Flow

## 3.3.1 General-purpose interrupt processing

When the CPU accepts an interrupt, the CPU performs the following processing. However, in the case of software interrupts and illegal instruction interrupts generated by the CPU, the CPU skips [1] and [3] and executes steps [2], [4], and [5].

- [1] The CPU reads the interrupt vector from the interrupt controller. If there are simultaneous interrupts set to the same level, the interrupt controller generates an interrupt vector in accordance with the default priority and clears the interrupt request.

- (The default priority is already fixed for each interrupt: the smaller the vector value, the higher the priority level.)

- [2] The CPU saves the contents of the program counter (PC) and status register (SR) to the stack area (indicated by XSP).

- [3] The CPU sets the value of the CPU's interrupt mask register <IFF2:0> to the received interrupt level incremented by 1. However, if the incremented value level is 7 or higher, the CPU just sets the register to 7.

- [4] The CPU increments interrupt nesting counter INTNEST by 1.

- [5] The CPU jumps to the address indicated by the data at address FFFF00H + interrupt vector, and starts the interrupt processing routine.

Table 3.3.1 shows the times for the above processing.

| Stack Area Bus<br>Width (Bits) | Interrupt Vector<br>Area Bus Width | Number of Interrupt<br>Processing Execution States | Interrupt Processing<br>Time (µs)<br>@ fc = 24 MHz |

|--------------------------------|------------------------------------|----------------------------------------------------|----------------------------------------------------|

|                                | 8                                  | 28                                                 | 2.33                                               |

| 0                              | 16                                 | 24                                                 | 2.00                                               |

| 16                             | 8                                  | 22                                                 | 1.83                                               |

| 1 10                           | 16                                 | 18                                                 | 1.50                                               |

Table 3.3.1 Interrupt Processing Times for Bus Widths

When the CPU has completed the interrupt processing, use the RETI instruction to return to the main routine. This instruction restores the contents of the program counter and status register from the stack, and decrements interrupt nesting counter INTNEST by 1.

Non-maskable interrupts cannot be disabled by program. Maskable interrupts can be enabled or disabled by program. The program can set a priority level for every interrupt source. (Setting the priority level to 0 (or 7) disables the interrupt request.)

If a request is received for an interrupt with a higher priority level than that set in the CPU interrupt mask register <IFF2:0>, the CPU accepts the interrupt. Set the CPU interrupt mask register <IFF2:0> to the received interrupt priority level incremented by 1.

If, during interrupt processing, an interrupt is generated with a higher level than the interrupt being currently processed, or if, during non-maskable interrupt processing, a non-maskable interrupt request is generated from another source, the CPU suspends the current processing routine and accepts the later interrupt. Then, after the CPU has finished processing the later interrupt, the CPU returns to the interrupt it previously suspended and resumes processing.

If the CPU receives a request for another interrupt while already performing processing steps [1] to [5], the second interrupt is sampled immediately after execution of the start instruction for its interrupt processing routine. Specifying DI as the start instruction disables maskable interrupt nesting. (Note: In the 900 and 900/L, sampling is performed before execution of the start instruction.)

After a reset, the interrupt mask register <IFF2:0> is initialized to 111, thus disabling maskable interrupts.

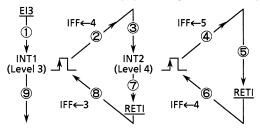

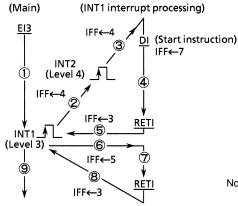

The following steps (1) through (5) show the interrupt processing flow.

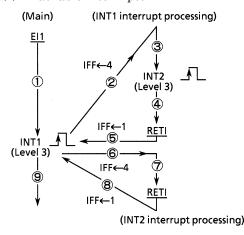

## (1) Maskable interrupts

When the CPU accepts an interrupt, it sets IFF to the priority level of the interrupt incremented by 1.

Accordingly, if during interrupt processing an interrupt request is received with the same or a lower priority than that of the interrupt being processed, because this priority level is lower than the IFF value, the second interrupt cannot be accepted until the processing of the prior interrupt is complete.

Note: \_\_(underline): Instruction

①, ②, : Execution flow

IFF : Interrupt mask register

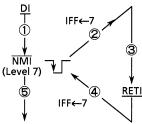

#### (2) Non-maskable interrupts (NMI, INTWD)

(Main) (INT1 interrupt processing)

When the DI instruction is executed (IFF is 7), only non-maskable interrupts can be received (because the priority level of non-maskable interrupts is fixed to 7.)

When the EI instruction is executed, the CPU sets IFF to 7 upon acceptance of an NMI or INTWD interrupt.

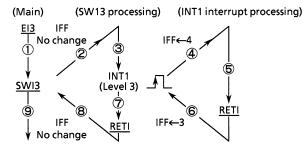

(3) Non-maskable interrupts (Software interrupts, illegal instruction interrupts)

When the DI instruction is executed (IFF is 7), the CPU can accept interrupts. However, unlike with NMI or INTWD interrupts, IFF does not change upon acceptance of an interrupt.

Therefore, during processing of a software interrupt, if a request is received for an interrupt with a priority the same or higher than the IFF value, the interrupt is nested.

## (4) Interrupt nesting

(Main) (INT1 interrupt processing) (INT2 interrupt processing)

During interrupt processing, if a request is received for an interrupt with a priority the same or higher than the interrupt being processed (the interrupt priority level is the same as or higher than the IFF value), the CPU receives the second interrupt and nests it.

## (5) Interrupt sampling (Maskable interrupt nesting disabled)

(INT2 interrupt processing)

If, after the time the CPU has accepted an interrupt but before the CPU begins processing it, the CPU receives a request for another interrupt with a higher priority, the second interrupt is nested after execution of the start instruction for processing of the interrupt accepted first.

Accordingly, issuing the DI instruction as the start instruction disables nesting of maskable interrupts.

Note:\_\_ (underline): Instruction

①, ②, : Execution flow

IFF : Interrupt mask register

Table 3.3.2 shows the TMP95CS54 interrupt vectors and micro DMA start vectors. With the TMP95CS54, FFFF00H to FFFFFFH (256 bytes) is allocated to the interrupt vector area.

Table 3.3.2 TMP95CS54 Interrupt Vectors and Micro DMA Start Vectors

| Default  |          |                                                                       | Vector value | Vector             | Micro DMA    |

|----------|----------|-----------------------------------------------------------------------|--------------|--------------------|--------------|

| priority | Туре     | Interrupt source and source of micro DMA request                      | Vector value | reference          | start vector |

| 1        |          | Reset or [SWI0] instruction                                           | 0 0 0 0 H    | address<br>FFFF00H |              |

| 2        |          | [SWI1] instruction                                                    | 0 0 0 0 H    |                    | _            |

| 3        |          | Illegal instruction or [SWI2] instruction                             | 0008H        |                    |              |

| 4        |          | [SWI3] instruction                                                    | 000CH        |                    | _            |

| 5        | Non-     | [SWI4] instruction                                                    | 0 0 1 0 H    |                    | _            |

| 6        | maskable |                                                                       | 0 0 1 4 H    | 1                  | _            |

| 7        | maskabie | [SWI6] instruction                                                    | 0 0 1 8 H    | 1                  | _            |

| 8        |          | [SWI7] instruction                                                    | 001CH        |                    | _            |

| 9        |          | NMI : NMI pin input                                                   | 0 0 2 0 H    |                    | _            |

| 10       |          | INTWD : Watchdog timer                                                | 0024H        |                    | _            |

| _        | _        | Micro DMA (Note)                                                      | _            | _                  | _            |

| 11       |          | INTO : INTO pin input                                                 | 0028H        | FFFF28H            | 28H          |

| 12       |          | INT1 : INT1 pin input                                                 | 002CH        |                    | 2CH          |

| 13       |          | INT2 : INT2 pin input                                                 | 0030H        |                    | 30H          |

| 14       |          | INT3 : INT3 pin input                                                 | 0034H        | FFFF34H            | 34H          |

| 15       |          | INT4 : INT4 pin input                                                 | 0038H        | FFFF38H            | 38H          |

| 16       |          | INT5 : INT5 pin input                                                 | 003CH        | FFFF3CH            | зсн          |

| 17       |          | INT6 : INT6 pin input                                                 | 0040H        | FFFF40H            | 40H          |

| 18       |          | INT7 : INT7 pin input                                                 | 0044H        | FFFF44H            | 44H          |

| 19       |          | INT8 : INT8 pin input                                                 | 0048H        |                    | 48H          |

| 20       |          | INTTO: 8-bit timer 0                                                  | 004CH        | FFFF4CH            | 4CH          |

| 21       |          | INTT1 : 8-bit timer 1                                                 | 0050H        | FFFF50H            | 50H          |

| 22       |          | INTT2 : 8-bit timer 2                                                 | 0054H        |                    | 54H          |

| 23       |          | INTT3 : 8-bit timer 3                                                 | 0058H        |                    | 58H          |

| - 24     |          | INTT4 : 8-bit timer 4                                                 | 005CH        | FFFF5CH            | 5CH          |

| 25       |          | INTT5 : 8-bit timer 5                                                 | 0060H        |                    | 60H          |

| 26       |          | INTT6 : 8-bit timer 6                                                 | 0064H        |                    | 64H          |

| 27       |          | INTT7 : 8-bit timer 7                                                 | 0068H        |                    | 68H          |

| 28       |          | INTTR8 : 16-bit timer 8 (TREG8)                                       | 006CH        |                    | 6CH          |

| 29       | l        | INTTR9 : 16-bit timer 8 (TREG9)                                       | 0070H        |                    | 70H          |

| 30       | Maskable | INTTRA: 16-bit timer 9 (TREGA)                                        | 0074H        | 1                  | 74H          |

| 31       |          | INTTRB : 16-bit timer 9 (TREGB)                                       | 0078H        |                    | 78H          |

| 32       |          | INTTO8: 16-bit timer 8 (Overflow)                                     | 007CH        |                    | 7CH          |

| 33       |          | INTTO9: 16-bit timer 9 (Overflow)                                     | 0080H        | 1                  | 80H          |

| 34       |          | INTRX0 : Serial receive (Channel 0)                                   | 0 0 8 4 H    |                    | 84H          |

| 35       |          | INTTX0 : Serial transmission (Channel 0)                              | 0088H        | l                  | 88H          |

| 36       |          | INTRX1 : Serial receive (Channel 1)                                   | 0 0 8 C H    |                    | 8CH          |

| 37<br>20 |          | INTTX1 : Serial transmission (Channel 1)                              | 0 0 9 0 H    |                    | 90H          |

| 38<br>39 |          | INTCR : CAN receive                                                   | 0 0 9 4 H    |                    | -            |

| 40       |          | INTCT: CAN global                                                     | 0098H        |                    | -            |

| 40       |          | INTCG : CAN global<br>INTSEI : SEI                                    | 0 0 9 C H    |                    | -            |

| 41       |          | INTAD : AD conversion end                                             |              | FFFFAOH            | -            |

| 42<br>43 |          | INTED: AD conversion end INTTCO: Micro DMA end (Channel 0)            |              | FFFFA4H            | A4H          |

| 43<br>44 |          |                                                                       |              | FFFFA8H            | -            |

| 44<br>45 |          | INTTC1 : Micro DMA end (Channel 1) INTTC2 : Micro DMA end (Channel 2) |              | FFFFACH            | -            |

| 45<br>46 |          | INTTC2: Micro DMA end (Channel 2)                                     | 0 0 B 0 H    |                    | -            |

| 40       |          | (Reserved)                                                            | 0 0 B 4 H    |                    | -            |

| -<br>+0  |          | to                                                                    | 00B8H        | FFFFB8H            |              |

| to       |          | (Reserved)                                                            | to           | to                 | to           |

|          | _        | Micro DMA soft start request                                          | UUFCH        | FFFFCH             | - FC!!       |

|          |          | where Divin soft start request                                        |              |                    | FCH          |

Note: Micro DMA default priority

If an interrupt request is generated by a source specified by micro DMA, the interrupt has the highest priority of the maskable interrupts (irrespective of the default priority allocated to all channels).

## Setting reset vectors and interrupt vectors

[1] Reset vector

XX: Don't care

[2] Interrupt vectors (Other than reset vector)

XX : Don't care

## (Setting example)

Where the reset vector is defined as FF0000H, the NMI vector as FF9ABCH, and the INT1 vector as FF3456H  $\,$

| ORG   | 0FF0000H         |                                        |

|-------|------------------|----------------------------------------|

| LD    | A, B             | Reference:                             |

|       |                  | ORG and DL are assembler directives    |

| ORG : | 0FF9ABCH         | ORG: For location counter control      |

| LD    | В, С             | DL : To define (32-bit) long word data |

|       |                  |                                        |

| ORG   | 0FF3456H         |                                        |

| LD    | C, A             |                                        |

|       |                  |                                        |

| ORG   | OFFFF00H         |                                        |

| DL    | <u>0FF0000</u> H | ; reset vector = FF0000H               |

|       |                  |                                        |

| ORG   | 0FFFF20H         |                                        |

| DL    | <u>0FF9ABC</u> H | ; NMI vector = FF9ABCH                 |

|       |                  |                                        |

| ORG   | 0FFFF2CH         |                                        |

| DL    | <u>0FF3456</u> H | ; INT1 vector = FF3456H                |

#### 3.3.2 Micro DMA processing

In addition to general-purpose interrupt processing, the TMP95CS54 supports a micro DMA function. Interrupt requests set by the micro DMA perform micro DMA processing at the highest priority level of maskable interrupts (level 6), regardless of the priority level of the particular interrupt source.

Because the micro DMA function is implemented with the cooperative operation of the CPU, when the CPU is put into stand-by state -by by HALT instruction, micro DMA requirements will be ignored (pending).

#### (1) Micro DMA Operation

When an interrupt request is generated by an interrupt source specified by the micro DMA start vector register, the micro DMA triggers a micro DMA request to the CPU at interrupt priority level 6 and starts processing the request. The four micro DMA channels allow micro DMA processing to be set for up to four types of interrupts at any one time.

When micro DMA is accepted, the interrupt request flip-flop assigned to that channel is cleared. The data are automatically transferred from the transfer source address to the transfer destination address set in the control register, and the transfer counter is decremented by 1. If the decremented counter reads other than 0, DMA processing ends with no change in the value of the micro DMA start vector register. If the decremented reading is 0, the micro DMA transfer end interrupt (INTTC0 to 3) passes from the CPU to the interrupt controller. In addition, the micro DMA start vector register is cleared to 0, the next micro DMA is disabled, and micro DMA processing is complete.

If a micro DMA request is set for more than one channel at a time, the priority is not based on the interrupt priority level but on the channel number: the smaller the channel number the higher the priority. (Channel 0 (high) --> channel 3 (low)).

If an interrupt request is triggered for the interrupt source in use during the interval between the clearing of the micro DMA start vector and the next setting, general-purpose interrupt processing is executed at the interrupt level set. Therefore, when using the interrupt only for starting the micro DMA (not using the interrupt as a general-purpose interrupt), first set the interrupt level to 0 (interrupt requests disabled).

When using micro DMA and general-purpose interrupts together as described above, first set the level of the interrupt used to start micro DMA processing lower than all the other interrupt levels. In this case, the cause of a general interrupt is limited to the edge interrupt.

Example: When using external interrupt INT0 to 3 to start micro DMA0 to 3, set:

External interrupt INT0 to 3 interrupt level ....."1"

Level of other interrupts......."2" to "6"

As with other maskable interrupts, the priority of the micro DMA transfer end interrupt is determined by the interrupt level and the default priority.

While the register for setting the transfer source/transfer destination addresses is a 32-bit control register, this register can only effectively output 24-bit addresses. Accordingly, micro DMA can access 16 Mbytes (the upper eight bits of the 32 bits are not valid).

Three micro DMA transfer modes are supported: 1-byte transfer, 2-byte (one word) transfer, and 4-byte transfer. After a transfer in any mode, the transfer source/destination addresses are incremented, decremented, or remain unchanged. This simplifies the transfer of data from I/O to memory, from memory to I/O, and from I/O to I/O. For details of the transfer modes, see 3.3.2 (4), Transfer Mode Register.

As the transfer counter is a 16-bit counter, micro DMA processing can be set for up to 65536 times per interrupt source. (The micro DMA processing count is maximized when the transfer counter initial value is set to 0000H.)

Micro DMA processing can be started by the 28 interrupts (INT0 to INTTX1, INTAD) shown in the micro DMA start vectors of Table 3.3.2 and by the micro DMA soft start, making a total of 29 interrupts.

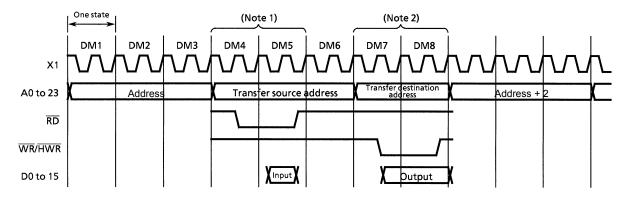

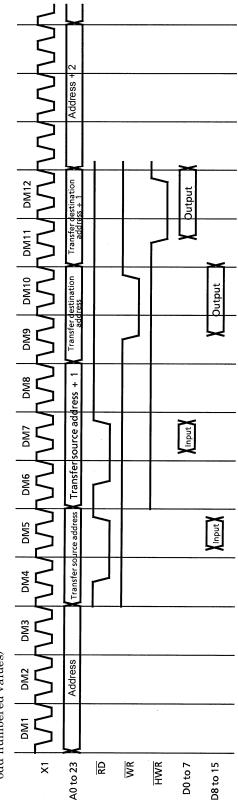

Figure 3.3.2 shows the micro DMA cycle in transfer destination address INC mode (the same as for other modes, with the exception of COUNTER mode).

[1] Word transfer (the conditions for this cycle are based on an external 16-bit bus, 0 waits, transfer source/transfer destination addresses both even-numbered values)

Figure 3.3.2 Timing of Micro DMA Cycle (1/3)

States 1 to 3 : Instruction fetch cycle (gets next address code).

If three or more instruction codes are inserted in the instruction queue buffer, this cycle

becomes a dummy cycle.

States 4 to 5 : Micro DMA read cycle

State 6 : Dummy cycle (the address bus remains as in state 5)

States 7 to 8 : Micro DMA write cycle

Note 1: If the source address area is an 8-bit bus, it is incremented by two states.

Note 2: If the destination address area is an 8-bit bus, it is incremented by two states.

Word transfer (the conditions for this cycle are based on a 16-bit external bus, 0 waits, transfer source/transfer destination addresses both odd-numbered values) <u>2</u>

Figure 3.3.2 Timing of Micro DMA Cycle (2/3)

[3] 4-byte transfer (the conditions for this cycle are based on a 16-bit external bus, 0 waits, transfer source/transfer destination addresses both even-numbered values

Figure 3.3.2 Timing of Micro DMA Cycle (3/3)

#### (2) Micro DMA soft start function

In addition to starting micro DMA by interrupt, the TMP95CS54 supports a micro DMA soft start function. This starts micro DMA by generating a cycle to write to the soft DMA control register.

To code a soft start, write micro DMA start vector FCH to micro DMA start vector register DMA0V to 3 V (at memory addresses 5AH, 5BH, 5CH, and 5DH).

Then, write any data to soft DMA control register SDMACR0 to 3 (at memory addresses 6AH, 6BH, 6CH, and 6DH). (The value of the data has no effect on the operation of the soft start.) This starts micro DMA of the applicable channel once. Then, whenever data are written again to the soft DMA control register, as long as the micro DMA transfer counter register values are other than 0, a soft start can be continuously triggered (without rewriting the micro DMA start vector).

Setting the micro DMA start vector is a prerequisite for generating a micro DMA software start. (The software start request is a one-shot request and not saved. Therefore, even if a cycle which writes to the soft DMA control register is generated, unless the micro DMA start vector is already set, a soft start cannot be generated.)

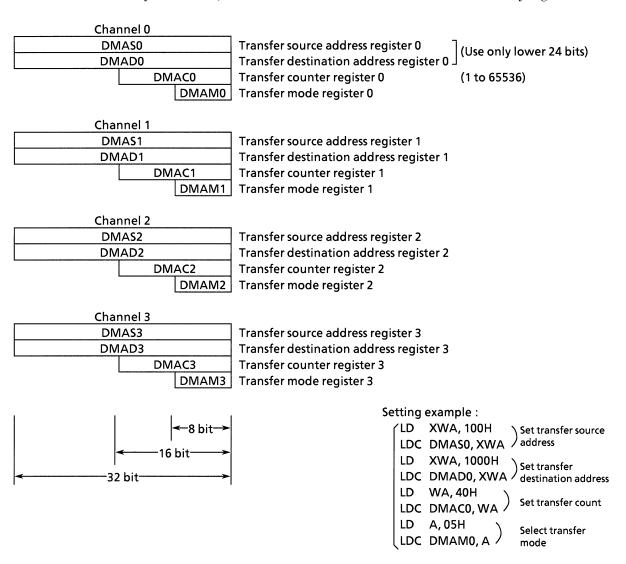

#### (3) Structure of micro DMA-only registers

Figure 3.3.3 shows the micro DMA-only registers. These registers are incorporated in the CPU. (See 3.2.5, Control Registers in Chapter 3, TLCS-900/H CPU.) To set the registers use the LDC instruction.

Set the transfer source address in the transfer source address register; the transfer destination address, in the transfer destination address register. These address registers use only the lower 24 bits. They support a 16-Mbyte address space.

Use the transfer counter register to set the number of times micro DMA is performed between 1 and 65536.

For details on setting the transfer mode register, see 3.3.2 (4), Transfer Mode Register. Only the LDC cr, r instruction can load data into the micro DMA-only registers.

Figure 3.3.3 Micro DMA-Only Registers

## (4) Transfer Mode Register

To set micro DMA transfer mode, use transfer mode register DMAM0 to 3. Table 3.3.3 shows the settings for each mode and the numbers of execution states.

Table 3.3.3 Micro DMA Transfer Mode

DMAM0 to 3 0 0 0 Mode

Note: When setting a value in this register, write 0 to the upper three bits.

| $\overline{}$  |        |                          |                             |                                                         |                                      | T - 27 Y                                   |  |

|----------------|--------|--------------------------|-----------------------------|---------------------------------------------------------|--------------------------------------|--------------------------------------------|--|

|                | ····   |                          | Number of<br>Transfer Bytes | Mode Description                                        | Number of<br>Execution States<br>(*) | Minimum<br>Execution Time<br>@ fc = 24 MHz |  |

| 000<br>(Fixed) |        |                          | Byte transfer               | Transfer destination address INC mode For I/O to memory | 8 states                             | 667                                        |  |

|                | 01     | 01                       | Word transfer               | (DMADn+)←(DMASn)<br>DMACn←DMACn-1                       | o states                             | 667 ns                                     |  |

|                |        | 10                       | 4-byte transfer             | If DMACn = 0, then INTTCn generated                     | 12 states                            | 1000 ns                                    |  |

|                | 001    | 00                       | Byte transfer               | Transfer destination address DEC mode For I/O to memory | 8 states                             | 667 ns                                     |  |

|                |        | 01                       | Word transfer               | (DMADn – ) ← (DMASn)  DMACn←DMACn – 1                   | o states                             | 007 115                                    |  |

|                |        | 10                       | 4-byte transfer             | If DMACn = 0, then INTTCn generated                     | 12 states                            | 1000 ns                                    |  |

|                | 010 00 |                          | Byte transfer               | Transfer source address INC mode For memory to I/O      | 8 states                             | 667 ns                                     |  |

|                | 10     | 01                       | Word transfer               | (DMADn) ← (DMASn + )<br>DMACn←DMACn – 1                 |                                      |                                            |  |

|                |        | 10                       | 4-byte transfer             | If DMACn = 0, then INTTCn generated                     | 12 states                            | 1000 ns                                    |  |

|                | 011    | UU   Byte transfer   ''a |                             | Transfer source address DEC mode For memory to I/O      | 8 states                             | 667 ns                                     |  |

|                | 0      |                          | Word transfer               | (DMADn) ← (DMASn − )<br>DMACn←DMACn − 1                 |                                      | 007 113                                    |  |

|                |        | 10                       | 4-byte transfer             | If DMACn = 0, then INTTCn generated                     | 12 states                            | 1000 ns                                    |  |

|                | 100    | 00                       | Byte transfer               | Address fixed mode For I/O to I/O                       | 8 states                             | 667 ns                                     |  |

|                |        | 01                       | Word transfer               | (DMADn) ← (DMASn)<br>DMACn←DMACn – 1                    | o states                             | 007 115                                    |  |

|                |        | 10                       | 4-byte transfer             | If DMACn = 0, then INTTCn generated                     | 12 states                            | 1000 ns                                    |  |

| 101 00         |        |                          | DMASn←DMASn<br>DMACn←DMACr  |                                                         | 5 states                             | 417 ns                                     |  |

<sup>\*</sup> For external 16-bit bus, 0 waits, word/4-byte transfer mode, transfer source/transfer destination addresses both have even-numbered values.

Note: n: Corresponding micro DMA channels 0 to 3

DMADn +/DMASn + : Post increment (increments register value after transfer)

DMADn -/ DMASn- : Post decrement (decrements register value after transfer)

The I/Os in the table mean fixed addresses; memory means incremented and decremented addresses.

Do not use undefined code, that is, codes other than those listed above for the transfer mode register.

95CS54-24

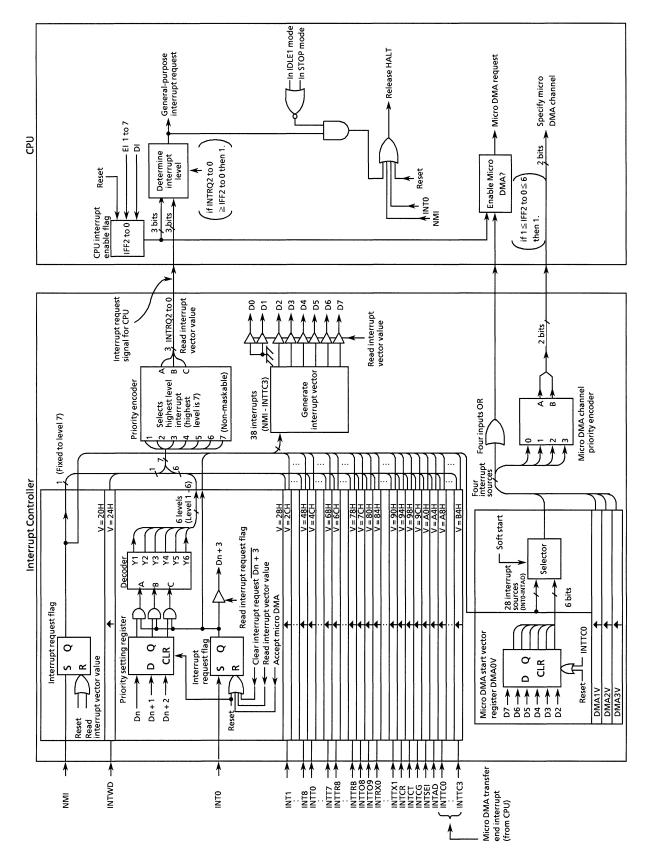

## 3.3.3 Interrupt Controller Control

Figure 3.3.4 is a block diagram of the interrupt controller circuit. The left-hand side of this diagram shows the interrupt controller. The right-hand side shows the CPU interrupt request signal circuit and CPU halt release circuit. (For details on halt modes, see 3.4, Standby Function.)

The interrupt controller has a total of 38 interrupt channels, consisting of NMI, INTWD, INTO to 8, INTTO to 7, INTTR8 to O9, INTRX0 to TX1, INTCR to G, INTSEI, INTAD, and INTTC0 to 3.

Each interrupt channel supports:

- Interrupt request flag (38 channels)

- Interrupt priority setting register (36 channels (NMI and INTWD excluded)).

In addition, there are also four channels of start vector registers for performing micro DMA processing.

#### (1) Interrupt request flags

The function of the interrupt request flag is to indicate the generation of an interrupt request. Apart from NMI and INTWD, each channel has a clear bit <IxxC> for clearing the interrupt requests (see Figure 3.3.5, Interrupt Priority Setting Registers). Reading clear bit <IxxC> reads the state of the interrupt request flag and indicates whether an interrupt request is generated or not.

The interrupt request flags are zero-cleared by the following operations:

- [1] A reset (clears all interrupt request flags)

- [2] When the CPU accepts an interrupt and reads the vector of the accepted interrupt channel

- [3] When the CPU accepts the micro DMA request of the specified channel

- [4] When 0 is written to clear bit <IxxC> of the interrupt priority setting register Note: [2], [3], and [4] operations do not include INTO level mode or INTRX0, 1.

In addition, flags are also cleared by the following operations.

Table 3.3.4 Other Flag Clearing Operations

Before clearing an interrupt request by writing 0 to the clear bit or by performing a Table 3.3.4 operation to clear the interrupt request flag, first execute the DI instruction.

(INT0 interrupt cautions)

Note the following cautions when using the INT0 interrupt in level mode.

In level mode, the INT0 pin input must be held continuously at high level until the interrupt response sequence is completed. Likewise, when releasing the halt in this mode, the INT0 pin must be held continuously at high level until the halt is released.

When using INTO level mode, be sure that a low level is not input as a result of noise as this can cause malfunction.

When switching the INTO pin operation mode from level to edge mode, first disable the INTO interrupt as follows. (In level mode, an accepted interrupt request must be cleared.)

Setting example:

DI ; disable interrupt

LD (IIMC), XX0XXX0XB ; switch from level to edge

LD (INTE0AD), XXXX0nnnB; clear interrupt request flag and set INT0

interrupt level to nnn

EI ; enable interrupt

95CS54-26 2005-05-10

Figure 3.3.4 Block Diagram of Interrupt Controller

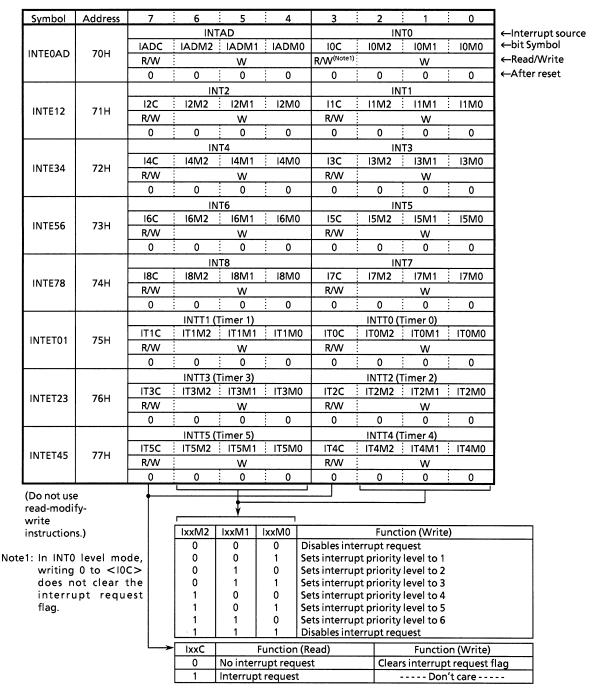

#### (2) Interrupt priority setting register

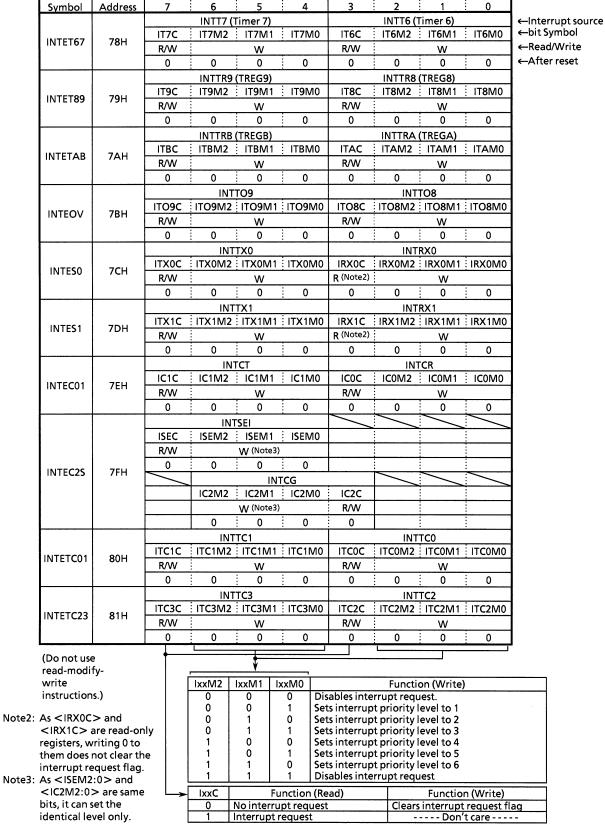

Figure 3.3.5 shows the interrupt priority setting registers. Each of the 36 interrupt channels (INT0 to AD, INTTC0 to 3) has an interrupt request level setting bit  $\langle IxxM2:0 \rangle$ . An interrupt request is generated at six interrupt levels (levels 1 through 6). Setting the priority level to 0 (or 7) disables the corresponding interrupt request. The priority level for non-maskable interrupts ( $\overline{NMI}$  pin input) is fixed to 7. If two or more interrupts with the same level occur simultaneously, the interrupts are accepted in accordance with the default priority.

Figure 3.3.5 Interrupt Priority Setting Registers (1/2)

2005-05-10

Figure 3.3.5 Interrupt Priority Setting Registers (2/2)

From among simultaneous interrupts, the interrupt controller selects the interrupt request with the highest level and sends its vector address to the CPU.

Then, the CPU compares the priority level of the interrupt request with the value of the interrupt mask register <IFF2:0> in the status register. If the priority level of the interrupt request is higher than the value of the interrupt mask register, the CPU accepts the interrupt. When the CPU side interrupt mask register <IFF2:0> is set to the priority level of the received interrupt incremented by 1, subsequent interrupt requests are only accepted if their level is equal to or greater than the incremented value.

#### (3) Micro DMA start vector

The interrupt controller has four channels of micro DMA start vector registers. Writing the micro DMA start vector value (Table 3.3.2) for each interrupt source to these registers makes the applicable interrupt request into a micro DMA request. But first set values in the registers for micro DMA parameters (DMAS, DMAD, DMAC, DMAM). Figure 3.3.6 shows the micro DMA start vector registers.

The function of the micro DMA start vector registers is to select the interrupt to use with micro DMA processing. The micro DMA start source is assigned to the interrupt source whose micro DMA start vector matches the vector value set in the micro DMA start vector register.

When the value of the micro DMA transfer counter is set to 0 after micro DMA processing, the CPU generates a micro DMA transfer end interrupt (INTTC0 to 3) corresponding to the micro DMA start vector register. When the micro DMA start vector register is cleared, the micro DMA startup source is released. Therefore, when continuously performing micro DMA processing, set the start vector value in the micro DMA start vector register again during processing of the micro DMA transfer end interrupt.

When the same vector is set in the micro DMA start vector registers of multiple channels, the lower the channel number the higher the priority.

The channel with the lowest number is executed until the micro DMA transfer end interrupt. Unless the micro DMA start vector is set again during the processing of the micro DMA transfer end interrupt, the subsequent micro DMA startup moves to the next smallest channel number. (This operation is called a micro DMA chain.)

#### Micro DMA0 start vector register

DMA0V (005AH) (Do not use read-modifywrite instructions.)

|             | 7           | 6                                                  | 5      | 4      | 3      | 2      | 1 | 0 |

|-------------|-------------|----------------------------------------------------|--------|--------|--------|--------|---|---|

| bit Symbol  | DMA0V7      | DMA0V6                                             | DMA0V5 | DMA0V4 | DMA0V3 | DMA0V2 |   |   |

| Read/Write  |             | W                                                  |        |        |        |        |   |   |

| After reset | 0           | 0                                                  | 0      | 0      | 0      | 0      |   |   |

| Function    | Set startup | t startup interrupt source for micro DMA channel 0 |        |        |        |        |   |   |

#### Micro DMA1 start vector register

# DMA1V (005BH)

(Do not use read-modifywrite instructions.)

|             | 7           | 6            | 5      | 4      | 3      | 2      | 1 | 0 |

|-------------|-------------|--------------|--------|--------|--------|--------|---|---|

| bit Symbol  | DMA1V7      | DMA1V6       | DMA1V5 | DMA1V4 | DMA1V3 | DMA1V2 |   | / |

| Read/Write  |             | W            |        |        |        |        |   |   |

| After reset | 0           | 0            | 0      | 0      | 0      | 0      |   |   |

| Function    | Set startup | interrupt so |        |        |        |        |   |   |

#### Micro DMA2 start vector register

| DMA2V<br>(005CH) |

|------------------|

| (Do not use      |

| read-modify      |

| write            |

instructions.)

|             | 7           | 6                                                  | 5      | 4      | 3      | 2      | 1 | 0 |  |

|-------------|-------------|----------------------------------------------------|--------|--------|--------|--------|---|---|--|

| bit Symbol  | DMA2V7      | DMA2V6                                             | DMA2V5 | DMA2V4 | DMA2V3 | DMA2V2 |   | / |  |

| Read/Write  |             |                                                    | ٧      | V      |        |        | : |   |  |

| After reset | 0           | 0                                                  | 0      | 0      | 0      | 0      |   |   |  |

| Function    | Set startup | t startup interrupt source for micro DMA channel 2 |        |        |        |        |   |   |  |

#### Micro DMA3 start vector register

| DMA3V       |

|-------------|

| (005DH)     |

| (Do not use |

| read-modify |

write instructions.)

|                                                               | 7      | 6      | 5      | 4      | 3      | 2      | 1 | 0 |

|---------------------------------------------------------------|--------|--------|--------|--------|--------|--------|---|---|

| bit Symbol                                                    | DMA3V7 | DMA3V6 | DMA3V5 | DMA3V4 | DMA3V3 | DMA3V2 |   |   |

| Read/Write                                                    |        |        |        | :      | :      |        |   |   |

| After reset                                                   | 0      | 0      | 0      | 0      | 0      | 0      |   |   |

| Function Set startup interrupt source for micro DMA channel 3 |        |        |        |        |        |        | : | : |

## Setting Micro DMA Startup Source

| Micro DMA startup<br>source | Value set in micro DMA<br>start vector register | Micro DMA startup<br>source | Value set in micro DMA<br>start vector register |  |  |

|-----------------------------|-------------------------------------------------|-----------------------------|-------------------------------------------------|--|--|

| INT 0 interrupt             | 28H                                             | INTT 6 interrupt            | 64H                                             |  |  |

| INT 1 interrupt             | 2CH                                             | INTT 7 interrupt            | 68H                                             |  |  |

| INT 2 interrupt             | 30H                                             | INTTR 8 interrupt           | 6CH                                             |  |  |

| INT 3 interrupt             | 34H                                             | INTTR 9 interrupt           | 70H                                             |  |  |

| INT 4 interrupt             | 38H                                             | INTTR A interrupt           | 74H                                             |  |  |

| INT 5 interrupt             | 3CH                                             | INTTR B interrupt           | 78H                                             |  |  |

| INT 6 interrupt             | 40H                                             | INTTO 8 interrupt           | 7CH                                             |  |  |

| INT 7 interrupt             | 44H                                             | INTTO 9 interrupt           | 80H                                             |  |  |

| INT 8 interrupt             | 48H                                             | INTRX 0 interrupt           | 84H                                             |  |  |

| INTT 0 interrupt            | 4CH                                             | INTTX 0 interrupt           | 88H                                             |  |  |

| INTT 1 interrupt            | 50H                                             | INTRX 1 interrupt           | 8CH                                             |  |  |

| INTT 2 interrupt            | 54H                                             | INTTX 1 interrupt           | 90H                                             |  |  |

| INTT 3 interrupt            | 58H                                             | INTAD interrupt             | A4H                                             |  |  |

| INTT 4 interrupt            | 5CH                                             | Niero DNA auft stant        | FCH                                             |  |  |

| INTT 5 interrupt            | 60H                                             | Micro DMA soft start        |                                                 |  |  |

Figure 3.3.6 Setting Micro DMA Start Vector Register and Startup Source

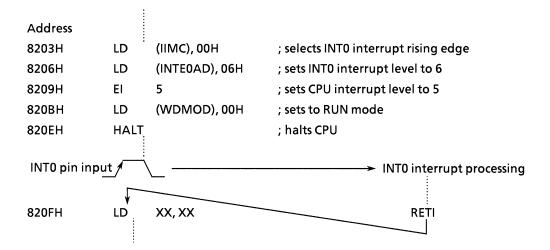

## (4) External Interrupt Control

Table 3.3.5 shows the function settings for the external interrupt pins.

TMP95CS54 can select the operating mode for the  $\overline{\text{NMI}}$ , INT0, INT5, or INT7 pins from among external interrupt functions. (For details on the external interrupt function pulse width, see "4.7 Interrupt Operations".)

Table 3.3.5 Setting Functions on External Interrupt Pins

| Interrupt pin | Shared pin |                               | Mode                          | Setting method                                       |

|---------------|------------|-------------------------------|-------------------------------|------------------------------------------------------|

|               |            | 7_                            | Falling edge                  | IIMC <nmiree> = 0</nmiree>                           |

| NMI           |            |                               | Both falling and rising edges | IIMC <nmiree> = 1</nmiree>                           |

|               | P56        |                               | Rising edge                   | IIMC <i0le> = 0, <i0ie> = 1</i0ie></i0le>            |

| INT0          |            | $\supset^{\bullet} \setminus$ | Level                         | IIMC<  OLE > = 1, <  OIE > = 1                       |

| INT1          | P70        |                               | Rising edge                   |                                                      |

| INT2          | P72        |                               | Rising edge                   |                                                      |

| INT3          | P73        | 1                             | Rising edge                   |                                                      |

| INT4          | P75        |                               | Rising edge                   |                                                      |

| INITE         | P90        |                               | Rising edge                   | T8MOD <cap12m1:0> = 0, 0 or 0, 1 or 1, 1</cap12m1:0> |

| INT5          |            | لم                            | Falling edge                  | T8MOD <cap12m1:0> = 1, 0</cap12m1:0>                 |

| INT6          | P91        | _                             | Rising edge                   |                                                      |

| INT7          | P94        |                               | Rising edge                   | T9MOD <cap34m1:0> = 0, 0 or 0, 1 or 1, 1</cap34m1:0> |

|               |            | 1                             | Falling edge                  | T9MOD <cap34m1:0> = 1, 0</cap34m1:0>                 |

| INT8          | P95        |                               | Rising edge                   |                                                      |

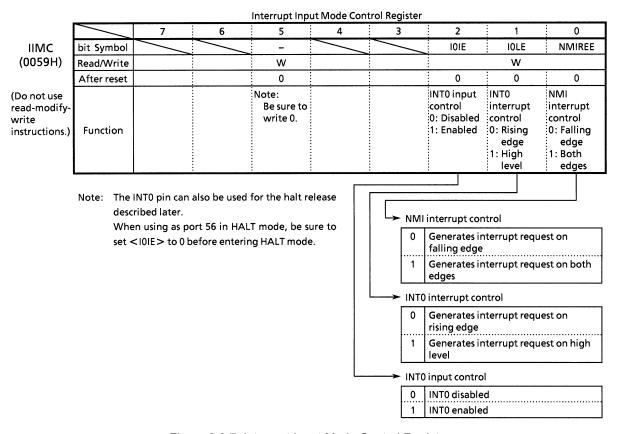

The input mode of the NMI and INT0 interrupts can be controlled by interrupt input mode control register IIMC.

Figure 3.3.7 shows the interrupt input mode control register.

Figure 3.3.7 Interrupt Input Mode Control Register

#### (5) Caution

When the CPU fetches an instruction to clear the interrupt request flag for the interrupt controller immediately before an interrupt is generated, the CPU may execute the instruction between receiving the interrupt and reading the interrupt vector.

To avoid the above occurring, clear the interrupt request flag by entering the instruction to clear the flag after the DI instruction. When setting an interrupt enable again by EI instruction after the execution of a clearing instruction, execute the EI instruction after the clearing instruction and following the execution of more than one more instruction. If the EI instruction is placed immediately after the clearing instruction, an interrupt could be enabled before interrupt request flags are cleared.

When changing the value of the interrupt mask register<IFF2:0> by execution of a POP SR instruction, disable an interrupt by DI instruction before execution of the POP SR instruction.

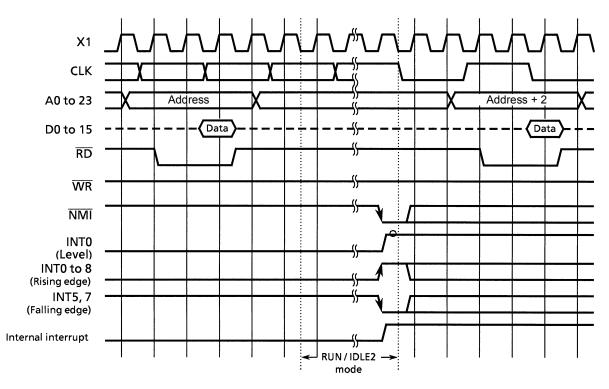

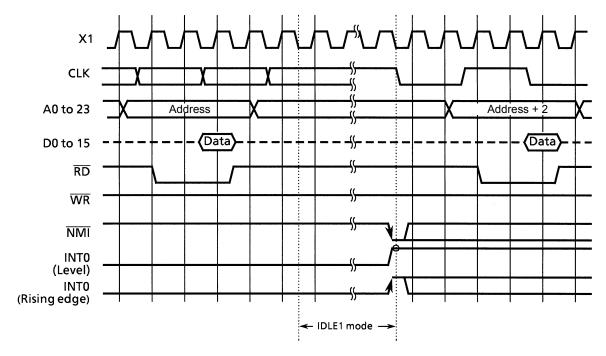

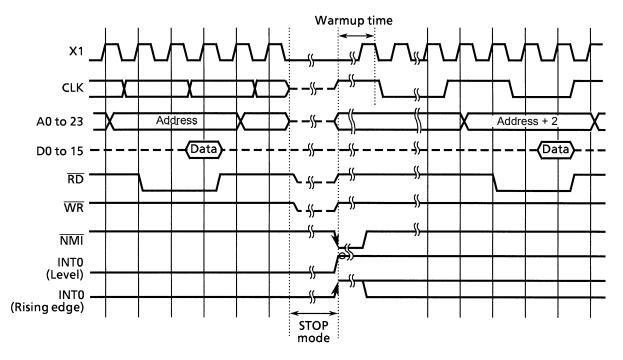

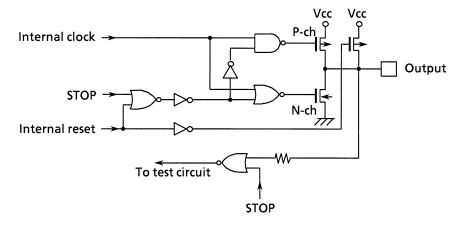

## 3.4 Standby Function

#### (1) HALT modes

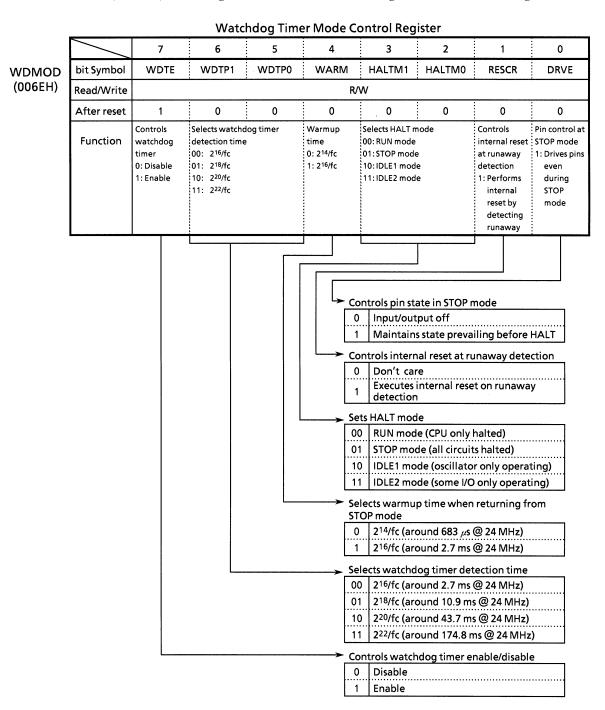

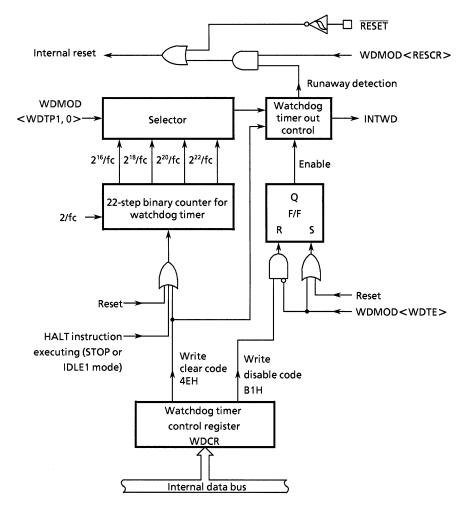

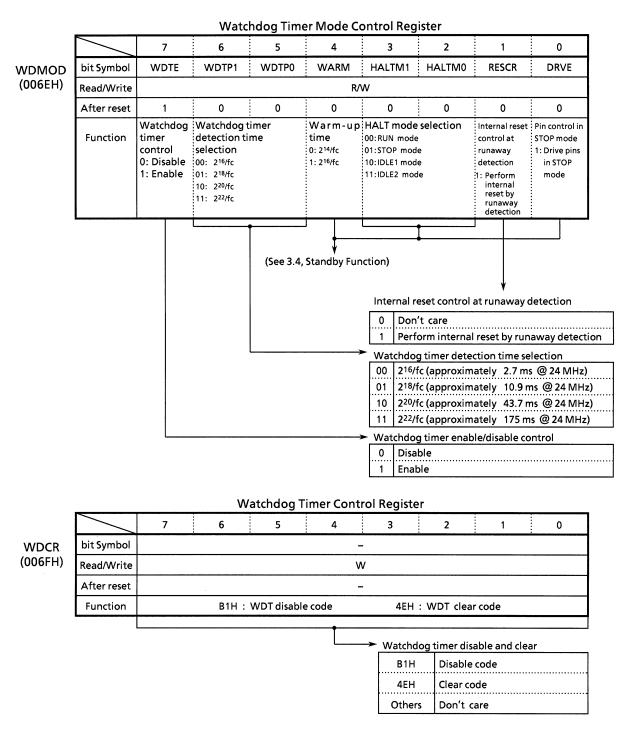

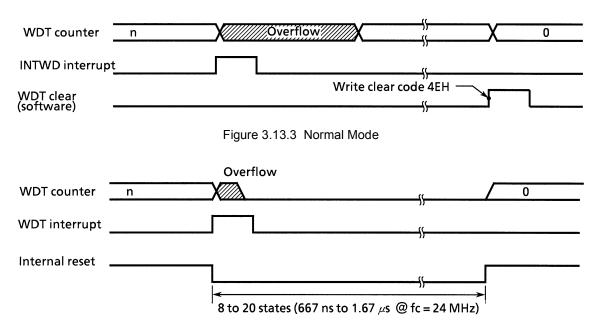

When the TMP95CS54 executes a HALT instruction, WDMOD<HALTM1:0> of the watchdog timer mode register can be used to set one of the following HALT modes: RUN, IDLE2, IDLE1, STOP. Figure 3.4.1 shows the watchdog timer mode control register.

Figure 3.4.1 Watchdog Timer Mode Control Register

The characteristics of RUN, IDLE2, IDLE1, and STOP modes are as follows:

[1] RUN: In this mode, only the CPU is halted. Power dissipation is almost the same as when the CPU is operating.

[2] IDLE2: Only the internal oscillator and specific internal I/O operate. Power dissipation is around one half that when the CPU is operating.

[3] IDLE1: Only the internal oscillator operates; all other circuits are halted. Power dissipation is one tenth of operating mode dissipation.

[4] STOP: All internal circuits, including the internal oscillator, are halted. In this mode power dissipation drops considerably.

Table 3.4.1 shows the operation of all blocks in HALT modes.

Halt mode RUN IDLE2 STOP WDMOD < HALTM1, 0> 00 11 10 01 CPU Halted I/O ports Maintains state prevailing at HALT instruction execution See Table 3.4.3 block 8-bit timers 16-bit timers Operating Serial channels Serial expansion Halted Operating **CAN** controller AD converter Watchdog timer Interrupt controller

Table 3.4.1 Blocks and I/O Pin Operation in Halt Modes

## (2) Release from HALT mode

Release from HALT mode can trigger an interrupt request or a reset. A combination of the interrupt mask register <IFF2:0> state and the halt mode determine the useable halt release source. (For details, see Table 3.4.2)

#### Release by interrupt request

The operation to release HALT mode by using an interrupt request differs according to the interrupt enable state. If the interrupt request level set prior to the execution of the HALT instruction is higher than the interrupt mask register value, after HALT mode is released, interrupt processing is performed by this source, and processing starts from the next instruction following the HALT instruction. If the interrupt request level is lower than the interrupt mask register value, HALT mode is not released. (At a non-maskable interrupt, interrupt processing is performed after HALT mode release irrespective of the mask register value.)

However, in the case of the INTO interrupt only, HALT mode can be released if the interrupt request level is lower than the interrupt mask register value. In this case the interrupt processing is not performed. Processing always starts from the next instruction following the HALT instruction. (The INTO interrupt request flag is held at 1.)

Note) Usually, interrupts can release all halts status. However, the interrupts (= NMI and INT0) which can release the HALT mode may not be able to do so if they are input during the period when the CPU is shifting to the HALT mode (for about 3 clocks of fc) with IDLE1 or STOP mode (RUN and IDLE2 are not applicable to this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted completely to HALT mode, halt status can be released without difficulty. The priority of this interrupt is compared with that of the interrupt kept on hold internally, and the interrupt with the higher priority is handled first followed by the other interrupt.

## Release by reset

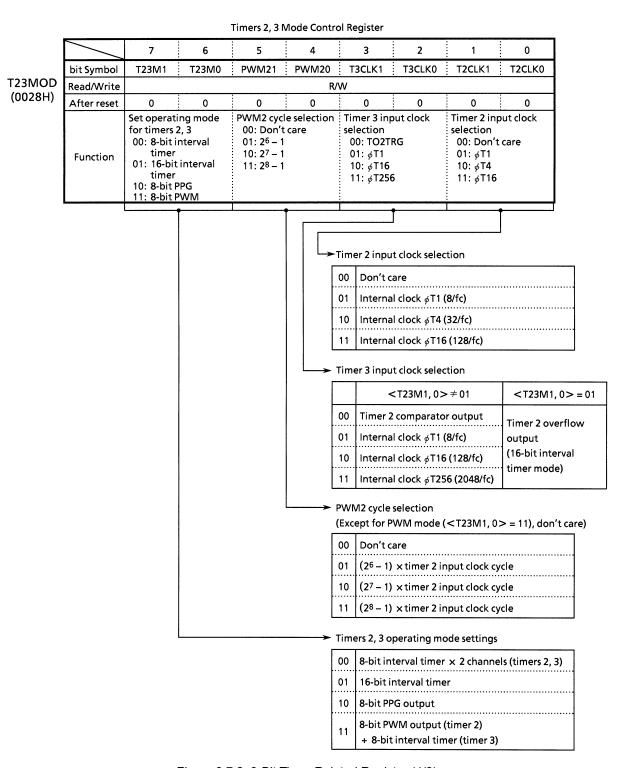

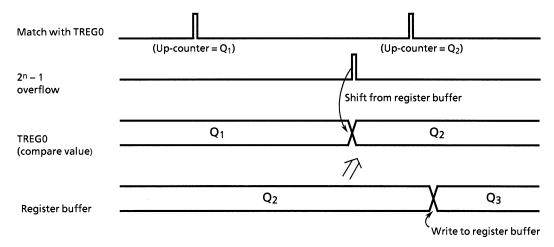

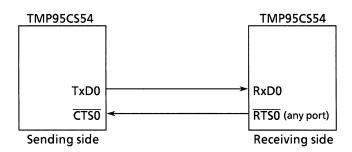

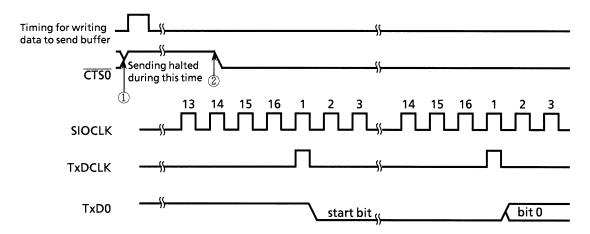

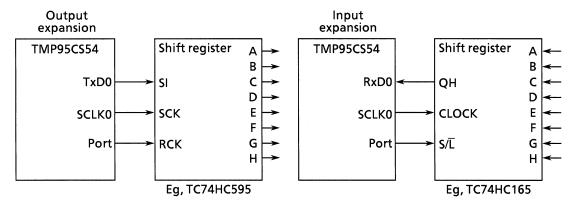

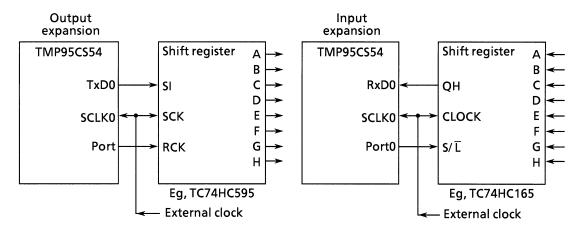

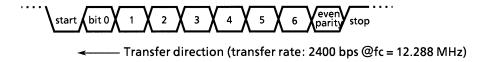

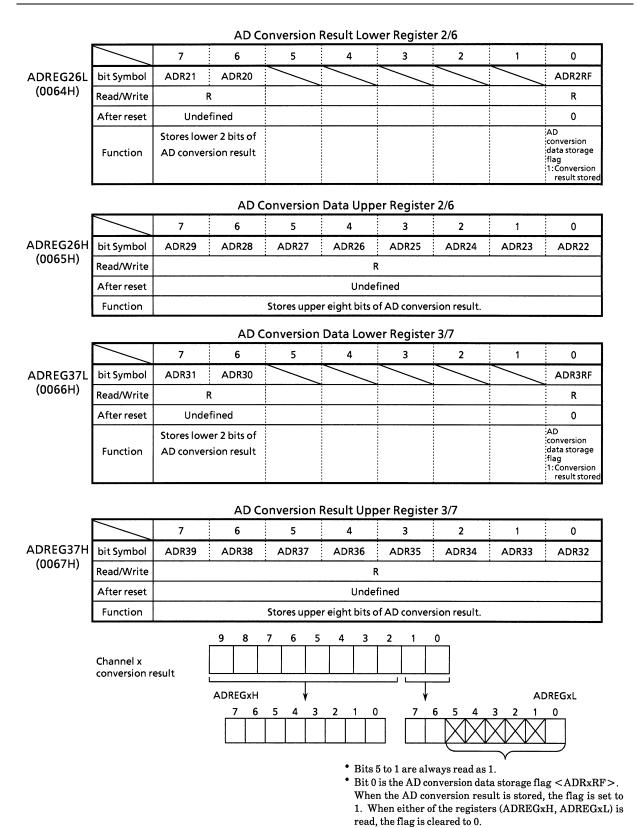

All HALT modes can be released by a reset. However, when releasing STOP mode, allow sufficient reset time (at least 3 ms) for the oscillator to stabilize.