### **FEATURES**

- 700MHz min. count frequency

- Extended 100E VEE range of -4.2V to -5.5V

- 1000ps CLK to Q, TC

- Internal, gated TC feedback

- 8 bits wide

- Fully synchronous counting and TC generation

- Asynchronous Master Reset

- Fully compatible with industry standard 10KH, 100K I/O levels

- Internal 75KΩ input pulldown resistors

- **ESD protection of 2000V**

- Fully compatible with Motorola MC10E/100E016

### DESCRIPTION

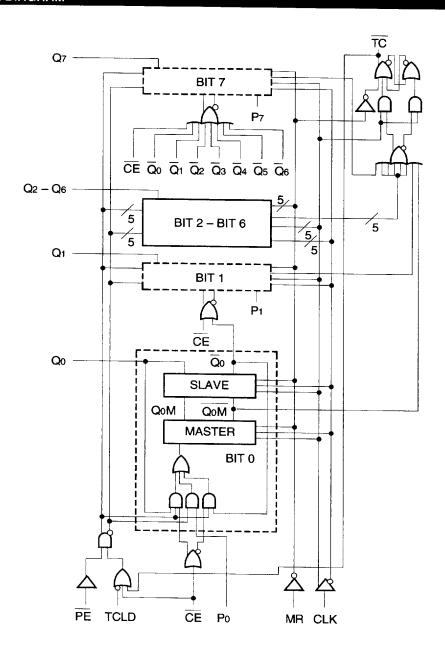

The SY10/100E016 are high-speed synchronous, presettable and cascadable 8-bit binary counters designed for use in new, high-performance ECL systems. Architecture and operation are the same as the Motorola MC10H016 in the MECL 10KH family, extended to 8 bits, as shown in the logic diagram.

The counters feature internal feedback of TC, gated by the TCLD (terminal count load) pin. When TCLD is LOW, the  $\overline{TC}$  feedback is disabled and counting proceeds continuously, with  $\overline{TC}$  going LOW to indicate an all-HIGH state. When TCLD is HIGH, the  $\overline{TC}$  feedback causes the counter to automatically reload upon  $\overline{TC} = LOW$ , thus functioning as a programmable counter.

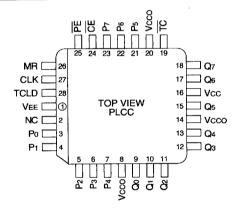

### PIN CONFIGURATION

### PIN NAMES

| Pin   | Function                           |

|-------|------------------------------------|

| P0-P7 | Parallel Data (Preset) Inputs      |

| Q0-Q7 | Data outputs                       |

| CE    | Count Enable Control Input         |

| PE    | Parallel Load Enable Control Input |

| MR    | Master Reset                       |

| CLK   | Clock                              |

| TC    | Terminal Count Output              |

| TCLD  | TC-Load Control Input              |

| Vcco  | Vcc to Output                      |

© 1996 Synergy Semiconductor Corporation

9001381 0001942 660 🖿

Rev.: C Amendment: /0 Issue Date: May, 1996

# **BLOCK DIAGRAM**

| TRUTH | TABLE <sup>(1)</sup> |      |    |     |                                  |

|-------|----------------------|------|----|-----|----------------------------------|

| CE    | PE                   | TCLD | MR | CLK | Function                         |

| Х     | L                    | Х    | L  | Z   | Load Parallel (Pn to Qn)         |

| L     | Н                    | L    | L  | Z   | Continuous Count                 |

| L     | Н                    | н    | L  | Z   | Count; Load Parallel on TC = LOW |

| Н     | Н                    | х    | L  | Z   | Hold                             |

| Х     | Х                    | х    | L  | ZZ  | Master respond, Slaves Hold      |

| Х     | ×                    | ×    | Н  | Z   | Reset (Qn : = LOW, TC : = HIGH)  |

NOTE:

1. Z = Clock Pulse (LOW-to-HIGH), ZZ = Clock Pulse (HIGH-to-LOW)

## DC ELECTRICAL CHARACTERISTICS

VEE = VEE (Min.) to VEE (Max.): VCC = VCCO = GND

|        |                                     | TA = 0°C |            |            | T/   | \ = +25°   | <u>c</u>   | Ta = +85°C |            |            |      |           |

|--------|-------------------------------------|----------|------------|------------|------|------------|------------|------------|------------|------------|------|-----------|

| Symbol | Parameter                           | Min.     | Тур.       | Max.       | Min. | Тур.       | Max.       | Min.       | Тур.       | Max.       | Unit | Condition |

| liн    | Input HIGH Current                  |          | 1          | 150        |      |            | 150        | _          |            | 150        | μΑ   |           |

| lEE    | Power Supply Current<br>10E<br>100E |          | 151<br>151 | 181<br>181 |      | 151<br>151 | 181<br>181 | _          | 151<br>174 | 181<br>208 | mA   |           |

### **AC ELECTRICAL CHARACTERISTICS**

VEF = VEF (Min.) to VEE (Max.); VCC = VCCO = GND

|              |                                                                                                                    | Т                               | A = 0°0                         | C                                   | Т                               | A = 25°                         | C                                   | TA                              | = +85                           | °C                                  |      |                  |

|--------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|-------------------------------------|---------------------------------|---------------------------------|-------------------------------------|---------------------------------|---------------------------------|-------------------------------------|------|------------------|

| Symbol       | Parameter                                                                                                          | Min.                            | Тур.                            | Max.                                | Min.                            | Тур.                            | Max.                                | Min.                            | Тур.                            | Max.                                | Unit | Condition        |

| fCOUNT       | Max. Count Frequency                                                                                               | 700                             | 900                             | _                                   | 700                             | 900                             | _                                   | 700                             | 900                             |                                     | MHz  | <u> </u>         |

| tPLH<br>tPHL | Propagation Delay to Output<br>CLK to Q<br>MR to Q<br>CLK to TC (Qs loaded)<br>CLK to TC (Qs unloaded)<br>MR to TC | 600<br>600<br>550<br>550<br>625 | 725<br>775<br>775<br>700<br>775 | 1000<br>1000<br>1050<br>900<br>1000 | 600<br>600<br>550<br>550<br>625 | 725<br>775<br>775<br>700<br>775 | 1000<br>1000<br>1050<br>900<br>1000 | 600<br>600<br>550<br>550<br>625 | 725<br>775<br>775<br>700<br>775 | 1000<br>1000<br>1050<br>900<br>1000 | ps   | -<br>-<br>1<br>1 |

| ts           | Set-up Time Pn CE PE TCLD                                                                                          | 150<br>600<br>600<br>500        | -30<br>400<br>400<br>300        |                                     | 150<br>600<br>600<br>500        | -30<br>400<br>400<br>300        |                                     | 150<br>600<br>600<br>500        | -30<br>400<br>400<br>300        | _<br>_<br>_                         | ps   | _                |

| tH           | Hold Time Pn CE PE TCLD                                                                                            | 250<br>0<br>0<br>100            | 30<br>-400<br>-400<br>-300      | <u>-</u>                            | 250<br>0<br>0<br>100            | 30<br>400<br>400<br>300         | _<br>_<br>_                         | 250<br>0<br>0<br>100            | 30<br>400<br>400<br>300         |                                     | ps   | _                |

| tra          | Reset Recovery Time                                                                                                | 900                             | 700                             |                                     | 900                             | 700                             |                                     | 900                             | 700                             |                                     | ps   |                  |

| twp          | Minimum Pulse Width<br>CLK, MR                                                                                     | 400                             |                                 | _                                   | 400                             | _                               | _                                   | 400                             |                                 | _                                   | ps   | _                |

| tr<br>tf     | Rise/Fall Times<br>20% to 80%                                                                                      | 300                             | 510                             | 800                                 | 300                             | 510                             | 800                                 | 300                             | 510                             | 800                                 | ps   |                  |

#### NOTE:

9001381 0001944 433

<sup>1.</sup> CLK to TC propagation delay is dependent on the loading of the Q outputs. With all of the Q outputs loaded, the noise generated in going from a IIII IIII state to a 0000 0000 state causes the CLk to TC+ delay to increase.

| FUNCTI   | ON T | ABLE |    |      |     |      | -  |                |    |    |       |    |                |                  |          |          |

|----------|------|------|----|------|-----|------|----|----------------|----|----|-------|----|----------------|------------------|----------|----------|

| Function | PE   | CE   | MR | TCLD | CLK | P7P4 | P3 | P <sub>2</sub> | P1 | Po | Q7-Q4 | Qз | Q <sub>2</sub> | Q <sub>1</sub>   | Qo       | TC       |

| Load     | L    | Х    | L  | Х    | Z   | Н    | Н  | Н              | L  | L  | н     | Н  | ——             | L                | L        | Н        |

| Count    | Н    | L    | L. | L    | Z   | x    | х  | Х              | Х  | х  | н     | Н  | н              | L                | Н        | Н        |

|          | Н    | L    | L  | L    | Z   | x    | Х  | х              | х  | х  | н     | Н  | н              | Н                | L        | н        |

|          | Н    | L    | L  | L    | Z   | X    | Х  | х              | х  | х  | н     | Н  | н              | н                | н        | <u>"</u> |

|          | Н    | L    | L  | L    | Z   | x    | Х  | Х              | Х  | х  | L     | L  | L              | L                | L        | Н        |

| Load     | L    | Х    | L  | Х    | Z   | Н    | Н  | Н              | L  | L  | Н     | Н  | Н              | _ <u>-</u> _     | <u>-</u> | Н        |

| Hold     | Н    | Н    | L  | ×    | Z   | ×    | Х  | Х              | Х  | х  | н     | н  | Н              | L                | L        | Н.       |

|          | Н    | Н    | L  | Х    | Z   | х    | Х  | Х              | х  | х  | н     | н  | Н              | L                | L        | Н        |

| Load On  | Н    | L    | L  | Н    | Z   | Н    | L  | Н              | Н  | L  | Н     | Н  | Н              | _ <del>_</del> _ | Н        | Н.       |

| Terminal | Н    | L    | L  | н    | Z   | н    | L  | Н              | Н  | L  | Н     | Н  | Н              | Н                | L        | н        |

| Count    | Н    | L    | L  | Н    | Z   | н    | L  | Н              | н  | L  | н     | н  | Н              | Н                | Н        |          |

|          | н    | L    | L  | Н    | Z   | н    | L  | Н              | Н  | L  | н     | L  | Н              | н                | L        | н        |

|          | Н    | L    | L  | Н    | Z   | н    | L  | Н              | н  | L  | н     | L  | Н              | н                | Н        | н        |

|          | Н    | L    | L  | Н    | Z   | Н    | L  | н              | Н  | L  | н     | н  | L              | Ŀ                | L.       | Н        |

| Reset    | Х    | X    | Н  | Х    | Х   | ×    | Х  | X              | Х  | X  | L     | L  | L              | L                | L        | Н        |

### **APPLICATIONS INFORMATION**

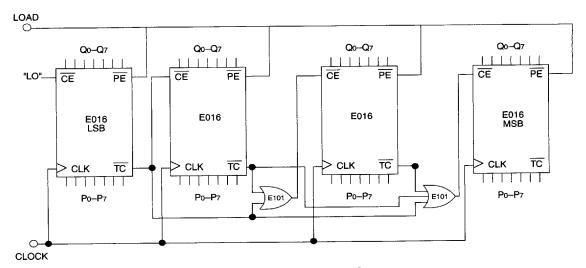

#### **Cascading Multiple E016 Devices**

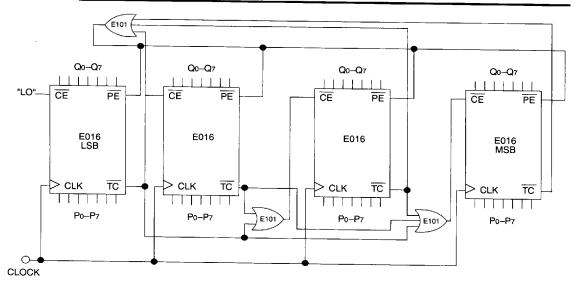

For applications which call for larger than 8-bit counters, multiple E016s can be tied together to achieve very wide bit width counters. The active low terminal count (TC) output and count enable input (CE) greatly facilitate the cascading of E016 devices. Two E016s can be cascaded without the need for external gating; however, for counters wider than 16 bits, external OR gates are necessary for cascade implementations.

Figure 1, below, pictorially illustrates the cascading of 4 E016s to build a 32-bit high frequency counter. Note the E101 gates used to OR the terminal count outputs of the lower order E016s to control the counting operation of the higher order bits. When the terminal count of the preceding device (or devices) goes low (the counter reaches an all 1s state), the more significant E016 is set in its count mode and will count one binary digit upon the next positive clock transition. In addition, the preceding devices will also count one bit, thus sending their terminal count outputs back to a high state, disabling the count operation of the more significant counters and placing them back into hold modes. Therefore, for an

E016 in the chain to count all of the lower order terminal count outputs, it must be in the low state. The bit width of the counter can be increased or decreased by simply adding or subtracting E016 devices from Figure 1 and maintaining the logic pattern illustrated in the same figure.

The maximum frequency of operation for the <u>cas</u>caded counter chain is set by the propagation delay of the TC output and the necessary set-up time of the CE input and the propagation delay through the OR gate controlling it (for 16-bit counters the limitation is only the TC propagation delay and the CE set-up time). Figure 1 shows E101 gates used to control the count enable inputs; however, if the frequency of operation is lower, a slower ECL OR gate can be used. Using the worst case guarantees for these parameters from the ECLinPS data book, the maximum count frequency for a greater than 16-bit counter is 475MHz and that for a 16-bit counter is 625MHz. Note that this assumes the trace delay between the TC outputs and the CE inputs are negligible. If this is not the case, estimates of these delays need to be added to the calculations.

Figure 1. 32-Bit Cascaded E016 Counter

#### Programmable Divider

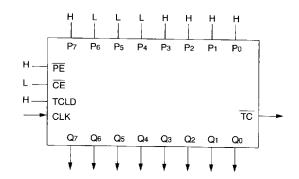

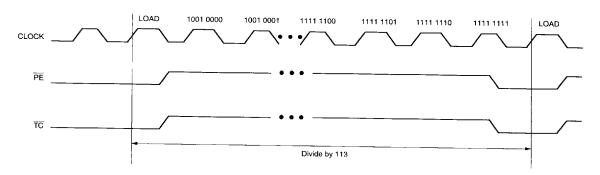

The E016 has been designed with a control pin which makes it ideal for use as an 8-bit programmable divider. The TCLD pin (load on terminal count), when asserted, reloads the data present at the parallel input pin (Pn's) upon reaching terminal count (an all 1s state on the outputs). Because this feedback is built internal to the chip, the programmable division operation will run at very nearly the same frequency as the maximum counting frequency of the device. Figure 2 below illustrates the input conditions necessary for utilizing the E016 as a programmable divider set up to divide by 113.

To determine what value to load into the device to accomplish the desired division, the designer simply subtracts the binary equivalent of the desired divide ratio for the binary value for 256. As an example for a divide ration of 113:

$$PN's = 256 - 113 = 8F_{16} = 1000 1111$$

where

Forcing this input condition, as per the set-up in Figure 2, will result in the waveforms of Figure 3. Note that the TC output

Figure 2. Mod 2 to 256 Programmable Divider

Figure 3. Divide by 113 E016 Programmable Divider Waveforms

| Divide | Preset Data Inputs |    |     |    |    |                |                |    |  |  |  |

|--------|--------------------|----|-----|----|----|----------------|----------------|----|--|--|--|

| Ratio  | P7                 | P6 | P5  | P4 | P3 | P <sub>2</sub> | P <sub>1</sub> | Po |  |  |  |

| 2      | Н                  | н  | Н . | Н  | Н  | н              | н              | L  |  |  |  |

| 3      | н                  | н  | н   | Н  | н  | н              | L              | Н  |  |  |  |

| 4      | н                  | Н  | н   | н  | н  | Н              | L              | L  |  |  |  |

| 5      | н                  | Н  | н   | Н  | Н  | L              | Н              | Н  |  |  |  |

| •      | •                  | •  | •   | •  | •  | •              | •              | •  |  |  |  |

| •      | •                  | •  | •   | •  | •  | •              | •              | •  |  |  |  |

| 112    | н                  | L  | L   | н  | L  | L              | L              | L  |  |  |  |

| 113    | н                  | L  | L   | L  | н  | н              | Н              | Н  |  |  |  |

| 114    | Н                  | L  | Ł   | L  | Н  | н              | Н              | L  |  |  |  |

| •      | •                  | •  | •   | •  | •  | •              | •              | •  |  |  |  |

| •      | •                  | •  | •   | •  | •  | •              | •              | •  |  |  |  |

| 254    | L                  | L  | L   | L  | L  | L              | Н              | Ĺ  |  |  |  |

| 255    | L                  | L  | L   | L  | L  | L              | L              | Н  |  |  |  |

| 256    | L                  | L  | L   | L  | L  | L              | L              | L  |  |  |  |

Table 1. Preset Values for Various Divide Ratios

4-10

is used as the divide output and the pulse duration is equal to a full clock period. For even divide ratios twice the desired divide ratio can be loaded into the E016 and the TC output can feed the clock input of a toggle flip-flop to create a signal divided as desired with a 50% duty cycle.

A single E016 can be used to divide by any ratio from 2 to 256, inclusive. If divide ratios of greater than 256 are needed, multiple E016s can be cascaded in a manner similar to that already discussed. When E016s are cascaded to build larger dividers, the TCLD pin will no longer provide a means for loading on terminal count. Because one does not want to reload the counters until all of the devices in the chain have reached terminal count, external gating of the TC pins must be used for multiple E016 divider chains.

Figure 4 on the following page shows a typical block diagram of a 32-bit divider chain. Once again, the maximize the frequency of operation, E101 OR gates were used. For lower frequency applications, a slower OR gate could replace the E101. Note that for a 16-bit divider, the OR function feeding the PE (program enable) input CANNOT be replaced by a wire OR tie as the TC output of the least significant E016 must also feed the CE input of the most significant E016. If the

two TC outputs were OR tied, the cascaded count operation would not operate properly. Because in the cascaded form the PE feedback is external and requires external gating, the maximum frequency of operation will be significantly less than the same operation in a single device.

#### Maximizing E016 Count Frequency

The E016 device produces nine fast transitioning single-ended outputs; thus, VCC noise can become significant in situations where all of the outputs switch simultaneously in the same direction. This VCC noise can negatively impact the maximum frequency of operation of the device. Since the device does not need to have the Q outputs terminated to count properly, it is recommended that, if the outputs are not going to be used in the rest of the system, they should be left unterminated. In addition, if only a subset of the Q outputs are used in the system, only those outputs should be terminated. Not terminating the unused outputs will not only cut down the VCC noise generated, but will also save in total system power dissipation. Following these guidelines will allow designers to either be more aggressive in their designs, or provide them with an extra margin to the published data book specifications.

Figure 4. 32-Bit Cascaded E016 Programmable Divider

| D | D | റ | ı | п | $\sim$ | $\Gamma $ | 7 = | ER | 13 |  | 7 | т. | ı |

|---|---|---|---|---|--------|-----------|-----|----|----|--|---|----|---|

|   |   | ) | _ | J | )      |           | 2   | _  | ш  |  | u | u  |   |

| Ordering<br>Code | Package<br>Type | Operating<br>Range |

|------------------|-----------------|--------------------|

| SY10E016JC       | J28-1           | Commercial         |

| SY10E016JCTR     | J28-1           | Commercial         |

| SY100E016JC      | J28-1           | Commercial         |

| SY100E016JCTR    | J28-1           | Commercial         |

9001381 0001949 T15 🖿 4-11