## 54/7476 54H/74H76 54LS/74LS76

### DESCRIPTION

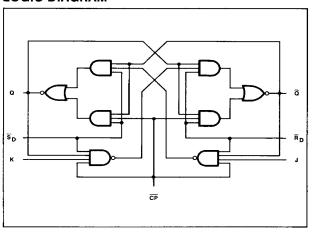

The "76" is a Dual JK Flip-Flop with individual J, K, Clock, Set and Reset inputs. The 7476 and 74H76 are positive pulse triggered flip-flops. JK information is loaded into the master while the Clock is HIGH and transferred to the slave on the HIGH-to-LOW Clock transition. The J and K inputs must be stable while the Clock is HIGH for conventional operation.

The 74LS76 is a negative edge triggered flip-flop. The J and K inputs must be stable only one setup time prior to the HIGH-to-LOW Clock transition.

The Set  $(\overline{S}_D)$  and Reset  $(\overline{R}_D)$  are asynchronous active LOW inputs. When LOW, they override the Clock and data inputs forcing the outputs to the steady state levels as shown in the Truth Table.

# ORDERING CODE (See Section 9 for further Package and Ordering Information)

| PACKAGES    | PIN<br>CONF.   | COMMERCIAL RANGES $V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $^{\circ}70^{\circ}C$ | MILITARY RANGES  VCC = 5V ± 10%; T <sub>A</sub> = -55°C to ·125°C |  |  |  |  |  |

|-------------|----------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|

| Plastic DIP | Fig A<br>Fig A | N7476N • N74H76N<br>N74LS76N                                                          |                                                                   |  |  |  |  |  |

| Ceramic DIP | Fig A<br>Fig A | N7476F • N74H76F<br>N74LS76F                                                          | S5476F • S54H76F<br>S54LS76F                                      |  |  |  |  |  |

| Flatpak     | Fig A<br>Fig A |                                                                                       | S5476W • S54H76W<br>S54LS76W                                      |  |  |  |  |  |

## INPUT AND OUTPUT LOADING AND FAN-OUT TABLE (a)

|                   | PINS        |                                              | 54/74      | 54H/74H     | 54\$/74\$ | 54LS/74LS                  |  |  |  |  |  |  |

|-------------------|-------------|----------------------------------------------|------------|-------------|-----------|----------------------------|--|--|--|--|--|--|

| СP                | Clock input | liн (μΑ)<br>fil (mA)                         | 80<br>-3.2 | 50<br>-2.0  |           | 80<br>-0.8                 |  |  |  |  |  |  |

| $\widetilde{R}_D$ | Reset input | l <sub>IH</sub> (μΑ)<br>l <sub>IL</sub> (mA) | 80<br>-3.2 | 100<br>-4.0 |           | 60<br>-0.8                 |  |  |  |  |  |  |

| S̄D               | Set input   | l <sub>IH</sub> (µA)<br>l <sub>IL</sub> (mA) | 80<br>-3.2 | 100<br>-4.0 |           | 60<br>0.8                  |  |  |  |  |  |  |

| JK                | Data inputs | liH (µA)<br>liL (mA)                         | 40<br>-1.6 | 50<br>-2.0  |           | 20<br>-0.4                 |  |  |  |  |  |  |

| Q &               | Q Outputs   | loh (μΑ)<br>loL (mA)                         | -400<br>16 | -500<br>20  |           | -400<br>4/8 <sup>(a)</sup> |  |  |  |  |  |  |

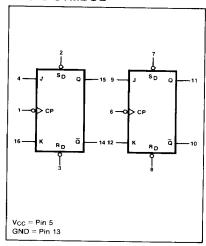

### LOGIC SYMBOL

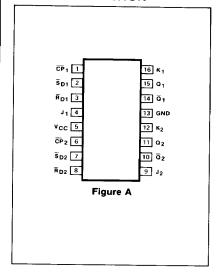

#### PIN CONFIGURATION

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (b)

| PARAMETER |                | TEST CONDITIONS                             | 54/74 |     | 54H/74H |     | 548/748 |     | 54LS/74LS |     | UNIT |

|-----------|----------------|---------------------------------------------|-------|-----|---------|-----|---------|-----|-----------|-----|------|

|           |                |                                             | Min   | Max | Min     | Max | Min     | Max | Min       | Max | UNIT |

| Icc       | Supply current | V <sub>CC</sub> = Max, V <sub>CP</sub> = 0V |       | 40  |         | 50  |         |     |           | 8.0 | mA   |

#### NOTES

- The slashed numbers indicate different parametric values for Military/Commercial temperature ranges respectively.

- For family dc characteristics, see inside front cover for 54/74 and 54H/74H and see inside back cover for 54S/74S and 54LS/74LS specification.

114

## signetics

### **LOGIC DIAGRAM**

## **MODE SELECT—TRUTH TABLE**

| OPERATING MODE             |   | H              | OUTPUTS |   |   |   |   |

|----------------------------|---|----------------|---------|---|---|---|---|

|                            |   | R <sub>D</sub> | CP (d)  | J | K | Q | ā |

| Asynchronous Set           |   | Τ              | ×       | Х | Х | Н | L |

| Asynchronous Reset (Clear) |   | L              | ×       | х | х | L | н |

| Undetermined (c)           |   | L              | x       | х | х | н | н |

| Toggle                     |   | н              |         | h | h | q | q |

| Load "0" (Reset)           |   | н              | 77      | 1 | ħ | L | н |

| Load "1" (Set)             |   | Н              |         | h | 1 | Н | L |

| Hold "no change"           | н | н              | 工       | ı | 1 | q | q |

- HIGH voltage level steady state.

- LOW voltage level steady state.

- HIGH voltage level one setup time prior to the HIGH-to-LOW Clock transition. (e)

- 1 = LOW voltage level one setup time prior to the HIGH-to-LOW Clock transition. (e)

- = Lower case letters indicate the state of the referenced output prior to the HIGH to LOW Clock transition.

- → = Positive Clock pulse.

## AC CHARACTERISTICS T<sub>A</sub> = 25°C (See Section 4 for Waveforms and Conditions)

| PARAMETER    |                                                              | 1               | 54/74  C <sub>L</sub> = 15 pF  R <sub>L</sub> = 400 Ω |          | 54H/74H<br>C <sub>L</sub> = 25 pF<br>R <sub>L</sub> = 280 Ω |          | 54\$/74\$ |     | 54LS/74LS  C <sub>L</sub> = 15pF  R <sub>L</sub> = 2kΩ |          | UNIT     |

|--------------|--------------------------------------------------------------|-----------------|-------------------------------------------------------|----------|-------------------------------------------------------------|----------|-----------|-----|--------------------------------------------------------|----------|----------|

|              |                                                              | TEST CONDITIONS |                                                       |          |                                                             |          |           |     |                                                        |          |          |

|              |                                                              |                 | Min                                                   | Max      | Min                                                         | Max      | Min       | Max | Min                                                    | Max      |          |

| fMAX         | Maximum Clock<br>frequency                                   | Waveform 4      | 15                                                    |          | 25                                                          |          |           |     | 30                                                     |          | MHz      |

| tpLH<br>tpHL | Propagation delay<br>Clock to Output                         | Waveform 4      |                                                       | 25<br>40 |                                                             | 21<br>27 |           |     |                                                        | 20<br>30 | ns<br>ns |

| tpLH<br>tpHL | Propagation delay S <sub>D</sub> or R <sub>D</sub> to Output | Waveform 5      |                                                       | 25<br>40 |                                                             | 13<br>24 |           |     |                                                        | 20<br>30 | ns<br>ns |

## AC SETUP REQUIREMENTS T<sub>A</sub> = 25°C (See Section 4 for Waveforms and Conditions)

| PARAMETER          |                                | TEST CONDITIONS | 54  | 54/74 |     | 54H/74H |     | 548/748 |     | 54LS/74LS |      |

|--------------------|--------------------------------|-----------------|-----|-------|-----|---------|-----|---------|-----|-----------|------|

|                    |                                |                 | Min | Max   | Min | Max     | Min | Max     | Min | Max       | UNIT |

| tw(H)              | Clock pulse<br>width (HIGH)    | Waveform 4      | 20  |       | 12  |         |     |         | 20  |           | ns   |

| t <sub>W</sub> (L) | Clock pulse<br>width (LOW)     | Waveform 4      | 47  |       | 28  |         |     |         | 13  |           | ns   |

| t <sub>W</sub> (L) | Set or Reset pulse width (LOW) | Waveform 5      | 25  |       | 16  |         |     |         | 25  |           | ns   |

| ts                 | Setup time<br>J or K to Clock  | Waveform 4      | (e) |       | (e) |         |     |         | 20  |           | ns   |

| th                 | Hold time<br>J or K to Clock   | Waveform 4      | 0   |       | 0   |         |     |         | 0   |           | ns   |

## NOTES

- c. Both outputs will be HIGH while both \$\overline{S}\_D\$ and \$\overline{R}\_D\$ are LOW, but the output states are unpredictable if \$\overline{S}\_D\$ and \$\overline{R}\_D\$ go HIGH simultaneously.

d. The 74LS76 is edge triggered. Data must be stable one setup time prior to the negative

- edge of the Clock for predictable operation.

- e. The J and K inputs of the 7476 and 74H76 must be stable while the Clock is HIGH for conventional operation.

signetics

115