### **General Description**

The MAX7454/MAX7455 triple-channel video reconstruction filters and buffers are ideal for high definition (HD), standard definition progressive scan/noninterlaced (SDp), and standard definition interlaced (SDi) television applications. These devices are a fully integrated solution for filtering and buffering HD and/or SDp/SDi TV signals in component video output format (Y PB PR or RGB). The MAX7454/MAX7455 are compatible with the 1080i, 720p, 480p, and 480i scanning system standards. In addition to having an HD/SD switchable frequency response, the magnitude response can be optimized by approximately 15% by a control input.

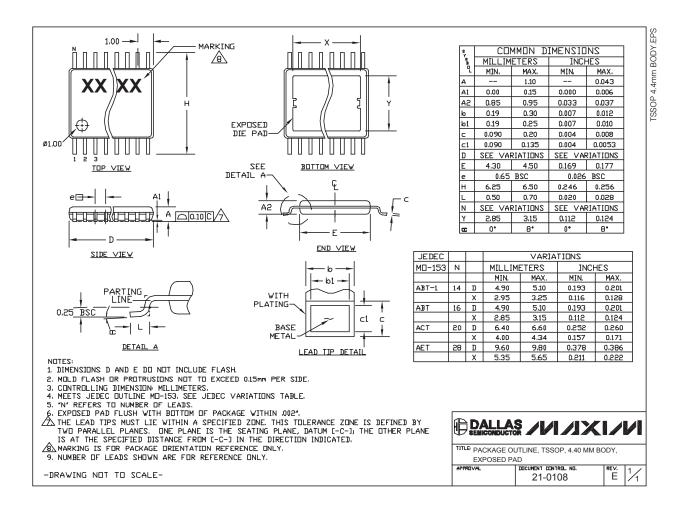

The input and output signals are DC-coupled to the MAX7454/MAX7455, eliminating the large output AC-coupling capacitors normally used. The MAX7454/MAX7455 output buffers drive a 2VP-P video signal into a standard 150 $\Omega$  load. The MAX7454 has a gain of +6dB and the MAX7455 has a gain of +12dB. Both devices are available in a 20-pin TSSOP package and are fully specified over the upper commercial (0°C to +85°C) temperature range.

## **Applications**

Set-Top Boxes

Direct-Broadcast Satellite (DBS) Receiver

**DVD Players**

Hard-Disk Recorders

HDTV (LCD, PDP, DLP)

Professional Cameras

#### **Features**

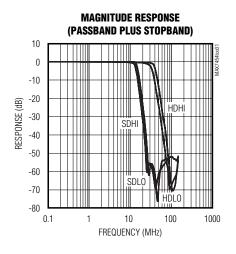

- ♦ 30MHz High Definition (HD)/10MHz Standard **Definition (SD) Switchable Video Reconstruction Filter**

- ♦ 15% Magnitude Response Adjustment

♦ Passband: -2.3dB at 30MHz

-0.40dB at 10MHz -0.10dB at 5MHz

◆ Stopband: -55dB at 74MHz (HDTV)

-62dB at 27MHz (SDTV)

- ♦ Output Blank Level <1V for DC-Coupled Output

- ♦ +6dB Gain (MAX7454) or +12dB Gain (MAX7455)

- ♦ Direct Coupled Input, Zero Tilt

- ♦ Direct Coupled Output, No Large Output Capacitor

- ♦ Drives 2V<sub>P-P</sub> Signal in 150Ω Video Load

- ♦ Small 20-Pin TSSOP Package

- ♦ Single +5V Supply

## **Ordering Information**

| PART        | TEMP<br>RANGE | PIN-PACKAGE  | BUFFER<br>GAIN (dB) |  |

|-------------|---------------|--------------|---------------------|--|

| MAX7454UUP  | 0°C to +85°C  | 20 TSSOP-EP* | +6                  |  |

| MAX7454UUP+ | 0°C to +85°C  | 20 TSSOP-EP* | +6                  |  |

| MAX7455UUP  | 0°C to +85°C  | 20 TSSOP-EP* | +12                 |  |

| MAX7455UUP+ | 0°C to +85°C  | 20 TSSOP-EP* | +12                 |  |

<sup>+</sup>Indicates lead-free packaging.

#### Pin Configuration appears at end of data sheet.

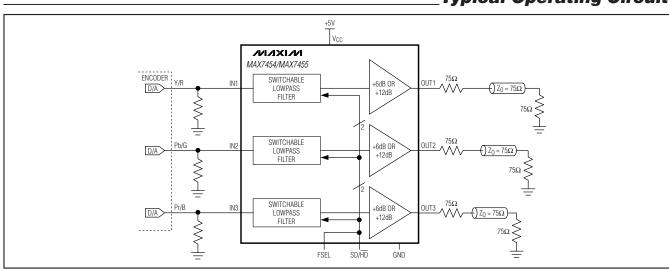

## Typical Operating Circuit

NIXIN

Maxim Integrated Products 1

<sup>\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +6V                       | Maximum Current into IN1, IN2, IN3, SD/HD, FSEL±50mA |

|---------------------------------------------------------|------------------------------------------------------|

| IN1, IN2, IN3 to GND0.3V to (V <sub>CC</sub> + 0.3V)    | Operating Temperature Range                          |

| OUT1, OUT2, OUT3 to GND0.3V to (V <sub>CC</sub> + 0.3V) | MAX745_UUP0°C to +85°C                               |

| SD/HD, FSEL to GND0.3V to (V <sub>CC</sub> + 0.3V)      | Storage Temperature Range65°C to +150°C              |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)   | Lead Temperature (soldering, 10s)+300°C              |

| 20-Pin TSSOP (derate 21.7mW/°C above +70°C)1739.1mW     | Junction Temperature+150°C                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5V \pm 5\%, R_{LOAD} = 150\Omega \text{ to GND, } C_{LOAD} = 0 \text{ to 20pF to GND, } SD/\overline{HD} = GND, FSEL = V_{CC}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V$  and  $T_A = +25^{\circ}C$ .)

| PARAMETERS                     | SYMBOL            | CONDITIONS                                                                               | MIN   | TYP   | MAX | UNITS   |  |

|--------------------------------|-------------------|------------------------------------------------------------------------------------------|-------|-------|-----|---------|--|

| HD-Filter Passband Response    |                   | f = 100kHz to 26MHz, FSEL = GND                                                          | -3.5  | -2.0  |     |         |  |

|                                | APB               | f = 100kHz to 26MHz, FSEL = V <sub>CC</sub>                                              | -2.6  | -1.7  |     | dB      |  |

|                                |                   | f = 100kHz to 30MHz, FSEL = V <sub>CC</sub>                                              | -3.6  | -2.3  |     | ]       |  |

| HD-Filter Stopband Attenuation | AsB               | f = 74MHz, FSEL = GND                                                                    | 45    | 55    |     | dB      |  |

| SD-Filter Passband Response    |                   | $f = 10MHz$ , $SD/\overline{HD} = V_{CC}$ , $FSEL = V_{CC}$                              | -0.85 | -0.40 |     | dB      |  |

| SD-Filter Stopband Attenuation |                   | $f = 27MHz$ , $SD/\overline{HD} = V_{CC}$ , $FSEL = GND$                                 | 50    | 62    |     | dB      |  |

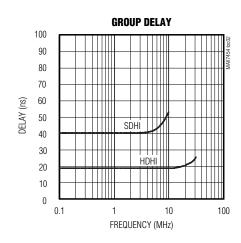

| HD Group Delay Deviation       | ΔtG               | 100kHz to 26MHz, relative to 100kHz; FSEL = VCC                                          |       | 4     |     | ns      |  |

| HD Group Delay Matching        | tG(MATCH)         | Channel to channel, 100kHz to 2MHz; FSEL = VCC                                           |       | 0.1   |     | ns      |  |

| SD Group Delay Deviation       |                   | 100kHz to 5.75MHz, relative to 100kHz;<br>SD/HD = VCC, FSEL = VCC                        |       | 2     |     |         |  |

|                                | Δt <sub>G</sub>   | 100kHz to 10MHz, relative to 100kHz;<br>SD/HD = V <sub>CC</sub> , FSEL = V <sub>CC</sub> |       | 12    |     | ns      |  |

| SD Group Delay Matching        | tG(MATCH)         | Channel to channel, 100kHz to 500kHz; FSEL = VCC                                         |       | 2     |     | ns      |  |

|                                | THD               | Gain = +2V/V, V <sub>OUT</sub> = 2V <sub>P-P</sub> video signal 100kHz to 26MHz          |       | -45   |     | - dB    |  |

| Total Harmonic Distortion      | IND               | Gain = +4V/V, V <sub>OUT</sub> = 2V <sub>P-P</sub> video signal 100kHz to 26MHz          |       | -53   |     | ] UD    |  |

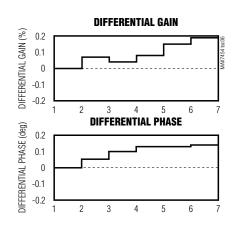

| Differential Gain              | dG                | 5-step modulated staircase (Note 1)                                                      |       | 0.3   |     | %       |  |

| Differential Phase             | dθ                | 5-step modulated staircase (Note 1)                                                      |       | 0.2   |     | Degrees |  |

| Signal-to-Noise Ratio          | SNR               | Output signal (2V <sub>P-P</sub> ) to RMS noise (100kHz to 30MHz)                        | 62    | 67    |     | dB      |  |

| Line Time Distortion           | H <sub>DIST</sub> | Deviations in a line with an 18µs, 100 IRE bar (Note 2)                                  |       | ±1    | ±3  | mV      |  |

|                                |                   | MAX7454, THD > -30dB, f <sub>IN</sub> = 4.43MHz                                          | 0     |       | 1.2 |         |  |

| Input Voltage Range            |                   | MAX7455, THD > -30dB, $f_{IN} = 4.43MHz$                                                 | 0     |       | 0.6 | -       |  |

\_\_\_\_\_\_NIXI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +5V \pm 5\%, R_{LOAD} = 150\Omega \text{ to GND, } C_{LOAD} = 0 \text{ to 20pF to GND, } SD/\overline{HD} = GND, FSEL = V_{CC}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V$  and  $T_A = +25^{\circ}C$ .)

| PARAMETERS                        | SYMBOL            | CONDITIONS                                                                  |                          | MIN   | TYP | MAX   | UNITS            |

|-----------------------------------|-------------------|-----------------------------------------------------------------------------|--------------------------|-------|-----|-------|------------------|

| Total Output DC Variation         |                   | V <sub>IN</sub> = 0.3V for the<br>MAX7454 or V <sub>IN</sub> =              | SD/HD = V <sub>C</sub> C | -0.25 |     | +0.25 | V                |

| Total Output DC Variation         |                   | 0.15V for the MAX7455,<br>FSEL = GND                                        | SD/HD = GND              | -0.25 |     | +0.25 | ]                |

| Field Time Distortion             | V <sub>DIST</sub> | 130 lines, 18µs, 100 IRE                                                    | bars                     |       | ±1  | ±10   | mV               |

| Input Leakage Current             | ΙΝ                |                                                                             |                          |       | ±10 |       | nA               |

| Input Capacitance                 | CIN               |                                                                             |                          |       | 5   |       | рF               |

| Low-Frequency Gain Accuracy       |                   | $f_{IN} = 100kHz$                                                           |                          | -2.5  |     | +2.5  | %                |

| Low-Frequency Gain Matching       |                   | f <sub>IN</sub> = 100kHz, maximum difference between any two input channels |                          |       | 0   | 1.2   | %                |

| Dynamic Output Swing              |                   | THD > -30dB                                                                 |                          | 2.4   |     |       | V <sub>P-P</sub> |

| Channel-to-Channel Isolation      |                   | DC to 1MHz                                                                  |                          |       | 70  |       | dB               |

| Davida Overska Daja stila a Datia | PSRR              | $V_{IN} = 100 \text{mVp-p}$ at $5 \text{MHz}$                               |                          |       | 35  |       | dB               |

| Power-Supply Rejection Ratio      |                   | V <sub>IN</sub> =10mV <sub>P-P</sub> at 26MHz                               |                          |       | 25  |       | uB               |

| Supply Voltage Range              | Vcc               |                                                                             |                          | 4.75  | 5   | 5.25  | V                |

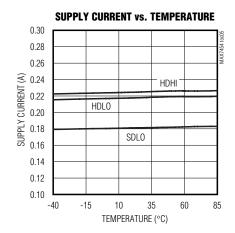

| Supply Current                    | Icc               | No load                                                                     |                          |       | 220 | 240   | mA               |

| LOGIC INPUTS (SD/HD, FSEL)        |                   |                                                                             |                          |       |     |       |                  |

| Input High Voltage                | VIH               |                                                                             |                          | 2.4   |     |       | V                |

| Input Low Voltage                 | $V_{IL}$          |                                                                             |                          |       |     | 0.8   | V                |

| Input Current                     |                   | Digital inputs = V <sub>CC</sub> or 0V                                      |                          |       |     | ±10   | μΑ               |

Note 1: The differential gain and differential phase specifications apply to standard-definition composite video signals only.

Note 2: This applies for an anti-aliasing filtering application using a 0.1µF input capacitor. This does not apply for a video reconstruction application, since there is no input-coupling capacitor.

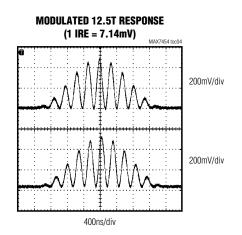

## Typical Operating Characteristics

$(R_{LOAD} = 150\Omega \text{ to GND}, V_{CC} = +5V, \text{ and } T_A = +25^{\circ}C.)$

## Typical Operating Characteristics (continued)

$(R_{LOAD} = 150\Omega \text{ to GND}, V_{CC} = +5V, \text{ and } T_A = +25^{\circ}C.)$

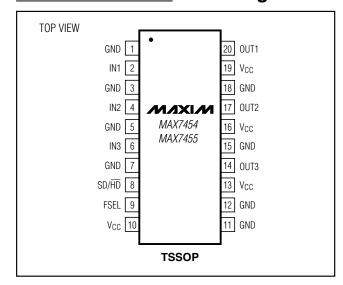

### **Pin Description**

| PIN                           | NAME  | FUNCTION                                                                                                                                   |

|-------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 7, 11,<br>12, 15, 18 | GND   | Ground                                                                                                                                     |

| 2                             | IN1   | Video Input 1                                                                                                                              |

| 4                             | IN2   | Video Input 2                                                                                                                              |

| 6                             | IN3   | Video Input 3                                                                                                                              |

| 8                             | SD/HD | SD/HD Select. Selects between HD or SD magnitude response. Connect to GND to choose HD bandwidth response.                                 |

| 9                             | FSEL  | Frequency Select. Selects either a low or high setting for both HD and SD frequency response (see the <i>Frequency Adjusting</i> section). |

| 10, 13, 16,<br>19             | Vcc   | +5V Power Supply. Bypass to GND with a 0.1µF capacitor. See the <i>Power-Supply Bypassing and Layout Considerations</i> section.           |

| 14                            | OUT3  | Video Output 3                                                                                                                             |

| 17                            | OUT2  | Video Output 2                                                                                                                             |

| 20                            | OUT1  | Video Output 1                                                                                                                             |

| _                             | EP    | Exposed Pad. The exposed pad is internally connected to ground.                                                                            |

### **Detailed Description**

The MAX7454/MAX7455 are ideal for use in consumer electronic products such as HD-compatible cable-TV set-top boxes or DBS receiver decoders, which process video signals in component output format. The MAX7454/MAX7455 support both the 1080i and the 720p scanning formats for HDTV as well as the 480i and 480p formats for SDi and SDp TV. The reconstruction filters take three signals out of a video digital-to-analog converter (DAC) or an encoder and smooth the signals with appropriate filtering. FSEL and SD/HD select the filter frequency response for SDp, SDi, and HDTV (see Table 1). The outputs are connected directly to standard  $150\Omega$  video loads.

The *Typical Operating Circuit* illustrates the internal structure of the MAX7454/MAX7455. The lowpass filter attenuates the high-frequency contents of the input, and the output amplifier drives a standard video load.

#### Filter

#### Filter Response

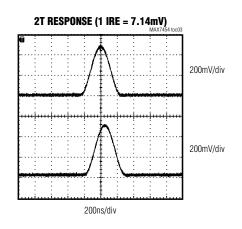

The video filter features an elliptic-type response with a steep transition band response to achieve a wider passband response along with an excellent stopband response. In addition, the filter has been optimized to give a good time domain response with low overshoot. The stopband offers 62dB (typ) of attenuation at sampling frequencies of 27MHz and above for SDTV and 55dB (typ) of stopband attenuation for

**Table 1. Frequency Selection Control**

| MODE    | SD/HD            | FSEL |

|---------|------------------|------|

| HD Low  | GND              | GND  |

| HD High | GND              | Vcc  |

| SD Low  | Vcc              | GND  |

| SD High | V <sub>C</sub> C | Vcc  |

frequencies of 74MHz and above for HDTV (see the *Typical Operating Characteristics*).

### Frequency Adjusting

SD/HD selects the HD or SD mode. In HD or SD mode, FSEL allows optimization of the passband or stopband performance by adjusting the cutoff frequency. If passband performance is the priority, set FSEL high for the maximum passband performance with a small compromise in stopband attenuation. If stopband performance is more important, set FSEL low for the maximum stopband attenuation with a small compromise in passband.

Due to the steep transition band response, the MAX7454/MAX7455 can be used in both progressive scan and interlaced video signals. The stopband attenuation at 27MHz or higher is >62dB.

#### **Output Buffer**

The output buffer on the MAX7454/MAX7455 drives a  $2V_{P-P}$  signal into a  $150\Omega$  video load. It is intended to be DC-coupled per the digital TV standard. No output AC-

coupling capacitors are required when driving a cable, thereby eliminating the normal adverse effects caused by these large capacitors. The output DC level is controlled to limit the DC voltage on the cable so the blanking level of the video signal is always less than 1V, meeting the digital TV specification. See the *Output DC Level* section for more information.

The output of the MAX7454/MAX7455 can also be AC-coupled when driving a high-impedance load. In antialiasing applications, when the optimum bias point for the converter needs to be established, the MAX7454/MAX7455 can drive a high impedance (typ >1k $\Omega$ ) through an AC-coupling capacitor.

#### **Gain Options**

The MAX7454 features an overall gain of +6dB, while the MAX7455 features an overall gain of +12dB.

#### **Output DC Level**

The MAX7454/MAX7455 are DC-coupled circuits. The nominal DC or nominal instantaneous AC voltage on the outputs of the MAX7454/MAX7455 can be determined by the following equations:

$V_{OUT} = 2 \times V_{IN} + 0.8V \text{ (MAX7454)}$  $V_{OUT} = 4 \times V_{IN} + 0.8V \text{ (MAX7455)}$

For example, in the MAX7454, 0V on the input results in an output nominal voltage of 0.8V, and a 0.3V input (typical blanking level) results in an output nominal level of 1.4V.

## Applications Information

#### **Input Considerations**

The inputs on the MAX7454/MAX7455 are normally DC-coupled. Thus, no AC-coupling capacitors are required. The input voltage range includes ground and typically extends up to 1.2V. If the input is from a typical single supply current output DAC or encoder it can be connected directly to the MAX7454/MAX7455. The board trace should be kept as short as possible to minimize the parasitic stray capacitance. The MAX7454/MAX7455 contribute 5pF of capacitance. For example, a total capacitance on the input of approximately 20pF causes a 100MHz pole if the DAC termination resistor is 75 $\Omega$ . A pole at 100MHz introduces an additional 0.5dB passband attenuation at 30MHz.

The input to the MAX7454/MAX7455 can be AC-coupled. In this case, it is important to set the DC bias properly to ensure that the negative peak of the video signal is as near to zero volts as possible. The bias can be fixed or a video clamp can be used. A video clamp is preferable because it limits the total swing of the signal by holding the blanking level of the signal constant.

#### **Output Considerations**

The outputs of the MAX7454/MAX7455 are normally DC-coupled. No AC-coupling capacitors are required. The MAX7454/MAX7455 connect directly to the video cable with a  $75\Omega$  series termination resistor. The other end of the cable should also be properly terminated with a  $75\Omega$  resistor. Because of the inherent divide-by-two of this configuration the peak-to-peak amplitude as well as the DC level of the signal are divided by two. The biasing on the output of the MAX7454/MAX7455 is such that the blanking level of the video signal on the cable is always less than 1V, which complies with digital TV requirements.

#### **Anti-Aliasing Filter**

The MAX7454/MAX7455 can be used as an anti-aliasing filter to eliminate out-of-band noise in an analog-todigital video-sampling system. The output of the MAX7454/MAX7455 can be DC- or AC-coupled. This decision depends on the input range of the analog-todigital converter and the required accuracy of the resulting digital blanking level. The output blanking level of the MAX7454/MAX7455 is 1.4V with the negative peak of the signal at 0.8V and the positive peak white at 2.8V. This assumes a 1V<sub>P-P</sub> input signal with the negative peak at OV. See the Electrical Characteristics table for the specified variations of these values. If the DC and peak levels are not compatible with the data-converter input, the outputs of the MAX7454/MAX7455 need to be AC-coupled. Choose an AC-coupling capacitor value that ensures that the lowest frequency content in the video signal is passed and the line time distortion is kept within desired limits. The resulting capacitor value is dependent on the input impedance of the converter circuit. Use a video clamp to re-establish the DC level.

# Power-Supply Bypassing and Layout Considerations

The MAX7454/MAX7455 operate from a single +5V supply. Bypass each  $V_{CC}$  to GND with a 0.1µF capacitor and an additional 1µF capacitor in parallel if any significant low-frequency disturbances are present in the vicinity of the MAX7454/MAX7455. Use an extensive ground plane to ensure optimum performance. The three  $V_{CC}$  pins (pins 13, 16, and 19) that supply the individual channels can be connected together and bypassed as one, provided the components are close to the pins. Bypass the remaining  $V_{CC}$  pin (pin 10) separately with the same 0.1µF and 1µF capacitor combination.

Place the input and output termination resistors as close to the device as possible. Alternatively, the terminations may be placed further from the device if the PC board

traces are designed to be a controlled impedance of  $75\Omega$ . Regardless, the parasitic capacitance should be kept as low as possible to avoid performance degradation in the frequency response at 30MHz.

Refer to the MAX7454/MAX7455 evaluation kit for a proven PC board layout.

#### **Exposed Pad and Heat Dissipation**

The TSSOP package of the MAX7454/MAX7455 has an exposed pad on its bottom. This pad is electrically connected to GND. Do not route signals under the package.

Heat dispersion is a very important issue for the MAX7454/MAX7455. The design of the PC board area associated with and in the vicinity of the device is important in achieving an adequate thermal resistance to keep the temperature of the MAX7454/MAX7455 within the specified limits.

The thermal resistance of the 20-pin TSSOP package is 60°C/W from die to ambient in free air. The thermal resistance from the die to the package surface (case) is 2°C/W. The net thermal resistance on a practical board is between these two numbers. The typical power dissipation of the MAX7454/MAX7455 is 1.2W. To keep the die temperature within specified limits, the maximum net thermal resistance should not exceed 30°C/W. This value is calculated assuming a worst-case ambient temperature of +85°C and the maximum die temperature.

The use of a 2-layer board with a good ground plane is recommended. Place copper directly under the MAX7454/MAX7455 package so that it matches the outline of the plastic encapsulated area. Place via holes in this area to electrically and thermally connect it to the ground plane. Use as many vias as possible for maximum heat transfer.

One tested board is a 4-layer board using FR-4 material and 1oz copper. It has equal areas of metal on the top side and bottom side that coincide with the plastic encapsulated area of the 20-pin TSSOP package. The two middle layers are power and ground planes. The board has 21 15-mil plated-through via holes between the top, bottom, and ground plane layers. This board was measured and has a total thermal resistance of 25°C/W, less than the 30°C/W goal.

## **Pin Configuration**

## **Chip Information**

TRANSISTOR COUNT: 19,191

PROCESS: BICMOS

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.