# WAN PLL<br/>IDT82V3280

Version 2 June 19, 2006

6024 Silver Creek Valley Road, San Jose, CA 95138

Telephone: (800) 345-7015 • TWX: 910-338-2070 • FAX: (408) 284-2775

Printed in U.S.A.

© 2006 Integrated Device Technology, Inc.

| DISCLAIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LIFE SUPPORT POLICY Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is exe-                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| cuted between the manufacturer and an officer of IDT.  1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in                                                                                                                                                                                                                                                                                                                                                                                                         |

| accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  2. A critical component is any components of a life support device or system, or to affect its                                                                                                                                                                                                                                                                                                                                                                                                                              |

| safety or effectiveness.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# **Table of Contents**

| FE | ATU  | RES    |                                                 | 9  |

|----|------|--------|-------------------------------------------------|----|

|    |      |        | IGHTS                                           |    |

|    |      |        | EATURES                                         |    |

|    |      |        | R FEATURES                                      |    |

| ΑF | PLIC |        | NS                                              |    |

|    |      |        | N                                               |    |

|    |      |        | BLOCK DIAGRAM                                   |    |

|    |      |        | SMENT                                           |    |

|    |      |        |                                                 |    |

|    |      |        | RIPTION                                         |    |

| 3  |      |        | IAL DESCRIPTION                                 |    |

|    |      |        |                                                 |    |

|    |      |        | ER CLOCK                                        |    |

|    | 3.3  |        | CLOCKS & FRAME SYNC SIGNAL                      |    |

|    |      |        | Input Clocks                                    |    |

|    | 2.4  |        | Frame SYNC Input Signals                        |    |

|    |      |        | CLOCK PRE-DIVIDERCLOCK QUALITY MONITORING       |    |

|    | 3.5  |        | LOS Monitoring                                  |    |

|    |      |        | Activity Monitoring                             |    |

|    |      |        | Frequency Monitoring                            |    |

|    | 3.6  |        | DPLL INPUT CLOCK SELECTION                      |    |

|    | 3.0  |        | External Fast Selection (T0 only)               |    |

|    |      |        | Forced Selection                                |    |

|    |      |        | Automatic Selection                             |    |

|    | 3.7  |        | TED INPUT CLOCK MONITORING                      |    |

|    | 0    |        | T0 / T4 DPLL Locking Detection                  |    |

|    |      | •      | 3.7.1.1 Fast Loss                               |    |

|    |      |        | 3.7.1.2 Coarse Phase Loss                       |    |

|    |      |        | 3.7.1.3 Fine Phase Loss                         |    |

|    |      |        | 3.7.1.4 Hard Limit Exceeding                    |    |

|    |      | 3.7.2  | Locking Status                                  |    |

|    |      |        | Phase Lock Alarm (T0 only)                      |    |

|    | 3.8  | SELEC  | TED INPUT CLOCK SWITCH                          | 29 |

|    |      | 3.8.1  | Input Clock Validity                            | 29 |

|    |      | 3.8.2  | Selected Input Clock Switch                     | 29 |

|    |      |        | 3.8.2.1 Revertive Switch                        | 29 |

|    |      |        | 3.8.2.2 Non-Revertive Switch (T0 only)          |    |

|    |      |        | Selected / Qualified Input Clocks Indication    |    |

|    | 3.9  |        | TED INPUT CLOCK STATUS VS. DPLL OPERATING MODE  |    |

|    |      |        | T0 Selected Input Clock vs. DPLL Operating Mode |    |

|    |      |        | T4 Selected Input Clock vs. DPLL Operating Mode |    |

|    | 3.10 |        | DPLL OPERATING MODE                             |    |

|    |      | 3.10.1 | T0 DPLL Operating Mode                          |    |

|    |      |        | 3.10.1.1 Free-Run Mode                          |    |

|    |      |        | 3.10.1.2 Pre-Locked Mode                        | 34 |

|    |      |        | 5 HL L 5 L OCKEO WOOD                           | ≺/ |

|   |      |        | 3.10.1.3.1 Temp-Holdover Mode                                   | . 34 |

|---|------|--------|-----------------------------------------------------------------|------|

|   |      |        | 3.10.1.4 Lost-Phase Mode                                        |      |

|   |      |        | 3.10.1.5 Holdover Mode                                          |      |

|   |      |        | 3.10.1.5.1 Automatic Instantaneous                              |      |

|   |      |        | 3.10.1.5.2 Automatic Slow Averaged                              |      |

|   |      |        | 3.10.1.5.3 Automatic Fast Averaged                              |      |

|   |      |        | 3.10.1.5.4 Manual                                               |      |

|   |      |        | 3.10.1.5.5 Holdover Frequency Offset Read                       |      |

|   |      |        | 3.10.1.6 Pre-Locked2 Mode                                       |      |

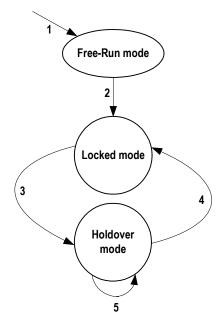

|   |      | 3.10.2 | T4 DPLL Operating Mode                                          |      |

|   |      |        | 3.10.2.1 Free-Run Mode                                          |      |

|   |      |        | 3.10.2.2 Locked Mode                                            |      |

|   |      |        | 3.10.2.3 Holdover Mode                                          |      |

|   | 3.11 |        | I DPLL OUTPUT                                                   |      |

|   |      |        | PFD Output Limit                                                |      |

|   |      |        | Frequency Offset Limit                                          |      |

|   |      |        | PBO (T0 only)                                                   |      |

|   |      |        | Phase Offset Selection (T0 only)                                |      |

|   |      | 3.11.5 | Four Paths of T0 / T4 DPLL Outputs                              |      |

|   |      |        | 3.11.5.1 TO Path                                                |      |

|   |      | / - /  | 3.11.5.2 T4 Path                                                |      |

|   |      |        | APLL                                                            |      |

|   | 3.13 |        | UT CLOCKS & FRAME SYNC SIGNALS                                  |      |

|   |      |        | Output Clocks                                                   |      |

|   | 244  |        | Frame SYNC Output Signals                                       |      |

|   |      |        | ER / SLAVE CONFIGURATION                                        |      |

|   |      |        | RUPT SUMMARY                                                    |      |

|   |      |        | D T4 SUMMARY                                                    |      |

|   |      |        | R SUPPLY FILTERING TECHNIQUES                                   |      |

| 4 |      |        | APPLICATION                                                     |      |

| _ |      |        | ER / SLAVE APPLICATION                                          |      |

| 5 | MIC  |        | OCESSOR INTERFACE                                               |      |

|   | 5.1  |        | M MODE                                                          |      |

|   | 5.2  |        | PLEXED MODE                                                     |      |

|   | 5.3  |        | MODE                                                            |      |

|   | 5.4  | мото   | ROLA MODE                                                       |      |

| _ | 5.5  |        | L MODE                                                          |      |

| 6 |      |        |                                                                 |      |

| 7 | PRC  | OGRAI  | MMING INFORMATION                                               | . 59 |

|   | 7.1  | REGIS  | STER MAP                                                        | 59   |

|   | 7.2  |        | STER DESCRIPTION                                                |      |

|   |      | 7.2.1  | Global Control Registers                                        | . 65 |

|   |      | 7.2.2  | Interrupt Registers                                             | . 74 |

|   |      | 7.2.3  | Input Clock Frequency & Priority Configuration Registers        | . 79 |

|   |      | 7.2.4  | Input Clock Quality Monitoring Configuration & Status Registers |      |

|   |      |        | T0 / T4 DPLL Input Clock Selection Registers                    |      |

|   |      |        | T0 / T4 DPLL State Machine Control Registers                    |      |

|   |      | 7.2.7  | T0 / T4 DPLL & APLL Configuration Registers                     | 122  |

|   |      | 7.2.8  | Output Configuration Registers                                  |      |

|   |      |        | PBO & Phase Offset Control Registers                            |      |

|   |      | 7.2.10 | Synchronization Configuration Registers                         | 148  |

| 8 | THE  | RMAL   | _ MANAGEMENT                                                    | 149  |

|   | Q 1  | HINCT  | TION TEMPERATURE                                                | 1/0  |

| 8.2 | <b>EXAM</b>                                   | PLE OF J                                                                                                   | IUNCTION TEMPERATURE CALCULATION                                                                                                                                                                                                                                  | 149                                                                                                                                                                                            |

|-----|-----------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.3 | HEATS                                         | SINK EVA                                                                                                   | \LUATION                                                                                                                                                                                                                                                          | 149                                                                                                                                                                                            |

| ELE | CTRIC                                         | CAL SPI                                                                                                    | ECIFICATIONS                                                                                                                                                                                                                                                      | 150                                                                                                                                                                                            |

| 9.1 | ABSO                                          | LUTE MA                                                                                                    | XIMUM RATING                                                                                                                                                                                                                                                      | 150                                                                                                                                                                                            |

| 9.2 | RECO                                          | MMENDE                                                                                                     | D OPERATION CONDITIONS                                                                                                                                                                                                                                            | 150                                                                                                                                                                                            |

| 9.3 | I/O SP                                        | ECIFICAT                                                                                                   | TIONS                                                                                                                                                                                                                                                             | 151                                                                                                                                                                                            |

| 0.0 | 9.3.1                                         | AMI Inp                                                                                                    | ut / Output Port                                                                                                                                                                                                                                                  | 151                                                                                                                                                                                            |

|     |                                               | 9.3.1.1                                                                                                    | Structure                                                                                                                                                                                                                                                         | 151                                                                                                                                                                                            |

|     |                                               | 9.3.1.2                                                                                                    | I/O Level                                                                                                                                                                                                                                                         | 151                                                                                                                                                                                            |

|     |                                               | 9.3.1.3                                                                                                    | Over-Voltage Protection                                                                                                                                                                                                                                           | 153                                                                                                                                                                                            |

|     | 9.3.2                                         | CMOS I                                                                                                     | nput / Output Port                                                                                                                                                                                                                                                | 153                                                                                                                                                                                            |

|     | 9.3.3                                         | PECL / I                                                                                                   | LVDS Input / Output Port                                                                                                                                                                                                                                          | 154                                                                                                                                                                                            |

|     |                                               | 9.3.3.1                                                                                                    | PECL Input / Output Port                                                                                                                                                                                                                                          | 154                                                                                                                                                                                            |

|     |                                               | 9.3.3.2                                                                                                    | LVDS Input / Output Port                                                                                                                                                                                                                                          | 156                                                                                                                                                                                            |

| 9.4 | JITTER                                        |                                                                                                            |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                |

| 9.5 | OUTP                                          | UT WAND                                                                                                    | DER GENERATION                                                                                                                                                                                                                                                    | 160                                                                                                                                                                                            |

| 9.6 |                                               |                                                                                                            |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                |

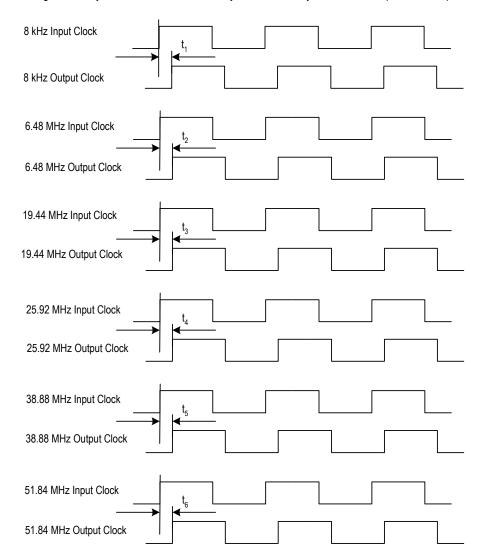

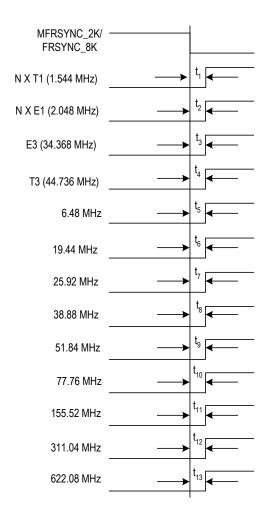

| 9.7 | OUTP                                          | UT CLOC                                                                                                    | K TIMING                                                                                                                                                                                                                                                          | 162                                                                                                                                                                                            |

| ORI |                                               |                                                                                                            |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                |

|     | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7 | 8.3 HEATS ELECTRIC 9.1 ABSO 9.2 RECO 9.3 I/O SP 9.3.1  9.3.2 9.3.3  9.4 JITTEI 9.5 OUTP 9.6 INPUT 9.7 OUTP | 8.3 HEATSINK EVA<br>ELECTRICAL SPI<br>9.1 ABSOLUTE MA<br>9.2 RECOMMENDE<br>9.3 I/O SPECIFICA<br>9.3.1.1 9.3.1.2<br>9.3.1.3<br>9.3.2 CMOS I<br>9.3.3 PECL / I<br>9.3.3.1<br>9.3.3.2<br>9.4 JITTER & WAN<br>9.5 OUTPUT WAND<br>9.6 INPUT / OUTPU<br>9.7 OUTPUT CLOC | 9.3.1       AMI Input / Output Port         9.3.1.1       Structure         9.3.1.2       I/O Level         9.3.1.3       Over-Voltage Protection         9.3.2       CMOS Input / Output Port |

# **List of Tables**

|           | Pin Description                                                                                |    |

|-----------|------------------------------------------------------------------------------------------------|----|

| Table 2:  | Related Bit / Register in Chapter 3.2                                                          | 19 |

|           | Related Bit / Register in Chapter 3.3                                                          |    |

| Table 4:  | Related Bit / Register in Chapter 3.4                                                          | 22 |

| Table 5:  | Related Bit / Register in Chapter 3.5                                                          | 24 |

| Table 6:  | Input Clock Selection for T0 Path                                                              | 25 |

| Table 7:  | Input Clock Selection for T4 Path                                                              | 25 |

|           | External Fast Selection                                                                        |    |

|           | Related Bit / Register in Chapter 3.6                                                          |    |

| Table 10: | Coarse Phase Limit Programming (the selected input clock of 2 kHz, 4 kHz or 8 kHz)             | 27 |

| Table 11: | Coarse Phase Limit Programming (the selected input clock of other than 2 kHz, 4 kHz and 8 kHz) | 27 |

| Table 12: | Related Bit / Register in Chapter 3.7                                                          | 28 |

| Table 13: | Conditions of Qualified Input Clocks Available for T0 & T4 Selection                           | 29 |

| Table 14: | Related Bit / Register in Chapter 3.8                                                          | 30 |

| Table 15: | T0 DPLL Operating Mode Control                                                                 | 31 |

| Table 16: | T4 DPLL Operating Mode Control                                                                 | 33 |

|           | Related Bit / Register in Chapter 3.9                                                          |    |

|           | Frequency Offset Control in Temp-Holdover Mode                                                 |    |

|           | Frequency Offset Control in Holdover Mode                                                      |    |

|           | Holdover Frequency Offset Read                                                                 |    |

| Table 21: | Related Bit / Register in Chapter 3.10                                                         | 36 |

|           | Related Bit / Register in Chapter 3.11                                                         |    |

|           | Related Bit / Register in Chapter 3.12                                                         |    |

|           | Outputs on OUT1 ~ OUT7 if Derived from T0/T4 DPLL Outputs                                      |    |

|           | Outputs on OUT1 ~ OUT7 if Derived from T0/T4 APLL                                              |    |

|           | Outputs on OUT8 & OUT9                                                                         |    |

|           | Synchronization Control                                                                        |    |

|           | Related Bit / Register in Chapter 3.13                                                         |    |

|           | Device Master / Slave Control                                                                  |    |

|           | Related Bit / Register in Chapter 3.15                                                         |    |

|           | Microprocessor Interface                                                                       |    |

|           | Access Timing Characteristics in EPROM Mode                                                    |    |

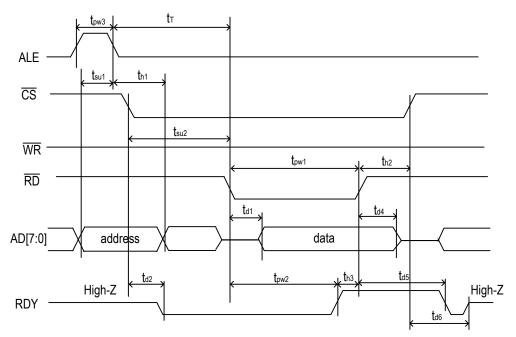

|           | Read Timing Characteristics in Multiplexed Mode                                                |    |

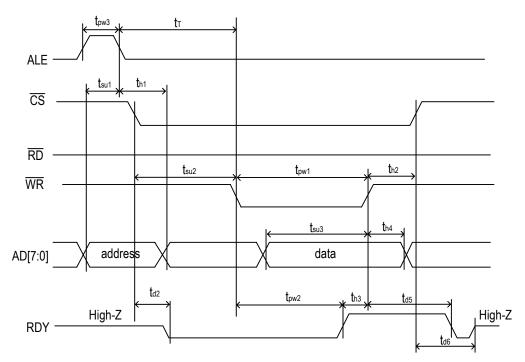

|           | Write Timing Characteristics in Multiplexed Mode                                               |    |

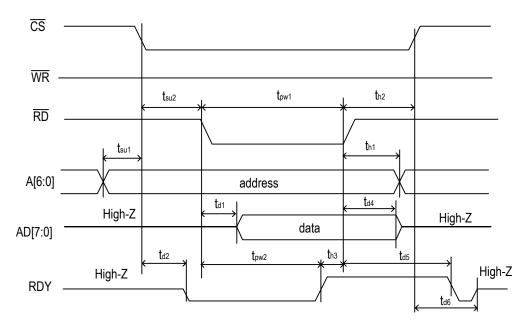

|           | Read Timing Characteristics in Intel Mode                                                      |    |

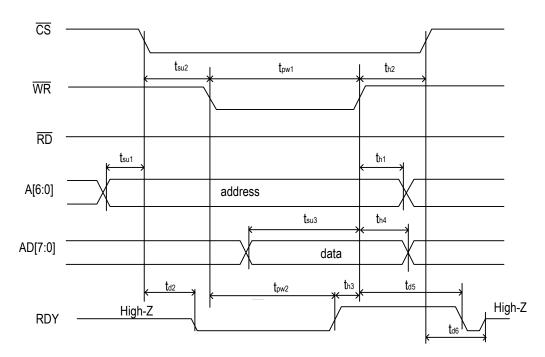

|           | Write Timing Characteristics in Intel Mode                                                     |    |

|           | Read Timing Characteristics in Motorola Mode                                                   |    |

|           | Write Timing Characteristics in Motorola Mode                                                  |    |

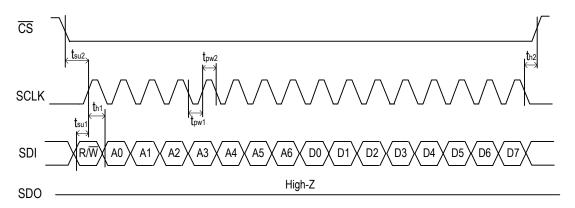

|           | Read Timing Characteristics in Serial Mode                                                     |    |

|           | Write Timing Characteristics in Serial Mode                                                    |    |

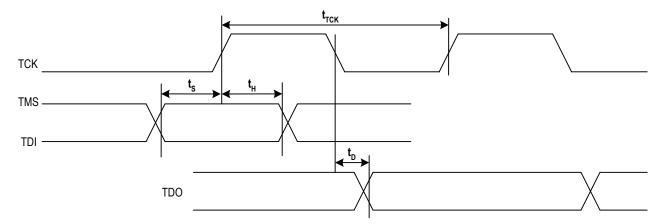

|           | JTAG Timing Characteristics                                                                    |    |

|           | Register List and Map                                                                          |    |

|           | Power Consumption and Maximum Junction Temperature                                             |    |

|           | Thermal Data                                                                                   |    |

|           | Absolute Maximum Rating                                                                        |    |

|           | Recommended Operation Conditions                                                               |    |

|           | AMI Input / Output Port Electrical Characteristics                                             |    |

|           | CMOS Input Port Electrical Characteristics                                                     |    |

|           |                                                                                                |    |

| Table 49: | CMOS Input Port with Internal Pull-Up Resistor Electrical Characteristics   | 153 |

|-----------|-----------------------------------------------------------------------------|-----|

|           | CMOS Input Port with Internal Pull-Down Resistor Electrical Characteristics |     |

| Table 51: | CMOS Output Port Electrical Characteristics                                 | 153 |

| Table 52: | PECL Input / Output Port Electrical Characteristics                         | 155 |

| Table 53: | LVDS Input / Output Port Electrical Characteristics                         | 156 |

|           | Output Clock Jitter Generation                                              |     |

|           | Output Clock Phase Noise                                                    |     |

|           | Input Jitter Tolerance (155.52 MHz)                                         |     |

| Table 57: | Input Jitter Tolerance (1.544 MHz)                                          | 158 |

| Table 58: | Input Jitter Tolerance (2.048 MHz)                                          | 158 |

| Table 59: | Input Jitter Tolerance (8 kHz)                                              | 158 |

| Table 60: | TO DPLL Jitter Transfer & Damping Factor                                    | 159 |

| Table 61: | T4 DPLL Jitter Transfer & Damping Factor                                    | 159 |

| Table 62: | Input/Output Clock Timing 3                                                 | 161 |

| Table 63: | Output Clock Timing                                                         | 162 |

|           |                                                                             |     |

# **List of Figures**

| Figure 1. | Functional Block Diagram                                        | 11 |

|-----------|-----------------------------------------------------------------|----|

| Figure 2. | Pin Assignment (Top View)                                       | 12 |

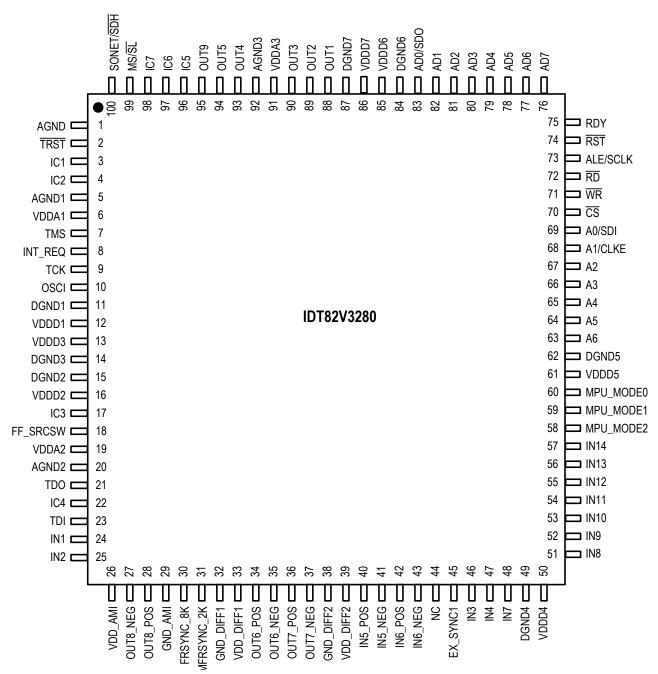

| Figure 3. | Pre-Divider for An Input Clock                                  | 21 |

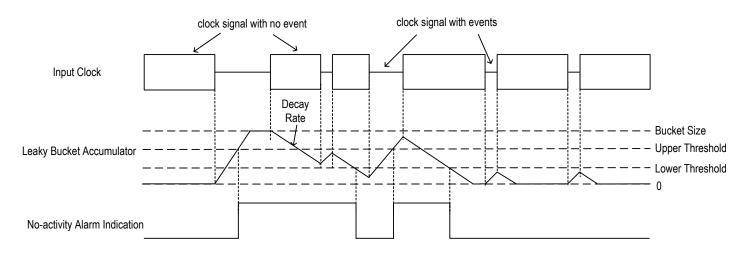

| Figure 4. | Input Clock Activity Monitoring                                 | 23 |

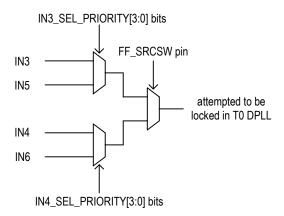

| Figure 5. | External Fast Selection                                         | 25 |

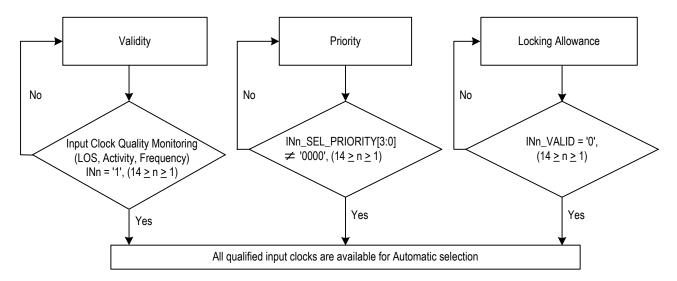

| Figure 6. | Qualified Input Clocks for Automatic Selection                  | 26 |

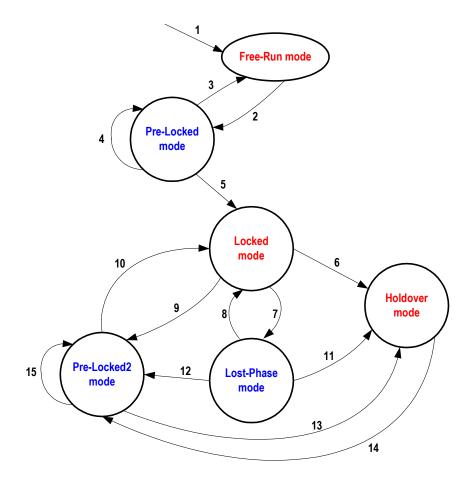

| Figure 7. | T0 Selected Input Clock vs. DPLL Automatic Operating Mode       | 32 |

| Figure 8. | T4 Selected Input Clock vs. DPLL Automatic Operating Mode       | 33 |

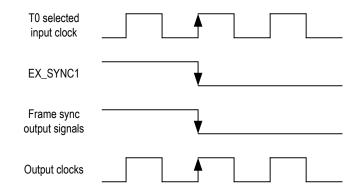

| Figure 9. | On Target Frame Sync Input Signal Timing                        | 42 |

| Figure 10 | . 0.5 UI Early Frame Sync Input Signal Timing                   | 42 |

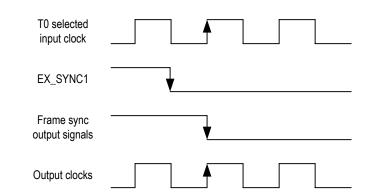

| Figure 11 | . 0.5 UI Late Frame Sync Input Signal Timing                    | 43 |

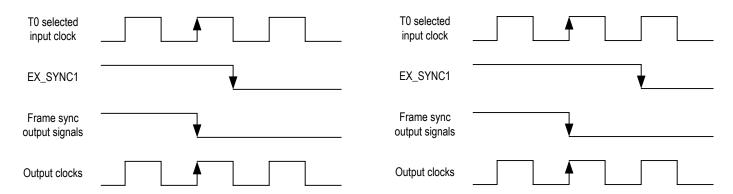

| Figure 12 | . 1 UI Late Frame Sync Input Signal Timing                      | 43 |

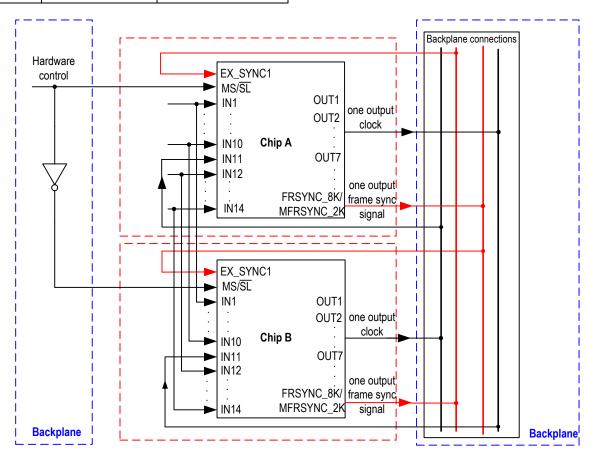

| Figure 13 | Physical Connection Between Two Devices                         | 44 |

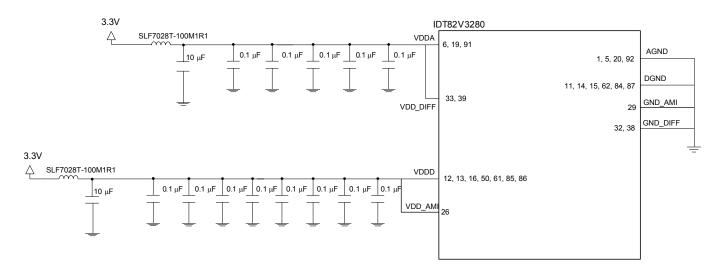

| Figure 14 | . IDT82V3280 Power Decoupling Scheme                            | 46 |

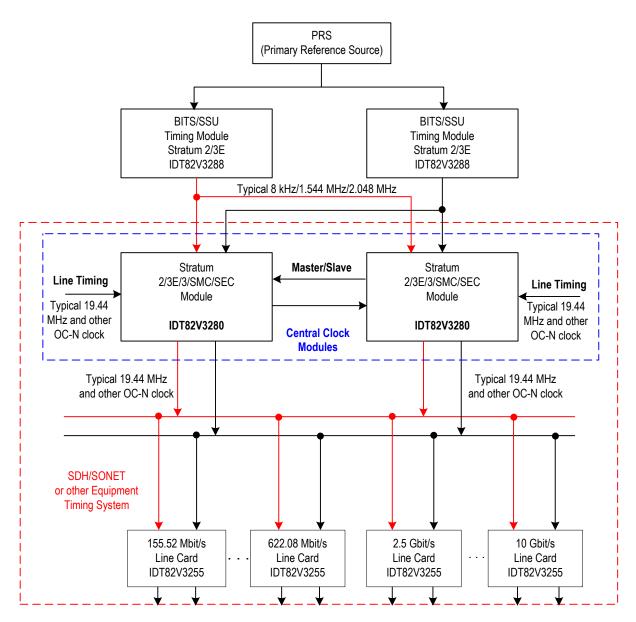

| Figure 15 | Typical Application                                             | 47 |

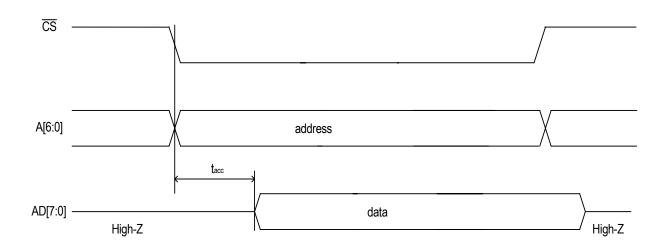

| Figure 16 | EPROM Access Timing Diagram                                     | 49 |

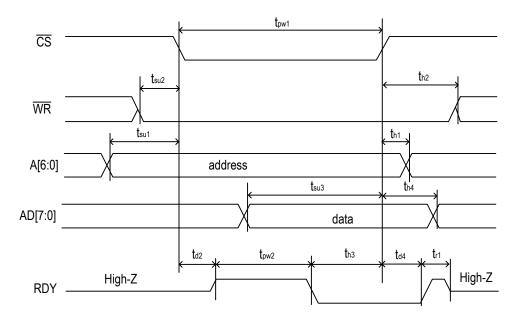

| Figure 17 | . Multiplexed Read Timing Diagram                               | 50 |

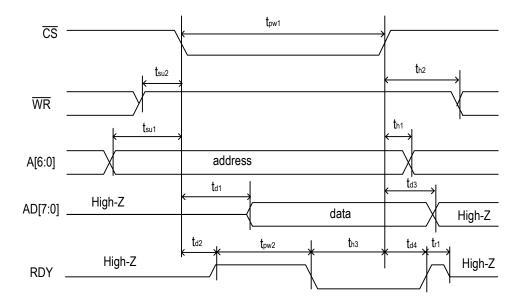

| Figure 18 | Multiplexed Write Timing Diagram                                | 51 |

| Figure 19 | . Intel Read Timing Diagram                                     | 52 |

| Figure 20 | . Intel Write Timing Diagram                                    | 53 |

| Figure 21 | . Motorola Read Timing Diagram                                  | 54 |

| Figure 22 | . Motorola Write Timing Diagram                                 | 55 |

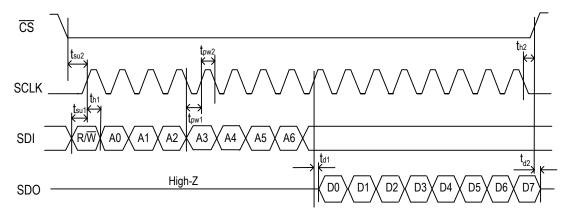

| Figure 23 | Serial Read Timing Diagram (CLKE Asserted Low)                  | 56 |

| Figure 24 | . Serial Read Timing Diagram (CLKE Asserted High)               | 56 |

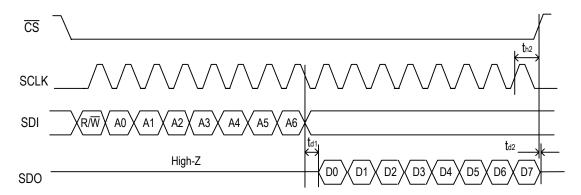

|           | Serial Write Timing Diagram                                     |    |

| Figure 26 | . JTAG Interface Timing Diagram                                 | 58 |

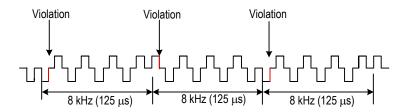

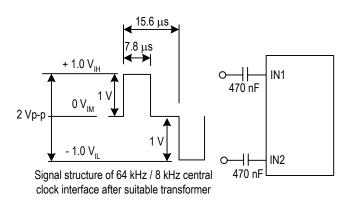

| Figure 27 | . 64 kHz + 8 kHz Signal Structure                               | 51 |

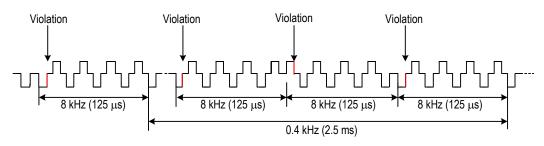

| Figure 28 | . 64 kHz + 8 kHz + 0.4 kHz Signal Structure                     | 51 |

| Figure 29 | . 64 kHz + 8 kHz / 64 kHz + 8 kHz + 0.4 kHz Signal Input Level  | 51 |

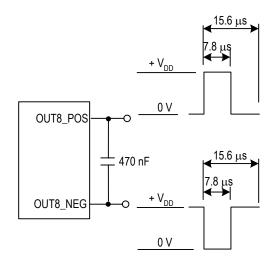

| Figure 30 | . 64 kHz + 8 kHz / 64 kHz + 8 kHz + 0.4 kHz Signal Output Level | 51 |

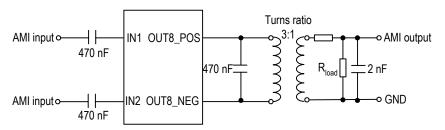

| Figure 31 | . AMI Input / Output Port Line Termination (Recommended)        | 52 |

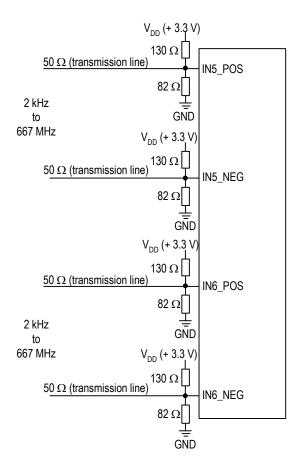

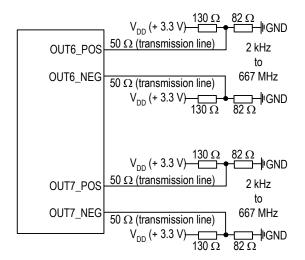

| Figure 32 | . Recommended PECL Input Port Line Termination                  | 54 |

| Figure 33 | Recommended PECL Output Port Line Termination                   | 54 |

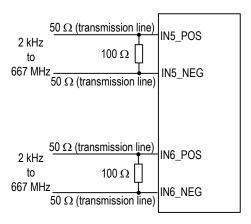

| Figure 34 | Recommended LVDS Input Port Line Termination                    | 56 |

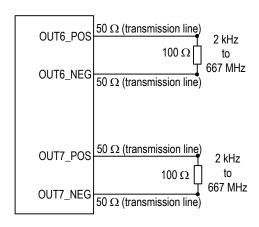

| Figure 35 | Recommended LVDS Output Port Line Termination                   | 56 |

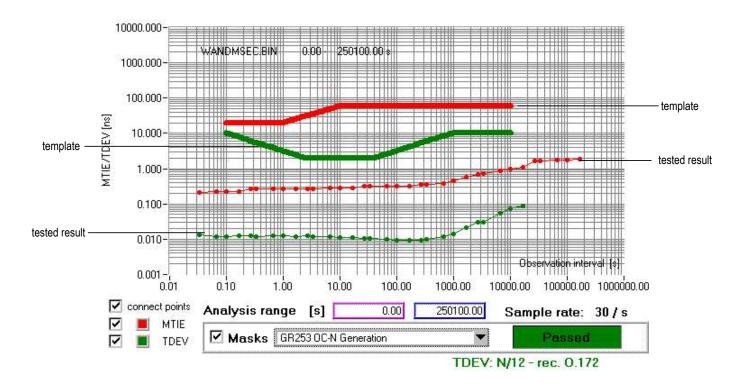

| Figure 36 | Output Wander Generation 1                                      | 60 |

| Figure 37 | . Input / Output Clock Timing                                   | 61 |

# **WAN PLL**

# **FEATURES**

# HIGHLIGHTS

- The first single PLL chip:

- · Features 0.5 mHz to 560 Hz bandwidth

- Exceeds GR-253-CORE (OC-12) and ITU-T G.813 (STM-16/ Option I) iitter generation requirements

- · Provides node clocks for Cellular and WLL base-station (GSM and 3G networks)

- · Provides clocks for DSL access concentrators (DSLAM), especially for Japan TCM-ISDN network timing based ADSL equipments

#### MAIN FEATURES

- Provides an integrated single-chip solution for Synchronous Equipment Timing Source, including Stratum 2, 3E, 3, SMC, 4E and 4 clocks

- Employs DPLL and APLL to feature excellent litter performance and minimize the number of the external components

- Integrates T0 DPLL and T4 DPLL; T4 DPLL locks independently or locks to T0 DPLL

- Supports Forced or Automatic operating mode switch controlled by an internal state machine; the primary operating modes are Free-Run. Locked and Holdover

- Supports programmable DPLL bandwidth (0.5 mHz to 560 Hz in 19 steps) and damping factor (1.2 to 20 in 5 steps)

- Supports 1.1X10<sup>-5</sup> ppm absolute holdover accuracy and 4.4X10<sup>-8</sup> ppm instantaneous holdover accuracy

- Supports PBO to minimize phase transients on T0 DPLL output to be no more than 0.61 ns

- Supports phase absorption when phase-time changes on T0 selected input clock are greater than a programmable limit over an interval of less than 0.1 seconds

- Supports programmable input-to-output phase offset adjustment

- Limits the phase and frequency offset of the outputs

- Supports manual and automatic selected input clock switch

- Supports automatic hitless selected input clock switch on clock fail-

- Supports three types of input clock sources: recovered clock from STM-N or OC-n, PDH network synchronization timing and external synchronization reference timing

- Provides a 2 kHz, 4 kHz or 8 kHz frame sync input signal, and a 2 kHz and an 8 kHz frame sync output signals

- Provides 14 input clocks whose frequency cover from 2 kHz to 622.08 MHz

- Provides 9 output clocks whose frequency cover from 1 Hz to 622.08 MHz

- Provides output clocks for BITS, GPS, 3G, GSM, etc.

- Supports AMI, PECL/LVDS and CMOS input/output technologies

- Supports master clock calibration

- Supports Master/Slave application (two chips used together) to enable system protection against single chip failure

- Meets Telcordia GR-1244-CORE, GR-253-CORE, GR-1377-CORE, ITU-T G.812, ITU-T G.813 and ITU-T G.783 criteria

# OTHER FEATURES

- Multiple microprocessor interface modes: EPROM, Multiplexed, Intel, Motorola and Serial

- IEEE 1149.1 JTAG Boundary Scan

- Single 3.3 V operation with 5 V tolerant CMOS I/Os

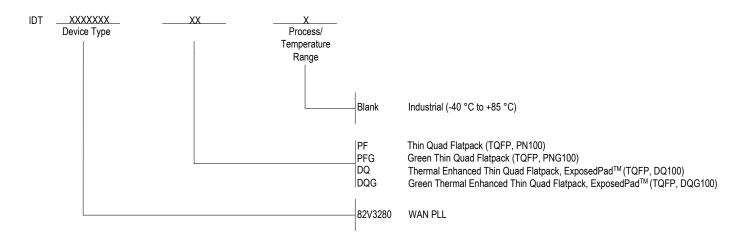

- 100-pin TQFP package, Green package options available

# **APPLICATIONS**

- BITS / SSU

- SMC / SEC (SONET / SDH)

- DWDM cross-connect and transmission equipments

- Central Office Timing Source and Distribution

- Core and access IP switches / routers

- Gigabit and Terabit IP switches / routers

- IP and ATM core switches and access equipments

- Cellular and WLL base-station node clocks

- Broadband and multi-service access equipments

- Any other telecom equipments that need synchronous equipment system timing

# **DESCRIPTION**

The IDT82V3280 is an integrated, single-chip solution for the Synchronous Equipment Timing Source for Stratum 2, 3E, 3, SMC, 4E and 4 clocks in SONET / SDH equipments, DWDM and Wireless base station, such as GSM, 3G, DSL concentrator, Router and Access Network applications.

The device supports three types of input clock sources: recovered clock from STM-N or OC-n, PDH network synchronization timing and external synchronization reference timing.

Based on ITU-T G.783 and Telcordia GR-253-CORE, the device consists of T0 and T4 paths. The T0 path is a high quality and highly configurable path to provide system clock for node timing synchronization within a SONET / SDH network. The T4 path is simpler and less configurable for equipment synchronization. The T4 path locks independently from the T0 path or locks to the T0 path.

An input clock is automatically or manually selected for T0 and T4 each for DPLL locking. Both the T0 and T4 paths support three primary operating modes: Free-Run, Locked and Holdover. In Free-Run mode, the DPLL refers to the master clock. In Locked mode, the DPLL locks to the selected input clock. In Holdover mode, the DPLL resorts to the fre-

quency data acquired in Locked mode. Whatever the operating mode is, the DPLL gives a stable performance without being affected by operating conditions or silicon process variations.

If the DPLL outputs are processed by T0/T4 APLL, the outputs of the device will be in a better jitter/wander performance.

The device provides programmable DPLL bandwidths: 0.5 mHz to 560 Hz in 19 steps and damping factors: 1.2 to 20 in 5 steps. Different settings cover all SONET / SDH clock synchronization requirements.

A high stable input is required for the master clock in different applications. The master clock is used as a reference clock for all the internal circuits in the device. It can be calibrated within ±741 ppm.

All the read/write registers are accessed through a microprocessor interface. The device supports five microprocessor interface modes: EPROM, Multiplexed, Intel, Motorola and Serial.

In general, the device can be used in Master/Slave application. In this application, two devices should be used together to enable system protection against single chip failure. See Chapter 4 Typical Application for details.

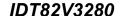

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

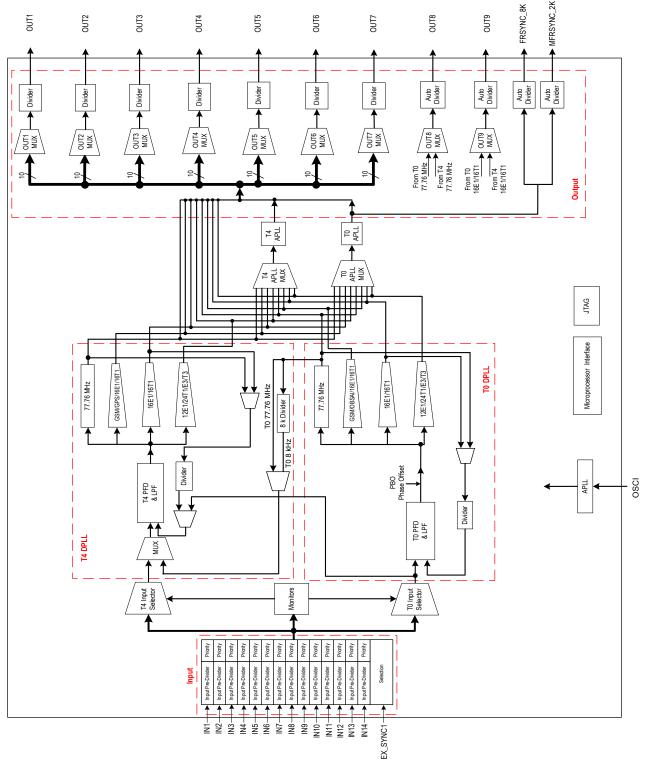

# 1 PIN ASSIGNMENT

Figure 2. Pin Assignment (Top View)

# 2 PIN DESCRIPTION

**Table 1: Pin Description**

| Name      | Pin No.               | I/O            | Туре         | Description <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----------|-----------------------|----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|           | Global Control Signal |                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| OSCI      | 10                    | I              | CMOS         | OSCI: Crystal Oscillator Master Clock A nominal 12.8000 MHz clock provided by a crystal oscillator is input on this pin. It is the master clock for the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| FF_SRCSW  | 18                    | l<br>pull-down | CMOS         | FF_SRCSW: External Fast Selection Enable  During reset, this pin determines the default value of the EXT_SW bit (b4, 0BH) <sup>2</sup> . The EXT_SW bit determines whether the External Fast Selection is enabled.  High: The default value of the EXT_SW bit (b4, 0BH) is '1' (External Fast selection is enabled);  Low: The default value of the EXT_SW bit (b4, 0BH) is '0' (External Fast selection is disabled).  After reset, this pin selects an input clock pair for the T0 DPLL if the External Fast selection is enabled:  High: Pair IN3 / IN5 is selected.  Low: Pair IN4 / IN6 is selected.  After reset, the input on this pin takes no effect if the External Fast selection is disabled. |  |  |  |  |

| MS/SL     | 99                    | l<br>pull-up   | CMOS         | MS/SL: Master / Slave Selection This pin, together with the MS_SL_CTRL bit (b0, 13H), controls whether the device is configured as the Master or as the Slave. Refer to Chapter 3.14 Master / Slave Configuration for details. The signal level on this pin is reflected by the MASTER_SLAVE bit (b1, 09H).                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| SONET/SDH | 100                   | l<br>pull-down | CMOS         | SONET/SDH: SONET / SDH Frequency Selection  During reset, this pin determines the default value of the IN_SONET_SDH bit (b2, 09H):  High: The default value of the IN_SONET_SDH bit is '1' (SONET);  Low: The default value of the IN_SONET_SDH bit is '0' (SDH).  After reset, the value on this pin takes no effect.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| RST       | 74                    | l<br>pull-up   | CMOS         | RST: Reset A low pulse of at least 50 µs on this pin resets the device. After this pin is high, the device will still be held in reset state for 500 ms (typical).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|           |                       |                | Frame        | Synchronization Input Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| EX_SYNC1  | 45                    | I<br>pull-down | CMOS         | EX_SYNC1: External Sync Input 1 A 2 kHz, 4 kHz or 8 kHz signal is input on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|           |                       | •              |              | Input Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| IN1       | 24                    | I              | AMI          | IN1: Input Clock 1 A 64 kHz + 8 kHz or 64 kHz + 8 kHz + 0.4 kHz composite clock is input on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| IN2       | 25                    | I              | AMI          | IN2: Input Clock 2 A 64 kHz + 8 kHz + 8 kHz + 0.4 kHz composite clock is input on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| IN3       | 46                    | l<br>pull-down | CMOS         | $ \begin{array}{l} \textbf{IN3: Input Clock 3} \\ \text{A 2 kHz, 4 kHz, N x 8 kHz}  ^3,  1.544  \text{MHz (SONET)}  /  2.048  \text{MHz (SDH)},  6.48  \text{MHz, 19.44 MHz,} \\ 25.92  \text{MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.} \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| IN4       | 47                    | l<br>pull-down | CMOS         | $ \begin{array}{l} \textbf{IN4: Input Clock 4} \\ \textbf{A 2 kHz, 4 kHz, N x 8 kHz} \\ \textbf{^3, 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz,} \\ \textbf{25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.} \\ \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| IN5_POS   | 40                    |                | DE01 ** \ 'T | IN5_POS / IN5_NEG: Positive / Negative Input Clock 5 A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| IN5_NEG   | 41                    |                | PECL/LVDS    | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz or 622.08 MHz clock is differentially input on this pair of pins. Whether the clock signal is PECL or LVDS is automatically detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

Table 1: Pin Description (Continued)

| Name       | Pin No. | I/O            | Туре      | Description <sup>1</sup>                                                                                                                                                                                                      |

|------------|---------|----------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |         |                |           | IN6_POS / IN6_NEG: Positive / Negative Input Clock 6                                                                                                                                                                          |

| IN6_POS    | 42      |                |           | A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz                                                                                                                             |

| INC NEO    | 12      | I              | PECL/LVDS | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz or 622.08 MHz                                                                                                                                              |

| IN6_NEG    | 43      |                |           | clock is differentially input on this pair of pins. Whether the clock signal is PECL or LVDS is automatically detected.                                                                                                       |

|            |         |                |           | IN7: Input Clock 7                                                                                                                                                                                                            |

| IN7        | 48      | 1              | CMOS      | A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz                                                                                                                             |

|            | .0      | pull-down      | ooo       | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                                                          |

|            |         |                |           | IN8: Input Clock 8                                                                                                                                                                                                            |

| IN8        | 51      | pull-down      | CMOS      | A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz                                                                                                                             |

|            |         | pull-down      |           | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                                                          |

|            |         |                |           | IN9: Input Clock 9                                                                                                                                                                                                            |

| IN9        | 52      | pull-down      | CMOS      | A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz                                                                                                                             |

|            |         |                |           | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                                                          |

| IN10       | 53      | 1              | CMOS      | IN10: Input Clock 10 A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz,                                                                                                       |

| 11410      | 33      | pull-down      | CIVIOS    | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                                                          |

|            |         |                |           | IN11: Input Clock 11                                                                                                                                                                                                          |

|            |         |                |           | A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz                                                                                                                             |

| IN11       | 54      | pull-down      | CMOS      | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                                                          |

|            |         | pan domi       |           | In Slave operation, the frequency of the T0 selected input clock IN11 is recommended to be                                                                                                                                    |

|            |         |                |           | 6.48 MHz.                                                                                                                                                                                                                     |

| IN12       | 55      | 1              | CMOS      | IN12: Input Clock 12 A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz                                                                                                        |

| IIVIZ      |         | pull-down      |           | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                                                          |

|            |         |                |           | IN13: Input Clock 13                                                                                                                                                                                                          |

| IN13       | 56      | l<br>pull-down | CMOS      | A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz                                                                                                                             |

|            |         |                |           | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                                                          |

|            |         |                |           | IN14: Input Clock 14                                                                                                                                                                                                          |

| IN14       | 57      | pull-down      | CMOS      | A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz                                                                                                                             |

|            |         |                | O 6       | 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                                                          |

|            |         |                | Output F  | Frame Synchronization Signal                                                                                                                                                                                                  |

| FRSYNC_8K  | 30      | 0              | CMOS      | FRSYNC_8K: 8 kHz Frame Sync Output                                                                                                                                                                                            |

|            |         |                |           | An 8 kHz signal is output on this pin.  MFRSYNC_2K: 2 kHz Multiframe Sync Output                                                                                                                                              |

| MFRSYNC_2K | 31      | 0              | CMOS      | A 2 kHz signal is output on this pin.                                                                                                                                                                                         |

|            |         | <b> </b>       |           | Output Clock                                                                                                                                                                                                                  |

|            |         |                |           | OUT1: Output Clock 1                                                                                                                                                                                                          |

| OUT1       | 88      | 0              | CMOS      | A 1 Hz, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup>                                                                                       |

| 0011       | 00      |                | CIVIOS    | 5 MHz, 10 MHz, 20 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz                                                                                                                                           |

|            |         |                |           | 77.76 MHz or 155.52 MHz clock is output on this pin.                                                                                                                                                                          |

|            |         |                |           | OUT2: Output Clock 2                                                                                                                                                                                                          |

| OUT2       | 89      | 0              | CMOS      | A 1 Hz, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> , 5 MHz, 10 MHz, 20 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz |

|            |         |                |           | 77.76 MHz, 10 MHz, 20 MHz, E3, 13, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is output on this pin.                                                                                 |

|            |         |                |           | OUT3: Output Clock 3                                                                                                                                                                                                          |

| OUT2       | 00      |                | CMOC      | A 1 Hz, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> ,                                                                                     |

| OUT3       | 90      | 0              | CMOS      | 5 MHz, 10 MHz, 20 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz,                                                                                                                                          |

| 1          |         |                |           | 77.76 MHz or 155.52 MHz clock is output on this pin.                                                                                                                                                                          |

Table 1: Pin Description (Continued)

| Name      | Pin No. | I/O            | Туре      | Description <sup>1</sup>                                                                                                                                                                                                                                                                                 |

|-----------|---------|----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT4      | 93      | 0              | CMOS      | OUT4: Output Clock 4 A 1 Hz, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 $^4$ , N x T1 $^5$ , N x 13.0 MHz $^6$ , N x 3.84 MHz $^7$ , 5 MHz, 10 MHz, 20 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is output on this pin.                                 |

| OUT5      | 94      | 0              | CMOS      | OUT5: Output Clock 5 A 1 Hz, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> , 5 MHz, 10 MHz, 20 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is output on this pin. |

| OUT6_POS  | 34      | 0              | PECL/LVDS | OUT6_POS / OUT6_NEG: Positive / Negative Output Clock 6  A 1 Hz, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> ,                                                                                                       |

| OUT6_NEG  | 35      |                | PECL/LVDS | 5 MHz, 10 MHz, 20 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz or 622.08 MHz clock is differentially output on this pair of pins.                                                                                                                |

| OUT7_POS  | 36      |                |           | OUT7_POS / OUT7_NEG: Positive / Negative Output Clock 7 A 1 Hz, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> ,                                                                                                        |

| OUT7_NEG  | 37      | 0              | PECL/LVDS | 5 MHz, 10 MHz, 20 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz or 622.08 MHz clock is differentially output on this pair of pins.                                                                                                                |

| OUT8_POS  | 28      |                | 444       | OUT8_POS / OUT8_NEG: Positive / Negative Output Clock 8                                                                                                                                                                                                                                                  |

| OUT8_NEG  | 27      | 0              | AMI       | A 64 kHz + 8 kHz or 64 kHz + 8 kHz + 0.4 kHz composite clock is differentially output on this pair of pins.                                                                                                                                                                                              |

| OUT9      | 95      | 0              | CMOS      | OUT9: Output Clock 9 A 1.544 MHz (SONET) / 2.048 MHz (SDH) BITS/SSU clock is output on this pin.                                                                                                                                                                                                         |

|           |         |                | М         | icroprocessor Interface                                                                                                                                                                                                                                                                                  |