# **Overview**

Zilog's Z8 Encore!<sup>®</sup> MCU family of products are the first in a line of Zilog<sup>®</sup> microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP<sup>®</sup> F082A Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of the Z8 Encore! XP F082A Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

#### **Features**

The key features of Z8 Encore! XP F082A Series products include:

- 20 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- Up to 128 B non-volatile data storage (NVDS)

- Internal precision oscillator trimmed to  $\pm 1\%$  accuracy

- External crystal oscillator, operating up to 20 MHz

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

- Up to thirteen 5 V-tolerant input pins

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brownout (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO, and LVD

- Power-On Reset (POR)

- 2.7 V to 3.6 V operating voltage

- 8-, 20-, and 28-pin packages

- $0 \,^{\circ}\text{C}$  to  $+70 \,^{\circ}\text{C}$  and  $-40 \,^{\circ}\text{C}$  to  $+105 \,^{\circ}\text{C}$  for operating temperature ranges

### **Part Selection Guide**

Table 1 on page 3 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\circledR}$  F082A Series product line.

Table 1. Z8 Encore! XP® F082A Series Family Part Selection Guide

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | NVDS <sup>1</sup><br>(B) | I/O  | Comparator | Advanced<br>Analog <sup>2</sup> | ADC<br>Inputs | Packages           |

|----------------|---------------|------------|--------------------------|------|------------|---------------------------------|---------------|--------------------|

| Z8F082A        | 8             | 1024       | 0                        | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F081A        | 8             | 1024       | 0                        | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F042A        | 4             | 1024       | 128                      | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F041A        | 4             | 1024       | 128                      | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F022A        | 2             | 512        | 64                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F021A        | 2             | 512        | 64                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F012A        | 1             | 256        | 16                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F011A        | 1             | 256        | 16                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

<sup>&</sup>lt;sup>1</sup>Non-volatile data storage.

<sup>&</sup>lt;sup>2</sup>Advanced Analog includes ADC, temperature sensor, and low-power operational amplifier.

# **Block Diagram**

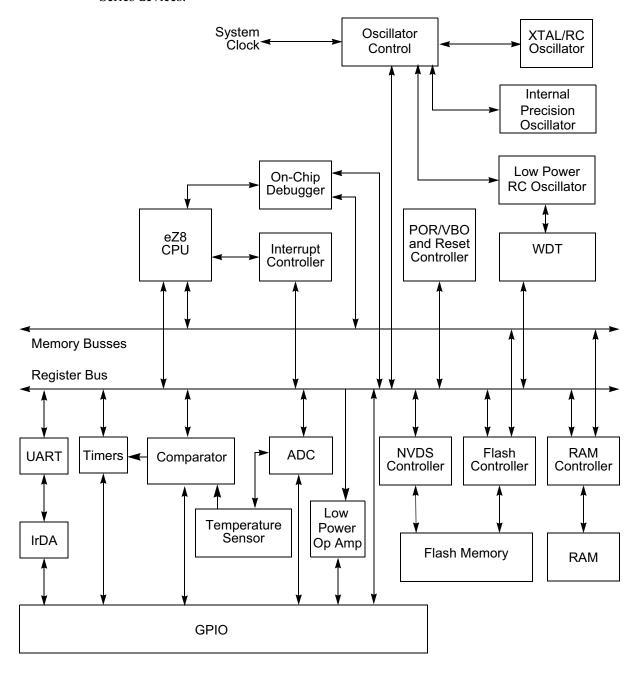

Figure 1 displays the block diagram of the architecture of the Z8 Encore! XP<sup>®</sup> F082A Series devices.

Figure 1. Z8 Encore! XP F082A Series Block Diagram

### **CPU and Peripheral Overview**

#### eZ8 CPU Features

The eZ8 CPU, Zilog's latest 8-bit Central Processing Unit (CPU), meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8<sup>®</sup> instruction set. The features of eZ8 CPU include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory.

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks.

- Compatible with existing Z8 code.

- Expanded internal Register File allows access of up to 4 KB.

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C.

- Pipelined instruction fetch and execution.

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL.

- New instructions support 12-bit linear addressing of the Register File.

- Up to 10 MIPS operation.

- C-Compiler friendly.

- 2 to 9 clock cycles per instruction.

For more information on eZ8 CPU, refer to eZ8 CPU Core User Manual (UM0128) available for download at www.zilog.com.

# 10-Bit Analog-to-Digital Converter

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes. The ADC also features a unity gain buffer when high input impedance is required.

#### **Low-Power Operational Amplifier**

The optional low-power operational amplifier (LPO) is a general-purpose amplifier primarily targeted for current sense applications. The LPO output may be routed internally to the ADC or externally to a pin.

#### Internal Precision Oscillator

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

### **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

#### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

### **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

### **Low Voltage Detector**

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

### **On-Chip Debugger**

The Z8 Encore! XP<sup>®</sup> F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints, and executing code.

#### **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

#### **Timers**

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

#### **General-Purpose Input/Output**

The Z8 Encore! XP F082A Series features 6 to 25 port pins (Ports A–D) for general-purpose input/output (GPIO). The number of GPIO pins available is a function of package, and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

#### **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

#### Flash Controller

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, as well as factory serialization and read protection.

### Non-Volatile Data Storage

The non-volatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8 KB Flash memory do not include the NVDS feature.

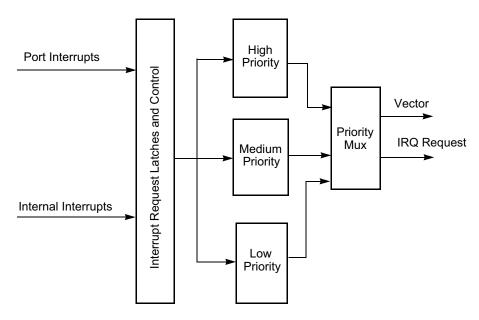

### **Interrupt Controller**

The Z8 Encore! XP<sup>®</sup> F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

#### **Reset Controller**

The Z8 Encore! XP F082A Series products can be reset using the RESET pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP mode exit, or Voltage Brownout (VBO) warning signal. The RESET pin is bi-directional, that is, it functions as reset source as well as a reset indicator.

# **Pin Description**

The Z8 Encore! XP<sup>®</sup> F082A Series products are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information on physical package specifications, see Packaging on page 241.

### **Available Packages**

The following package styles are available for each device in the Z8 Encore! XP F082A Series product line:

- SOIC

- 8-, 20-, and 28-pin

- PDIP

- 8-, 20-, and 28-pin

- SSOP

- 20- and 28- pin

- QFN (this is an MLF-S, a QFN style package with an 8-pin SOIC footprint)

- 8-pir

In addition, the Z8 Encore! XP F082A Series devices are available both with and without advanced analog capability (ADC, temperature sensor and op amp). Devices Z8F082A, Z8F042A, Z8F022A, and Z8F012A contain the advanced analog, while devices Z8F081A, Z8F041A, Z8F021A, and Z8F011A do not have the advanced analog capability.

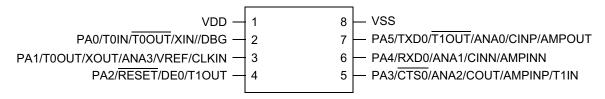

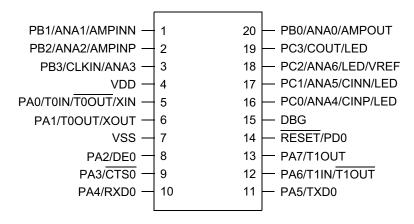

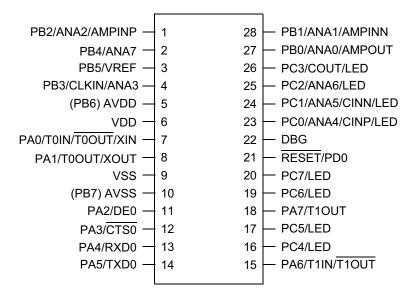

# **Pin Configurations**

Figure 2 through Figure 4 display the pin configurations for all the packages available in the Z8 Encore! XP F082A Series. See Table 2 on page 11 for a description of the signals. The analog input alternate functions (ANAx) are not available on the Z8F081A, Z8F041A, Z8F021A, and Z8F011A devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all Port A, B and C pins default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general purpose input ports until programmed otherwise. At powerup, the PD0 pin defaults to the RESET alternate function.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

Figure 2. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package

Figure 3. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package

Figure 4. Z8F08xA, Z8F04xA, Z8F02xA, and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package

# **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See Pin Configurations on page 9 to determine the signals available for the specific package styles.

**Table 2. Signal Descriptions**

| Signal Mnemonic                                          | I/O     | Description                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/C                                      | ) Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                                                  | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0]                                                  | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]                                                  | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PD[0]                                                    | I/O     | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |

| <b>Note:</b> PB6 and PB7 are replaced by AV <sub>D</sub> |         | vailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}$ .                                                                                                                                                                                                           |

| <b>UART Controllers</b>                                  |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                                                     | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                                                     | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                                                     | I       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                                                       | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                                                   |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT                                              | 0       | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |

| T0OUT/T1OUT                                              | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |

| T0IN/T1IN                                                | I       | Timer Input 0–1. These signals are used as the capture, gating and counter inputs.                                                                                                                                                                                                                      |

| Comparator                                               |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN                                                | I       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| COUT                                                     | 0       | Comparator Output.                                                                                                                                                                                                                                                                                      |

**Table 2. Signal Descriptions (Continued)**

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                   |

|---------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog              |         | ·                                                                                                                                                                                                                                                                             |

| ANA[7:0]            | I       | Analog Port. These signals are used as inputs to the analog-to-digital converter (ADC).                                                                                                                                                                                       |

| VREF                | I/O     | Analog-to-digital converter reference voltage input, or buffered output for internal reference.                                                                                                                                                                               |

| Low-Power Operation | onal An | nplifier (LPO)                                                                                                                                                                                                                                                                |

| AMPINP/AMPINN       | I       | LPO inputs. If enabled, these pins drive the positive and negative amplifier inputs respectively.                                                                                                                                                                             |

| AMPOUT              | 0       | LPO output. If enabled, this pin is driven by the on-chip LPO.                                                                                                                                                                                                                |

| Oscillators         |         |                                                                                                                                                                                                                                                                               |

| XIN                 | I       | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| XOUT                | 0       | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |

| Clock Input         |         |                                                                                                                                                                                                                                                                               |

| CLKIN               | I       | Clock Input Signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                          |

| LED Drivers         |         |                                                                                                                                                                                                                                                                               |

| LED                 | 0       | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |

| On-Chip Debugger    |         |                                                                                                                                                                                                                                                                               |

| DBG                 | I/O     | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |

|                     |         | Caution: The DBG pin is open-drain and requires a pull-up resistor to ensure proper operation.                                                                                                                                                                                |

| Reset               |         |                                                                                                                                                                                                                                                                               |

| RESET               | I/O     | RESET. Generates a Reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                         |

**Table 2. Signal Descriptions (Continued)**

| Signal Mnemonic  | I/O | Description           |

|------------------|-----|-----------------------|

| Power Supply     |     |                       |

| $V_{DD}$         | I   | Digital Power Supply. |

| AV <sub>DD</sub> | I   | Analog Power Supply.  |

| V <sub>SS</sub>  | I   | Digital Ground.       |

| AV <sub>SS</sub> | I   | Analog Ground.        |

**Note:** The  $AV_{DD}$  and  $AV_{SS}$  signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

#### **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 4 on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note:

All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

Table 3. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output | 5 V<br>Tolerance                        |

|--------------------|-----------|--------------------|---------------------------------------|--------------------|--------------------------------------|------------------------------|----------------------|-----------------------------------------|

| AVDD               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | N/A                                     |

| AVSS               | N/A       | N/A                | N/A                                   | N/A                | N/A                                  | N/A                          | N/A                  | NA                                      |

| DBG                | I/O       | 1                  | N/A                                   | Yes                | Yes                                  | Yes                          | Yes                  | No                                      |

| PA[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PA[7:2]<br>unless<br>pullups<br>enabled |

| PB[7:0]            | I/O       | I                  | N/A                                   | Yes                | Programmable<br>Pull-up              | Yes                          | Yes,<br>Programmable | PB[7:6]<br>unless<br>pullups<br>enabled |

Table 3. Pin Characteristics (20- and 28-pin Devices) (Continued)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction         | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down            | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                            | 5 V<br>Tolerance                        |

|--------------------|-----------|----------------------------|---------------------------------------|--------------------|-------------------------------------------------|------------------------------|-------------------------------------------------|-----------------------------------------|

| PC[7:0]            | I/O       | 1                          | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | PC[7:3]<br>unless<br>pullups<br>enabled |

| RESET/PD0          | I/O       | I/O (defaults<br>to RESET) | Low (in<br>Reset<br>mode)             | Yes (PD0<br>only)  | Programmable<br>for PD0; always<br>on for RESET | Yes                          | Programmable<br>for PD0; always<br>on for RESET | Yes, unless<br>pullups<br>enabled       |

| VDD                | N/A       | N/A                        | N/A                                   | N/A                |                                                 |                              | N/A                                             | N/A                                     |

| VSS                | N/A       | N/A                        | N/A                                   | N/A                |                                                 |                              | N/A                                             | N/A                                     |

**Note:** *PB6 and PB7 are available only in those devices without ADC.*

**Table 4. Pin Characteristics (8-Pin Devices)**

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                      | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down            | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                            | 5 V<br>Tolerance                   |

|--------------------|-----------|-------------------------------------------------------------------------|---------------------------------------|--------------------|-------------------------------------------------|------------------------------|-------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during reset<br>if key<br>sequence<br>detected) | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | I                                                                       | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O (defaults<br>to RESET)                                              | Low (in<br>Reset<br>mode)             | Yes                | Programmable<br>for PA2; always<br>on for RESET | Yes                          | Programmable<br>for PA2; always<br>on for RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | 1                                                                       | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| $V_{DD}$           | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                             | N/A                          | N/A                                             | N/A                                |

| V <sub>SS</sub>    | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                             | N/A                          | N/A                                             | N/A                                |

# **General-Purpose Input/Output**

The Z8 Encore! XP® F082A Series products support a maximum of 25 port pins (Ports A-D) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality, and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

## **GPIO Port Availability By Device**

Table 13 lists the port pins available with each device and package type.

Table 13. Port Availability by Device and Package Type

| Devices                                                                                                                                  | Package | ADC | Port A | Port B | Port C | Port D | Total I/O |

|------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------|--------|--------|--------|-----------|

| Z8F082ASB, Z8F082APB, Z8F082AQB<br>Z8F042ASB, Z8F042APB, Z8F042AQB<br>Z8F022ASB, Z8F022APB, Z8F022AQB<br>Z8F012ASB, Z8F012APB, Z8F012AQB | 8-pin   | Yes | [5:0]  | No     | No     | No     | 6         |

| Z8F081ASB, Z8F081APB, Z8F081AQB<br>Z8F041ASB, Z8F041APB, Z8F041AQB<br>Z8F021ASB, Z8F021APB, Z8F021AQB<br>Z8F011ASB, Z8F011APB, Z8F011AQB | 8-pin   | No  | [5:0]  | No     | No     | No     | 6         |

| Z8F082APH, Z8F082AHH, Z8F082ASH<br>Z8F042APH, Z8F042AHH, Z8F042ASH<br>Z8F022APH, Z8F022AHH, Z8F022ASH<br>Z8F012APH, Z8F012AHH, Z8F012ASH | ·       | Yes | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F081APH, Z8F081AHH, Z8F081ASH<br>Z8F041APH, Z8F041AHH, Z8F041ASH<br>Z8F021APH, Z8F021AHH, Z8F021ASH<br>Z8F011APH, Z8F011AHH, Z8F011ASH |         | No  | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F082APJ, Z8F082ASJ, Z8F082AHJ<br>Z8F042APJ, Z8F042ASJ, Z8F042AHJ<br>Z8F022APJ, Z8F022ASJ, Z8F022AHJ<br>Z8F012APJ, Z8F012ASJ, Z8F012AHJ | 28-pin  | Yes | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F081APJ, Z8F081ASJ, Z8F081AHJ<br>Z8F041APJ, Z8F041ASJ, Z8F041AHJ<br>Z8F021APJ, Z8F021ASJ, Z8F021AHJ<br>Z8F011APJ, Z8F011ASJ, Z8F011AHJ | 28-pin  | No  | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

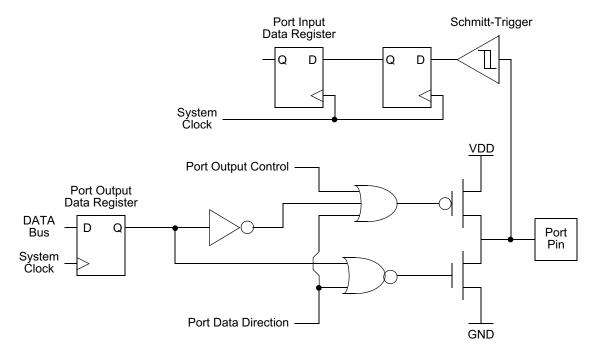

#### **Architecture**

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

Figure 7. GPIO Port Pin Block Diagram

#### **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function sub-registers configure these pins for either General-Purpose I/O or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 14 on page 41 lists the alternate functions possible with each port pin. For those pins with more one alternate function, the alternate function is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. See Timers on page 69 for more details.

Caution: For pin with multiple alternate functions, it is recommended to write to the AFS1 and AFS2 sub-registers before enabling the alternate function via the AF sub-register. This prevents spurious transitions through unwanted alternate function modes.

#### **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA and 20 mA. This mode is enabled through the Alternate Function sub-register AFS1 and is programmable through the LED control registers. The LED Drive Enable (LEDEN) register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{\mbox{\scriptsize DD}}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See Electrical Characteristics on page 221 for the maximum total current for the applicable package.

#### **Shared Reset Pin**

On the 20- and 28-pin devices, the PD0 pin shares function with a bi-directional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bi-directional reset until the software re-configures it. The PD0 pin is output-only when in GPIO mode.

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

**Caution:** *If PA2 on the 8-pin product is reconfigured as an input, ensure that no external* stimulus drives the pin low during any reset sequence. Since PA2 returns to its RESET alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

### **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PAO GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer functions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 173.

### **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 190), the GPIO settings are overridden and PA0 and PA1 are disabled.

#### **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

Note:

In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  except when the programmable pull-ups are enabled.

## **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control (OSCCTL) register (see Oscillator Control Register Definitions on page 190) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

**Table 14. Port Alternate Function Mapping (Non 8-Pin Parts)**

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | N/A                                     |                                         |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | T0OUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA4 | RXD0/IRRX0  | UART 0/IrDA 0 Receive Data              |                                         |

|        |     | Reserved    |                                         | _                                       |

|        | PA5 | TXD0/IRTX0  | UART 0/IrDA 0 Transmit Data             | _                                       |

|        |     | Reserved    |                                         | _                                       |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | _                                       |

|        |     | Reserved    |                                         | _                                       |

|        | PA7 | T1OUT       | Timer 1 Output                          | _                                       |

|        |     | Reserved    |                                         |                                         |

Note: Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A-D Alternate Function Sub-Registers on page 47 automatically enables the associated alternate function.

<sup>\*</sup> Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 82.

Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

| Port   | Pin | Mnemonic                                   | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|--------|-----|--------------------------------------------|--------------------------------|-----------------------------------------|

| Port B | PB0 | Reserved                                   | AFS1[0]: 0                     |                                         |

|        |     | ANA0/AMPOUT                                | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|        | PB1 | Reserved                                   |                                | AFS1[1]: 0                              |

|        |     | ANA1/AMPINN                                | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|        | PB2 | Reserved                                   |                                | AFS1[2]: 0                              |

|        |     | ANA2/AMPINP ADC Analog Input/LPO Input (P) |                                | AFS1[2]: 1                              |

|        | PB3 | CLKIN                                      | External Clock Input           | AFS1[3]: 0                              |

|        |     | ANA3                                       | ADC Analog Input               | AFS1[3]: 1                              |

|        | PB4 | Reserved                                   |                                | AFS1[4]: 0                              |

|        |     | ANA7                                       | ADC Analog Input               | AFS1[4]: 1                              |

|        | PB5 | Reserved                                   |                                | AFS1[5]: 0                              |

|        |     | VREF*                                      | ADC Voltage Reference          | AFS1[5]: 1                              |

|        | PB6 | Reserved                                   |                                | AFS1[6]: 0                              |

|        |     | Reserved                                   |                                | AFS1[6]: 1                              |

|        | PB7 | Reserved                                   |                                | AFS1[7]: 0                              |

|        |     | Reserved                                   |                                | AFS1[7]: 1                              |

**Note:** Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A–D Alternate Function Sub-Registers on page 47 must also be enabled.

<sup>\*</sup> VREF is available on PB5 in 28-pin products only.

Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

| Port   | Pin | Mnemonic                | Alternate Function Description                         | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------------------|--------------------------------------------------------|-----------------------------------------|

| Port C | PC0 | Reserved                |                                                        | AFS1[0]: 0                              |

|        |     | ANA4/CINP/LED<br>Drive  | ADC or Comparator Input, or LED drive                  | AFS1[0]: 1                              |

|        | PC1 | Reserved                |                                                        | AFS1[1]: 0                              |

|        |     | ANA5/CINN/ LED<br>Drive | ADC or Comparator Input, or LED drive                  | AFS1[1]: 1                              |

|        | PC2 | Reserved                |                                                        | AFS1[2]: 0                              |

|        |     | ANA6/LED/<br>VREF*      | ADC Analog Input or LED Drive or ADC Voltage Reference | AFS1[2]: 1                              |

|        | PC3 | COUT                    | Comparator Output                                      | AFS1[3]: 0                              |

|        |     | LED                     | LED drive                                              | AFS1[3]: 1                              |

|        | PC4 | Reserved                |                                                        | AFS1[4]: 0                              |

|        |     | LED                     | LED Drive                                              | AFS1[4]: 1                              |

|        | PC5 | Reserved                |                                                        | AFS1[5]: 0                              |

|        |     | LED                     | LED Drive                                              | AFS1[5]: 1                              |

|        | PC6 | Reserved                |                                                        | AFS1[6]: 0                              |

|        |     | LED                     | LED Drive                                              | AFS1[6]: 1                              |

|        | PC7 | Reserved                |                                                        | AFS1[7]: 0                              |

|        |     | LED                     | LED Drive                                              | AFS1[7]: 1                              |

Note: Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A–D Alternate Function Sub-Registers on page 47 must also be enabled.

\*VREF is available on PC2 in 20-pin parts only.

**Table 15. Port Alternate Function Mapping (8-Pin Parts)**

| Port   | Pin | Mnemonic          | Alternate Function Description         | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select Register<br>AFS2 |

|--------|-----|-------------------|----------------------------------------|-----------------------------------------------|--------------------------------------------------|

| Port A | PA0 | TOIN              | Timer 0 Input                          | AFS1[0]: 0                                    | AFS2[0]: 0                                       |

|        |     | Reserved          |                                        | AFS1[0]: 0                                    | AFS2[0]: 1                                       |

|        |     | Reserved          |                                        | AFS1[0]: 1                                    | AFS2[0]: 0                                       |

|        |     | T0OUT             | Timer 0 Output Complement              | AFS1[0]: 1                                    | AFS2[0]: 1                                       |

|        | PA1 | T0OUT             | Timer 0 Output                         | AFS1[1]: 0                                    | AFS2[1]: 0                                       |

|        |     | Reserved          |                                        | AFS1[1]: 0                                    | AFS2[1]: 1                                       |

|        |     | CLKIN             | External Clock Input                   | AFS1[1]: 1                                    | AFS2[1]: 0                                       |

|        |     | Analog Functions* | ADC Analog Input/VREF                  | AFS1[1]: 1                                    | AFS2[1]: 1                                       |

|        | PA2 | DE0               | UART 0 Driver Enable                   | AFS1[2]: 0                                    | AFS2[2]: 0                                       |

|        |     | RESET             | External Reset                         | AFS1[2]: 0                                    | AFS2[2]: 1                                       |

|        |     | T1OUT             | Timer 1 Output                         | AFS1[2]: 1                                    | AFS2[2]: 0                                       |

|        |     | Reserved          |                                        | AFS1[2]: 1                                    | AFS2[2]: 1                                       |

|        | PA3 | CTS0              | UART 0 Clear to Send                   | AFS1[3]: 0                                    | AFS2[3]: 0                                       |

|        |     | COUT              | Comparator Output                      | AFS1[3]: 0                                    | AFS2[3]: 1                                       |

|        |     | T1IN              | Timer 1 Input                          | AFS1[3]: 1                                    | AFS2[3]: 0                                       |

|        |     | Analog Functions* | ADC Analog Input/LPO Input (P)         | AFS1[3]: 1                                    | AFS2[3]: 1                                       |

|        | PA4 | RXD0              | UART 0 Receive Data                    | AFS1[4]: 0                                    | AFS2[4]: 0                                       |

|        |     | Reserved          |                                        | AFS1[4]: 0                                    | AFS2[4]: 1                                       |

|        |     | Reserved          |                                        | AFS1[4]: 1                                    | AFS2[4]: 0                                       |

|        |     | Analog Functions* | ADC/Comparator Input (N)/LPO Input (N) | AFS1[4]: 1                                    | AFS2[4]: 1                                       |

|        | PA5 | TXD0              | UART 0 Transmit Data                   | AFS1[5]: 0                                    | AFS2[5]: 0                                       |

|        |     | T10UT             | Timer 1 Output Complement              | AFS1[5]: 0                                    | AFS2[5]: 1                                       |

|        |     | Reserved          |                                        | AFS1[5]: 1                                    | AFS2[5]: 0                                       |

|        |     | Analog Functions* | ADC/Comparator Input (P) LPO<br>Output | AFS1[5]: 1                                    | AFS2[5]: 1                                       |

<sup>\*</sup>Analog Functions include ADC inputs, ADC reference, comparator inputs and LPO ports.

**Note:** Also, alternate function selection as described in Port A–D Alternate Function Sub-Registers on page 47 must be enabled.

### **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See Interrupt Controller on page 55 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 16 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

Table 16. GPIO Port Registers and Sub-Registers

| Port Register Mnemonic     | Port Register Name                                              |

|----------------------------|-----------------------------------------------------------------|

| PxADDR                     | Port A–D Address Register<br>(Selects sub-registers)            |

| PxCTL                      | Port A–D Control Register<br>(Provides access to sub-registers) |

| PxIN                       | Port A–D Input Data Register                                    |

| PxOUT                      | Port A–D Output Data Register                                   |

| Port Sub-Register Mnemonic | Port Register Name                                              |

| PxDD                       | Data Direction                                                  |

| PxAF                       | Alternate Function                                              |

| PxOC                       | Output Control (Open-Drain)                                     |

| PxHDE                      | High Drive Enable                                               |

| PxSMRE                     | Stop Mode Recovery Source Enable                                |

| PxPUE                      | Pull-up Enable                                                  |

| PxAFS1                     | Alternate Function Set 1                                        |

| PxAFS2                     | Alternate Function Set 2                                        |

### Port A–D Address Registers

The Port A–D Address registers select the GPIO Port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO Port controls (Table 17).

Table 17. Port A–D GPIO Address Registers (PxADDR)

| BITS  | 7   | 6          | 5   | 4          | 3         | 2   | 1   | 0   |  |  |

|-------|-----|------------|-----|------------|-----------|-----|-----|-----|--|--|

| FIELD |     | PADDR[7:0] |     |            |           |     |     |     |  |  |

| RESET |     | 00H        |     |            |           |     |     |     |  |  |

| R/W   | R/W | R/W        | R/W | R/W        | R/W       | R/W | R/W | R/W |  |  |

| ADDR  |     |            | FI  | D0H, FD4H, | FD8H, FDC | H   |     |     |  |  |

PADDR[7:0]—Port Address

The Port Address selects one of the sub-registers accessible through the Port Control register.

| PADDR[7:0] | Port Control sub-register accessible using the Port A–D Control Registers      |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental Port reconfiguration. |

| 01H        | Data Direction.                                                                |

| 02H        | Alternate Function.                                                            |

| 03H        | Output Control (Open-Drain).                                                   |

| 04H        | High Drive Enable.                                                             |

| 05H        | Stop Mode Recovery Source Enable.                                              |

| 06H        | Pull-up Enable.                                                                |

| 07H        | Alternate Function Set 1.                                                      |

| 08H        | Alternate Function Set 2.                                                      |

| 09H–FFH    | No function.                                                                   |

### Port A–D Control Registers

The Port A–D Control registers set the GPIO port operation. The value in the corresponding Port A–D Address register determines which sub-register is read from or written to by a Port A–D Control register transaction (Table 18).

Table 18. Port A–D Control Registers (PxCTL)

| BITS  | 7   | 6                       | 5  | 4          | 3         | 2 | 1 | 0 |  |  |

|-------|-----|-------------------------|----|------------|-----------|---|---|---|--|--|

| FIELD |     | PCTL                    |    |            |           |   |   |   |  |  |

| RESET |     | 00H                     |    |            |           |   |   |   |  |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W |    |            |           |   |   |   |  |  |

| ADDR  |     |                         | FI | D1H, FD5H, | FD9H, FDD | Н |   |   |  |  |

PCTL[7:0]—Port Control

The Port Control register provides access to all sub-registers that configure the GPIO Port operation.

### Port A-D Data Direction Sub-Registers

The Port A–D Data Direction sub-register is accessed through the Port A–D Control register by writing 01H to the Port A–D Address register (Table 19).

Table 19. Port A–D Data Direction Sub-Registers (PxDD)

| BITS  | 7        | 6            | 5           | 4             | 3             | 2             | 1            | 0        |

|-------|----------|--------------|-------------|---------------|---------------|---------------|--------------|----------|

| FIELD | DD7      | DD6          | DD5         | DD4           | DD3           | DD2           | DD1          | DD0      |

| RESET | 1        | 1            | 1           | 1             | 1             | 1             | 1            | 1        |

| R/W   | R/W      | R/W          | R/W         | R/W           | R/W           | R/W           | R/W          | R/W      |

| ADDR  | If 01H i | n Port A–D / | Address Reg | gister, acces | sible througl | h the Port A- | –D Control F | Register |

DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 = Output. Data in the Port A–D Output Data register is driven onto the port pin.

1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register. The output driver is tristated.

### Port A-D Alternate Function Sub-Registers

The Port A–D Alternate Function sub-register (Table 20) is accessed through the Port A–D Control register by writing 02H to the Port A–D Address register. The Port A–D Alternate Function sub-registers enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the Port A–D Alternate Function

Set 1 Sub-Registers on page 50, GPIO Alternate Functions on page 38, and Port A–D Alternate Function Set 2 Sub-Registers on page 51. See GPIO Alternate Functions on page 38 to determine the alternate function associated with each port pin.

#### Caution:

Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

Table 20. Port A–D Alternate Function Sub-Registers (PxAF)

| BITS  | 7                                                           | 6          | 5           | 4             | 3             | 2             | 1            | 0        |  |  |  |

|-------|-------------------------------------------------------------|------------|-------------|---------------|---------------|---------------|--------------|----------|--|--|--|

| FIELD | AF7                                                         | AF6        | AF5         | AF4           | AF3           | AF2           | AF1          | AF0      |  |  |  |

| RESET | 00H (Ports A–C); 01H (Port D); 04H (Port A of 8-pin device) |            |             |               |               |               |              |          |  |  |  |

| R/W   |                                                             | R/W        |             |               |               |               |              |          |  |  |  |

| ADDR  | If 02H i                                                    | n Port A–D | Address Reg | gister, acces | sible through | n the Port A- | –D Control F | Register |  |  |  |

AF[7:0]—Port Alternate Function enabled

0 = The port pin is in normal mode and the DDx bit in the Port A–D Data Direction sub-register determines the direction of the pin.

1 = The alternate function selected through Alternate Function Set sub-registers is enabled. Port pin operation is controlled by the alternate function.

#### Port A-D Output Control Sub-Registers

The Port A–D Output Control sub-register (Table 21) is accessed through the Port A–D Control register by writing 03H to the Port A–D Address register. Setting the bits in the Port A–D Output Control sub-registers to 1 configures the specified port pins for opendrain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

Table 21. Port A–D Output Control Sub-Registers (PxOC)

| BITS  | 7                             | 6                       | 5           | 4             | 3             | 2             | 1            | 0        |  |  |

|-------|-------------------------------|-------------------------|-------------|---------------|---------------|---------------|--------------|----------|--|--|

| FIELD | POC7                          | POC6                    | POC5        | POC4          | POC3          | POC2          | POC1         | POC0     |  |  |

| RESET | 00H (Ports A-C); 01H (Port D) |                         |             |               |               |               |              |          |  |  |

| R/W   | R/W                           | R/W R/W R/W R/W R/W R/W |             |               |               |               |              |          |  |  |

| ADDR  | If 03H i                      | n Port A–D /            | Address Reg | jister, acces | sible througl | n the Port A- | -D Control F | Register |  |  |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

0 = The source current is enabled for any output mode (unless overridden by the alternate

function). (Push-pull output)

1 = The source current for the associated pin is disabled (open-drain mode).

#### Port A-D High Drive Enable Sub-Registers

The Port A–D High Drive Enable sub-register (Table 22) is accessed through the Port A–D Control register by writing 04H to the Port A–D Address register. Setting the bits in the Port A–D High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

Table 22. Port A–D High Drive Enable Sub-Registers (PxHDE)

| BITS  | 7        | 6          | 5           | 4             | 3             | 2             | 1            | 0        |

|-------|----------|------------|-------------|---------------|---------------|---------------|--------------|----------|

| FIELD | PHDE7    | PHDE6      | PHDE5       | PHDE4         | PHDE3         | PHDE2         | PHDE1        | PHDE0    |

| RESET | 0        | 0          | 0           | 0             | 0             | 0             | 0            | 0        |

| R/W   | R/W      | R/W        | R/W         | R/W           | R/W           | R/W           | R/W          | R/W      |

| ADDR  | If 04H i | n Port A–D | Address Reg | jister, acces | sible througl | n the Port A- | -D Control F | Register |

PHDE[7:0]—Port High Drive Enabled

0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

#### Port A-D Stop Mode Recovery Source Enable Sub-Registers

The Port A–D Stop Mode Recovery Source Enable sub-register (Table 23) is accessed through the Port A–D Control register by writing 05H to the Port A–D Address register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable sub-registers to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

Table 23. Port A–D Stop Mode Recovery Source Enable Sub-Registers (PxSMRE)

| BITS  | 7        | 6          | 5           | 4             | 3             | 2             | 1            | 0        |

|-------|----------|------------|-------------|---------------|---------------|---------------|--------------|----------|

| FIELD | PSMRE7   | PSMRE6     | PSMRE5      | PSMRE4        | PSMRE3        | PSMRE2        | PSMRE1       | PSMRE0   |

| RESET | 0        | 0          | 0           | 0             | 0             | 0             | 0            | 0        |

| R/W   | R/W      | R/W        | R/W         | R/W           | R/W           | R/W           | R/W          | R/W      |

| ADDR  | If 05H i | n Port A–D | Address Reg | gister, acces | sible througl | n the Port A- | -D Control F | Register |

PSMRE[7:0]—Port Stop Mode Recovery Source Enabled

0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin

during STOP mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP mode initiates Stop Mode Recovery.

#### Port A-D Pull-up Enable Sub-Registers

The Port A–D Pull-up Enable sub-register (Table 24) is accessed through the Port A–D Control register by writing 06H to the Port A–D Address register. Setting the bits in the Port A–D Pull-up Enable sub-registers enables a weak internal resistive pull-up on the specified Port pins.

Table 24. Port A-D Pull-Up Enable Sub-Registers (PxPUE)

| BITS  | 7        | 6                                                           | 5           | 4             | 3             | 2            | 1            | 0        |  |  |  |

|-------|----------|-------------------------------------------------------------|-------------|---------------|---------------|--------------|--------------|----------|--|--|--|

| FIELD | PPUE7    | PPUE6                                                       | PPUE5       | PPUE4         | PPUE3         | PPUE2        | PPUE1        | PPUE0    |  |  |  |

| RESET |          | 00H (Ports A-C); 01H (Port D); 04H (Port A of 8-pin device) |             |               |               |              |              |          |  |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W                                     |             |               |               |              |              |          |  |  |  |

| ADDR  | If 06H i | n Port A–D /                                                | Address Reg | jister, acces | sible through | n the Port A | -D Control F | Register |  |  |  |

PPUE[7:0]—Port Pull-up Enabled

0 = The weak pull-up on the Port pin is disabled.

1 = The weak pull-up on the Port pin is enabled.

#### Port A–D Alternate Function Set 1 Sub-Registers

The Port A–D Alternate Function Set1 sub-register (Table 25) is accessed through the Port A–D Control register by writing 07H to the Port A–D Address register. The Alternate Function Set 1 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in GPIO Alternate Functions on page 38.

Note:

Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

Table 25. Port A–D Alternate Function Set 1 Sub-Registers (PxAFS1)

| BITS  | 7        | 6                           | 5           | 4             | 3             | 2             | 1            | 0        |  |  |

|-------|----------|-----------------------------|-------------|---------------|---------------|---------------|--------------|----------|--|--|

| FIELD | PAFS17   | PAFS16                      | PAFS15      | PAFS14        | PAFS13        | PAFS12        | PAFS11       | PAFS10   |  |  |

| RESET | 0        | 0                           | 0           | 0             | 0             | 0             | 0            | 0        |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |             |               |               |               |              |          |  |  |

| ADDR  | If 07H i | n Port A–D                  | Address Reg | gister, acces | sible througl | n the Port A- | -D Control F | Register |  |  |

PAFS1[7:0]—Port Alternate Function Set 1

0 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

1 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

#### Port A-D Alternate Function Set 2 Sub-Registers

The Port A–D Alternate Function Set 2 sub-register (Table 26) is accessed through the Port A–D Control register by writing 08H to the Port A–D Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 15.

Note:

Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

Table 26. Port A–D Alternate Function Set 2 Sub-Registers (PxAFS2)

| BITS  | 7        | 6                                                                  | 5           | 4             | 3             | 2             | 1            | 0        |  |  |  |

|-------|----------|--------------------------------------------------------------------|-------------|---------------|---------------|---------------|--------------|----------|--|--|--|

| FIELD | PAFS27   | PAFS26                                                             | PAFS25      | PAFS24        | PAFS23        | PAFS22        | PAFS21       | PAFS20   |  |  |  |

| RESET |          | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |             |               |               |               |              |          |  |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W                                            |             |               |               |               |              |          |  |  |  |

| ADDR  | If 08H i | n Port A–D                                                         | Address Reg | gister, acces | sible through | n the Port A- | -D Control F | Register |  |  |  |

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 15.

1 = Port Alternate Function selected as defined in Table 15.

### Port A-C Input Data Registers

Reading from the Port A–C Input Data registers (Table 27) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

Table 27. Port A-C Input Data Registers (PxIN)

| BITS           | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------------|------------------|------|------|------|------|------|------|------|

| FIELD          | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET          | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W            | R                | R    | R    | R    | R    | R    | R    | R    |

| ADDR           | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |

| X = Undefined. |                  |      |      |      |      |      |      |      |

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 =Input data is logical 0 (Low).

1 = Input data is logical 1 (High).

#### Port A-D Output Data Register

The Port A–D Output Data register (Table 28) controls the output data to the pins.

Table 28. Port A–D Output Data Register (PxOUT)

| BITS  | 7     | 6                      | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|------------------------|-------|-------|-------|-------|-------|-------|

| FIELD | POUT7 | POUT6                  | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET | 0     | 0                      | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W   | R/W   | R/W                    | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| ADDR  |       | FD3H, FD7H, FDBH, FDFH |       |       |       |       |       |       |

POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1= Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

### **LED Drive Enable Register**

The LED Drive Enable register (Table 29) activates the controlled current drive. The Port C pin must first be enabled by setting the Alternate Function register to select the LED function.

**Table 29. LED Drive Enable (LEDEN)**

| BITS  | 7          | 6                       | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|-------------------------|---|---|---|---|---|---|

| FIELD | LEDEN[7:0] |                         |   |   |   |   |   |   |

| RESET | 0          | 0                       | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W   | R/W        | R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| ADDR  |            | F82H                    |   |   |   |   |   |   |

LEDEN[7:0]—LED Drive Enable

These bits determine which Port C pins are connected to an internal current sink.

0 = Tristate the Port C pin.

1= Enable controlled current sink on the Port C pin.

### **LED Drive Level High Register**

The LED Drive Level registers contain two control bits for each Port C pin (Table 30). These two bits select between four programmable drive levels. Each pin is individually programmable.