### **General Description**

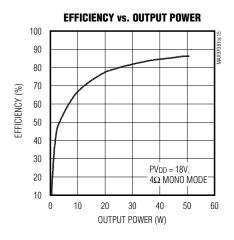

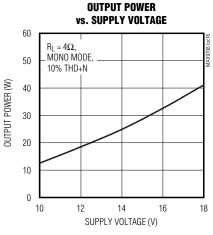

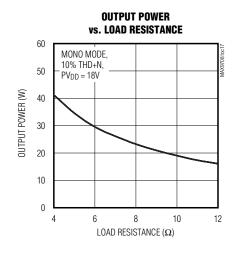

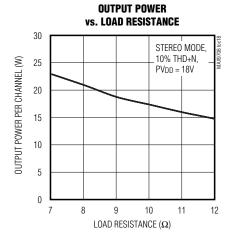

The MAX9708 mono/stereo, Class D audio power amplifier delivers up to 2 x 21W into an  $8\Omega$  stereo mode and 1 x 42W into a  $4\Omega$  load in mono mode while offering up to 87% efficiency. The MAX9708 provides Class AB amplifier performance with the benefits of Class D efficiency, eliminating the need for a bulky heatsink and conserving power. The MAX9708 operates from a single +10V to +18V supply, driving the load in a BTL configuration.

The MAX9708 offers two modulation schemes: a fixedfrequency modulation (FFM) mode, and a spread-spectrum modulation (SSM) mode that reduces EMI-radiated emissions. The MAX9708 can be synchronized to an external clock from 600kHz to 1.2MHz. A synchronized output allows multiple units to be cascaded in the system.

Features include fully differential inputs, comprehensive click-and-pop suppression, and four selectable-gain settings (22dB, 25dB, 29.5dB, and 36dB). A pin-programmable thermal flag provides seven different thermal warning thresholds. Short-circuit and thermal-overload protection prevent the device from being damaged during a fault condition.

The MAX9708 is available in 56-pin TQFN (8mm x 8mm x 0.8mm) and 64-pin TQFP (10mm x 10mm x 1.4mm) packages, and is specified over the extended -40°C to +85°C temperature range.

#### **Applications**

PDP TVs LCD TVs

Automotive PC/HiFi Audio Solutions

## Features

- ♦ 2 x 21W Output Power in Stereo Mode  $(8\Omega, THD = 10\%)$

- ♦ 1 x 42W Output Power in Mono Mode  $(4\Omega, THD = 10\%)$

- ♦ High Efficiency: Up to 87%

- **♦** Filterless Class D Amplifier

- ♦ Unique Patented Spread-Spectrum Mode

- ♦ Programmable Gain (+22dB, +25dB, +29.5dB, +36dB)

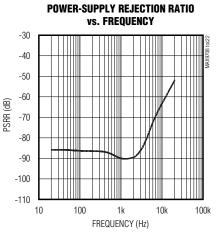

- ♦ High PSRR (90dB at 1kHz)

- ♦ Differential Inputs Suppress Common-Mode

- Shutdown and Mute Control

- ♦ Integrated Click-and-Pop Suppression

- ♦ Low 0.1% THD+N

- **♦ Current Limit and Thermal Protection**

- Programmable Thermal Flag

- ♦ SYNC Input/Output

- ♦ Available in Thermally Efficient, Space-Saving Packages: 56-Pin TQFN and 64-Pin TQFP

### **Ordering Information**

|   | PART        | TEMP RANGE     | PIN-PACKAGE  | PKG<br>CODE |

|---|-------------|----------------|--------------|-------------|

| N | MAX9708ETN  | -40°C to +85°C | 56 TQFN-EP** | T5688-3     |

| Ν | MAX9708ECB* | -40°C to +85°C | 64 TQFP-EP** | C64E-6      |

<sup>\*</sup>Future product—Contact factory for availability.

#### Pin Configurations appear at end of data sheet.

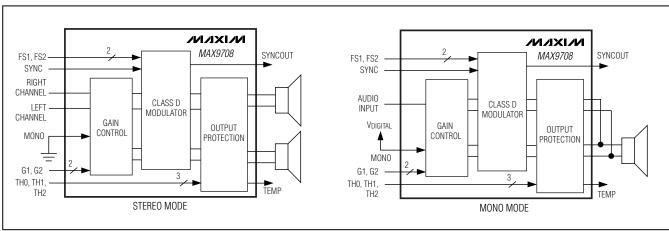

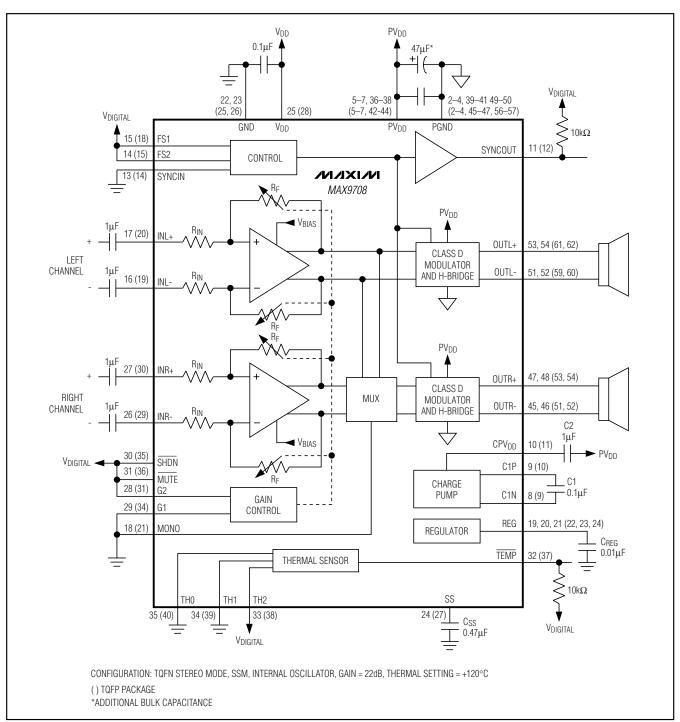

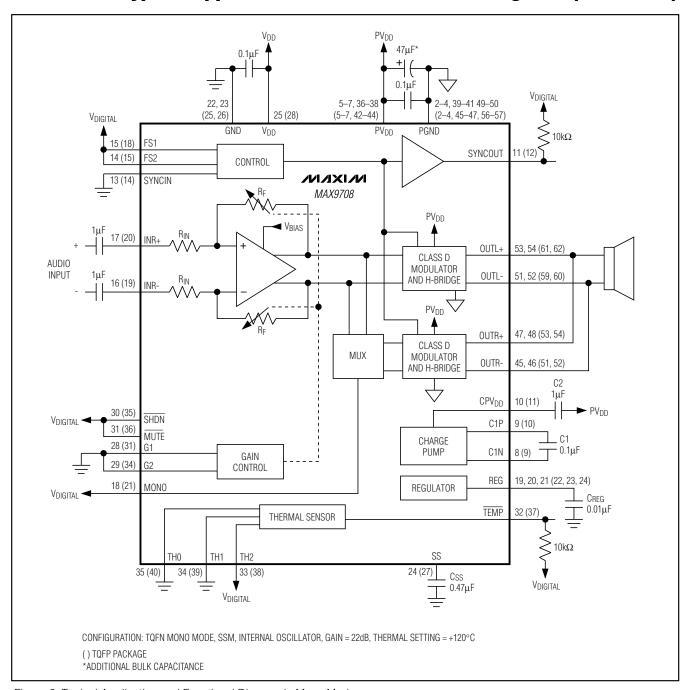

### Simplified Block Diagram

NIXIN

Maxim Integrated Products 1

<sup>\*\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| , , , , , , , , , , , , , , , , , , , , | -0.3 to +30V<br>-0.3V to +0.3V                   | Continuous Power Diss<br>56-Pin Thin QFN (der<br>64-Pin TQFP (derate |

|-----------------------------------------|--------------------------------------------------|----------------------------------------------------------------------|

| OUTL- to PGND, GND                      | 0.3V to (PV <sub>DD</sub> + 0.3V)                | Operating Temperature                                                |

|                                         | 0.3V to (PV <sub>DD</sub> + 0.3V)                | Storage Temperature F                                                |

| C1P to GND                              | ( $PV_{DD} - 0.3V$ ) to ( $CPV_{DD} + 0.3V$ )    | Junction Temperature.                                                |

| CPV <sub>DD</sub> to GND                | (PV <sub>DD</sub> - 0.3V) to +40V                | Thermal Resistance (θ,                                               |

| All Other Pins to GND                   | 0.3V to +12V                                     | 56-Pin Thin QFN                                                      |

| Continuous Input Current (ex            | cept PV <sub>DD</sub> , V <sub>DD</sub> , OUTR+, | 64-Pin TQFP                                                          |

| OUTR-, OUTL+, and OUTL                  | )20mA                                            | Lead Temperature (sol                                                |

|                                         |                                                  |                                                                      |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|-------------------------------------------------------|

| 56-Pin Thin QFN (derate 47.6mW/°C above +70°C)3.81W   |

| 64-Pin TQFP (derate 43.5mW/°C above +70°C)3.48W       |

| Operating Temperature Range40°C to +85°C              |

| Storage Temperature Range65°C to +150°C               |

| Junction Temperature+150°C                            |

| Thermal Resistance (θ <sub>JC</sub> )                 |

| 56-Pin Thin QFN                                       |

| 64-Pin TQFP2°C/W                                      |

| Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(PV_{DD} = V_{DD} = +18V, PGND = GND = 0V, C_{SS} = 0.47\mu F, C_{REG} = 0.01\mu F, C1 = 0.1\mu F, C2 = 1\mu F, R_{LOAD} = \infty$ , MONO = low (stereo mode),  $\overline{SHDN} = \overline{MUTE}$  = high, G1 = low, G2 = high (A<sub>V</sub> = 22dB), FS1 = FS2 = high (SSM), SYNCIN = low. All load resistors (R<sub>L</sub>) are connected between OUT\_+ and OUT\_-, unless otherwise stated. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                    | SYMBOL          | CONDITIONS                         |                                                    | MIN | TYP | MAX  | UNITS     |

|------------------------------|-----------------|------------------------------------|----------------------------------------------------|-----|-----|------|-----------|

| Supply Voltage Range         | V <sub>DD</sub> | Inferred from PSRF                 | R test                                             | 10  |     | 18   | V         |

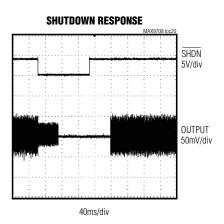

| Shutdown Current             | ISHDN           | SHDN = low                         | SHDN = low                                         |     | 0.1 | 1    | μΑ        |

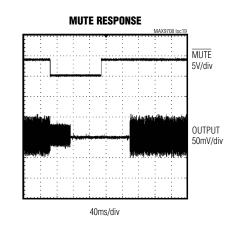

| Shutdown to Full Operation   | tson            |                                    |                                                    |     | 100 |      | ms        |

| Mute to Full Operation       | tmute           |                                    |                                                    |     | 100 |      | ms        |

|                              |                 | G1 = 0, G2 = 1                     |                                                    | 50  | 85  | 125  |           |

| land the land of days of     | D               | G1 = 1, G2 = 1                     |                                                    | 40  | 63  | 90   | $k\Omega$ |

| Input Impedance              | R <sub>IN</sub> | G1 = 1, G2 = 0                     |                                                    | 25  | 43  | 60   | KZ2       |

|                              |                 | G1= 0, G2 = 0                      |                                                    | 12  | 21  | 30   |           |

| Output Pulldown Resistance   |                 | SHDN = GND                         |                                                    |     | 600 |      | kΩ        |

| Output Offset Voltage        | Vos             | AC-coupled input,<br>OUT_+ and OUT | AC-coupled input, measured between OUT + and OUT - |     |     | ±30  | mV        |

|                              |                 | PV <sub>DD</sub> = 10V to 18V      |                                                    | 68  | 90  |      |           |

| Power-Supply Rejection Ratio | PSRR            | 200mV <sub>P-P</sub> ripple        | f <sub>RIPPLE</sub> = 1kHz                         |     | 90  |      | dB        |

|                              |                 | (Note 2)                           | f <sub>RIPPLE</sub> = 20kHz                        |     | 50  |      |           |

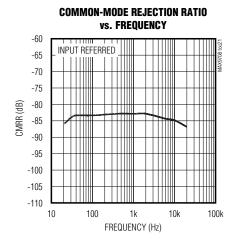

| Carrona Mada Daiastian Datia | CMDD            | DC, input referred                 |                                                    | 50  | 70  |      | ۵D        |

| Common-Mode Rejection Ratio  | CMRR            | f = 20Hz to $20kHz$ ,              | input referred                                     |     | 70  |      | dB        |

| Switch On-Resistance         | R <sub>DS</sub> | One power switch                   |                                                    |     | 0.3 | 0.75 | Ω         |

|                              |                 | FS1                                | FS2                                                |     |     |      |           |

|                              |                 | 0                                  | 0                                                  | 180 | 200 | 220  |           |

| Switching Frequency          | fsw             | 1                                  | 1 (SSM)                                            |     | 200 |      | kHz       |

|                              |                 | 1                                  | 0                                                  |     | 160 |      |           |

|                              |                 | 0                                  | 1                                                  |     | 250 |      |           |

| Oscillator Spread Bandwidth  |                 | FS1 = FS2 = high (                 | (SSM)                                              |     | ±2  |      | %         |

| SYNCIN Lock Range            |                 | Equal to fsw x 4                   |                                                    | 600 |     | 1200 | kHz       |

\_\_ /N/1XI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(PV_{DD} = V_{DD} = +18V, PGND = GND = 0V, C_{SS} = 0.47\mu F, C_{REG} = 0.01\mu F, C1 = 0.1\mu F, C2 = 1\mu F, R_{LOAD} = ∞, MONO = low (stereo mode), SHDN = MUTE = high, G1 = low, G2 = high (A<sub>V</sub> = 22dB), FS1 = FS2 = high (SSM), SYNCIN = low. All load resistors (R<sub>L</sub>) are connected between OUT_+ and OUT_-, unless otherwise stated. <math>T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                    | SYMBOL            |                              | CONDITIO                                                | ONS |               | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------|-------------------|------------------------------|---------------------------------------------------------|-----|---------------|------|------|------|-------|

|                                              |                   | G1 = 0, G2 = 1               |                                                         |     | 21.6          | 22.0 | 22.3 |      |       |

|                                              |                   | G1 = 1, G2 = 1               |                                                         |     | 24.9          | 25.0 | 25.6 |      |       |

| Gain                                         | Av                | G1 = 1, G                    | 2 = 0                                                   |     |               | 29.2 | 29.5 | 29.9 | dB    |

|                                              |                   | G1 = 0, G                    | 2 = 0                                                   |     |               | 35.9 | 36.0 | 36.6 |       |

|                                              |                   | TH2                          | TH1                                                     |     | TH0           |      |      |      |       |

|                                              |                   | 0                            | 0                                                       |     | 0             |      | +80  |      |       |

|                                              |                   | 0                            | 0                                                       | İ   | 1             |      | +90  |      |       |

|                                              |                   | 0                            | 1                                                       |     | 0             |      | +100 |      |       |

| TEMP Flag Threshold                          | T <sub>FLAG</sub> | 0                            | 1                                                       |     | 1             |      | +110 |      | °C    |

|                                              |                   | 1                            | 0                                                       |     | 0             |      | +120 |      |       |

|                                              |                   | 1                            | 0                                                       |     | 1             |      | +129 |      |       |

|                                              |                   | 1                            | 1                                                       |     | 0             |      | +139 |      |       |

|                                              |                   | 1                            | 1                                                       |     | 1             |      | +150 |      |       |

| TEMP Flag Accuracy                           |                   | From +80°                    | °C to +140°C                                            |     |               |      |      | ±6   | °C    |

| TEMP Flag Hysteresis                         |                   |                              |                                                         |     |               |      | 2    |      | °C    |

| STEREO MODE (R <sub>LOAD</sub> = $8\Omega$ ) |                   |                              |                                                         |     |               |      |      |      |       |

| Ossis-s-s-t Ossas-at                         |                   | $\overline{\text{MUTE}} = 1$ | , Rload = ∞                                             |     |               |      | 20   | 30   | ^     |

| Quiescent Current                            |                   | MUTE = 0                     |                                                         |     |               |      | 5    | 11   | mA    |

| Output Power                                 | Pout              |                              | THD = 10%, T <sub>A</sub><br>BΩ, PV <sub>DD</sub> = 18\ |     | 25°C,         | 20   | 21   |      | W     |

| Total Harmonic Distortion Plus Noise         | THD+N             |                              | BW = 22Hz to 2<br>B $\Omega$ , P <sub>OUT</sub> = 8W    |     | Z,            |      | 0.1  |      | %     |

| Circulto Naisa Datia                         | SNR               | D                            | 20 Davie 10V                                            | .,  | 22Hz to 22kHz |      | 91   |      | dB    |

| Signal-to-Noise Ratio                        | SINK              | RLOAD  = 6                   | $B\Omega$ , $P_{OUT} = 10V$                             | ۷ [ | A-weighted    |      | 96   |      | T OB  |

| Efficiency                                   | η                 | $R_{LOAD} = 8$<br>f = 1kHz   | BΩ, L > 60μH, P                                         | OUT | = 15W + 15W,  |      | 87   |      | %     |

| Left-Right Channel Gain<br>Matching          |                   | P <sub>OUT</sub> = 10        | )W                                                      |     |               |      | 0.02 |      | dB    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(PV_{DD} = V_{DD} = +18V, PGND = GND = 0V, C_{SS} = 0.47\mu F, C_{REG} = 0.01\mu F, C1 = 0.1\mu F, C2 = 1\mu F, R_{LOAD} = \infty, MONO = low (stereo mode), $\overline{SHDN} = \overline{MUTE} = high, G1 = low, G2 = high (A_V = 22dB), FS1 = FS2 = high (SSM), SYNCIN = low. All load resistors (R_L) are connected between OUT_+ and OUT_-, unless otherwise stated. $T_A = T_{MIN}$ to $T_{MAX}$, unless otherwise noted. Typical values are at $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                      | SYMBOL          |                                        | CONDITIO                       | ONS             | MIN | TYP  | MAX | UNITS |

|------------------------------------------------|-----------------|----------------------------------------|--------------------------------|-----------------|-----|------|-----|-------|

| Output Short-Circuit Current<br>Threshold      | I <sub>SC</sub> | $R_{LOAD} = 0\Omega$                   |                                |                 |     | 2.4  |     | А     |

|                                                |                 | _                                      | Peak voltage, 32 Into shutdown |                 |     | -63  |     |       |

| Click-and-Pop Level                            | KCP             | samples/second-<br>A-weighted (I       |                                | Out of shutdown |     | -55  |     | dBV   |

| MONO MODE (R <sub>LOAD</sub> = $4\Omega$ , MON | NO = High)      | 1                                      |                                | I               |     |      |     | ı     |

|                                                |                 | MUTE = 1, R                            | _OAD = ∞                       |                 |     | 20   |     |       |

| Quiescent Current                              |                 | MUTE = 0                               |                                |                 |     | 5    |     | mA    |

| Output Davier                                  | D               | f = 1kHz,                              | RLOAD = 8                      | $\Omega$        |     | 23   |     | W     |

| Output Power                                   | Pout            | THD = 10%                              | R <sub>LOAD</sub> = 4          | <b>Ω</b>        |     | 42   |     | ] VV  |

| Total Harmonic Distortion Plus<br>Noise        |                 | $f = 1kHz$ , BW $R_{LOAD} = 4\Omega$ , |                                | · ·             |     | 0.12 |     | %     |

| Cignal to Naisa Datia                          | CND             | $R_{LOAD} = 4\Omega$ ,                 |                                | 20Hz to 20kHz   |     | 91   |     | -10   |

| Signal-to-Noise Ratio                          | SNR             | Pout = 10W                             |                                | A-weighted      |     | 95   |     | dB    |

| Efficiency                                     | η               | $R_{LOAD} = 4\Omega,$<br>f = 1kHz      | L > 40µH, F                    | POUT = 42W,     |     | 85   |     | %     |

| Output Short-Circuit Current<br>Threshold      | Isc             | $R_{LOAD} = 0\Omega$                   |                                |                 |     | 4.8  |     | А     |

| Olish and Day Lavel                            | IZ :            | Peak voltage                           |                                | Into shutdown   |     | -60  |     | -IDV  |

| Click-and-Pop Level                            | KCP             | samples/second-<br>A-weighted (I       | ,                              | Out of shutdown |     | -63  |     | dBV   |

| DIGITAL INPUTS (SHDN, MUTE,                    | G1, G2, FS1,    | FS2, TH0, TH                           | 1, TH2, SYN                    | ICIN, MONO)     |     |      |     |       |

| Logic-Input Current                            | I <sub>IN</sub> | 0 to 12V                               |                                |                 |     |      | 1   | μΑ    |

| Logic-Input High Voltage                       | V <sub>IH</sub> |                                        |                                |                 | 2.5 |      |     | V     |

| Logic-Input Low Voltage                        | VIL             |                                        |                                |                 |     |      | 0.8 | V     |

| OPEN-DRAIN OUTPUTS (TEMP,                      | SYNCOUT)        |                                        |                                |                 |     |      |     |       |

| Open-Drain Output Low Voltage                  | V <sub>OL</sub> | I <sub>SINK</sub> = 3mA                |                                |                 |     |      | 0.4 | V     |

| Leakage Current                                | ILEAK           | VPULLUP = 5.                           | 5V                             |                 |     | 0.2  |     | μΑ    |

- Note 1: All devices are 100% production tested at +25°C. All temperature limits are guaranteed by design.

- Note 2: Inputs AC-coupled to GND.

- **Note 3:** The device is current limited. The maximum output power is obtained with an  $8\Omega$  load.

- **Note 4:** Testing performed with an  $8\Omega$  resistive load in series with a 68µH inductive load connected across BTL outputs. Mode transitions are controlled by  $\overline{SHDN}$ .

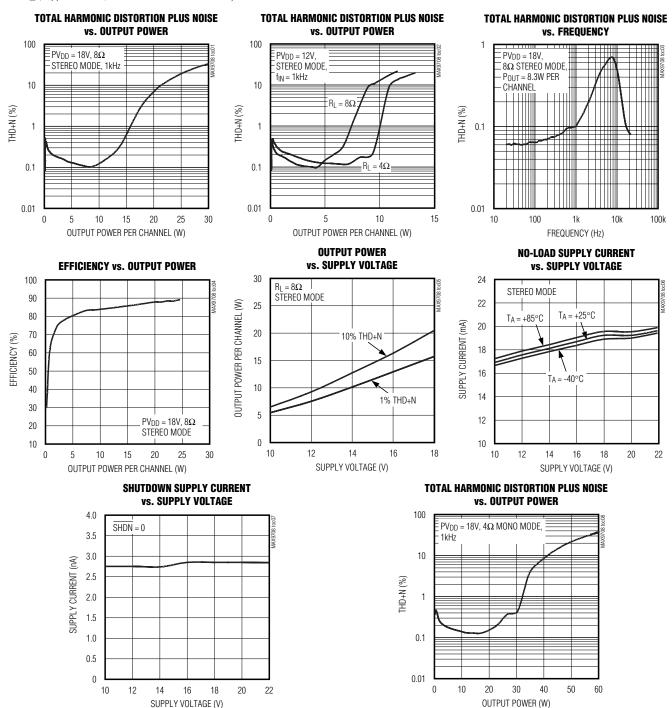

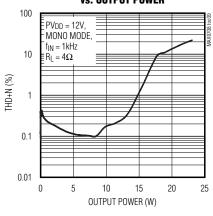

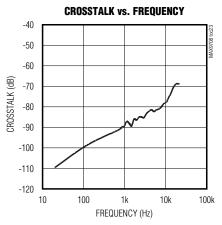

### **Typical Operating Characteristics**

$(PV_{DD} = V_{DD} = +18V, PGND = GND = 0V, C_{SS} = 0.47\mu F, C_{REG} = 0.01\mu F, C1 = 0.1\mu F, C2 = 1\mu F, R_{LOAD} = \infty, \overline{SHDN} = high, MONO = low, \overline{MUTE} = high, G1 = low, G2 = high, FS1 = FS2 = high (SSM), SYNCIN = low. All load resistors (R<sub>L</sub>) are between OUT_+ and OUT_-, T<sub>A</sub> = +25°C, unless otherwise stated.)$

### Typical Operating Characteristics (continued)

$(PV_{DD} = V_{DD} = +18V, PGND = GND = 0V, C_{SS} = 0.47\mu F, C_{REG} = 0.01\mu F, C1 = 0.1\mu F, C2 = 1\mu F, R_{LOAD} = ∞, \overline{SHDN} = high, MONO$ = low, MUTE = high, G1 = low, G2 = high, FS1 = FS2 = high (SSM), SYNCIN = low. All load resistors (R<sub>L</sub>) are between OUT\_+ and OUT\_-,  $T_A = +25$ °C, unless otherwise stated.)

#### TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER

#### TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY

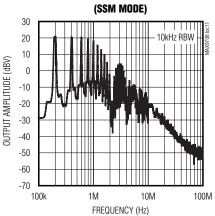

#### WIDEBAND OUTPUT SPECTRUM (SSM MODE)

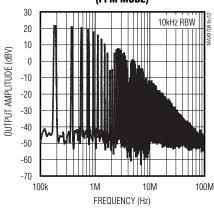

#### **WIDEBAND OUTPUT SPECTRUM** (FFM MODE)

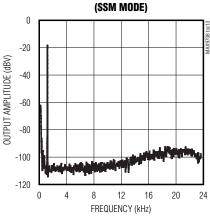

## **OUTPUT FREQUENCY SPECTRUM**

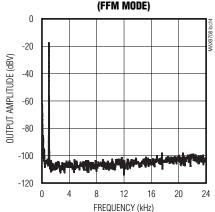

#### **OUTPUT FREQUENCY SPECTRUM** (FFM MODE)

### Typical Operating Characteristics (continued)

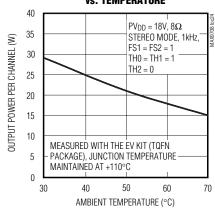

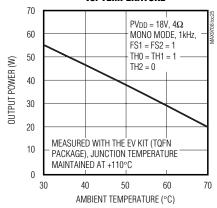

$(PV_{DD} = V_{DD} = +18V, PGND = GND = 0V, C_{SS} = 0.47\mu F, C_{REG} = 0.01\mu F, C1 = 0.1\mu F, C2 = 1\mu F, R_{LOAD} = \infty, \overline{SHDN} = high, MONO = low, \overline{MUTE} = high, G1 = low, G2 = high, FS1 = FS2 = high (SSM), SYNCIN = low. All load resistors (R<sub>L</sub>) are between OUT_+ and OUT_-, T<sub>A</sub> = +25°C, unless otherwise stated.)$

### Typical Operating Characteristics (continued)

$(PV_{DD} = V_{DD} = +18V, PGND = GND = 0V, C_{SS} = 0.47\mu F, C_{REG} = 0.01\mu F, C1 = 0.1\mu F, C2 = 1\mu F, R_{LOAD} = \infty, \overline{SHDN} = high, MONO = low, \overline{MUTE} = high, G1 = low, G2 = high, FS1 = FS2 = high (SSM), SYNCIN = low. All load resistors (R<sub>L</sub>) are between OUT_+ and OUT_-, T<sub>A</sub> = +25°C, unless otherwise stated.)$

## MAXIMUM STEADY-STATE OUTPUT POWER vs. TEMPERATURE

## MAXIMUM STEADY-STATE OUTPUT POWER vs. TEMPERATURE

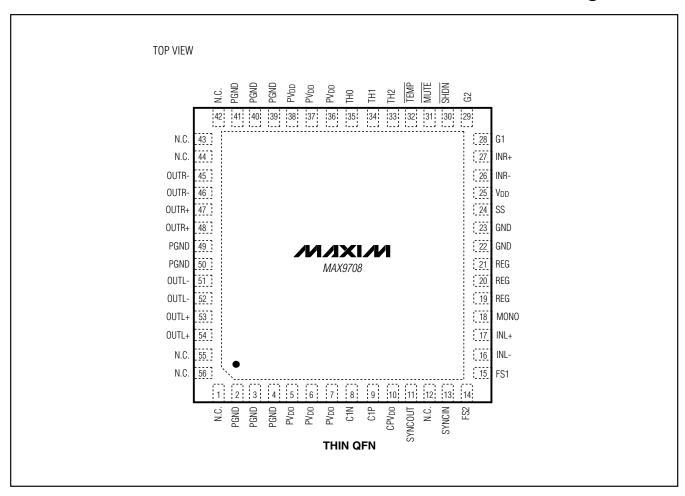

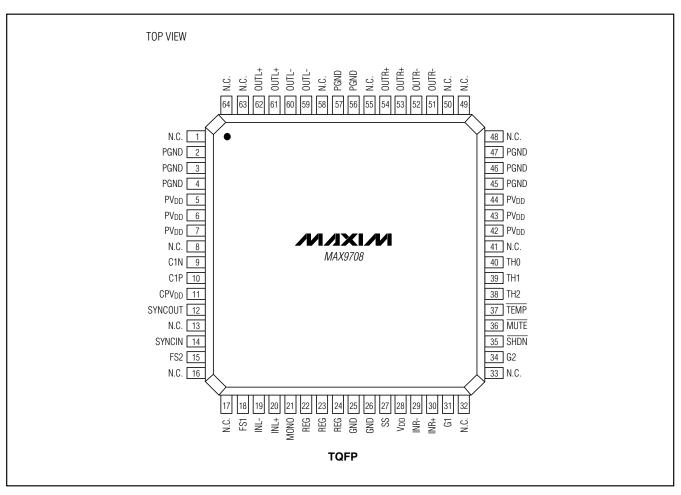

### **Pin Description**

| PI                                                                | PIN                            |           | FUNCTION                                                                                                                                 |  |  |

|-------------------------------------------------------------------|--------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TQFP                                                              | TQFN                           | NAME      | FUNCTION                                                                                                                                 |  |  |

| 1, 8, 13, 16,<br>17, 32, 33, 41,<br>48, 49, 50, 55,<br>58, 63, 64 | 1, 12, 42, 43,<br>44, 55, 56   | N.C.      | No Connection. Not internally connected.                                                                                                 |  |  |

| 2, 3, 4, 45, 46,<br>47, 56, 57                                    | 2, 3, 4, 39,<br>40, 41, 49, 50 | PGND      | Power Ground                                                                                                                             |  |  |

| 5, 6, 7,<br>42, 43, 44                                            | 5, 6, 7,<br>36, 37, 38         | $PV_{DD}$ | Positive Power Supply. Bypass to PGND with a 0.1µF and a 47µF capacitor with the smallest capacitor placed as close to pins as possible. |  |  |

## Pin Description (continued)

| PIN        |            |                   |                                                                                                                                                                                                                                                             |  |  |  |

|------------|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TQFP       | TQFN       | NAME              | FUNCTION                                                                                                                                                                                                                                                    |  |  |  |

| 9          | 8          | C1N               | Charge-Pump Flying Capacitor C1, Negative Terminal                                                                                                                                                                                                          |  |  |  |

| 10         | 9          | C1P               | Charge-Pump Flying Capacitor C1, Positive Terminal                                                                                                                                                                                                          |  |  |  |

| 11         | 10         | CPV <sub>DD</sub> | Charge-Pump Power Supply. Bypass to PV <sub>DD</sub> with a 1µF capacitor as close to the pin as possible.                                                                                                                                                  |  |  |  |

| 12         | 11         | SYNCOUT           | Open-Drain, Slew-Rate Limited Clock Output. Pullup with a 10kΩ resistor to REG.                                                                                                                                                                             |  |  |  |

| 14         | 13         | SYNCIN            | Clock Synchronization Input. Allows for synchronization of the internal oscillator with an external clock. SYNCIN is internally pulled up to $V_{REG}$ with a $100 k\Omega$ resistor.                                                                       |  |  |  |

| 15         | 14         | FS2               | Frequency Select 2                                                                                                                                                                                                                                          |  |  |  |

| 18         | 15         | FS1               | Frequency Select 1                                                                                                                                                                                                                                          |  |  |  |

| 19         | 16         | INL-              | Left-Channel Negative Input (Stereo Mode Only)                                                                                                                                                                                                              |  |  |  |

| 20         | 17         | INL+              | Left-Channel Positive Input (Stereo Mode Only)                                                                                                                                                                                                              |  |  |  |

| 21         | 18         | MONO              | Mono/Stereo Mode Input. Drive logic-high for mono mode. Drive logic-low for stereo mode.                                                                                                                                                                    |  |  |  |

| 22, 23, 24 | 19, 20, 21 | REG               | Internal Regulator Output Voltage (6V). Bypass with a 0.01µF capacitor to GND.                                                                                                                                                                              |  |  |  |

| 25, 26     | 22, 23     | GND               | Analog Ground                                                                                                                                                                                                                                               |  |  |  |

| 27         | 24         | SS                | Soft-Start. Connect a 0.47µF capacitor to GND to utilize soft-start power-up sequence.                                                                                                                                                                      |  |  |  |

| 28         | 25         | V <sub>DD</sub>   | Analog Power Supply. Bypass to GND with a 0.1µF capacitor as close to pin as possible.                                                                                                                                                                      |  |  |  |

| 29         | 26         | INR-              | Right-Channel Positive Input. In mono mode, INR+ is the positive input.                                                                                                                                                                                     |  |  |  |

| 30         | 27         | INR+              | Right-Channel Negative Input. In mono mode, INR- is the negative input.                                                                                                                                                                                     |  |  |  |

| 31         | 28         | G1                | Gain Select Input 1                                                                                                                                                                                                                                         |  |  |  |

| 34         | 29         | G2                | Gain Select Input 2                                                                                                                                                                                                                                         |  |  |  |

| 35         | 30         | SHDN              | Active-Low Shutdown Input. Drive SHDN high for normal operation. Drive SHDN low to place the device in shutdown mode.                                                                                                                                       |  |  |  |

| 36         | 31         | MUTE              | Active-Low Mute Input. Drive logic-low to place the device in mute. In mute mode, Class D output stage is no longer switching. Drive high for normal operation. $\overline{\text{MUTE}}$ is internally pulled up to $V_{REG}$ with a $100k\Omega$ resistor. |  |  |  |

| 37         | 32         | TEMP              | Thermal Flag Output, Open Drain. Pull up with a 10k $\Omega$ resistor to REG.                                                                                                                                                                               |  |  |  |

| 38         | 33         | TH2               | Temperature Flag Threshold Select Input 2                                                                                                                                                                                                                   |  |  |  |

| 39         | 34         | TH1               | Temperature Flag Threshold Select Input 1                                                                                                                                                                                                                   |  |  |  |

| 40         | 35         | TH0               | Temperature Flag Threshold Select Input 0                                                                                                                                                                                                                   |  |  |  |

| 51, 52     | 45, 46     | OUTR-             | Right-Channel Negative Output                                                                                                                                                                                                                               |  |  |  |

| 53, 54     | 47, 48     | OUTR+             | Right-Channel Positive Output                                                                                                                                                                                                                               |  |  |  |

| 59, 60     | 51, 52     | OUTL-             | Left-Channel Negative Output                                                                                                                                                                                                                                |  |  |  |

| 61, 62     | 53, 54     | OUTL+             | Left-Channel Positive Output                                                                                                                                                                                                                                |  |  |  |

| EP         | EP         | EP                | Exposed Paddle. Connect to GND with multiple vias for best heat dissipation.                                                                                                                                                                                |  |  |  |

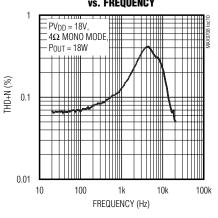

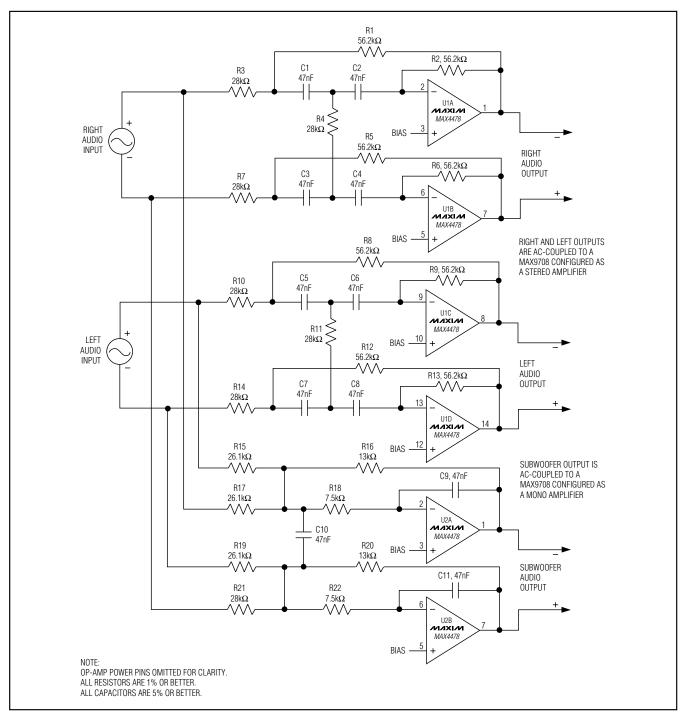

### **Typical Application Circuits/Functional Diagrams**

Figure 1. Typical Application and Functional Diagram in Stereo Mode

### Typical Application Circuits/Functional Diagrams (continued)

Figure 2. Typical Application and Functional Diagram in Mono Mode

### Detailed Description

The MAX9708 filterless, Class D audio power amplifier features several improvements to switch-mode amplifier technology. The MAX9708 is a two-channel, stereo amplifier with 21W output power on each channel. The amplifier can be configured to output 42W output power in mono mode. The device offers Class AB performance with Class D efficiency, while occupying minimal board space. A unique filterless modulation scheme and spread-spectrum switching mode create a compact, flexible, low-noise, efficient audio power amplifier. The differential input architecture reduces common-mode noise pickup, and can be used without input-coupling capacitors. The device can also be configured as a single-ended input amplifier.

#### **Mono/Stereo Configuration**

The MAX9708 features a mono mode that allows the right and left channels to operate in parallel, achieving up to 42W of output power. The mono mode is enabled by applying logic-high to MONO. In this mode, an audio signal applied to the right channel (INR+/INR-) is routed to the H-bridge of both channels, while a signal applied to the left channel (INL+/INL-) is ignored. OUTL+ must be connected to OUTR+ and OUTL- must be connected to OUTR- using heavy PC board traces as close to the device as possible (see Figure 2).

When the device is placed in mono mode on a PC board with outputs wired together, ensure that the MONO pin can never be driven low when the device is enabled. Driving the MONO pin low (stereo mode) while the outputs are wired together in mono mode may trigger the short circuit or thermal protection or both, and may even damage the device.

#### Efficiency

Efficiency of a Class D amplifier is attributed to the region of operation of the output stage transistors. In a Class D amplifier, the output transistors act as current-steering switches and consume negligible additional power. Any power loss associated with the Class D output stage is mostly due to the I<sup>2</sup>R loss of the MOSFET on-resistance and quiescent current overhead. The theoretical best efficiency of a linear amplifier is 78%; however, that efficiency is only exhibited at peak output

powers. Under normal operating levels (typical music reproduction levels), efficiency falls below 30%, whereas the MAX9708 still exhibits 87% efficiency under the same conditions.

#### **Shutdown**

The MAX9708 features a shutdown mode that reduces power consumption and extends battery life. Driving SHDN low places the device in low-power (0.1µA) shutdown mode. Connect SHDN to digital high for normal operation.

#### **Mute Function**

The MAX9708 features a clickless/popless mute mode. When the device is muted, the outputs stop switching, muting the speaker. Mute only affects the output stage and does not shut down the device. To mute the MAX9708, drive MUTE to logic-low. Driving MUTE low during the power-up/down or shutdown/turn-on cycle optimizes click-and-pop suppression.

#### Click-and-Pop Suppression

The MAX9708 features comprehensive click-and-pop suppression that eliminates audible transients on start-up and shutdown. While in shutdown, the H-bridge is pulled to GND through a 330k $\Omega$  resistor. During startup or power-up, the input amplifiers are muted and an internal loop sets the modulator bias voltages to the correct levels, preventing clicks and pops when the H-bridge is subsequently enabled. Following startup, a soft-start function gradually un-mutes the input amplifiers. The value of the soft-start capacitor has an impact on the click-and-pop levels as well as startup time.

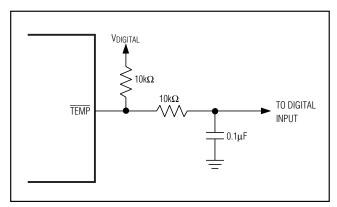

#### **Thermal Sensor**

The MAX9708 features an on-chip temperature sensor that monitors the die temperature. When the junction temperature exceeds a programmed level, TEMP is pulled low. This flags the user to reduce power or shut down the device. TEMP may be connected to SS or MUTE for automatic shutdown during overheating. If TEMP is connected to MUTE, during thermal-protection mode, the audio is muted and the device is in mute mode. If TEMP is connected to SS, during thermal-protection mode, the device is shut down but the thermal sensor is still active.

TEMP returns high once the junction temperature cools below the set threshold minus the thermal hysteresis. If TEMP is connected to either MUTE or SS, the audio output resumes. The temperature threshold is set by the TH0, TH1, and TH2 inputs as shown in Table 1. An RC filter may be used to eliminate any transient at the TEMP output as shown in Figure 3.

#### **Gain Selection**

The MAX9708 features four pin-selectable gain settings; see Table 2.

Figure 3. An RC Filter Eliminates Transient During Switching

# Table 1. MAX9708 Junction Temperature Threshold Setting

|                                 | 3    |      |      |  |  |  |

|---------------------------------|------|------|------|--|--|--|

| JUNCTION<br>TEMPERATURE<br>(°C) | TH2  | TH1  | ТН0  |  |  |  |

| 80                              | Low  | Low  | Low  |  |  |  |

| 90                              | Low  | Low  | High |  |  |  |

| 100                             | Low  | High | Low  |  |  |  |

| 110                             | Low  | High | High |  |  |  |

| 120                             | High | Low  | Low  |  |  |  |

| 129                             | High | Low  | High |  |  |  |

| 139                             | High | High | Low  |  |  |  |

| 150                             | High | High | High |  |  |  |

|                                 |      |      |      |  |  |  |

### Table 2. MAX9708 Gain Setting

| G1   | G2   | GAIN (dB) |

|------|------|-----------|

| Low  | High | 22        |

| High | High | 25        |

| High | Low  | 29.5      |

| Low  | Low  | 36        |

#### **Operating Modes**

### Fixed-Frequency Modulation (FFM) Mode

The MAX9708 features three switching frequencies in the FFM mode (Table 3). In this mode, the frequency spectrum of the Class D output consists of the fundamental switching frequency and its associated harmonics (see the Wideband Output Spectrum graph in the *Typical Operating Characteristics*). Select one of the three fixed switching frequencies such that the harmonics do not fall in a sensitive band. The switching frequency can be changed at any time without affecting audio reproduction.

#### Spread-Spectrum Modulation (SSM) Mode

The MAX9708 features a unique, patented spreadspectrum (SSM) mode that flattens the wideband spectral components, improving EMI emissions that may be radiated by the speaker and cables. This mode is enabled by setting FS1 = FS2 = high. In SSM mode, the switching frequency varies randomly by ±4% around the center frequency (200kHz). The modulation scheme remains the same, but the period of the triangle waveform changes from cycle to cycle. Instead of a large amount of spectral energy present at multiples of the switching frequency, the energy is now spread over a bandwidth that increases with frequency. Above a few megahertz, the wideband spectrum looks like white noise for EMI purposes. SSM mode reduces EMI compared to fixed-frequency mode. This can also help to randomize visual artifacts caused by radiated or supply-borne interference in displays.

#### Synchronous Switching Mode

The MAX9708 SYNCIN input allows the Class D amplifier to switch at a frequency defined by an external clock frequency. Synchronizing the amplifier with an external clock source may confine the switching frequency to a less sensitive band. The external clock frequency range is from 600kHz to 1.2MHz and can have any duty cycle, but the minimum pulse must be greater than 100ns.

SYNCOUT is an open-drain clock output for synchronizing external circuitry. Its frequency is four times the amplifier's switching frequency, and it is active in either internal or external oscillator mode.

**Table 3. Switching Frequencies**

|   | FS1 | FS2 | SYNCOUT<br>FREQUENCY (kHz) | MODULATION      |

|---|-----|-----|----------------------------|-----------------|

| Ī | 0   | 0   | 200                        | Fixed-Frequency |

|   | 0   | 1   | 250                        | Fixed-Frequency |

| Ī | 1   | 0   | 160                        | Fixed-Frequency |

|   | 1   | 1   | 200 ±4                     | Spread-Spectrum |

#### **Linear Regulator (REG)**

The supply voltage range for the MAX9708 is from 10V to 18V to achieve high-output power. An internal linear regulator reduces this voltage to 6.3V for use with small-signal and digital circuitry that does not require a high-voltage supply. Bypass a  $0.01\mu F$  capacitor from REG to GND.

### Applications Information

#### **Logic Inputs**

All of the digital logic inputs and output have an absolute maximum rating of +12V. If the MAX9708 is operating with a supply voltage between 10V and 12V, digital inputs can be connected to PVDD or VDD. If PVDD and VDD are greater than 12V, digital inputs and outputs must connected to a digital system supply lower than 12V.

### **Input Amplifier**

#### Differential Input

The MAX9708 features a differential input structure, making them compatible with many CODECs, and offering improved noise immunity over a single-ended input amplifier. In devices such as flat-panel displays, noisy digital signals can be picked up by the amplifier's inputs. These signals appear at the amplifiers' inputs as common-mode noise. A differential input amplifier amplifies only the difference of the two inputs, while any signal common to both inputs is attenuated.

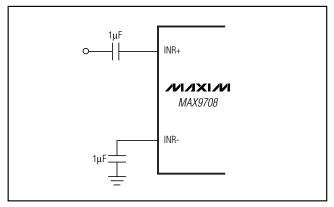

#### Single-Ended Input

The MAX9708 can be configured as a single-ended input amplifier by capacitively coupling either input to GND and driving the other input (Figure 4).

#### **Component Selection**

#### Input Filter

An input capacitor, C<sub>IN</sub>, in conjunction with the input impedance of the MAX9708, forms a highpass filter that removes the DC bias from an incoming signal. The AC-coupling capacitor allows the amplifier to bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN} C_{IN}}$$

Figure 4. Single-Ended Input Connections

Choose C<sub>IN</sub> so that f<sub>-3dB</sub> is well below the lowest frequency of interest. Setting f<sub>-3dB</sub> too high affects the low-frequency response of the amplifier. Use capacitors with dielectrics that have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with high-voltage coefficients, such as ceramics, may result in increased distortion at low frequencies.

#### **Output Filter**

The MAX9708 does not require an output filter. However, output filtering can be used if a design is failing radiated emissions due to board layout or cable length, or the circuit is near EMI-sensitive devices. Refer to the MAX9708 Evaluation Kit for suggested filter topologies. The tuning and component selection of the filter should be optimized for the load. A purely resistor load (8 $\Omega$ ) used for lab testing will require different components than a real, complex load-speaker load.

#### Charge-Pump Capacitor Selection

The MAX9708 has an internal charge-pump converter that produces a voltage level for internal circuitry. It requires a flying capacitor (C1) and a holding capacitor (C2). Use capacitors with an ESR less than  $100m\Omega$  for optimum performance. Low-ESR ceramic capacitors minimize the output resistance of the charge pump. For best performance over the extended temperature range, select capacitors with an X7R dielectric. The capacitors' voltage rating must be greater than 36V.

#### **Sharing Input Sources**

In certain systems, a single audio source can be shared by multiple devices (speaker and headphone amplifiers). When sharing inputs, it is common to mute the unused device, rather than completely shutting it down, preventing the unused device inputs from distorting the input signal. Mute the MAX9708 by driving MUTE low. Driving MUTE low turns off the Class D output stage, but does not affect the input bias levels of the MAX9708.

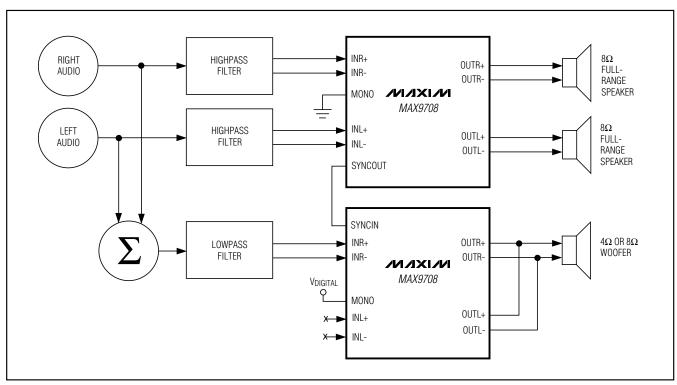

#### Frequency Synchronization

The MAX9708 outputs up to 21W on each channel in stereo mode. If higher output power or a 2.1 solution is needed, two MAX9708s can be used. Each MAX9708 is synchronized by connecting SYNCOUT from the first MAX9708 to SYNCIN of the second MAX9708 (see Figure 5).

#### Supply Bypassing/Layout

Proper power-supply bypassing ensures low-distortion operation. For optimum performance, bypass PVDD to PGND with a 0.1µF capacitor as close to each PVDD pin as possible. A low-impedance, high-current powersupply connection to PVDD is assumed. Additional bulk capacitance should be added as required depending on the application and power-supply characteristics. GND and PGND should be star-connected to system ground. For the TQFN package, solder the exposed paddle (EP) to the ground plane using multiple-plated through-hole vias. The exposed paddle must be soldered to the ground plane for rated power dissipation and good ground return. Use wider PC board traces to lower the parasitic resistance for the high-power output pins (OUTR+, OUTR-, OUTL+, OUTL-). Refer to the MAX9708 Evaluation Kit for layout guidance.

#### **Thermal Considerations**

Class D amplifiers provide much better efficiency and thermal performance than a comparable Class AB amplifier. However, the system's thermal performance must be considered with realistic expectations along with its many parameters.

#### Continuous Sine Wave vs. Music

When a Class D amplifier is evaluated in the lab, often a continuous sine wave is used as the signal source. While this is convenient for measurement purposes, it represents a worst-case scenario for thermal loading on the amplifier. It is not uncommon for a Class D amplifier to enter thermal shutdown if driven near maximum output power with a continuous sine wave. The PC board must be optimized for best dissipation (see the *PC Board Thermal Considerations* section).

Audio content, both music and voice, has a much lower RMS value relative to its peak output power. Therefore, while an audio signal may reach similar peaks as a continuous sine wave, the actual thermal impact on the Class D amplifier is highly reduced. If the thermal performance of a system is being evaluated, it is important to use actual audio signals instead of sine waves for testing. If sine waves must be used, the thermal performance will be less than the system's actual capability for real music or voice.

#### PC Board Thermal Considerations

The exposed pad is the primary route for conducting heat away from the IC. With a bottom-side exposed pad, the PC board and its copper becomes the primary heatsink for the Class D amplifier. Solder the exposed pad to a copper polygon. Add as much copper as possible from this polygon to any adjacent pin on the Class D amplifier as well as to any adjacent components, provided these connections are at the same potential. These copper paths must be as wide as possible. Each of these paths contributes to the overall thermal capabilities of the system.

The copper polygon to which the exposed pad is attached should have multiple vias to the opposite side of the PC board, where they connect to another copper polygon. Make this polygon as large as possible within the system's constraints for signal routing.

Additional improvements are possible if all the traces from the device are made as wide as possible. Although the IC pins are not the primary thermal path out of the package, they do provide a small amount. The total improvement would not exceed approximately 10%, but it could make the difference between acceptable performance and thermal problems.

#### Auxiliary Heatsinking

If operating in higher ambient temperatures, it is possible to improve the thermal performance of a PC board with the addition of an external heatsink. The thermal resistance to this heatsink must be kept as low as possible to maximize its performance. With a bottom-side exposed pad, the lowest resistance thermal path is on the bottom of the PC board. The topside of the IC is not a significant thermal path for the device, and therefore is not a cost-effective location for a heatsink. If an LC filter is used in the design, placing the inductor in close proximity to the IC can help draw heat away from the MAX9708.

#### Thermal Calculations

The die temperature of a Class D amplifier can be estimated with some basic calculations. For example, the die temperature is calculated for the below conditions:

- $T_A = +40^{\circ}C$

- Pout = 16W

- Efficiency (η) = 87%

- $\theta_{JA} = 21^{\circ}C/W$

First, the Class D amplifier's power dissipation must be calculated:

$$P_{DISS} = \frac{P_{OUT}}{\eta} - P_{OUT} = \frac{16W}{0.87} - 16W = 2.4W$$

Then the power dissipation is used to calculate the die temperature, T<sub>C</sub>, as follows:

$$T_C = T_A + P_{DISS} \times \theta_{JA} = 40^{\circ}C + 24W \times 21^{\circ}C/W = 90.4^{\circ}C$$

#### Load Impedance

The on-resistance of the MOSFET output stage in Class D amplifiers affects both the efficiency and the peak-current capability. Reducing the peak current into the load reduces the I<sup>2</sup>R losses in the MOSFETs, which increases efficiency. To keep the peak currents lower, choose the highest impedance speaker that can still deliver the desired output power within the voltage swing limits of the Class D amplifier and its supply voltage.

Although most loudspeakers fall either  $4\Omega$  or  $8\Omega$ , there are other impedances available that can provide a more thermally efficient solution.

Another consideration is the load impedance across the audio frequency band. A loudspeaker is a complex electro-mechanical system with a variety of resonance. In other words, an  $8\Omega$  speaker usually has  $8\Omega$  impedance within a very narrow range. This often extends well below  $8\Omega$ , reducing the thermal efficiency below what is expected. This lower-than-expected impedance can be further reduced when a crossover network is used in a multidriver audio system.

#### **Systems Application Circuit**

The MAX9708 can be configured into multiple amplifier systems. One concept is a 2.1 audio system (Figure 5) where a stereo audio source is split into three channels. The left- and right-channel inputs are highpass filtered to remove the bass content, and then amplified by the MAX9708 in stereo mode. Also, the left- and right-channel inputs are summed together and lowpass filtered to remove the high-frequency content, then amplified by a second MAX9708 in mono mode.

The conceptual drawing of Figure 5 can be applied to either single-ended or differential systems. Figure 6 illustrates the circuitry required to implement a fully differential filtering system. By maintaining a fully differential path, the signal-to-noise ratio remains uncompromised and noise pickup is kept very low. However, keeping a fully differential signal path results in almost twice the component count, and therefore performance must be weighed against cost and size.

The highpass and lowpass filters should have different cutoff frequencies to ensure an equal power response at the crossover frequency. The filters should be at -6dB amplitude at the crossover frequency, which is known as a Linkwitz-Riley alignment. In the example circuit of Figure 6, the -3dB cutoff frequency for the highpass filters is 250Hz, and the -3dB cutoff frequency for the lowpass filter is 160Hz. Both the highpass filters and the lowpass filters are at a -6dB amplitude at approximately 200Hz. If the filters were to have the same -3dB cutoff frequency, a measurement of sound pressure level (SPL) vs. frequency would have a peak at the crossover frequency.

The circuit in Figure 6 uses inverting amplifiers for their ease in biasing. Note the phase labeling at the outputs has been reversed. The resistors should be 1% or better in tolerance and the capacitors 5% tolerance or better.

Mismatch in the components can cause discrepancies between the nominal transfer function and actual performance. Also, the mismatch of the input resistors (R15, R17, R19, and R21 in Figure 6) of the summing amplifier and lowpass filter will cause some high-frequency sound to be sent to the subwoofer.

The circuit in Figure 6 drives a pair of MAX9708 devices similar to the circuit in Figure 5. The inputs to the MAX9708 still require AC-coupling to prevent compromising the click-and-pop performance of the MAX9708.

The left and right drivers should be at an  $8\Omega$  to  $12\Omega$  impedance, whereas the subwoofer can be  $4\Omega$  to  $12\Omega$  depending on the desired output power, the available power-supply voltage, and the sensitivity of the individual speakers in the system. The four gain settings of the MAX9708 allow gain adjustments to match the sensitivity of the speakers.

Figure 5. Multiple Amplifiers Implement a 2.1 Audio System

Figure 6. Fully Differential Crossover Filters

**Pin Configurations**

### Pin Configurations (continued)

\_\_\_\_Chip Information

PROCESS: BiCMOS

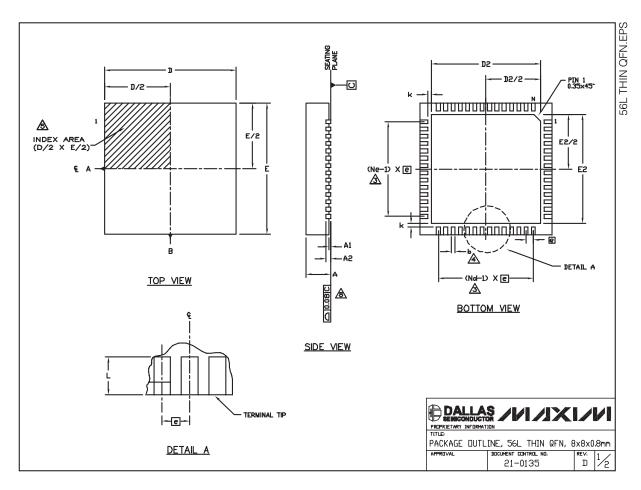

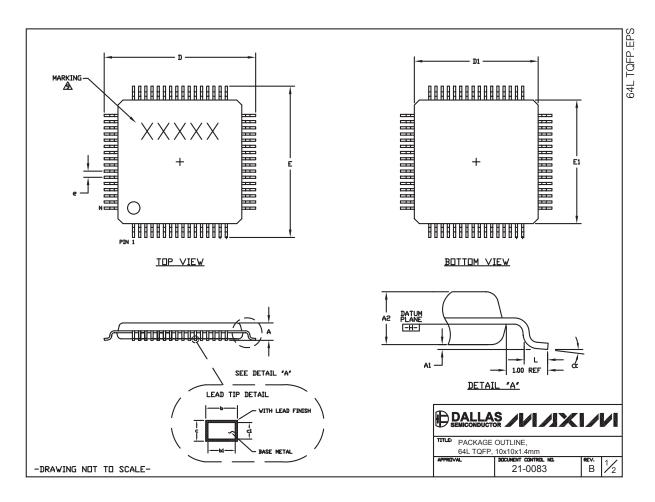

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

#### NOTES:

1. DIE THICKNESS ALLOWABLE IS 0.225mm MAXIMUM (0.009 INCHES MAXIMUM).

2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. - 1994.

$\sqrt{3.}$  N is the number of terminals.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION & No IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

4. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

5. THE PIN #1 IDENTIFIER MUST BE LOCATED ON THE TOP SURFACE OF THE PACKAGE WITHIN HATCHED AREA AS SHOWN.

EITHER AN INDENTATION MARK OR INK/LASER MARK IS ACCEPTABLE.

6. ALL DIMENSIONS ARE IN MILLIMETERS.

7. PACKAGE WARPAGE MAX 0.01mm.

APPLIES TO EXPOSED PAD AND TERMINALS. EXCLUDES INTERNAL DIMENSION OF EXPOSED PAD.

9. MEETS JEDEC MO220.

| - OWE (B  | 5    | 8              | No.  |   |  |  |  |

|-----------|------|----------------|------|---|--|--|--|

| <b></b> • | MIN. | MIN. NOM. MAX. |      |   |  |  |  |

| Α         | 0.70 | 0.75           | 0.80 |   |  |  |  |

| Ь         | 0.20 | 0.25           | 0.30 | 4 |  |  |  |

| D         | 7.90 | 8.00           | 8.10 |   |  |  |  |

| E         | 7.90 | 8.00           | 8.10 |   |  |  |  |

| е         |      | 0.50 BSC       | ;    |   |  |  |  |

| N         |      | 56             |      | 3 |  |  |  |

| Nd        |      | 14             |      | 3 |  |  |  |

| Ne        |      | 14             |      | 3 |  |  |  |

| L         | 0.30 | 0.40           | 0.50 |   |  |  |  |

| A1        | 0.00 | 0.02           | 0.05 |   |  |  |  |

| A2        |      | 0.20 REF       |      |   |  |  |  |

| k         | 0.25 |                |      |   |  |  |  |

|         | EXPOSED PAD VARIATION |      |      |      |      |      |        |               |

|---------|-----------------------|------|------|------|------|------|--------|---------------|

| PKG.    | D2                    |      |      | E2   |      |      | JEDEC  | DOWN<br>BONDS |

| CODE    | MIN.                  | NOM. | MAX. | MIN. | NOM. | MAX. | ULDLO  | ALLOVED       |

| T5688-1 | 6.50                  | 6.65 | 6.70 | 6.50 | 6.65 | 6.70 | WLLD-5 | NO            |

| T5688-2 | 6.50                  | 6.65 | 6.70 | 6.50 | 6.65 | 6.70 | WLLD-5 | YES           |

| T5688-3 | 6.50                  | 6.65 | 6.70 | 6.50 | 6.65 | 6.70 | WLLD-5 | N0            |

### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

#### NOTES:

- 1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5-1982.

2. DATUM PLANE HE IS LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

3. DIMENSIONS D1 AND E1 D0 NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.25 MM ON D1 AND E1

- 4. THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE

- 4. HE TOP OF PACKAGE IS SMALLER THAN THE BUTTOM OF PACKAGE BY 0.15 MILLIMETERS.

5. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE & DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. ALL DIMENSIONS ARE IN MILLIMETERS.

- THIS DUTLINE CONFORMS TO JEDEC PUBLICATION 95, REGISTRATION MS-026, VARIATION BCD.

8. LEADS SHALL BE COPLANAR WITHIN .004 INCH.

AMARKING SHOWN IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

| JEDEC VARIATION |           |       |  |  |  |  |

|-----------------|-----------|-------|--|--|--|--|

|                 | BCD       |       |  |  |  |  |

|                 | 64 LEAD   |       |  |  |  |  |

|                 | MIN.      | MAX.  |  |  |  |  |

| Α               |           | 1.60  |  |  |  |  |

| A <sub>1</sub>  | 0.05      | 0.15  |  |  |  |  |

| Ag              | 1.35      | 1.45  |  |  |  |  |

| D               | 11.80     | 12.20 |  |  |  |  |

| D <sub>1</sub>  | 9.80      | 10.20 |  |  |  |  |

| Ε               | 11.80     | 12.20 |  |  |  |  |

| E <sub>1</sub>  | 9.80      | 10.20 |  |  |  |  |

| e               | 0.50 BSC. |       |  |  |  |  |

| L               | 0.45      | 0.75  |  |  |  |  |

| b               | 0.17      | 0.27  |  |  |  |  |

| b1              | 0.17      | 0.23  |  |  |  |  |

| С               | 0.09      | 0.20  |  |  |  |  |

| <b>c</b> 1      | 0.09      | 0.16  |  |  |  |  |

| α               | 0,        | 7°    |  |  |  |  |

DALLAS /// SEMICONDUCTOR ///

PACKAGE OUTLINE.

64L TQFP, 10x10x1.4mm 21-0083

-DRAWING NOT TO SCALE-

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.