# CMX850 Communications Controller

D/850/2 April 2002 Advance Information

#### **Features**

- 8051 mC with internal 8K XRAM and up to 35 GPIO

- 64K address, bank switchable to many Mbytes

- Interfaces for external RAM, LCD controller

- V.22bis, V.22, V.23, V.21 (and Bell) integral modem

- · DTMF/Tones transmit and receive

- · Line and Phone differential amplifiers

- · Dual clocks with separate Xtals

- CAS Tones detection and generation

- · Line reversal / Ring detection

- · Off-hook detector

- Low power operation

- · Advanced power management features

- · Watchdog timer

- · Real-time clock and alarm function

- Standard 8051 UART and timers

- · 2 input 10-bit A to D converter

- Keyboard encoder (16 x 8 matrix max)

- 2 x low power PWM outputs

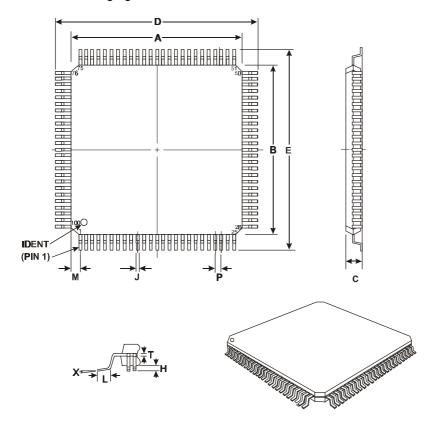

- Small footprint: 100-pin LQFP

#### **Applications**

- · SMS and ADSI terminals

- · Telemetry and meter reading systems

- · Security systems

- · Feature phones

- Routers

- · EPOS terminals

- E-Mail and Internet appliances

#### 1.1 Brief Description

This IC combines an extended function CMX860 with a full-function 8051 microcontroller (including UART and timer/counters), and has 8kbytes of RAM to form a powerful communications processor. Extended addressing offers page mode access to 4Mbytes of external Flash memory. A 32.768kHz clock system allows a very low power interrupt-driven real time clock, watchdog timer, and keyboard encoder. The device also includes a separate CAS tone detector, two low power PWM outputs and a multiplexed 2-input 10-bit A to D converter with auto-convert and threshold detect. Advanced low power and sleep modes, including the ability to operate from an on-chip RC oscillator, contribute to low battery consumption.

## **CONTENTS**

| <u>Section</u> |         |               | <u>Page</u>                                 |

|----------------|---------|---------------|---------------------------------------------|

| 1.0            | Featur  | es and Applic | cations1                                    |

| 1.1            | Brief D | escription    | 1                                           |

| 1.2            | Block   | Diagram       | 4                                           |

| 1.3            | Signal  | List          | 5                                           |

| 1.4            | Extern  | al Componer   | nts8                                        |

|                | 1.4.1   |               | or Interface10                              |

|                | 1.4.2   |               | tor Interface11                             |

|                | 1.4.3   | RESETN pin    | 111                                         |

|                | 1.4.4   | Line Interfac | ce12                                        |

| 1.5            | Microc  | ontroller Cor | e14                                         |

|                | 1.5.1   |               | ction Register Memory Map14                 |

|                | 1.5.2   |               | ointer15                                    |

|                |         | 1.5.2.1       | DPTR1 Registers (DPL1/DPH1)15               |

|                |         | 1.5.2.2       | Data Pointer Select Register (DPS)15        |

|                | 1.5.3   | I/O Ports     | 16                                          |

|                |         | 1.5.3.1       | Port Data Registers (P0-P5)17               |

|                |         | 1.5.3.2       | Port Direction Registers (P0DIR-P5DIR) 17   |

|                |         | 1.5.3.3       | Port Open-Drain Registers (P10D-P50D)17     |

|                |         | 1.5.3.4       | Port Res Pull-up Registers (P1RES-P5RES) 18 |

|                | 1.5.4   | Memory Inte   | erface19                                    |

|                |         | 1.5.4.1       | Memory Control Register (MEMCON)19          |

|                | 1.5.5   | Interrupts    | 21                                          |

|                |         | 1.5.5.1       | Interrupt Enable 1 Register (IE_1)22        |

|                |         | 1.5.5.2       | Interrupt Priority 1 Register (IP_1)22      |

|                |         | 1.5.5.3       | Interrupt Control Registers (ICON1A/B)22    |

|                | 1.5.6   |               | nd Power Management23                       |

|                |         | 1.5.6.1       | Oscillator Control Register (OSCCON)23      |

|                |         | 1.5.6.2       | Speed Control Register (SPDCON)25           |

|                |         | 1.5.6.3       | Speed Control Exit Register (SPXMASK)26     |

|                |         | 1.5.6.4       | Power Down Exit Register (PDXMASK)27        |

|                | 1.5.7   |               | Modulators28                                |

|                |         | 1.5.7.1       | PWM Control Register (PWMCON)28             |

|                |         | 1.5.7.2       | PWM Data Registers (PWM1, PWM2)29           |

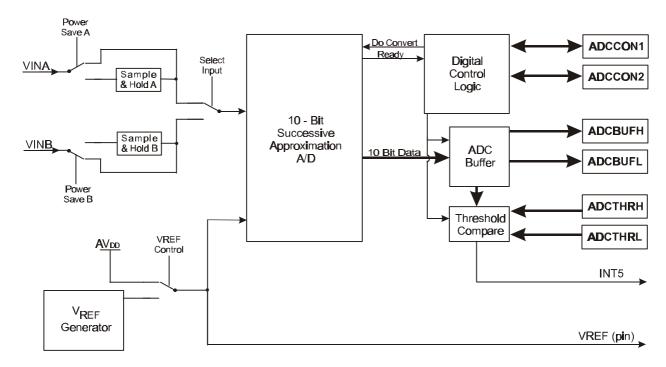

|                | 1.5.8   |               | igital Converter30                          |

|                |         | 1.5.8.1       | ADC Control Registers (ADCCON1/2)30         |

|                |         | 1.5.8.2       | ADC Buffer Registers (ADCBUFL/H)34          |

|                |         | 1.5.8.3       | ADC Threshold Registers (ADCTHRL/H)35       |

|                | 1.5.9   |               | roller35                                    |

|                |         | 1.5.9.1       | C-BUS Control Register (CBUSCON)36          |

|                |         | 1.5.9.2       | C-BUS Buffer Register (CBUSBUF)37           |

|                | 1.5.10  | •             | ncoder38                                    |

|                |         | 1.5.10.1      | Keyboard Control Register (KBCON)38         |

|                |         | 1.5.10.2      | Keyboard Status Register (KBSTAT)39         |

|                |         | 1.5.10.3      | Keyboard Buffer Register (KBBUF)40          |

|     | 1.5.11 | watchdog i ir               | ner                                  | 41 |  |  |  |  |

|-----|--------|-----------------------------|--------------------------------------|----|--|--|--|--|

|     |        | 1.5.11.1                    | Watchdog Control Register (WDTCON)   | 41 |  |  |  |  |

|     |        | 1.5.11.2                    | Watchdog Load Register (WDTLD)       | 43 |  |  |  |  |

|     | 1.5.12 | Real Time Clo               | ock                                  | 44 |  |  |  |  |

|     |        | 1.5.12.1                    | RTC Control Register (RTCCON)        | 44 |  |  |  |  |

|     |        | 1.5.12.2                    | RTC Time Registers (TIME0-TIME3)     |    |  |  |  |  |

|     |        | 1.5.12.3                    | RTC Alarm Registers (ALM0-ALM3)      | 46 |  |  |  |  |

|     | 1.5.13 | <b>CAS Tone De</b>          | tector                               |    |  |  |  |  |

|     |        | 1.5.13.1                    | CAS Detect Control Register (CASDET) | 48 |  |  |  |  |

| 1.6 | Moden  | n General Desc              | cription                             | 50 |  |  |  |  |

|     | 1.6.1  |                             |                                      |    |  |  |  |  |

|     | 1.6.2  | FSK and QAM                 | //DPSK Modulators                    | 53 |  |  |  |  |

|     | 1.6.3  | Tx Filter and               | Equaliser                            | 54 |  |  |  |  |

|     | 1.6.4  | DTMF/Tone G                 | Generator                            | 54 |  |  |  |  |

|     | 1.6.5  | Tx Level Con                | trol and Output Drivers              | 54 |  |  |  |  |

|     | 1.6.6  | DTMF Decode                 | er and Tone Detectors                | 55 |  |  |  |  |

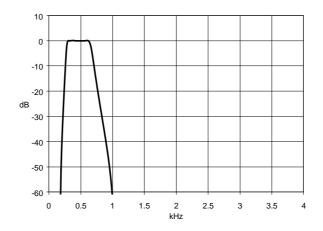

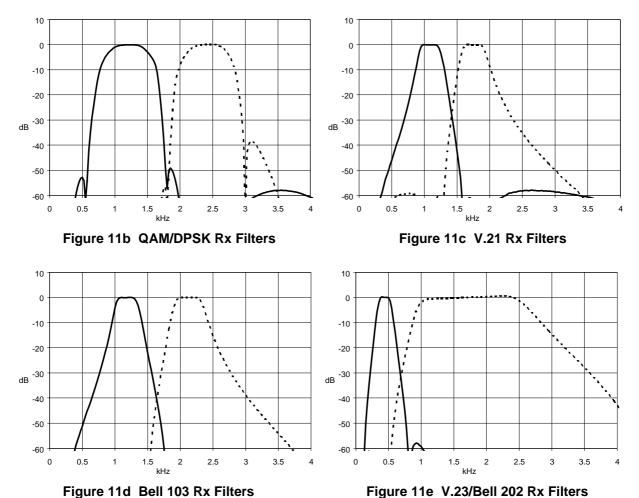

|     | 1.6.7  | Rx Modem Fi                 | Iterering and Demodulation           | 56 |  |  |  |  |

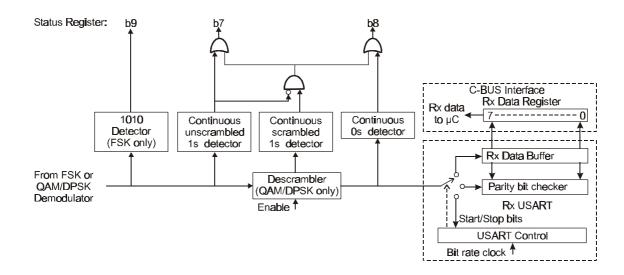

|     | 1.6.8  | Rx Modem Pa                 | attern Detectors and Descrambler     | 57 |  |  |  |  |

|     | 1.6.9  | Rx Data Register and USART5 |                                      |    |  |  |  |  |

|     | 1.6.10 | Analogue Signal Routing     |                                      |    |  |  |  |  |

|     | 1.6.11 | 'C-BUS' Interf              | ace                                  | 59 |  |  |  |  |

|     |        | 1.6.11.1                    | General Reset Command                | 59 |  |  |  |  |

|     |        | 1.6.11.2                    | General Control Register             | 60 |  |  |  |  |

|     |        | 1.6.11.3                    | Transmit Mode Register               |    |  |  |  |  |

|     |        | 1.6.11.4                    | Receive Mode Register                |    |  |  |  |  |

|     |        | 1.6.11.5                    | Tx Data Register                     | 67 |  |  |  |  |

|     |        | 1.6.11.6                    | Rx Data Register                     |    |  |  |  |  |

|     |        | 1.6.11.7                    | Analogue Signal Path Register        |    |  |  |  |  |

|     |        | 1.6.11.8                    | Status Register                      |    |  |  |  |  |

|     |        | 1.6.11.9                    | Status Register                      |    |  |  |  |  |

|     |        | 1.6.11.10                   | Programming Register                 |    |  |  |  |  |

|     |        | 1.6.11.11                   | Other Registers                      |    |  |  |  |  |

| 1.7 | Perfor | mance Specific              | cation                               | 76 |  |  |  |  |

|     | 1.7.1  | <b>Electrical Per</b>       | formance                             | 76 |  |  |  |  |

|     |        | 1.7.1.1 Absol               | ute Maximum Ratings                  | 76 |  |  |  |  |

|     |        |                             | iting Limits                         |    |  |  |  |  |

|     |        | 1.7.1.3 Opera               | ting Characteristics                 | 77 |  |  |  |  |

|     | 1.7.2  | Packaging                   |                                      | 87 |  |  |  |  |

**Note:** This product is in development: Changes and additions will be made to this specification. Items marked TBD or left blank will be included in later issues.

Information in this data sheet should not be relied upon for final product design.

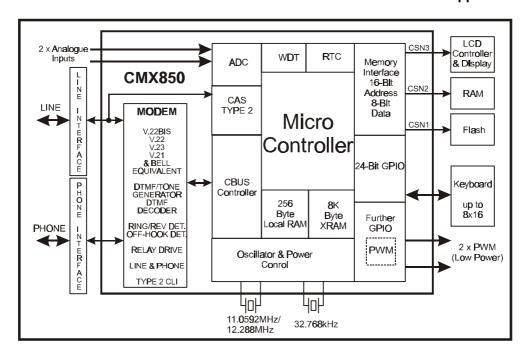

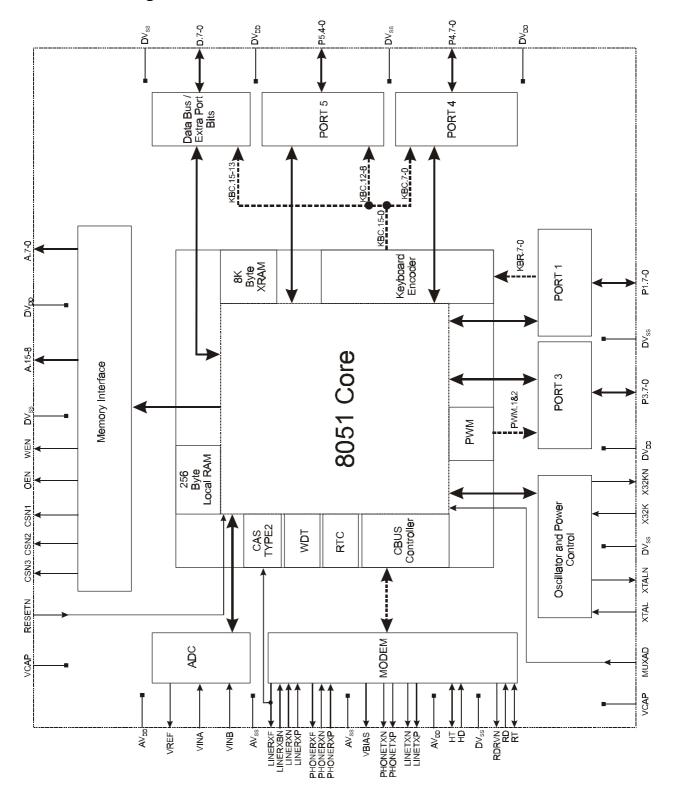

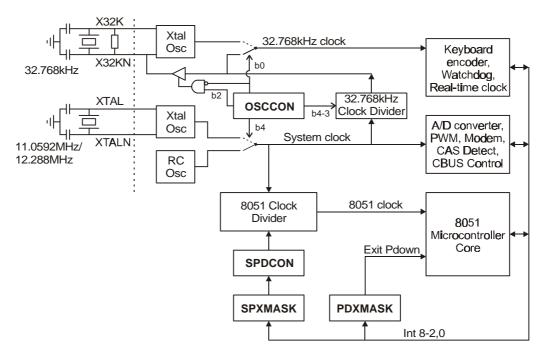

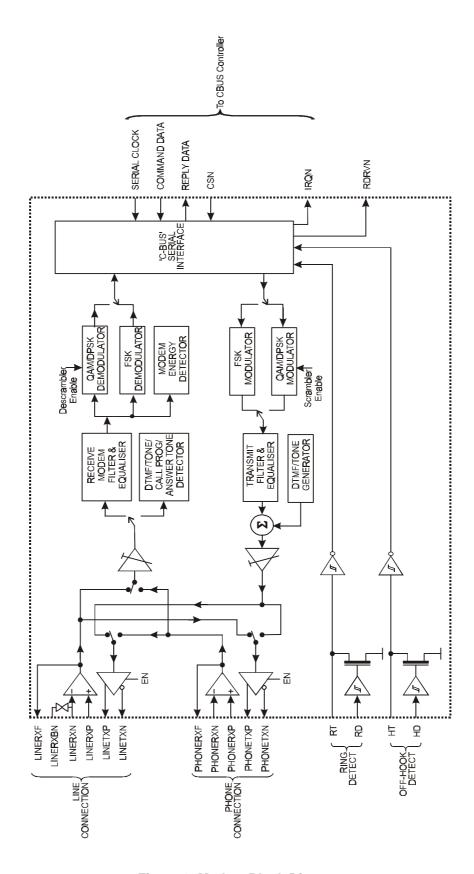

# 1.2 Block Diagram

Figure 1 Block Diagram

# 1.3 Signal List

| Package<br>L8 | Signa            | <u> </u> | Description                                                                                                                                                                                               |  |  |  |

|---------------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin No.       | Name             | Туре     |                                                                                                                                                                                                           |  |  |  |

| 1             | VCAP             | O/P      | Decoupling capacitor                                                                                                                                                                                      |  |  |  |

| 2             | MUXAD            | I/P      | Multiplexed address/data bus select for external memory. Tie to $DV_SS$ for non-multiplexed address/data. Tie to $DV_DD$ for multiplexed address/data (frees up the D7-0 pins for alternative functions). |  |  |  |

| 3             | XTAL             | I/P      | The input to the 11.0592MHz or 12.288MHz oscillator circuit from the Xtal or external clock source.                                                                                                       |  |  |  |

| 4             | XTALN            | O/P      | The output of the on-chip 11.0592MHz/12.288MHz Xtal oscillator circuit.                                                                                                                                   |  |  |  |

| 5             | DV <sub>SS</sub> | Power    | The digital negative supply rail (ground).                                                                                                                                                                |  |  |  |

| 6             | X32K             | I/P      | The input to the 32.768kHz oscillator circuit from the Xtal.                                                                                                                                              |  |  |  |

| 7             | X32KN            | O/P      | also be used to output an internally derived 32.768kHz signal                                                                                                                                             |  |  |  |

| 8             | $DV_{DD}$        | Power    | 3 1 11 7                                                                                                                                                                                                  |  |  |  |

| 9             | P3.0 (RXD)       | BI       | Port 3 bit 0. Alternative function is serial port receive data.                                                                                                                                           |  |  |  |

| 10            | P3.1 (TXD)       | BI       | Port 3 bit 1. Alternative function is serial port transmit data.                                                                                                                                          |  |  |  |

| 11            | P3.2 (INT0)      | BI       | Port 3 bit 2. Alternative function is Int0 interrupt input.                                                                                                                                               |  |  |  |

| 12            | P3.3 (INT1)      | BI       | Port 3 bit 3. Alternative function is Int1 interrupt input.                                                                                                                                               |  |  |  |

| 13            | P3.4 (T0)        | BI       | Port 3 bit 4. Alternative function is Timer 0 control input.                                                                                                                                              |  |  |  |

| 14            | P3.5 (T1)        | BI       | Port 3 bit 5. Alternative function is Timer 1 control input.                                                                                                                                              |  |  |  |

| 15            | P3.6 (PWM1)      | BI       | Port 3 bit 6. Alternative function is PWM 1 output.                                                                                                                                                       |  |  |  |

| 16            | P3.7 (PWM2)      | BI       | Port 3 bit 7. Alternative function is PWM 2 output.                                                                                                                                                       |  |  |  |

| 17            | DV <sub>SS</sub> | Power    | The digital negative supply rail (ground).                                                                                                                                                                |  |  |  |

| 18            | P1.0 (KBR.0)     | BI       | Port 1 bits 7-0. Alternative function is keyboard row input pins,                                                                                                                                         |  |  |  |

| 19            | P1.1 (KBR.1)     | BI       | bits 7-0.                                                                                                                                                                                                 |  |  |  |

| 20            | P1.2 (KBR.2)     | BI       |                                                                                                                                                                                                           |  |  |  |

| 21            | P1.3 (KBR.3)     | BI       |                                                                                                                                                                                                           |  |  |  |

| 22            | P1.4 (KBR.4)     | BI       |                                                                                                                                                                                                           |  |  |  |

| 23            | P1.5 (KBR.5)     | BI       | 7                                                                                                                                                                                                         |  |  |  |

| 24            | P1.6 (KBR.6)     | BI       | 7                                                                                                                                                                                                         |  |  |  |

| 25            | P1.7 (KBR.7)     | BI       |                                                                                                                                                                                                           |  |  |  |

| 26            | DV <sub>DD</sub> | Power    | The digital positive supply rail.                                                                                                                                                                         |  |  |  |

| 27            | P4.0 (KBC.0)     | BI       | Port 4 bits 7-0. Alternative function is keyboard column drivers,                                                                                                                                         |  |  |  |

| 28            |                  |          | bits 7-0. Unused column drivers remain as general-purpose port pins.                                                                                                                                      |  |  |  |

| 29            | P4.2 (KBC.2)     | BI       | _ ροιτ ρίπο.<br>                                                                                                                                                                                          |  |  |  |

| 30            | P4.3 (KBC.3)     | BI       | 7                                                                                                                                                                                                         |  |  |  |

| 31            | P4.4 (KBC.4)     | BI       |                                                                                                                                                                                                           |  |  |  |

| 32            | P4.5 (KBC.5)     | BI       |                                                                                                                                                                                                           |  |  |  |

| 33            | P4.6 (KBC.6)     | BI       | 7                                                                                                                                                                                                         |  |  |  |

| 34            | P4.7 (KBC.7)     | BI       |                                                                                                                                                                                                           |  |  |  |

| Package<br>L8 | Signal             |                 | Description                                                           |                                                        |  |  |

|---------------|--------------------|-----------------|-----------------------------------------------------------------------|--------------------------------------------------------|--|--|

| 35            | DV <sub>SS</sub>   | Power           | The digital negative supply rail                                      | (ground).                                              |  |  |

| 36            | P5.0 (KBC.8)       | BI              |                                                                       | tion is keyboard column drivers,                       |  |  |

| 37            | P5.1 (KBC.9)       | BI              | bits 12-8. Unused column drive                                        | rs remain as general-purpose                           |  |  |

| 38            | P5.2 (KBC.10)      | BI              | port pins.                                                            |                                                        |  |  |

| 39            | P5.3 (KBC.11)      | BI              |                                                                       |                                                        |  |  |

| 40            | P5.4 (KBC.12)      | BI              |                                                                       |                                                        |  |  |

| 41            | $DV_{DD}$          | Power           | The digital positive supply rail.                                     |                                                        |  |  |

|               |                    |                 | With pin MUXAD tied to DV <sub>SS</sub> : With pin MUXAD tied to DV   |                                                        |  |  |

| 42            | D0: P5.5 (KBC.13)  | BI : <i>BI</i>  | Bi-directional data bus for                                           | Port 5 bits 7-5. Alternative                           |  |  |

| 43            | D1: P5.6 (KBC.14)  | BI : <i>BI</i>  | external memory. function is keyboard col<br>drivers, bits 15-13. Unu |                                                        |  |  |

| 44            | D2 : P5.7 (KBC.15) | BI : <i>BI</i>  |                                                                       | column drivers remain as general-purpose port pins.    |  |  |

| 45            | D3 : P0.0          | BI : <i>BI</i>  |                                                                       | Port 0 bits 2-0.                                       |  |  |

| 46            | D4: P0.1           | BI : <i>BI</i>  |                                                                       |                                                        |  |  |

| 47            | D5 : P0.2          | BI : <i>BI</i>  |                                                                       |                                                        |  |  |

| 48            | D6 : INT9          | BI : <i>I/P</i> |                                                                       | Super priority interrupt.                              |  |  |

| 49            | D7 : <i>ALE</i>    | BI : <i>O/P</i> | Address latch enable.                                                 |                                                        |  |  |

| 50            | DV <sub>SS</sub>   | Power           | The digital negative supply rail (ground).                            |                                                        |  |  |

|               |                    |                 | With pin MUXAD tied to $DV_{SS}$ :                                    | With pin MUXAD tied to $DV_{DD}$ :                     |  |  |

| 51            | A0 : <i>AD0</i>    | O/P : <i>BI</i> | External memory interface                                             | External memory interface                              |  |  |

| 52            | A1 : <i>AD1</i>    | O/P : <i>BI</i> | address bus (LSB).                                                    | multiplexed address (LSB) and data. While ALE is high, |  |  |

| 53            | A2 : <i>AD</i> 2   | O/P : <i>BI</i> |                                                                       | the LSB of the memory                                  |  |  |

| 54            | A3 : <i>AD</i> 3   | O/P : <i>BI</i> |                                                                       | address is driven out. When                            |  |  |

| 55            | A4 : <i>AD4</i>    | O/P : <i>BI</i> |                                                                       | ALE goes low, the pins change to a bi-directional      |  |  |

| 56            | A5 : <i>AD</i> 5   | O/P : <i>BI</i> |                                                                       | data bus.                                              |  |  |

| 57            | A6 : <i>AD</i> 6   | O/P : <i>BI</i> |                                                                       |                                                        |  |  |

| 58            | A7 : <i>AD</i> 7   | O/P : <i>BI</i> |                                                                       |                                                        |  |  |

| 59            | DV <sub>DD</sub>   | Power           | The digital positive supply rail.                                     |                                                        |  |  |

| 60            | A8                 | O/P             | External memory interface addr                                        | ress bus (MSB).                                        |  |  |

| 61            | A9                 | O/P             |                                                                       |                                                        |  |  |

| 62            | A10                | O/P             |                                                                       |                                                        |  |  |

| 63            | A11                | O/P             |                                                                       |                                                        |  |  |

| 64            | A12                | O/P             |                                                                       |                                                        |  |  |

| 65            | A13                | O/P             |                                                                       |                                                        |  |  |

| 66            | A14                | O/P             |                                                                       |                                                        |  |  |

| 67            | A15                | O/P             |                                                                       |                                                        |  |  |

| 68            | DV <sub>SS</sub>   | Power           | The digital negative supply rail                                      | (ground).                                              |  |  |

| 69            | WEN                | O/P             | External memory read/~write co                                        |                                                        |  |  |

| 70            | OEN                | O/P             | External memory output enable                                         | (active low).                                          |  |  |

| 71            | CSN1               | O/P             | External memory chip select #1                                        | (active low).                                          |  |  |

| Package<br>L8 | L8 Signal        |       | Description                                                                                                                                                                                                                                |

|---------------|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 72            | CSN2             | O/P   | External memory chip select #2 (active low).                                                                                                                                                                                               |

| 73            | CSN3             | O/P   | External memory chip select #3 (active low).                                                                                                                                                                                               |

| 74            | RESETN           | I/P   | Chip reset (active low).                                                                                                                                                                                                                   |

| 75            | VCAP             | O/P   | Decoupling capacitor                                                                                                                                                                                                                       |

| 76            | $AV_{DD}$        | Power | The analogue positive supply rail. Levels and thresholds within the modem are proportional to this voltage.                                                                                                                                |

| 77            | VREF             | O/P   | A/D converter voltage reference output.                                                                                                                                                                                                    |

| 78            | VINA             | I/P   | A/D converter input A.                                                                                                                                                                                                                     |

| 79            | VINB             | I/P   | A/D converter input B.                                                                                                                                                                                                                     |

| 80            | AV <sub>SS</sub> | Power | The analogue negative supply rail (ground).                                                                                                                                                                                                |

| 81            | LINERXF          | O/P   | The output of the Line Rx Input Amplifier.                                                                                                                                                                                                 |

| 82            | LINERXBN         | I/P   | An auxiliary inverting input to the Line Rx Input Amplifier, switched in parallel with LINERXN to boost gain.                                                                                                                              |

| 83            | LINERXN          | I/P   | The inverting input to the Line Rx Input Amplifier.                                                                                                                                                                                        |

| 84            | LINERXP          | I/P   | The non-inverting input to the Line Rx Input Amplifier.                                                                                                                                                                                    |

| 85            | PHONERXF         | O/P   | The output of the Phone Rx Input Amplifier.                                                                                                                                                                                                |

| 86            | PHONERXN         | I/P   | The inverting input to the Phone Rx Input Amplifier.                                                                                                                                                                                       |

| 87            | PHONERXP         | I/P   | The non-inverting input to the Phone Rx Input Amplifier.                                                                                                                                                                                   |

| 88            | AV <sub>SS</sub> | Power | The analogue negative supply rail (ground).                                                                                                                                                                                                |

| 89            | VBIAS            | O/P   | Internally generated bias voltage of approximately $AV_{SS}/2$ , except when the device is in 'Power save' mode when VBIAS will discharge to $AV_{SS}$ . Should be decoupled to $AV_{SS}$ by a capacitor mounted close to the device pins. |

| 90            | PHONETXN         | O/P   | The inverted output of the Phone Tx Output Driver.                                                                                                                                                                                         |

| 91            | PHONETXP         | O/P   | The non-inverted output of the Phone Tx Output Driver.                                                                                                                                                                                     |

| 92            | LINETXN          | O/P   | The inverted output of the Line Tx Output Driver.                                                                                                                                                                                          |

| 93            | LINETXP          | O/P   | The non-inverted output of the Line Tx Output Driver.                                                                                                                                                                                      |

| 94            | AV <sub>DD</sub> | Power | The analogue positive supply rail. Levels and thresholds within the modem are proportional to this voltage.                                                                                                                                |

| 95            | НТ               | BI    | Open drain output and Schmitt trigger input forming part of the Hook signal detector. Connect to DV <sub>DD</sub> if Hook Detector not used.                                                                                               |

| 96            | HD               | I/P   | Schmitt trigger input to the Hook signal detector. Connect to DV <sub>SS</sub> if Hook Detector not used.                                                                                                                                  |

| 97            | DV <sub>SS</sub> | Power | The digital negative supply rail (ground).                                                                                                                                                                                                 |

| 98            | RDRVN            | O/P   | Relay drive output, low resistance pull down to DV <sub>SS</sub> when active, medium resistance pull up to DV <sub>DD</sub> when inactive.                                                                                                 |

| 99            | RD               | I/P   | Schmitt trigger input to the Ring signal detector. Connect to DV <sub>SS</sub> if Ring Detector not used.                                                                                                                                  |

| 100           | RT               | BI    | Open drain output and Schmitt trigger input forming part of the Ring signal detector. Connect to DV <sub>DD</sub> if Ring Detector not used.                                                                                               |

I/P = O/P = BI Input Output Notes:

ВΙ Bi-directional

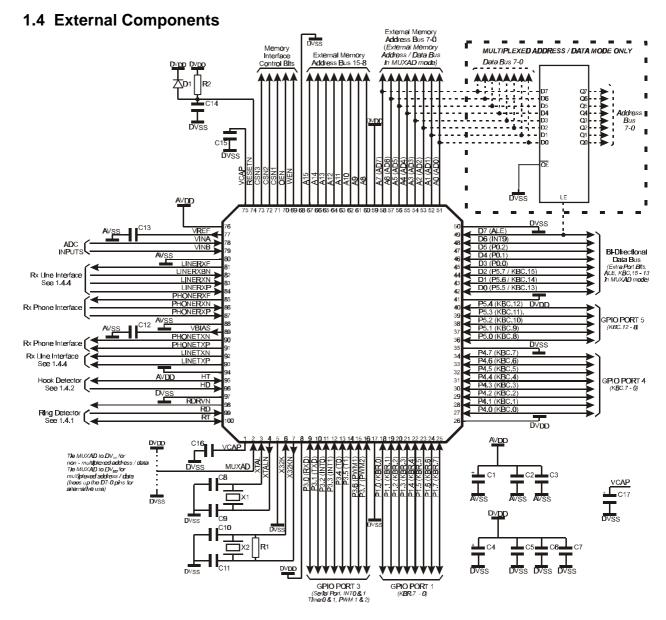

Figure 2a Recommended External Components for a Typical Application

| C1, C4,C17          | 10μF         | C2, C3, C12         | 100nF         |

|---------------------|--------------|---------------------|---------------|

| C5, C6, C7,C15,C16  | 100nF        | C8, C9              | 22pF          |

| C10, C11            | 18pF         | C13                 | 1nF           |

| (optional see note) | •            | C14                 | (not used)    |

| C14                 | 1μF          | D1                  | 1N914         |

| R1                  | 10MΩ         | R2                  | 100k $\Omega$ |

| (optional see note) |              |                     |               |

| X1                  | 11.0592MHz   | X2                  | 32.768kHz     |

|                     | or 12.288MHz | (optional see note) |               |

Resistors ±5%, capacitors and inductors ±20% unless otherwise stated.

Note: The components C10, C11, R1 and X2 are optional, they are not required if the 32.768kHz clock is derived internally from the 11.0592MHz/12.288MHz system clock. See section 1.5.6 for details.

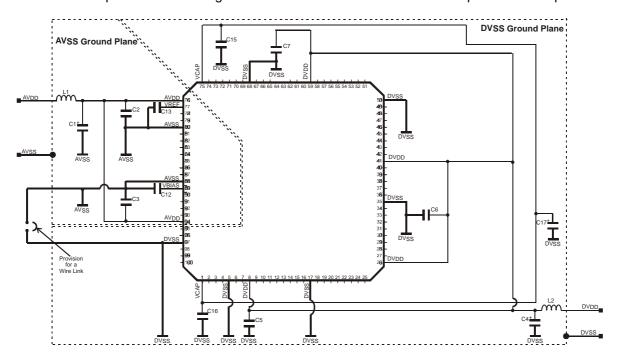

The CMX850 modem and ADC interfaces are capable of detecting and decoding small amplitude signals. To achieve this,  $DV_{DD}$ ,  $AV_{DD}$  and  $V_{BIAS}$  should be decoupled and the receive path protected from extraneous in-band signals. It is recommended that the printed circuit board is laid out with  $AV_{SS}$  and  $DV_{SS}$  ground planes in the CMX850 area, as shown in Figure 2b, with provision to make a link between them close to the CMX850. To provide a low impedance connection to ground, the decoupling capacitors C1-C7, C12, C13 and C15-C17 must be mounted as close to the CMX850 as possible and connected directly to their respective ground plane. The use of surface mounted capacitors is recommended.

$V_{BIAS}$  is used as an internal reference for detecting and generating the various analogue signals. It must be carefully decoupled, to ensure its integrity. Apart from the decoupling capacitor shown (C12), no other loads are allowed. If  $V_{BIAS}$  needs to be used to set external analogue levels, it must be buffered with a high input impedance buffer.

VREF is the internal reference voltage generated for the ADC. For best ADC performance, it is recommended that a 1nF capacitor be placed on this pin and connected to  $AV_{SS}$ . The pin may also be used as a reference voltage externally (see section 1.5.8), however it is recommended that a maximum of  $1\mu A$  is drawn from the pin. If more current is required externally, then a suitable buffer must be used.

The DV<sub>SS</sub> to the Xtal oscillator capacitors C8 – C11 should be of low impedance and preferably be part of the DV<sub>SS</sub> ground plane to ensure reliable start up. The resistor across the 32.768kHz Xtal should be  $10M\Omega$  for best performance. Using a smaller resistor will result in increased power consumption.

Figure 2b Recommended Power Supply Connections and De-coupling

| C1, C4, C17<br>C5, C6, C7, | 10µF<br>100nF        | C2, C3, C12<br>C13 | 100nF<br>1nF         |

|----------------------------|----------------------|--------------------|----------------------|

| C15, C16                   | 100nF                |                    |                      |

| L1                         | 100nH                | L2                 | 100nH                |

|                            | (optional, see note) |                    | (optional, see note) |

Note: The inductors L1 and L2 can be omitted but this may degrade system performance.

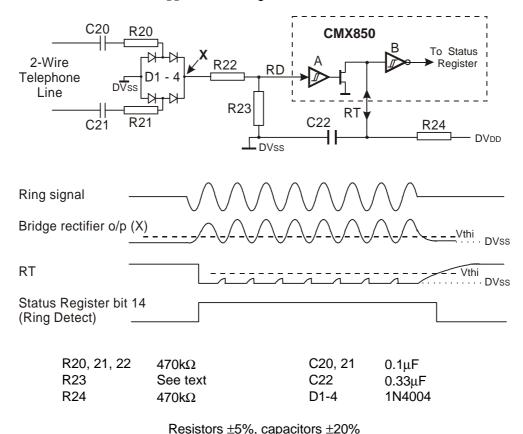

#### 1.4.1 Ring Detector Interface

Figure 3 shows how the Modem may be used to detect the large amplitude ringing signal voltage present on the 2-wire line at the start of an incoming telephone call.

The ring signal is usually applied at the subscriber's exchange as an ac voltage inserted in series with one of the telephone wires and will pass through either C20 and R20 or C21 and R21 to appear at the top end of R22 (point X in Figure 3) in a rectified and attenuated form.

The signal at point X is further attenuated by the potential divider formed by R22 and R23 before being applied to the CMX850 RD input. If the amplitude of the signal appearing at RD is greater than the input threshold (Vthi) of Schmitt trigger 'A' then the N transistor connected to RT will be turned on, pulling the voltage at RT to DV<sub>SS</sub> by discharging the external capacitor C22. The output of the Schmitt trigger 'B' will then go high, setting bit 14 (Ring Detect) of the modem's Status Register 1.

The minimum amplitude ringing signal that is certain to be detected is:

$$(0.7 + Vthi x [R20 + R22 + R23] / R23) x 0.707 Vrms$$

where Vthi is the high-going threshold voltage of the Schmitt trigger A. See Figure 16.

With R20 - R22 all  $470k\Omega$  as Figure 3, then setting R23 to  $68k\Omega$  will guarantee detection of ringing signals of 40Vrms and above for  $DV_{DD}$  over the range 3V to 3.6V.

Figure 3 Ring Signal Detector Interface Circuit

If the time constant of R24 and C22 is large enough then the voltage on RT will remain below the threshold of the 'B' Schmitt trigger for the duration of a ring cycle.

The time for the voltage on RT to charge from DV<sub>SS</sub> towards DV<sub>DD</sub> can be derived from the formula:

$$V_{RT} = DV_{DD} x [1 - exp(-t/(R24 x C22))]$$

As the Schmitt trigger high-going input threshold voltage (Vthi) has a minimum value of  $0.56 \times DV_{DD}$ , then the Schmitt trigger B output will remain high for a time of at least  $0.821 \times R24 \times C22$  following a pulse at RD.

The values of R24 and C22 given in Figure 3 (470k $\Omega$  and 0.33 $\mu$ F) give a minimum RT charge time of 100 msec, which is adequate for ring frequencies of 10Hz or above.

Note that the circuit will also respond to a telephone line voltage reversal. If necessary the  $\mu$ C can distinguish between a Ring signal and a line voltage reversal by measuring the time that bit 14 of the modem's Status Register 1 (Ring Detect) is high.

If the Ring detect function is not used then pin RD should be connected to DVss and RT to DVDD.

#### 1.4.2 Hook Detector Interface

This is identical internally to the Ring Detector interface circuit and similar components could be used externally, with appropriate values, if hook detection is to be performed by detecting a voltage change across the tip and ring lines to the local phone.

#### 1.4.3 RESETN pin

When this pin is taken low, it resets the CMX850, which includes the  $\mu$ C and modem. The reset to the modem performs the same operation as a C-BUS General Reset command. As a consequence the modem will enter the powersaved state. Refer to section 1.6.11.1 (General Reset Command) and 1.6.11.2 (General Control Register, Powerup bit) for further information.

#### 1.4.4 Line Interface

A line interface circuit is needed to provide dc isolation and to terminate the line.

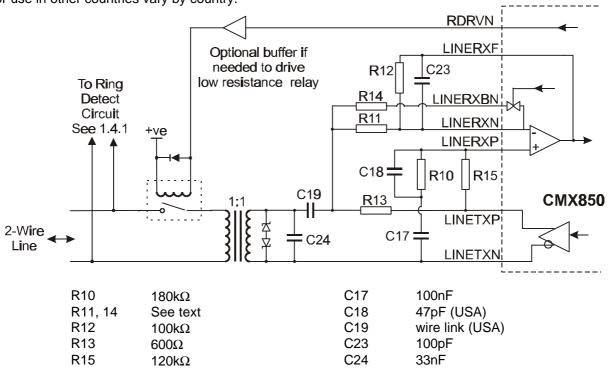

#### 2-Wire Line Interface

Figure 4a shows an interface for use with a USA  $600\Omega$  2-wire line. The complex line termination is provided by R10, R13, C17, C18, C19 and C24, high frequency noise is attenuated by C23 and C24, while R11 and R12 set the receive signal level into the modem. R14 connects in parallel with R11 when enabled in the Analogue Signal Path Register. This is for the purpose of increasing gain, which is necessary to compensate for signal attenuation during on-hook CLI detection. Tx rejection into the Rx is provided by R15. For clarity, not all of the 2-wire line protection circuits have been shown. Components for use in other countries vary by country.

Resistors ±5%, capacitors ±20%

Figure 4a 2-Wire Line Interface Circuit

The transmit line signal level is determined by the voltage swing between the TXP and TXN pins, less 6dB due to the line termination resistor R13, and less the loss in the line coupling transformer.

Allowing for 1dB loss in the transformer, then with the Tx Mode Register set for a Tx Level Control gain of 0dB the nominal transmit line levels will be:

|                                            | $V_{DD} = 3.3V$   |

|--------------------------------------------|-------------------|

| QAM, DPSK and FSK Tx modes (no guard tone) | -9.2dBm           |

| Single tone transmit mode                  | -9.2dBm           |

| DTMF transmit mode                         | -5.2 and -7.2 dBm |

For a line impedance of  $600\Omega$ , 0dBm = 775mVrms. See also section 1.7.1.3.

In the receive direction, the signal detection thresholds within the modem are proportional to  $V_{DD}$  and are affected by the Rx Gain Control gain setting in the Rx Mode Register. The signal level into the modem is affected by the line coupling transformer loss and the values of R11 and R12 of Figure 4a.

Assuming 1dB transformer loss, the Rx Gain Control programmed to 0dB and R12 =  $100k\Omega$ , then for correct operation (see section 1.7.1.3) the value of R11 should be equal to  $500 / V_{DD} k\Omega$ , i.e.  $150k\Omega$  at  $V_{DD} = 3.3V$ .

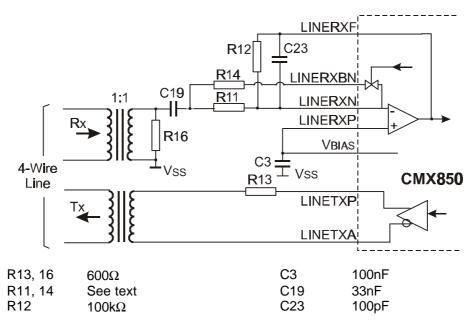

#### 4-Wire Line Interface

Figure 4b shows a simplified interface for use with a  $600\Omega$  4-wire line. The line terminations are provided by R13 and R16, high frequency noise is attenuated by C23 while R11 and R12 set the receive signal level into the modem. R14 connects in parallel with R11 when enabled in the Analogue Signal Path Register. This is for the purpose of increasing gain, which is necessary to compensate for signal attenuation during on-hook CLI detection.

Transmit and receive line level settings and the value of R11 and R14 are as for the 2-wire circuit.

Resistors ±5%, capacitors ±20%

Figure 4b Simplified 4-Wire Line Interface Circuit

#### 1.5 Microcontroller Core

The CMX850 microcontroller core is software and cycle-timing compatible with the industry standard 80C51 and includes standard hardware such as a 256-byte local RAM, timer/counters, serial interface and interrupt controller. The microcontroller architecture is further enhanced by the addition of extra core functionality along with a comprehensive set of on-chip "peripheral" hardware. These are controlled by new registers mapped into the 8051's Special Function Register space. These additional features include:

- Dual data pointers

- 8kbyte on-chip XRAM

- General-purpose ports (up to 35 pins) with explicit direction and open-drain control, and optional pull-up resistors

- External 64kbyte program address space, extendable using bank switching

- Four independently selectable XRAM source/destination areas, including on-chip XRAM and three off-chip areas accessible through separate chip select pins

- Optional "MOVX" wait state for slow external peripherals

- 8 extra interrupts

- Advanced oscillator and power saving controls

- C-BUS controller connected to on-chip DSP modem

- Keyboard encoder (up to 128 keys)

- Dual channel 10-bit ADC with threshold comparators and internal bandgap reference

- Real time clock and alarm

- Watchdog timer

- Dual pulse-width modulators

- Debugger support through the use of a super priority interrupt pin

#### 1.5.1 Special Function Register Memory Map

The CMX850 microcontroller's special function register (SFR) area contains the complete set of standard 8051 SFRs, along with the additional SFRs required to control the CMX850's extra hardware functions.

| -         | ↓ Bit add | Iressable |         |         | Standar | d 80C51 SFRs | are shown in | parentheses |

|-----------|-----------|-----------|---------|---------|---------|--------------|--------------|-------------|

| (Isb<br>) | ' 000'    | ' 001'    | ' 010'  | ' 011'  | ' 100'  | ' 101'       | ' 110'       | ' 111'      |

| \$F8      |           |           | MEMCON  | RTCCON  | TIME0   | TIME1        | TIME2        | TIME3       |

| \$F0      | (B)       |           | WDTCON  | WDTLD   | ALM0    | ALM1         | ALM2         | ALM3        |

| \$E8      |           | CASDET    | CBUSCON | CBUSBUF | KBCON   | KBSTAT       | KBBUF        |             |

| \$E0      | (ACC)     |           | ADCCON1 | ADCCON2 | ADCBUFL | ADCBUFH      | ADCTHRL      | ADCTHRH     |

| \$D8      | P5        | P5DIR     | P5OD    | P5RES   |         | PWMCON       | PWM1         | PWM2        |

| \$D0      | (PSW)     |           |         |         |         |              |              |             |

| \$C8      |           |           |         |         |         |              |              |             |

| \$C0      | P4        | P4DIR     | P4OD    | P4RES   |         |              |              |             |

| \$B8      | (IP)      | IP_1      |         |         |         |              |              |             |

| \$B0      | (P3)      | P3DIR     | P3OD    | P3RES   |         |              |              |             |

| \$A8      | (IE)      | IE_1      | ICON1A  | ICON1B  |         |              |              |             |

| \$A0      | (P2)      |           |         |         |         |              |              |             |

| \$98      | (SCON)    | (SBUF)    |         |         | OSCCON  | SPDCON       | SPXMASK      | PDXMASK     |

| \$90      | (P1)      | P1DIR     | P1OD    | P1RES   | P0DIR   |              |              | TESTCON     |

| \$88      | (TCON)    | (TMOD)    | (TL0)   | (TL1)   | (TH0)   | (TH1)        |              |             |

| \$80      | (P0)      | (SP)      | (DPL)   | (DPH)   | DPL1    | DPH1         | DPS          | (PCON)      |

**Table 1 Special Function Registers**

The CMX850's SFRs are mapped into the local RAM address space between locations \$80 and \$FF, and are accessible by standard 8051 instructions which use direct addressing. SFRs whose address is divisible by 8 are also accessible using bit-addressing instructions. The TESTCON SFR is used for production test only, and should not be written to under any circumstances.

#### 1.5.2 Dual Data Pointer

The standard 8051 has a single 16-bit data pointer DPTR which can be used to address XRAM or program memory, using MOVX and MOVC instructions respectively. The DPTR register is also mapped into two 8-bit SFRs, DPL and DPH. The CMX850 has an additional 16-bit data pointer DPTR1 that can significantly speed up block moves by allowing 16-bit source and destination pointers to be maintained simultaneously. DPTR1 is mapped into SFR registers DPL1 and DPH1. A separate SFR register DPS is used to select between DPTR and DPTR1: all instructions that use the data pointer directly (INC DPTR; MOV DPTR,#data16; MOVC A,@A+DPTR; MOVX A,@DPTR; MOVX @DPTR,A) will be directed to whichever data pointer is currently selected by DPS. Swapping between the two data pointers can be easily achieved by using the increment instruction, INC, to toggle DPS bit 0.

#### 1.5.2.1 DPTR1 Registers (DPL1/DPH1)

#### **DPL1: SFR Address \$84**

All bits cleared to 0 on reset.

| 7 | 6              | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---|----------------|---|---|---|---|---|---|--|

|   | DPTR1 Low Byte |   |   |   |   |   |   |  |

# DPH1: SFR Address \$85

All bits cleared to 0 on reset.

Bit:

| 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|---|---|---|---|---|---|---|

| DPTR1 High Byte |   |   |   |   |   |   |   |

#### 1.5.2.2 Data Pointer Select Register (DPS)

#### **DPS: SFR Address \$86**

Bit b0 is cleared to 0 on reset. Other bits are unused, and are 0.

Bit:

| 7 | 6                         | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---------------------------|---|---|---|---|---|---|

|   | Unused (always read as 0) |   |   |   |   |   |   |

DPS Register b0: Set to 0 to select DPTR, set to 1 to select DPTR1

#### 1.5.3 I/O Ports

The 8051  $\mu$ C port structure within the CMX850 has been enhanced by the addition of two extra byte-wide ports, port 4 and port 5. The ports have also been enhanced for low power operation by the addition of explicit port direction control registers, which means that port input pins consume no dc current when driven with a logic 0 (standard 8051 port inputs consume several tens of microamps of dc current per pin when driven with a logic 0). To further enhance flexibility, all of the port 1, 3, 4 and 5 pins can be individually configured as open-drain output drivers, and with optional pull-up resistors.

The port configuration within the CMX850 is shown in Table 2.

| Port   |                                                                                                                                                                                                                                                                                                                                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Port 0 | MUXAD<br>3) are ur<br>onto the                                                                                                                                                                                                                                                                                                                  | When the CMX850 is configured with a multiplexed external memory interface (pin MUXAD = 1), port 0 bits 2-0 are available as I/O pins. The remaining port 0 bits (7-3) are unused. Note that the port 0 pins do <b>not</b> have memory address/data driven onto them during an external memory access, as would happen on a standard 8051: the CMX850 external memory interface is completely separate from the port 0 circuit. |  |  |  |  |  |

| Port 1 | keyboar                                                                                                                                                                                                                                                                                                                                         | Port 1 bits 7-0 are available as I/O pins. They are automatically configured as keyboard row input pins with pull-up resistors when the keyboard encoder is enabled.                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Port 2 | Port 2 bits 7-0 are not available directly as I/O pins, but the contents of the byte-wide port 2 output latch is used during MOVX A,@Ri and MOVX @Ri,A instructions to form the upper eight address bits on pins A15-8. This is done to maintain compatibility with the standard 8051 instruction set.                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Port 3 | Port 3 bits 7-0 are available as I/O pins. Each pin also has an alternative output function, as shown below. Pins P3.6 and P3.7 are automatically configured as an output when the associated PWM block is enabled. The other alternative pin functions require the correct pin direction to be explicitly configured using the P3DIR register. |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|        | Port                                                                                                                                                                                                                                                                                                                                            | Alternative function                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|        | P3.0                                                                                                                                                                                                                                                                                                                                            | RXD (Serial port receive data)                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|        | P3.1                                                                                                                                                                                                                                                                                                                                            | TXD (Serial port transmit data)                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|        | P3.2                                                                                                                                                                                                                                                                                                                                            | Int0 (External interrupt 0)                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|        | P3.3                                                                                                                                                                                                                                                                                                                                            | Int1 (External interrupt 1)                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|        | P3.4                                                                                                                                                                                                                                                                                                                                            | T0 (Timer/counter 0 external input)                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|        | P3.5                                                                                                                                                                                                                                                                                                                                            | T1 (Timer/counter 1 external input)                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|        | P3.6                                                                                                                                                                                                                                                                                                                                            | PWM1 (Pulse-width modulator 1 output)                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|        | P3.7                                                                                                                                                                                                                                                                                                                                            | PWM2 (Pulse-width modulator 2 output)                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Port 4 | Port 4 bits 7-0 are available as I/O pins. Between one and eight port 4 pins are automatically configured as open-drain column drivers when the keyboard encode is enabled, depending on the contents of the KBCON register.                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Port 5 | configur<br>automat                                                                                                                                                                                                                                                                                                                             | its 7-0 are available as I/O pins (bits 7-5 are only available if the CMX850 is ed with a multiplexed external memory interface). Up to eight port 5 pins are ically configured as open-drain column drivers when the keyboard encoder ed, depending on the contents of the KBCON register.                                                                                                                                     |  |  |  |  |  |

Table 2 I/O Port Function

#### 1.5.3.1 Port Data Registers (P0-P5)

The  $8051~\mu C$  retains the standard port registers (P0, P1, P2, P3) as well as having two new ports, P4 and P5. Writing to these port SFRs loads the associated output data register, which gets driven onto those device pins that are configured as outputs. Reading from a port SFR will either read the contents of the port output data register, or read directly from the port pins, depending on which instruction is used. The instructions that read the data register rather than the pins are those that perform a read-modify-write operation on a port or a port bit (this is explained in more detail in any standard 8051~documentation).

#### P4: SFR Address \$C0 P5: SFR Address \$D8

All bits set to 1 on reset. These registers are bit addressable.

#### 1.5.3.2 Port Direction Registers (P0DIR-P5DIR)

Ports 0, 1, 3, 4 and 5 each have a direction control register that allows individual port pins to be configured either as an input or an output. The bits should be cleared to a 0 for an input, or set to 1 for an output.

P0DIR: SFR Address \$94 P1DIR: SFR Address \$91 P3DIR: SFR Address \$B1 P4DIR: SFR Address \$C1 P5DIR: SFR Address \$D9 All bits cleared to 0 on reset.

#### 1.5.3.3 Port Open-Drain Registers (P10D-P50D)

Ports 1, 3, 4 and 5 each have an open-drain control register which allows individual port outputs to be configured either with a pull-up/pull-down driver or with an open-drain driver. The bits should be cleared to a 0 for an active pull-up/pull-down driver, or set to 1 for an open-drain driver. Note that if a pin is configured as an input by the port direction control register, then the pin driver will go into a high impedance state irrespective of the contents of the associated open-drain control register bit.

P10D: SFR Address \$92 P30D: SFR Address \$B2 P40D: SFR Address \$C2 P50D: SFR Address \$DA All bits cleared to 0 on reset.

#### 1.5.3.4 Port Res Pull-up Registers (P1RES-P5RES)

Ports 1, 3, 4 and 5 each have a resistor pull-up control register which allows individual port pins to be configured either with or without a pull-up resistor. The bits should be cleared to a 0 if no resistor is required, or set to 1 to connect a  $50k\Omega$  (nominal) resistor between the pin and  $DV_{DD}$ . A port pin should not be configured with a pull-up resistor at the same time as being configured as an output with active pull-up/pull-down drivers, otherwise power will be needlessly wasted when driving out a logic 0.

P1RES: SFR Address \$93 P3RES: SFR Address \$B3 P4RES: SFR Address \$C3 P5RES: SFR Address \$DB All bits cleared to 0 on reset.

| Bit: | 7 | 6 | 5           | 4            | 3             | 2           | 1 | 0 |

|------|---|---|-------------|--------------|---------------|-------------|---|---|

|      |   |   | Bits 7-0 of | the resistor | pull-up contr | ol register |   |   |

CMX850 Communications Controller

#### **Memory Interface** 1.5.4

In addition to 256 bytes of scratchpad RAM, the CMX850 has 8kbytes of on-chip extension RAM (XRAM) and three separate 64k areas for off-chip memory and peripherals, accessible without glue logic via chip select pins CSN1, CSN2 and CSN3. External memory size can easily be increased to several megabytes by using a code-banking compiler along with a number of CMX850 port output pins as bank select bits.

The CSN1 pin is normally used during program instruction fetches, although there is an option to replace the bottom 8kbytes of off-chip program ROM with the on-chip XRAM, allowing short sections of temporary program code to be executed from the on-chip XRAM. This could be used, for instance, when the CMX850 is re-programming external flash memory.

MOVX read and write instructions can be independently directed to either the on-chip XRAM or any of the three off-chip memory areas, including the program ROM area (this allows the CMX850 to re-program external flash memory, if necessary). Combined with the dual data pointer architecture of the CMX850 microcontroller, this allows rapid block moves between any of the memory areas. The MOVX read and write instructions can also be independently stretched to allow access to slow memory or peripherals, without any external circuitry being required.

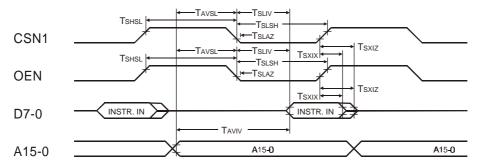

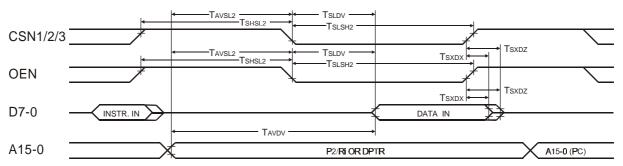

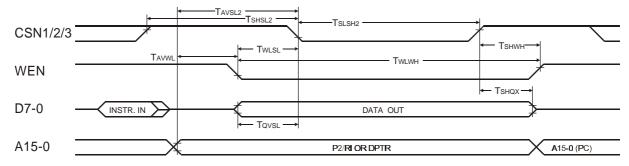

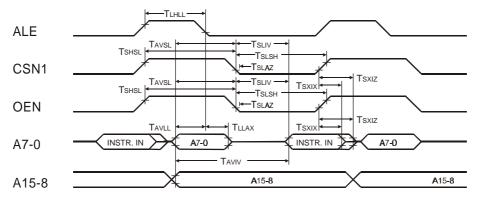

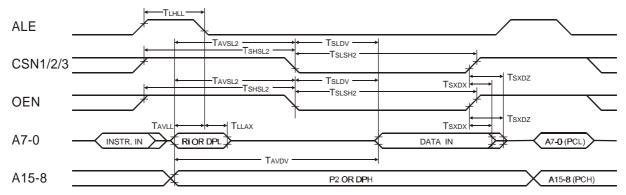

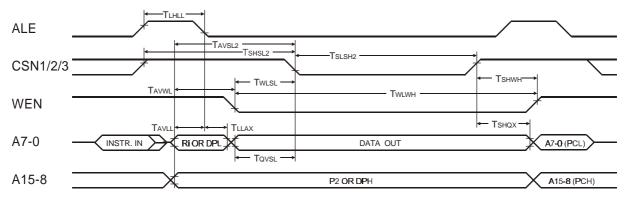

All off-chip accesses use the same 16-bit address bus and 8-bit data bus, along with output enable (OEN) and write enable (WEN) control pins. The address and data pins can be configured to be non-multiplexed by tying input pin MUXAD low (address output on pins A15-0, bi-directional data uses pins D7-0), or the data can be multiplexed with the lower eight address pins (A7-0) by tying input pin MUXAD high.

If configured with a multiplexed address/data bus, an external address latch ('373 or '573 type) is required. Pin D7 becomes an address latch enable (ALE), and pins D6-0 are reassigned as an extra interrupt pin and general-purpose port bits. During the time when ALE is high, the least significant byte (LSB) of the 16-bit memory address is driven onto pins A7-0. When ALE goes low, the LSB of the memory address gets held in the external address latch, and the A7-0 pins change to a bi-directional data

In order to minimise power consumption and EMI, the CMX850 only performs program memory reads when necessary, rather than doing continuous reads and discarding the unnecessary ones as on a standard 8051. This typically reduces the number of program read operations by 30% - 40%. Furthermore, when using a multiplexed address/data bus, unnecessary ALE pulses are inhibited.

The CMX850 data pins (D7-0 for non-multiplexed, or A7-0 for multiplexed) can be configured with weak bus-holding devices to prevent voltage drift on the pins during long periods of inactivity (e.g. when in idle/power down mode, or executing programs from entirely within on-chip XRAM). This can help reduce unnecessary current consumption in devices connected to the data bus.

The memory interface is configured using the MEMCON SFR.

## 1.5.4.1 Memory Control Register (MEMCON)

#### MEMCON: SFR Address \$FA All bits cleared to 0 on reset.

| $\overline{}$ | ٠.  |

|---------------|-----|

|               | 1+• |

| $\mathbf{D}$  | н.  |

| 7                  | 6                  | 5                        | 4 | 3                 | 2                       | 1       | 0         |

|--------------------|--------------------|--------------------------|---|-------------------|-------------------------|---------|-----------|

| Enable<br>bus-hold | Internal<br>progam | MOVX<br>write<br>stretch | _ | X write<br>nation | MOVX<br>read<br>stretch | MOVX re | ad source |

#### MEMCON Register b7: Enable bus-hold

| b7 = 1 | Enable data pin bus-holding devices  |

|--------|--------------------------------------|

| b7= 0  | Disable data pin bus-holding devices |

#### **MEMCON Register b6: Internal program**

| b7 = 1 | On-chip XRAM mapped into bottom 8Kbytes of program memory |

|--------|-----------------------------------------------------------|

| b6 = 0 | Program memory is entirely off-chip                       |

Allows temporary program code to be executed from on-chip XRAM. Care must be taken not to change this register bit while program execution is taking place in the bottom 8kbytes of memory. Any interrupt service routine vectors being used (these begin at locations \$03 to \$6B) should be duplicated in XRAM before setting this bit; alternatively the interrupts should be disabled.

#### **MEMCON** Register b5: MOVX write stretch

| b5 = 1 | MOVX write operations are stretched by one machine cycle (12 xtal cycles) |

|--------|---------------------------------------------------------------------------|

| b4 = 0 | MOVX write operations are not stretched                                   |

#### MEMCON Register b4-3: MOVX write destination

| b4 | b3 |                                                    |

|----|----|----------------------------------------------------|

| 0  | 0  | MOVX write destination is on-chip XRAM             |

| 0  | 1  | MOVX write destination is off-chip, using pin CSN1 |

| 1  | 0  | MOVX write destination is off-chip, using pin CSN2 |

| 1  | 1  | MOVX write destination is off-chip, using pin CSN3 |

#### MEMCON Register b2: MOVX read stretch

| b2 = 1 | MOVX read operations are stretched by one machine cycle (12 xtal cycles) |

|--------|--------------------------------------------------------------------------|

| b2 = 0 | MOVX read operations are not stretched                                   |

#### MEMCON Register b1-0: MOVX read source

| b1 | b0 |                                              |

|----|----|----------------------------------------------|

| 0  | 0  | MOVX read source is on-chip XRAM             |

| 0  | 1  | MOVX read source is off-chip, using pin CSN1 |

| 1  | 0  | MOVX read source is off-chip, using pin CSN2 |

| 1  | 1  | MOVX read source is off-chip, using pin CSN3 |

#### 1.5.5 Interrupts

The 8051 interrupt logic has been extended, so that the original five interrupt sources (Int0, Timer0, Int1, Timer1, Serial) have been supplemented by eight new interrupt sources (Int2, Int3, Int4, Int5, Int6, Int7, Int8 and Int9). With the exception of Int9, these new interrupts are connected to the 8051  $\mu$ C's on-chip peripheral hardware logic as shown in Table 3, so that the hardware can be interrupt driven. Int9 is a super priority interrupt, which can interrupt both low and high priority interrupts, and is available on a device pin when the CMX850 is configured with a multiplexed memory address/data bus. This pin may be driven by an external ROM emulator to assist with program debugging.

| Interrupt signal | Hardware source                | Vector address | Priority within level |

|------------------|--------------------------------|----------------|-----------------------|

| Int2             | CAS Detect                     | \$33           | 1 (Highest)           |

| (Int0)           | Interrupt 0 input pin (P3.2)   | \$03           | 2                     |

| Int3             | DSP Modem                      | \$3B           | 3                     |

| (Timer0)         | 8051 timer 0                   | \$0B           | 4                     |

| Int4             | Keyboard encoder               | \$43           | 5                     |

| (Int1)           | Interrupt 1 input pin (P3.3)   | \$13           | 6                     |

| Int5             | A/D converter                  | \$4B           | 7                     |

| (Timer1)         | 8051 timer 1                   | \$1B           | 8                     |

| Int6             | RTC time interrupt             | \$53           | 9                     |

| (Serial)         | RI or TI from 8051 serial port | \$23           | 10                    |

| Int7             | RTC alarm interrupt            | \$5B           | 11                    |

| Int8             | Watchdog timeout               | \$63           | 12 (Lowest)           |

| Int9             | Interrupt 9 input pin (D6)*    | \$6B           | N/A (super priority)  |

<sup>\*</sup> Note: D6 is only available as an interrupt with a multiplexed memory interface (pin MUXAD = 1)

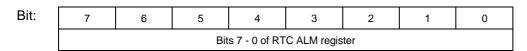

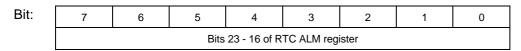

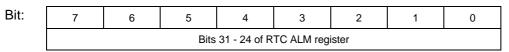

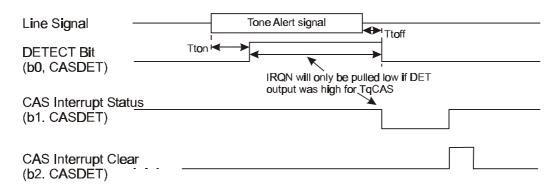

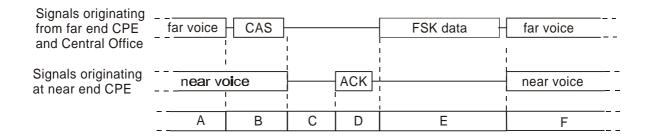

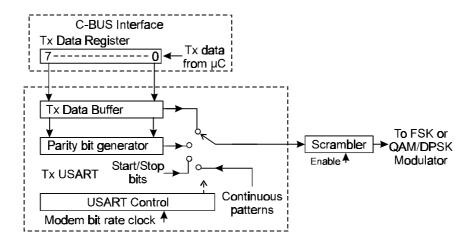

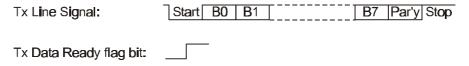

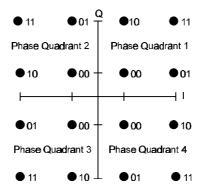

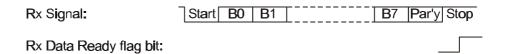

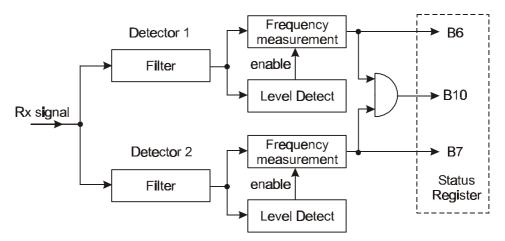

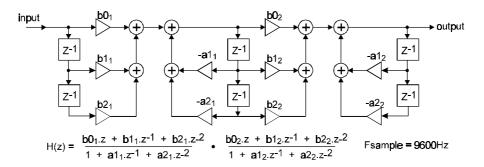

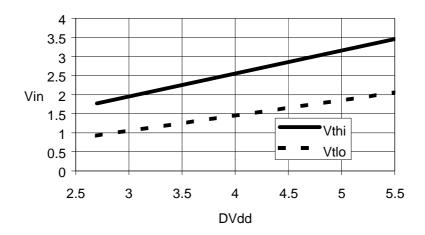

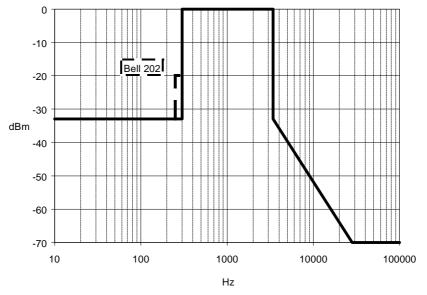

#### Table 3 Interrupt structure