# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

- Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but

there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire

or property damage.

- Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation

product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any

other rights, belonging to Renesas Technology Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors.

- Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# Hitachi 4-Bit Single-Chip Microcomputers

# HMCS43XX Family

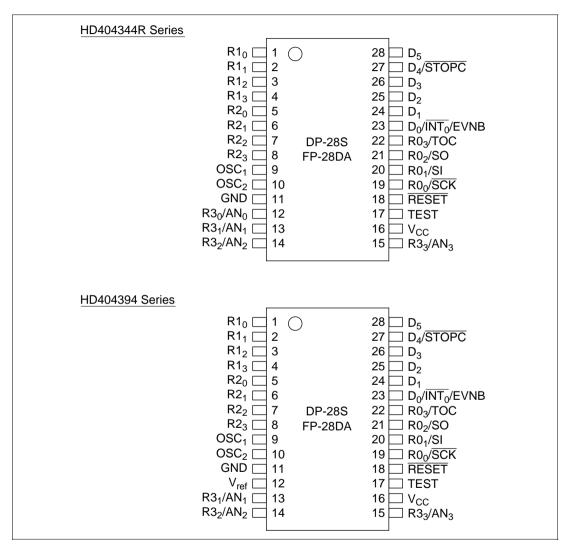

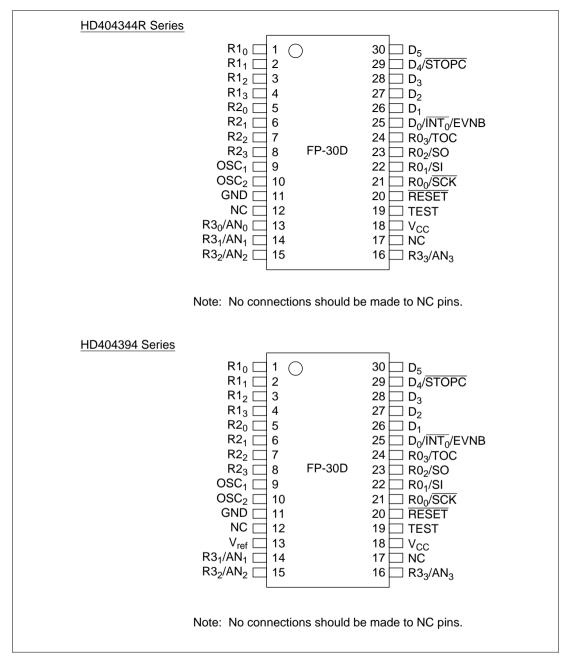

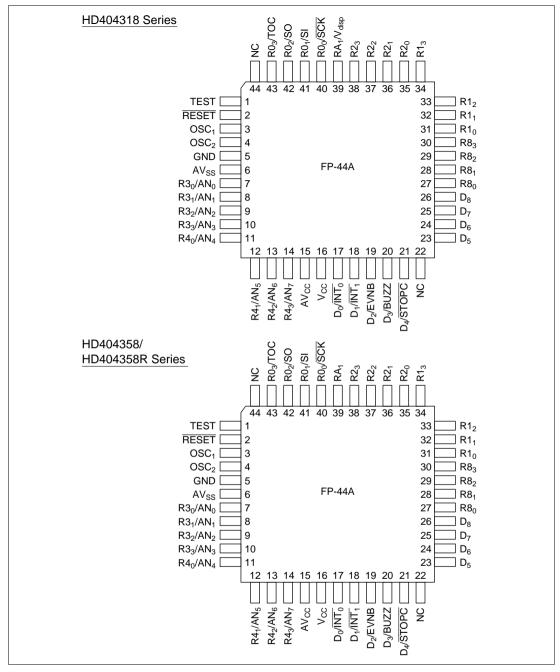

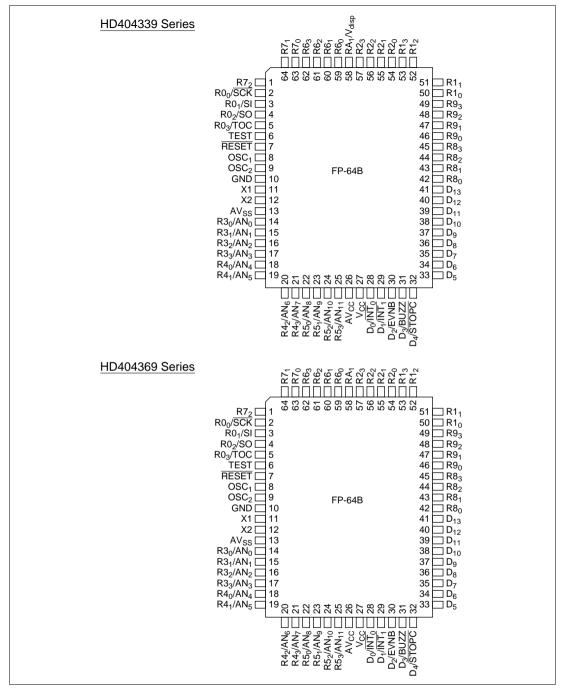

HD404344R Series, HD404394 Series, HD404318 Series, HD404358 Series, HD404358 Series, HD404369 Series, HD404369 Series

Hardware Manual

ADE-602-081B Rev.3.0 3/5/03 Hitachi, Ltd.

#### **Cautions**

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party's

rights, including intellectual property rights, in connection with use of the information

contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# List of Items Revised or Added for This Version

| Page | Item                                                                 | Description                                                      |

|------|----------------------------------------------------------------------|------------------------------------------------------------------|

| _    | Timer Function Overview                                              | Prescaler W column amended                                       |

| 405  | 18.2.1 Timer Mode Register B1 (TMB1:\$009)                           | Note amended                                                     |

| 418  | 18.4 Interrupts                                                      | Series name amended                                              |

| 560  | Table 25-21 Absolute Maximum Ratings (HD404358 and HD404358R Series) | Pin voltage HD404358 Series<br>Rated Value amended               |

| 566  | Table 25-25 AC Characteristics (HD404358 and HD404358R Series)       | Oscillator stabilization period (crystal oscillator) Notes added |

| 633  | B.2 I/O Registers (2)<br>\$030—Data Control Register R0 DCR0         | Series name amended                                              |

| 636  | B.2 I/O Registers (2)<br>\$038—Data Control Register R8 DCR8         | Series name amended                                              |

### **Preface**

#### Introduction

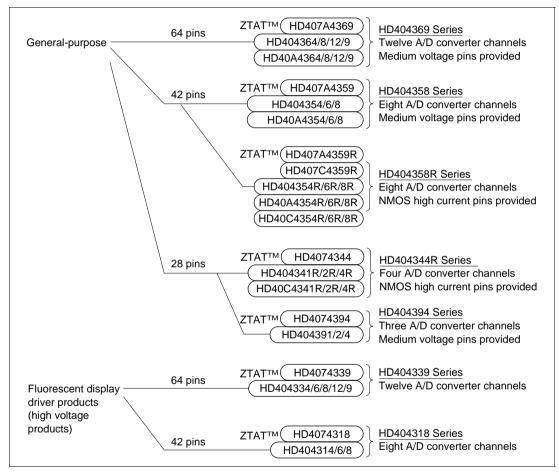

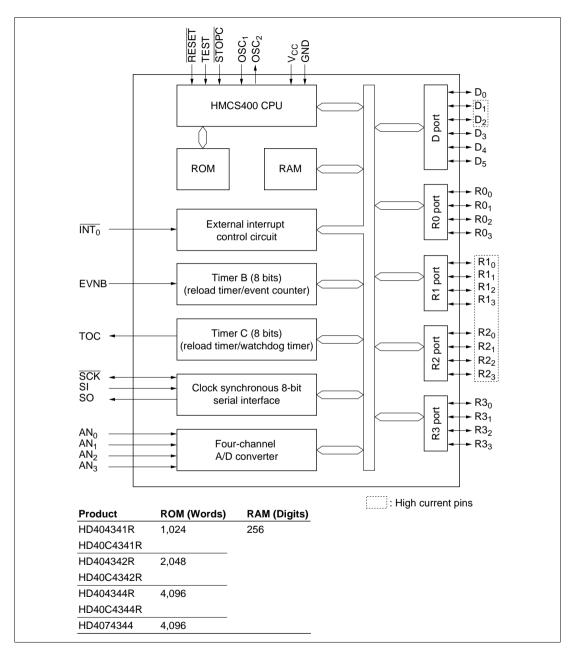

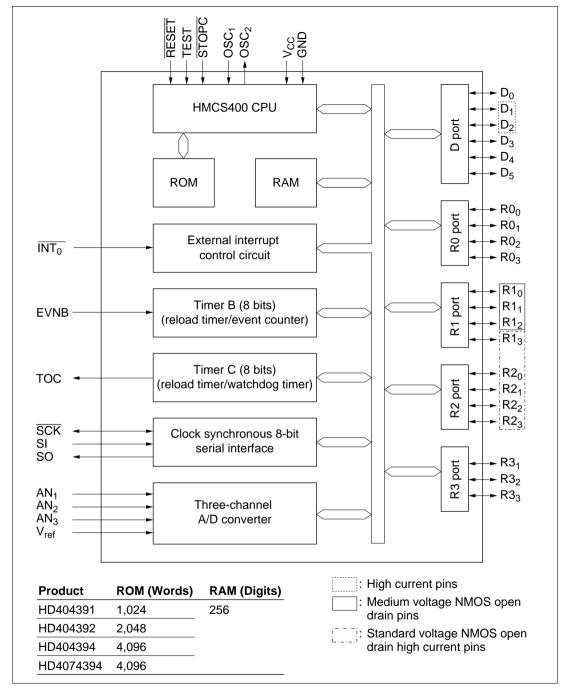

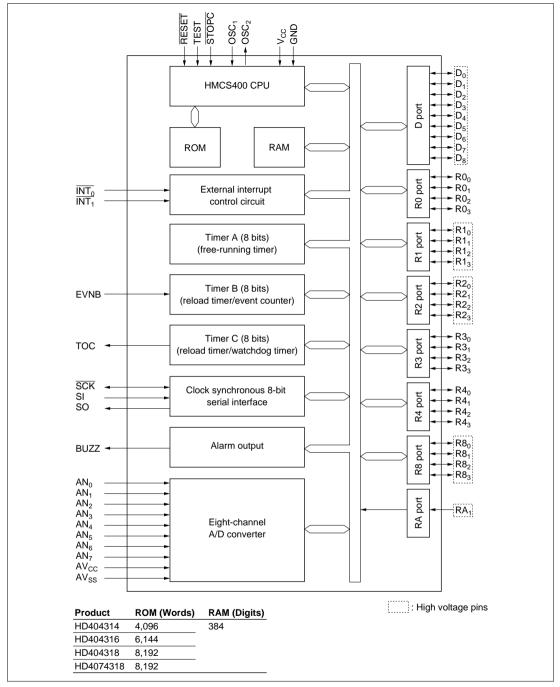

The HMCS43XX Family of 4-bit microcomputers are built around the HMCS400 CPU core, which has a powerful architecture designed for efficient programming. All of these microcomputers include standard on-chip peripheral functions, including a multiple input channel A/D converter, a serial interface, and multi-function timers.

The peripheral functions are developed individually as modules, and connected using a standard interface.

This manual describes six product series in the HMCS43XX Family: the HD404344R, HD404394, HD404318, HD404358, HD404358R, HD404339, and HD404369 series. The products in these series form a fine-grained product line in which products are differentiated by their memory capacities, medium and high voltage pins, high current pins, low power modes, normal vs. high-speed versions, and other aspects. This allows an appropriate microcomputer to be selected for a wide range of applications.

All members of the HMCS43XX Family are available in both ROM and PROM (ZTAT<sup>TM</sup>) versions. PROM versions can be programmed freely by the user with a general purpose PROM writer.

Note: ZTAT<sup>TM</sup> is a registered trademark of Hitachi, Ltd.

# **Manual Layout**

The microcomputers in the HMCS43XX family differ in their memory capacities and peripheral functions. This table provides an overview of the differences between these products as they relate to the structure of this manual. Use this table to determine which sections are relevant to the product(s) of interest.

| Organizati  | on                     |                                                                   | HD404344R<br>Series | HD404394<br>Series | HD404318<br>Series | HD404358/<br>HD404358R<br>Series | HD404339<br>Series | HD404369<br>Series |

|-------------|------------------------|-------------------------------------------------------------------|---------------------|--------------------|--------------------|----------------------------------|--------------------|--------------------|

| Section 1:  | Overview               | Provides a brief overview of the features of the HMCS43XX Family. | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 2:  | Memory                 | These sections describe                                           | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 3:  | CPU                    | the HMCS400 CPU and its internal states.                          | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 4:  | Exception<br>Handling  | no mornar diatos.                                                 | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 5:  | Low Power<br>Modes     |                                                                   | •                   | •                  | •                  | •                                | _                  | _                  |

| Section 6:  | Low Power<br>Modes     |                                                                   | _                   | _                  | _                  | _                                | •                  | •                  |

| Section 7:  | I/O Ports              | These sections describe                                           | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 8:  | I/O Ports              | the peripheral functions used in the HMCS43XX                     | _                   | •                  | _                  | _                                | _                  | _                  |

| Section 9:  | I/O Ports              | Family. Note that the                                             | _                   | _                  | •                  | _                                | _                  | _                  |

| Section 10: | I/O Ports              | peripheral functions actually present differ                      | _                   | _                  | _                  | •                                | _                  | _                  |

| Section 11: | I/O Ports              | between product series.                                           | _                   | _                  | _                  | _                                | •                  | _                  |

| Section 12: | I/O Ports              |                                                                   | _                   | _                  | _                  | _                                | _                  | •                  |

| Section 13: | Oscillator<br>Circuits |                                                                   | •                   | •                  | •                  | •                                | _                  | _                  |

| Section 14: | Oscillator<br>Circuits |                                                                   | _                   | _                  | _                  | _                                | •                  | •                  |

| Section 15: | A/D<br>converter       |                                                                   | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 16: | Prescaler              |                                                                   | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 17: | Timer A                |                                                                   | _                   | _                  | •                  | •                                | •                  | •                  |

| Section 18: | Timer B                |                                                                   | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 19: | Timer C                |                                                                   | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 20: | Serial<br>Interface    |                                                                   | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 21: | Alarm Output           |                                                                   | _                   | _                  | •                  | •                                | •                  | •                  |

| Section 22: | ROM                    |                                                                   | •                   | •                  | •                  | •                                | •                  | •                  |

| Section 23: | RAM                    |                                                                   | •                   | •                  | •                  | •                                | •                  | •                  |

| Organization                                                                                                                                            | HD404344F<br>Series | R HD404394<br>Series | HD404318<br>Series | HD404358R<br>Series | HD404339<br>Series | HD404369<br>Series |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|--------------------|---------------------|--------------------|--------------------|

| Section 24: Application Examples  Describes the use of A/D converter and tir B. Refer to this section when developing sof for any of these productions. | ner<br>on<br>tware  | •                    | •                  | •                   | •                  | •                  |

| Section 25: Electrical Characteristics                                                                                                                  | •                   | •                    | •                  | •                   | •                  | •                  |

| Appendices                                                                                                                                              | •                   | •                    | •                  | •                   | •                  | •                  |

HD4042E0/

#### Note on How to Use this Manual

Either <series name(s)> or <All Products> is printed at the top of each page in this manual to indicate that the page refers to one or more specific series or to all products, respectively. Since the peripheral functions actually present differ between products, care is required when reading this manual. Differences between products are specified in notes and by shading.

This manual describes seven product series, the HD404344R, HD404394, HD404318, HD404358, HD404358R, HD404339, and HD404369 series. To use this manual as the manual for a particular product be sure to read both the chapters that pertain to all products as well as the chapters that are related to the product being used.

# **Function Overview**

| Item                        |                      | HD404344R<br>Series                      | HD404394<br>Series                       | HD404318<br>Series                         | HD404358<br>Series                                 | HD404358R<br>Series                      | HD404339<br>Series                         | HD404369<br>Series                       |

|-----------------------------|----------------------|------------------------------------------|------------------------------------------|--------------------------------------------|----------------------------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|

| ROM                         | Capacity<br>(words)  | Mask ROM<br>1/2/4 k<br>ZTAT™<br>4 k      | Mask ROM<br>1/2/4 k<br>ZTAT™<br>4 k      | Mask ROM<br>4/6/8 k<br>ZTAT™<br>8 k        | Mask ROM<br>4/6/8 k<br>ZTAT™<br>16 k               | Mask ROM<br>4/6/8 k<br>ZTAT™<br>16 k     | Mask ROM<br>4/6/8/12/16 k<br>ZTAT™<br>16 k | Mask ROM<br>4/8/12/16 k<br>ZTAT™<br>16 k |

| RAM                         | Capacity<br>(digits) | 256                                      | 256                                      | 384                                        | 384<br>(Mask ROM)/<br>512<br>(ZTAT <sup>TM</sup> ) | 512                                      | 512                                        | 512                                      |

| I/O                         | Pins                 | 22                                       | 21                                       | 34                                         | 34                                                 | 34                                       | 54                                         | 54                                       |

|                             | Medium voltage pins  | _                                        | 3                                        | _                                          | 4                                                  | _                                        | _                                          | 8                                        |

|                             | High voltage pins    | _                                        | _                                        | 22<br>(of which one<br>is input-only)      | _                                                  | _                                        | 31<br>(of which one<br>is input-only)      | _                                        |

|                             |                      | 10                                       | _                                        | _                                          | _                                                  | 20                                       | _                                          | _                                        |

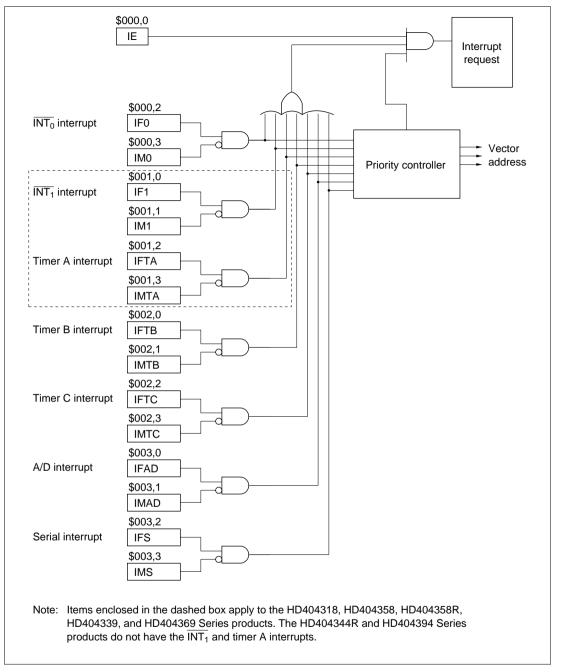

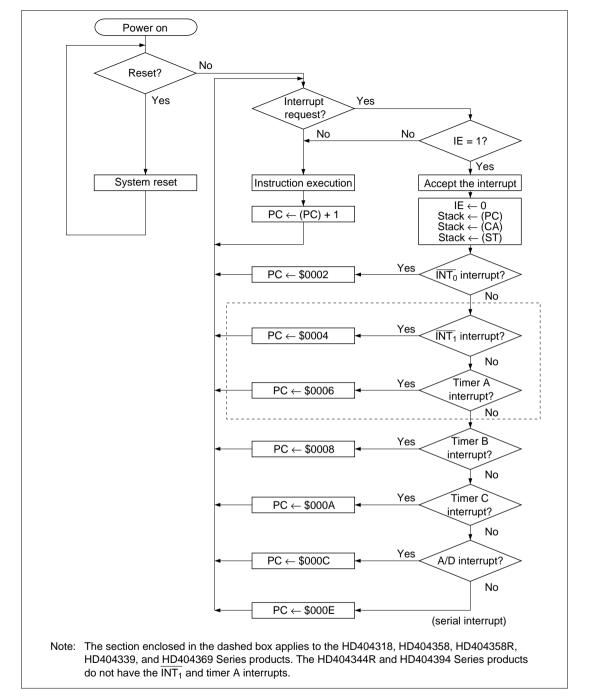

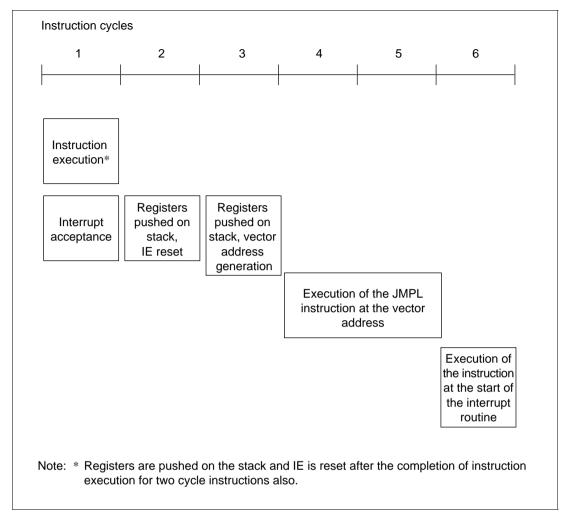

| Interrupts                  | Priority High        | ĪNT <sub>0</sub>                         | ĪNT <sub>0</sub>                         | ĪNT <sub>0</sub>                           | ĪNT <sub>0</sub>                                   | ĪNT <sub>0</sub>                         | ĪNT <sub>0</sub>                           | ĪNT <sub>0</sub>                         |

|                             |                      | _                                        | _                                        | ĪNT <sub>1</sub>                           | ĪNT <sub>1</sub>                                   | ĪNT <sub>1</sub>                         | ĪNT <sub>1</sub>                           | ĪNT <sub>1</sub>                         |

|                             |                      | _                                        | _                                        | Timer A                                    | Timer A                                            | Timer A                                  | Timer A                                    | Timer A                                  |

|                             |                      | Timer B                                  | Timer B                                  | Timer B                                    | Timer B                                            | Timer B                                  | Timer B                                    | Timer B                                  |

| Interrupts Serial interface |                      | Timer C                                  | Timer C                                  | Timer C                                    | Timer C                                            | Timer C                                  | Timer C                                    | Timer C                                  |

|                             | ₩                    | A/D                                      | A/D                                      | A/D                                        | A/D                                                | A/D                                      | A/D                                        | A/D                                      |

|                             | Low                  | Serial                                   | Serial                                   | Serial                                     | Serial                                             | Serial                                   | Serial                                     | Serial                                   |

| Serial                      | Pins                 | 1                                        | 1                                        | 1                                          | 1                                                  | 1                                        | 1                                          | 1                                        |

|                             | Clock<br>selection   | Prescaler<br>output divided<br>by 2 or 4 | Prescaler<br>output divided<br>by 2 or 4 | Prescaler<br>l output divided<br>by 2 or 4 | Prescaler<br>output divided<br>by 2 or 4           | Prescaler<br>output divided<br>by 2 or 4 | Prescaler<br>output divided<br>by 2 or 4   | Prescaler<br>output divided<br>by 2 or 4 |

|                             | Idle control         | Yes                                      | Yes                                      | Yes                                        | Yes                                                | Yes                                      | Yes                                        | Yes                                      |

|                             | Start instruction    | STS instruction                          | STS instruction                          | STS instruction                            | STS instruction                                    | STS instruction                          | STS instruction                            | STS instruction                          |

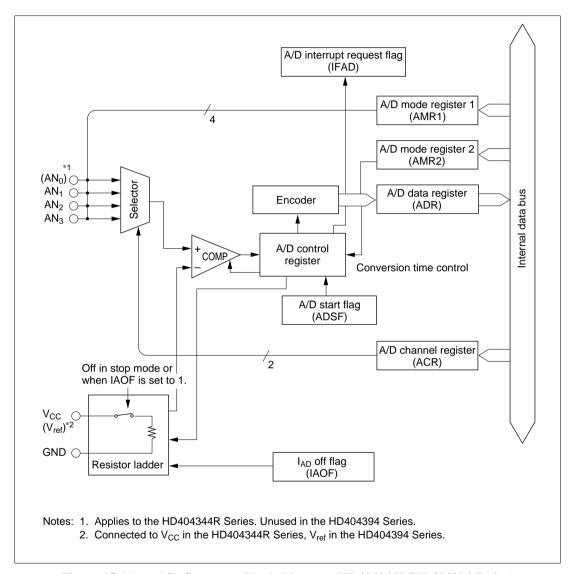

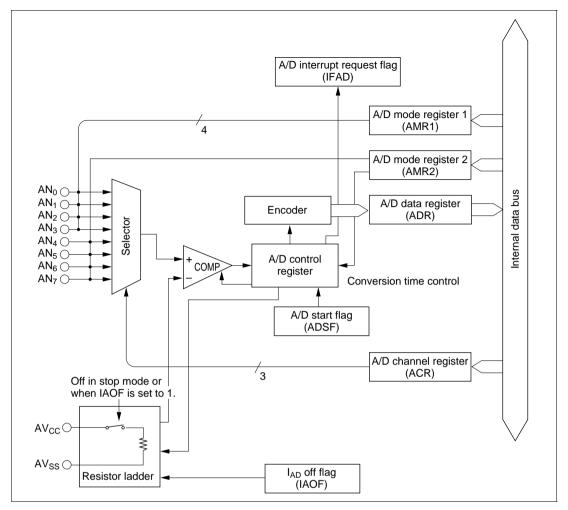

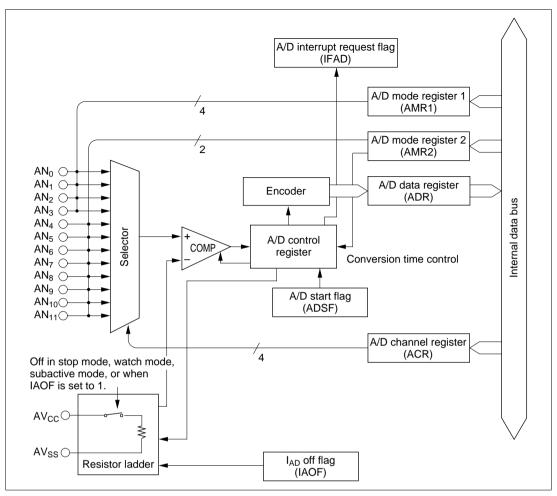

| A/D                         | Channels             | 4                                        | 3                                        | 8                                          | 8                                                  | 8                                        | 12                                         | 12                                       |

| A/D<br>converter            | I <sub>AD</sub> off  | Yes                                      | Yes                                      | Yes                                        | Yes                                                | Yes                                      | Yes                                        | Yes                                      |

|                             | V <sub>ref</sub> pin | _                                        | Built-in                                 | _                                          | _                                                  | _                                        | _                                          | _                                        |

Note: \* Under development

| Item                                             |                       | HD404344R<br>Series                                     | HD404394<br>Series   | HD404318<br>Series               | HD404358<br>Series                                                                     | HD404358R<br>Series                                                                                                          | HD404339<br>Series                    | HD404369<br>Series                                                                     |

|--------------------------------------------------|-----------------------|---------------------------------------------------------|----------------------|----------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------|

| Alarm out                                        | out                   | _                                                       | _                    | On-chip                          | On-chip                                                                                | On-chip                                                                                                                      | On-chip                               | On-chip                                                                                |

| System<br>clock<br>oscillator                    | Oscillator            | Ceramic,<br>external,<br>CR                             | Ceramic,<br>external | Crystal,<br>ceramic,<br>external | Crystal,<br>ceramic,<br>external                                                       | Crystal,<br>ceramic, CR,<br>external                                                                                         | Crystal,<br>ceramic,<br>external      | Crystal,<br>ceramic,<br>external                                                       |

|                                                  | Frequency             | 0.4 to<br>4.5 MHz<br>1.0 to<br>3.5 MHz<br>(CR versions) | 0.4 to<br>4.5 MHz    | 0.4 to<br>4.5 MHz                | 0.4 to<br>5.0 MHz<br>(5 MHz<br>versions)<br>0.4 to<br>8.5 MHz<br>(8.5 MHz<br>versions) | 0.4 to<br>5.0 MHz<br>(5 MHz<br>versions)<br>0.4 to<br>8.5 MHz<br>(8.5 MHz<br>versions)<br>1.0 to<br>3.5 MHz<br>(CR versions) | 0.4 to<br>4.5 MHz                     | 0.4 to<br>5.0 MHz<br>(5 MHz<br>versions)<br>0.4 to<br>8.5 MHz<br>(8.5 MHz<br>versions) |

|                                                  | Divisor               | 4                                                       | 4                    | 4                                | 4                                                                                      | 4                                                                                                                            | 4/8/16/32<br>(software<br>selectable) | 4/8/16/32<br>(software<br>selectable)                                                  |

| Sub-                                             | Frequency             | _                                                       | _                    | _                                | _                                                                                      | _                                                                                                                            | 32 kHz                                | 32 kHz                                                                                 |

| system<br>clock<br>oscillator                    | Divisor               | _                                                       | _                    | _                                | _                                                                                      | _                                                                                                                            | 4/8<br>(software<br>selectable)       | 4/8<br>(software<br>selectable)                                                        |

|                                                  | Stopping in stop mode | _                                                       | _                    | _                                | _                                                                                      | _                                                                                                                            | Yes                                   | Yes                                                                                    |

| Low                                              | Watch<br>mode         | _                                                       | _                    | _                                | _                                                                                      | _                                                                                                                            | Yes                                   | Yes                                                                                    |

| modes                                            | Subactive mode        | _                                                       | _                    | _                                | _                                                                                      | _                                                                                                                            | Yes                                   | Yes                                                                                    |

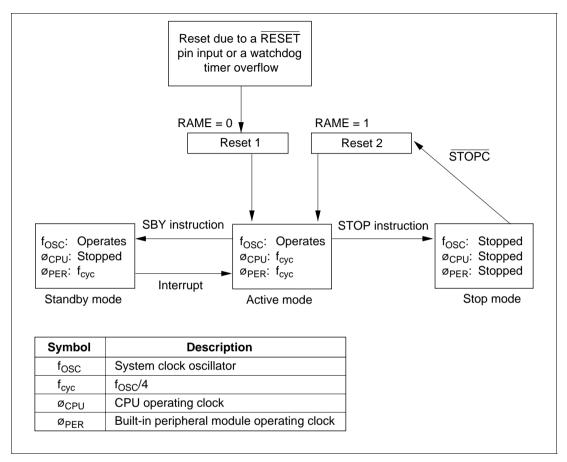

|                                                  | Standby mode          | Yes                                                     | Yes                  | Yes                              | Yes                                                                                    | Yes                                                                                                                          | Yes                                   | Yes                                                                                    |

|                                                  | Stop mode             | Yes                                                     | Yes                  | Yes                              | Yes                                                                                    | Yes                                                                                                                          | Yes                                   | Yes                                                                                    |

| Direct return to active mode from subactive mode |                       | _                                                       | _                    | _                                | _                                                                                      | _                                                                                                                            | Yes                                   | Yes                                                                                    |

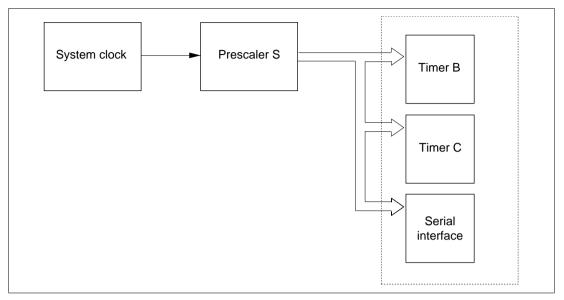

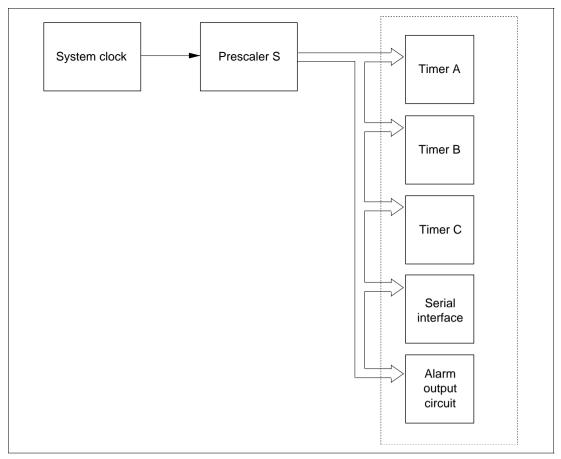

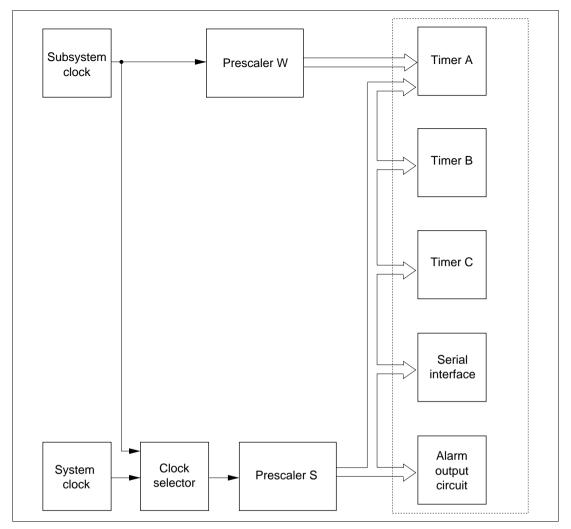

#### **Timer Function Overview**

|       |                                                                  |         | HD404344R/<br>HD404394<br>Series |         | HD404318/<br>HD404358/<br>HD404358R Series |         |         | HD404339/<br>HD404369 Series |         |  |

|-------|------------------------------------------------------------------|---------|----------------------------------|---------|--------------------------------------------|---------|---------|------------------------------|---------|--|

| Item  |                                                                  | В       | С                                | Α       | В                                          | С       | Α       | В                            | С       |  |

| Timer | Prescaler S                                                      | 0       | 0                                | $\circ$ | 0                                          | 0       | $\circ$ | 0                            | 0       |  |

|       | Prescaler W                                                      | _       | _                                | _       | _                                          | _       | 0       | _                            | _       |  |

|       | External event input (falling edge, rising edge, or double edge) | 0       | _                                | _       | 0                                          | _       | _       | 0                            | _       |  |

|       | Free-running timer                                               | $\circ$ | $\circ$                          | $\circ$ | $\circ$                                    | $\circ$ | $\circ$ | $\circ$                      | $\circ$ |  |

|       | Time base                                                        | _       | _                                | _       | _                                          | _       | $\circ$ | _                            | _       |  |

|       | Event counter                                                    | $\circ$ | _                                | _       | 0                                          | _       | _       | 0                            | _       |  |

|       | Reload                                                           | $\circ$ | $\circ$                          | _       | $\circ$                                    | $\circ$ | _       | $\circ$                      | $\circ$ |  |

|       | Watchdog                                                         | _       | 0                                |         |                                            | 0       | _       |                              | 0       |  |

|       | PWM                                                              | _       | 0                                | _       | _                                          | 0       | _       | _                            | 0       |  |

|       | Input capture                                                    | _       | _                                | _       | 0                                          | _       | _       | 0                            | _       |  |

# Contents

| Secti       | on 1    | Overview                                           | 1   |

|-------------|---------|----------------------------------------------------|-----|

| 1.1         | Overv   | iew                                                | 1   |

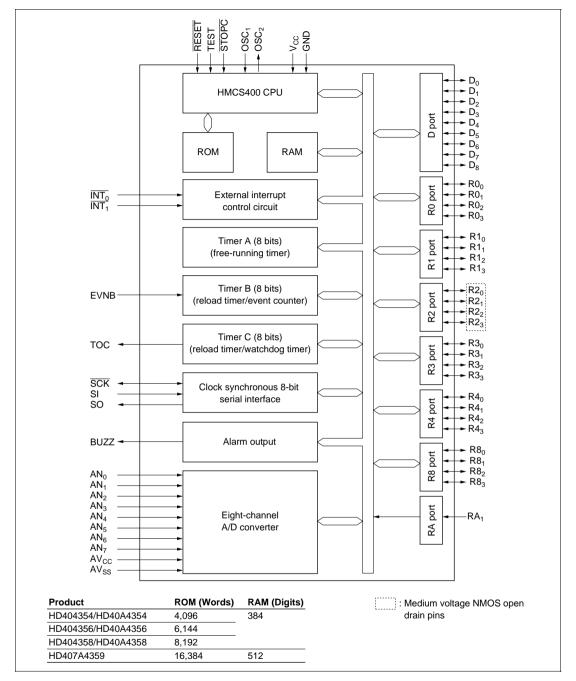

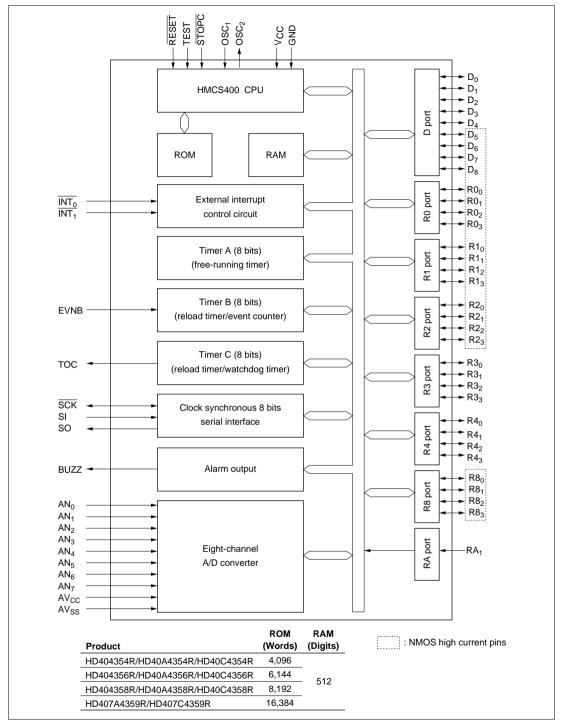

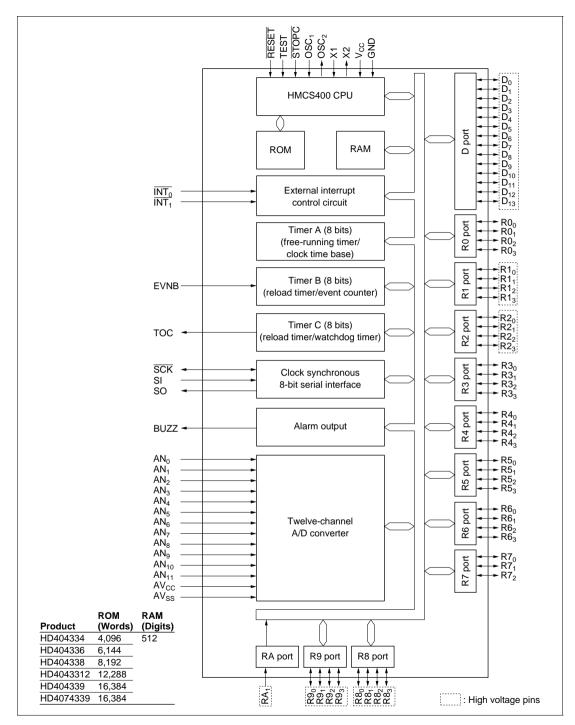

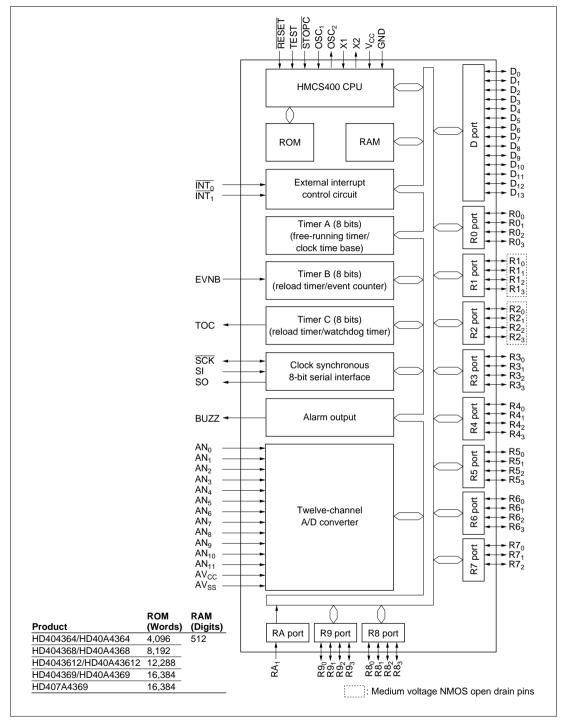

| 1.2         | Intern  | al Block Diagrams                                  | 10  |

| 1.3         | Pin Fu  | inctions                                           | 17  |

|             | 1.3.1   | HD404344R and HD404394 Series Pin Functions        | 17  |

|             | 1.3.2   | HD404318/HD404358/HD404358R Series Pin Functions   | 23  |

|             | 1.3.3   | HD404339/HD404369 Series Pin Functions             | 31  |

| Secti       | on 2    | Memory                                             | 39  |

| 2.1         | Overv   | iew                                                | 39  |

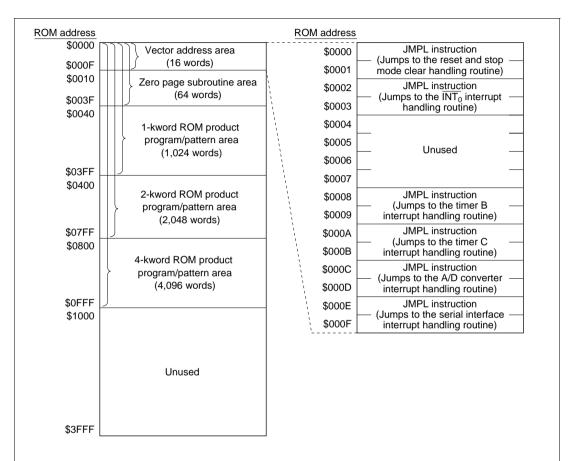

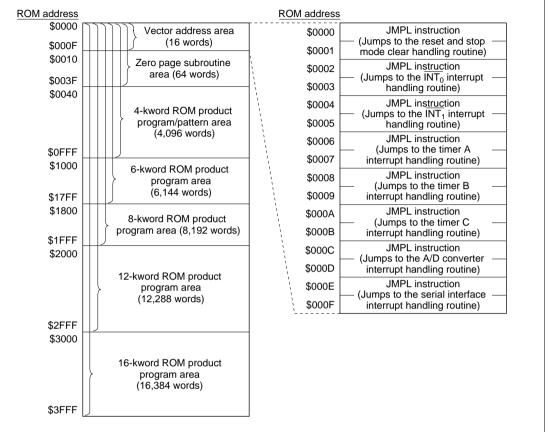

| 2.2         | ROM     |                                                    | 40  |

|             | 2.2.1   | Vector Address Area                                | 40  |

|             | 2.2.2   | Zero Page Subroutine Area                          | 40  |

|             | 2.2.3   | Pattern Area                                       | 40  |

|             | 2.2.4   | Program Area                                       | 41  |

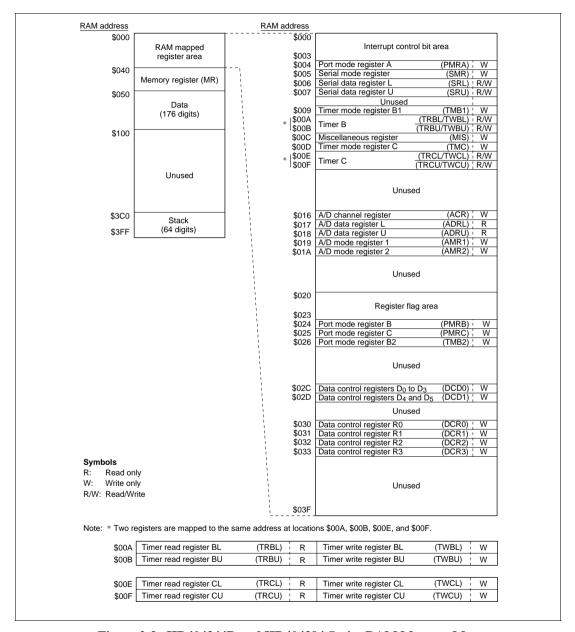

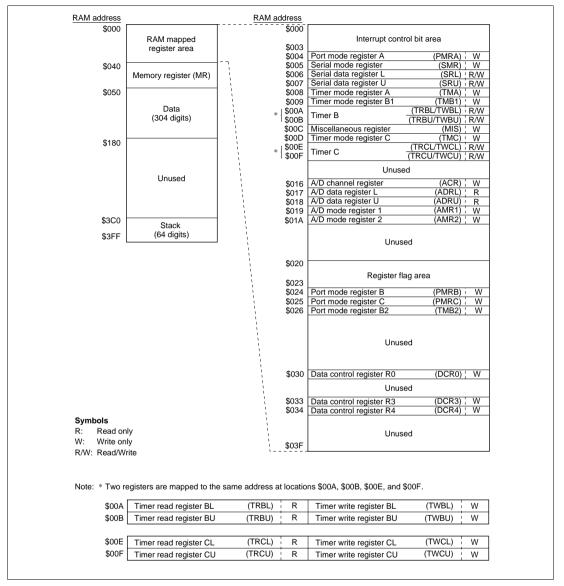

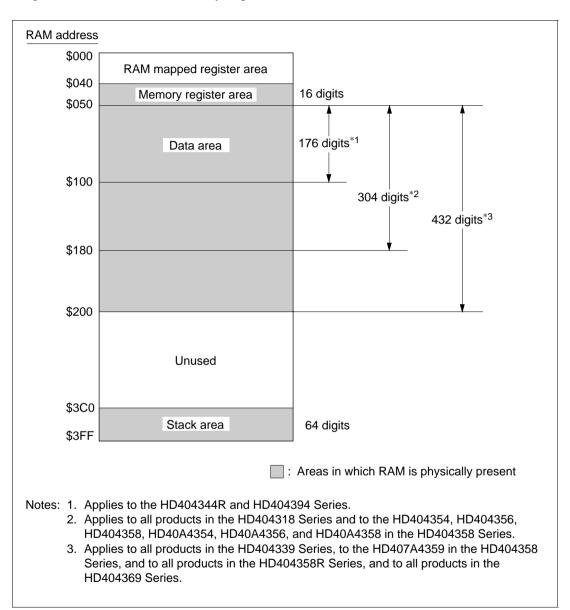

| 2.3         | RAM     |                                                    | 43  |

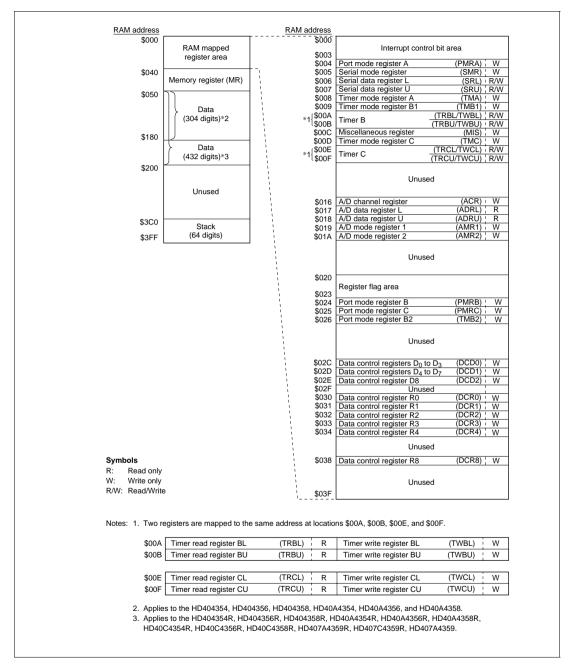

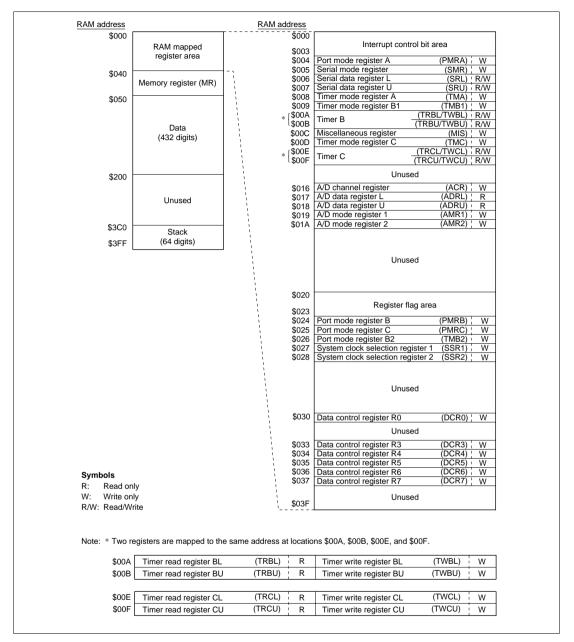

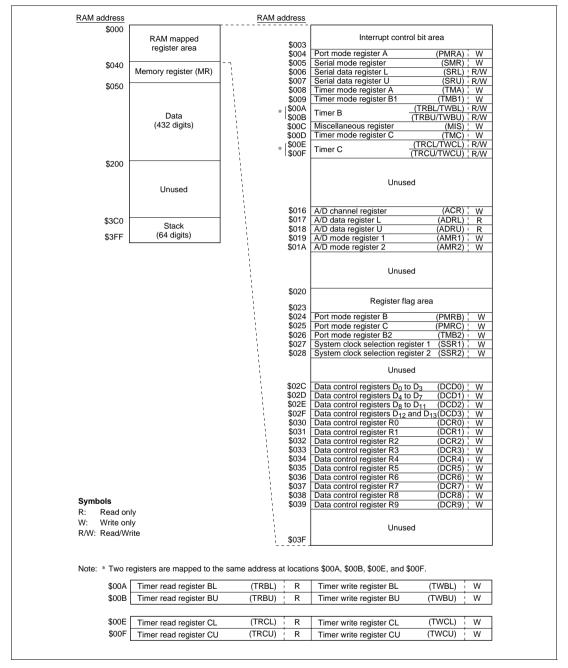

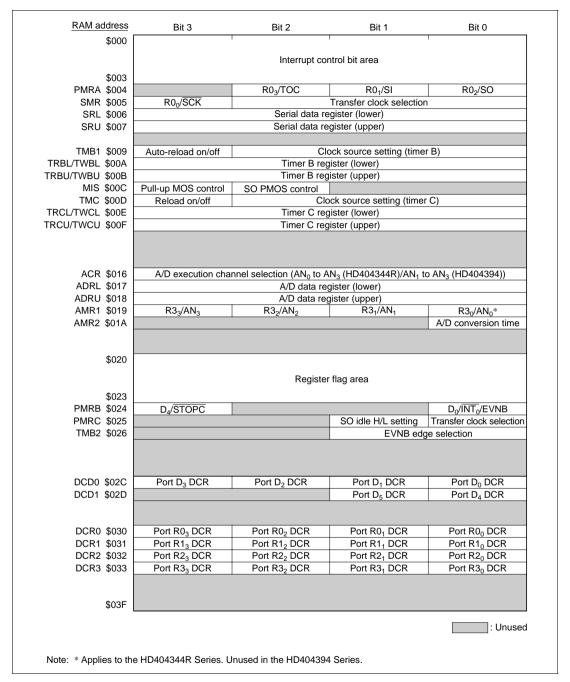

|             | 2.3.1   | RAM Mapped Register Area                           | 48  |

|             | 2.3.2   | Memory Register Area                               | 57  |

|             | 2.3.3   | Data Area                                          | 58  |

|             | 2.3.4   | Stack Area                                         | 59  |

| Secti       | on 3    | CPU                                                | 61  |

| 3.1         |         | iew                                                | 61  |

|             | 3.1.1   | Features                                           | 61  |

|             | 3.1.2   | Address Space                                      | 62  |

|             | 3.1.3   | Register Organization                              | 63  |

| 3.2         |         | Registers                                          | 64  |

| J. <b>_</b> | 3.2.1   | Accumulator (A) and B Register (B)                 | 64  |

|             | 3.2.2   | W Register (W), X Register (X), and Y Register (Y) | 64  |

|             | 3.2.3   | SPX Register (SPX), SPY Register (SPY)             | 64  |

|             | 3.2.4   | Carry Flag (CA)                                    | 64  |

|             | 3.2.5   | Status Flag (ST)                                   | 64  |

|             | 3.2.6   | Program Counter (PC)                               | 64  |

|             | 3.2.7   | Stack Pointer (SP)                                 | 65  |

| 3.3         |         | ssing Modes                                        | 65  |

| ٠.٥         | 3.3.1   | RAM Addressing Modes                               | 65  |

|             | 3.3.2   | ROM Addressing Modes and the P Instruction.        | 67  |

| 3.4         |         | ssing States                                       | 70  |

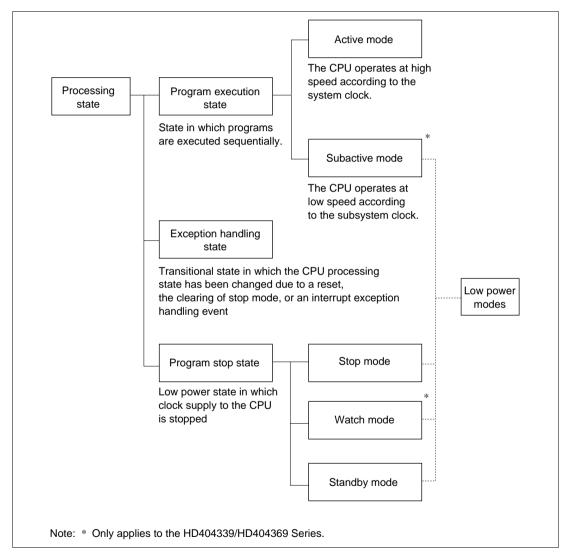

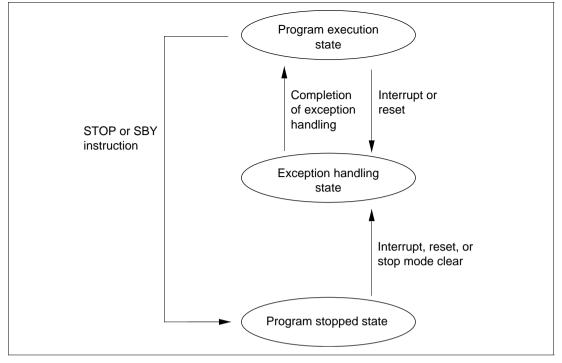

| J.T         | 3.4.1   | Overview                                           | 70  |

|             | J. F. I | O 101 120 11                                       | , 0 |

|      | 3.4.2   | Program Execution State                                                   | 71  |

|------|---------|---------------------------------------------------------------------------|-----|

|      | 3.4.3   | Exception Handling State                                                  | 72  |

|      | 3.4.4   | Program Stopped State                                                     |     |

| Sect | ion 4   | Exception Handling                                                        | 73  |

| 4.1  | Overv   | iew                                                                       | 73  |

| 4.2  | Reset   |                                                                           | 74  |

|      | 4.2.1   | Overview                                                                  | 74  |

|      | 4.2.2   | Reset Sequence                                                            | 74  |

| 4.3  | Stop N  | Mode Clear                                                                | 75  |

|      | 4.3.1   | Overview                                                                  | 75  |

|      | 4.3.2   | Stop Mode Clear Sequence (RESET Pin Input)                                | 75  |

|      | 4.3.3   | Stop Mode Clear Sequence (STOPC Pin Input)                                | 75  |

| 4.4  | Initial | Values of Registers and Flags on Reset and Stop Mode Clear                | 76  |

| 4.5  | Interru | ipts                                                                      | 79  |

|      | 4.5.1   | Overview                                                                  | 79  |

|      | 4.5.2   | Interrupt Registers and Flags                                             | 80  |

|      | 4.5.3   | External Interrupts                                                       | 88  |

|      | 4.5.4   | Internal Interrupts                                                       | 88  |

|      | 4.5.5   | Interrupt Handling Sequence                                               | 89  |

|      |         | Low Power Modes (HD404344R/HD404394/HD404318 /HD404358 /HD404358R Series) |     |

| 5.1  |         | iew                                                                       |     |

|      | 5.1.1   | Features                                                                  |     |

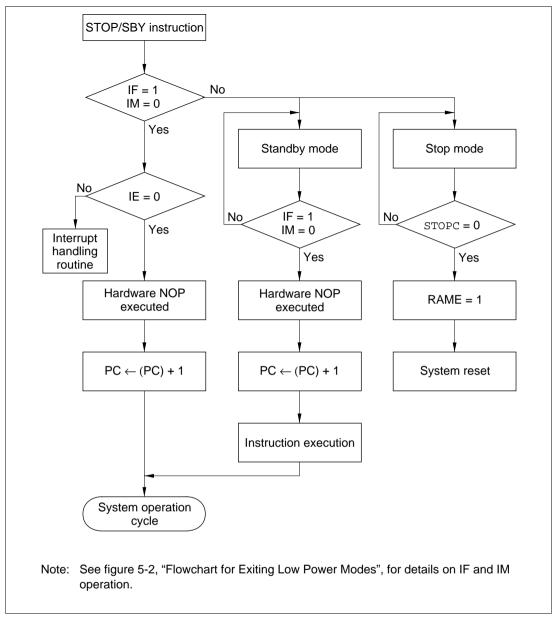

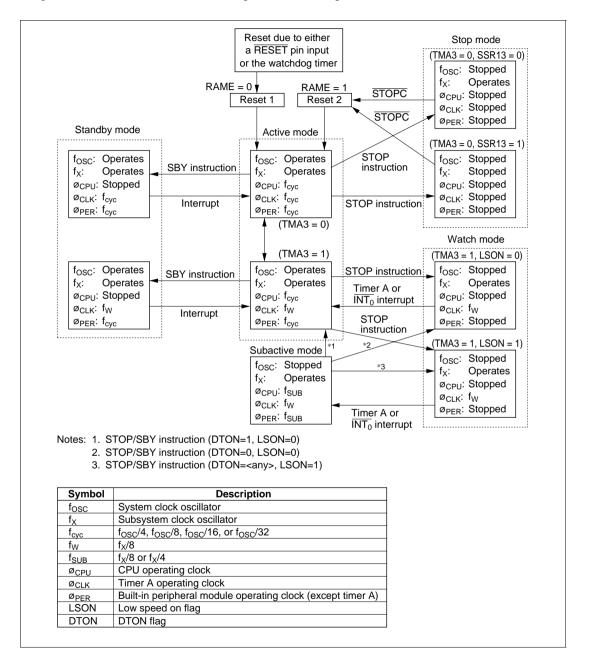

|      | 5.1.2   | State Transition Diagram                                                  |     |

|      | 5.1.3   | Pin Functions                                                             |     |

|      | 5.1.4   | Registers and Flags                                                       |     |

| 5.2  | _       | er and Flag Descriptions                                                  |     |

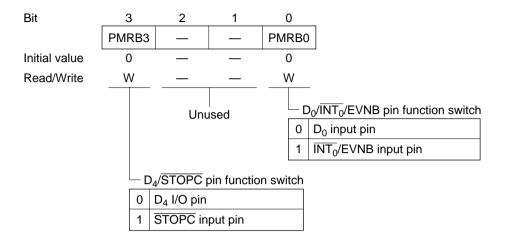

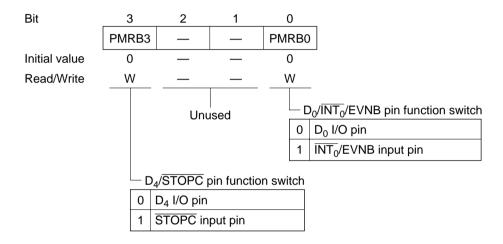

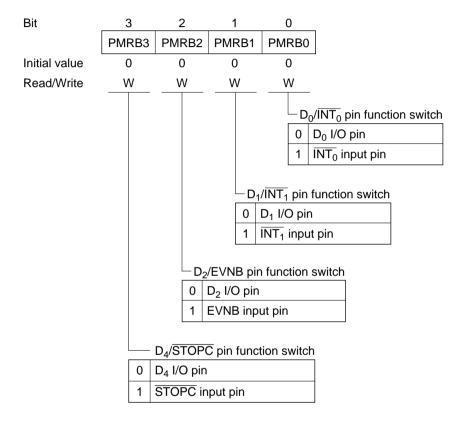

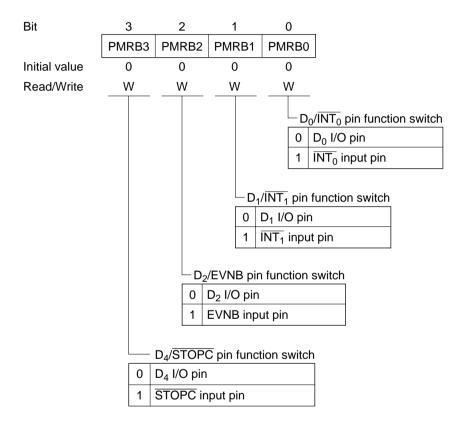

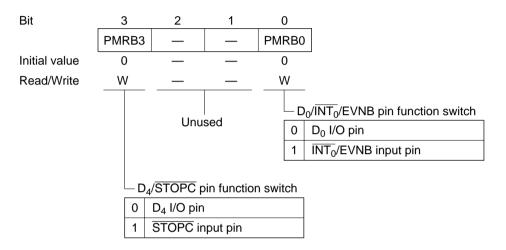

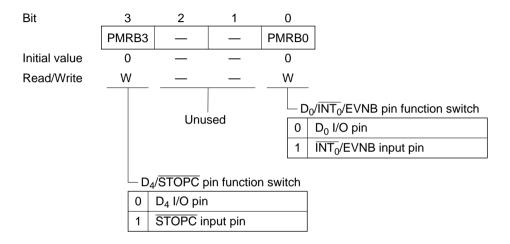

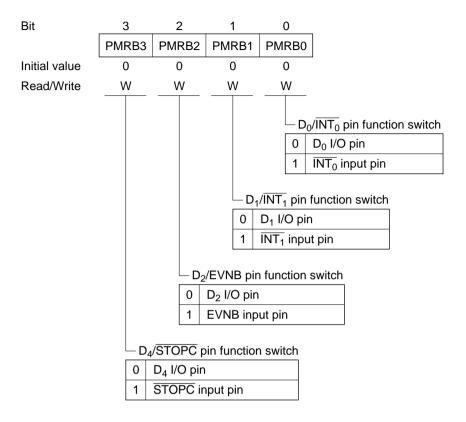

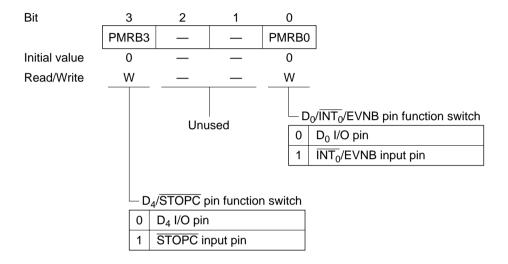

|      | 5.2.1   | Port Mode Register B (PMRB: \$024)                                        |     |

|      | 5.2.2   | RAM Enable Flag (RAME: \$021, 3)                                          |     |

| 5.3  |         | by Mode                                                                   |     |

|      | 5.3.1   | Entering Standby Mode                                                     |     |

|      | 5.3.2   | Clearing Standby Mode                                                     |     |

| 5.4  | _       | Mode                                                                      |     |

|      | 5.4.1   | Entering Stop Mode                                                        |     |

|      | 5.4.2   | Clearing Stop Mode                                                        |     |

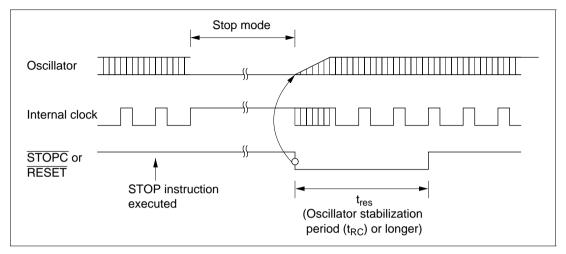

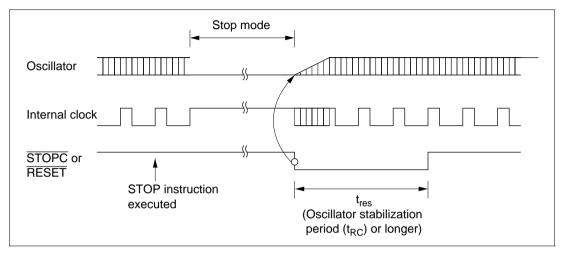

|      | 5.4.3   | Post-Stop Mode Oscillator Stabilization Period                            |     |

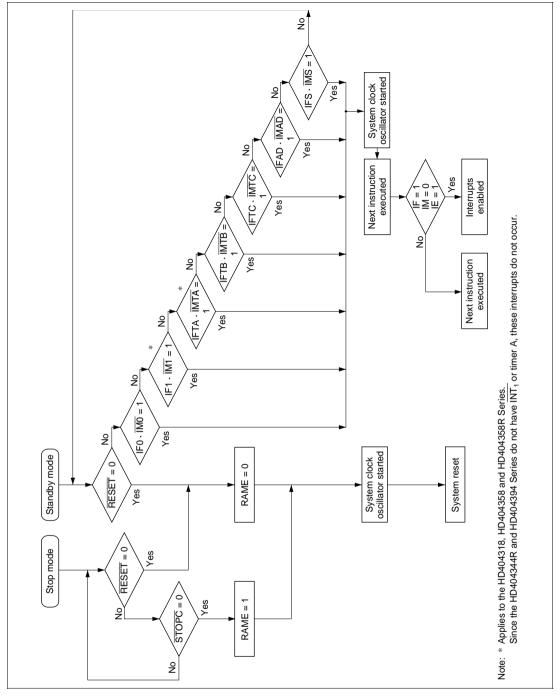

| 5.5  | Low F   | Power Mode Operating Sequence                                             | 105 |

| Sect | ion 6   | Low Power Modes (HD404339 and HD404369 Series)                            | 107 |

| 6.1  | Overv   | iew                                                                       | 107 |

|      | 6.1.1   | Features                                                                  | 107 |

| ii   |         |                                                                           |     |

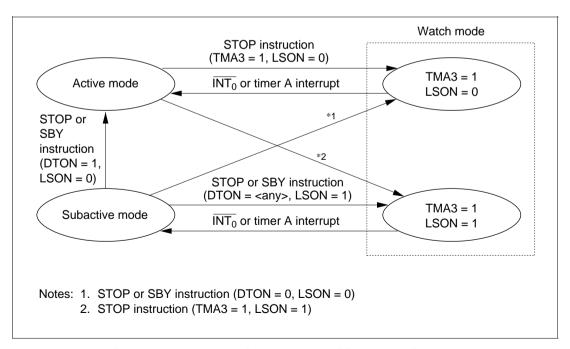

|       | 6.1.2    | State Transition Diagram                                                 | 109 |

|-------|----------|--------------------------------------------------------------------------|-----|

|       | 6.1.3    | Pin Functions                                                            | 110 |

|       | 6.1.4    | Registers and Flags                                                      | 110 |

| 6.2   | Registe  | r and Flag Descriptions                                                  | 111 |

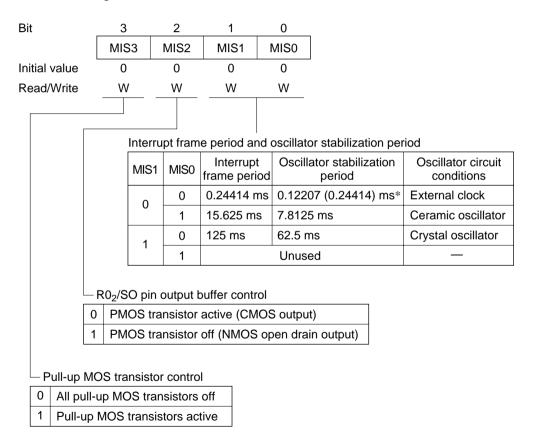

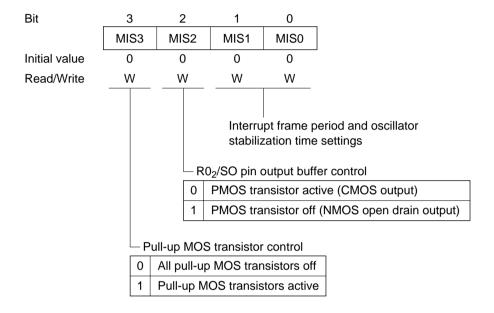

|       | 6.2.1    | Miscellaneous Register (MIS: \$00C)                                      | 111 |

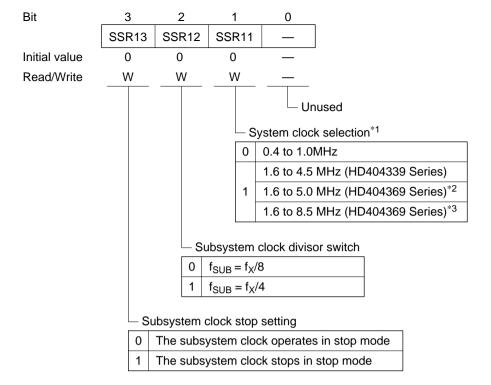

|       | 6.2.2    | System Clock Selection Register 1 (SSR1: \$027)                          | 112 |

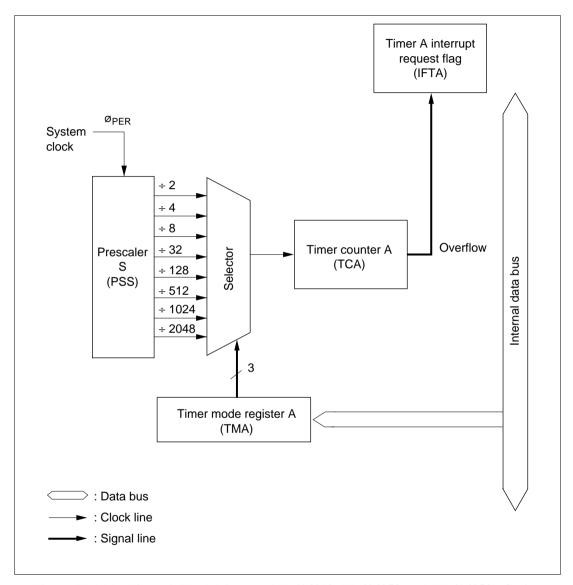

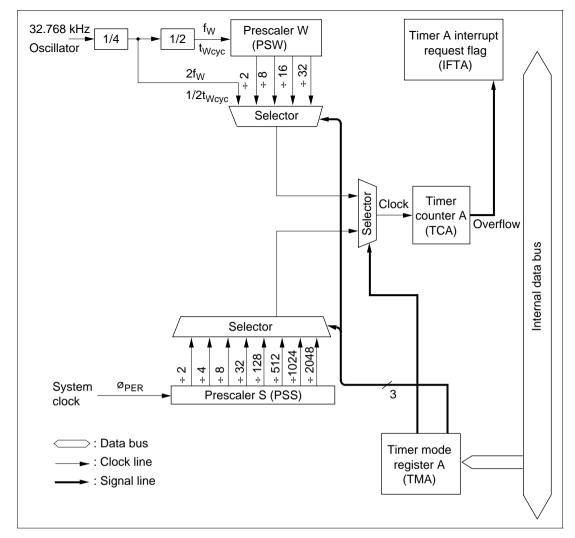

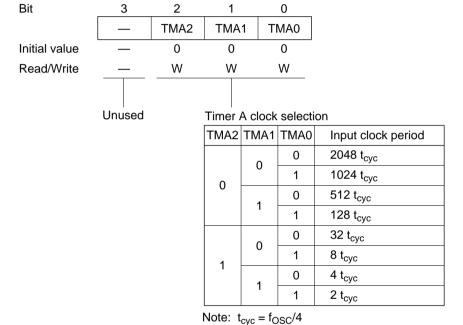

|       | 6.2.3    | Timer Mode Register A (TMA: \$008)                                       | 114 |

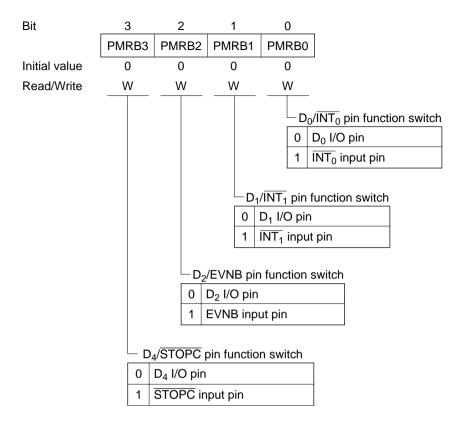

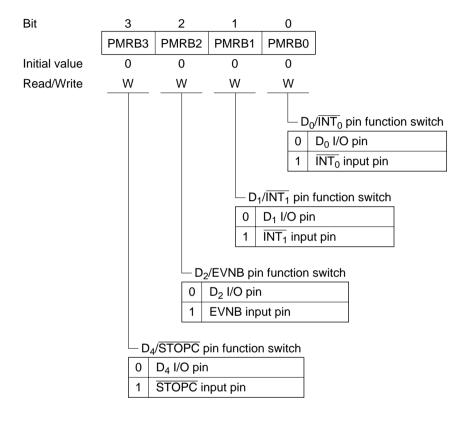

|       | 6.2.4    | Port Mode Register B (PMRB: \$024)                                       | 116 |

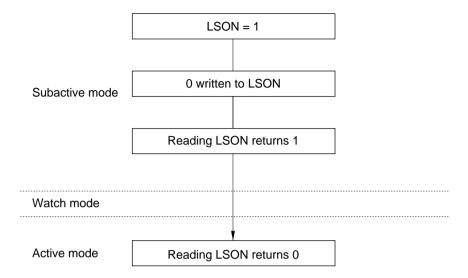

|       | 6.2.5    | Low Speed On Flag (LSON: \$020, 0)                                       | 117 |

|       | 6.2.6    | DTON Flag (DTON: \$020, 3)                                               | 119 |

|       | 6.2.7    | RAM Enable Flag (RAME: \$021, 3)                                         | 119 |

| 6.3   | Standby  | / Mode                                                                   | 120 |

|       | 6.3.1    | Entering Standby Mode                                                    | 120 |

|       | 6.3.2    | Clearing Standby Mode                                                    | 120 |

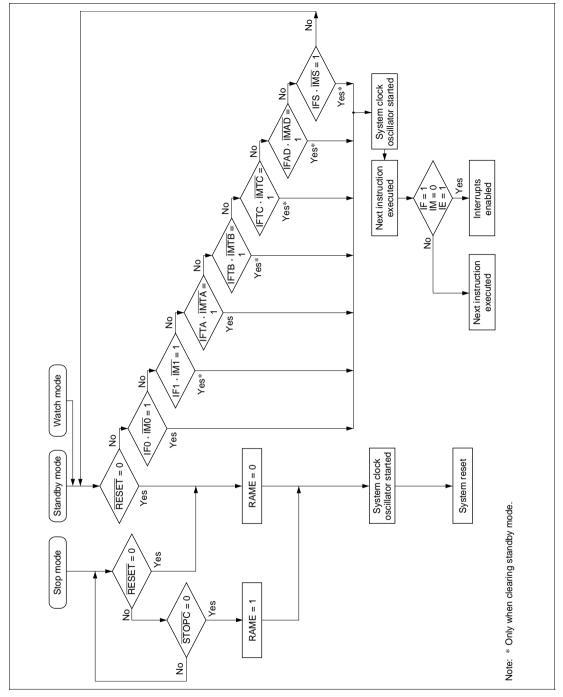

| 6.4   | Stop M   | ode                                                                      | 122 |

|       | 6.4.1    | Entering Stop Mode                                                       | 122 |

|       | 6.4.2    | Clearing Stop Mode                                                       | 122 |

|       | 6.4.3    | Post-Stop Mode Oscillator Stabilization Period                           | 123 |

| 6.5   | Watch    | Mode                                                                     | 124 |

|       | 6.5.1    | Entering Watch Mode                                                      | 124 |

|       | 6.5.2    | Clearing Watch Mode                                                      | 124 |

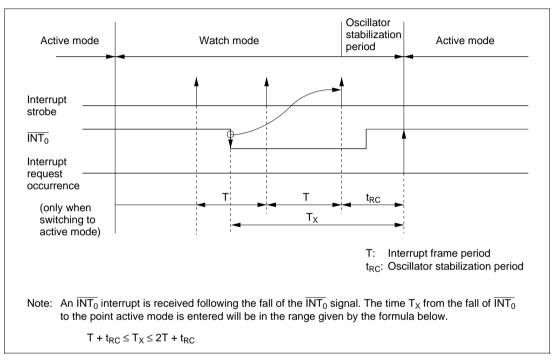

|       | 6.5.3    | Post-Watch Mode Operating Timing                                         | 125 |

| 6.6   | Subacti  | ve Mode                                                                  | 126 |

|       | 6.6.1    | Entering Subactive Mode                                                  | 126 |

|       | 6.6.2    | Clearing Subactive Mode                                                  | 126 |

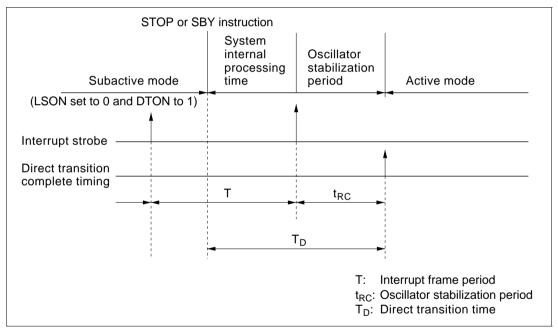

|       | 6.6.3    | System Timing when Switching Directly from Subactive Mode to Active Mode | 127 |

| 6.7   | Interrup | ot Frame                                                                 | 128 |

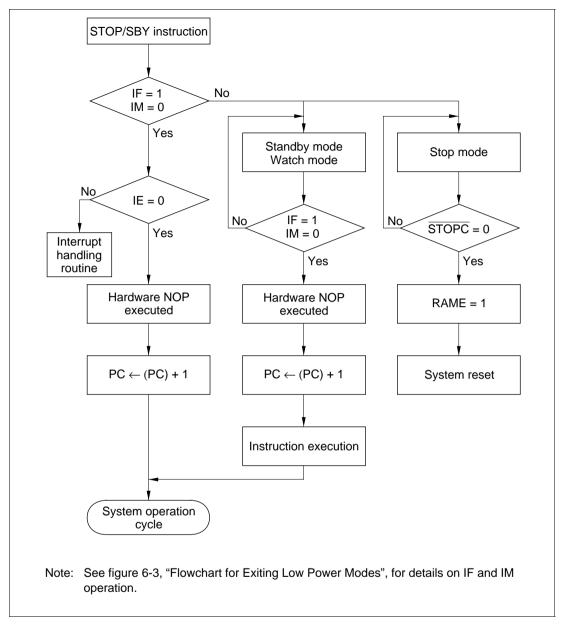

| 6.8   | Low Po   | ower Mode Operating Sequence                                             | 128 |

| 6.9   | Usage I  | Notes                                                                    | 130 |

|       | _        |                                                                          |     |

| Secti | on 7 I   | /O Ports (HD404344R Series)                                              | 131 |

| 7.1   | Overvie  | ew                                                                       | 131 |

|       | 7.1.1    | Features                                                                 | 131 |

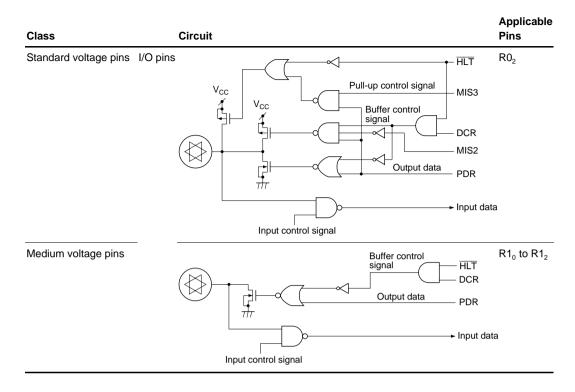

|       | 7.1.2    | I/O Control                                                              | 133 |

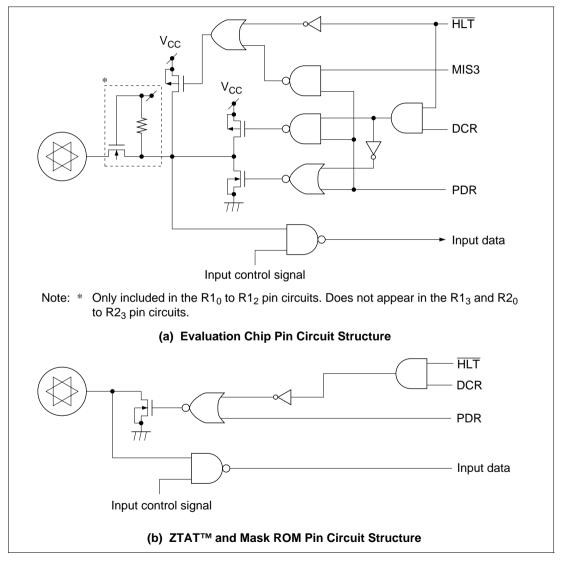

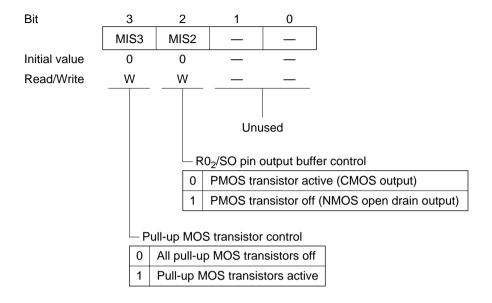

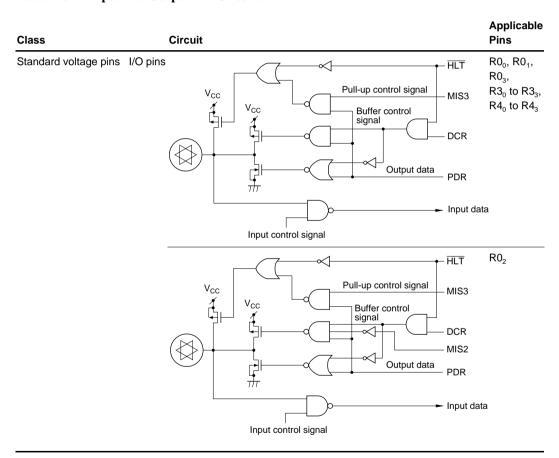

|       | 7.1.3    | I/O Pin Circuit Structures                                               | 136 |

|       | 7.1.4    | Port States in Low Power Modes                                           | 139 |

|       | 7.1.5    | Handling Unused Pins                                                     |     |

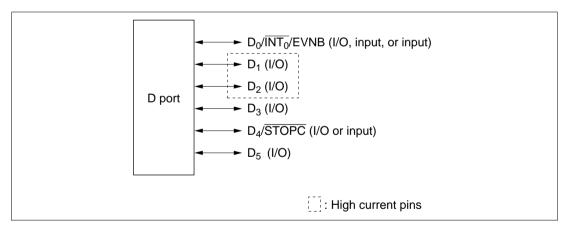

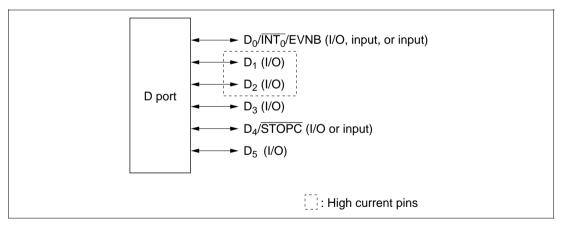

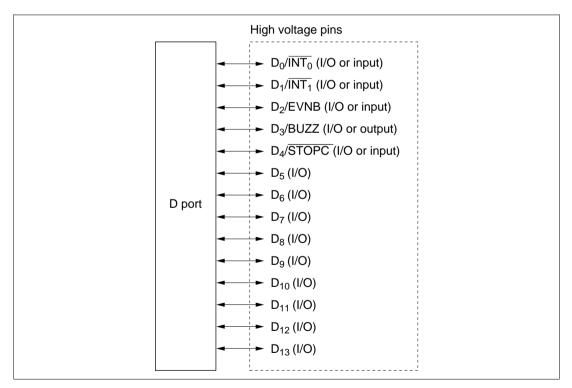

| 7.2   | D Port.  |                                                                          |     |

|       | 7.2.1    | Overview                                                                 | 140 |

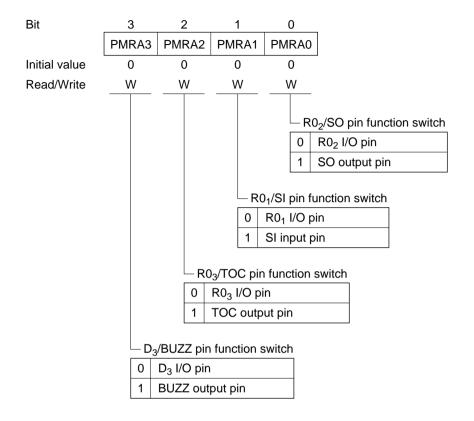

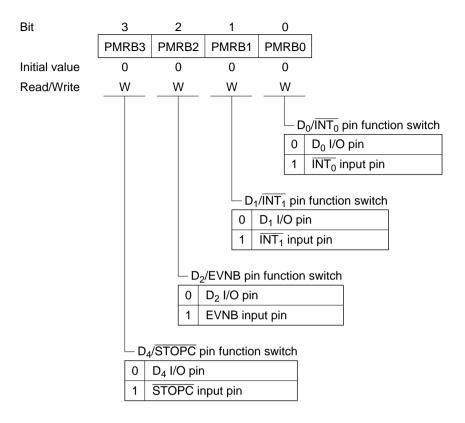

|       | 7.2.2    | Register Configuration and Descriptions                                  |     |

|       | 7.2.3    | Pin Functions.                                                           |     |

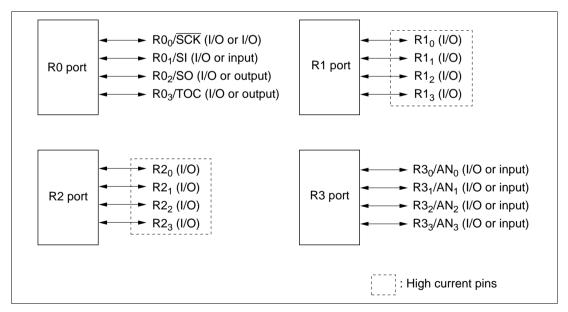

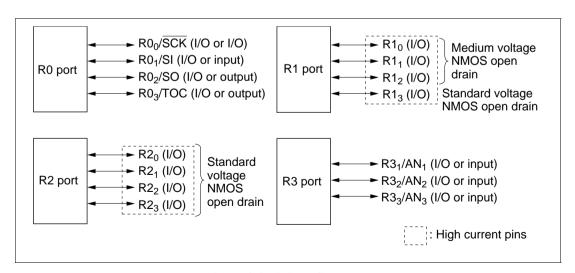

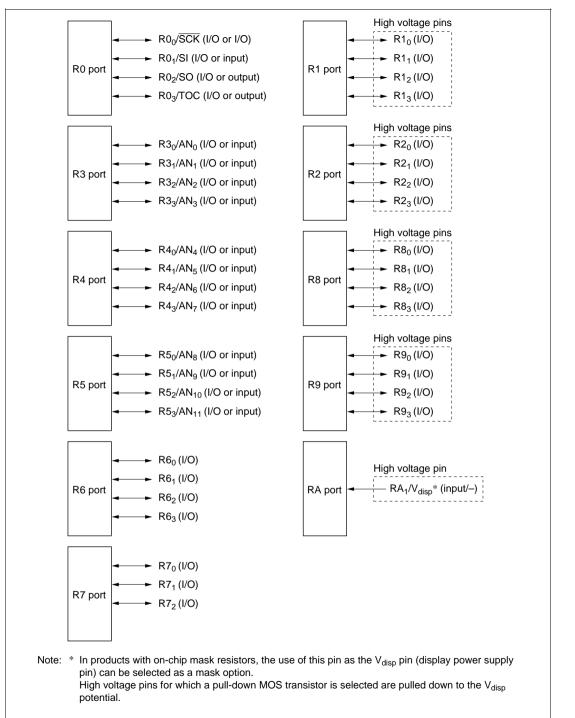

| 7.3   |          |                                                                          |     |

|       | 7.3.1    | Overview                                                                 |     |

|       |          |                                                                          | ;;  |

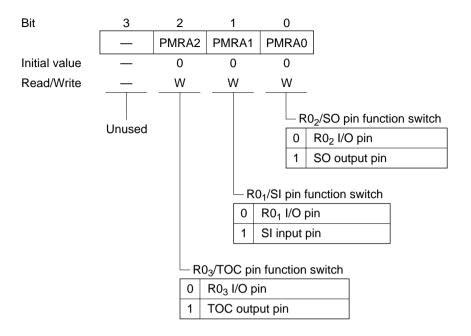

|      | 7.3.2   | Register Configuration and Descriptions   | 145 |

|------|---------|-------------------------------------------|-----|

|      | 7.3.3   | Pin Functions                             | 151 |

| 7.4  | Usage   | Notes                                     | 154 |

|      |         |                                           |     |

| Sect |         | I/O Ports (HD404394 Series)               |     |

| 8.1  |         | ew                                        | 157 |

|      | 8.1.1   | Features                                  |     |

|      | 8.1.2   | I/O Control                               |     |

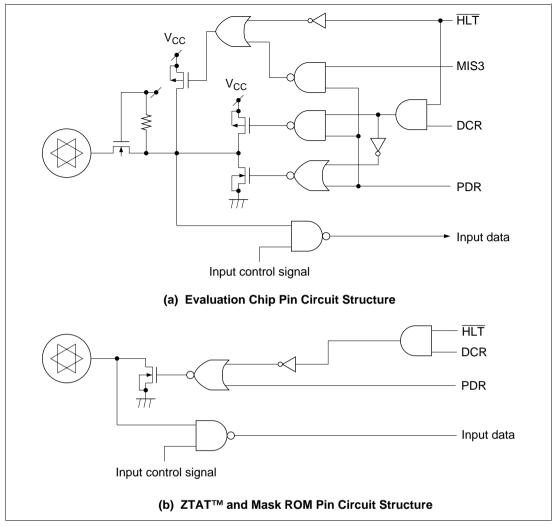

|      | 8.1.3   | I/O Pin Circuit Structures                |     |

|      | 8.1.4   | Port States in Low Power Modes            |     |

|      | 8.1.5   | Handling Unused Pins                      | 166 |

| 8.2  |         |                                           |     |

|      | 8.2.1   | Overview                                  |     |

|      | 8.2.2   | Register Configuration and Descriptions   | 168 |

|      | 8.2.3   | Pin Functions                             |     |

| 8.3  | R Ports | S                                         | 171 |

|      | 8.3.1   | Overview                                  |     |

|      | 8.3.2   | Register Configuration and Descriptions   |     |

|      | 8.3.3   | Pin Functions                             | 178 |

| 8.4  | Usage   | Notes                                     | 181 |

|      |         |                                           |     |

| Sect |         | I/O Ports (HD404318 Series)               |     |

| 9.1  | Overvi  | ew                                        | 185 |

|      | 9.1.1   | Features                                  | 185 |

|      | 9.1.2   | I/O Control                               | 188 |

|      | 9.1.3   | I/O Pin Circuit Structures                |     |

|      | 9.1.4   | Port States in Low Power Modes            |     |

|      | 9.1.5   | Handling Unused Pins                      | 195 |

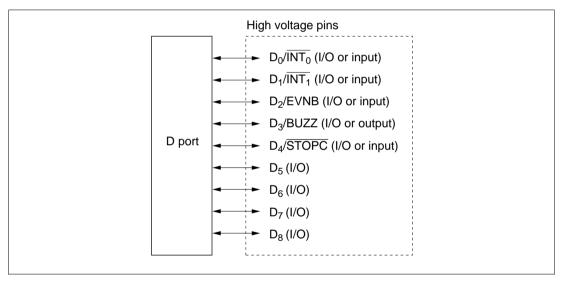

| 9.2  | D Port  |                                           |     |

|      | 9.2.1   | Overview                                  |     |

|      | 9.2.2   | Register Configuration and Descriptions   |     |

|      | 9.2.3   | Pin Functions                             | 201 |

| 9.3  | R Ports | S                                         | 202 |

|      | 9.3.1   | Overview                                  | 202 |

|      | 9.3.2   | Register Configuration and Descriptions   | 204 |

|      | 9.3.3   | Pin Functions                             | 211 |

| 9.4  | Usage   | Notes                                     | 214 |

|      |         |                                           |     |

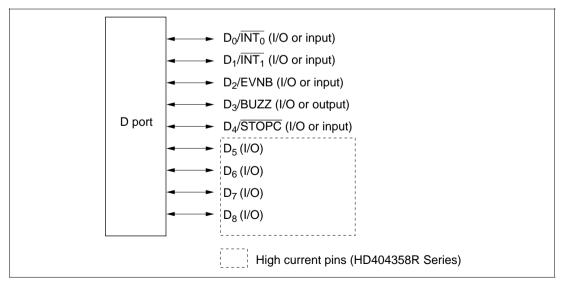

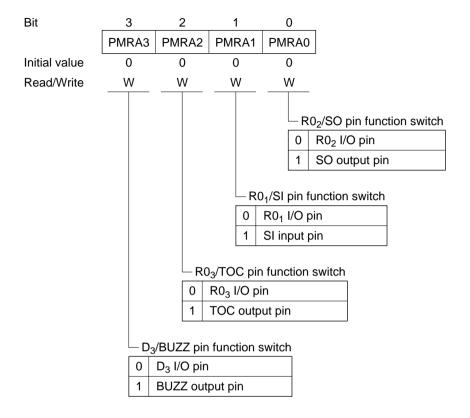

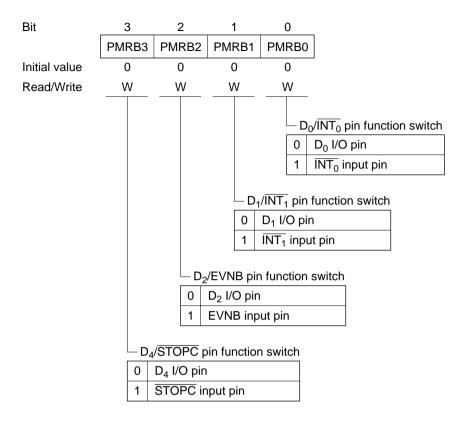

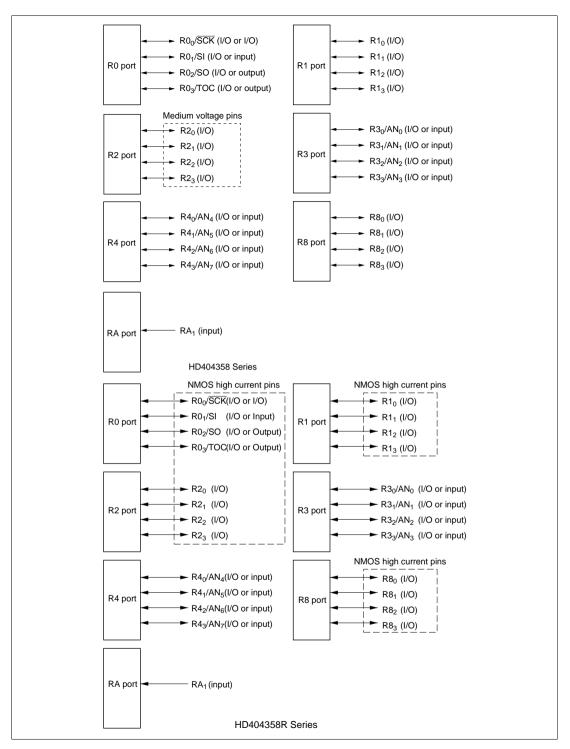

|      |         | I/O Ports (HD404358 and HD404358R Series) |     |

| 10.1 | Overvi  | ew                                        | 217 |

|      | 10.1.1  | Features                                  | 217 |

|      |         | I/O Control                               |     |

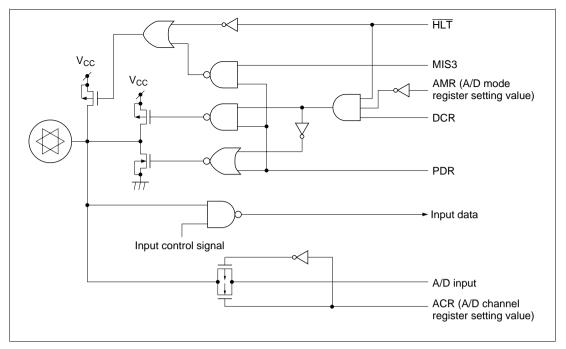

|      | 10.1.3  | I/O Pin Circuit Structures                | 223 |

| iv   |         |                                           |     |

|            | 10.1.4  | Port States in Low Power Modes          | 230 |

|------------|---------|-----------------------------------------|-----|

|            | 10.1.5  | Handling Unused Pins                    | 230 |

| 10.2       | D Port. |                                         | 231 |

|            | 10.2.1  | Overview                                | 231 |

|            | 10.2.2  | Register Configuration and Descriptions | 232 |

|            | 10.2.3  | Pin Functions                           | 237 |

| 10.3       | R Ports |                                         | 239 |

|            | 10.3.1  | Overview                                | 239 |

|            | 10.3.2  | Register Configuration and Descriptions | 241 |

|            | 10.3.3  | Pin Functions                           | 250 |

| 10.4       | Usage 1 | Notes                                   | 255 |

|            |         |                                         |     |

| Secti      |         | I/O Ports (HD404339 Series)             |     |

| 11.1       |         | ew                                      |     |

|            |         | Features                                |     |

|            |         | I/O Control                             |     |

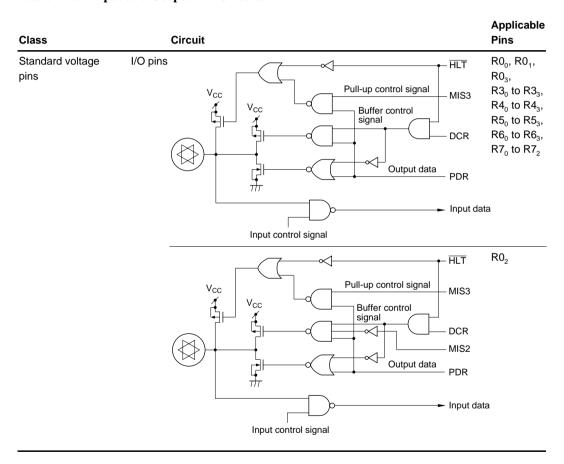

|            |         | I/O Pin Circuit Structures              |     |

|            |         | Port States in Low Power Modes          |     |

|            |         | Handling Unused Pins                    |     |

| 11.2       |         |                                         |     |

|            |         | Overview                                |     |

|            |         | Register Configuration and Descriptions |     |

|            |         | Pin Functions                           |     |

| 11.3       |         |                                         |     |

|            |         | Overview                                |     |

|            |         | Register Configuration and Descriptions |     |

|            |         | Pin Functions                           |     |

| 11.4       | Usage 1 | Notes                                   | 291 |

| <b>a</b> . |         | T/O D (VID 10 10 co G . 1 . )           |     |

|            |         | I/O Ports (HD404369 Series)             |     |

| 12.1       |         | ew                                      |     |

|            |         | Features                                |     |

|            |         | I/O Control.                            |     |

|            |         | I/O Pin Circuit Structures              |     |

|            |         | Port States in Low Power Modes          |     |

|            |         | Handling Unused Pins                    |     |

| 12.2       |         |                                         |     |

|            |         | Overview                                |     |

|            |         | Register Configuration and Descriptions |     |

|            |         | Pin Functions                           |     |

| 12.3       |         |                                         |     |

|            |         | Overview                                |     |

|            | 12.3.2  | Register Configuration and Descriptions | 315 |

|            |         | Ochice ve                               | V   |

| 12.4 Usage Notes       330         Section 13 Oscillator Circuits (HD404344R/HD404394/HD404318 /HD404358/ HD404358R Series)         13.1 Overview       335         13.1.1 Features       335         13.1.2 Block Diagram       336         13.1.3 Oscillator Circuit Pins       337         13.2 Oscillator Connection and External Clock Input       338         13.3 Usage Notes       340         Section 14 Oscillator Circuits (HD404339 and HD404369 Series)       343         14.1 Overview       343         14.1.1 Features       343         14.1.2 Block Diagram       344         14.1.3 Oscillator Circuit Pins       346         14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.4 Usage Notes       353 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /HD404358/ HD404358R Series)       335         13.1 Overview       335         13.1.1 Features       335         13.1.2 Block Diagram       336         13.1.3 Oscillator Circuit Pins       337         13.2 Oscillator Connection and External Clock Input       338         13.3 Usage Notes       340         Section 14 Oscillator Circuits (HD404339 and HD404369 Series)       343         14.1 Features       343         14.1.2 Block Diagram       344         14.1.3 Oscillator Circuit Pins       346         14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.3 Oscillator Connection and External Clock Input       351                                                                                     |

| /HD404358/ HD404358R Series)       335         13.1 Overview       335         13.1.1 Features       335         13.1.2 Block Diagram       336         13.1.3 Oscillator Circuit Pins       337         13.2 Oscillator Connection and External Clock Input       338         13.3 Usage Notes       340         Section 14 Oscillator Circuits (HD404339 and HD404369 Series)       343         14.1 Features       343         14.1.2 Block Diagram       344         14.1.3 Oscillator Circuit Pins       346         14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.3 Oscillator Connection and External Clock Input       351                                                                                     |

| 13.1       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13.1.1 Features       335         13.1.2 Block Diagram       336         13.1.3 Oscillator Circuit Pins       337         13.2 Oscillator Connection and External Clock Input       338         13.3 Usage Notes       340         Section 14 Oscillator Circuits (HD404339 and HD404369 Series)       343         14.1 Overview       343         14.1.1 Features       343         14.1.2 Block Diagram       344         14.1.3 Oscillator Circuit Pins       346         14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.3 Oscillator Connection and External Clock Input       351                                                                                                                                  |

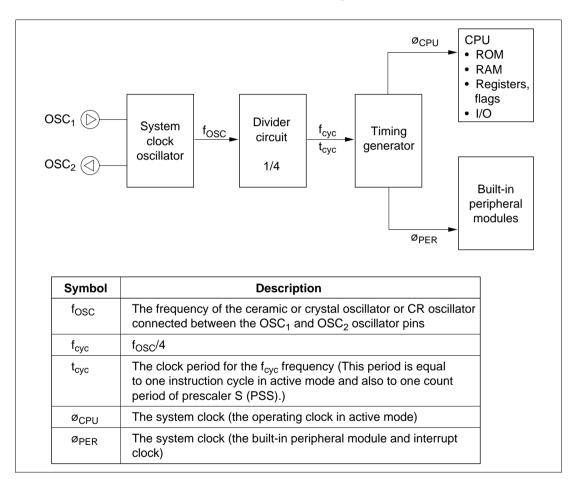

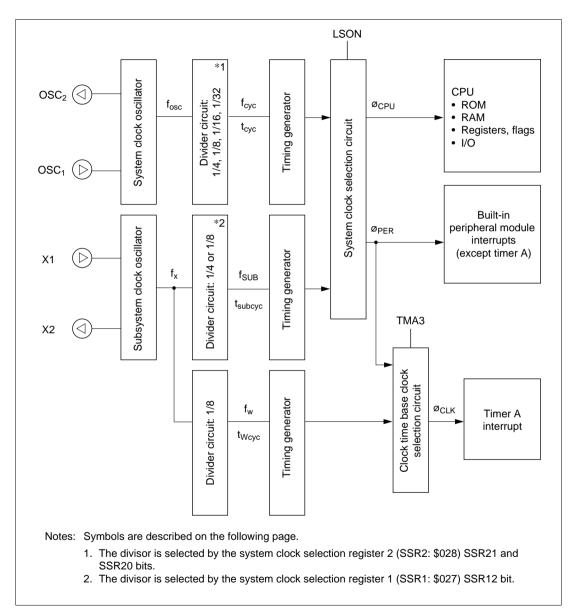

| 13.1.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

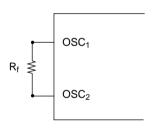

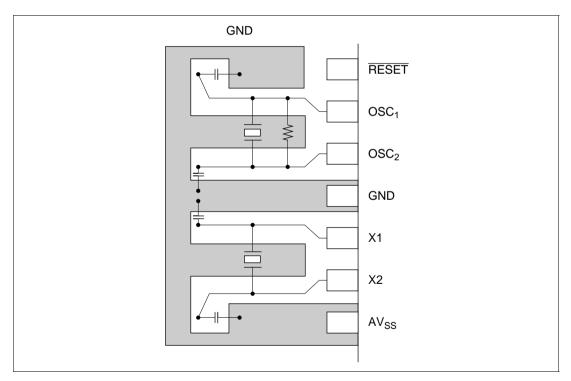

| 13.1.3 Oscillator Circuit Pins       337         13.2 Oscillator Connection and External Clock Input       338         13.3 Usage Notes       340         Section 14 Oscillator Circuits (HD404339 and HD404369 Series)       343         14.1 Overview       343         14.1.1 Features       343         14.1.2 Block Diagram       344         14.1.3 Oscillator Circuit Pins       346         14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.3 Oscillator Connection and External Clock Input       351                                                                                                                                                                                                           |

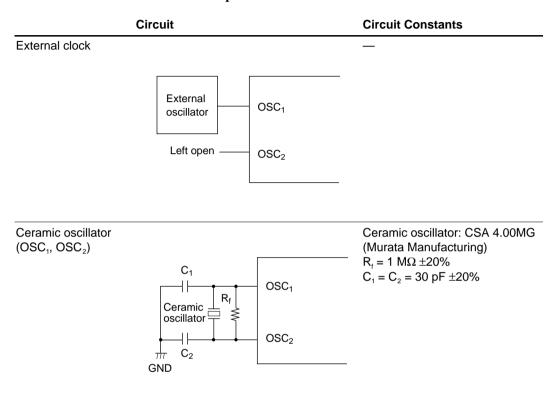

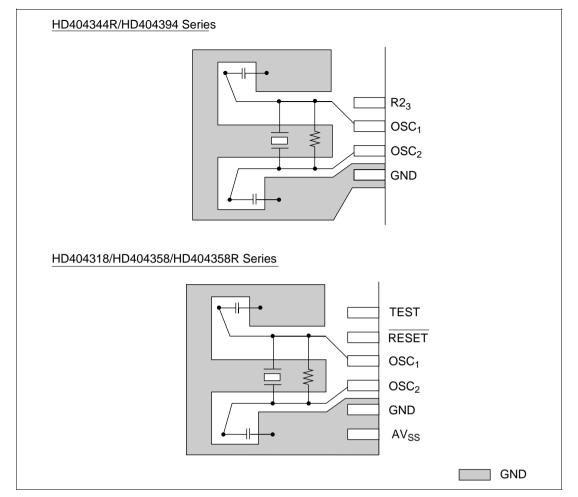

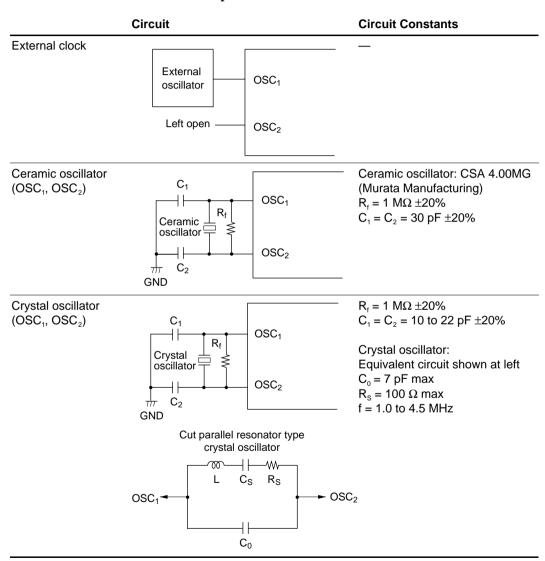

| 13.2 Oscillator Connection and External Clock Input       338         13.3 Usage Notes       340         Section 14 Oscillator Circuits (HD404339 and HD404369 Series)       343         14.1 Overview       343         14.1.1 Features       343         14.1.2 Block Diagram       344         14.1.3 Oscillator Circuit Pins       346         14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.3 Oscillator Connection and External Clock Input       351                                                                                                                                                                                                                                                            |

| 13.3 Usage Notes       340         Section 14 Oscillator Circuits (HD404339 and HD404369 Series)       343         14.1 Overview       343         14.1.1 Features       343         14.1.2 Block Diagram       344         14.1.3 Oscillator Circuit Pins       346         14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.3 Oscillator Connection and External Clock Input       351                                                                                                                                                                                                                                                                                                                                  |

| 14.1       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14.1       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14.1.1 Features       343         14.1.2 Block Diagram       344         14.1.3 Oscillator Circuit Pins       346         14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.3 Oscillator Connection and External Clock Input       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14.1.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14.1.3 Oscillator Circuit Pins       346         14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.3 Oscillator Connection and External Clock Input       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14.1.4 Register and Flag Configuration       346         14.2 Register and Flag Descriptions       347         14.2.1 System Clock Selection Register 1 (SSR1: \$027)       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028)       349         14.2.3 Low Speed On Flag (LSON: \$020, 0)       350         14.3 Oscillator Connection and External Clock Input       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 14.2       Register and Flag Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

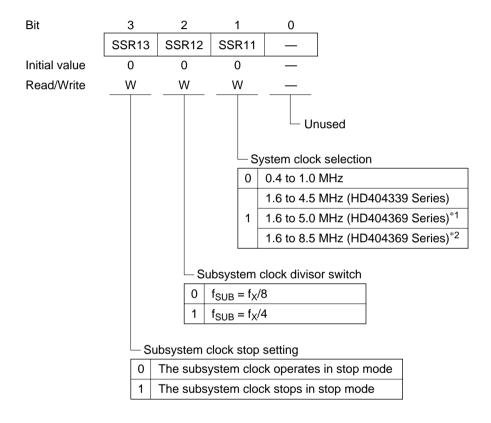

| 14.2.1 System Clock Selection Register 1 (SSR1: \$027).       347         14.2.2 System Clock Selection Register 2 (SSR2: \$028).       349         14.2.3 Low Speed On Flag (LSON: \$020, 0).       350         14.3 Oscillator Connection and External Clock Input       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

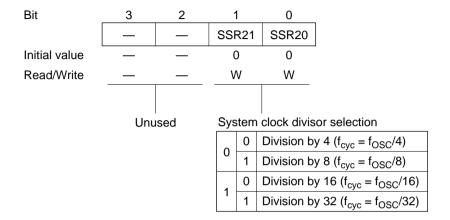

| 14.2.2System Clock Selection Register 2 (SSR2: \$028).34914.2.3Low Speed On Flag (LSON: \$020, 0).35014.3Oscillator Connection and External Clock Input.351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14.2.3 Low Speed On Flag (LSON: \$020, 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14.3 Oscillator Connection and External Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |