# SIO RLDRAM® 2

**MT49H32M18C – 32 Meg x 18 x 8 banks**

**MT49H64M9C – 64 Meg x 9 x 8 banks**

## Features

- 533 MHz DDR operation (1.067 Gb/s/pin data rate)

- 38.4 Gb/s peak bandwidth (x18 at 533 MHz clock frequency)

- Organization

- 32 Meg x 18 and 64 Meg x 9 separate I/O

- 8 banks

- Reduced cycle time (15ns at 533 MHz)

- Nonmultiplexed addresses (address multiplexing option available)

- SRAM-type interface

- Programmable READ latency (RL), row cycle time, and burst sequence length

- Balanced READ and WRITE latencies in order to optimize data bus utilization

- Data mask for WRITE commands

- Differential input clocks (CK, CK#)

- Differential input data clocks (DKx, DKx#)

- On-die DLL generates CK edge-aligned data and output data clock signals

- Data valid signal (QVLD)

- 32ms refresh (16K refresh for each bank; 128K refresh command must be issued in total each 32ms)

- HSTL I/O (1.5V or 1.8V nominal)

- 25–60Ω matched impedance outputs

- 2.5VV<sub>EXT</sub>, 1.8VV<sub>DD</sub>, 1.5V or 1.8VV<sub>DDQ</sub> I/O

- On-die termination (ODT) R<sub>TT</sub>

## Options<sup>1</sup>

|                                                                                                                                                                                                                                | <b>Marking</b>            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| • Clock cycle timing <ul style="list-style-type: none"><li>– 1.875ns @ t<sub>RC</sub> = 15ns</li><li>– 2.5ns @ t<sub>RC</sub> = 15ns</li><li>– 2.5ns @ t<sub>RC</sub> = 20ns</li><li>– 3.3ns @ t<sub>RC</sub> = 20ns</li></ul> | -18<br>-25E<br>-25<br>-33 |

| • Configuration <ul style="list-style-type: none"><li>– 64 Meg x 9</li><li>– 32 Meg x 18</li></ul>                                                                                                                             | 64M9<br>32M18             |

| • Operating temperature range <ul style="list-style-type: none"><li>– Commercial (0° to +95°C)</li><li>– Industrial (T<sub>C</sub> = -40°C to +95°C; T<sub>A</sub> = -40°C to +85°C)</li></ul>                                 | None<br>IT                |

| • Package <ul style="list-style-type: none"><li>– 144-ball µBGA</li><li>– 144-ball µBGA (Pb-free)</li><li>– 144-ball FBGA</li><li>– 144-ball FBGA (Pb-free)</li></ul>                                                          | FM<br>BM<br>TR<br>SJ      |

| Revision                                                                                                                                                                                                                       | :A/:B                     |

Note: 1. Not all options listed can be combined to define an offered product. Use the part catalog search on [www.micron.com](http://www.micron.com) for available offerings.

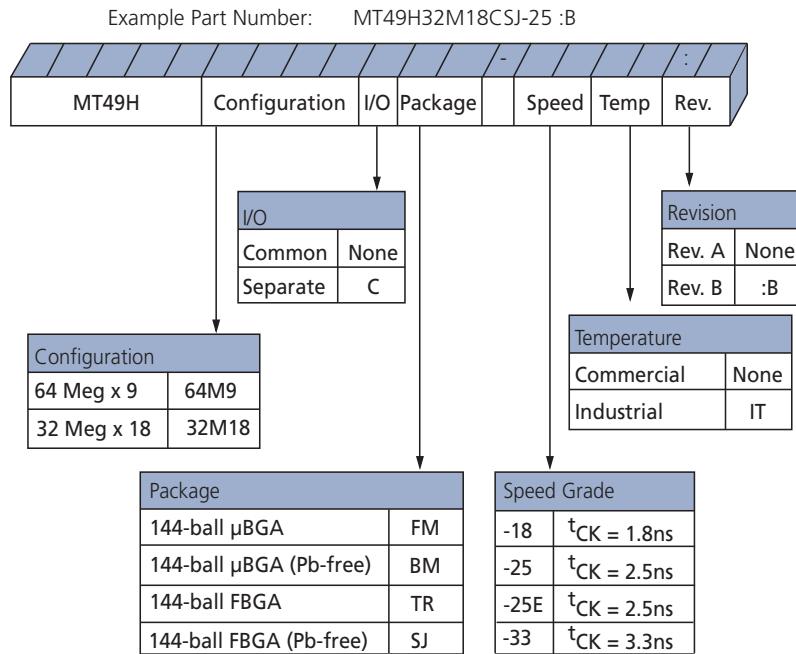

**Figure 1: Part Numbers**

# BGA Marking Decoder

Due to space limitations, BGA-packaged components have an abbreviated part marking that is different from the part number. Micron's BGA Part Marking Decoder is available on Micron's Web site at [www.micron.com](http://www.micron.com).

## Contents

|                                                        |    |

|--------------------------------------------------------|----|

| General Description .....                              | 7  |

| Functional Block Diagrams .....                        | 8  |

| Ball Assignments and Descriptions .....                | 10 |

| Package Dimensions .....                               | 14 |

| Electrical Specifications – I <sub>DD</sub> .....      | 16 |

| Electrical Specifications – AC and DC .....            | 19 |

| Absolute Maximum Ratings .....                         | 19 |

| AC and DC Operating Conditions .....                   | 19 |

| Input Slew Rate Derating .....                         | 22 |

| Temperature and Thermal Impedance .....                | 28 |

| Commands .....                                         | 30 |

| MODE REGISTER SET (MRS) .....                          | 31 |

| Configuration Tables .....                             | 33 |

| Burst Length (BL) .....                                | 33 |

| Address Multiplexing .....                             | 34 |

| DLL RESET .....                                        | 35 |

| Drive Impedance Matching .....                         | 35 |

| On-Die Termination (ODT) .....                         | 35 |

| WRITE .....                                            | 37 |

| READ .....                                             | 38 |

| AUTO REFRESH (AREF) .....                              | 39 |

| Operations .....                                       | 40 |

| INITIALIZATION .....                                   | 40 |

| WRITE .....                                            | 43 |

| READ .....                                             | 47 |

| AUTO REFRESH .....                                     | 52 |

| On-Die Termination .....                               | 53 |

| Multiplexed Address Mode .....                         | 55 |

| Address Mapping in Multiplexed Address Mode .....      | 58 |

| Configuration Tables in Multiplexed Address Mode ..... | 58 |

| REFRESH Command in Multiplexed Address Mode .....      | 59 |

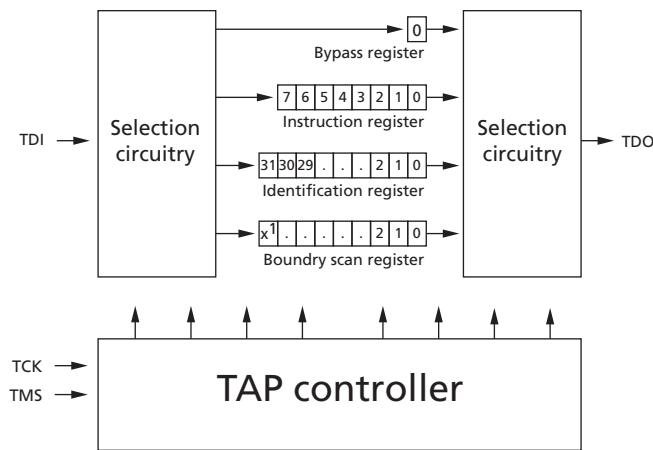

| IEEE 1149.1 Serial Boundary Scan (JTAG) .....          | 63 |

| Disabling the JTAG Feature .....                       | 63 |

| Test Access Port (TAP) .....                           | 63 |

| Test Clock (TCK) .....                                 | 63 |

| Test Mode Select (TMS) .....                           | 63 |

| Test Data-In (TDI) .....                               | 64 |

| Test Data-Out (TDO) .....                              | 64 |

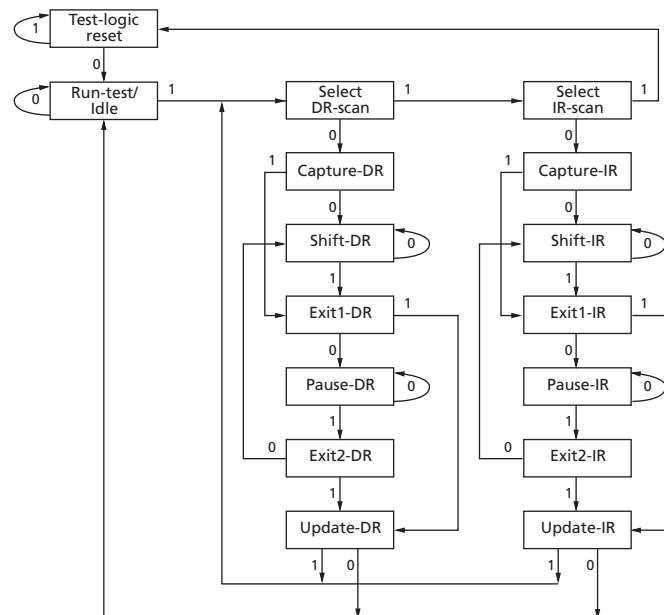

| TAP Controller .....                                   | 64 |

| Test-Logic-Reset .....                                 | 64 |

| Run-Test/Idle .....                                    | 64 |

| Select-DR-Scan .....                                   | 64 |

| Capture-DR .....                                       | 64 |

| Shift-DR .....                                         | 64 |

| Exit1-DR, Pause-DR, and Exit2-DR .....                 | 65 |

| Update-DR .....                                        | 65 |

| Instruction Register States .....                      | 65 |

| Performing a TAP RESET .....                           | 66 |

| TAP Registers .....                                    | 66 |

| Instruction Register .....                             | 66 |

|                                    |    |

|------------------------------------|----|

| Bypass Register .....              | 66 |

| Boundary Scan Register .....       | 67 |

| Identification (ID) Register ..... | 67 |

| TAP Instruction Set .....          | 67 |

| EXTEST .....                       | 68 |

| IDCODE .....                       | 68 |

| High-Z .....                       | 68 |

| CLAMP .....                        | 68 |

| SAMPLE/PRELOAD .....               | 68 |

| BYPASS .....                       | 69 |

| Reserved for Future Use .....      | 69 |

| Revision History .....             | 73 |

| Rev. I – 06/15 .....               | 73 |

| Rev. H – 10/12 .....               | 73 |

| Rev. G – 09/10 .....               | 73 |

| Rev. F – 06/09 .....               | 73 |

| Rev. E – 05/09 .....               | 73 |

| Rev. D – 06/08 .....               | 73 |

| Rev. C – 09/07 .....               | 73 |

| Rev. B – 05/07 .....               | 74 |

| Rev. A – 02/06 .....               | 74 |

| Rev. 1 – 09/04 .....               | 74 |

## List of Figures

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| Figure 1: Part Numbers .....                                                        | 2  |

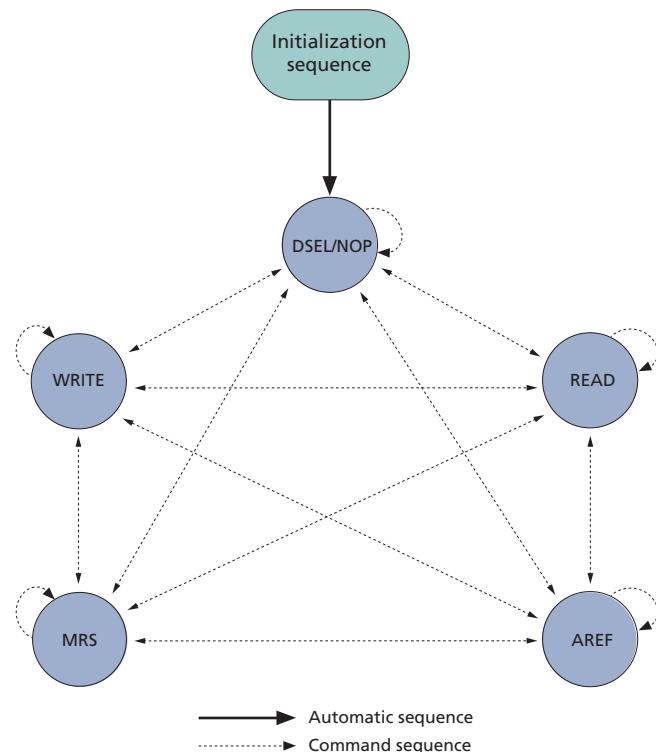

| Figure 2: State Diagram .....                                                       | 7  |

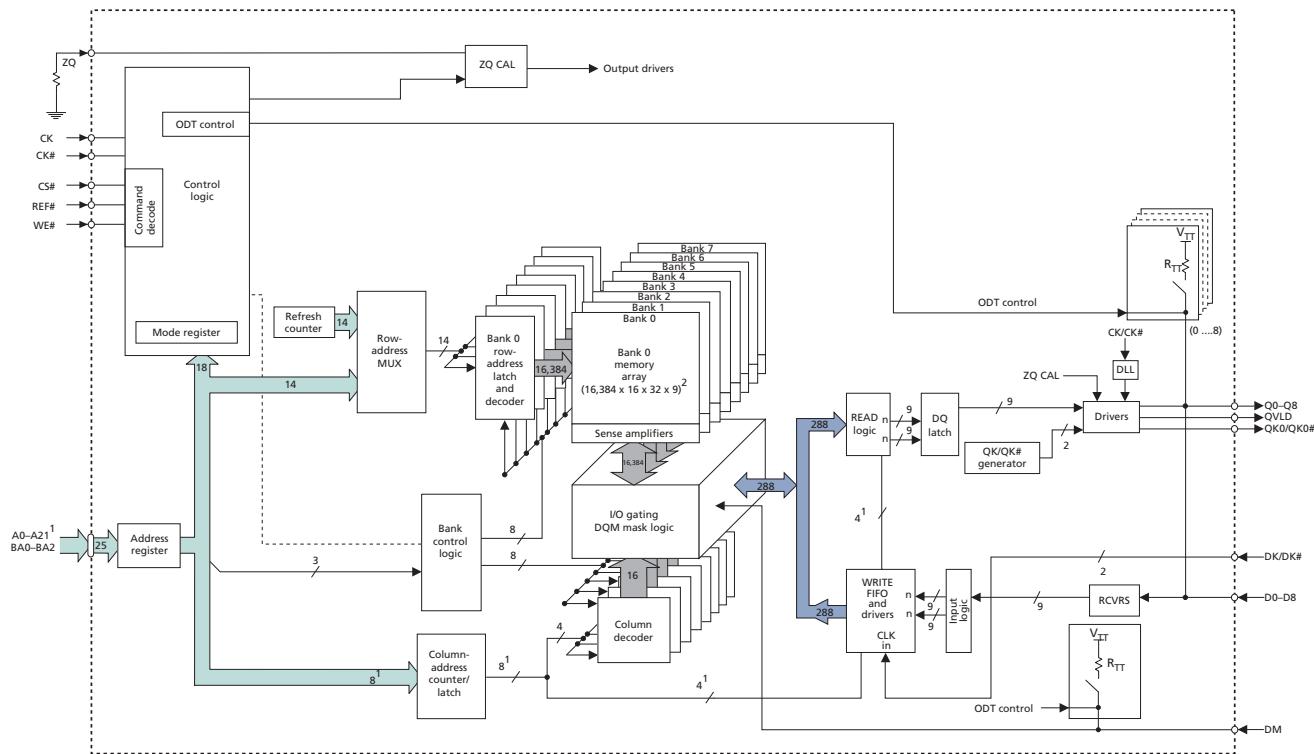

| Figure 3: Functional Block Diagram – 64 Meg x 9 .....                               | 8  |

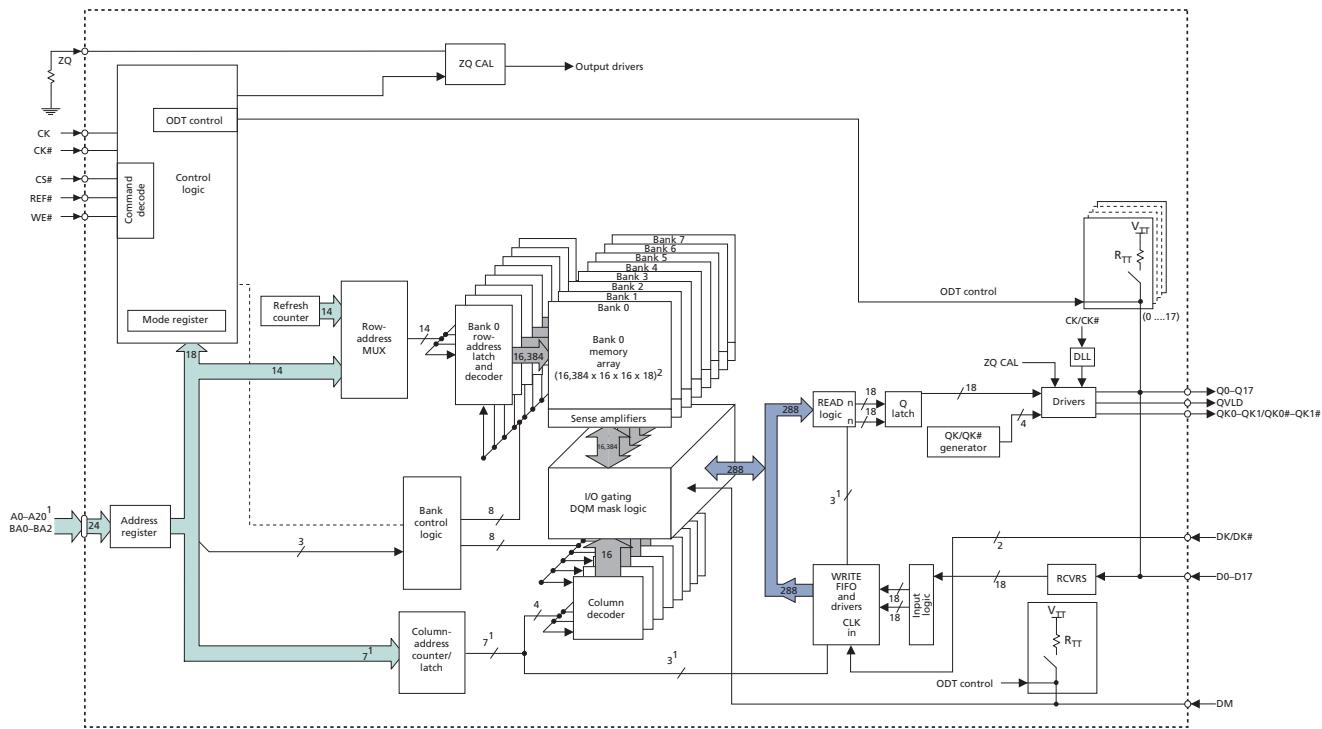

| Figure 4: Functional Block Diagram – 32 Meg x 18 .....                              | 9  |

| Figure 5: 144-Ball µBGA .....                                                       | 14 |

| Figure 6: 144-Ball FBGA .....                                                       | 15 |

| Figure 7: Clock Input .....                                                         | 21 |

| Figure 8: Nominal $t_{AS}/t_{CS}/t_{DS}$ and $t_{AH}/t_{CH}/t_{DH}$ Slew Rate ..... | 25 |

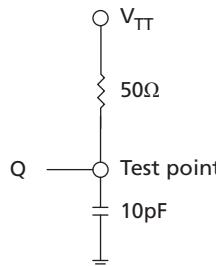

| Figure 9: Example Temperature Test Point Location .....                             | 29 |

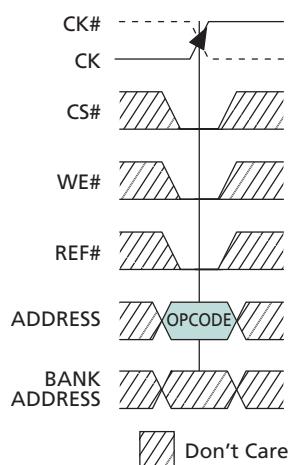

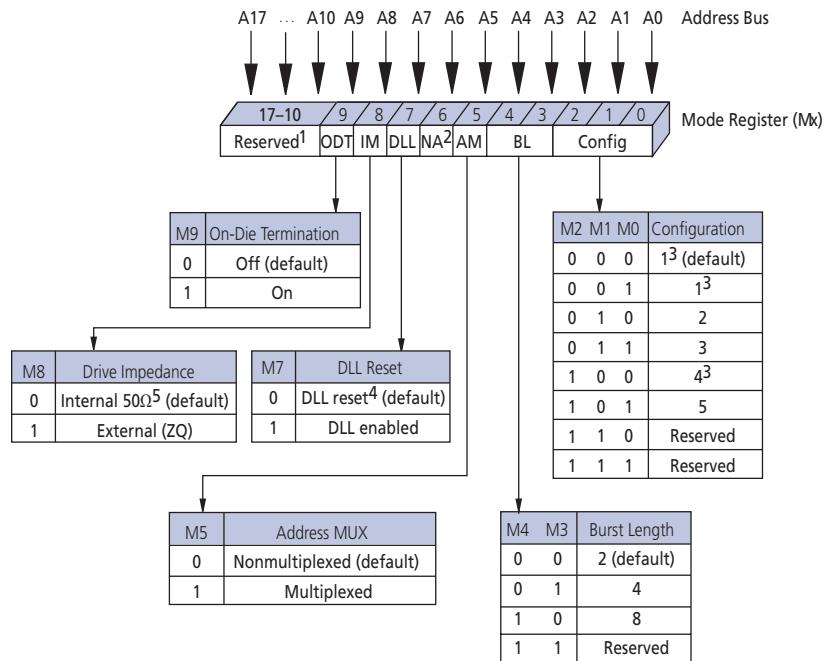

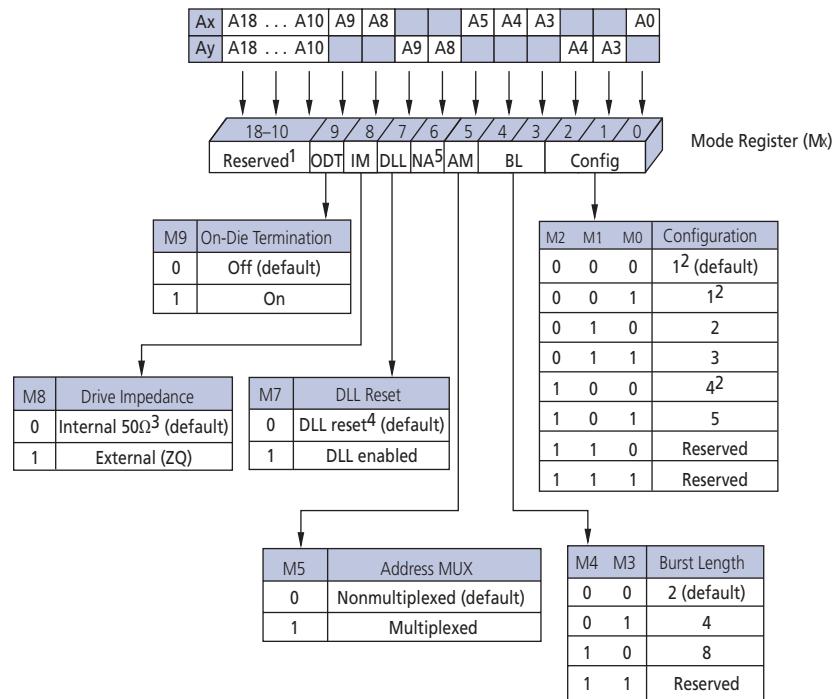

| Figure 10: Mode Register Set .....                                                  | 31 |

| Figure 11: Mode Register Definition in Nonmultiplexed Address Mode .....            | 32 |

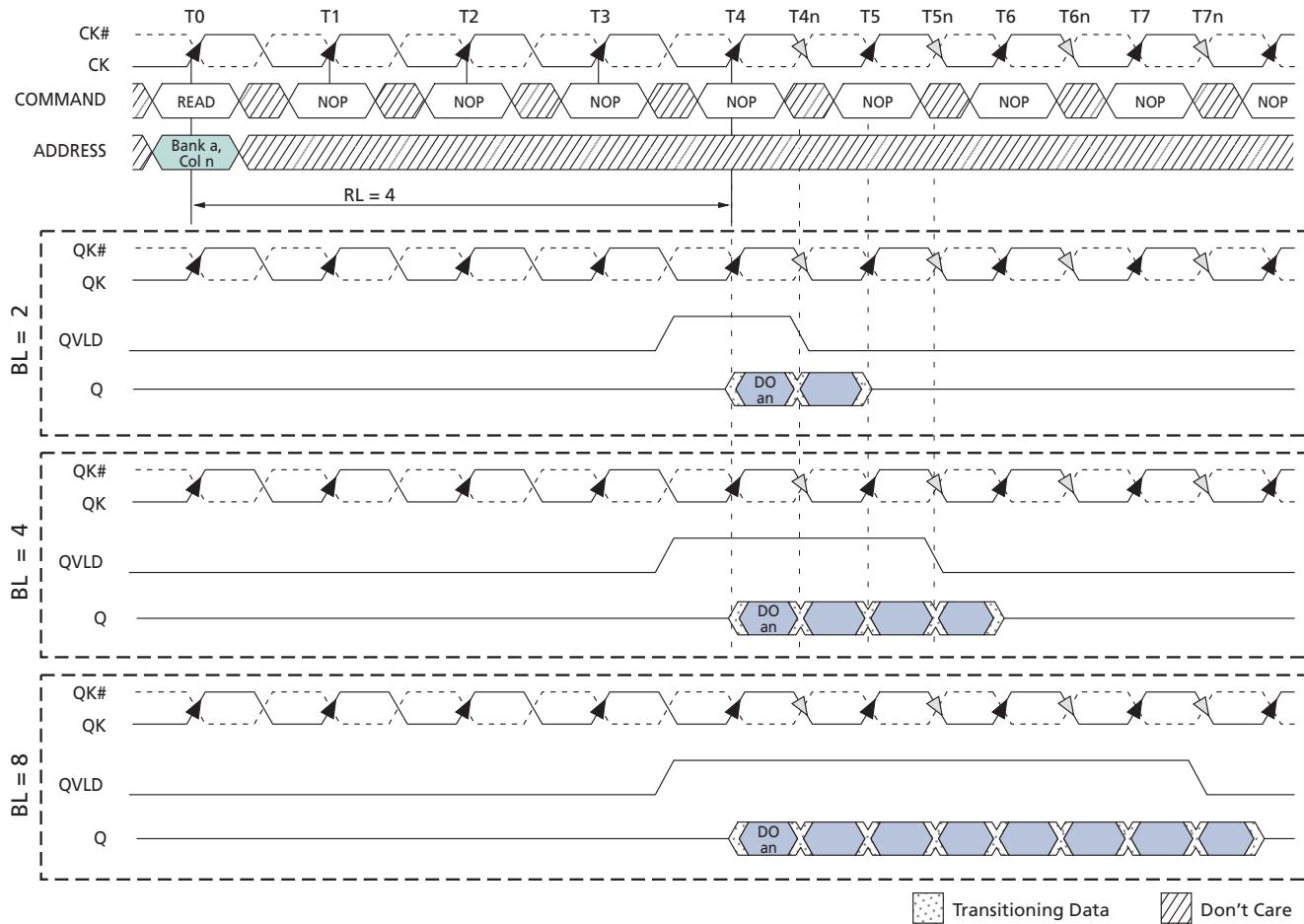

| Figure 12: Read Burst Lengths .....                                                 | 34 |

| Figure 13: On-Die Termination-Equivalent Circuit .....                              | 36 |

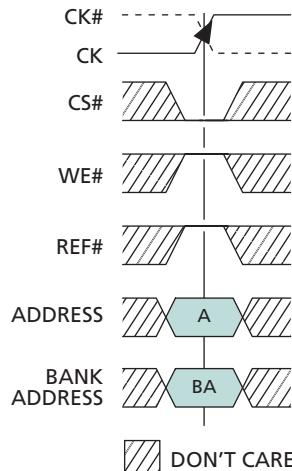

| Figure 14: WRITE Command .....                                                      | 37 |

| Figure 15: READ Command .....                                                       | 38 |

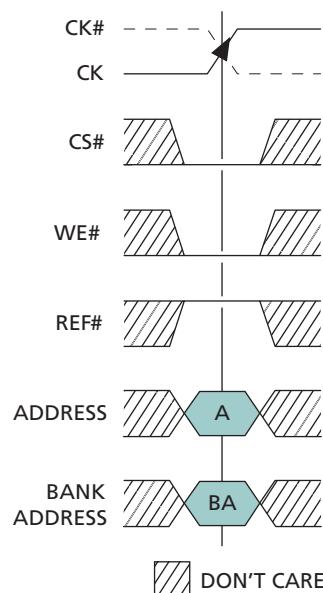

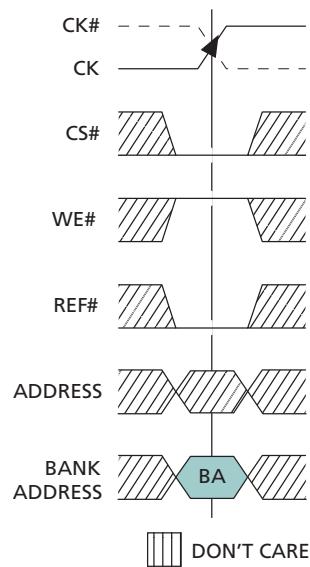

| Figure 16: AUTO REFRESH Command .....                                               | 39 |

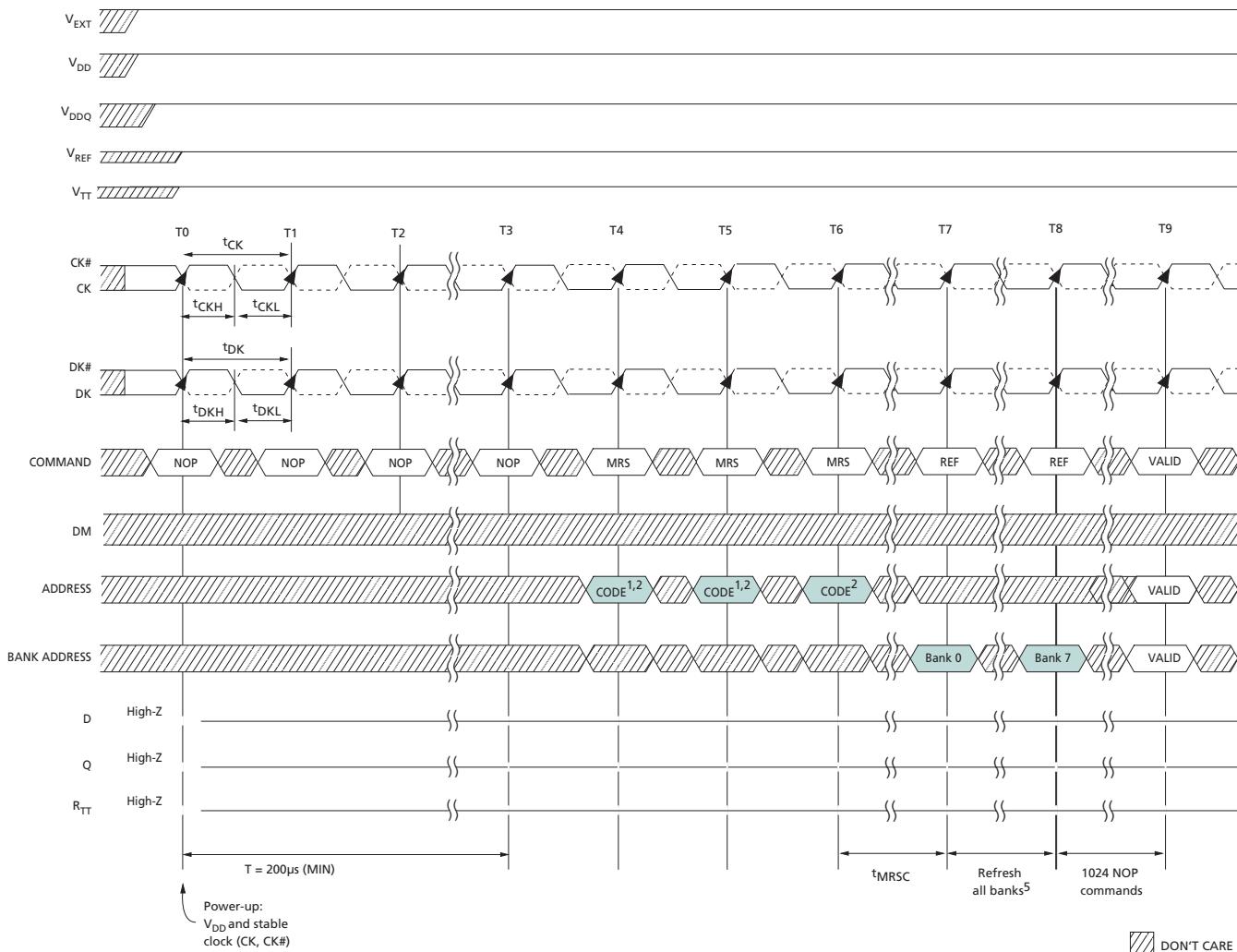

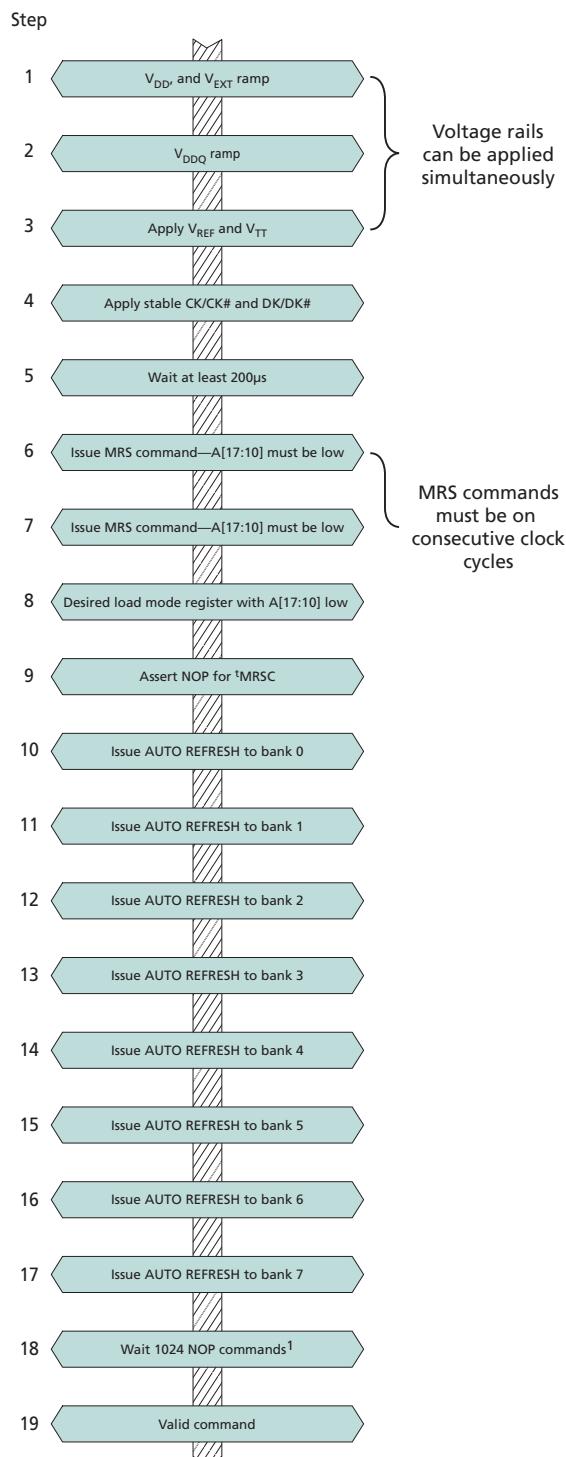

| Figure 17: Power-Up/Initialization Sequence .....                                   | 41 |

| Figure 18: Power-Up/Initialization Flow Chart .....                                 | 42 |

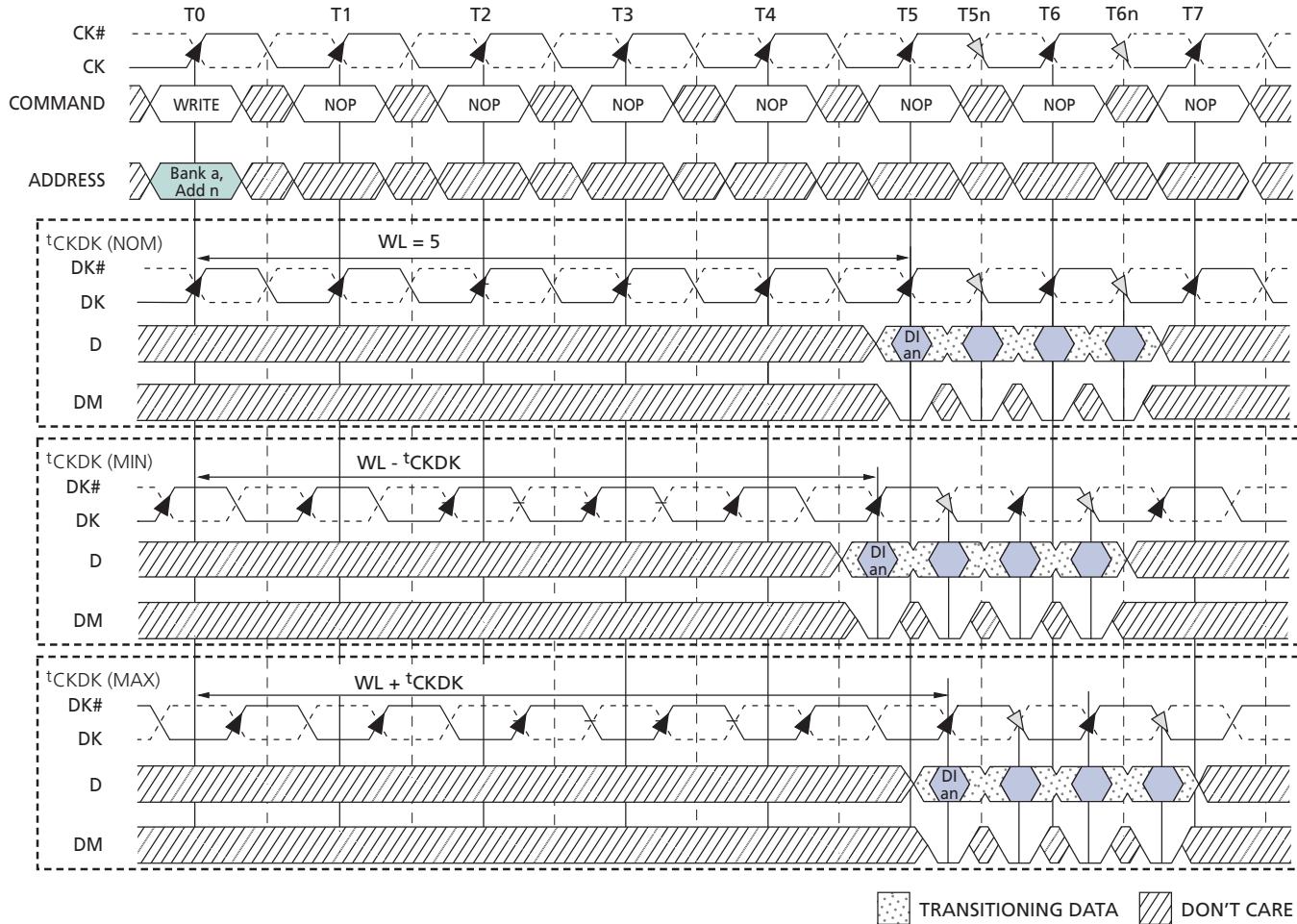

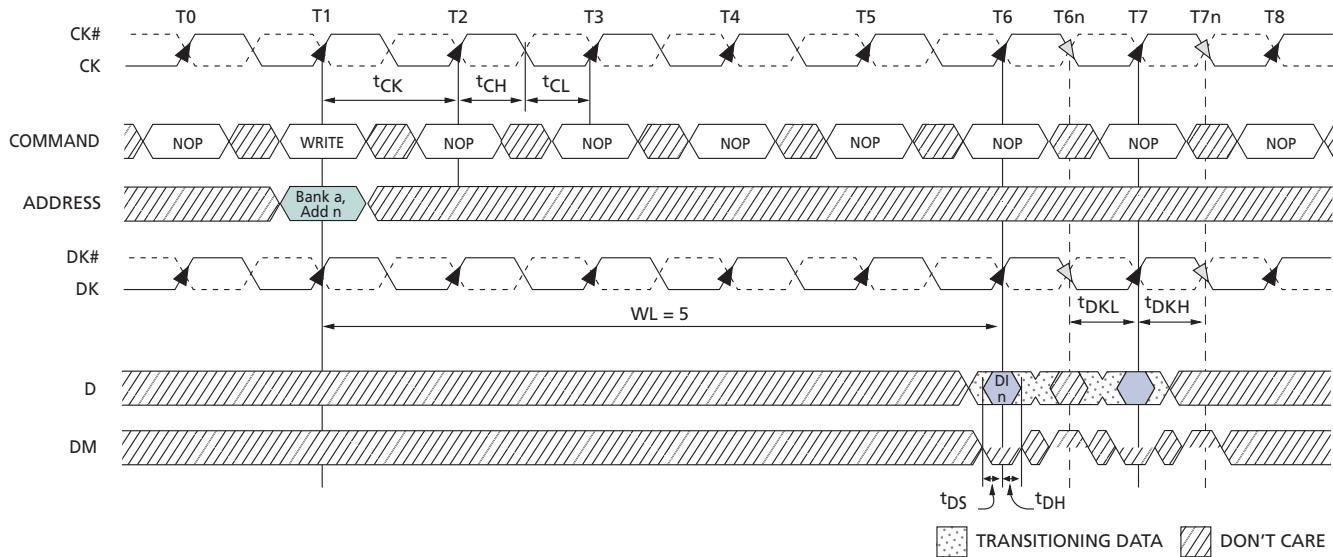

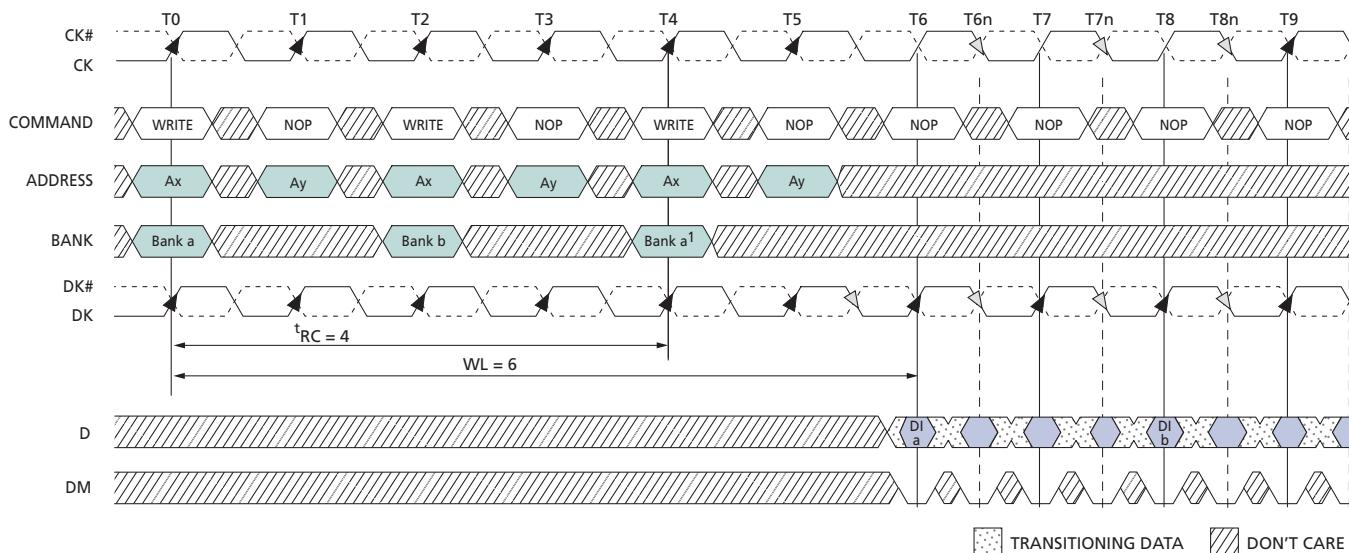

| Figure 19: WRITE Burst .....                                                        | 43 |

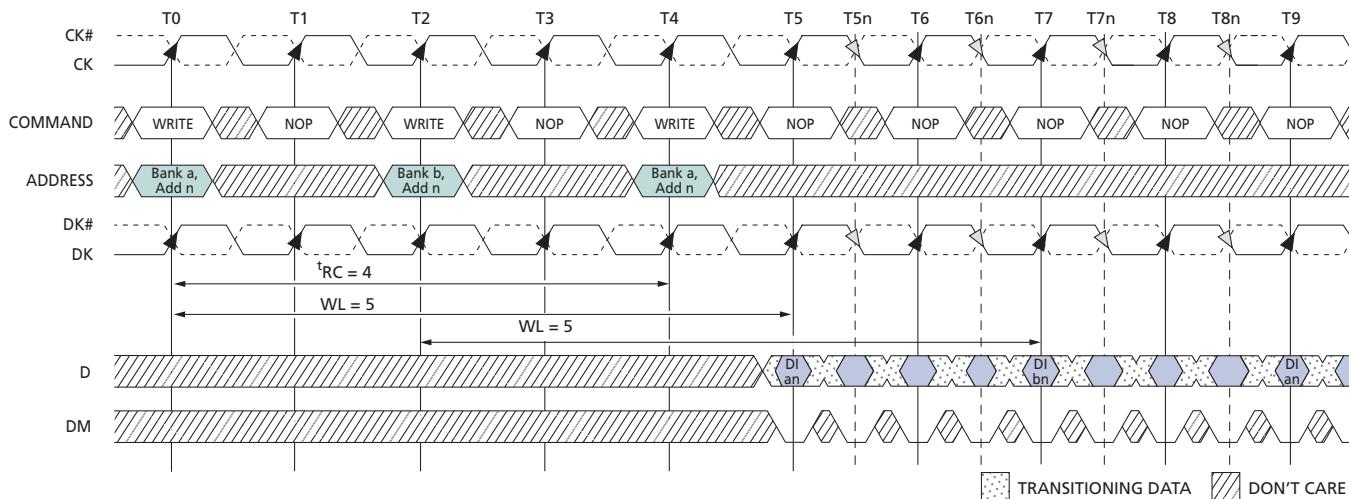

| Figure 20: Consecutive WRITE-to-WRITE .....                                         | 44 |

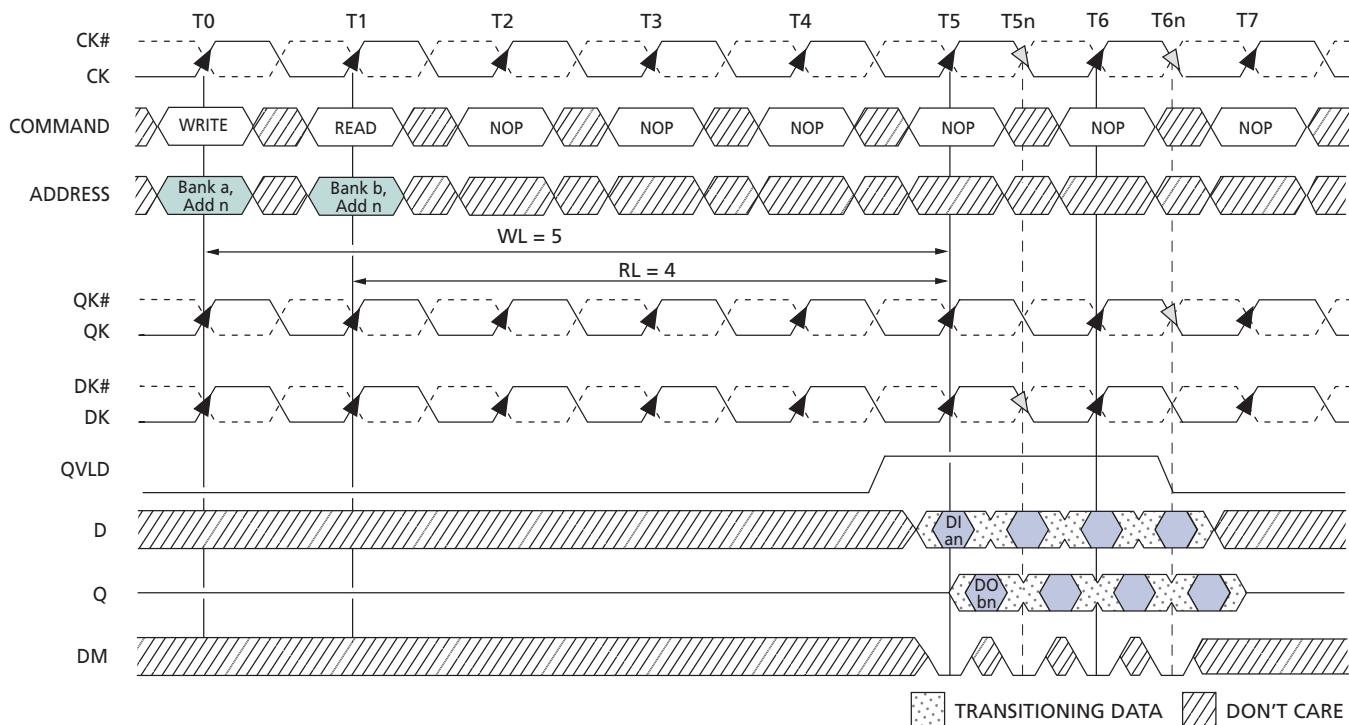

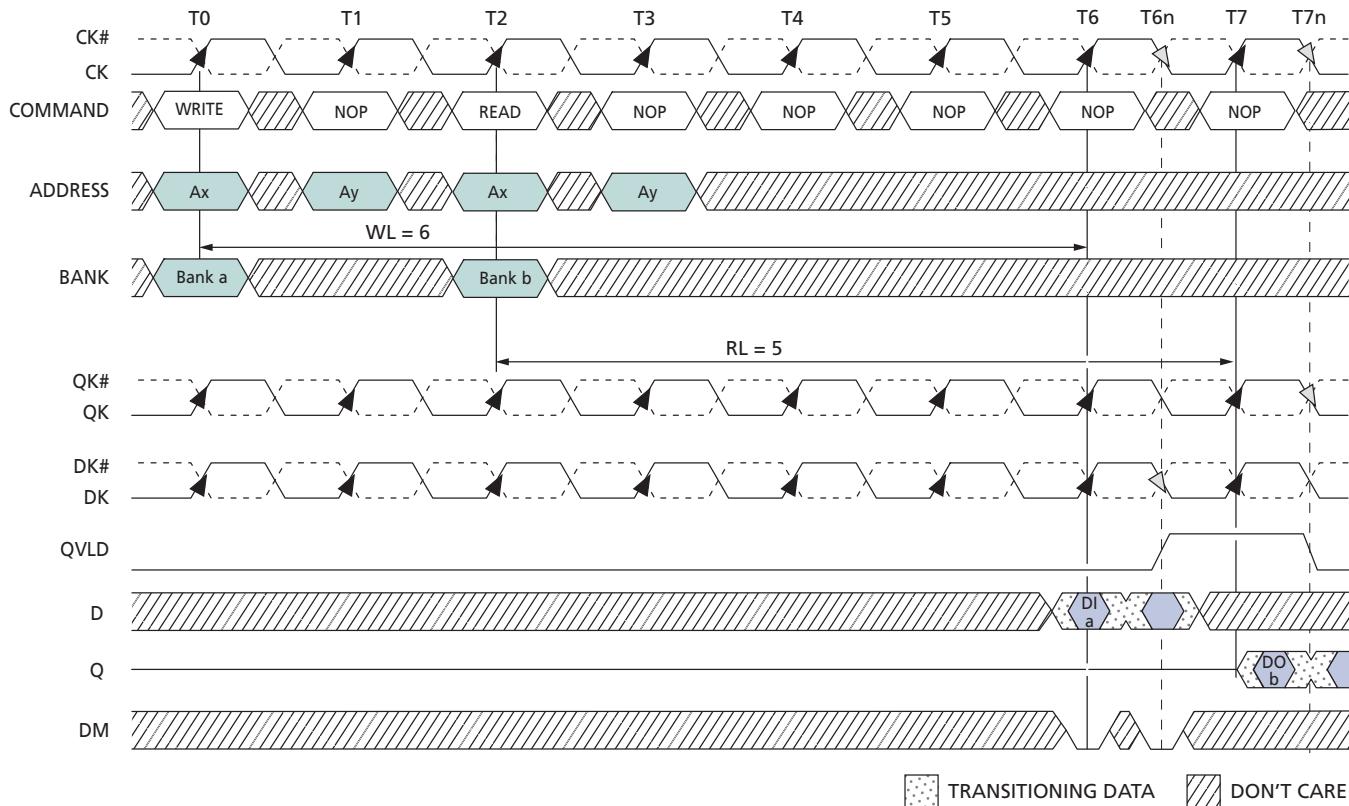

| Figure 21: WRITE-to-READ .....                                                      | 45 |

| Figure 22: WRITE – DM Operation .....                                               | 46 |

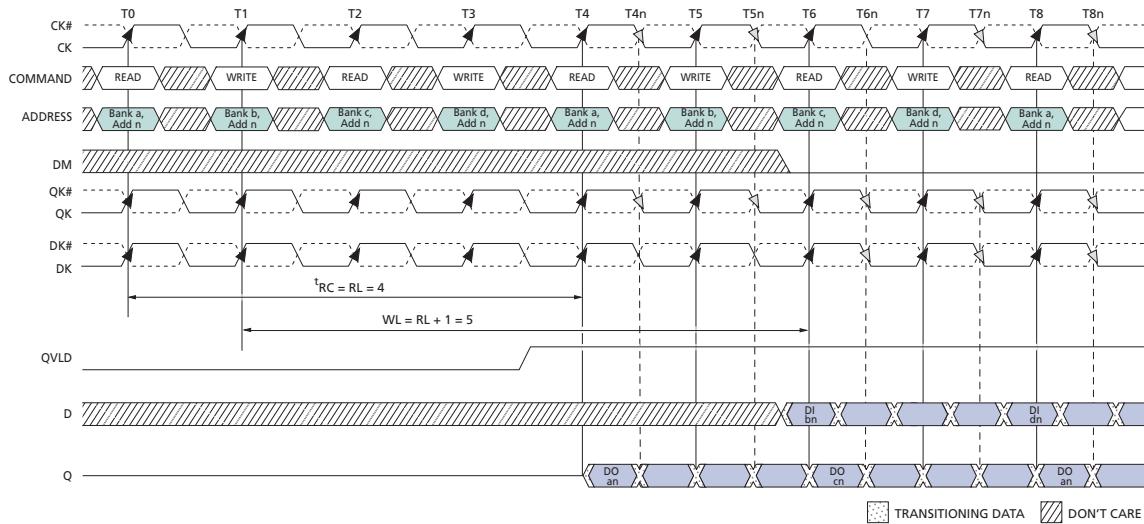

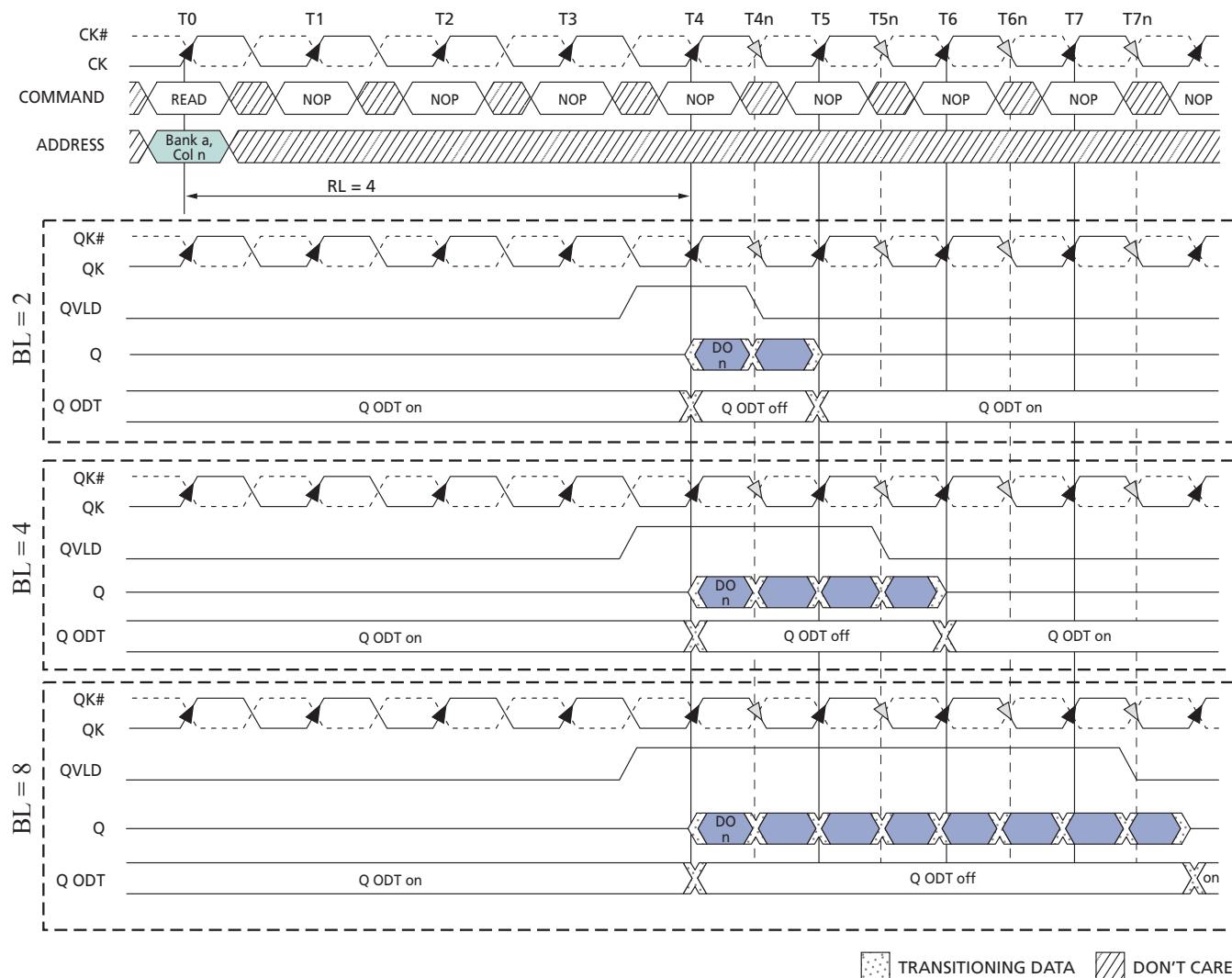

| Figure 23: Basic READ Burst Timing .....                                            | 47 |

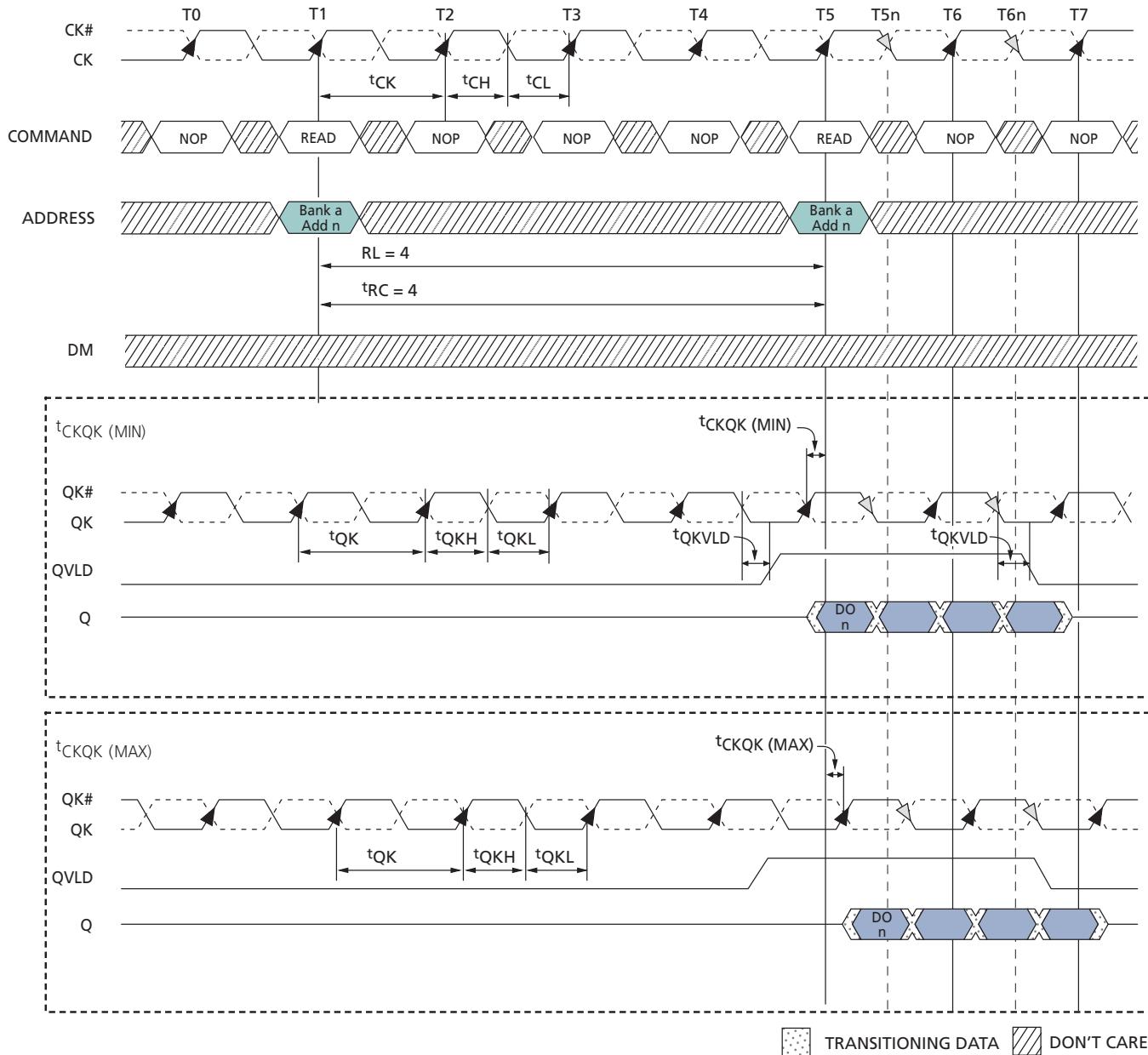

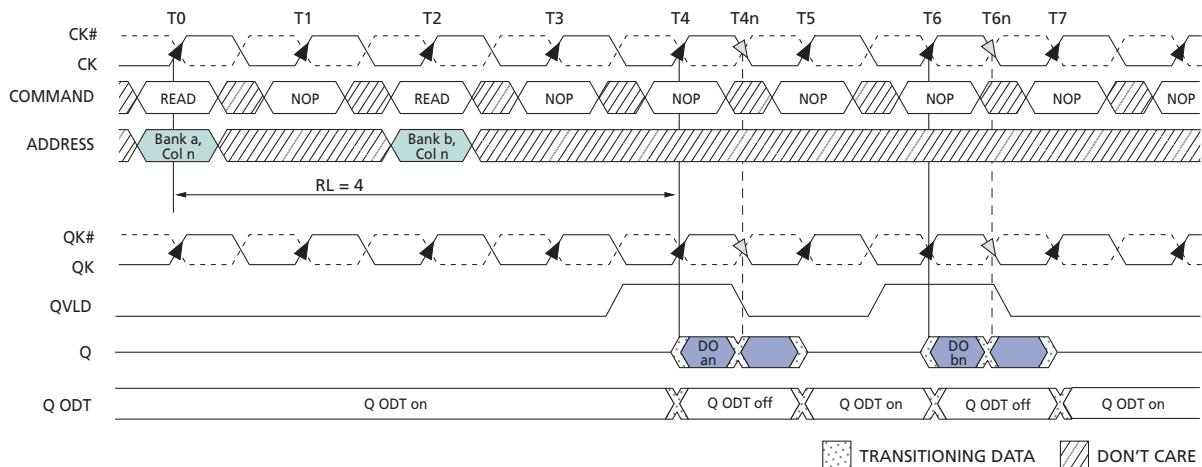

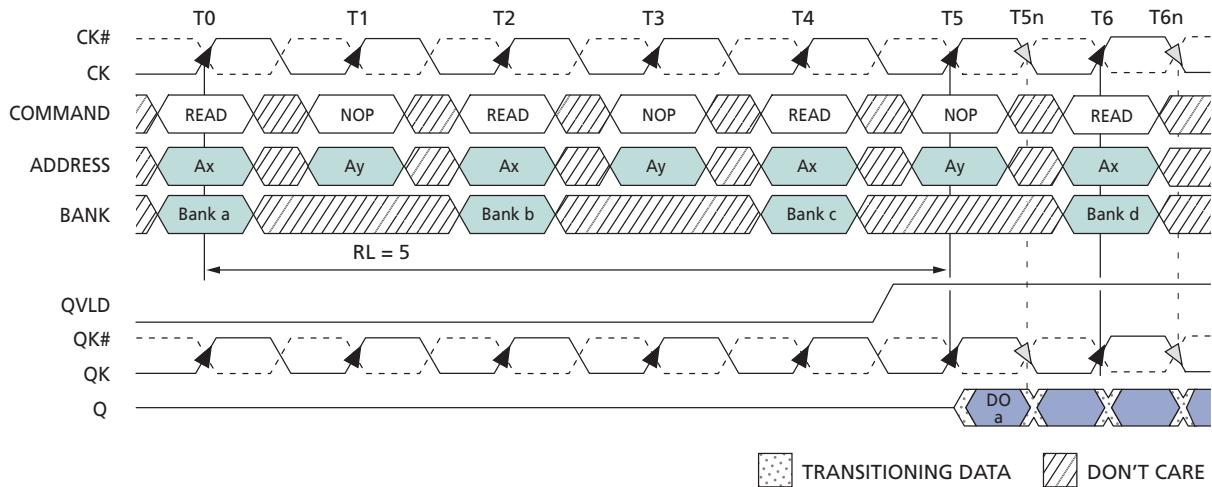

| Figure 24: Consecutive READ Bursts (BL = 2) .....                                   | 48 |

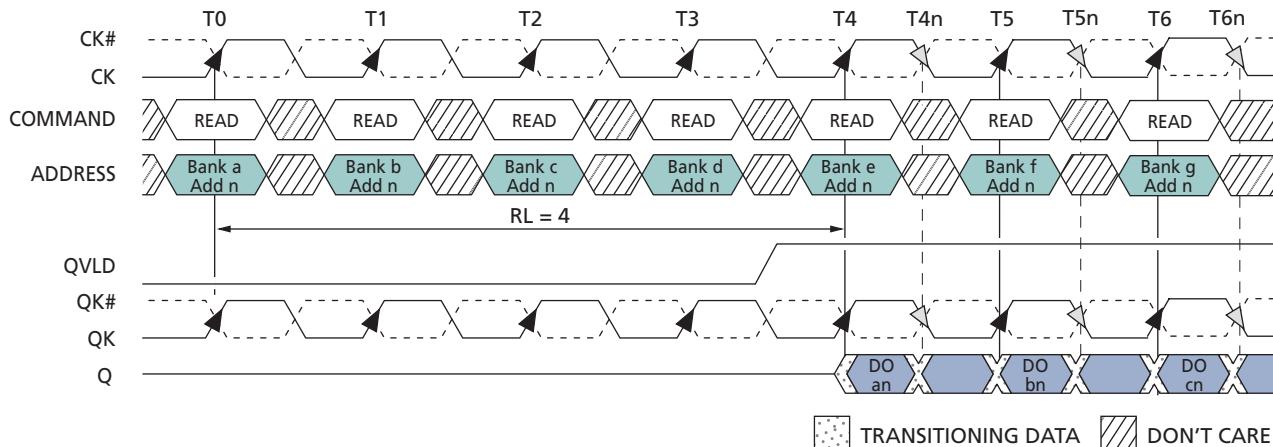

| Figure 25: Consecutive READ Bursts (BL = 4) .....                                   | 48 |

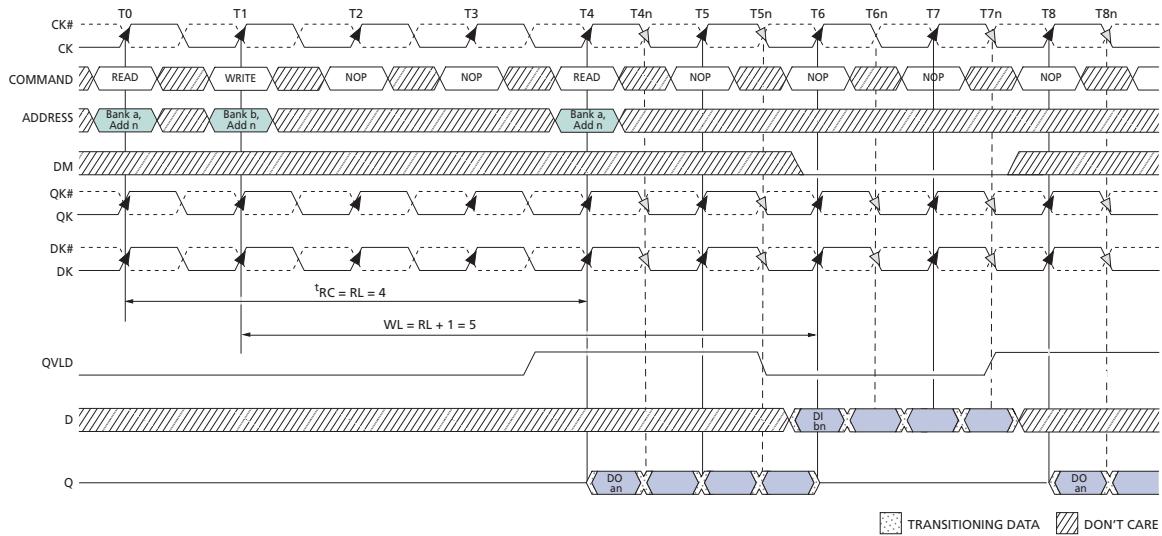

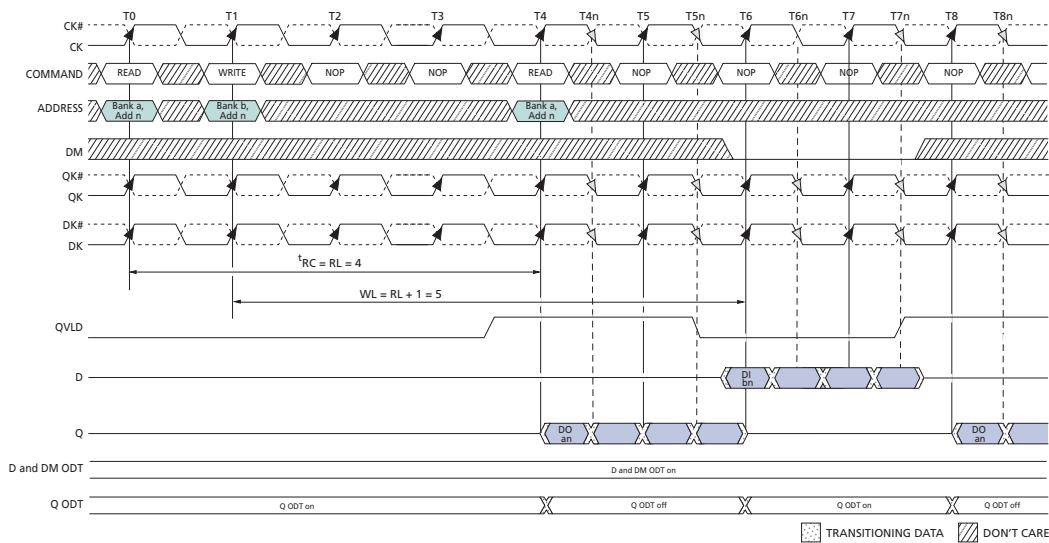

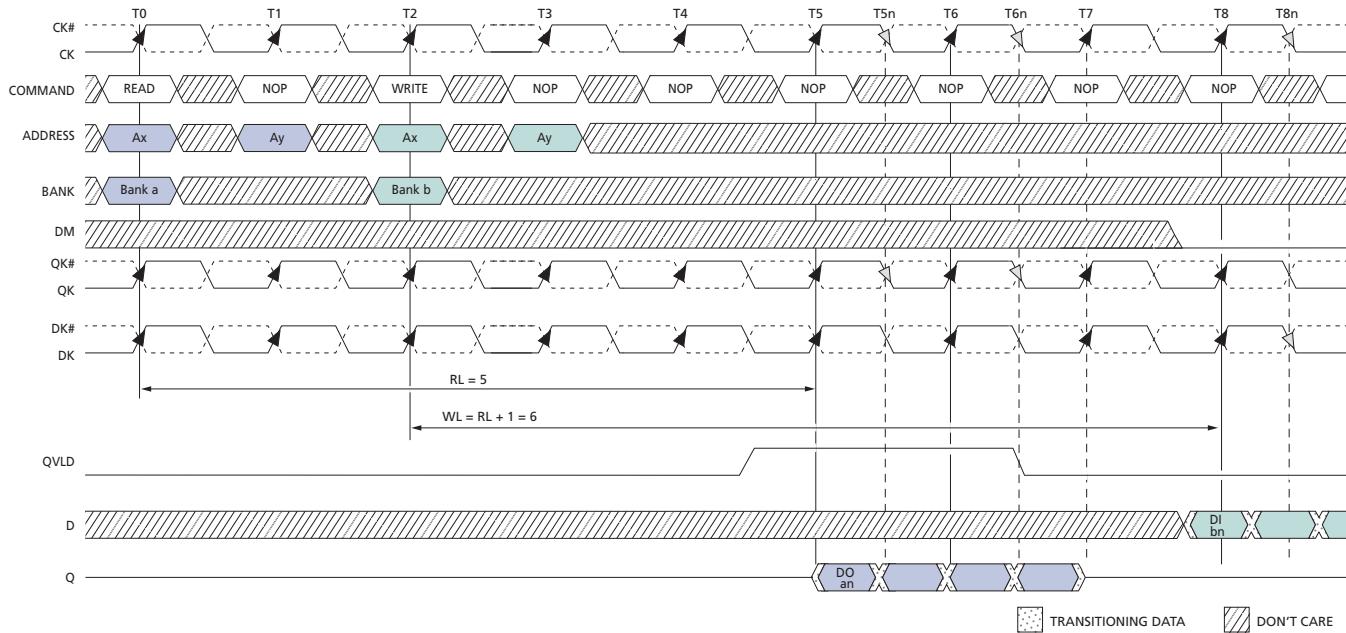

| Figure 26: READ-to-WRITE .....                                                      | 49 |

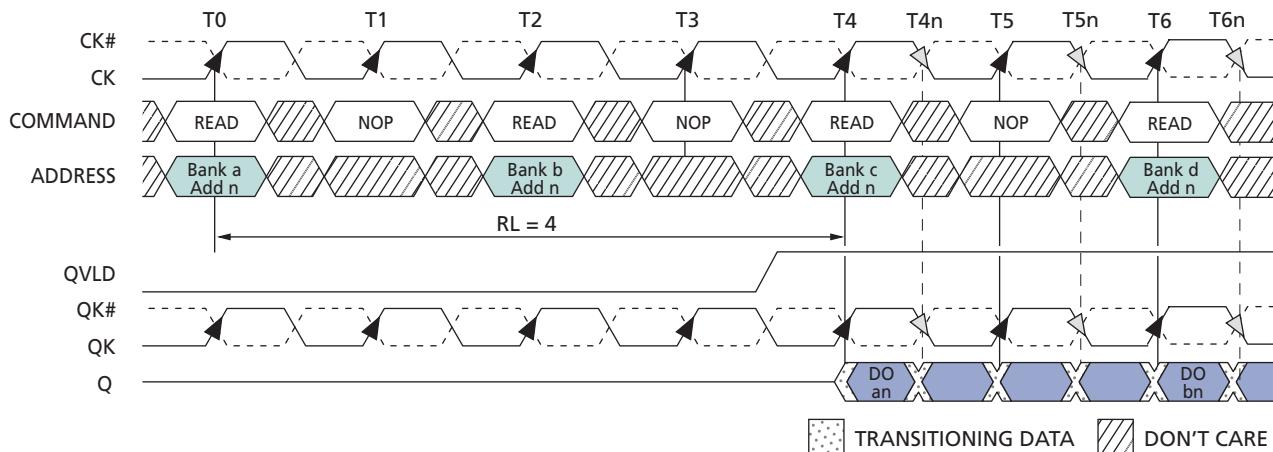

| Figure 27: READ/WRITE Interleave .....                                              | 49 |

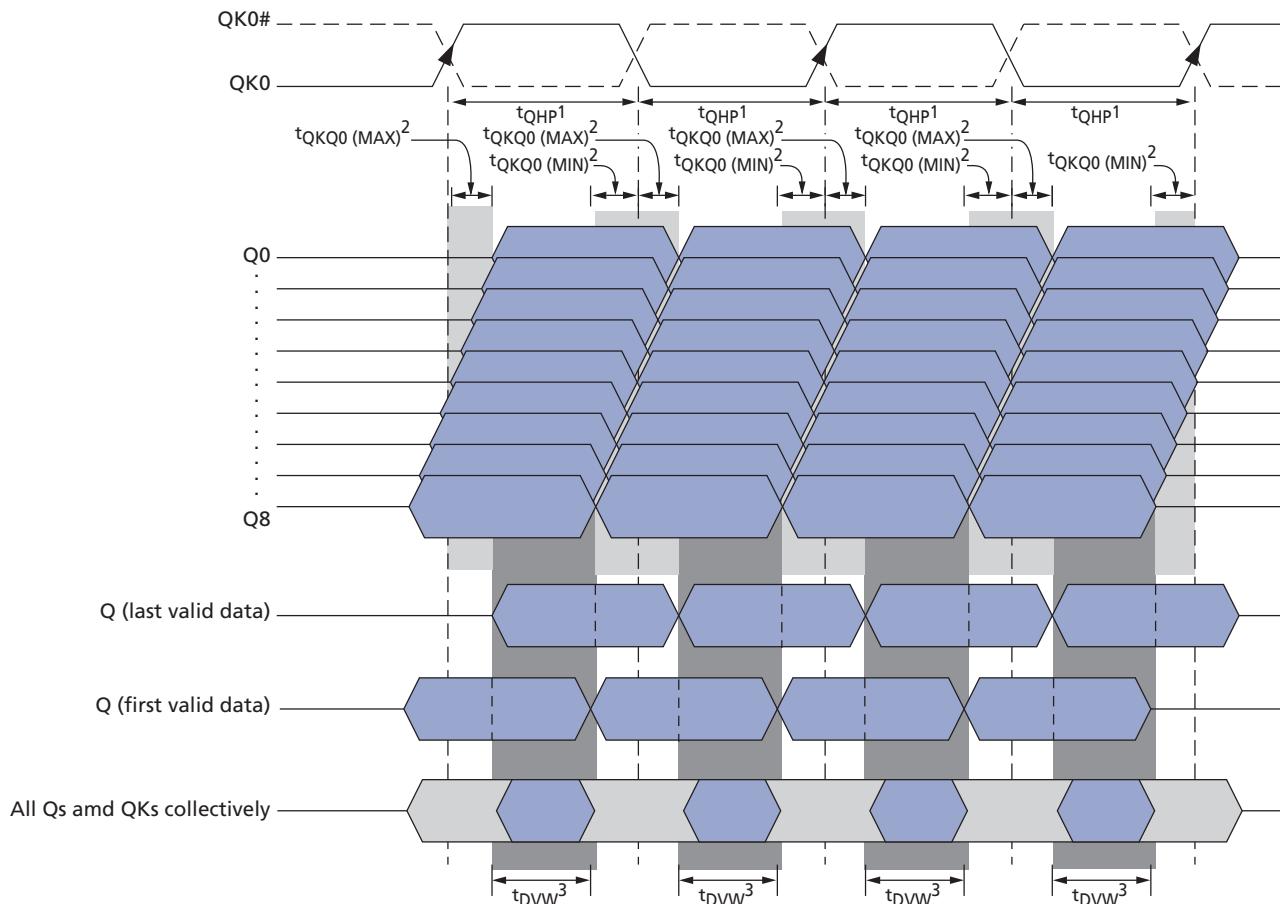

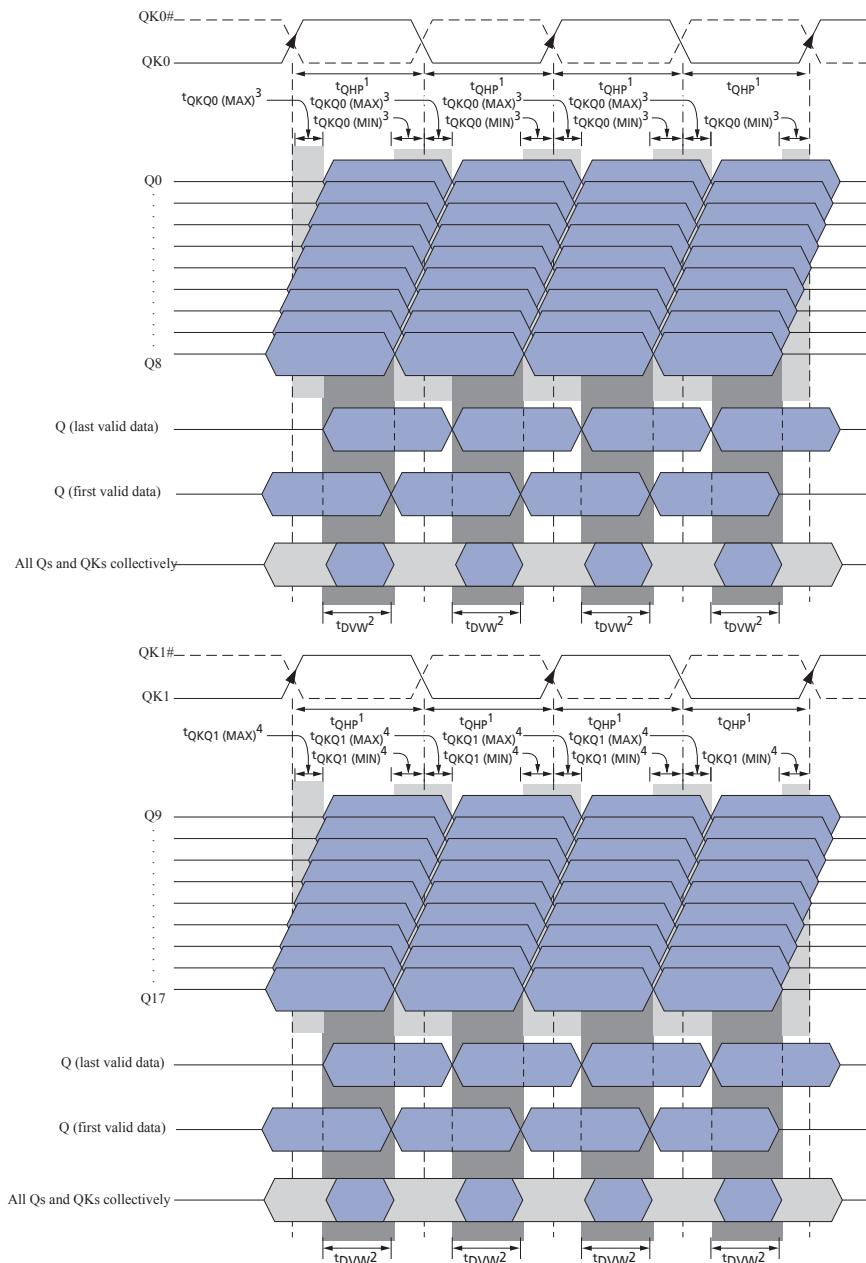

| Figure 28: Read Data Valid Window for x9 Device .....                               | 50 |

| Figure 29: Read Data Valid Window for x18 Device .....                              | 51 |

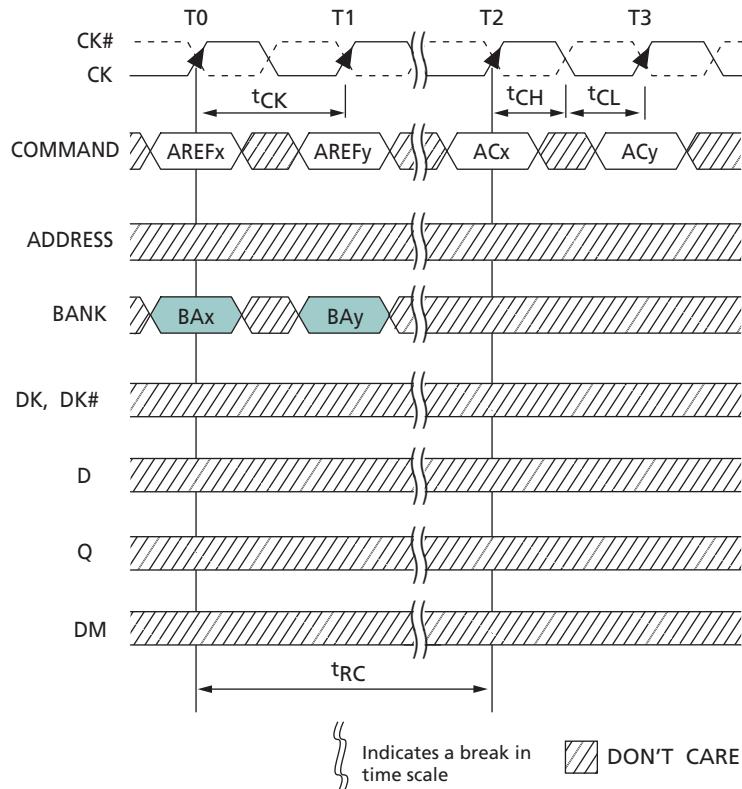

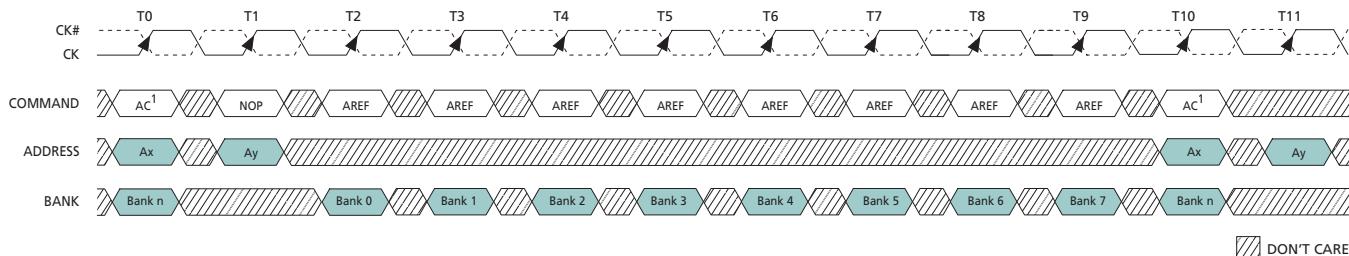

| Figure 30: AUTO REFRESH Cycle .....                                                 | 52 |

| Figure 31: READ Burst with ODT .....                                                | 53 |

| Figure 32: READ-NOP-READ with ODT .....                                             | 54 |

| Figure 33: READ-to-WRITE with ODT .....                                             | 54 |

| Figure 34: Command Description in Multiplexed Address Mode .....                    | 55 |

| Figure 35: Power-Up/Initialization Sequence in Multiplexed Address Mode .....       | 56 |

| Figure 36: Mode Register Definition in Multiplexed Address Mode .....               | 57 |

| Figure 37: Burst REFRESH Operation with Multiplexed Addressing .....                | 59 |

| Figure 38: Consecutive WRITE Bursts with Multiplexed Addressing .....               | 59 |

| Figure 39: WRITE-to-READ with Multiplexed Addressing .....                          | 60 |

| Figure 40: Consecutive READ Burst with Multiplexed Addressing .....                 | 61 |

| Figure 41: READ-to-WRITE with Multiplexed Addressing .....                          | 62 |

| Figure 42: TAP Controller State Diagram .....                                       | 65 |

| Figure 43: TAP Controller Block Diagram .....                                       | 66 |

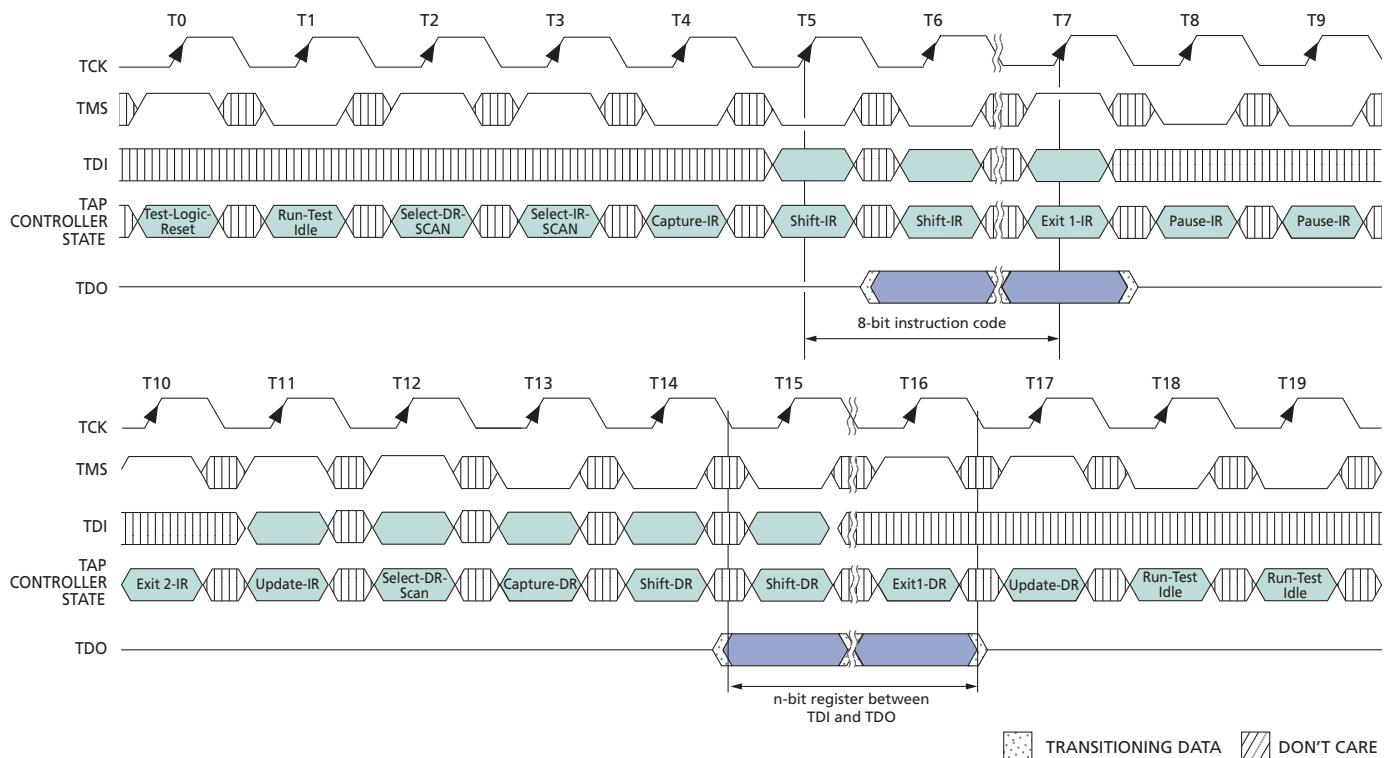

| Figure 44: JTAG Operation – Loading Instruction Code and Shifting Out Data .....    | 69 |

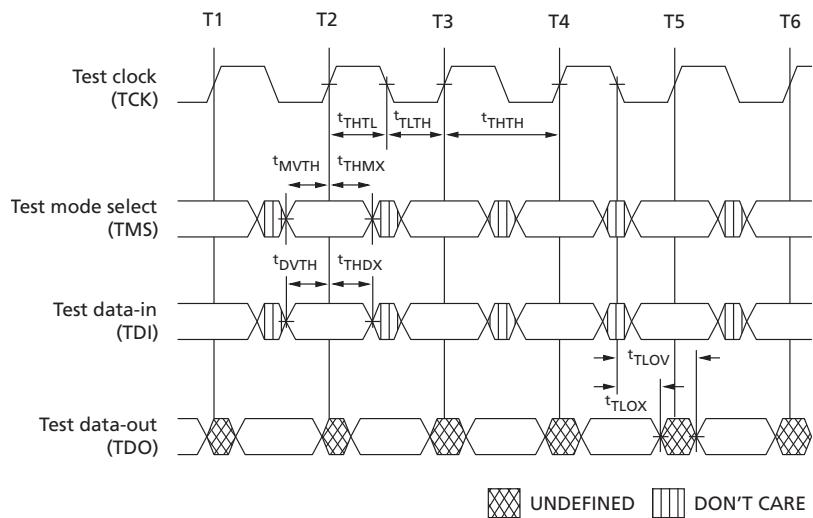

| Figure 45: TAP Timing .....                                                         | 70 |

## List of Tables

|                                                                                           |    |

|-------------------------------------------------------------------------------------------|----|

| Table 1: 64 Meg x 9 Ball Assignments (Top View) 144-Ball $\mu$ BGA/FBGA .....             | 10 |

| Table 2: 32 Meg x 18 Ball Assignments (Top View) 144-Ball $\mu$ BGA/FBGA .....            | 11 |

| Table 3: Ball Descriptions .....                                                          | 12 |

| Table 4: $I_{DD}$ Operating Conditions and Maximum Limits – Rev. A .....                  | 16 |

| Table 5: $I_{DD}$ Operating Conditions and Maximum Limits – Rev. B .....                  | 17 |

| Table 6: Absolute Maximum Ratings .....                                                   | 19 |

| Table 7: DC Electrical Characteristics and Operating Conditions .....                     | 19 |

| Table 8: Input AC Logic Levels .....                                                      | 20 |

| Table 9: Differential Input Clock Operating Conditions .....                              | 21 |

| Table 10: Address and Command Setup and Hold Derating Values .....                        | 23 |

| Table 11: Data Setup and Hold Derating Values .....                                       | 24 |

| Table 12: Capacitance – $\mu$ BGA .....                                                   | 25 |

| Table 13: Capacitance – FBGA .....                                                        | 25 |

| Table 14: AC Electrical Characteristics: -18, -25E, -25, -33 .....                        | 26 |

| Table 15: Temperature Limits .....                                                        | 28 |

| Table 16: Thermal Impedance .....                                                         | 29 |

| Table 17: Description of Commands .....                                                   | 30 |

| Table 18: Command Table .....                                                             | 30 |

| Table 19: Cycle Time and READ/WRITE Latency Configuration Table .....                     | 33 |

| Table 20: Address Widths at Different Burst Lengths .....                                 | 33 |

| Table 21: On-Die Termination DC Parameters .....                                          | 36 |

| Table 22: Address Mapping in Multiplexed Address Mode .....                               | 58 |

| Table 23: Cycle Time and READ/WRITE Latency Configuration Table in Multiplexed Mode ..... | 58 |

| Table 24: Instruction Codes .....                                                         | 67 |

| Table 25: TAP Input AC Logic Levels .....                                                 | 70 |

| Table 26: TAP AC Electrical Characteristics .....                                         | 70 |

| Table 27: TAP DC Electrical Characteristics and Operating Conditions .....                | 71 |

| Table 28: Identification Register Definitions .....                                       | 71 |

| Table 29: Scan Register Sizes .....                                                       | 71 |

| Table 30: Boundary Scan (Exit) Order .....                                                | 72 |

## General Description

The Micron® reduced latency DRAM (RLDRAM®) 2 is a high-speed memory device designed for high bandwidth data storage—telecommunications, networking, and cache applications, etc. The chip's 8-bank architecture is optimized for sustainable high speed operation.

The double data rate (DDR) separate I/O interface transfers two data words per clock cycle at the I/O balls. The read port has dedicated data outputs to support READ operations, while the write port has dedicated input balls to support WRITE operations. Output data is referenced to the free-running output data clock. This architecture eliminates the need for high-speed bus turnaround.

Commands, addresses, and control signals are registered at every positive edge of the differential input clock, while input data is registered at both positive and negative edges of the input data clock(s).

Read and write accesses to the RLDRAM are burst-oriented. The burst length (BL) is programmable from 2, 4, or 8 by setting the mode register.

The device is supplied with 2.5V and 1.8V for the core and 1.5V or 1.8V for the output drivers.

Bank-scheduled refresh is supported with the row address generated internally.

The 144-ball µBGA/FBGA package is used to enable ultra high-speed data transfer rates and a simple upgrade path from early generation devices.

**Figure 2: State Diagram**

## Functional Block Diagrams

**Figure 3: Functional Block Diagram – 64 Meg x 9**

Notes: 1. Example for BL = 2; column address will be reduced with an increase in burst length.

2.  $32 = (\text{length of burst}) \times 2^{\text{(number of column addresses to WRITE FIFO and READ logic)}}$ .

**Figure 4: Functional Block Diagram – 32 Meg x 18**

Notes:

1. Example for BL = 2; column address will be reduced with an increase in burst length.

2.  $16 = (\text{length of burst}) \times 2^{(\text{number of column addresses to WRITE FIFO and READ logic})}$ .

## Ball Assignments and Descriptions

**Table 1: 64 Meg x 9 Ball Assignments (Top View) 144-Ball µBGA/FBGA**

|          | <b>1</b>         | <b>2</b>         | <b>3</b>         | <b>4</b>  | <b>5</b> | <b>6</b> | <b>7</b> | <b>8</b> | <b>9</b>  | <b>10</b> | <b>11</b> | <b>12</b> |

|----------|------------------|------------------|------------------|-----------|----------|----------|----------|----------|-----------|-----------|-----------|-----------|

| <b>A</b> | $V_{REF}$        | $V_{SS}$         | $V_{EXT}$        | $V_{SS}$  |          |          |          |          | $V_{SS}$  | $V_{EXT}$ | TMS       | TCK       |

| <b>B</b> | $V_{DD}$         | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q0        | D0        | $V_{DD}$  |

| <b>C</b> | $V_{TT}$         | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{DDQ}$ |          |          |          |          | $V_{DDQ}$ | Q1        | D1        | $V_{TT}$  |

| <b>D</b> | A22 <sup>1</sup> | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | QK0#      | QK0       | $V_{SS}$  |

| <b>E</b> | A21              | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{DDQ}$ |          |          |          |          | $V_{DDQ}$ | Q2        | D2        | A20       |

| <b>F</b> | A5               | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q3        | D3        | QVLD      |

| <b>G</b> | A8               | A6               | A7               | $V_{DD}$  |          |          |          |          | $V_{DD}$  | A2        | A1        | A0        |

| <b>H</b> | BA2              | A9               | $V_{SS}$         | $V_{SS}$  |          |          |          |          | $V_{SS}$  | $V_{SS}$  | A4        | A3        |

| <b>J</b> | NF <sup>2</sup>  | NF <sup>2</sup>  | $V_{DD}$         | $V_{DD}$  |          |          |          |          | $V_{DD}$  | $V_{DD}$  | BA0       | CK        |

| <b>K</b> | DK               | DK#              | $V_{DD}$         | $V_{DD}$  |          |          |          |          | $V_{DD}$  | $V_{DD}$  | BA1       | CK#       |

| <b>L</b> | REF#             | CS#              | $V_{SS}$         | $V_{SS}$  |          |          |          |          | $V_{SS}$  | $V_{SS}$  | A14       | A13       |

| <b>M</b> | WE#              | A16              | A17              | $V_{DD}$  |          |          |          |          | $V_{DD}$  | A12       | A11       | A10       |

| <b>N</b> | A18              | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q4        | D4        | A19       |

| <b>P</b> | A15              | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{DDQ}$ |          |          |          |          | $V_{DDQ}$ | Q5        | D5        | DM        |

| <b>R</b> | $V_{SS}$         | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q6        | D6        | $V_{SS}$  |

| <b>T</b> | $V_{TT}$         | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{DDQ}$ |          |          |          |          | $V_{DDQ}$ | Q7        | D7        | $V_{TT}$  |

| <b>U</b> | $V_{DD}$         | DNU <sup>3</sup> | DNU <sup>3</sup> | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q8        | D8        | $V_{DD}$  |

| <b>V</b> | $V_{REF}$        | ZQ               | $V_{EXT}$        | $V_{SS}$  |          |          |          |          | $V_{SS}$  | $V_{EXT}$ | TDO       | TDI       |

Notes:

1. Reserved for future use. This may be optionally connected to GND.

2. No function. This signal is internally connected and has parasitic characteristics of a clock input signal. This may be optionally connected to GND.

3. Do not use. This signal is internally connected and has parasitic characteristics of an I/O. This may be optionally connected to GND. Note that if ODT is enabled on Rev. A die, these pins will be connected to  $V_{TT}$ . The DNU pins are High-Z on Rev. B die when ODT is enabled.

**Table 2: 32 Meg x 18 Ball Assignments (Top View) 144-Ball µBGA/FBGA**

|          | <b>1</b>         | <b>2</b>        | <b>3</b>  | <b>4</b>  | <b>5</b> | <b>6</b> | <b>7</b> | <b>8</b> | <b>9</b>  | <b>10</b> | <b>11</b> | <b>12</b> |

|----------|------------------|-----------------|-----------|-----------|----------|----------|----------|----------|-----------|-----------|-----------|-----------|

| <b>A</b> | $V_{REF}$        | $V_{SS}$        | $V_{EXT}$ | $V_{SS}$  |          |          |          |          | $V_{SS}$  | $V_{EXT}$ | TMS       | TCK       |

| <b>B</b> | $V_{DD}$         | D4              | Q4        | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q0        | D0        | $V_{DD}$  |

| <b>C</b> | $V_{TT}$         | D5              | Q5        | $V_{DDQ}$ |          |          |          |          | $V_{DDQ}$ | Q1        | D1        | $V_{TT}$  |

| <b>D</b> | A22 <sup>1</sup> | D6              | Q6        | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | QK0#      | QK0       | $V_{SS}$  |

| <b>E</b> | A21 <sup>2</sup> | D7              | Q7        | $V_{DDQ}$ |          |          |          |          | $V_{DDQ}$ | Q2        | D2        | A20       |

| <b>F</b> | A5               | D8              | Q8        | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q3        | D3        | QVLD      |

| <b>G</b> | A8               | A6              | A7        | $V_{DD}$  |          |          |          |          | $V_{DD}$  | A2        | A1        | A0        |

| <b>H</b> | BA2              | A9              | $V_{SS}$  | $V_{SS}$  |          |          |          |          | $V_{SS}$  | $V_{SS}$  | A4        | A3        |

| <b>J</b> | NF <sup>3</sup>  | NF <sup>3</sup> | $V_{DD}$  | $V_{DD}$  |          |          |          |          | $V_{DD}$  | $V_{DD}$  | BA0       | CK        |

| <b>K</b> | DK               | DK#             | $V_{DD}$  | $V_{DD}$  |          |          |          |          | $V_{DD}$  | $V_{DD}$  | BA1       | CK#       |

| <b>L</b> | REF#             | CS#             | $V_{SS}$  | $V_{SS}$  |          |          |          |          | $V_{SS}$  | $V_{SS}$  | A14       | A13       |

| <b>M</b> | WE#              | A16             | A17       | $V_{DD}$  |          |          |          |          | $V_{DD}$  | A12       | A11       | A10       |

| <b>N</b> | A18              | D14             | Q14       | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q9        | D9        | A19       |

| <b>P</b> | A15              | D15             | Q15       | $V_{DDQ}$ |          |          |          |          | $V_{DDQ}$ | Q10       | D10       | DM        |

| <b>R</b> | $V_{SS}$         | QK1             | QK1#      | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q11       | D11       | $V_{SS}$  |

| <b>T</b> | $V_{TT}$         | D16             | Q16       | $V_{DDQ}$ |          |          |          |          | $V_{DDQ}$ | Q12       | D12       | $V_{TT}$  |

| <b>U</b> | $V_{DD}$         | D17             | Q17       | $V_{SSQ}$ |          |          |          |          | $V_{SSQ}$ | Q13       | D13       | $V_{DD}$  |

| <b>V</b> | $V_{REF}$        | ZQ              | $V_{EXT}$ | $V_{SS}$  |          |          |          |          | $V_{SS}$  | $V_{EXT}$ | TDO       | TDI       |

Notes:

1. Reserved for future use. This may be optionally connected to GND.

2. Reserved for future use. This signal is internally connected and has parasitic characteristics of an address input signal. This may be optionally connected to GND.

3. No function. This signal is internally connected and has parasitic characteristics of a clock input signal. This may be optionally connected to GND.

**Table 3: Ball Descriptions**

| Symbol           | Type      | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0–A21           | Input     | <b>Address inputs:</b> A0–A21 define the row and column addresses for READ and WRITE operations. During a MODE REGISTER SET, the address inputs define the register settings. They are sampled at the rising edge of CK.                                                                                                                                                                             |

| BA0–BA2          | Input     | <b>Bank address inputs:</b> Select to the internal bank to which a command is being applied.                                                                                                                                                                                                                                                                                                         |

| CK, CK#          | Input     | <b>Input clock:</b> CK and CK# are differential input clocks. Addresses and commands are latched on the rising edge of CK. CK# is ideally 180 degrees out of phase with CK.                                                                                                                                                                                                                          |

| CS#              | Input     | <b>Chip select:</b> CS# enables the command decoder when LOW and disables it when HIGH. When the command decoder is disabled, new commands are ignored but internal operations continue.                                                                                                                                                                                                             |

| D0–D17           | Input     | <b>Data input:</b> The D signals form the 18-bit input data bus. During WRITE commands, the data is sampled at both edges of DK.                                                                                                                                                                                                                                                                     |

| DK, DK#          | Input     | <b>Input data clock:</b> DK and DK# are the differential input data clocks. All input data is referenced to both edges of DK. DK# is ideally 180 degrees out of phase with DK. In both x9 and x18 configurations, all Ds are referenced to DK and DK#.                                                                                                                                               |

| DM               | Input     | <b>Input data mask:</b> The DM signal is the input mask signal for WRITE data. Input data is masked when DM is sampled HIGH. DM is sampled on both edges of DK. Tie signal to ground if not used.                                                                                                                                                                                                    |

| TMS, TDI         | Input     | <b>IEEE 1149.1 test inputs:</b> These balls may be left as no connects if the JTAG function is not used.                                                                                                                                                                                                                                                                                             |

| TCK              | Input     | <b>IEEE 1149.1 clock input:</b> This ball must be tied to V <sub>SS</sub> if the JTAG function is not used.                                                                                                                                                                                                                                                                                          |

| WE#, REF#        | Input     | <b>Command inputs:</b> Sampled at the positive edge of CK, WE#, and REF# define (together with CS#) the command to be executed.                                                                                                                                                                                                                                                                      |

| Q0–Q17           | Output    | <b>Data output:</b> The Q signals form the 18-bit output data bus. During READ commands, the data is referenced to both edges of QK.                                                                                                                                                                                                                                                                 |

| QKx, QKx#        | Output    | <b>Output data clocks:</b> QKx and QKx# are opposite polarity, output data clocks. They are free-running, and during READs, edge-aligned with data output from the RLDRAM. QKx# is ideally 180 degrees out of phase with QKx. For the x9 device, all Qs are aligned with QK0 and QK0#. For the x18 device, QK0 and QK0# are aligned with Q0–Q8 and QK1 and QK1# are aligned with Q9–Q17.             |

| QVLD             | Output    | <b>Data valid:</b> Indicates valid output data and is edge-aligned with QKx and QKx#.                                                                                                                                                                                                                                                                                                                |

| TDO              | Output    | <b>IEEE 1149.1 test output:</b> JTAG output. This ball may be left as no connect if the JTAG function is not used.                                                                                                                                                                                                                                                                                   |

| ZQ               | Reference | <b>External impedance (25–60Ω):</b> This signal is used to tune the device outputs to the system data bus impedance. Q output impedance is set to 0.2 × RQ, where RQ is a resistor from this signal to ground. Connecting ZQ to GND invokes the minimum impedance mode. Connecting ZQ to V <sub>DD</sub> invokes the maximum impedance mode. Refer to Figure 11 (page 32) to activate this function. |

| V <sub>EXT</sub> | Supply    | <b>Power supply:</b> Nominally, 2.5V. See Table 7 (page 19) for range.                                                                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub>  | Supply    | <b>Power supply:</b> Nominally, 1.8V. See Table 7 for range.                                                                                                                                                                                                                                                                                                                                         |

| V <sub>DDQ</sub> | Supply    | <b>DQ power supply:</b> Nominally, 1.5V or 1.8V. Isolated on the device for improved noise immunity. See Table 7 for range.                                                                                                                                                                                                                                                                          |

**Table 3: Ball Descriptions (Continued)**

| Symbol    | Type   | Description                                                                                                                                                                                                |

|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{REF}$ | Supply | <b>Input reference voltage:</b> Nominally $V_{DDQ}/2$ . Provides a reference voltage for the input buffers.                                                                                                |

| $V_{SS}$  | Supply | Ground.                                                                                                                                                                                                    |

| $V_{SSQ}$ | Supply | <b>DQ ground:</b> Isolated on the device for improved noise immunity.                                                                                                                                      |

| $V_{TT}$  | Supply | <b>Power supply:</b> Isolated termination supply. Nominally, $V_{DDQ}/2$ . See Table 7 for range.                                                                                                          |

| A22       | –      | <b>Reserved for future use:</b> This signal is not connected and may be connected to ground.                                                                                                               |

| DNU       | –      | <b>Do not use:</b> These balls may be connected to ground. Note that if ODT is enabled on Rev A die, these pins will be connected to $V_{TT}$ . The DNU pins are High-Z on Rev. B die when ODT is enabled. |

| NF        | –      | <b>No function:</b> These balls can be connected to ground.                                                                                                                                                |

## Package Dimensions

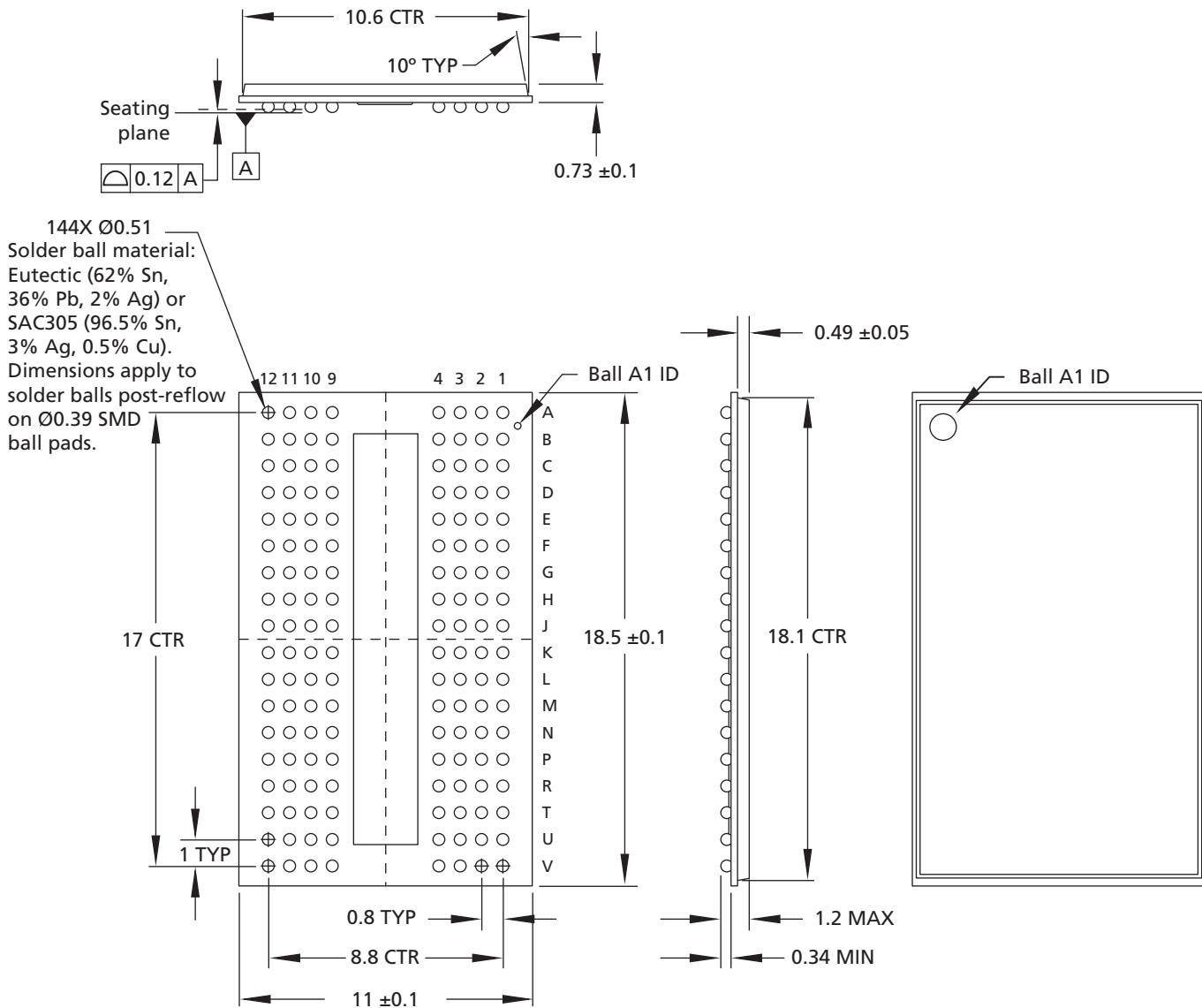

**Figure 5: 144-Ball µBGA**

**Note:** 1. All dimensions are in millimeters.

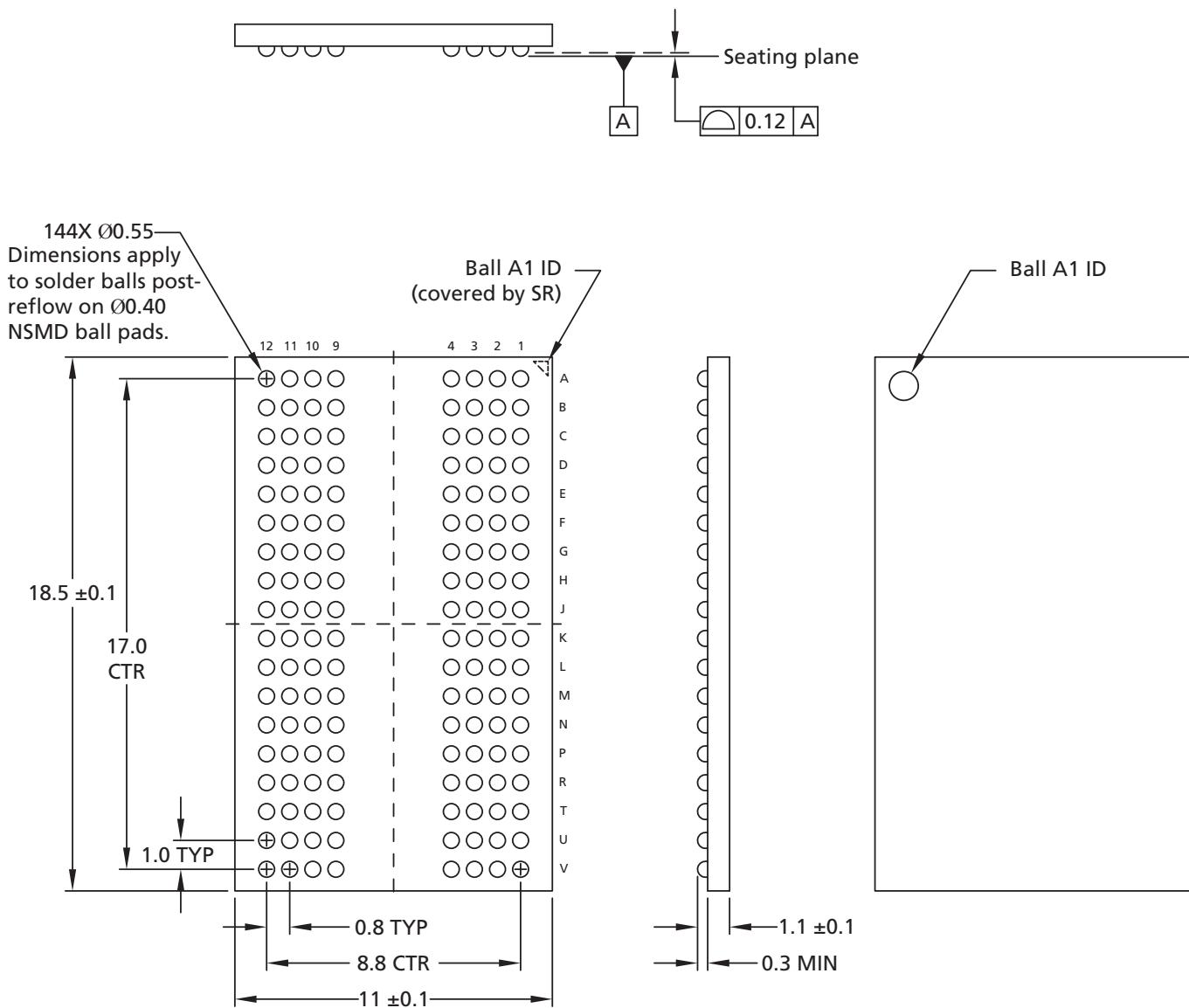

**Figure 6: 144-Ball FBGA**

Notes:

1. All dimensions are in millimeters.

2. Solder ball material: SAC302 (96.8% Sn, 3% Ag, 0.2% Cu).

## Electrical Specifications – $I_{DD}$

**Table 4:  $I_{DD}$  Operating Conditions and Maximum Limits – Rev. A**

| Description                           | Condition                                                                                                                                                                                    | Symbol                     | -18  | -25E | -25 | -33 | Units |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|------|-----|-----|-------|

| Standby current                       | $t_{CK}$ = idle; All banks idle, no inputs toggling                                                                                                                                          | $I_{SB1} (V_{DD})$ x9/x18  | 55   | 53   | 48  | 48  | mA    |

|                                       |                                                                                                                                                                                              | $I_{SB1} (V_{EXT})$        | 5    | 5    | 5   | 5   |       |

| Active standby current                | CS# = 1; No commands; Bank address incriminated and half address/data change once every 4 clock cycles                                                                                       | $I_{SB2} (V_{DD})$ x9/x18  | 365  | 293  | 288 | 233 | mA    |

|                                       |                                                                                                                                                                                              | $I_{SB2} (V_{EXT})$        | 5    | 5    | 5   | 5   |       |

| Operational current                   | BL = 2; Sequential bank access; Bank transitions once every $t_{RC}$ ; Half address transitions once every $t_{RC}$ ; Read followed by write sequence; Continuous data during WRITE commands | $I_{DD1} (V_{DD})$ x9/x18  | 465  | 380  | 348 | 305 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD1} (V_{EXT})$        | 15   | 15   | 15  | 13  |       |

| Operational current                   | BL = 4; Sequential bank access; Bank transitions once every $t_{RC}$ ; Half address transitions once every $t_{RC}$ ; Read followed by write sequence; Continuous data during WRITE commands | $I_{DD2} (V_{DD})$ x9/x18  | 475  | 400  | 362 | 319 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD2} (V_{EXT})$        | 15   | 15   | 15  | 13  |       |

| Operational current                   | BL = 8; Sequential bank access; Bank transitions once every $t_{RC}$ ; Half address transitions once every $t_{RC}$ ; Read followed by write sequence; Continuous data during WRITE commands | $I_{DD3} (V_{DD})$ x9/x18  | 505  | 430  | 408 | 368 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD3} (V_{EXT})$        | 20   | 20   | 20  | 18  |       |

| Burst refresh current                 | Eight-bank cyclic refresh; Continuous address/data; Command bus remains in refresh for all 8 banks                                                                                           | $I_{REF1} (V_{DD})$ x9/x18 | 995  | 790  | 785 | 615 | mA    |

|                                       |                                                                                                                                                                                              | $I_{REF1} (V_{EXT})$       | 80   | 80   | 80  | 70  |       |

| Distributed refresh current           | Single-bank refresh; Sequential bank access; Half address transitions once every $t_{RC}$ ; Continuous data                                                                                  | $I_{REF2} (V_{DD})$ x9/x18 | 425  | 330  | 325 | 267 | mA    |

|                                       |                                                                                                                                                                                              | $I_{REF2} (V_{EXT})$       | 20   | 20   | 20  | 18  |       |

| Operating burst write current example | BL = 2; Cyclic bank access; Half of address bits change every clock cycle; Continuous data; Measurement is taken during continuous WRITE                                                     | $I_{DD2W} (V_{DD})$ x9/x18 | 1335 | 980  | 970 | 819 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD2W} (V_{EXT})$       | 50   | 50   | 50  | 40  |       |

| Operating burst write current example | BL = 4; Cyclic bank access; Half of address bits change every 2 clock cycles; Continuous data; Measurement is taken during continuous WRITE                                                  | $I_{DD4W} (V_{DD})$ x9/x18 | 985  | 785  | 779 | 609 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD4W} (V_{EXT})$       | 30   | 30   | 30  | 25  |       |

| Operating burst write current example | BL = 8; Cyclic bank access; Half of address bits change every 4 clock cycles; Continuous data; Measurement is taken during continuous WRITE                                                  | $I_{DD8W} (V_{DD})$ x9/x18 | 770  | 675  | 668 | 525 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD8W} (V_{EXT})$       | 30   | 30   | 30  | 25  |       |

| Operating burst read current example  | BL = 2; Cyclic bank access; Half of address bits change every clock cycle; Continuous data; Measurement is taken during continuous READ                                                      | $I_{DD2R} (V_{DD})$ x9/x18 | 1225 | 865  | 860 | 735 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD2R} (V_{EXT})$       | 50   | 50   | 50  | 40  |       |

| Operating burst read current example  | BL = 4; Cyclic bank access; Half of address bits change every 2 clock cycles; Continuous data; Measurement is taken during continuous READ                                                   | $I_{DD4R} (V_{DD})$ x9/x18 | 860  | 685  | 680 | 525 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD4R} (V_{EXT})$       | 30   | 30   | 30  | 25  |       |

| Operating burst read current example  | BL = 8; Cyclic bank access; Half of address bits change every 4 clock cycles; Continuous data; Measurement is taken during continuous READ                                                   | $I_{DD8R} (V_{DD})$ x9/x18 | 655  | 575  | 570 | 450 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD8R} (V_{EXT})$       | 30   | 30   | 30  | 25  |       |

**Table 5:  $I_{DD}$  Operating Conditions and Maximum Limits – Rev. B**

| Description                           | Condition                                                                                                                                                                                    | Symbol                     | -18 | -25E | -25 | -33 | Units |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|------|-----|-----|-------|

| Standby current                       | $t_{CK}$ = idle; All banks idle, no inputs toggling                                                                                                                                          | $I_{SB1} (V_{DD})$ x9/x18  | 55  | 55   | 55  | 55  | mA    |

|                                       |                                                                                                                                                                                              | $I_{SB1} (V_{EXT})$        | 5   | 5    | 5   | 5   |       |

| Active standby current                | CS# = 1; No commands; Bank address incriminated and half address/data change once every 4 clock cycles                                                                                       | $I_{SB2} (V_{DD})$ x9/x18  | 250 | 215  | 215 | 190 | mA    |

|                                       |                                                                                                                                                                                              | $I_{SB2} (V_{EXT})$        | 5   | 5    | 5   | 5   |       |

| Operational current                   | BL = 2; Sequential bank access; Bank transitions once every $t_{RC}$ ; Half address transitions once every $t_{RC}$ ; Read followed by write sequence; Continuous data during WRITE commands | $I_{DD1} (V_{DD})$ x9/x18  | 310 | 285  | 260 | 225 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD1} (V_{EXT})$        | 10  | 10   | 10  | 10  |       |

| Operational current                   | BL = 4; Sequential bank access; Bank transitions once every $t_{RC}$ ; Half address transitions once every $t_{RC}$ ; Read followed by write sequence; Continuous data during WRITE commands | $I_{DD2} (V_{DD})$ x9/x18  | 315 | 290  | 260 | 220 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD2} (V_{EXT})$        | 10  | 10   | 10  | 10  |       |

| Operational current                   | BL = 8; Sequential bank access; Bank transitions once every $t_{RC}$ ; Half address transitions once every $t_{RC}$ ; Read followed by write sequence; Continuous data during WRITE commands | $I_{DD3} (V_{DD})$ x9/x18  | 330 | 305  | 275 | 230 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD3} (V_{EXT})$        | 15  | 15   | 15  | 15  |       |

| Burst refresh current                 | Eight-bank cyclic refresh; Continuous address/data; Command bus remains in refresh for all 8 banks                                                                                           | $I_{REF1} (V_{DD})$ x9/x18 | 660 | 540  | 530 | 430 | mA    |

|                                       |                                                                                                                                                                                              | $I_{REF1} (V_{EXT})$       | 45  | 30   | 30  | 25  |       |

| Distributed refresh current           | Single-bank refresh; Sequential bank access; Half address transitions once every $t_{RC}$ ; Continuous data                                                                                  | $I_{REF2} (V_{DD})$ x9/x18 | 295 | 265  | 250 | 215 | mA    |

|                                       |                                                                                                                                                                                              | $I_{REF2} (V_{EXT})$       | 10  | 10   | 10  | 10  |       |

| Operating burst write current example | BL = 2; Cyclic bank access; Half of address bits change every clock cycle; Continuous data; Measurement is taken during continuous WRITE                                                     | $I_{DD2W} (V_{DD})$ x9/x18 | 830 | 655  | 655 | 530 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD2W} (V_{EXT})$       | 40  | 35   | 35  | 30  |       |

| Operating burst write current example | BL = 4; Cyclic bank access; Half of address bits change every 2 clock cycles; Continuous data; Measurement is taken during continuous WRITE                                                  | $I_{DD4W} (V_{DD})$ x9/x18 | 580 | 465  | 465 | 385 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD4W} (V_{EXT})$       | 25  | 20   | 20  | 20  |       |

| Operating burst write current example | BL = 8; Cyclic bank access; Half of address bits change every 4 clock cycles; Continuous data; Measurement is taken during continuous WRITE                                                  | $I_{DD8W} (V_{DD})$ x9/x18 | 445 | 370  | 370 | 305 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD8W} (V_{EXT})$       | 25  | 20   | 20  | 20  |       |

| Operating burst read current example  | BL = 2; Cyclic bank access; Half of address bits change every clock cycle; Continuous data; Measurement is taken during continuous READ                                                      | $I_{DD2R} (V_{DD})$ x9/x18 | 805 | 640  | 640 | 515 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD2R} (V_{EXT})$       | 40  | 35   | 35  | 30  |       |

| Operating burst read current example  | BL = 4; Cyclic bank access; Half of address bits change every 2 clock cycles; Continuous data; Measurement is taken during continuous READ                                                   | $I_{DD4R} (V_{DD})$ x9/x18 | 545 | 440  | 440 | 365 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD4R} (V_{EXT})$       | 25  | 20   | 20  | 20  |       |

| Operating burst read current example  | BL = 8; Cyclic bank access; Half of address bits change every 4 clock cycles; Continuous data; Measurement is taken during continuous READ                                                   | $I_{DD8R} (V_{DD})$ x9/x18 | 410 | 335  | 335 | 280 | mA    |

|                                       |                                                                                                                                                                                              | $I_{DD8R} (V_{EXT})$       | 25  | 20   | 20  | 20  |       |

Notes: 1.  $I_{DD}$  specifications are tested after the device is properly initialized.  $+0^{\circ}\text{C} \leq T_c \leq +95^{\circ}\text{C}$ ;  $+1.7\text{V} \leq V_{DD} \leq +1.9\text{V}$ ,  $+2.38\text{V} \leq V_{EXT} \leq +2.63\text{V}$ ,  $+1.4\text{V} \leq V_{DDQ} \leq V_{DD}$ ,  $V_{REF} = V_{DDQ}/2$ .

2.  $t_{CK} = t_{DK} = \text{MIN}$ ,  $t_{RC} = \text{MIN}$ .

3. Input slew rate is specified in Table 8 (page 20).

4. Definitions for  $I_{DD}$  conditions

5. LOW is defined as  $V_{IN} \leq V_{IL(AC)} \text{ MAX.}$

6. HIGH is defined as  $V_{IN} \geq V_{IH(AC)} \text{ MIN.}$

7. Stable is defined as inputs remaining at a HIGH or LOW level.

8. Floating is defined as inputs at  $V_{REF} = V_{DDQ/2}$ .

9. Continuous data is defined as half the D or Q signals changing between HIGH and LOW every half clock cycle (twice per clock).

10. Continuous address is defined as half the address signals changing between HIGH and LOW every clock cycle (once per clock).

11. Sequential bank access is defined as the bank address incrementing by one every  $t_{RC}$ .

12. Cyclic bank access is defined as the bank address incrementing by one for each command access. For  $BL = 2$  this is every clock, for  $BL = 4$  this is every other clock, and for  $BL = 8$  this is every fourth clock.

13. CS# is HIGH unless a READ, WRITE, AREF, or MRS command is registered. CS# never transitions more than once per clock cycle.

14.  $I_{DD}$  parameters are specified with ODT disabled.

15. Tests for AC timing,  $I_{DD}$ , and electrical AC and DC characteristics may be conducted at nominal reference/supply voltage levels, but the related specifications and device operations are tested for the full voltage range specified.

16.  $I_{DD}$  tests may use a  $V_{IL}$ -to- $V_{IH}$  swing of up to 1.5V in the test environment, but input timing is still referenced to  $V_{REF}$  (or to the crossing point for CK/CK#). Parameter specifications are tested for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals used to test the device is 2 V/ns in the range between  $V_{IL(AC)}$  and  $V_{IH(AC)}$ .

## Electrical Specifications – AC and DC

### Absolute Maximum Ratings

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Table 6: Absolute Maximum Ratings**

| Parameter                                        | Min  | Max             | Units |

|--------------------------------------------------|------|-----------------|-------|

| I/O voltage                                      | -0.3 | $V_{DDQ} + 0.3$ | V     |

| Voltage on $V_{EXT}$ supply relative to $V_{SS}$ | -0.3 | +2.8            | V     |

| Voltage on $V_{DD}$ supply relative to $V_{SS}$  | -0.3 | +2.1            | V     |

| Voltage on $V_{DDQ}$ supply relative to $V_{SS}$ | -0.3 | +2.1            | V     |

### AC and DC Operating Conditions

**Table 7: DC Electrical Characteristics and Operating Conditions**

Note 1 applies to the entire table; Unless otherwise noted:  $+0^{\circ}\text{C} \leq T_C \leq +95^{\circ}\text{C}$ ;  $+1.7\text{V} \leq V_{DD} \leq +1.9\text{V}$

| Description                   | Conditions                    | Symbol    | Min                              | Max                              | Units         | Notes     |

|-------------------------------|-------------------------------|-----------|----------------------------------|----------------------------------|---------------|-----------|

| Supply voltage                | –                             | $V_{EXT}$ | 2.38                             | 2.63                             | V             |           |

| Supply voltage                | –                             | $V_{DD}$  | 1.7                              | 1.9                              | V             | 2         |

| Isolated output buffer supply | –                             | $V_{DDQ}$ | 1.4                              | $V_{DD}$                         | V             | 2, 3      |

| Reference voltage             | –                             | $V_{REF}$ | $0.49 \times V_{DDQ}$            | $0.51 \times V_{DDQ}$            | V             | 4, 5, 6   |

| Termination voltage           | –                             | $V_{TT}$  | $0.95 \times V_{REF}$            | $1.05 \times V_{REF}$            | V             | 7, 8      |

| Input high (logic 1) voltage  | –                             | $V_{IH}$  | $V_{REF} + 0.1$                  | $V_{DDQ} + 0.3$                  | V             | 2         |

| Input low (logic 0) voltage   | –                             | $V_{IL}$  | $V_{SS} - 0.3$                   | $V_{REF} - 0.1$                  | V             | 2         |

| Output high current           | $V_{OH} = V_{DDQ}/2$          | $I_{OH}$  | $(V_{DDQ}/2)/(1.15 \times RQ/5)$ | $(V_{DDQ}/2)/(0.85 \times RQ/5)$ | A             | 9, 10, 11 |

| Output low current            | $V_{OL} = V_{DDQ}/2$          | $I_{OL}$  | $(V_{DDQ}/2)/(1.15 \times RQ/5)$ | $(V_{DDQ}/2)/(0.85 \times RQ/5)$ | A             | 9, 10, 11 |

| Clock input leakage current   | $0V \leq V_{IN} \leq V_{DD}$  | $I_{LC}$  | -5                               | 5                                | $\mu\text{A}$ |           |

| Input leakage current         | $0V \leq V_{IN} \leq V_{DD}$  | $I_{LI}$  | -5                               | 5                                | $\mu\text{A}$ |           |

| Output leakage current        | $0V \leq V_{IN} \leq V_{DDQ}$ | $I_{LO}$  | -5                               | 5                                | $\mu\text{A}$ |           |

| Reference voltage current     | –                             | $I_{REF}$ | -5                               | 5                                | $\mu\text{A}$ |           |

Notes: 1. All voltages referenced to  $V_{SS}$  (GND).

2. Overshoot:  $V_{IH(AC)} \leq V_{DD} + 0.7V$  for  $t \leq t_{CK}/2$ . Undershoot:  $V_{IL(AC)} \geq -0.5V$  for  $t \leq t_{CK}/2$ . During normal operation,  $V_{DDQ}$  must not exceed  $V_{DD}$ . Control input signals may not have pulse widths less than  $t_{CK}/2$  or operate at frequencies exceeding  $t_{CK}$  (MAX).

3.  $V_{DDQ}$  can be set to a nominal  $1.5V \pm 0.1V$  or  $1.8V \pm 0.1V$  supply.

4. Typically the value of  $V_{REF}$  is expected to be  $0.5 \times V_{DDQ}$  of the transmitting device.  $V_{REF}$  is expected to track variations in  $V_{DDQ}$ .

5. Peak-to-peak AC noise on  $V_{REF}$  must not exceed  $\pm 2\% V_{REF(DC)}$ .

6.  $V_{REF}$  is expected to equal  $V_{DDQ/2}$  of the transmitting device and to track variations in the DC level of the same. Peak-to-peak noise (non-common mode) on  $V_{REF}$  may not exceed  $\pm 2\%$  of the DC value. Thus, from  $V_{DDQ/2}$ ,  $V_{REF}$  is allowed  $\pm 2\% V_{DDQ/2}$  for DC error and an additional  $\pm 2\% V_{DDQ/2}$  for AC noise. This measurement is to be taken at the nearest  $V_{REF}$  bypass capacitor.

7.  $V_{TT}$  is expected to be set equal to  $V_{REF}$  and must track variations in the DC level of  $V_{REF}$ .

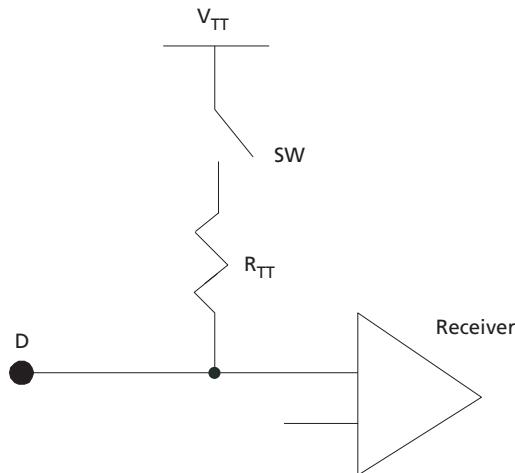

8. On-die termination may be selected using mode register bit 9 (see Figure 11 (page 32)). A resistance  $R_{TT}$  from each data input signal to the nearest  $V_{TT}$  can be enabled.  $R_{TT} = 125-185\Omega$  at  $95^\circ C$   $T_C$ .

9.  $I_{OH}$  and  $I_{OL}$  are defined as absolute values and are measured at  $V_{DDQ/2}$ .  $I_{OH}$  flows from the device,  $I_{OL}$  flows into the device.

10. If MRS bit A8 is 0, use  $R_Q = 250\Omega$  in the equation in lieu of presence of an external impedance matched resistor.

11. For  $V_{OL}$  and  $V_{OH}$ , refer to the RLDRAM 2 HSPICE or IBIS driver models.

**Table 8: Input AC Logic Levels**

Unless otherwise noted:  $+0^\circ C \leq T_C \leq +95^\circ C$ ;  $+1.7V \leq V_{DD} \leq +1.9V$

| Description                  | Symbol   | Min             | Max             | Units |

|------------------------------|----------|-----------------|-----------------|-------|

| Input high (logic 1) voltage | $V_{IH}$ | $V_{REF} + 0.2$ | –               | V     |

| Input low (logic 0) voltage  | $V_{IL}$ | –               | $V_{REF} - 0.2$ | V     |

Notes: 1. All voltages referenced to  $V_{SS}$  (GND).

2. The AC and DC input level specifications are as defined in the HSTL standard (that is, the receiver will effectively switch as a result of the signal crossing the AC input level, and will remain in that state as long as the signal does not ring back above [below] the DC input LOW [HIGH] level).

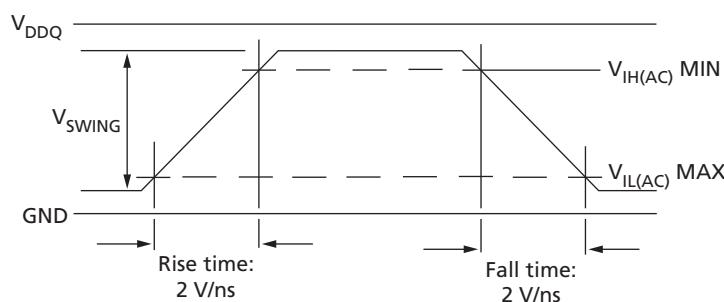

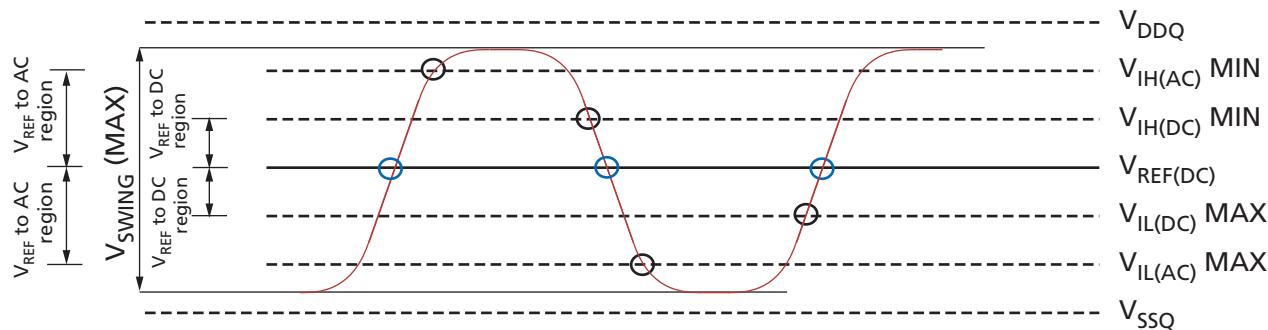

3. The minimum slew rate for the input signals used to test the device is  $2 V/ns$  in the range between  $V_{IL(AC)}$  and  $V_{IH(AC)}$ . See illustration below:

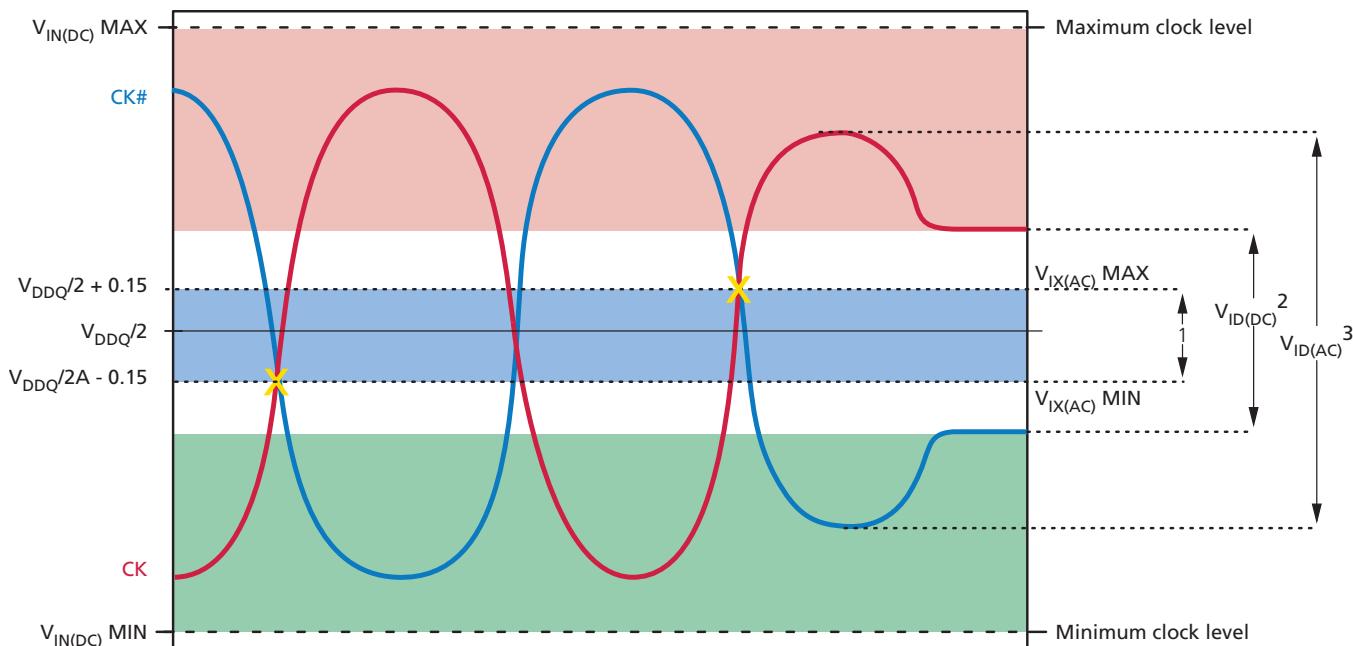

**Table 9: Differential Input Clock Operating Conditions**

Notes 1–4 apply to the entire table; Unless otherwise noted:  $+0^{\circ}\text{C} \leq T_{\text{C}} \leq +95^{\circ}\text{C}$ ;  $+1.7\text{V} \leq V_{\text{DD}} \leq +1.9\text{V}$

| Parameter/Condition                            | Symbol                     | Min                       | Max                       | Units | Notes |

|------------------------------------------------|----------------------------|---------------------------|---------------------------|-------|-------|

| Clock input voltage level: CK and CK#          | $V_{\text{IN}(\text{DC})}$ | -0.3                      | $V_{\text{DDQ}} + 0.3$    | V     |       |

| Clock input differential voltage: CK and CK#   | $V_{\text{ID}(\text{DC})}$ | 0.2                       | $V_{\text{DDQ}} + 0.6$    | V     | 5     |

| Clock input differential voltage: CK and CK#   | $V_{\text{ID}(\text{AC})}$ | 0.4                       | $V_{\text{DDQ}} + 0.6$    | V     | 5     |

| Clock input crossing point voltage: CK and CK# | $V_{\text{IX}(\text{AC})}$ | $V_{\text{DDQ}/2} - 0.15$ | $V_{\text{DDQ}/2} + 0.15$ | V     | 6     |

Notes:

1.  $\text{DKx}$  and  $\text{DKx}\#$  have the same requirements as CK and CK#.

2. All voltages referenced to  $V_{\text{SS}}$  (GND).

3. The CK/CK# input reference level (for timing referenced to CK/CK#) is the point at which CK and CK# cross. The input reference level for signals other than CK/CK# is  $V_{\text{REF}}$ .

4. CK and CK# input slew rate must be  $\geq 2 \text{ V/ns}$  ( $\geq 4 \text{ V/ns}$  if measured differentially).

5.  $V_{\text{ID}}$  is the magnitude of the difference between the input level on CK and the input level on CK#.

6. The value of  $V_{\text{IX}}$  is expected to equal  $V_{\text{DDQ}/2}$  of the transmitting device and must track variations in the DC level of the same.

**Figure 7: Clock Input**

Notes:

1. CK and CK# must cross within this region.

2. CK and CK# must meet at least  $V_{\text{ID}(\text{DC})\text{ MIN}}$  when static and centered around  $V_{\text{DDQ}/2}$ .

3. Minimum peak-to-peak swing.

4. It is a violation to tri-state CK and CK# after the part is initialized.

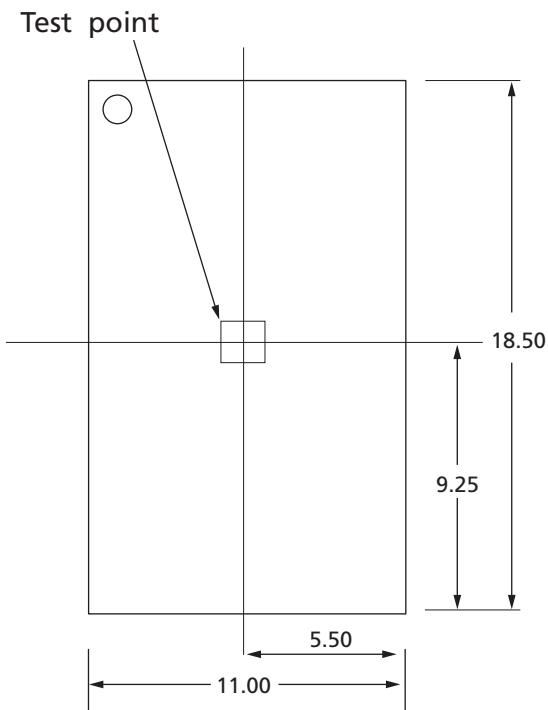

## Input Slew Rate Derating

The following tables define the address, command, and data setup and hold derating values. These values are added to the default  $t_{AS}/t_{CS}/t_{DS}$  and  $t_{AH}/t_{CH}/t_{DH}$  specifications when the slew rate of any of these input signals is less than the 2 V/ns the nominal setup and hold specifications are based upon.

To determine the setup and hold time needed for a given slew rate, add the  $t_{AS}/t_{CS}$  default specification to the “ $t_{AS}/t_{CS} V_{REF}$  to CK/CK# Crossing” and the  $t_{AH}/t_{CH}$  default specification to the “ $t_{AH}/t_{CH} CK/CK# Crossing to V_{REF}$ ” derated values on the Address and Command Setup and Hold Derating Values table. The derated data setup and hold values can be determined in a like manner using the “ $t_{DS} V_{REF}$  to CK/CK# Crossing” and “ $t_{DH}$  to CK/CK# Crossing to  $V_{REF}$ ” values on the Data Setup and Hold Derating Values table. The derating values on the Address and Command Setup and Hold Derating Values table and the Data Setup and Hold Derating Values table apply to all speed grades.

The setup times on the Address and Command Setup and Hold Derating Values table and the Data Setup and Hold Derating Values table represent a rising signal. In this case, the time from which the rising signal crosses  $V_{IH(AC)}\text{ MIN}$  to the CK/CK# cross point is static and must be maintained across all slew rates. The derated setup timing represents the point at which the rising signal crosses  $V_{REF(DC)}$  to the CK/CK# cross point. This derated value is calculated by determining the time needed to maintain the given slew rate and the delta between  $V_{IH(AC)}\text{ MIN}$  and the CK/CK# cross point. The setup values in the Address and Command Setup and Hold Derating Values table and the Data Setup and Hold Derating Values table are also valid for falling signals (with respect to  $V_{IL(AC)}\text{ MAX}$  and the CK/CK# cross point).

The hold times in the Address and Command Setup and Hold Derating Values table and the Data Setup and Hold Derating Values table represent falling signals. In this case, the time from the CK/CK# cross point to when the signal crosses  $V_{IH(DC)}\text{ MIN}$  is static and must be maintained across all slew rates. The derated hold timing represents the delta between the CK/CK# cross point to when the falling signal crosses  $V_{REF(DC)}$ . This derated value is calculated by determining the time needed to maintain the given slew rate and the delta between the CK/CK# cross point and  $V_{IH(DC)}$ . The hold values in The Address and Command Setup and Hold Derating Values table and the Data Setup and Hold Derating Values table are also valid for rising signals (with respect to  $V_{IL(DC)}\text{ MAX}$  and the CK and CK# cross point).

### Note:

The above descriptions also pertain to data setup and hold derating when CK/CK# are replaced with DK/DK#.

**Table 10: Address and Command Setup and Hold Derating Values**

| Command/<br>Address Slew<br>Rate (V/ns)         | $t_{AS}/t_{CS}$ $V_{REF}$ to<br>CK/CK# Crossing | $t_{AS}/t_{CS}$ $V_{IH(AC)}$<br>MIN to CK/CK#<br>Crossing | $t_{AH}/t_{CH}$ CK/CK#<br>Crossing to $V_{REF}$ | $t_{AH}/t_{CH}$ CK/CK#<br>Crossing to $V_{IH(DC)}$<br>MIN | Units |

|-------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------|-------|

| <b>CK, CK# Differential Slew Rate: 2.0 V/ns</b> |                                                 |                                                           |                                                 |                                                           |       |

| 2.0                                             | 0                                               | -100                                                      | 0                                               | -50                                                       | ps    |

| 1.9                                             | 5                                               | -100                                                      | 3                                               | -50                                                       | ps    |

| 1.8                                             | 11                                              | -100                                                      | 6                                               | -50                                                       | ps    |

| 1.7                                             | 18                                              | -100                                                      | 9                                               | -50                                                       | ps    |

| 1.6                                             | 25                                              | -100                                                      | 13                                              | -50                                                       | ps    |

| 1.5                                             | 33                                              | -100                                                      | 17                                              | -50                                                       | ps    |

| 1.4                                             | 43                                              | -100                                                      | 22                                              | -50                                                       | ps    |

| 1.3                                             | 54                                              | -100                                                      | 27                                              | -50                                                       | ps    |

| 1.2                                             | 67                                              | -100                                                      | 34                                              | -50                                                       | ps    |

| 1.1                                             | 82                                              | -100                                                      | 41                                              | -50                                                       | ps    |

| 1.0                                             | 100                                             | -100                                                      | 50                                              | -50                                                       | ps    |

| <b>CK, CK# Differential Slew Rate: 1.5 V/ns</b> |                                                 |                                                           |                                                 |                                                           |       |

| 2.0                                             | 30                                              | -70                                                       | 30                                              | -20                                                       | ps    |

| 1.9                                             | 35                                              | -70                                                       | 33                                              | -20                                                       | ps    |

| 1.8                                             | 41                                              | -70                                                       | 36                                              | -20                                                       | ps    |

| 1.7                                             | 48                                              | -70                                                       | 39                                              | -20                                                       | ps    |

| 1.6                                             | 55                                              | -70                                                       | 43                                              | -20                                                       | ps    |

| 1.5                                             | 63                                              | -70                                                       | 47                                              | -20                                                       | ps    |

| 1.4                                             | 73                                              | -70                                                       | 52                                              | -20                                                       | ps    |

| 1.3                                             | 84                                              | -70                                                       | 57                                              | -20                                                       | ps    |

| 1.2                                             | 97                                              | -70                                                       | 64                                              | -20                                                       | ps    |

| 1.1                                             | 112                                             | -70                                                       | 71                                              | -20                                                       | ps    |

| 1.0                                             | 130                                             | -70                                                       | 80                                              | -20                                                       | ps    |

| <b>CK, CK# Differential Slew Rate: 1.0 V/ns</b> |                                                 |                                                           |                                                 |                                                           |       |

| 2.0                                             | 60                                              | -40                                                       | 60                                              | 10                                                        | ps    |

| 1.9                                             | 65                                              | -40                                                       | 63                                              | 10                                                        | ps    |

| 1.8                                             | 71                                              | -40                                                       | 66                                              | 10                                                        | ps    |

| 1.7                                             | 78                                              | -40                                                       | 69                                              | 10                                                        | ps    |

| 1.6                                             | 85                                              | -40                                                       | 73                                              | 10                                                        | ps    |

| 1.5                                             | 93                                              | -40                                                       | 77                                              | 10                                                        | ps    |

| 1.4                                             | 103                                             | -40                                                       | 82                                              | 10                                                        | ps    |

| 1.3                                             | 114                                             | -40                                                       | 87                                              | 10                                                        | ps    |

| 1.2                                             | 127                                             | -40                                                       | 94                                              | 10                                                        | ps    |

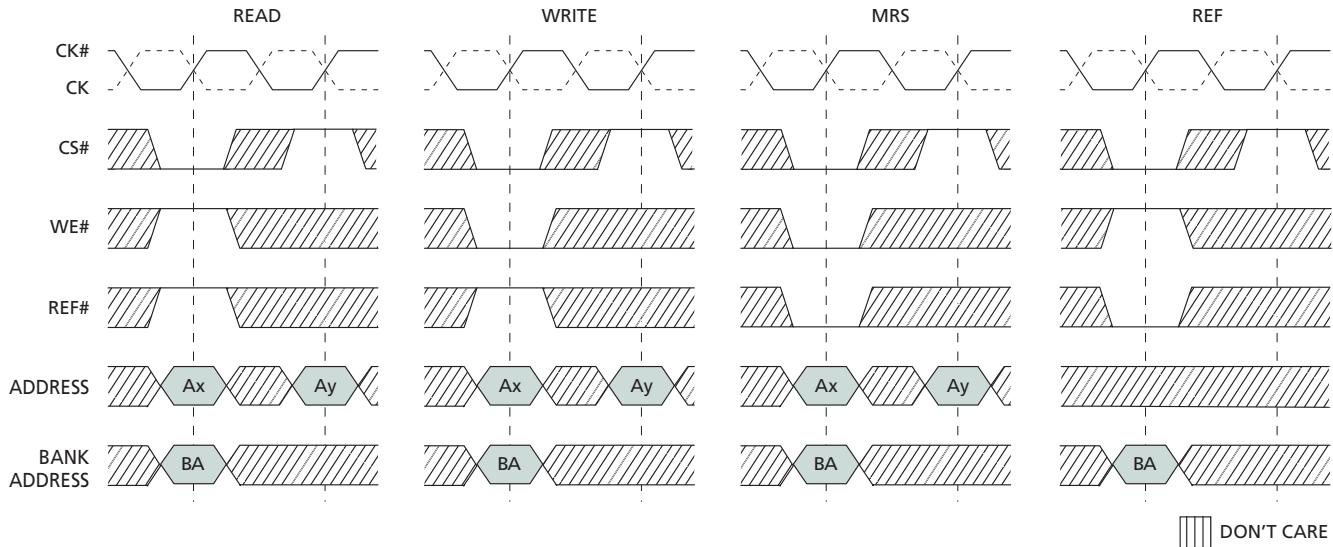

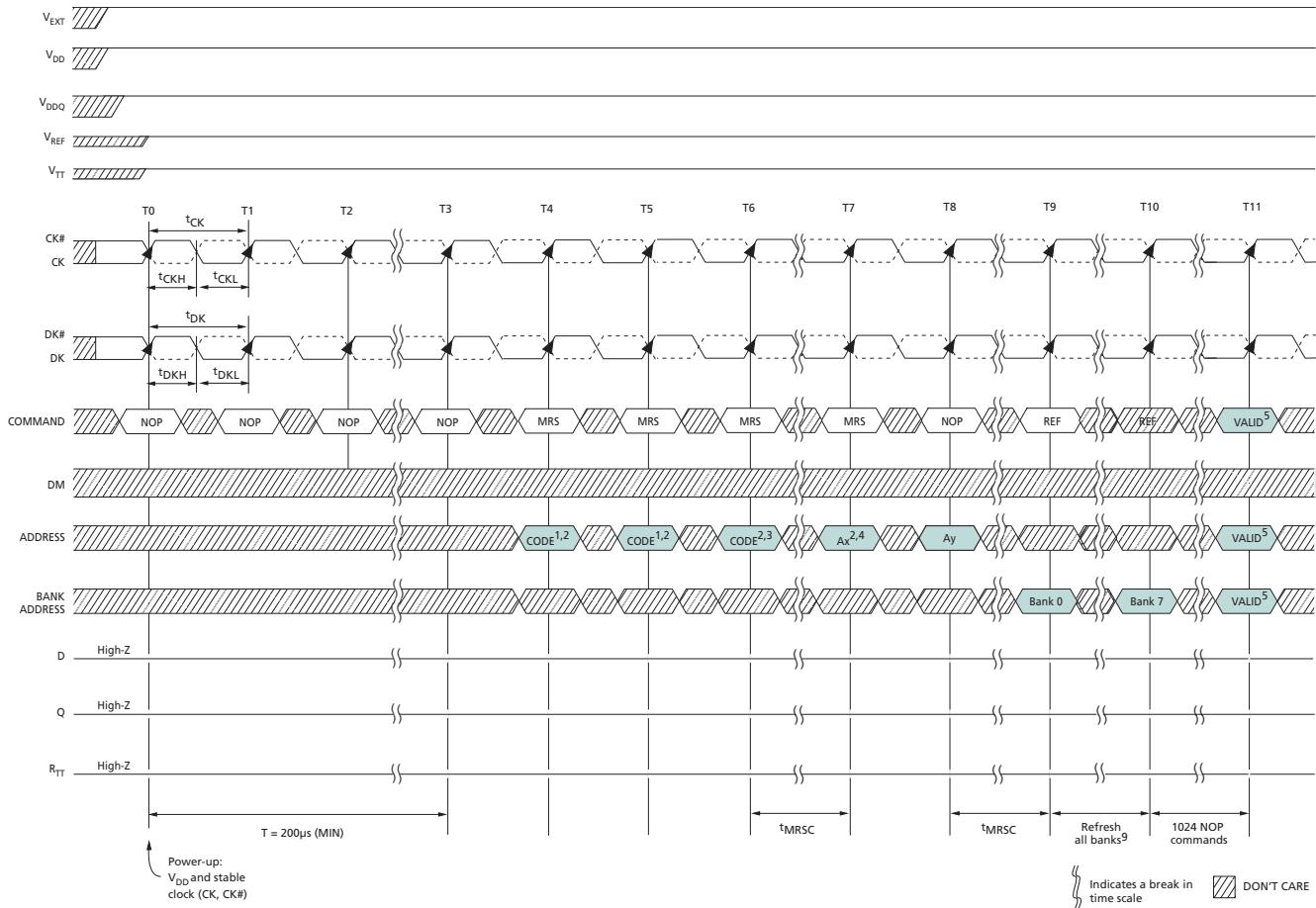

| 1.1                                             | 142                                             | -40                                                       | 101                                             | 10                                                        | ps    |