# Cortina Systems® LXT9860/LXT9880 Advanced 10/100 Repeater with Integrated Management

#### **Datasheet**

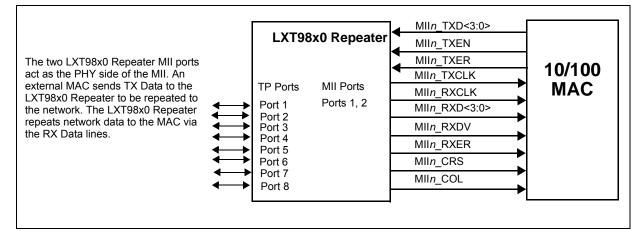

The Cortina Systems<sup>®</sup> LXT9860/LXT9880 Advanced 10/100 Repeater with Integrated Management (LXT98x0 Repeater) is the next-generation repeater family, integrated with six/eight 10/100 transceivers. The LXT98x0 Repeater is compatible with previous generations of Intel\* Repeaters from the LXT980 and LXT918 families. In the LXT9880 Repeater, eight ports directly support 100BASE-TX/10BASE-T copper media. Two additional Media Independent Interface (MII) ports (10/100 Mbps selectable) connect to Media Access Controllers (MACs) for bridge/switch applications. The LXT9860 Repeater offers the same features and functionality in a six-port device.

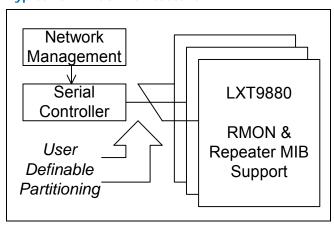

The LXT98x0 Repeater provides auto-negotiation with parallel detection for the PHY ports. The LXT98x0 Repeater provides two internal repeater state machines—one operating at 10 Mbps and one at 100 Mbps. Once configured, the LXT98x0 Repeater automatically connects each port to the appropriate repeater. The LXT98x0 Repeater also provides two Inter-Repeater Backplanes (IRBs) for expansion — one operating at 10 Mbps and one at 100 Mbps. Up to 240 twisted-pair and MII ports can logically be combined into one repeater. The LXT98x0 Repeater supports SNMP and RMON management via on-chip 32- and 64-bit counters. The counters and control functions are accessible via a high-speed Serial Management Interface (SMI).

# **Product Features**

- Six or eight 10/100 ports with integrated twisted-pair PHYs including integrated filters.

- Two 10/100 MIIs for bridging.

- Independent segments for 10 Mbps and 100 Mbps operation.

- Cascadable Inter-Repeater Backplanes (IRBs), with option for 5 V stacking compatibility.

- Hardware assist for RMON and the Repeater MIB.

- High-speed Serial Management Interface (SMI).

- Two address-tracking registers per port.

- Source Address matching function.

- Integrated LED drivers with user-selectable modes.

- Available in 208-pin QFP package.

- Operating temperature range: 0-70 °C, ambient.

- Available in extended temperature range:

-40 to +85 °C, ambient.

Note:

The LXT9880 Repeater and the LXT9860 Repeater are not recommended for new designs. Contact your Cortina Systems, Inc. representative for product availability.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH CORTINA SYSTEMS® PRODUCTS.

NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

EXCEPT AS PROVIDED IN CORTINA'S TERMS AND CONDITIONS OF SALE OF SUCH PRODUCTS, CORTINA ASSUMES NO LIABILITY WHATSOEVER, AND CORTINA DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF CORTINA PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Cortina products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Cortina Systems<sup>®</sup> and the Cortina Systems logo are the trademarks or registered trademarks of Cortina Systems, Inc. and its subsidiaries in the U.S. and other countries. Other names and brands may be claimed as the property of others.

Copyright © 2001-2007 Cortina Systems, Inc. All rights reserved.

# **Contents**

| 1.0 | Pin A | ssignm   | ents and Signal Descriptions           | 10 |

|-----|-------|----------|----------------------------------------|----|

| 2.0 | Func  | tional D | Description                            | 29 |

|     | 2.1   | Introdu  | uction                                 | 29 |

|     | 2.2   |          | onfiguration                           |    |

|     |       | 2.2.1    | Auto-Negotiation                       |    |

|     |       | 2.2.2    | Forced Operation                       |    |

|     |       | 2.2.3    | Changing Port Speed - Forced           |    |

|     |       | 2.2.4    | Link Establishment and Port Connection |    |

|     |       | 2.2.5    | MII Port Configuration                 | 31 |

|     | 2.3   | Interfac | ce Descriptions                        | 31 |

|     |       | 2.3.1    | Twisted-Pair Interface                 | 31 |

|     |       | 2.3.2    | Media Independent Interface            | 31 |

|     |       | 2.3.3    | Serial Management Interface            | 32 |

|     |       | 2.3.4    | Serial PROM Interface                  | 32 |

|     | 2.4   | Repeat   | ter Operation                          | 32 |

|     |       | 2.4.1    | 100 Mbps Repeater Operation            |    |

|     |       | 2.4.2    | 10 Mbps Repeater Operation             |    |

|     | 2.5   | Manag    | gement Support                         |    |

|     |       | 2.5.1    | Configuration and Status               |    |

|     |       | 2.5.2    | SNMP and RMON Support                  |    |

|     |       | 2.5.3    | Source Address Management              |    |

|     | 2.6   | •        | rements                                |    |

|     |       | 2.6.1    | Power                                  |    |

|     |       | 2.6.2    | Clock                                  |    |

|     |       | 2.6.3    | Bias Resistor                          |    |

|     |       | 2.6.4    | Reset                                  |    |

|     |       | 2.6.5    | PROM                                   |    |

|     |       | 2.6.6    | Chip ID                                |    |

|     |       | 2.6.7    | Management Master I/O Link             |    |

|     |       | 2.6.8    | IRB Bus Pull-ups                       |    |

|     | 2.7   |          | peration                               |    |

|     |       | 2.7.1    | LEDs at Start-up                       |    |

|     |       | 2.7.2    | LED Event Stretching                   |    |

|     |       | 2.7.3    | LED Blink Rates                        |    |

|     |       | 2.7.4    | Serial LED Interface                   |    |

|     |       | 2.7.5    | Direct Drive LEDs                      |    |

|     | 2.0   |          | LED Modes                              |    |

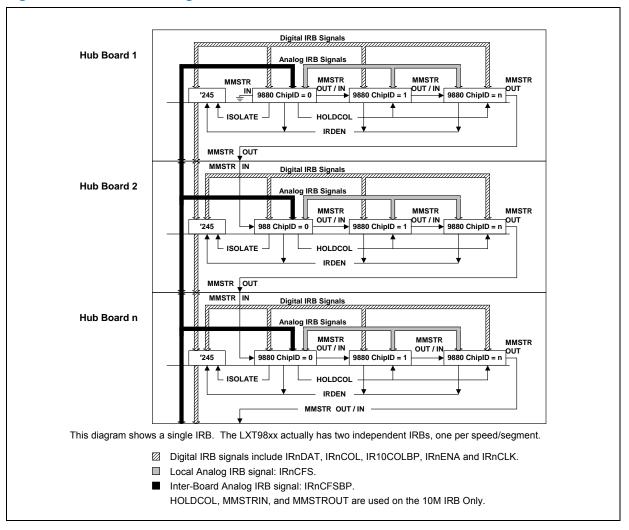

|     | 2.8   | 2.8.1    | peration<br>IRB Signal Types           |    |

|     |       | 2.8.2    | IRB Isolation                          |    |

|     |       | 2.8.3    | 10 Mbps-Only Operation                 |    |

|     |       | 2.8.4    | LXT98x/91x/98x0 Compatibility          |    |

|     | 2.9   |          | rt Operation                           |    |

|     | ۷.5   | 2.9.1    | Preamble Handling                      |    |

|     | 2.10  |          | Management I/F                         |    |

|     | 2.10  |          | SMI Signals                            |    |

|     |       |          | Read and Write Operations              |    |

|     |       |          |                                        |    |

|     |      | 2.10.3 Address Assignment Methods      |     |

|-----|------|----------------------------------------|-----|

|     |      | 2.10.4 Interrupt Functions             |     |

|     | 2.11 | Serial PROM Interface                  |     |

|     | 2.12 | Serial Configuration Interface         | 58  |

| 3.0 | Appl | ication Information                    | 60  |

|     | 3.1  | General Design Guidelines              | 60  |

|     | 3.2  | Typical Applications                   | 60  |

|     | 3.3  | Application Circuitry                  | 61  |

|     |      | 3.3.1 Power and Ground                 | 61  |

|     |      | 3.3.2 MII Terminations                 | 63  |

|     |      | 3.3.3 Twisted-Pair Interface           | 64  |

|     |      | 3.3.4 Clock                            |     |

|     |      | 3.3.5 SMI and PROM Circuits            | 66  |

|     |      | 3.3.6 LED Circuits                     |     |

|     | 3.4  | Inter-Repeater Backplane Compatibility | 69  |

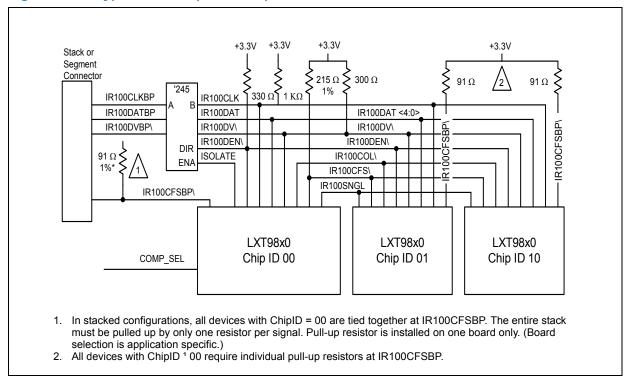

|     |      | 3.4.1 Local Backplane—3.3 V Only       | 70  |

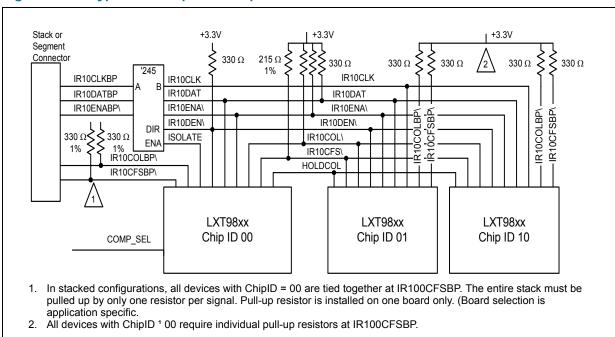

|     |      | 3.4.2 Stack Backplane—3.3 V or 5 V     | 70  |

| 4.0 | Test | Specifications                         | 73  |

| 5.0 | Regi | ster Definitions                       | 87  |

|     | 5.1  | Register Map                           | 87  |

|     | 5.2  | Counter Registers                      |     |

|     |      | 5.2.1 Port Counter Registers           |     |

|     |      | 5.2.2 RMON Counter Registers           |     |

|     | 5.3  | Ethernet Address Registers             |     |

|     |      | 5.3.1 Port Address Registers           |     |

|     |      | 5.3.2 Search Address Registers         |     |

|     | 5.4  | Repeater Port Control Registers        |     |

|     |      | 5.4.1 General Port Control Registers   |     |

|     |      | 5.4.2 Port Link Control Register       |     |

|     |      | 5.4.3 Port Learn Enable Register       |     |

|     | 5.5  | Repeater Port Status Registers         |     |

|     | 5.6  | PHY Port Status Registers              |     |

|     | 5.7  | PHY Port Control Registers             | 109 |

|     | 5.8  | Repeater Port Control/Status Registers | 110 |

|     |      | 5.8.1 Device/Revision Register         | 112 |

|     |      | 5.8.2 LED Control Registers            |     |

|     |      | 5.8.3 LED Global Control Register      | 113 |

|     |      | 5.8.4 Port LED Control Register        | 113 |

|     |      | 5.8.5 LED Timer Control Register       |     |

|     |      | 5.8.6 Repeater Reset Register          |     |

|     |      | 5.8.7 Software Reset Register          |     |

|     |      | 5.8.8 Interrupt Registers              |     |

|     | 5.9  | Serial Controller Registers            |     |

| 6.0 | Mech | nanical Specifications                 | 119 |

# **Figures**

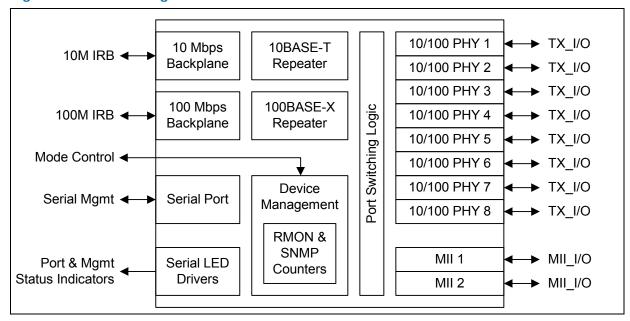

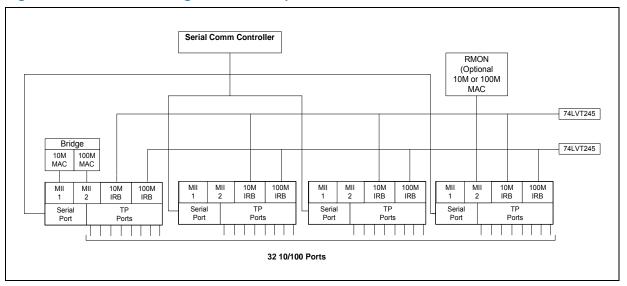

| 1  | Block Diagram                                                     | 9   |

|----|-------------------------------------------------------------------|-----|

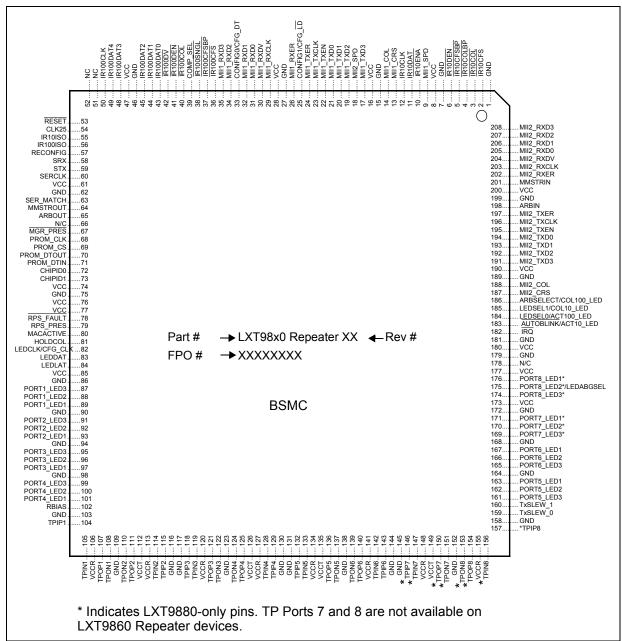

| 2  | Pin Assignments                                                   | 10  |

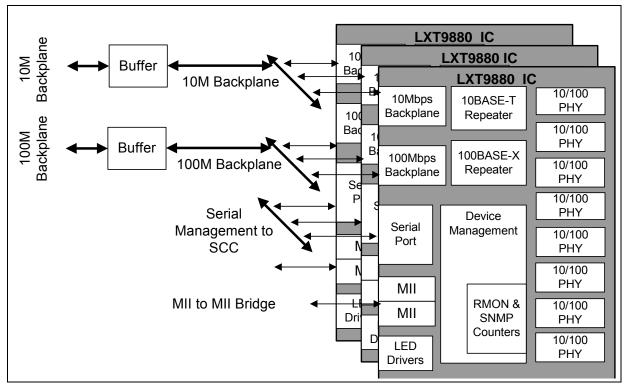

| 3  | Typical LXT988x Managed Repeater Architectures                    | 29  |

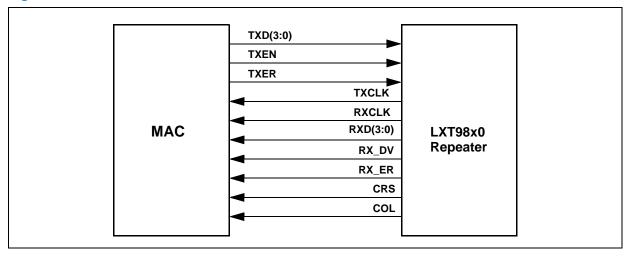

| 4  | MII Interface                                                     | 32  |

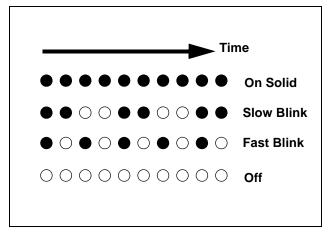

| 5  | LED Blink Rates                                                   | 37  |

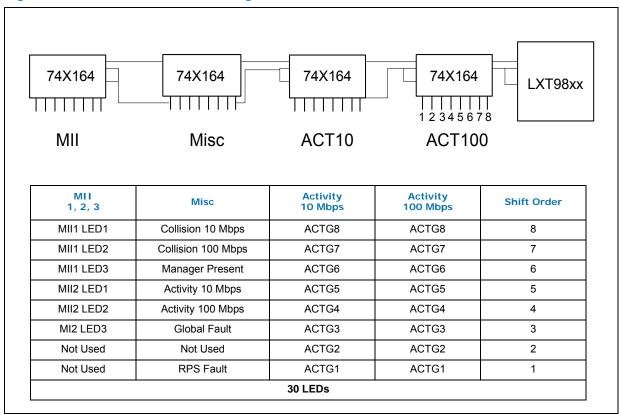

| 6  | Serial LED Shift Loading                                          | 38  |

| 7  | Serial LED Port Signaling                                         | 39  |

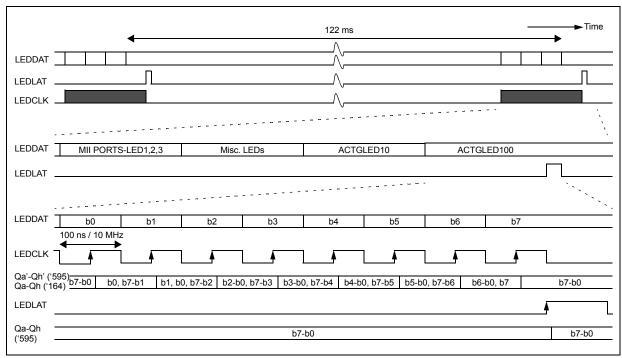

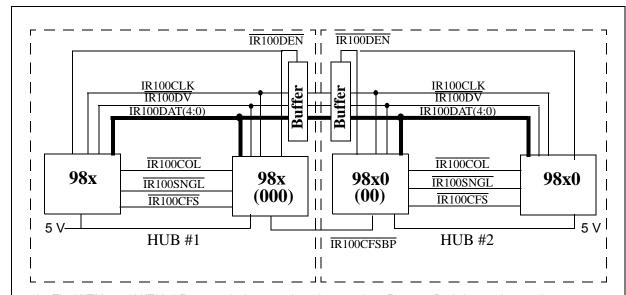

| 8  | 100 Mbps IRB Connection                                           | 47  |

| 9  | IRB Block Diagram                                                 |     |

| 10 | LXT9880 Repeater MII Operation                                    | 50  |

| 11 | Typical SMI Bus Architecture                                      | 50  |

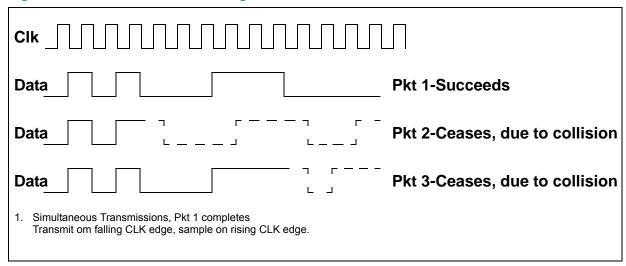

| 12 | SMI Collision Handling                                            | 52  |

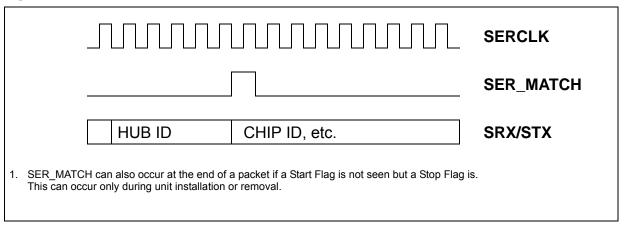

| 13 | SMI Address Match Indication                                      |     |

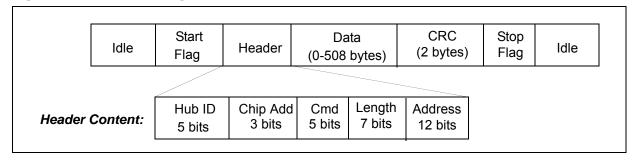

| 14 | Serial Management Frame Format                                    |     |

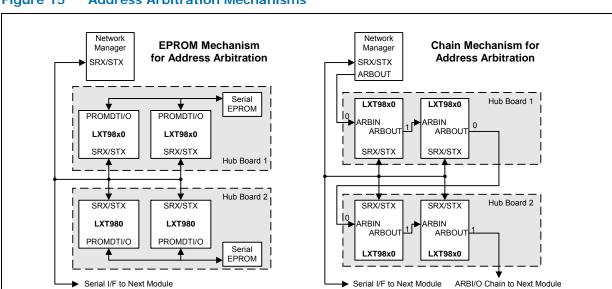

| 15 | Address Arbitration Mechanisms                                    |     |

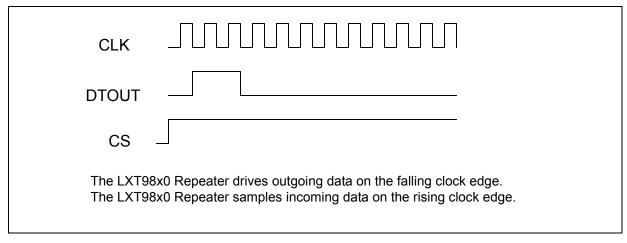

| 16 | Optional R/W Serial PROM Interface                                |     |

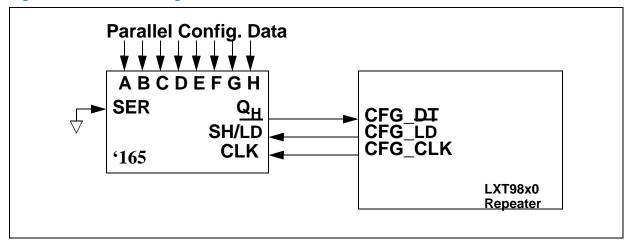

| 17 | Serial Configuration Interface                                    |     |

| 18 | Serial Configuration Interface Signaling                          |     |

| 19 | 8-Port Managed 10/100 Stackable Repeater                          |     |

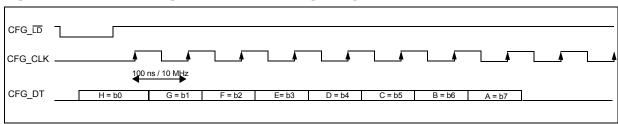

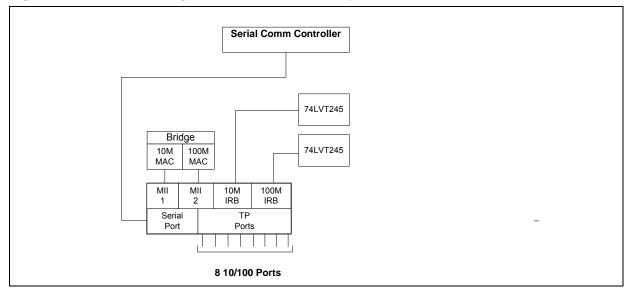

| 20 | 32-Port Managed 10/100 Repeater                                   | 61  |

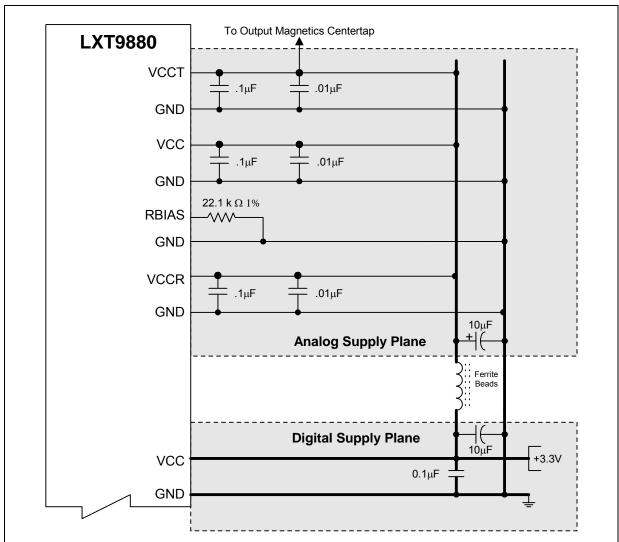

| 21 | Power and Ground Connections                                      |     |

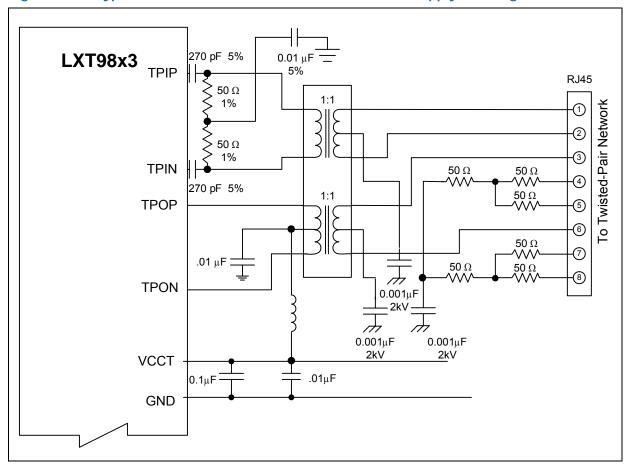

| 22 | Typical Twisted-Pair Port Interface and Power Supply Filtering    |     |

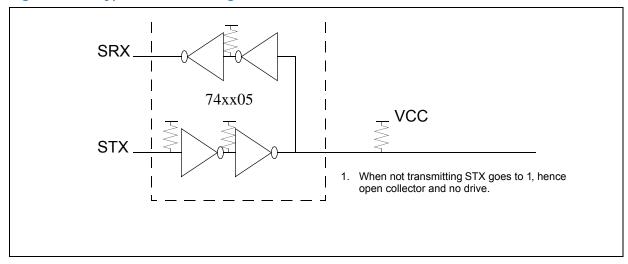

| 23 | Typical Serial Management Interface Connections                   |     |

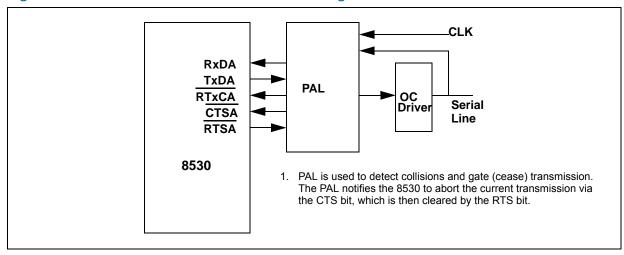

| 24 | Serial Controller Connection Showing PAL                          |     |

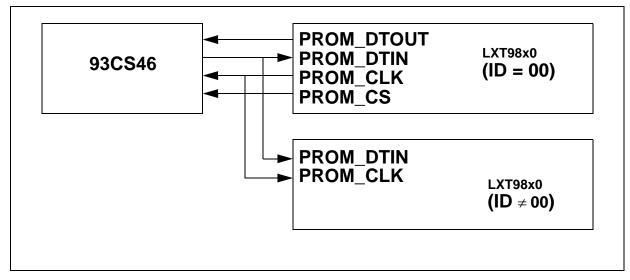

| 25 | Serial PROM Interface                                             |     |

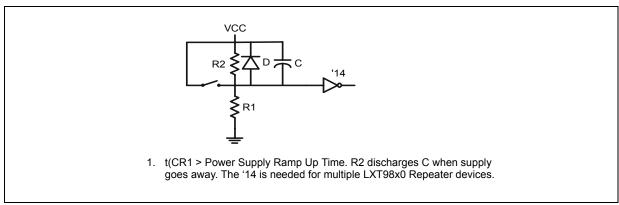

| 26 | Typical Reset Circuit                                             | 67  |

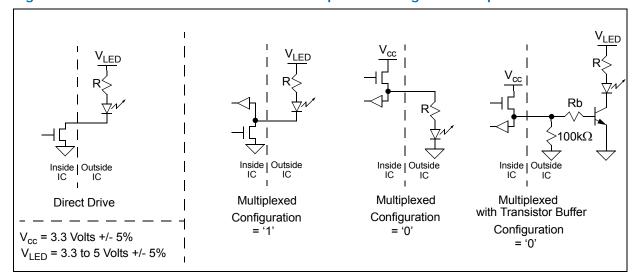

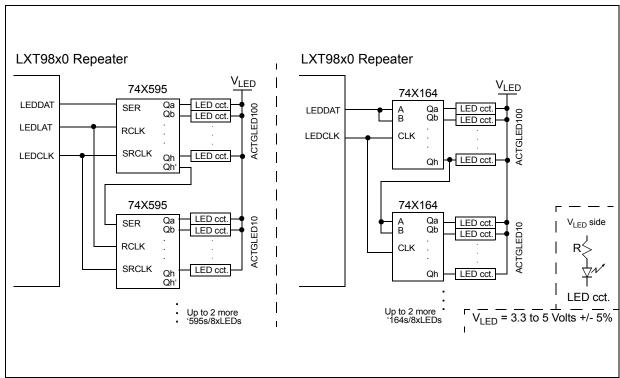

| 27 | LED Circuits - Direct Drive & Multiplexed Configuration Inputs    |     |

| 28 | Serial LED Circuit                                                |     |

| 29 | 100 Mbps Backplane Connection between LXT98x and LXT98x0 Repeater | 71  |

| 30 | Typical 100 Mbps IRB Implementation                               |     |

| 31 | Typical 10 Mbps IRB Implementation                                |     |

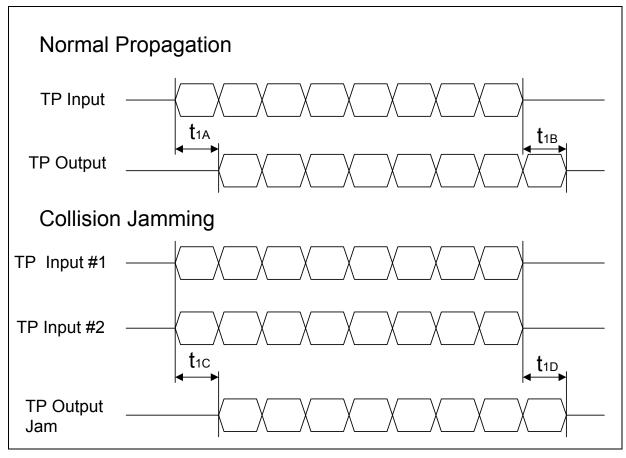

| 32 | 100 Mbps TP Port-to-Port Delay Timing                             |     |

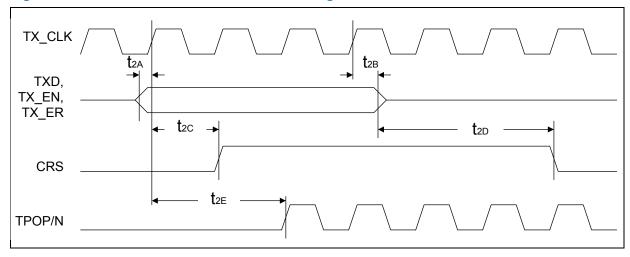

| 33 | 100BASE-TX MII-to-TP Port Timing                                  |     |

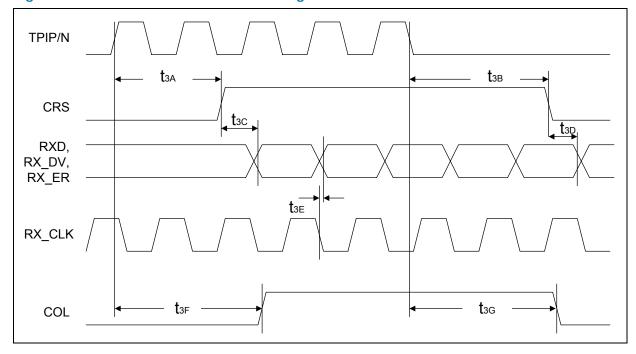

| 34 | 100BASE-TX TP-to-MII Timing                                       |     |

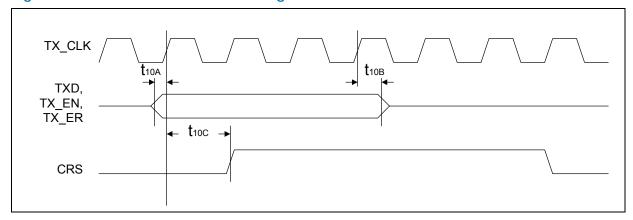

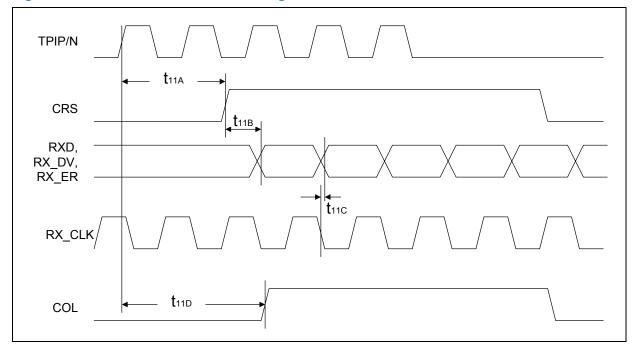

| 35 | 10BASE-T MII-to-TP Timing                                         |     |

| 36 | 10BASE-T TP-to-MII Timing                                         |     |

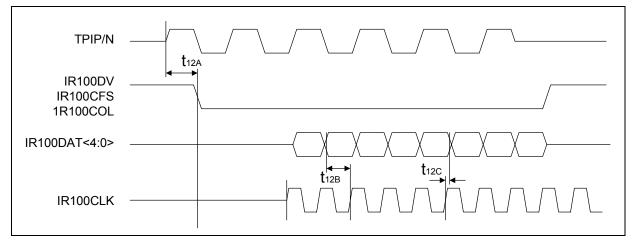

| 37 | 100 Mbps TP-to-IRB Timing                                         | 82  |

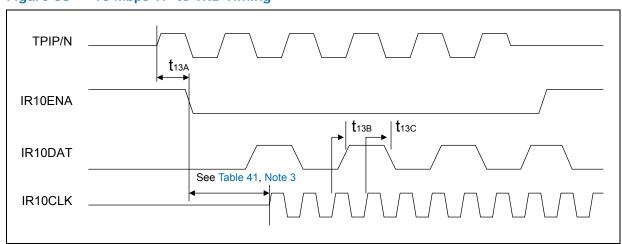

| 38 | 10 Mbps TP-to-IRB Timing                                          |     |

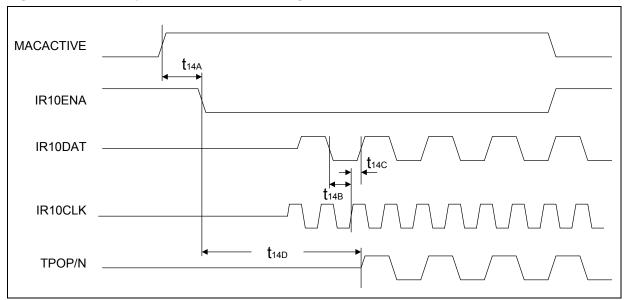

| 39 | 10 Mbps IRB-to-TP Port Timing                                     |     |

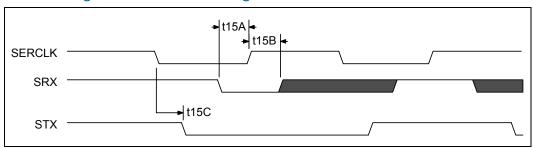

| 40 | Serial Management Interface Timing                                |     |

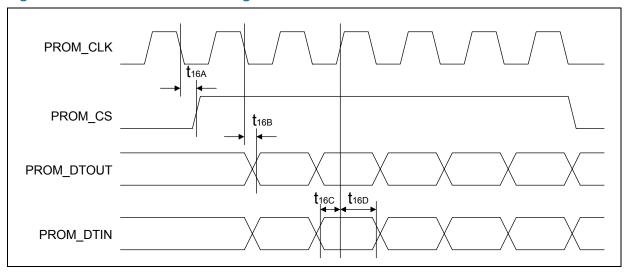

| 41 | PROM Interface Timing                                             |     |

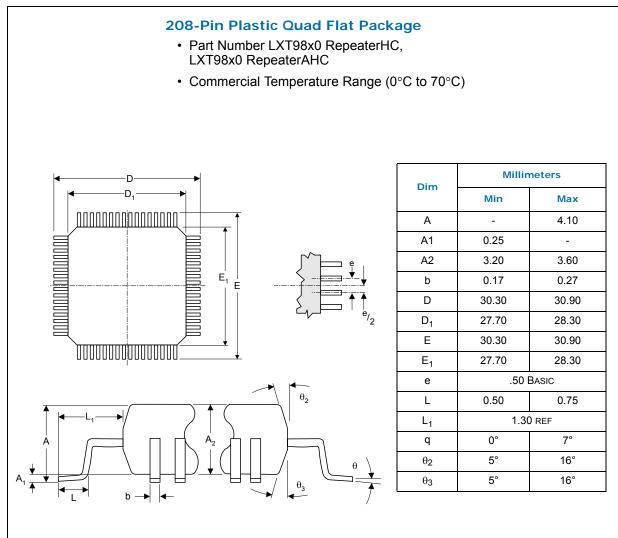

| 42 | Package Specifications for Commercial Temperature                 |     |

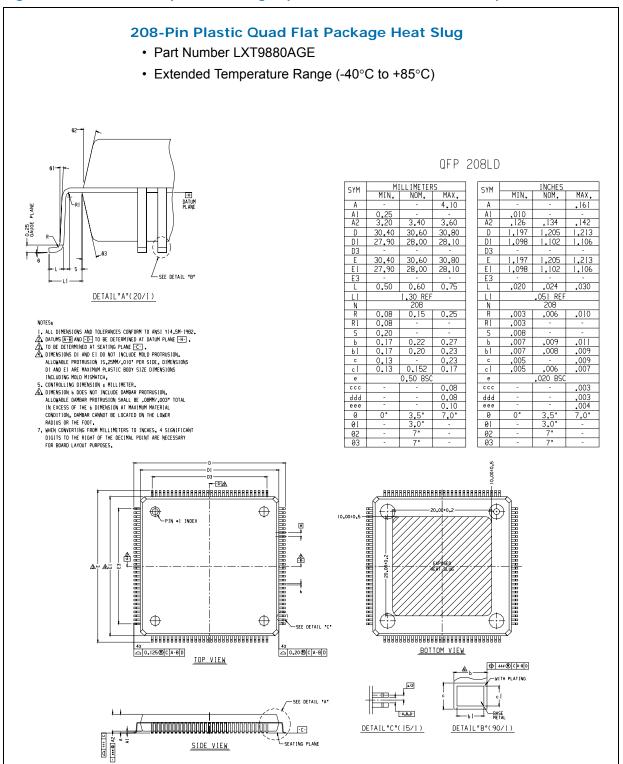

| 43 | LXT98x0 Repeater Package Specifications for Extended Temperature  | 120 |

# **Tables**

| 1  | Signal Types                                       | 11 |

|----|----------------------------------------------------|----|

| 2  | Pins, Numeric Order                                | 11 |

| 3  | MII #1 Signal Descriptions                         | 18 |

| 4  | MII #2 Signal Descriptions                         |    |

| 5  | Inter-Repeater Backplane Signal Descriptions       |    |

| 6  | Twisted-Pair Port Signal Descriptions              |    |

| 7  | Serial Management Interface Signal Descriptions    |    |

| 8  | LED Signal Descriptions                            |    |

| 9  | Power Supply and Indication Signal Descriptions    |    |

| 10 | PROM Interface Signal Descriptions                 |    |

| 11 | Miscellaneous Signal Descriptions                  |    |

| 12 | Serial LED Port Bit Stream                         |    |

| 13 | ACTGLED Display Modes                              |    |

| 14 | LED Terms                                          |    |

| 15 | LED Mode 1 Indications                             |    |

| 16 | LED Mode 2 Indications                             |    |

| 17 | LED Mode 3 Indications                             |    |

|    | LED Mode 4 Indications                             |    |

| 18 | Cascading and Stacking Connections                 |    |

| 19 |                                                    |    |

| 20 | IRB Signal Details                                 |    |

| 21 | SMI Message Fields                                 |    |

| 22 | SMI Header Storage                                 |    |

| 23 | SMI Command Set                                    |    |

| 24 | Typical Serial Management Packets                  |    |

| 25 | LXT98x0 Repeater Magnetics Specifications          |    |

| 26 | Oscillator Manufacturers                           |    |

| 27 | Absolute Maximum Ratings                           |    |

| 28 | Operating Conditions                               |    |

| 29 | Input System Clock <sup>1</sup> Requirements       |    |

| 30 | I/O Electrical Characteristics                     |    |

| 31 | 100 Mbps IRB Electrical Characteristics            |    |

| 32 | 10 Mbps IRB Electrical Characteristics             |    |

| 33 | 100BASE-TX Transceiver Electrical Characteristics  |    |

| 34 | 10BASE-T Transceiver Electrical Characteristics    |    |

| 35 | 100 Mbps TP Port-to-Port Delay Timing Parameters   |    |

| 36 | 100BASE-TX MII-to-TP Port Timing Parameters        |    |

| 37 | 100BASE-TX TP-to-MII Timing Parameters             |    |

| 38 | 10BASE-T MII-to-TP Timing Parameters               |    |

| 39 | 10BASE-T TP-to-MII Timing Parameters               | 81 |

| 40 | 100 Mbps TP-to-IRB Timing Parameters <sup>1</sup>  | 82 |

| 41 | 10 Mbps TP-to-IRB Timing Parameters <sup>1</sup>   | 83 |

| 42 | 10 Mbps IRB-to-TP Port Timing Parameters           | 84 |

| 43 | Serial Management Interface Timing Characteristics | 84 |

| 44 | PROM Interface Timing Characteristics              | 85 |

| 45 | Register Map                                       |    |

| 46 | Port Counter Registers                             |    |

| 47 | RMON Counter Registers - 10 Mbps                   |    |

| 48 | RMON Counter Registers - 100 Mbps                  | 99 |

| 49 | Ethernet Address RegisterBit Assignments                  | 100 |

|----|-----------------------------------------------------------|-----|

| 50 | Port Address Tracking Registers                           |     |

| 51 | Search Address/Search Address Match Register              | 101 |

| 52 | Search Address RegisterBit Assignments                    |     |

| 53 | Search Match Address Bit Assignments                      |     |

| 54 | Search Match Address Bit Definitions                      | 101 |

| 55 | Port Control Register Bit Assignments                     |     |

| 56 | General Port Control Registers                            |     |

| 57 | Port Link Control and Status Register Bit Assignments     |     |

| 58 | Port Link Control Register                                |     |

| 59 | Port Learn Enable Register                                | 104 |

| 60 | Port Learn Enable Register                                | 104 |

| 61 | Port Status Register Bit Assignments                      |     |

| 62 | Port Status Registers                                     |     |

| 63 | MII Speed Status Bit Assignments                          | 105 |

| 64 | MII Status Bit Definitions                                | 105 |

| 65 | Auto-Negotiation Registers                                | 106 |

| 66 | Auto-Negotiate Link Partner Advertisement Bit Definitions | 106 |

| 67 | Auto-Negotiate Expansion Bit Definitions                  | 107 |

| 68 | PHY Port Status Register Summary                          |     |

| 69 | PHY Port Status Register Bit Definitions                  |     |

| 70 | Auto-Negotiation Advertisement Registers                  |     |

| 71 | Auto Negotiate Advertisement Bit Definitions              | 109 |

| 72 | PHY Port Control Register                                 | 109 |

| 73 | PHY Port Control Bit Definitions                          | 110 |

| 74 | Configuration Registers                                   | 110 |

| 75 | Repeater Configuration Register                           | 111 |

| 76 | Repeater Serial Configuration                             |     |

| 77 | Device/Revision Register Bit Assignment                   | 113 |

| 78 | Global Fault LED Bit Assignments                          | 113 |

| 79 | LED Configuration                                         | 113 |

| 80 | Port LED1, 2, 3 Control Encodings                         | 114 |

| 81 | LED Timer Control Register Bit Assignments                | 114 |

| 82 | Repeater Reset                                            | 115 |

| 83 | Software Reset                                            | 115 |

| 84 | Interrupt Status/Mask Register                            | 115 |

| 85 | Interrupt Status Register Bit Definitions                 | 116 |

| 86 | Interrupt Mask Bit Definitions                            |     |

| 87 | Configuration Registers                                   | 117 |

| 88 | Assign Addr 1                                             |     |

| 89 | Assign Addr 2                                             | 118 |

| 90 | PROM Addr 1                                               | 118 |

| 91 | PROM Addr 2                                               | 118 |

# **Revision History**

Revision 5.0 Revision Date: 14 August 2007

First release of this document from Cortina Systems, Inc.

Revision 004 Revision Date: 29 March 2006

- Added Section 7.1, "Top Label Markings" on page 119.

- Added Section 8.0, "Product Ordering Information" on page 121.

Revision 003 Revision Date: August 2001

Changed Absolute Maximum Ratings Supply Voltage value to 4.0 V.

Revision 002 Revision Date: January 2001

- · Added extended temperature range to title page.

- Modified LXT98x0 Repeater Pins, Numeric Order table (Pins 10, 11, 17, 19, 20, 185.

- · Modified clock requirements language.

- · Replaced TBD with 3.15 V under Reset.

- Under Twisted Pair Interface, 4th bullet: Replaced text containing TBDs with: A ferrite bead with a total maximum current rating of 1.5Amp is recommended.

- · Modified Oscillator Manufacturers table.

- · Modified Absolute Maximum Ratings table.

- · Modified Operating Conditions table.

- Mechanical Specifications: Add part number LXT98x0 RepeaterAHC to LXT98x0 Repeater Package Specifications

Commercial Temperature figure; Add page for LXT98x0 Repeater Package Specifications Extended Temperature figure.

Revision 001 Revision Date: January 2001

Initial release.

Figure 1 Block Diagram

# 1.0 Pin Assignments and Signal Descriptions

Figure 2 Pin Assignments

#### Table 1 **Signal Types**

| Туре | Name          | Definition                                        |  |

|------|---------------|---------------------------------------------------|--|

| I    | Input         | Standard input-only signal.                       |  |

| 0    | Output        | tandard output-only signal.                       |  |

| I/O  | Bidirectional | nput and output signal.                           |  |

| Α    | Analog        | Current source signal.                            |  |

| OD   | Open Drain    | Output that will only drive the signal Low.       |  |

| os   | Open Source   | Output that will only drive the signal High.      |  |

| PD   | Pull Down     | Internal, weak pull down signal.                  |  |

| PU   | Pull Up       | Internal, weak pull up signal.                    |  |

| NC   | No Clamp      | Pad does not clamp input in the absence of power. |  |

#### Pins, Numeric Order (Sheet 1 of 7) Table 2

| Pin | Symbol         | Type <sup>1,2</sup> | Reference<br>for Full<br>Description |

|-----|----------------|---------------------|--------------------------------------|

| 1.  | GND            | _                   | Table 9 on page 26                   |

| 2.  | IR10CFS        | A, I/O, OD          | Table 5 on page 20                   |

| 3.  | ĪR10COL        | I/O, OD, PU         | Table 5 on page 20                   |

| 4.  | IR10COLBP I/O, | OD                  | Table 5 on page 20                   |

| 5.  | IR10CFSBP A    | I/O, OD             | Table 5 on page 20                   |

| 6.  | IR10DEN O,     | OD                  | Table 5 on page 20                   |

| 7.  | GND            | _                   | Table 9 on page 26                   |

| 8.  | VCC            | _                   | Table 9 on page 26                   |

| 9.  | MII1_SPD       | I, PU               | Table 3 on page 18                   |

| 10. | ĪR10ENA        | 0                   | Table 3 on page 18                   |

| 11. | IR10DAT        | 0                   | Table 3 on page 18                   |

| 12. | IR10CLK        | I/O                 | Table 5 on page 20                   |

| 13. | MII1_CRS       | 0                   | Table 3 on page 18                   |

| 14. | MII1_COL       | 0                   | Table 3 on page 18                   |

| 15. | GND            | _                   | Table 9 on page 26                   |

| 16. | VCC            | _                   | Table 9 on page 26                   |

| 17. | MII1_TXD3      | I                   | Table 3 on page 18                   |

| 18. | MII2_SPD       | I                   | Table 3 on page 18                   |

| 19. | MII1_TXD2      | I                   | Table 3 on page 18                   |

| 20. | MII1_TXD1      | I                   | Table 3 on page 18                   |

<sup>1.</sup> Refer to Table 1 for Signal Type definitions.

Pins are 5 V tolerant, unless indicated.

Input must be static; Refer to Section 3.3.6.2, LED Pins Multiplexed

#### Table 2 Pins, Numeric Order (Sheet 2 of 7)

| 21.         MII1_TXD0         I         Table 3 on page 18           22.         MII1_TXEN         I         Table 3 on page 18           23.         MII1_TXCLK         I         Table 3 on page 18           24.         MII1_TXER         I         Table 3 on page 18           25.         CONFIGI/CF         I/O         Table 11 on page 28           26.         MIIT_RXER         I         Table 9 on page 26           28.         VCC         —         Table 9 on page 26           29.         MIIT_RXCLK         O         Table 3 on page 18           30.         MIIT_RXDV         O         Table 3 on page 18           31.         MIIT_RXDD         O         Table 3 on page 18           32.         MIIT_RXD1         O         Table 3 on page 18           33.         CONFIG/CFG_DT         I         Table 3 on page 18           34.         MIIT_RXD2         O         Table 3 on page 18           35.         MIIT_RXD3         O         Table 5 on page 20           37.         IR100CFS A         I/O         Table 5 on page 20           38.         IR100SNGL I/O         Table 5 on page 20           40.         IR100COL         O         Table 5 on pa | Pin | Symbol        | Type <sup>1,2</sup> | Reference<br>for Full<br>Description |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|---------------------|--------------------------------------|

| 23.         MII1_TXCLK         I         Table 3 on page 18           24.         MII1_TXER         I         Table 3 on page 18           25.         CONFIGI/CF         I/O         Table 11 on page 28           26.         MII1RXER         I         Table 3 on page 18           27.         GND         —         Table 9 on page 26           28.         VCC         —         Table 9 on page 26           29.         MII1_RXCLK         O         Table 3 on page 18           30.         MII1_RXDV         O         Table 3 on page 18           31.         MII1_RXD0         O         Table 3 on page 18           32.         MII1_RXD1         O         Table 3 on page 18           33.         CONFIG/CFG_DT         I         Table 3 on page 18           34.         MII1_RXD2         O         Table 3 on page 18           35.         MII1_RXD3         O         Table 3 on page 18           36.         IR100CFS A         I/O         Table 5 on page 20           37.         IR100CFS A         I/O         Table 5 on page 20           38.         IR100CFS A         I/O         Table 5 on page 20           40.         IR100CFS A         I/O              | 21. | MII1_TXD0     | I                   | Table 3 on page 18                   |

| 24.         MII1_TXER         I         Table 3 on page 18           25.         CONFIG1/CF         I/O         Table 11 on page 28           26.         MII1RXER         I         Table 3 on page 18           27.         GND         —         Table 9 on page 26           28.         VCC         —         Table 9 on page 26           29.         MII1_RXCLK         O         Table 3 on page 18           30.         MII1_RXDV         O         Table 3 on page 18           31.         MII1_RXD0         O         Table 3 on page 18           32.         MII1_RXD1         O         Table 3 on page 18           33.         CONFIG/CFG_DT         I         Table 3 on page 18           35.         MII1_RXD3         O         Table 3 on page 18           36.         IR100CFS A         I/O         Table 5 on page 20           37.         IR100CFS A         I/O         Table 5 on page 20           38.         IR100SNGL I/O         Table 5 on page 20           39.         COMP_SEL         AI         Table 5 on page 20           40.         IR100CDL         O         Table 5 on page 20           41.         IR100DAT         I/O         Table 5 on page 2 | 22. | MII1_TXEN     | ı                   | Table 3 on page 18                   |

| 25.         CONFIG1/CF         I/O         Table 11 on page 28           26.         MII1RXER         I         Table 3 on page 18           27.         GND         —         Table 9 on page 26           28.         VCC         —         Table 9 on page 26           29.         MII1_RXCLK         O         Table 3 on page 18           30.         MII1_RXDV         O         Table 3 on page 18           31.         MII1_RXD0         O         Table 3 on page 18           32.         MII1_RXD1         O         Table 3 on page 18           33.         CONFIG/CFG_DT         I         Table 3 on page 18           34.         MII1_RXD2         O         Table 3 on page 18           35.         MII1_RXD3         O         Table 3 on page 18           36.         IR100CFS A         I/O         Table 5 on page 20           37.         IR100CFS A         I/O         Table 5 on page 20           38.         IR100SNGL I/O         Table 5 on page 20           40.         IR100CFSBP A         I/O         Table 5 on page 20           41.         IR100COL         O         Table 5 on page 20           42.         IR100COL         O         Table 5 on pag | 23. | MII1_TXCLK    | I                   | Table 3 on page 18                   |

| 26. MII1RXER I Table 3 on page 18 27. GND — Table 9 on page 26 28. VCC — Table 9 on page 26 29. MII1_RXCLK O Table 3 on page 18 30. MII1_RXDV O Table 3 on page 18 31. MII1_RXDO O Table 3 on page 18 32. MII1_RXD1 O Table 3 on page 18 33. CONFIG/CFG_DT I Table 12 on page 39 34. MII1_RXD2 O Table 3 on page 18 35. MII1_RXD3 O Table 3 on page 18 36. IR100CFS A I/O Table 5 on page 20 37. IR100CFSBP A I/O Table 5 on page 20 38. IR100SNGL I/O Table 5 on page 20 40. IR100COL O Table 5 on page 20 41. IR100DEN O Table 5 on page 20 42. IR100DV I/O Table 5 on page 20 43. IR100DAT0 I/O Table 5 on page 20 44. IR100DAT1 I/O Table 5 on page 20 45. IR100DAT2 I/O Table 5 on page 20 46. GND — Table 9 on page 26 47. VCC — Table 9 on page 26 48. IR100DAT3 I/O Table 5 on page 20 50. IR100CLK I/O Table 5 on page 20 51. NC — Table 11 on page 28 52. NC — Table 11 on page 28                                                                                                                                                                                                                                                                                                          | 24. | MII1_TXER     | I                   | Table 3 on page 18                   |

| 27.         GND         —         Table 9 on page 26           28.         VCC         —         Table 9 on page 26           29.         MII1_RXCLK         O         Table 3 on page 18           30.         MII1_RXDV         O         Table 3 on page 18           31.         MII1_RXD0         O         Table 3 on page 18           32.         MII1_RXD1         O         Table 3 on page 18           33.         CONFIG/CFG_DT         I         Table 12 on page 39           34.         MII1_RXD2         O         Table 3 on page 18           35.         MII1_RXD3         O         Table 3 on page 18           36.         IR100CFS A         I/O         Table 5 on page 20           37.         IR100CFSBP A         I/O         Table 5 on page 20           38.         IR100SNGL I/O         Table 5 on page 20           39.         COMP_SEL         AI         Table 5 on page 20           40.         IR100COL         O         Table 5 on page 20           41.         IR100DEN         O         Table 5 on page 20           42.         IR100DAT0         I/O         Table 5 on page 20           44.         IR100DAT2         I/O         Table 5 on page | 25. | CONFIG1/CF    | I/O                 | Table 11 on page 28                  |

| 28.         VCC         —         Table 9 on page 26           29.         MII1_RXCLK         O         Table 3 on page 18           30.         MII1_RXDV         O         Table 3 on page 18           31.         MII1_RXD0         O         Table 3 on page 18           32.         MII1_RXD1         O         Table 3 on page 18           33.         CONFIG/CFG_DT         I         Table 12 on page 39           34.         MII1_RXD2         O         Table 3 on page 18           35.         MII1_RXD3         O         Table 3 on page 18           36.         IR100CFS A         I/O         Table 5 on page 20           37.         IR100CFS A         I/O         Table 5 on page 20           38.         IR100SNGL I/O         Table 5 on page 20           39.         COMP_SEL         AI         Table 5 on page 20           40.         IR100COL         O         Table 5 on page 20           41.         IR100DEN         O         Table 5 on page 20           42.         IR100DAT0         I/O         Table 5 on page 20           43.         IR100DAT1         I/O         Table 5 on page 20           44.         IR100DAT2         I/O         Table 5 o | 26. | MII1RXER      | I                   | Table 3 on page 18                   |

| 29. MII1_RXCLK O Table 3 on page 18 30. MII1_RXDV O Table 3 on page 18 31. MII1_RXDO O Table 3 on page 18 32. MII1_RXD1 O Table 3 on page 18 33. CONFIG/CFG_DT I Table 12 on page 39 34. MII1_RXD2 O Table 3 on page 18 35. MII1_RXD3 O Table 3 on page 18 36. IR100CFS A I/O Table 5 on page 20 37. IR100CFSBP A I/O Table 5 on page 20 38. IR100SNGL I/O Table 5 on page 20 40. IR100COL O Table 5 on page 20 41. IR100DEN O Table 5 on page 20 42. IR100DV I/O Table 5 on page 20 43. IR100DATO I/O Table 5 on page 20 44. IR100DATO I/O Table 5 on page 20 45. IR100DAT2 I/O Table 5 on page 20 46. GND — Table 5 on page 20 47. VCC — Table 9 on page 20 48. IR100DAT3 I/O Table 5 on page 20 49. IR100DAT4 I/O Table 5 on page 20 50. IR100CLK I/O Table 5 on page 20 51. NC — Table 11 on page 28 52. NC — Table 11 on page 28 53. RESET I Table 11 on page 28                                                                                                                                                                                                                                                                                                                                 | 27. | GND           | _                   | Table 9 on page 26                   |

| 30. MII1_RXDV O Table 3 on page 18 31. MII1_RXD0 O Table 3 on page 18 32. MII1_RXD1 O Table 3 on page 18 33. CONFIG/CFG_DT I Table 12 on page 39 34. MII1_RXD2 O Table 3 on page 18 35. MII1_RXD3 O Table 3 on page 18 36. IR100CFS A I/O Table 5 on page 20 37. IR100CFSBP A I/O Table 5 on page 20 38. IR100SNGL I/O Table 5 on page 20 39. COMP_SEL AI Table 5 on page 20 40. IR100COL O Table 5 on page 20 41. IR100DEN O Table 5 on page 20 42. IR100DV I/O Table 5 on page 20 43. IR100DAT0 I/O Table 5 on page 20 44. IR100DAT1 I/O Table 5 on page 20 45. IR100DAT2 I/O Table 5 on page 20 46. GND — Table 9 on page 26 47. VCC — Table 9 on page 26 48. IR100DAT4 I/O Table 5 on page 20 50. IR100CLK I/O Table 5 on page 20 51. NC — Table 11 on page 28 52. NC — Table 11 on page 28 53. RESET I Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                       | 28. | VCC           | _                   | Table 9 on page 26                   |

| 31.         MII1_RXD0         O         Table 3 on page 18           32.         MII1_RXD1         O         Table 3 on page 18           33.         CONFIG/CFG_DT         I         Table 12 on page 39           34.         MII1_RXD2         O         Table 3 on page 18           35.         MII1_RXD3         O         Table 5 on page 20           36.         IR100CFS A         I/O         Table 5 on page 20           37.         IR100CFSBP A         I/O         Table 5 on page 20           38.         IR100SNGL I/O         Table 5 on page 20           39.         COMP_SEL         AI         Table 5 on page 20           40.         IR100COL         O         Table 5 on page 20           41.         IR100DEN         O         Table 5 on page 20           42.         IR100DAT0         I/O         Table 5 on page 20           43.         IR100DAT0         I/O         Table 5 on page 20           44.         IR100DAT2         I/O         Table 5 on page 20           45.         IR100DAT2         I/O         Table 9 on page 26           47.         VCC         —         Table 9 on page 26           48.         IR100DAT3         I/O         Tabl | 29. | MII1_RXCLK    | 0                   | Table 3 on page 18                   |

| 32. MII1_RXD1 O Table 3 on page 18 33. CONFIG/CFG_DT I Table 12 on page 39 34. MII1_RXD2 O Table 3 on page 18 35. MII1_RXD3 O Table 3 on page 18 36. IR100CFS A I/O Table 5 on page 20 37. IR100CFSBP A I/O Table 5 on page 20 38. IR100SNGL I/O Table 5 on page 20 39. COMP_SEL AI Table 5 on page 20 40. IR100COL O Table 5 on page 20 41. IR100DEN O Table 5 on page 20 42. IR100DV I/O Table 5 on page 20 43. IR100DAT0 I/O Table 5 on page 20 44. IR100DAT1 I/O Table 5 on page 20 45. IR100DAT1 I/O Table 5 on page 20 46. GND — Table 5 on page 20 47. VCC — Table 9 on page 26 47. VCC — Table 9 on page 26 48. IR100DAT3 I/O Table 5 on page 20 50. IR100CLK I/O Table 5 on page 20 51. NC — Table 11 on page 28 52. NC — Table 11 on page 28 53. RESET I Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                | 30. | MII1_RXDV     | 0                   | Table 3 on page 18                   |

| 33. CONFIG/CFG_DT I Table 12 on page 39  34. MII1_RXD2 O Table 3 on page 18  35. MII1_RXD3 O Table 3 on page 18  36. IR100CFS A I/O Table 5 on page 20  37. IR100CFSBP A I/O Table 5 on page 20  38. IR100SNGL I/O Table 5 on page 20  39. COMP_SEL AI Table 5 on page 20  40. IR100COL O Table 5 on page 20  41. IR100DEN O Table 5 on page 20  42. IR100DV I/O Table 5 on page 20  43. IR100DAT0 I/O Table 5 on page 20  44. IR100DAT1 I/O Table 5 on page 20  45. IR100DAT1 I/O Table 5 on page 20  46. GND — Table 9 on page 20  47. VCC — Table 9 on page 26  48. IR100DAT3 I/O Table 5 on page 20  49. IR100DAT4 I/O Table 5 on page 20  50. IR100CLK I/O Table 5 on page 20  51. NC — Table 11 on page 28  52. NC — Table 11 on page 28  53. RESET I Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                       | 31. | MII1_RXD0     | 0                   | Table 3 on page 18                   |

| 34. MII1_RXD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32. | MII1_RXD1     | 0                   | Table 3 on page 18                   |

| 35. MII1_RXD3 O Table 3 on page 18 36. IR100CFS A I/O Table 5 on page 20 37. IR100CFSBP A I/O Table 5 on page 20 38. IR100SNGL I/O Table 5 on page 20 39. COMP_SEL AI Table 5 on page 20 40. IR100COL O Table 5 on page 20 41. IR100DEN O Table 5 on page 20 42. IR100DV I/O Table 5 on page 20 43. IR100DAT0 I/O Table 5 on page 20 44. IR100DAT1 I/O Table 5 on page 20 45. IR100DAT2 I/O Table 5 on page 20 46. GND — Table 9 on page 20 47. VCC — Table 9 on page 26 48. IR100DAT3 I/O Table 5 on page 20 49. IR100DAT4 I/O Table 5 on page 20 50. IR100CLK I/O Table 5 on page 20 51. NC — Table 11 on page 28 52. NC — Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33. | CONFIG/CFG_DT | I                   | Table 12 on page 39                  |

| 36.         IR100CFS A         I/O         Table 5 on page 20           37.         IR100CFSBP A         I/O         Table 5 on page 20           38.         IR100SNGL I/O         Table 5 on page 20           39.         COMP_SEL         AI         Table 5 on page 20           40.         IR100COL         O         Table 5 on page 20           41.         IR100DEN         O         Table 5 on page 20           42.         IR100DATO         I/O         Table 5 on page 20           43.         IR100DAT0         I/O         Table 5 on page 20           44.         IR100DAT1         I/O         Table 5 on page 20           45.         IR100DAT2         I/O         Table 5 on page 20           46.         GND         —         Table 9 on page 26           47.         VCC         —         Table 9 on page 26           48.         IR100DAT3         I/O         Table 5 on page 20           49.         IR100CLK         I/O         Table 5 on page 20           50.         IR100CLK         I/O         Table 5 on page 20           51.         NC         —         Table 11 on page 28           52.         NC         —         Table 11 on page 28        | 34. | MII1_RXD2     | 0                   | Table 3 on page 18                   |

| 37.         IR100CFSBP A         I/O         Table 5 on page 20           38.         IR100SNGL I/O         Table 5 on page 20           39.         COMP_SEL         AI         Table 5 on page 20           40.         IR100COL         O         Table 5 on page 20           41.         IR100DEN         O         Table 5 on page 20           42.         IR100DATO         I/O         Table 5 on page 20           43.         IR100DATO         I/O         Table 5 on page 20           44.         IR100DAT1         I/O         Table 5 on page 20           45.         IR100DAT2         I/O         Table 5 on page 20           46.         GND         —         Table 9 on page 26           47.         VCC         —         Table 9 on page 26           48.         IR100DAT3         I/O         Table 5 on page 20           49.         IR100DAT4         I/O         Table 5 on page 20           50.         IR100CLK         I/O         Table 5 on page 20           51.         NC         —         Table 11 on page 28           52.         NC         —         Table 11 on page 28                                                                               | 35. | MII1_RXD3     | 0                   | Table 3 on page 18                   |

| 38.         IR100SNGL I/O         Table 5 on page 20           39.         COMP_SEL         AI         Table 5 on page 20           40.         IR100COL         O         Table 5 on page 20           41.         IR100DEN         O         Table 5 on page 20           42.         IR100DV I/O         Table 5 on page 20           43.         IR100DAT0         I/O         Table 5 on page 20           44.         IR100DAT1         I/O         Table 5 on page 20           45.         IR100DAT2         I/O         Table 5 on page 20           46.         GND         —         Table 9 on page 26           47.         VCC         —         Table 9 on page 26           48.         IR100DAT3         I/O         Table 5 on page 20           49.         IR100DAT4         I/O         Table 5 on page 20           50.         IR100CLK         I/O         Table 5 on page 20           51.         NC         —         Table 11 on page 28           52.         NC         —         Table 11 on page 28                                                                                                                                                                   | 36. | ĪR100CFS A    | I/O                 | Table 5 on page 20                   |

| 39. COMP_SEL AI Table 5 on page 20 40. IR100COL O Table 5 on page 20 41. IR100DEN O Table 5 on page 20 42. IR100DV I/O Table 5 on page 20 43. IR100DAT0 I/O Table 5 on page 20 44. IR100DAT1 I/O Table 5 on page 20 45. IR100DAT2 I/O Table 5 on page 20 46. GND — Table 9 on page 26 47. VCC — Table 9 on page 26 48. IR100DAT3 I/O Table 5 on page 20 49. IR100DAT4 I/O Table 5 on page 20 50. IR100CLK I/O Table 5 on page 20 51. NC — Table 11 on page 28 52. NC — Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37. | IR100CFSBP A  | I/O                 | Table 5 on page 20                   |

| 40. IR100COL O Table 5 on page 20 41. IR100DEN O Table 5 on page 20 42. IR100DV I/O Table 5 on page 20 43. IR100DAT0 I/O Table 5 on page 20 44. IR100DAT1 I/O Table 5 on page 20 45. IR100DAT2 I/O Table 5 on page 20 46. GND — Table 9 on page 26 47. VCC — Table 9 on page 26 48. IR100DAT3 I/O Table 5 on page 20 49. IR100DAT4 I/O Table 5 on page 20 50. IR100CLK I/O Table 5 on page 20 51. NC — Table 11 on page 28 52. NC — Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38. | IR100SNGL I/O |                     | Table 5 on page 20                   |

| 41.       IR100DEN       O       Table 5 on page 20         42.       IR100DV I/O       Table 5 on page 20         43.       IR100DAT0       I/O       Table 5 on page 20         44.       IR100DAT1       I/O       Table 5 on page 20         45.       IR100DAT2       I/O       Table 5 on page 20         46.       GND       —       Table 9 on page 26         47.       VCC       —       Table 9 on page 26         48.       IR100DAT3       I/O       Table 5 on page 20         49.       IR100DAT4       I/O       Table 5 on page 20         50.       IR100CLK       I/O       Table 5 on page 20         51.       NC       —       Table 11 on page 28         52.       NC       —       Table 11 on page 28         53.       RESET       I       Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                             | 39. | COMP_SEL      | Al                  | Table 5 on page 20                   |

| 42.       IR100DV I/O       Table 5 on page 20         43.       IR100DAT0       I/O       Table 5 on page 20         44.       IR100DAT1       I/O       Table 5 on page 20         45.       IR100DAT2       I/O       Table 5 on page 20         46.       GND       —       Table 9 on page 26         47.       VCC       —       Table 9 on page 26         48.       IR100DAT3       I/O       Table 5 on page 20         49.       IR100DAT4       I/O       Table 5 on page 20         50.       IR100CLK       I/O       Table 5 on page 20         51.       NC       —       Table 11 on page 28         52.       NC       —       Table 11 on page 28         53.       RESET       I       Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40. | ĪR100COL      | 0                   | Table 5 on page 20                   |

| 43.       IR100DAT0       I/O       Table 5 on page 20         44.       IR100DAT1       I/O       Table 5 on page 20         45.       IR100DAT2       I/O       Table 5 on page 20         46.       GND       —       Table 9 on page 26         47.       VCC       —       Table 9 on page 26         48.       IR100DAT3       I/O       Table 5 on page 20         49.       IR100DAT4       I/O       Table 5 on page 20         50.       IR100CLK       I/O       Table 5 on page 20         51.       NC       —       Table 11 on page 28         52.       NC       —       Table 11 on page 28         53.       RESET       I       Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41. | IR100DEN      | 0                   | Table 5 on page 20                   |

| 44.       IR100DAT1       I/O       Table 5 on page 20         45.       IR100DAT2       I/O       Table 5 on page 20         46.       GND       —       Table 9 on page 26         47.       VCC       —       Table 9 on page 26         48.       IR100DAT3       I/O       Table 5 on page 20         49.       IR100DAT4       I/O       Table 5 on page 20         50.       IR100CLK       I/O       Table 5 on page 20         51.       NC       —       Table 11 on page 28         52.       NC       —       Table 11 on page 28         53.       RESET       I       Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42. | IR100DV I/O   |                     | Table 5 on page 20                   |

| 45.       IR100DAT2       I/O       Table 5 on page 20         46.       GND       —       Table 9 on page 26         47.       VCC       —       Table 9 on page 26         48.       IR100DAT3       I/O       Table 5 on page 20         49.       IR100DAT4       I/O       Table 5 on page 20         50.       IR100CLK       I/O       Table 5 on page 20         51.       NC       —       Table 11 on page 28         52.       NC       —       Table 11 on page 28         53.       RESET       I       Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43. | IR100DAT0     | I/O                 | Table 5 on page 20                   |

| 46. GND — Table 9 on page 26 47. VCC — Table 9 on page 26 48. IR100DAT3 I/O Table 5 on page 20 49. IR100DAT4 I/O Table 5 on page 20 50. IR100CLK I/O Table 5 on page 20 51. NC — Table 11 on page 28 52. NC — Table 11 on page 28 53. RESET I Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44. | IR100DAT1     | I/O                 | Table 5 on page 20                   |

| 47.         VCC         —         Table 9 on page 26           48.         IR100DAT3         I/O         Table 5 on page 20           49.         IR100DAT4         I/O         Table 5 on page 20           50.         IR100CLK         I/O         Table 5 on page 20           51.         NC         —         Table 11 on page 28           52.         NC         —         Table 11 on page 28           53.         RESET         I         Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45. | IR100DAT2     | I/O                 | Table 5 on page 20                   |

| 48. IR100DAT3 I/O Table 5 on page 20 49. IR100DAT4 I/O Table 5 on page 20 50. IR100CLK I/O Table 5 on page 20 51. NC — Table 11 on page 28 52. NC — Table 11 on page 28 53. RESET I Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46. | GND           | _                   | Table 9 on page 26                   |

| 49.       IR100DAT4       I/O       Table 5 on page 20         50.       IR100CLK       I/O       Table 5 on page 20         51.       NC       —       Table 11 on page 28         52.       NC       —       Table 11 on page 28         53.       RESET       I       Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47. | VCC           | _                   | Table 9 on page 26                   |

| 50.         IR100CLK         I/O         Table 5 on page 20           51.         NC         —         Table 11 on page 28           52.         NC         —         Table 11 on page 28           53.         RESET         I         Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48. | IR100DAT3     | I/O                 | Table 5 on page 20                   |

| 51.         NC         —         Table 11 on page 28           52.         NC         —         Table 11 on page 28           53.         RESET         I         Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49. | IR100DAT4     | I/O                 | Table 5 on page 20                   |

| 52.         NC         —         Table 11 on page 28           53.         RESET         I         Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50. | IR100CLK      | I/O                 | Table 5 on page 20                   |

| 53. RESET I Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51. | NC            | _                   | Table 11 on page 28                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52. | NC            | _                   | Table 11 on page 28                  |

| 54. CLK25 I Table 11 on page 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53. | RESET         | I                   | Table 11 on page 28                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54. | CLK25         | I                   | Table 11 on page 28                  |

<sup>1.</sup> Refer to Table 1 for Signal Type definitions.

Pins are 5 V tolerant, unless indicated.

Input must be static; Refer to Section 3.3.6.2, LED Pins Multiplexed

#### Table 2 Pins, Numeric Order (Sheet 3 of 7)

| Pin     | Symbol            | Type <sup>1,2</sup>    | Reference<br>for Full<br>Description |

|---------|-------------------|------------------------|--------------------------------------|

| 55.     | IR10ISO           | 0                      | Table 5 on page 20                   |

| 56.     | IR100ISO          | 0                      | Table 5 on page 20                   |

| 57.     | RECONFIG          | I, PD                  | Table 7 on page 24                   |

| 58.     | SRX               | I, PD                  | Table 7 on page 24                   |

| 59.     | STX               | O, OD                  | Table 7 on page 24                   |

| 60.     | SERCLK            | I/O, Tri-State,<br>PD  | Table 7 on page 24                   |

| 61. VCC |                   | _                      | Table 9 on page 26                   |

| 62.     | GND               |                        | Table 9 on page 26                   |

| 63.     | SER_MATCH         | 0                      | Table 7 on page 24                   |

| 64.     | MMSTROUT          | 0                      | Table 5 on page 20                   |

| 65.     | ARBOUT            | 0                      | Table 7 on page 24                   |

| 66. NC  |                   | _                      | Table 11 on page 28                  |

| 67.     | MGR_PRES          | I<br>PU                | Table 7 on page 24                   |

| 68.     | PROM_CLK          | I/O<br>Tri-State<br>PD | Table 10 on page 27                  |

| 69.     | PROM_CS           | O, Tri-State           | Table 10 on page 27                  |

| 70.     | PROM_DTOUT        | O, Tri-State           | Table 10 on page 27                  |

| 71.     | PROM_DTIN         | I, PD                  | Table 10 on page 27                  |

| 72.     | CHIPID0           | I<br>PD                | Table 11 on page 28                  |

| 73.     | CHIPID1           | I<br>PD                | Table 11 on page 28                  |

| 74.     | VCC               | _                      | Table 9 on page 26                   |

| 75.     | GND               | _                      | Table 9 on page 26                   |

| 76.     | VCC               | _                      | Table 9 on page 26                   |

| 77.     | VCC               | _                      | Table 9 on page 26                   |

| 78.     | RPS_FAULT I,      | PU                     | Table 9 on page 26                   |

| 79.     | RPS_PRES          | I, PU                  | Table 9 on page 26                   |

| 80.     | MACACTIVE         | I, PD                  | Table 5 on page 20                   |

| 81.     | HOLDCOL           | I/O, PD                | Table 5 on page 20                   |

| 82.     | LEDCLK<br>CFG_CLK | 0                      | Table 8 on page 25                   |

| 83.     | LEDDAT            | 0                      | Table 8 on page 25                   |

| 1       |                   |                        | •                                    |

<sup>1.</sup> Refer to Table 1 for Signal Type definitions.

<sup>2.</sup> Pins are 5 V tolerant, unless indicated.

<sup>3.</sup> Input must be static; Refer to Section 3.3.6.2, *LED Pins Multiplexed with Configuration Inputs*, on page 67 for information on pin use.

Table 2 Pins, Numeric Order (Sheet 4 of 7)

| 84.         LEDLAT         O         Table 8 on page 25           85.         VCC         —         Table 9 on page 26           86.         GND         —         Table 9 on page 26           87.         PORT1_LED3         O, OD         Table 8 on page 25           88.         PORT1_LED1         O, OD         Table 8 on page 25           89.         PORT1_LED1         O, OD         Table 8 on page 25           90.         GND         —         Table 9 on page 26           91.         PORT2_LED3         O, OD         Table 8 on page 25           92.         PORT2_LED2         O, OD         Table 8 on page 25           93.         PORT2_LED1         O, OD         Table 8 on page 25           94.         GND         —         Table 9 on page 26           95.         PORT3_LED3         O, OD         Table 8 on page 25           96.         PORT3_LED3         O, OD         Table 8 on page 25           97.         PORT3_LED1         O, OD         Table 8 on page 25           98.         GND         —         Table 8 on page 25           100.         PORT4_LED3         O, OD         Table 8 on page 25           101.         PORT4_LED3         O,  | Pin  | Symbol     | Type <sup>1,2</sup> | Reference<br>for Full<br>Description |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|---------------------|--------------------------------------|

| 86. GND — Table 9 on page 26 87. PORT1_LED3 — O, OD Table 8 on page 25 88. PORT1_LED1 — O, OD Table 8 on page 25 89. PORT1_LED1 — O, OD Table 8 on page 25 90. GND — Table 9 on page 26 91. PORT2_LED3 — O, OD Table 8 on page 25 92. PORT2_LED2 — O, OD Table 8 on page 25 93. PORT2_LED1 — O, OD Table 8 on page 25 94. GND — Table 9 on page 26 95. PORT3_LED1 — O, OD Table 8 on page 25 96. PORT3_LED2 — O, OD Table 8 on page 25 97. PORT3_LED2 — O, OD Table 8 on page 25 98. GND — Table 8 on page 25 99. PORT3_LED1 — O, OD Table 8 on page 25 99. PORT4_LED3 — O, OD Table 8 on page 25 100. PORT4_LED3 — O, OD Table 8 on page 25 101. PORT4_LED1 — O, OD Table 8 on page 25 102. RBIAS — A Table 9 on page 26 103. GND — Table 8 on page 25 104. TPIP1 — Al Table 6 on page 23 105. TPIN1 — Al Table 6 on page 23 106. VCCR — Table 9 on page 26 107. TPOP1 — AO Table 6 on page 23 108. TPON1 — AO Table 6 on page 23 110. TPON2 — AO Table 6 on page 23 111. TPOP2 — AO Table 6 on page 23 112. VCCT — Table 9 on page 26 113. VCCR — Table 9 on page 26 114. TPIN2 — AI Table 6 on page 23 115. TPIP2 — AI Table 6 on page 23 116. GND — Table 9 on page 26                            | 84.  | LEDLAT     | 0                   | Table 8 on page 25                   |

| 87. PORT1_LED3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85.  | VCC        | _                   | Table 9 on page 26                   |