### **FEATURES**

#### ■ Ultra low power

- Designed for applications that require long battery life while using standard AA/AAA batteries

- Average 45 mW/66 mW in normal operation (2.7 V/3.3 V, 13 MHz/18.432 MHz)

- Average 15 mW in idle mode (clock to the CPU stopped, everything else running)

- Average 15  $\mu$ A in standby mode (realtime clock on, everything else stopped)

# ■ Performance matching 33-MHz Intel® '486-based PC

— 15 Vax™-MIPS (Dhrystone®) at 18 MHz

### ■ ARM710a microprocessor

- ARM7 CPU

- 8 Kbytes of four-way set-associative cache

- MMU with 64-entry TLB (transition look-aside buffer)

#### ■ DRAM controller

- Supports both 16- and 32-bit-wide DRAMs

### ■ ROM/SRAM/flash memory control

Decodes 4, 5, or 6 separate memory segments of 256 Mbytes (cont.) Low-Power System-on-a-Chip

### **OVERVIEW**

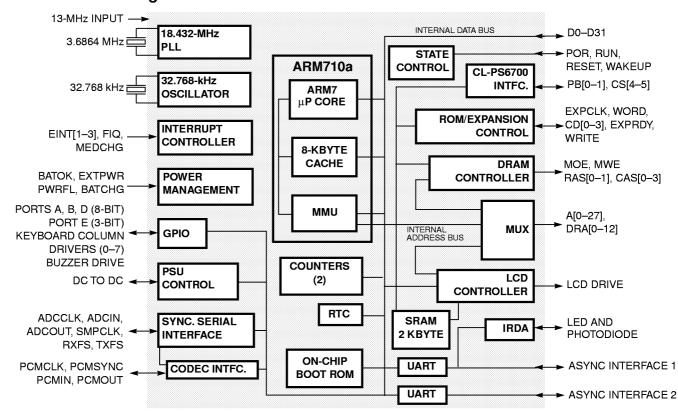

The CL-PS7111 is designed for ultra-low-power applications such as organizers/PDAs, two-way pagers, smart phones, and hand-held internet appliances. The core-logic functionality of the device is built around an ARM710a microprocessor with 8 Kbytes of four-way set-associative unified cache.

At 18.432 MHz (for 3.3-V operation), the CL-PS7111 delivers nearly 15 Vax-MIPS of performance (based on Dhrystone® benchmark) — roughly the same level of performance offered by a 33-MHz Intel® '486-based PC.

(cont.)

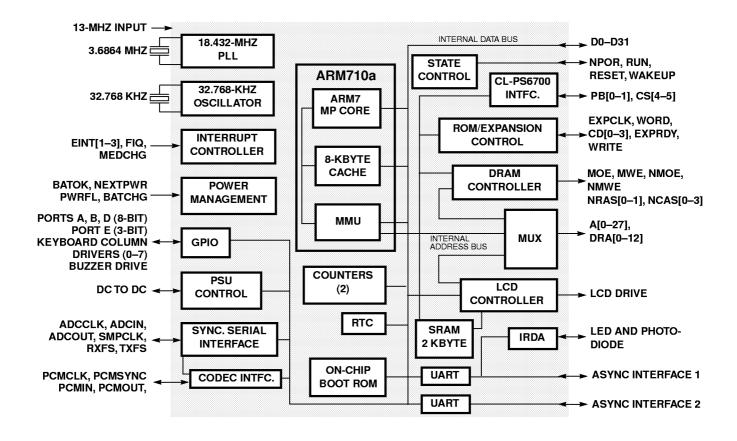

## **Functional Block Diagram**

Version 2.0 September 1997

## FEATURES (cont.)

- Mbytes

- Each segment can be configured as 8, 16, or 32 bits wide and support page-mode access

- Programmable access time for conventional SRAM/ROM/flash memory

- Support for up to two ultra-low-power CL-PS6700 PC Card controllers

- 2 Kbytes of on-chip SRAM for fast program execution

- On-chip boot ROM

- Two synchronous serial interfaces

- Supports SPI®1 or Microwire®2-compatible

- Audio codec

- 27-bit general-purpose I/O

- Three 8-bit and one 3-bit GPIO port

- Supports scanning keyboard matrix

- <sup>1</sup> SPI is a registered trademark of Motorola<sup>®</sup>.

- <sup>2</sup> Microwire is a registered trademark of National Semiconductor<sup>®</sup>.

#### ■ Two UARTs

- Supports bit rates up to 115.2 kbps

- Contains two 16-byte FIFOs for Tx and Rx

- Supports modem control signals

### ■ SIR (slow — up to 115.2 kbps — infrared) encoder

IrDA (Infrared Data Association) SIR protocol encoder can be optionally switched into Tx and Rx signals of UART 1 up to 115 kbps

#### ■ DC-to-DC converter interface

Provides two 96-kHz clock outputs with programmable duty ratio (from 1-in-16 to 15-in-16)

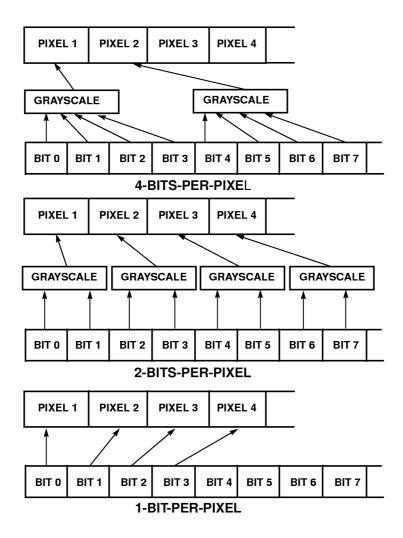

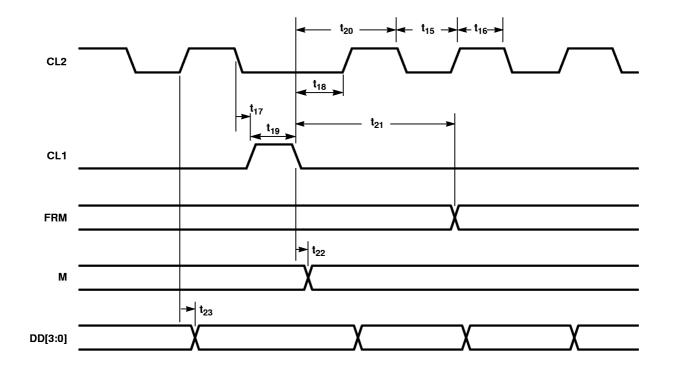

#### ■ LCD controller

- Interfaces directly to a single-scan panel monochrome LCD

- Panel size is programmable from 16 to 1024 pixels in 16pixel increments

- Video frame size programmable up to 128 Kbytes

- Bits per pixel programmable from 1, 2, or 4

- Timer and counters

- 3.3 V at 18.432 MHz and 2.7 V at 13 MHz

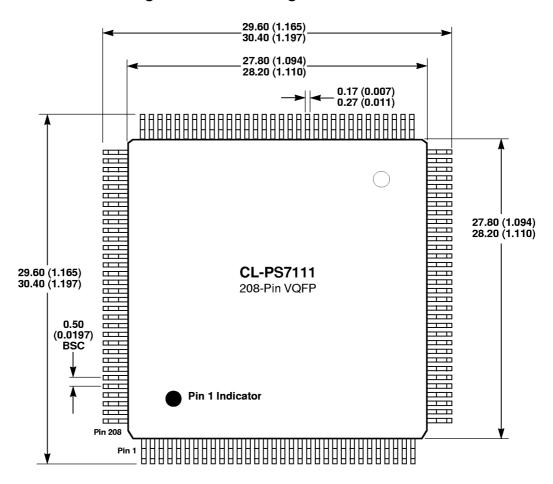

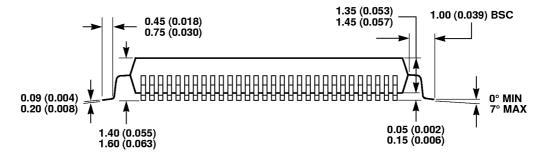

- 208-pin VQFP package

- Evaluation kit available with BOM, schematics, and design database

## **OVERVIEW** (cont.)

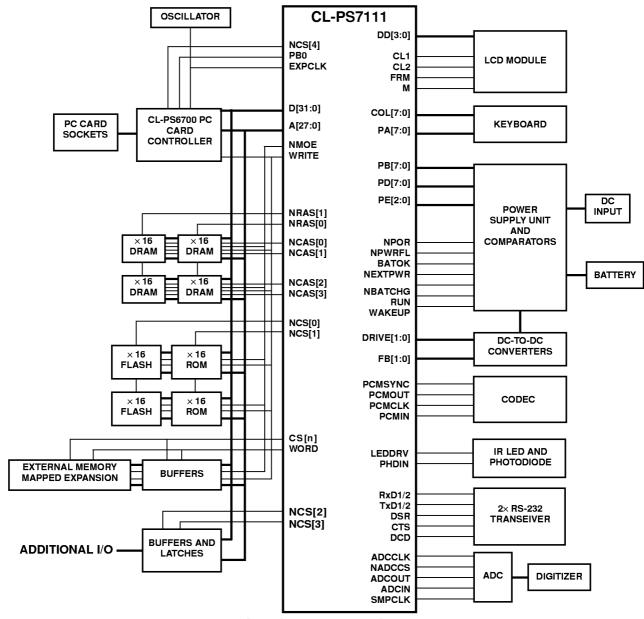

As shown in the system block diagram, simply adding desired memory and peripherals to the highly integrated CL-PS7111 completes a hand-held organizer/PDA system board. All the interface logic is integrated on-chip.

### Memory Interface

There are two main external memory interfaces and a DMA controller that fetches video display data for the LCD controller from main DRAM memory.

The SRAM/ROM-style interface has programmable wait-state timings and includes burst-mode capability, with six chip selects decoding six 256-Mbyte sections of addressable space. For maximum flexibility, each bank can be specified to be 8, 16 or 32 bits wide to enable the use of low-cost memory in a 32-bit system. The system can have an 8-bit-wide boot option to optimize memory size.

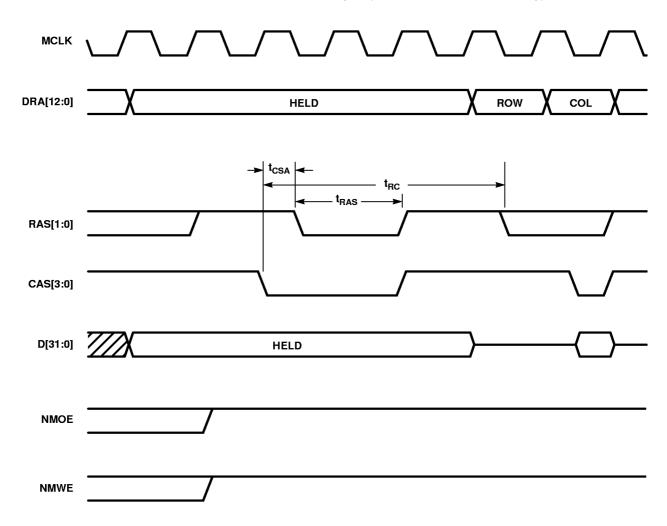

The programmable 16- or 32-bit-wide DRAM interface allows direct connection of up to two banks of DRAM, each bank containing up to 256 Mbytes. To

assure the lowest possible power consumption, the CL-PS7111 supports self-refresh DRAMs, which are placed in a low-power state by the device when it enters low-power standby mode.

#### Serial Interface

For RS-232 serial communications, the CL-PS7111 includes two UARTs, both of which have two 16-byte FIFOs for receive and transmit data. The UARTs support bit rates of up to 115.2 kbps. An IrDA SIR protocol encoder/decoder can be optionally switched into the Rx/Tx signals to/from one of the UARTs to enable these signals to drive an infrared communication interface directly.

A full-duplex codec interface allows direct connection of a standard codec chip to the CL-PS7111, allowing storage and playback of sound. A separate synchronous serial interface supports two industry-standard protocols (SPI® and Microwire®) for interfacing to standard devices such as an ADC, allowing for peripheral expansion such as the use of a digitizer pen.

A CL-PS7111-Based System

## **OVERVIEW** (cont.)

### Power Management

The CL-PS7111 is designed for low-power operation. There are three basic power states:

- Standby This state is equivalent to the computer being switched off (no display), and the main oscillator shut down.

- Idle In this state, the device is functioning and all oscillators are running, but the processor clock is halted while waiting for an event such as a key press.

Operating — This state is the same as the idle state, except that the processor clock is running.

### Packaging

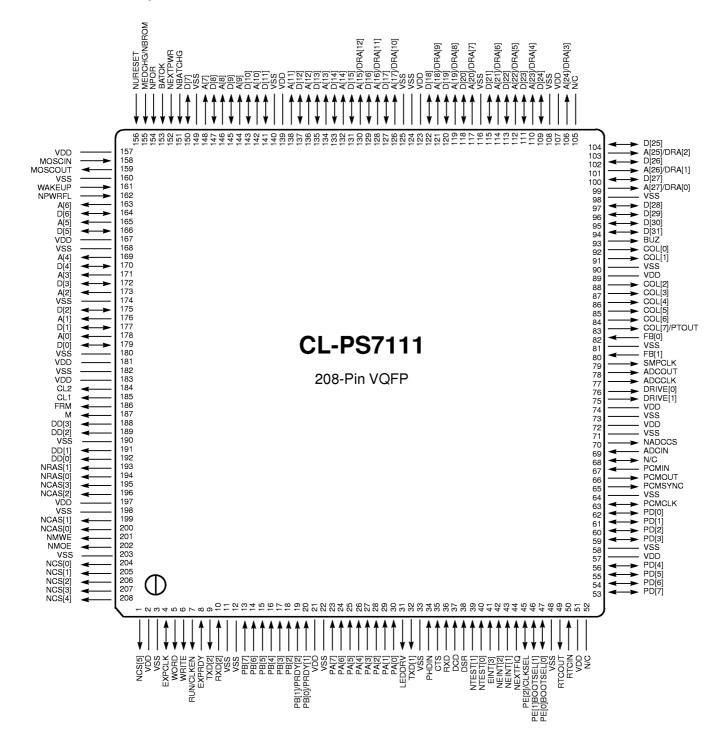

The CL-PS7111 is packaged in a 208-pin VQFP package, with a body size of 28-mm square, a lead pitch of 0.5 mm and thickness of 1.4 mm.

# **Table of Contents**

| 1.         | COL        | IVENTIONS                                                                  | ხ  |

|------------|------------|----------------------------------------------------------------------------|----|

| 2.         | PIN        | INFORMATION                                                                | 8  |

|            | 2.1        | Pin Diagram                                                                | _  |

|            | 2.2        | Pin Descriptions                                                           |    |

|            |            | 2.2.1 External Signal Functions                                            |    |

|            |            | 2.2.2 Numeric Pin Listing                                                  |    |

| 3.         | FIIN       | ICTIONAL DESCRIPTION                                                       |    |

| <b>J</b> . | 3.1        | Main Functional Blocks                                                     |    |

|            | 3.2        | System Maximization                                                        |    |

|            | 3.3        | Endian Functionality                                                       |    |

|            | 3.4        | CPU Core                                                                   |    |

|            | 3.5        | Counters                                                                   |    |

|            |            | 3.5.1 Free-Running Mode                                                    |    |

|            |            | 3.5.2 Prescale Mode                                                        |    |

|            | 3.6        | Realtime Clock                                                             |    |

|            | 3.7        | State Control                                                              |    |

|            | 3.8        | Expansion and ROM Interface                                                |    |

|            |            | 3.8.1 CL-PS7111 Boot ROM                                                   | 26 |

|            |            | 3.8.2 CL-PS6700 PCMCIA controller interface                                |    |

|            | 3.9        | DRAM Controller                                                            |    |

|            | 3.10       | LCD Controller                                                             |    |

|            | 3.11       | Two Internal UARTs and SIR Encoder                                         | 34 |

|            |            | Clocks                                                                     |    |

|            | 3.13       | Interrupt Controller                                                       |    |

|            |            | 3.13.1 Interrupt Latencies in Different States                             |    |

|            |            | Resets                                                                     |    |

|            |            | Two DC-to-DC Converters                                                    |    |

|            | 3.16       | Serial Interface                                                           |    |

|            |            | 3.16.1 Codec Interface                                                     |    |

|            |            | 3.16.2 ADC Interface — Master-Mode Only SSI (Synchronous Serial Interface) | 41 |

| 4.         | MEN        | NORY MAP                                                                   | 43 |

| 5.         | REG        | GISTER DESCRIPTIONS                                                        | 44 |

|            | 5.1        | Port A Data Register — PADR                                                | 47 |

|            | 5.2        | Port B Data Register — PBDR                                                |    |

|            | 5.3        | Port D Data Register — PDDR                                                |    |

|            | 5.4        | Port A Data Direction Register — PADDR                                     |    |

|            | 5.5        | Port B Data Direction Register — PBDDR                                     |    |

|            | 5.6        | Port D Data Direction Register — PDDDR                                     |    |

|            | 5.7        | Port E Data Register — PEDR                                                |    |

|            | 5.8        | Port E Data Direction Register — PEDDR                                     |    |

|            | <b>-</b> 0 | 5.8.1 System Control Register 1 — SYSCON1                                  |    |

|            | 5.9        | System Status Flags Register 1 — SYSFLG1                                   |    |

|            | 5.10       | Memory Configuration Register 1 — MEMCFG1                                  |    |

|            | E 44       | 5.10.1 Memory Configuration Register 2 — MEMCFG2                           |    |

|            | 5.11       | DRAM Refresh Period Register — DRFPR                                       |    |

|            |            | Interrupt Status Register 1 — INTSR1Interrupt Mask Register 1 — INTMR1     |    |

|            | 5.13       | Interrupt wask register   — Intriniti                                      | 00 |

|    |      | NDEX                                                                                |    |

|----|------|-------------------------------------------------------------------------------------|----|

| Α. |      | OT CODE                                                                             |    |

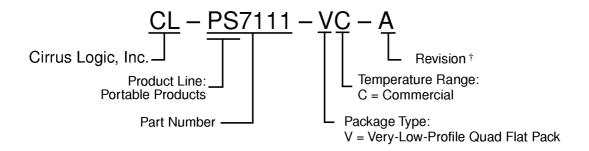

| 8. |      | DERING INFORMATION                                                                  |    |

| 0  | 7.1  | 208-Pin VQFP Package Outline Drawing                                                |    |

| 7. | PAC  | KAGE SPECIFICATIONS                                                                 |    |

|    |      | 6.6.6 Software-Selectable Test Functionality                                        | 90 |

|    |      | 6.6.5 High-Z (System) Test Mode                                                     |    |

|    |      | 6.6.4 Pin Test Mode                                                                 |    |

|    |      | 6.6.3 Oscillator and PLL Test Mode                                                  |    |

|    |      | 6.6.2 Functional (EPB) Test Mode                                                    | 88 |

|    |      | 6.6.1 Oscillator and PLL Bypass Mode                                                | 88 |

|    | 6.6  | Test Modes                                                                          |    |

|    | 6.5  | I/O Buffer Characteristics                                                          |    |

|    | 6.4  | AC Characteristics                                                                  | 75 |

|    | 6.3  | DC Characteristics                                                                  |    |

|    | 6.2  | Recommended Operating Conditions                                                    |    |

| ٠. | 6.1  | Absolute Maximum Ratings                                                            |    |

| 6. |      | CTRICAL SPECIFICATIONS                                                              |    |

|    |      | Keyboard End-of-Interrupt Location — KBDEOI                                         |    |

|    | 5.41 | Interrupt Mask Register 2 — INTMR2                                                  |    |

|    |      | Interrupt Status Register 2 — INTSR2                                                |    |

|    |      | System Status Flags Register 2 — SYSFLG2                                            |    |

|    |      | System Control Register 2 — SYSCON2                                                 |    |

|    |      | Enter Standby State Location — STDBYLCD Frame Buffer Start Address — FRBADDR        |    |

|    |      | Enter Idle State Location — HALT                                                    |    |

|    |      | Codec End-of-Interrupt Location — COEOI                                             |    |

|    |      | UART1 Modem Status Changed End-of-Interrupt — UMSEOI                                |    |

|    |      | RTC Match End-of-Interrupt — RTCEOI                                                 |    |

|    |      | End-of-Interrupt Location — TC2EOI TC2                                              |    |

|    | 5.30 | Endof-Interrupt Location — TC1EOI TC1                                               | 69 |

|    | 5.29 | Tick End-of-Interrupt Location — TEOI                                               | 69 |

|    |      | Media Changed End-of-Interrupt — MCEOI                                              |    |

|    |      | Battery Low End-of-Interrupt — BLEOI                                                |    |

|    |      | Clear All Start Up Reason Flags Location — STFCLR                                   |    |

|    |      | Most-Significant Word-LCD Palette Register — PALMSW                                 |    |

|    |      | Least-Significant Word-LCD Palette Register — PALLSW                                |    |

|    |      | Synchronous Serial ADC Interface Data Register — SYNCIO                             |    |

|    | 5.21 | UART Data Registers — UARTDR1–2UART Bit Rate and Line Control Registers — UBRLCR1–2 | 54 |

|    |      | Codec Interface Data Register — CODR                                                |    |

|    |      | Pump Control Register — PMPCON                                                      |    |

|    |      | Realtime Clock Match Register — RTCMR                                               |    |

|    |      | Realtime Clock Data Register — RTCDR                                                |    |

|    |      | Timer Counter 2 Data Register — TC2D                                                |    |

|    |      | Timer Counter 1 Data Register — TC1D                                                |    |

|    |      | LCD Control Register — LCDCON                                                       |    |

PRELIMINARY DATA BOOK v2.0

## 1. CONVENTIONS

This section presents acronyms, abbreviations, units of measurement, and conventions used in this data book.

## Acronyms and Abbreviations

The following table lists abbreviations and acronyms used in this data book.

| Acronym/<br>Abbreviation | Definition                              |

|--------------------------|-----------------------------------------|

| AC                       | alternating current                     |

| ADC                      | analog-to-digital                       |

| codec                    | coder/decoder                           |

| CMOS                     | complementary metal-oxide semiconductor |

| CPU                      | central processing unit                 |

| DC                       | direct current                          |

| DMA                      | direct-memory access                    |

| DRAM                     | dynamic random-access memory            |

| EPB                      | embedded peripheral bus                 |

| FCS                      | frame check sequence                    |

| FIFO                     | first in/first out                      |

| GPIO                     | general-purpose I/O                     |

| ICT                      | in circuit test                         |

| IR                       | infrared                                |

| IrDA                     | infrared data association               |

| LCD                      | liquid-crystal display                  |

| LSB                      | least-significant bit                   |

| MIPS                     | millions of instructions per second     |

| A = ================================== |                                             |  |  |  |  |

|----------------------------------------|---------------------------------------------|--|--|--|--|

| Acronym/<br>Abbreviation               | Definition (cont.)                          |  |  |  |  |

| MMU                                    | memory management unit                      |  |  |  |  |

| MSB                                    | most-significant bit                        |  |  |  |  |

| РСВ                                    | printed circuit board                       |  |  |  |  |

| PDA                                    | personal digital assistant                  |  |  |  |  |

| PIA                                    | peripheral interface adapter                |  |  |  |  |

| PLL                                    | phase locked loop                           |  |  |  |  |

| PSU                                    | power supply unit                           |  |  |  |  |

| p/u                                    | pull-up resistor                            |  |  |  |  |

| RAM                                    | random-access memory                        |  |  |  |  |

| RISC                                   | reduced-instruction-set computer            |  |  |  |  |

| ROM                                    | read-only memory                            |  |  |  |  |

| RTC                                    | realtime clock                              |  |  |  |  |

| SIR                                    | slow (9600-115.2 kbps) infrared             |  |  |  |  |

| SRAM                                   | static random-access memory                 |  |  |  |  |

| SSI                                    | synchronous serial interface                |  |  |  |  |

| TLB                                    | translation look-aside buffer               |  |  |  |  |

| UART                                   | universal asynchronous receiver transmitter |  |  |  |  |

| VQFP                                   | very-tight-pitch quad flat pack             |  |  |  |  |

6 CONVENTIONS PRELIMINARY DATA BOOK v2.0 September 1997

#### Units of Measurement

| Symbol | Unit of Measure                      |

|--------|--------------------------------------|

| °C     | degree Celsius                       |

| Hz     | hertz (cycle per second)             |

| Kbyte  | kilobyte (1,024 bytes)               |

| kHz    | kilohertz                            |

| kΩ     | kilohm                               |

| Mbps   | megabits (1,048,576 bits) per second |

| Mbyte  | megabyte (1,048,576 bytes)           |

| MHz    | megahertz (1,000 kilohertz)          |

| μF     | microfarad                           |

| μА     | microampere                          |

| μs     | microsecond (1,000 nanoseconds)      |

| mA     | milliampere                          |

| ms     | millisecond (1,000 microseconds)     |

| ns     | nanosecond                           |

| V      | volt                                 |

| W      | watt                                 |

#### General Conventions

Hexadecimal numbers are presented with all letters in uppercase and a lowercase h appended. For example, 14h and 03CAh are hexadecimal numbers. Binary numbers are enclosed in single quotation marks when in text (for example, '11' designates a binary number). Numbers not indicated by an h or quotation marks are decimal.

Registers are referred to by acronym, as listed in Table 5-1 and Table 5-2, with bits listed in brackets MSB-to-LSB separated by a colon (:) (for example, CODR[7:0]) or LSB-to-MSB separated by a hyphen (for example, CODR[0-2]).

The use of 'tbd' indicates values that are 'to be determined', 'n/a' designates 'not available', and 'n/c' indicates a pin that is a 'no connect'.

### Pin Description Conventions

Abbreviations used for signal directions in Chapter 2 are listed in the following table:

| Abbreviation | Direction       |

|--------------|-----------------|

| I            | Input           |

| 0            | Output          |

| I/O          | Input or output |

## 2. PIN INFORMATION

## 2.1 Pin Diagram

8 PIN INFORMATION PRELIMINARY DATA BOOK v2.0 September 1997

## 2.2 Pin Descriptions

## 2.2.1 External Signal Functions

| Function               | Signal<br>Name                     | Туре | Description                                                                                                                              |

|------------------------|------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| Address and            | D[0-31]                            | I/O  | 32-bit system data bus for DRAM, ROM, and memory-mapped expansion.                                                                       |

| Data Bus               | A[0-14]                            | 0    | Least-significant 15 bits of system byte address during ROM and expansion cycles.                                                        |

|                        | A[15]/<br>DRA[12]–<br>A[27]/DRA[0] | 0    | 13-bit multiplexed DRAM word address during DRAM cycles or address bits 16 to 27 of system byte address during ROM and expansion cycles. |

| Memory and             | NRAS[0-1]                          | 0    | DRAM RAS outputs to DRAM banks 0-1.                                                                                                      |

| Expansion<br>Interface | NCAS[0-3]                          | 0    | DRAM CAS outputs for bytes 0 to 3 within 32-bit word. NCAS[0] enables D[7:0].                                                            |

|                        | NMOE                               | 0    | DRAM, ROM, and expansion output enable.                                                                                                  |

|                        | NMWE                               | 0    | DRAM, ROM, and expansion write enable.                                                                                                   |

|                        | NCS[0-3]                           | 0    | Expansion channel I/O strobes. Active-low, SRAM-like chip selects for expansion.                                                         |

|                        | NCS[4-5]                           | 0    | Expansion channel I/O strobes. Active-low chip select for expansion of low for CL-PS6700 interface.                                      |

|                        | EXPRDY                             | ı    | Expansion channel ready. Extends bus cycle when low.                                                                                     |

|                        | WRITE                              | 0    | Transfer direction. Low during reads, high during writes from the CL-PS7111. Also connected to PTYPE of CL-PS6700.                       |

|                        | WORD                               | 0    | Word access enable. Driven high during word-wide cycles; low during byte-wide cycles.                                                    |

|                        | EXPCLK                             | I/O  | Expansion clock output. Clock output at the same phase and speed as the CPU clock. In 13-MHz mode, this pin is used as the clock input.  |

| Interrupts             | MEDCHG/<br>NBROM                   | I    | Media changed input. Active-high deglitched input for media insertion; should be set low during NPOR to enable boot code.                |

|                        | NEXTFIQ                            | 1    | External active-low fast interrupt request input.                                                                                        |

|                        | EINT[3]                            | 1    | External active-high interrupt request input.                                                                                            |

|                        | NEINT[1-2]                         | I    | Two general-purpose, active-low interrupt inputs.                                                                                        |

| Power                  | NPWRFL                             | I    | Power fail input. Active-low deglitched input to force system into the standby state.                                                    |

| Management             | BATOK                              | I    | Main battery OK input. Falling edge generates a FIQ; a low level in standby mode inhibits system start up; deglitched input.             |

|                        | NEXTPWR                            | I    | External power sense. Must be driven low if the system is powered by external source.                                                    |

|                        | NBATCHG                            | I    | New battery sense. Must be driven low if battery voltage falls below the 'no-battery' threshold.                                         |

## 2.2.1 External Signal Functions (cont.)

| Function              | Signal<br>Name | Туре | Description                                                                                          |

|-----------------------|----------------|------|------------------------------------------------------------------------------------------------------|

| State Control         | NPOR           | I    | Power on reset input. Active-low input completely resets the system.                                 |

|                       | RUN/CLKEN      | 0    | System active output. High when system is active or idle, low while in the standby state.            |

|                       | WAKEUP         | I    | Wake-up input signal. Rising edge forces system into operating state; active after a power on reset. |

|                       | NURESET        | I    | User reset input. Active-low input from user reset button.                                           |

| Codec Interface       | PCMCLK         | I/O  | Codec clock signal.                                                                                  |

|                       | PCMSYNC        | 0    | Codec frame synchronization, pulse output.                                                           |

|                       | PCMOUT         | 0    | Codec serial data output.                                                                            |

|                       | PCMIN          | I    | Codec serial data input.                                                                             |

| ADC Interface<br>SSI1 | ADCCLK         | 0    | Serial clock output.                                                                                 |

| 3311                  | SMPCLK         | 0    | Serial sample clock output.                                                                          |

|                       | NADCCS         | 0    | Chip select for ADC interface.                                                                       |

|                       | ADCOUT         | 0    | Serial data output.                                                                                  |

|                       | ADCIN          | I    | Serial data input.                                                                                   |

| IrDA and<br>RS-232    | LEDDRV         | 0    | Infrared LED drive output, multiplexed with UART1.                                                   |

| Interface             | PHDIN          | I    | Photo diode input, multiplexed with UART1.                                                           |

|                       | TxD[1-2]       | 0    | RS-232 UART1 and two Tx outputs.                                                                     |

|                       | RxD[1-2]       | I    | RS-232 UART1 and two Rx inputs.                                                                      |

|                       | DSR            | I    | RS-232 DSR input.                                                                                    |

|                       | DCD            | I    | RS-232 DCD input.                                                                                    |

|                       | CTS            | I    | RS-232 CTS input.                                                                                    |

| LCD                   | DD[0-3]        | 0    | LCD serial display data.                                                                             |

|                       | CL[1]          | 0    | LCD line clock.                                                                                      |

|                       | CL[2]          | 0    | LCD pixel clock.                                                                                     |

|                       | FRM            | 0    | LCD frame synchronization pulse output.                                                              |

|                       | М              | 0    | LCD AC bias drive.                                                                                   |

10 PIN INFORMATION PRELIMINARY DATA BOOK v2.0 September 1997

## **2.2.1 External Signal Functions** (cont.)

| Function                | Signal<br>Name    | Туре | Description                                    |

|-------------------------|-------------------|------|------------------------------------------------|

| Keyboard                | COL[0-7]          | 0    | Keyboard column drives.                        |

| Buzzer Drive            | BUZ               | 0    | Buzzer drive output in 18.432-MHz mode.        |

| General-<br>Purpose I/O | PA[0-7]           | I/O  | Port A I/O.                                    |

| ruipose I/O             | PB[0-7]           | I/O  | Port B I/O (default input).                    |

|                         | PD[0-7]           | I/O  | Port D I/O (higher drive, default output).     |

|                         | PE[0-2]           | I/O  | Port E I/O (three bits only, default input).   |

| DC-to-DC Drives         | DRIVE[0-1]        | 0    | DC-to-DC converter drive outputs.              |

|                         | FB[0-1]           | I    | DC-to-DC feedback inputs.                      |

| Test                    | NTEST[0-1]        | I    | Test mode select inputs.                       |

| Oscillators             | MOSCIN/<br>MOSOUT | I/O  | Main 3.6864-MHz oscillator for 18.432-MHz PLL. |

|                         | RTCIN/<br>RTCOUT  | I/O  | Realtime clock 32.768-kHz oscillator.          |

## 2.2.2 Numeric Pin Listing

| Pin<br>No. | Signal        | Buffer           | Reset and<br>Pin Test<br>Reset State | Pin<br>No. | Signal                | Buffer                  | Reset and<br>Pin Test<br>Reset State |

|------------|---------------|------------------|--------------------------------------|------------|-----------------------|-------------------------|--------------------------------------|

| 1          | NCS[5]        | I/O - strength 1 | Low                                  | 27         | PA[3]                 | I/O - strength 1        | Input                                |

| 2          | VDD           | Pad power        | -                                    | 28         | PA[2]                 | I/O - strength 1        | Input                                |

| 3          | VSS           | Pad power        | -                                    | 29         | PA[1]                 | I/O - strength 1        | Input                                |

| 4          | EXPCLK        | I/O - strength 1 | Low/Input                            | 30         | PA[0]                 | I/O - strength 1        | Input                                |

| 5          | WORD          | I/O - strength 1 | Low                                  | 31         | LEDDRV                | I/O - strength 1        | Low                                  |

| 6          | WRITE         | I/O - strength 1 | Low                                  | 32         | TXD[1]                | I/O - strength 1        | High                                 |

| 7          | RUN/CLKEN     | I/O - strength 1 | Low                                  | 33         | VSS                   | Pad power               | -                                    |

| 8          | EXPRDY        | I/O - strength 1 | Input                                | 34         | PHDIN                 | I/O - strength 1        | Input                                |

| 9          | TXD[2]        | I/O - strength 1 | High                                 | 35         | CTS                   | I/O - strength 1        | Input                                |

| 10         | RXD[2]        | I/O - strength 1 | Input                                | 36         | RXD[1]                | I/O - strength 1        | Input                                |

| 11         | VSS           | Core power       | -                                    | 37         | DCD                   | I/O - strength 1        | Input                                |

| 12         | VSS           |                  | -                                    | 38         | DSR                   | I/O - strength 1        | Input                                |

| 13         | PB[7]         | I/O - strength 1 | Input                                | 39         | NTEST[1]              | Input with p/u          | High Input                           |

| 14         | PB[6]         | I/O - strength 1 | Input                                | 40         | NTEST[0]              | Input with p/u          | High Input                           |

| 15         | PB[5]         | I/O - strength 1 | Input                                | 41         | EINT[3]               | I/O - strength 1        | Input                                |

| 16         | PB[4]         | I/O - strength 1 | Input                                | 42         | NEINT[2]              | I/O - strength 1        | Input                                |

| 17         | PB[3]         | I/O - strength 1 | Input                                | 43         | NEINT[1]              | I/O - strength 1        | Input                                |

| 18         | PB[2]         | I/O - strength 1 | Input                                | 44         | NEXTFIQ               | I/O - strength 1        | Input                                |

| 19         | PB[1]/PRDY[2] | I/O - strength 1 | Input                                | 45         | PE[2]/CLKSEL          | I/O - strength 1        | Input                                |

| 20         | PB[0]/PRDY[1] | I/O - strength 1 | Input                                | 46         | PE[1] /<br>BOOTSEL[1] | I/O - strength 1        | Input                                |

| 21         | VDD           | Pad power        | -                                    | 47         | PE[0]/<br>BOOTSEL[0]  | I/O - strength 1        | Input                                |

| 22         | VSS           | Pad power        | -                                    | 48         | VSS                   | 32K oscillator power    | _                                    |

| 23         | PA[7]         | I/O - strength 1 | Input                                | 49         | RTCOUT                | 32K oscillator          | Х                                    |

| 24         | PA[6]         | I/O - strength 1 | Input                                | 50         | RTCIN                 | 32K oscillator          | Х                                    |

| 25         | PA[5]         | I/O - strength 1 | Input                                | 51         | VDD                   | 32K oscillator<br>power | _                                    |

| 26         | PA[4]         | I/O - strength 1 | Input                                | 52         | N/Ca                  |                         |                                      |

| 53         | PD[7]         | I/O - strength 1 | Low                                  | 79         | SMPCLK                | I/O - strength 1        | Low                                  |

12 PIN INFORMATION PRELIMINARY DATA BOOK v2.0 September 1997

## 2.2.2 Numeric Pin Listing (cont.)

| Pin<br>No. | Signal   | Buffer           | Reset and<br>Pin Test<br>Reset State | Pin<br>No. | Signal           | Buffer                        | Reset and<br>Pin Test<br>Reset State |

|------------|----------|------------------|--------------------------------------|------------|------------------|-------------------------------|--------------------------------------|

| 54         | PD[6]    | I/O - strength 1 | Low                                  | 80         | FB[1]            |                               | Input                                |

| 55         | PD[5]    | I/O - strength 1 | Low                                  | 81         | VSS              | I/O - strength 1              | Input                                |

| 56         | PD[4]    | I/O - strength 1 | Low                                  | 82         | FB[0]            | I/O - strength 1              | Input                                |

| 57         | VDD      | Pad power        | -                                    | 83         | COL[7]/<br>PTOUT | I/O - strength 1              | High                                 |

| 58         | VSS      | Pad power        | -                                    | 84         | COL[6]           | I/O - strength 1              | High                                 |

| 59         | PD[3]    | I/O - strength 1 | Low                                  | 85         | COL[5]           | I/O - strength 0 <sup>b</sup> | High                                 |

| 60         | PD[2]    | I/O - strength 1 | Low                                  | 86         | COL[4]           | I/O - strength 1              | High                                 |

| 61         | PD[1]    | I/O - strength 1 | Low                                  | 87         | COL[3]           | I/O - strength 1              | High                                 |

| 62         | PD[0]    | I/O - strength 1 | Low                                  | 88         | COL[2]           | I/O - strength 1              | High                                 |

| 63         | PCMCLK   | -                | Input                                | 89         | VDD              | Pad power                     | -                                    |

| 64         | VSS      | Core power       | -                                    | 90         | VSS              | Pad power                     | _                                    |

| 65         | PCMSYNC  | I/O - strength 1 | Low                                  | 91         | COL[1]           | I/O - strength 1              | High                                 |

| 66         | PCMOUT   | I/O - strength 1 | Low                                  | 92         | COL[0]           | I/O - strength 1              | High                                 |

| 67         | PCMIN    | I/O - strength 1 | Input                                | 93         | BUZ              | I/O - strength 1              | Low                                  |

| 68         | N/C      | I/O - strength 1 | Low                                  | 94         | D[31]            | I/O - strength 1              | Low                                  |

| 69         | ADCIN    | I/O - strength 1 | Input                                | 95         | D[30]            | I/O - strength 1              | Low                                  |

| 70         | NADCCS   | I/O - strength 1 | High                                 | 96         | D[29]            | I/O - strength 1              | Low                                  |

| 71         | VSS      | Core power       | -                                    | 97         | D[28]            | I/O - strength 1              | Low                                  |

| 72         | VDD      | Core power       | _                                    | 98         | VSS              | _                             |                                      |

| 73         | VSS      | Pad power        | _                                    | 99         | A[27]/DRA[0]     | I/O - strength 2              | Low                                  |

| 74         | VDD      | Pad power        | -                                    | 100        | D[27]            | I/O - strength 1              | Low                                  |

| 75         | DRIVE[1] | I/O - strength 3 | High/Low                             | 101        | A[26]/DRA[1]     | I/O - strength 2              | Low                                  |

| 76         | DRIVE[0] | I/O - strength 3 | High/Low                             | 102        | D[26]            | I/O - strength 1              | Low                                  |

| 77         | ADCCLK   | I/O - strength 1 | Low                                  | 103        | A[25]/DRA[2]     | I/O - strength 1              | Low                                  |

| 78         | ADCOUT   | I/O - strength 1 | Low                                  | 104        | D[25]            | I/O - strength 1              | Low                                  |

| 77         | ADCCLK   | I/O - strength 1 | Low                                  | 105        | N/C              |                               |                                      |

| 78         | ADCOUT   | I/O - strength 1 | Low                                  | 106        | A[24]/DRA[3]     | I/O - strength 1              | Low                                  |

| 107        | VDD      | Pad power        | _                                    | 136        | A[12]            | I/O - strength 1              | Low                                  |

| 108        | VSS      | Pad power        | _                                    | 137        | D[12]            | I/O - strength 1              | Low                                  |

## 2.2.2 Numeric Pin Listing (cont.)

| Pin<br>No. | Signal        | Buffer           | Reset and<br>Pin Test<br>Reset State | Pin<br>No. | Signal           | Buffer           | Reset and<br>Pin Test<br>Reset State |

|------------|---------------|------------------|--------------------------------------|------------|------------------|------------------|--------------------------------------|

| 109        | D[24]         | I/O - strength 1 | Low                                  | 138        | A[11]            | I/O - strength 1 | Low                                  |

| 110        | A[23]/DRA[4]  | I/O - strength 1 | Low                                  | 139        | VDD              | Pad power        | -                                    |

| 111        | D[23]         | I/O - strength 1 | Low                                  | 140        | VSS              | Pad power        | -                                    |

| 112        | A[22]/DRA[5]  | I/O - strength 1 | Low                                  | 141        | D[11]            | I/O - strength 1 | Low                                  |

| 113        | D[22]         | I/O - strength 1 | Low                                  | 142        | A[10]            | I/O - strength 1 | Low                                  |

| 114        | A[21]/DRA[6]  | I/O - strength 1 | Low                                  | 143        | D[10]            | I/O - strength 1 | Low                                  |

| 115        | D[21]         | I/O - strength 1 | Low                                  | 144        | A[9]             | I/O - strength 1 | Low                                  |

| 116        | VSS           |                  | -                                    | 145        | D[9]             | I/O - strength 1 | Low                                  |

| 117        | A[20]/DRA[7]  | I/O - strength 1 | Low                                  | 146        | A[8]             | I/O - strength 1 | Low                                  |

| 118        | D[20]         | I/O - strength 1 | Low                                  | 147        | D[8]             | I/O - strength 1 | Low                                  |

| 119        | A[19]/DRA[8]  | I/O - strength 1 | Low                                  | 148        | A[7]             | I/O - strength 1 | Low                                  |

| 120        | D[19]         | I/O - strength 1 | Low                                  | 149        | VSS              |                  | -                                    |

| 121        | A[18]/DRA[9]  | I/O - strength 1 | Low                                  | 150        | D[7]             | I/O - strength 1 | Low                                  |

| 122        | D[18]         | I/O - strength 1 | Low                                  | 151        | NBATCHG          | I/O - strength 1 | Input                                |

| 123        | VDD           | Pad power        | -                                    | 152        | NEXTPWR          | I/O - strength 1 | Input                                |

| 124        | VSS           | Pad power        | -                                    | 153        | BATOK            | I/O - strength 1 | Input                                |

| 125        | VSS           | Core power       | -                                    | 154        | NPOR             | Schmitt I/O      | Input                                |

| 126        | A[17]/DRA[10] | I/O - strength 1 | Low                                  | 155        | MEDCHG/<br>NBROM | I/O - strength 1 | Input                                |

| 127        | D[17]         | I/O - strength 1 | Low                                  | 156        | NURESET          | Schmitt I/O      | Input                                |

| 128        | A[16]/DRA[11] | I/O - strength 1 | Low                                  | 157        | VDD              | Osc power        | _                                    |

| 129        | D[16]         | I/O - strength 1 | Low                                  | 158        | MOSCIN           | 3M6864 Osc       | Х                                    |

| 130        | A[15]/DRA[12] | I/O - strength 1 | Low                                  | 159        | MOSCOUT          | 3M6864 Osc       | Х                                    |

| 131        | D[15]         | I/O - strength 1 | Low                                  | 160        | VSS              | Osc power        | -                                    |

| 132        | A[14]         | I/O - strength 1 | Low                                  | 161        | WAKEUP           | Schmitt I/O      | Input                                |

| 133        | D[14]         | I/O - strength 1 | Low                                  | 162        | NPWRFL           | I/O - strength 1 | Input                                |

| 134        | A[13]         | I/O - strength 1 | Low                                  | 163        | A[6]             | I/O - strength 1 | Input                                |

| 135        | D[13]         | I/O - strength 1 | Low                                  | 164        | D[6]             | I/O - strength 1 | Low                                  |

| 165        | A[5]          | I/O - strength 1 | Low                                  | 187        | М                | I/O - strength 1 | Low                                  |

| 166        | D[5]          | I/O - strength 1 | Low                                  | 188        | DD[3]            | I/O - strength 1 | Low                                  |

14 PIN INFORMATION PRELIMINARY DATA BOOK v2.0 September 1997

## 2.2.2 Numeric Pin Listing (cont.)

| Pin<br>No. | Signal | Buffer           | Reset and<br>Pin Test<br>Reset State | Pin<br>No. | Signal  | Buffer           | Reset and<br>Pin Test<br>Reset State |

|------------|--------|------------------|--------------------------------------|------------|---------|------------------|--------------------------------------|

| 167        | VDD    | Pad power        | -                                    | 189        | DD[2]   | I/O - strength 1 | Low                                  |

| 168        | VSS    | Pad power        | -                                    | 190        | VSS     |                  | -                                    |

| 169        | A[4]   | I/O - strength 1 | Low                                  | 191        | DD[1]   | I/O - strength 1 | Low                                  |

| 170        | D[4]   | I/O - strength 1 | Low                                  | 192        | DD[0]   | I/O - strength 1 | Low                                  |

| 171        | A[3]   | I/O - strength 2 | Low                                  | 193        | NRAS[1] | I/O - strength 1 | High                                 |

| 172        | D[3]   | I/O - strength 1 | Low                                  | 194        | NRAS[0] | I/O - strength 1 | High                                 |

| 173        | A[2]   | I/O - strength 2 | Low                                  | 195        | NCAS[3] | I/O - strength 1 | High                                 |

| 174        | VSS    |                  | _                                    | 196        | NCAS[2] | I/O - strength 1 | High                                 |

| 175        | D[2]   | I/O - strength 1 | Low                                  | 197        | VDD     | Pad power        | -                                    |

| 176        | A[1]   | I/O - strength 1 | Low                                  | 198        | VSS     | Pad power        | _                                    |

| 177        | D[1]   | I/O - strength 1 | Low                                  | 199        | NCAS[1] | I/O - strength 2 | High                                 |

| 178        | A[0]   | I/O - strength 1 | Low                                  | 200        | NCAS[0] | I/O - strength 2 | High                                 |

| 179        | D[0]   | I/O - strength 1 | Low                                  | 201        | NMWE    | I/O - strength 1 | High                                 |

| 180        | VSS    | Core power       | -                                    | 202        | NMOE    | I/O - strength 1 | High                                 |

| 181        | VDD    | Core power       | -                                    | 203        | VSS     |                  | -                                    |

| 182        | VSS    | Pad power        | -                                    | 204        | NCS[0]  | I/O - strength 1 | High                                 |

| 183        | VDD    | Pad power        | -                                    | 205        | NCS[1]  | I/O - strength 1 | High                                 |

| 184        | CL[2]  | I/O - strength 1 | Low                                  | 206        | NCS[2]  | I/O - strength 1 | High                                 |

| 185        | CL[1]  | I/O - strength 1 | Low                                  | 207        | NCS[3]  | I/O - strength 1 | High                                 |

| 186        | FRM    | I/O - strength 1 | Low                                  | 208        | NCS[4]  | I/O - strength 1 | Low                                  |

<sup>&</sup>lt;sup>a</sup> Pins that are 'no connect' (N/C) may have a signal.

<sup>&</sup>lt;sup>b</sup> Also has analog bypass path for oscillator test.

### FUNCTIONAL DESCRIPTION

The CL-PS7111 is a single-device embedded controller designed to be used in low-cost and low-power applications such as hand-held personal organizers and hand-held internet browsers. There are other devices offered by Cirrus Logic (http://www.cirrus.com) that can be used around the CL-PS7111 to build a complete hand-held organizer, such as the CL-PS6700 PCMCIA controller, fax/modem chipsets, IR chipsets, codecs, and so on. The CL-PS7111 operates at 2.7 V (at 13.0 MHz) or 3.3 V (at 18.432 MHz).

The various peripheral functions are built around an ARM710a microprocessor with 8 Kbytes of four-way set-associative cache. At 18.432 MHz the CL-PS7111 delivers approximately 15 MIPS of sustained performance and 18.4 MIPS of peak performance. This is approximately the same as a 33-MHz '486-based PC.

The CL-PS7111 design is optimized for low-power dissipation. At 3.3 V and 18.432-MHz clock speed, the device typically dissipates 66 mW during the 'operating state' (all oscillators, PLL, LCD, and processor clock running), 15 mW in the 'idle state' (all oscillators and LCD running, but processor clock is halted), and 15 µW in the 'standby state' (no display and the main oscillator is shut down). At 2.7 V and 13.0 MHz, the respective values are 45 mW, 9 mW, and 15  $\mu$ W.

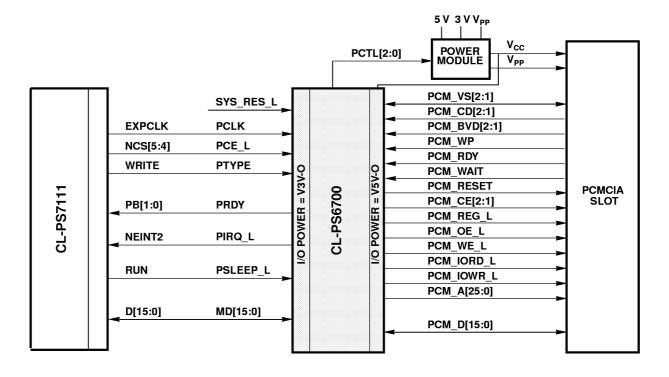

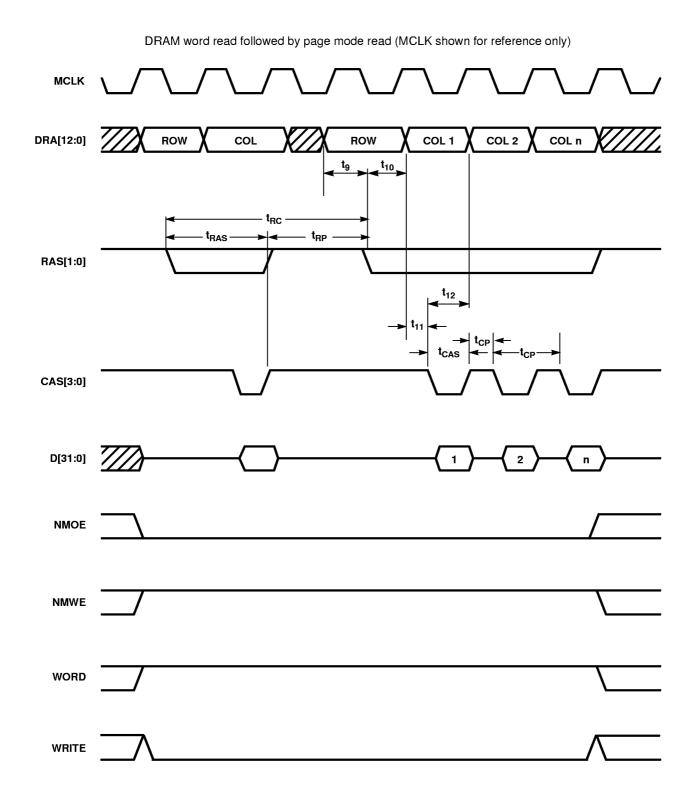

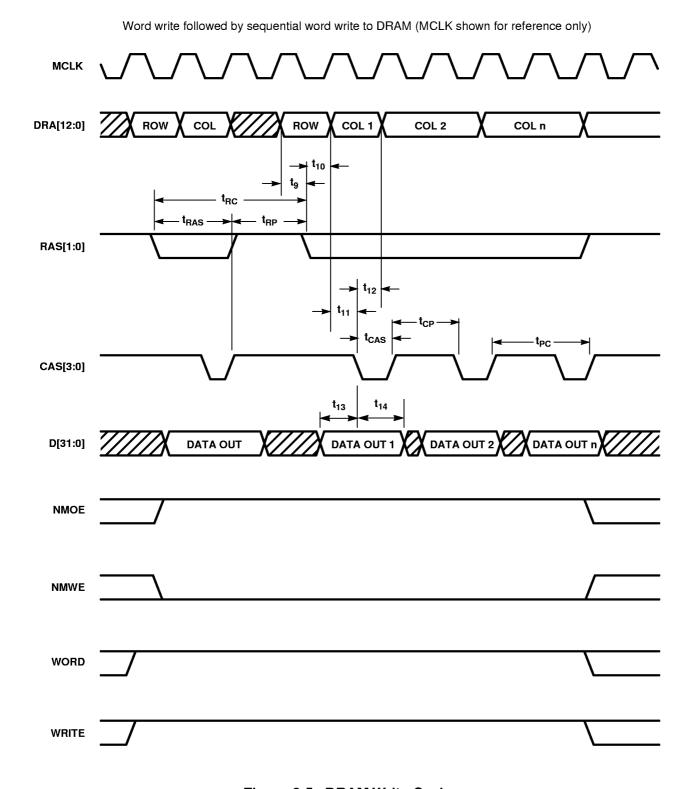

The CL-PS7111 can interface to two banks of DRAM; each bank can be up to 256 Mbytes. There is also an interface for two ROM/flash and three expansion devices, each up to 256 Mbytes, and an interface to two CL-PS6700 PCMCIA controllers. The expansion devices could be additional ROM/SRAM/Flash. In addition, the CL-PS7111 provides 2 Kbytes of on-chip SRAM and internal 128 bytes of boot ROM. The SRAM may be used for critical program storage as well as LCD frame buffer. The start address of the frame buffer can reside anywhere in the addressable memory space. A system can therefore be designed with SRAM only for very low power applications.

The boot ROM is hardware selectable on power-on or reset. This boot ROM initializes UART1 and downloads the application-specific main boot code into the on-chip SRAM. Once download is complete, execution jumps to the start of the on-chip SRAM.

The CL-PS7111 supports a number of serial interfaces including two high-speed (115 kbps) UARTs with Rx and Tx FIFOs, a codec interfaces with FIFO and an additional synchronous serial interface.

The CL-PS7111 is fabricated in a 0.6-μm CMOS process and is fully static. The CL-PS7111 is available in a 208-pin VQFP package.

Figure 3-1 shows a system-level block diagram for the CL-PS7111. As is shown, all the peripherals (such as the LCD module, keyboard, PCMCIA socket, and so on) can be added without any glue logic.

16 September 1997 **FUNCTIONAL DESCRIPTION** PRELIMINARY DATA BOOK v2.0

Figure 3-1. System-Level Block Diagram

#### 3.1 Main Functional Blocks

The CL-PS7111 is built around the ARM710a processor core. For a more detailed description of the ARM710a, refer to the ARM710a Macrocell Data Sheet (http://www.arm.com/).

The main functional blocks in CL-PS7111 are:

- ARM7 CPU core

- 8 Kbytes of unified instruction and data cache, a four-way set-associative

- Memory management unit (MMU)

- Two 16-bit general-purpose counters

- A 32-bit realtime clock and comparator

- On-chip boot ROM programmed with serial boot load sequence

- Advanced system state control and power management

- Direct interface to two CL-PS6700 PCMCIA controllers

- Expansion and ROM interface for four, five, or six 256-Mbyte expansion segments with independent wait state control

- DRAM controller supporting Fast Page mode, self-refresh in Standby mode, and both 16-bit and 32-bit-wide memory

- Programmable LCD controller with 1-, 4-, or 16-level grayscaler

- 2 Kbytes of SRAM for a small LCD frame buffer

- IrDA SIR protocol controller, capable of speeds up to 115.2 kbps

- Two full-duplex 16C550 style UARTs with two 16-byte FIFOs

- Main oscillator with PLL (phase locked loop) to generate the system clock of 18.432 MHz from a 3.6864-MHz crystal

- Optional external 13-MHz clock input

- A low-power 32.768-kHz oscillator

- Interrupt and fast interrupt controller

- 27 bits of general-purpose I/Os

- Two DC-to-DC converter interfaces

- One synchronous serial interface for Microwire® or SPI® peripherals (such as ADCs)

- Telephony codec interface with 16-byte FIFOs for transmit and receive

- Programmable frame buffer start address, allowing a system to be built using only external or internal SRAMs for memory, eliminating any need for DRAMs

- Pin test and device-isolation test logic

- External tracing support for debug

September 1997 **FUNCTIONAL DESCRIPTION**

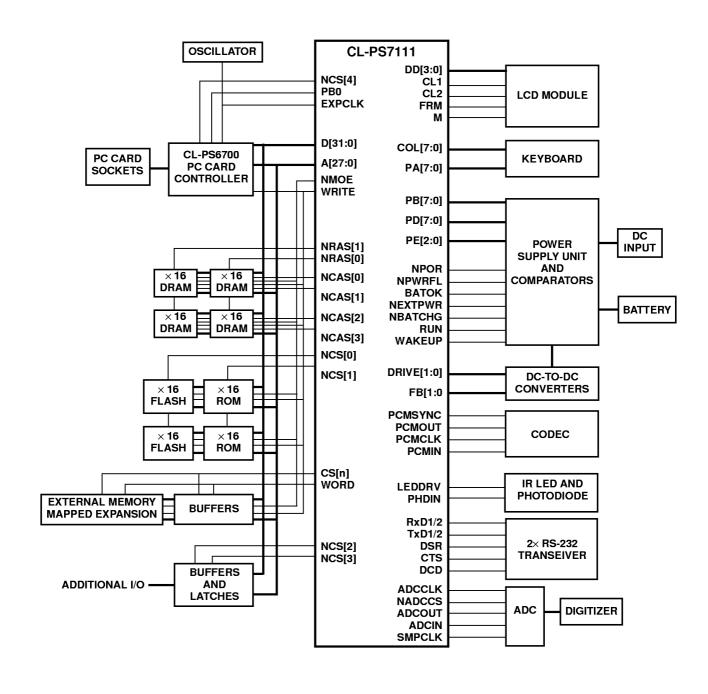

Figure 3-2 shows a simplified functional block diagram of the CL-PS7111. All external memory and peripheral devices are connected to the 8-, 16-, or 32-bit data bus, using the external 28-bit address bus and control signals. Bus transfer times can be extended by using the EXPRDY signal to lengthen bus cycles. The maximum burst transfer rate of the external bus is approximately 70 Mbytes per sec. using 32-bit-wide DRAM at 18.432 MHz or 25 Mbytes per sec. using 16-bit-wide DRAM at 13 MHz.

Figure 3-2. CL-PS7111 Block Diagram

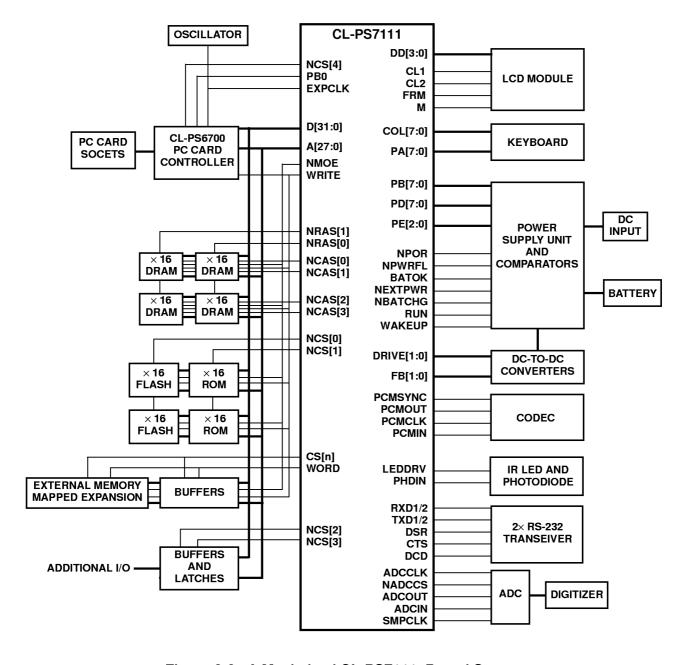

### 3.2 System Maximization

A maximum-configured system using the CL-PS7111 is shown in Figure 3-3. This system assumes all DRAMs and ROMs are 16-bit-wide devices. Watch-dog-timer tick rate is 1 Hz (in 13-MHz and 18.432-MHz modes). This 1-Hz clock is generated by a divider chain that divides the 64-Hz clock. The LSB of the RTCDIV field (SYSFLG[21:16]) provides the 1-Hz clock.

**NOTE:** The keyboard can be connected to more GPIO bits than illustrated to allow more than 64 keys. These extra pins, however, will not be wired into the WAKEUP pin functionality.

Figure 3-3. A Maximized CL-PS7111-Based System

### 3.3 Endian Functionality

The CL-PS7111 uses a little-endian configuration for internal registers. However, it is possible to connect the device to a big-endian external memory system. Table 3-1 and Table 3-2 demonstrate the behavior of the CL-PS7111 in big- and little-endian mode, including the effect of performing non-aligned word accesses. The register definitions in Chapter 5 define the behavior of the internal CL-PS7111 registers in big-endian mode in more detail.

The NCAS[3:0] lines for DRAM must always be connected with the same byte lane regardless of the endian functionality, so that NCAS[0] is connected with D[7:0], and NCAS[3] with D[31:24]. In a little-endian system, NCAS[0] is asserted for a read/write to byte 0 of DRAM and in a big-endian system NCAS[3] is asserted to access byte 0 of DRAM.

Table 3-1. Endian Functionality and Read Operations

|                  |                   | Byte Lanes to Memory/Ports/Registers |      |       |                      |     |      |       |       | R0 Contents |          |

|------------------|-------------------|--------------------------------------|------|-------|----------------------|-----|------|-------|-------|-------------|----------|

| Address<br>(W/B) | Data in<br>Memory | Big-endian Memory                    |      |       | Little-endian Memory |     |      |       | Big-  | Little-     |          |

|                  |                   | 7:0                                  | 15:8 | 23:16 | 31:24                | 7:0 | 15:8 | 23:16 | 31:24 | endian      | endian   |

| Word + 0 (W)     | 11223344          | 44                                   | 33   | 22    | 11                   | 44  | 33   | 22    | 11    | 11223344    | 11223344 |

| Word + 1 (W)     | 11223344          | 44                                   | 33   | 22    | 11                   | 44  | 33   | 22    | 11    | 44112233    | 44112233 |

| Word + 2 (W)     | 11223344          | 44                                   | 33   | 22    | 11                   | 44  | 33   | 22    | 11    | 33441122    | 33441122 |

| Word + 3 (W)     | 11223344          | 44                                   | 33   | 22    | 11                   | 44  | 33   | 22    | 11    | 22334411    | 22334411 |

| Word + 0 (B)     | 11223344          | χа                                   | Х    | Х     | 11                   | 44  | Х    | Х     | Х     | 00000011    | 00000044 |

| Word + 0 (B)     | 11223344          | Х                                    | Х    | 22    | Х                    | Х   | 33   | Х     | Х     | 00000022    | 00000033 |

| Word + 0 (B)     | 11223344          | Х                                    | 33   | Х     | Х                    | Х   | Х    | 22    | Х     | 00000033    | 00000022 |

| Word + 0 (B)     | 11223344          | 44                                   | Х    | Х     | Х                    | Х   | Х    | Х     | 11    | 00000044    | 00000011 |

a X indicates a 'don't care' state.

Table 3-2. Endian Functionality and Write Operations

|               |                   | Byte Lanes to Memory/Ports/Registers |                   |       |             |     |                      |       |       |  |

|---------------|-------------------|--------------------------------------|-------------------|-------|-------------|-----|----------------------|-------|-------|--|

| Address (W/B) | Register Contents | E                                    | Big-endian Memory |       |             |     | Little-endian Memory |       |       |  |

|               |                   | 7:0                                  | 15:8              | 23:16 | 31:24       | 7:0 | 15:8                 | 23:16 | 31:24 |  |

| Word + 0 (W)  | 11223344          | 44                                   | 33                | 22    | 11          | 44  | 33                   | 22    | 11    |  |

| Word + 1 (W)  | 11223344          | 44                                   | 33                | 22    | 11          | 44  | 33                   | 22    | 11    |  |

| Word + 2 (W)  | 11223344          | 44                                   | 33                | 22    | 11          | 44  | 33                   | 22    | 11    |  |

| Word + 3 (W)  | 11223344          | 44                                   | 33                | 22    | 11          | 44  | 33                   | 22    | 11    |  |

| Word + 0 (B)  | 11223344          | 44                                   | 44                | 44    | <b>44</b> a | 44  | 44                   | 44    | 44    |  |

**Table 3-2.** Endian Functionality and Write Operations (cont.)

|               |                   | Byte Lanes to Memory/Ports/Registers |      |       |       |                      |      |       |       |  |

|---------------|-------------------|--------------------------------------|------|-------|-------|----------------------|------|-------|-------|--|

| Address (W/B) | Register Contents | Big-endian Memory                    |      |       |       | Little-endian Memory |      |       |       |  |

|               |                   | 7:0                                  | 15:8 | 23:16 | 31:24 | 7:0                  | 15:8 | 23:16 | 31:24 |  |

| Word + 0 (B)  | 11223344          | 44                                   | 44   | 44    | 44    | 44                   | 44   | 44    | 44    |  |

| Word + 0 (B)  | 11223344          | 44                                   | 44   | 44    | 44    | 44                   | 44   | 44    | 44    |  |

| Word + 0 (B)  | 11223344          | 44                                   | 44   | 44    | 44    | 44                   | 44   | 44    | 44    |  |

a Bold indicates active byte lane.

### 3.4 CPU Core

The ARM710a microprocessor is a 32-bit RISC processor with an 8-Kbyte unified cache. This cache has 512 lines of four words arranged as a four-way set association. The cache is directly connected to the ARM710a microprocessor and caches the *virtual address* from the processor. The MMU translates the virtual address into a physical address, and contains a 64-entry TLB (translation look aside buffer) and is *post cache*; that is, it only translates external memory references (cache misses) to save power.

The big end bit in the ARM710a control register sets whether the CL-PS7111 treats words in memory as being stored in big-endian or little-endian format. See Chapters 5 and 11 of the *ARM710a Macrocell Data Sheet* for more information on the control register. Memory is viewed as a linear collection of bytes numbered upwards from zero. Bytes 0 to 3 hold the first stored word, bytes 4 to 7 the second, and so on. In the little-endian scheme, the lowest numbered byte in a word is considered to be the least-significant byte of the word, and the highest numbered byte is the most-significant. Byte 0 of the memory system should be connected to data lines 7 through 0 (D[7:0]) in this scheme. In the big-endian scheme, the most-significant byte of a word is stored at the lowest numbered byte and the least-significant byte is stored at the highest numbered byte. However, the memory controller of the CL-PS7111 will align the byte lane such that byte 0 of the memory system may always be connected to D[7:0]. Load and store are the only instructions affected by the endian functionality. For details on the ARM7 instruction set and CPU architecture, refer to the *ARM710a Macrocell Data Sheet*.

#### 3.5 Counters

The CL-PS7111 has two integrated identical timer counters: TC1 and TC2. Each timer counter has an associated 16-bit read/write data register and control bits in the System Control registers. Each counter is immediately loaded with the value written to the data register. This value decrements on the second active clock edge, arriving after the write (after the first complete period of the clock). When the timer counter underflows (reaches 0) the appropriate interrupt asserts. The timer counters can be read at any time. The clock source and mode are selected by writing to various bits in the System Control registers. Clock sources, when running from an 18.432-MHz master clock, are 512kHz and 2 kHz. When using the 13-MHz source, the default frequencies are 541 kHz and 2.115 kHz, respectively. However, in non-PLL mode, an optional divide by 26 frequency can be generated, thus generating a 500-kHz frequency when using the 13-MHz source. This divider is enabled by setting OSTB (Operating System Timing in SYSCON2[12]). When OSTB is set high to select the 500-kHz mode, the 500-kHz frequency is routed to the timers instead of 512 kHz. This does not affect the frequencies derived from any of the other internal peripherals.

The timer counters can operate in two modes: free-running or prescale.

### 3.5.1 Free-Running Mode

In free-running mode, the counter wraps around to 0xFFFF, then underflows and continues to count down. Any value written to TC1 or TC2 decrements on the second edge of the selected clock.

#### 3.5.2 Prescale Mode

In prescale mode, the value written to TC1 or TC2 automatically reloads when the counter underflows. Any value written to TC1 or TC2 decrements on the second edge of the selected clock. This mode can produce a programmable frequency to drive the buzzer or generate a periodic interrupt.

### 3.6 Realtime Clock

The CL-PS7111 contains a 32-bit RTC (realtime clock). The RTC is written and read the same as the timer counters, but is 32 bits wide. The RTC is always clocked at 1 Hz, generated from the 32.768-kHz oscillator. It also contains a 32-bit output-match register, that can be programmed to generate an interrupt when the time in the RTC matches a specific time written to this register. The RTC is only reset by an NPOR cold reset. Because the Realtime Clock Data register is updated from the 1-Hz clock derived from the 32-kHz source (asynchronous to the main memory system clock) the data register must always be read twice to ensure a valid and stable reading. This also applies when reading back the RTCDIV field (SYSFLG1[21:16]), reflecting the status of the six LSBs of the realtime clock counter.

### 3.7 State Control

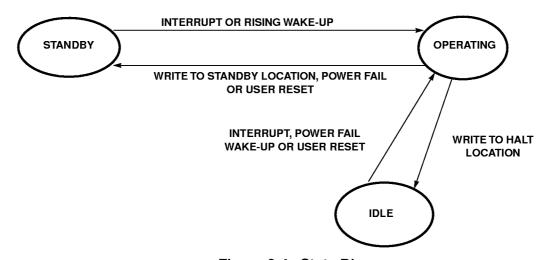

The CL-PS7111 supports three operating states: standby, idle, and operating.

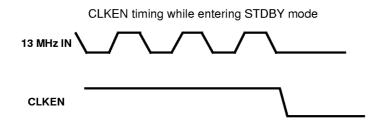

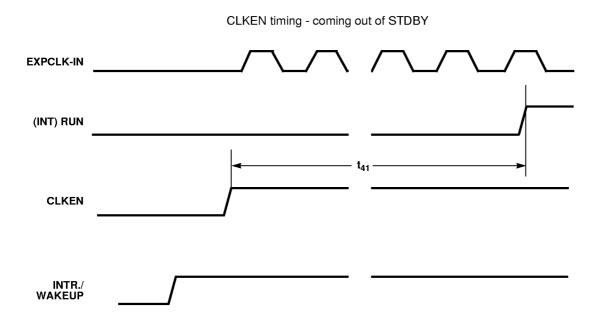

In the following descriptions, the RUN/CLKEN pin is used for the run functionality or the CLKEN functionality, allowing an external oscillator to be disabled in 13-MHz mode. Either RUN or CLKEN functionality is selected according to the state of CLKENSL bit (SYSCON2[[13]).

Table 3-3 shows how different modules in CL-PS7111 behave in different states.

Table 3-3. Peripheral Status in Different Operating States

| Module        | Operating | ldle | Standby      | NPOR<br>Reset | NURESET<br>Reset |

|---------------|-----------|------|--------------|---------------|------------------|

| DRAM Ctrl     | ON        | ON   | Self refresh | OFF           | Self refresh     |

| UARTs         | ON        | ON   | OFF          | Reset         | Reset            |

| LCD FIFO      | ON        | ON   | Reset        | Reset         | Reset            |

| LCD           | ON        | ON   | OFF          | Reset         | Reset            |

| ADC Interface | ON        | ON   | OFF          | Reset         | Reset            |

| Codec         | ON        | ON   | OFF          | Reset         | Reset            |

| Timers        | ON        | ON   | OFF          | Reset         | Reset            |

| RTC           | ON        | ON   | ON           | ON            | ON               |

| DC-to-DC      | ON        | ON   | OFF          | Reset         | Reset            |

| CPU           | ON        | OFF  | OFF          | Reset         | Reset            |

Table 3-3. Peripheral Status in Different Operating States (cont.)

| Module         | Operating | Idle | Standby | NPOR<br>Reset | NURESET<br>Reset |

|----------------|-----------|------|---------|---------------|------------------|

| Interrupt Ctrl | ON        | ON   | ON      | Reset         | Reset            |

| PLL/CLKEN      | ON        | ON   | OFF     | OFF           | OFF              |

### Standby State

The standby state is as if the computer is switched off, there is no display and the main oscillator is shut down. When the 18.432-MHz mode is selected, the PLL will be shut down. In 13-MHz mode, if the CLKENSL bit is set low, then the CLKEN signal will be forced low and can disable an external oscillator. Only the realtime clock is running. The device automatically enters the standby state after power is first applied or after a system reset. The only exit from the standby state is to the operating state. Before entering the standby state, if external I/O devices (such as CL-PS6700s connected to NCS[4] or NCS[5]) are in use, the software must check for idle before issuing the write to the standby location.

When in standby, all system memory and states are maintained and the system clock is kept current. The PLL/on-chip oscillator or external oscillator is disabled, and the system is static except for the low-power (32-kHz) watch crystal oscillator and divider chain to the realtime clock. The RUN signal is driven low. This signal can be used externally in the system to power down other system modules.

### Idle State

The idle state means the device is functioning, but the processor clock is halted while it waits for an event, such as a key press, to generate an interrupt (a rising edge on the external wake-up pin or a rising edge on the decode of Port A bits 0–5 or 7). The PLL (in 18.432-MHz mode) or the external 13-MHz clock source always remains active in the idle state.

### Operating State

The operating state is the same as the idle state, except that the processor clock is running.

The device is forced into the standby state at power up or reset by the NPOR signal (called a 'cold' reset) and is the only completely asynchronous reset to the CL-PS7111. The transition to the operating state is caused by a rising edge on the WAKEUP input signal, or by a rising edge on any of the Port A bits 0–5 or 7 (corresponding to keyboard input). After a cold reset, these are the only possible events for waking up the device. When entering the standby state from the operating state, the software should leave some interrupt sources enabled, meaning there is a third possible means of exit from the standby state if an enabled interrupt is generated (for example, the RTC interrupt). Once self-refresh is enabled for the DRAMs, any transition to the standby state forces the DRAMs to the self-refresh state before stopping the PLL or external oscillator.

Once in the operating state, the idle state is entered by writing to a special internal memory location in the CL-PS7111. If an interrupt or wake-up event occurs, execution of the next instruction continues in the operating state. A write to the STDBY-WAKEUP internal memory location causes the transition from the operating state to the standby state.

The system can also be forced into the standby state by hardware if the NPWRFL or NURESET inputs are forced low. In this case, the transition is synchronized with DRAM cycles to avoid errors or short cycles.

The system only transitions to the operating state from the standby state if either the NEXTPWR input is low or the BATOK and NPWRFL inputs are high. This prevents the system attempting to start when the power supply is inadequate (for example, when the main batteries are flat corresponding to a low level in NPWRFL or BATOK).

From standby mode, when the WAKEUP signal is applied, the CL-PS7111 initializes into a ready-to-start state and waits for the first clocks, although the CPU is still held in reset. When the first clock is applied, there is a delay of about eight clocks before the CPU is first clocked.

Figure 3-4 is a state diagram for the CL-PS7111.

Figure 3-4. State Diagram

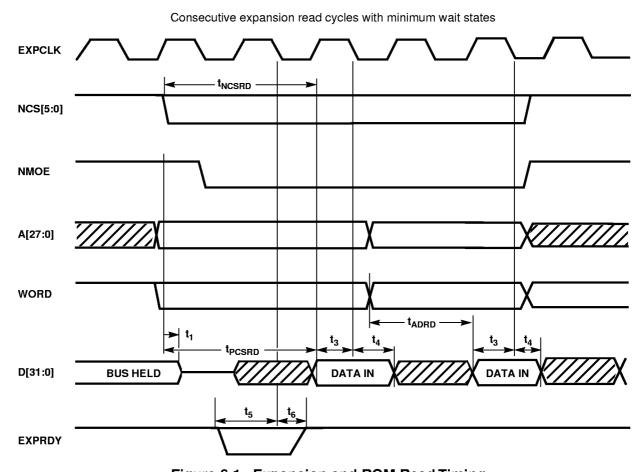

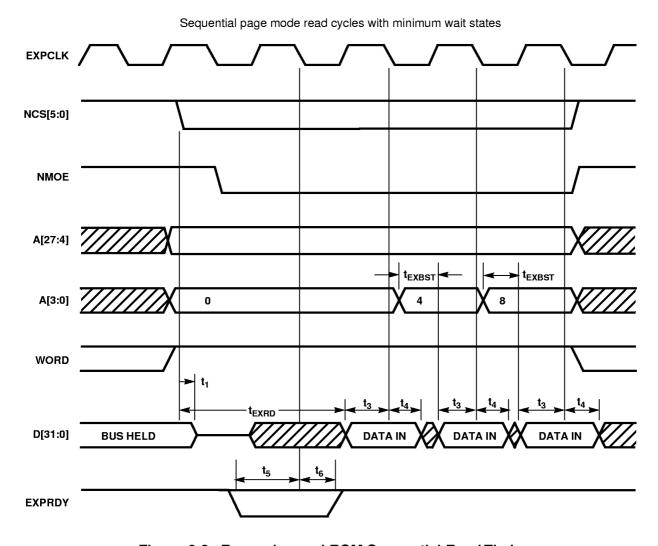

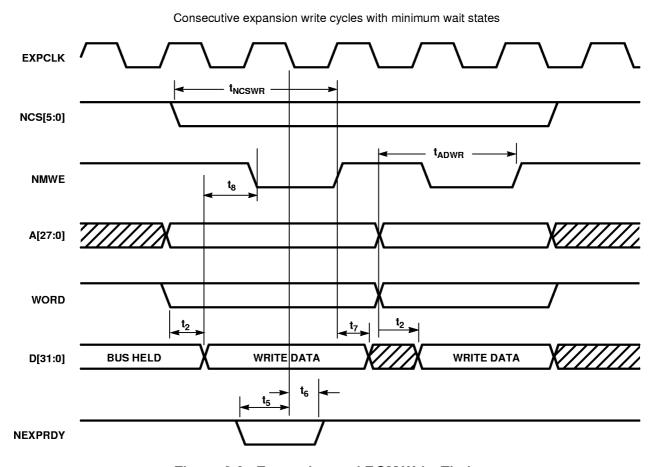

### 3.8 Expansion and ROM Interface

Six separate linear memory or expansion segments are decoded by the CL-PS7111, two of which can be reserved for two PCMCIA cards each interfacing to the single device CL-PS6700. Each segment is 256 Mbytes and can be interfaced by using a conventional SRAM-like interface. Aside from the six segments, an additional segment is dedicated for the on-chip 2 Kbytes of SRAM and is fully decoded such that the addresses for the SRAM do not repeat within the bank. Any of the six segments can be individually programmed to be 8-, 16-, or 32-bits wide, support Page mode access, and execute from 1–4 wait states for nonsequential accesses, and 0–3 for burst mode accesses. The zero-wait-state sequential access feature is designed to support burst mode ROMs; for writable memory devices that use the NMWE pin, zero-wait-state sequential accesses are not permitted and one wait state is the minimum that should be programmed in the sequential field of the appropriate MEMCFG register. Bus cycles can also be extended using the EXPRDY input signal. Page mode access is accomplished by running up to four accesses together. This can significantly improve bus bandwidth to devices such as ROMs. Sequential Burst mode access is always faulted (the bus returned to idle) after four accesses, regardless of bus width to allow DMA and refresh cycles to occur.

Bits 5 and 6 of the SYSCON2 register (see Section 5.38 on page 70) independently enable the interfaces to the CL-PS6700 (PCMCIA slot drivers). When either of these interfaces are enabled, the corresponding device select (NCS4 and/or NCS5) becomes dedicated to that CL-PS6700 interface. The state of SYSCON2[5] determines the function of device select NCS4 (such as the CL-PS6700 interface or standard device select functionality); SYSCON2[6] controls NCS5 in a similar way. There is no interaction between these bits.

For applications that require a small display (such as an alphanumeric one-way pager), on-chip SRAM can be used as the frame buffer and no external DRAM are required.