# 6-channel switching regulator controller

## BA9736KV

The BA9736KV is a 6-channel controller that includes all of the circuits required to construct a switching regulator. The circuits on the chip include a triangular-wave generator, a reference voltage circuit, an error amplifier, a PWM comparator, a pseudo-totem-pole driver, and a variety of protection circuits.

### ● Applications

VCR / cameras, digital still cameras, and other portable equipment

### ● Features

- 1) The totem-pole driver can directly drive power transistors, and the on current can be set to the rating current using an external resistor.

- 2) Miss-operation prevention circuit for low-voltage input.

- 3) Output cutoff circuit (timer latch type) for overload protection.

- 4) Channels 1 and 4 employ FETs, and have totem-pole drivers that rectify synchronously with a chopper. The duty offset of the chopper can be adjusted externally.

- 5) For channel control, by making STB low level, all channels go off, and by making STB3 low level, channel 3 can be switched off independently.

- 6) Soft start is applied to all channels using an external capacitor, and is synchronized with the rising edges of STB and STB3.

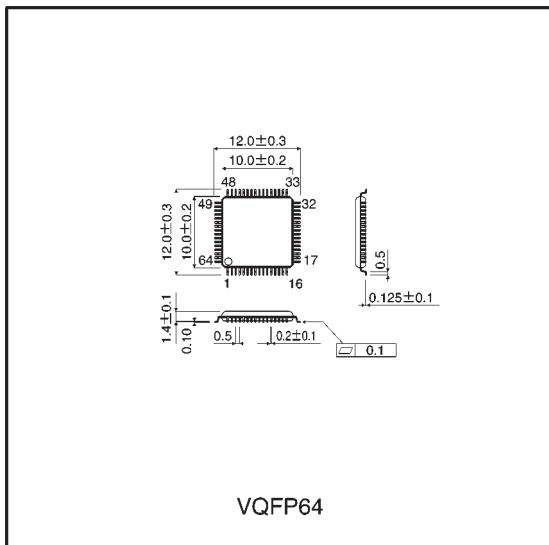

- 7) VQFP64 package (0.5mm pitch).

### ● Absolute maximum ratings (Ta = 25°C)

| Parameter             | Symbol           | Limits   | Unit |

|-----------------------|------------------|----------|------|

| Power supply voltage  | V <sub>cc</sub>  | 13.5     | V    |

| Output current        | I <sub>out</sub> | 100      | mA   |

| Power dissipation     | P <sub>d</sub>   | 750*1    | mW   |

|                       |                  | 1000*2   | mW   |

| Operating temperature | T <sub>opr</sub> | -25~+85  | °C   |

| Storage temperature   | T <sub>stg</sub> | -55~+125 | °C   |

\*1 Reduced by 7.5mW for each increase in Ta of 1°C over 25°C(stand alone).

\*2 When mounted on a 70mm × 70mm × 1.6mm PC board.

### ● Recommended operating conditions (Ta = 25°C)

| Parameter                          | Symbol            | Min. | Typ. | Max.  | Unit |

|------------------------------------|-------------------|------|------|-------|------|

| Power supply voltage               | V <sub>cc</sub>   | 2.8  | -    | 13.5  | V    |

| OSC timing resistor                | R <sub>T</sub>    | 12   | -    | -     | kΩ   |

| OSC timing capacitor               | C <sub>T</sub>    | 100  | -    | 10000 | pF   |

| OSC oscillator frequency           | f <sub>osc</sub>  | 10   | -    | 800   | kHz  |

| Output current setting resistor    | R <sub>BIAS</sub> | 3.3  | 10   | 33    | kΩ   |

| Off-peak current setting capacitor | C <sub>OFF</sub>  | 100  | -    | -     | pF   |

## ● Block diagram

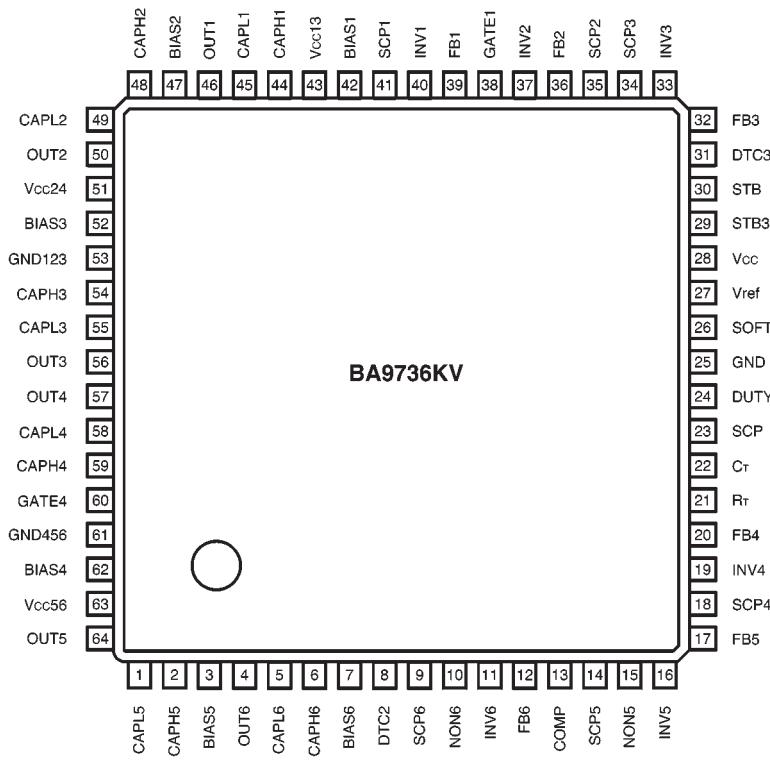

## ● Pin descriptions

| Pin No.                | Pin name              | Function                                                  |

|------------------------|-----------------------|-----------------------------------------------------------|

| 1, 5, 45, 49, 55, 58   | CAPL 5, 6, 1, 2, 3, 4 | L connection for off transistor current-setting capacitor |

| 2, 6, 44, 48, 54, 59   | CAPH 5, 6, 1, 2, 3, 4 | H connection for off transistor current-setting capacitor |

| 3, 7, 42, 47, 52, 62   | BIAS 5, 6, 1, 2, 3, 4 | Output current setting                                    |

| 4, 46, 50, 56, 57, 64  | OUT 6, 1, 2, 3, 4, 5  | Power transistor base connection                          |

| 9, 14, 18, 34, 35, 41  | SCP 6, 5, 4, 3, 2, 1  | Output voltage monitor for ch1 to ch6 protection          |

| 11, 16, 19, 33, 37, 40 | INV6, 5, 4, 3, 2, 1   | Inverting input for error amplifier                       |

| 12, 17, 20, 32, 36, 39 | FB 6, 5, 4, 3, 2, 1   | Error amplifier output                                    |

| 13                     | COMP                  | Timer latch external trigger input                        |

| 21                     | R <sub>T</sub>        | Connection for resistor for triangular-wave timing        |

| 22                     | C <sub>T</sub>        | Connection for capacitor for triangular-wave timing       |

| 23                     | SCP                   | Connection for capacitor for setting timing latch delay   |

| 24                     | DUTY                  | MOSFET duty control                                       |

| 25                     | GND                   | Ground                                                    |

| 26                     | SOFT                  | Connection for capacitor for setting soft start           |

| 27                     | V <sub>ref</sub>      | Reference voltage output                                  |

| 28                     | V <sub>cc</sub>       | Power supply input                                        |

| 29                     | STB3                  | Channel 3 on / off switch                                 |

| 30                     | STB                   | All channel on / off switches                             |

| 8, 31                  | DTC 2, 3              | Dead time control                                         |

| 38, 60                 | GATE1, 4              | MOSFET gate connection                                    |

| 43                     | V <sub>cc13</sub>     | Power supply input for channels 1 and 3 output stages     |

| 51                     | V <sub>cc24</sub>     | Power supply input for channels 2 and 4 output stages     |

| 63                     | V <sub>cc56</sub>     | Power supply input for channels 5 and 6 output stages     |

| 53                     | GND123                | Ground connection for channels 1, 2, and 3 output stages  |

| 61                     | GND456                | Ground connection for channels 4, 5, and 6 output stages  |

| 10, 15                 | NON6, 5               | Non-inverting input for error amplifier                   |

●Electrical characteristics (unless otherwise noted,  $T_a = 25^\circ\text{C}$ ,  $V_{cc} = 7.2\text{V}$ ,  $f_{osc} = 700\text{kHz}$  and output voltage off)

| Parameter                    | Symbol     | Min.             | Typ.           | Max.             | Unit          | Conditions                                                 | Measurement circuit |

|------------------------------|------------|------------------|----------------|------------------|---------------|------------------------------------------------------------|---------------------|

| Standby current              | $I_{st}$   | —                | 70             | 120              | $\mu\text{A}$ | $STB=0\text{V}$                                            | Fig.1               |

| Circuit current              | $I_{cc}$   | —                | 7.5            | 10.2             | mA            | $R_T=47\text{k}\Omega$                                     | Fig.1               |

| ⟨Reference voltage⟩          |            |                  |                |                  |               |                                                            |                     |

| Output voltage               | $V_{ref}$  | 1.485            | 1.5            | 1.515            | V             | $I_{ref}=-1\text{mA}$                                      | Fig.1               |

| Line regulation              | $DV_{LI}$  | —                | 2.0            | 12.5             | mV            | $V_{cc}=2.8\text{V}\sim13\text{V}$ , $I_{ref}=-1\text{mA}$ | Fig.1               |

| Load regulation              | $DV_{LO}$  | —                | 1.0            | 7.5              | mV            | $I_{ref}=-0.1\text{m}\sim-1\text{mA}$                      | Fig.1               |

| Short-circuit output current | $I_{os}$   | —4               | —20            | —                | mA            | $V_{ref}=0\text{V}$                                        | Fig.1               |

| ⟨Low-voltage input monitor⟩  |            |                  |                |                  |               |                                                            |                     |

| Threshold voltage 1          | $V_{UV1}$  | —                | 2.40           | 2.50             | V             | ON STATE                                                   | Fig.3               |

| Threshold voltage 2          | $V_{UV2}$  | 1.90             | 2.30           | —                | V             | OFF STATE                                                  | Fig.3               |

| Hysteresis width             | $V_{HYS}$  | 0.05             | 0.1            | 0.6              | V             | —                                                          | Fig.3               |

| ⟨Overload cutoff⟩            |            |                  |                |                  |               |                                                            |                     |

| Channel 1 threshold          | $V_{sc1}$  | 1.47             | 1.50           | 1.53             | V             | Including reference voltage ( $V_{ref}$ ) error            | Fig.2               |

| Channel 2 threshold          | $V_{sc2}$  | 1.47             | 1.50           | 1.53             | V             | Including reference voltage ( $V_{ref}$ ) error            | Fig.2               |

| Channel 3 threshold          | $V_{sc3}$  | 1.47             | 1.50           | 1.53             | V             | Including reference voltage ( $V_{ref}$ ) error            | Fig.2               |

| Channel 4 threshold          | $V_{sc4}$  | 1.47             | 1.50           | 1.53             | V             | Including reference voltage ( $V_{ref}$ ) error            | Fig.2               |

| Channel 5 threshold          | $V_{sc5}$  | NON×             | NON            | NON×             | V             | —                                                          | Fig.2               |

| Channel 6 threshold          | $V_{sc6}$  | 2.85/10<br>—0.07 | ×3/10<br>—0.05 | 3.15/10<br>—0.03 | V             | —                                                          | Fig.2               |

| ⟨Protection circuit⟩         |            |                  |                |                  |               |                                                            |                     |

| Input threshold              | $V_{tsc}$  | 1.42             | 1.50           | 1.58             | V             | —                                                          | Fig.2               |

| Standby voltage              | $V_{ssc}$  | —                | 10             | 30               | mV            | —                                                          | Fig.2               |

| Input source current         | $I_{SCP}$  | —4.0             | —2.5           | —1.0             | $\mu\text{A}$ | —                                                          | Fig.2               |

| ⟨STB⟩                        |            |                  |                |                  |               |                                                            |                     |

| Input bias current           | $I_{st}$   | —                | 190            | —                | $\mu\text{A}$ | $STB=5\text{V}$                                            | Fig.1               |

| Threshold voltage            | $V_{STB}$  | 0.4              | —              | 2.0              | V             | —                                                          | Fig.1               |

| ⟨STB3⟩                       |            |                  |                |                  |               |                                                            |                     |

| Input bias current           | $I_{st3}$  | —                | 95             | —                | $\mu\text{A}$ | $STB3=5\text{V}$                                           | Fig.1               |

| Threshold voltage            | $V_{STB3}$ | 0.4              | —              | 2.0              | V             | —                                                          | Fig.1               |

| ⟨SCP trigger⟩                |            |                  |                |                  |               |                                                            |                     |

| Input bias current           | $I_{BT}$   | —                | —0.4           | 2.0              | $\mu\text{A}$ | $COMP=1\text{V}$                                           | —                   |

| Threshold voltage            | $V_{TT}$   | 1.45             | 1.5            | 1.55             | V             | —                                                          | —                   |

©Not designed for radiation resistance.

| Parameter                                              | Symbol                               | Min.                     | Typ. | Max.                 | Unit | Conditions                                  | Measurement circuit |

|--------------------------------------------------------|--------------------------------------|--------------------------|------|----------------------|------|---------------------------------------------|---------------------|

| <b>&lt;Triangular wave oscillator&gt;</b>              |                                      |                          |      |                      |      |                                             |                     |

| Oscillation frequency                                  | fosc1                                | 385                      | 430  | 475                  | kHz  | R <sub>T</sub> =47kΩ, C <sub>T</sub> =100pF | Fig.1               |

|                                                        | fosc2                                | 630                      | 700  | 770                  | kHz  | R <sub>T</sub> =27kΩ, C <sub>T</sub> =100pF | Fig.1               |

| Frequency deviation                                    | Df                                   | —                        | 1    | 5                    | %    | V <sub>CC</sub> =2.8→13V                    | Fig.1               |

| Upper limit voltage for the triangular wave            | V <sub>CM1</sub>                     | 1.35                     | 1.50 | 1.65                 | V    | —                                           | Fig.1               |

| Lower limit voltage for the triangular wave            | V <sub>CM1</sub>                     | 0.93                     | 1.08 | 1.23                 | V    | —                                           | Fig.1               |

| <b>&lt;Error amplifier&gt;</b>                         |                                      |                          |      |                      |      |                                             |                     |

| Channel 1 output setting voltage                       | V <sub>O1</sub>                      | 1.47                     | 1.5  | 1.53                 | V    | Including reference voltage (Vref) error    | Fig.2               |

| Channel 2 output setting voltage                       | V <sub>O2</sub>                      | 1.47                     | 1.5  | 1.53                 | V    | Including reference voltage (Vref) error    | Fig.2               |

| Channel 3 output setting voltage                       | V <sub>O3</sub>                      | 1.47                     | 1.5  | 1.53                 | V    | Including reference voltage (Vref) error    | Fig.2               |

| Channel 4 output setting voltage                       | V <sub>O4</sub>                      | 1.47                     | 1.5  | 1.53                 | V    | Including reference voltage (Vref) error    | Fig.2               |

| Non-inverting input voltage range for channels 5 and 6 | V <sub>N56</sub>                     | 0                        | —    | V <sub>CC</sub> —1.7 | V    | NON5, 6                                     | Fig.2               |

| Inverting input voltage range for channels 5 and 6     | V <sub>I56</sub>                     | 0                        | —    | V <sub>CC</sub> —1.7 | V    | INV5, 6                                     | Fig.2               |

| Channel 5 and channel 6 input offset voltage           | V <sub>OS5</sub><br>V <sub>OS6</sub> | —15                      | —    | 15                   | mV   | —                                           | —                   |

| Output low level voltage                               | V <sub>OL</sub>                      | —                        | —    | 0.2                  | V    | —                                           | Fig.2               |

| Output high level voltage                              | V <sub>OH</sub>                      | V <sub>ref</sub><br>—0.1 | —    | —                    | V    | —                                           | Fig.2               |

| <b>&lt;PWM comparator&gt;</b>                          |                                      |                          |      |                      |      |                                             |                     |

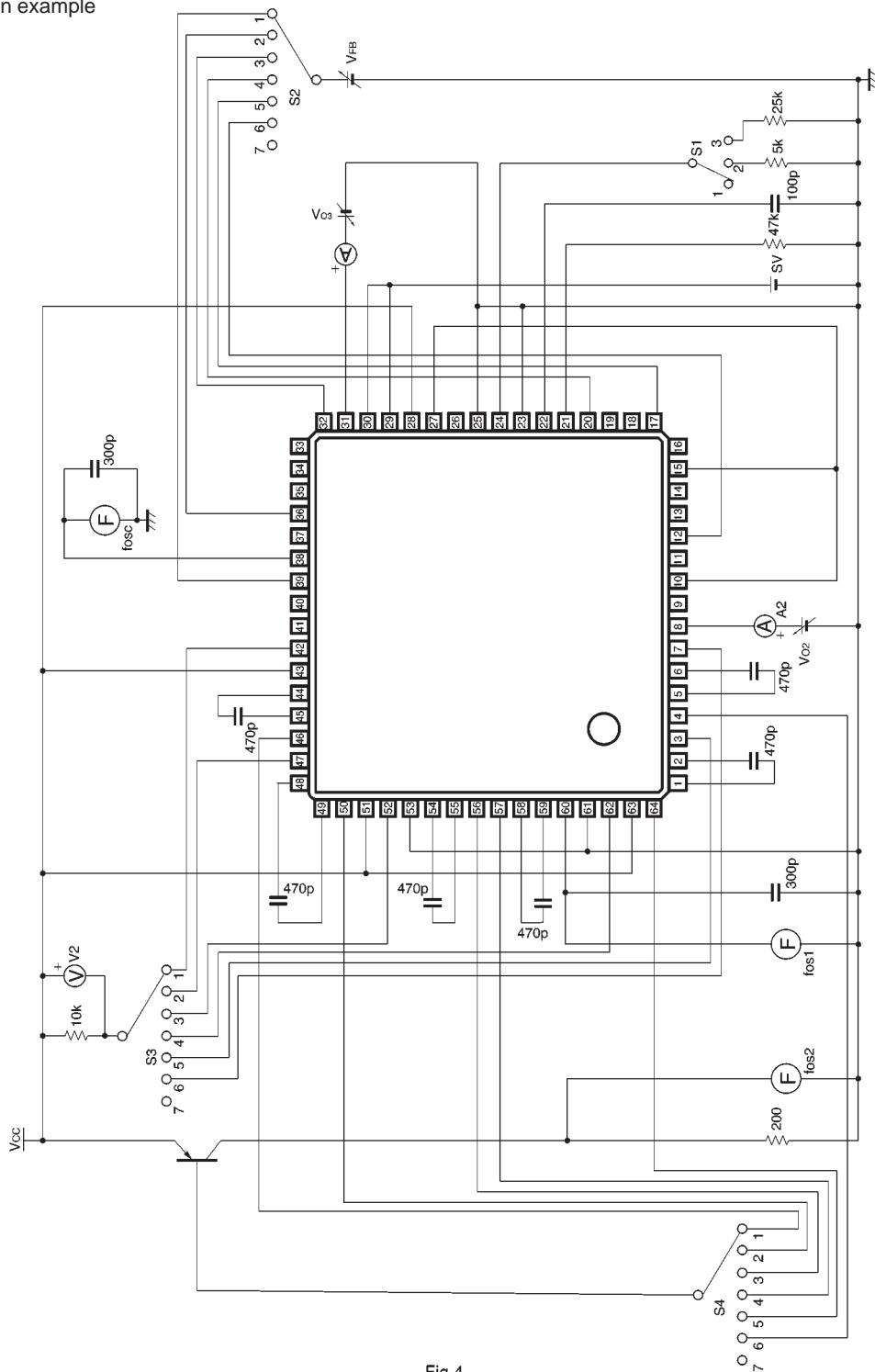

| DTC input current                                      | I <sub>DT</sub>                      | —                        | —0.4 | —6.0                 | μA   | DTC2, 3=0.5V                                | Fig.4               |

| 0% DUTY threshold                                      | V <sub>to</sub>                      | 0.53                     | 0.63 | 0.73                 | V    | —                                           | Fig.4               |

| 100% DUTY threshold                                    | V <sub>t100</sub>                    | 1.22                     | 1.32 | 1.42                 | V    | —                                           | Fig.4               |

| <b>&lt;Soft start&gt;</b>                              |                                      |                          |      |                      |      |                                             |                     |

| Input source current                                   | I <sub>so</sub>                      | —1                       | —2.5 | —4                   | μA   | STB3=3V, SOFT=1V                            | Fig.1               |

| <b>&lt;MOS DUTY control&gt;</b>                        |                                      |                          |      |                      |      |                                             |                     |

| ON DUTY1                                               | D <sub>1</sub>                       | —                        | 20   | —                    | %    | V <sub>FB1</sub> , 4=1V, RD=5kΩ             | Fig.4               |

| ON DUTY2                                               | D <sub>2</sub>                       | —                        | 40   | —                    | %    | V <sub>FB1</sub> , 4=1V, RD=25kΩ            | Fig.4               |

| <b>&lt;Output stage&gt;</b>                            |                                      |                          |      |                      |      |                                             |                     |

| Output sink current                                    | I <sub>OUT</sub>                     | 4.3                      | 5.8  | 7.3                  | mA   | RB=10kΩ                                     | Fig.3               |

| MOS gate sink current                                  | I <sub>GS1</sub>                     | —                        | 40   | —                    | mA   | GATE1, 4=1V                                 | Fig.3               |

| MOS gate sink current                                  | I <sub>GS0</sub>                     | —                        | —140 | —                    | mA   | GATE1, 4=2V                                 | Fig.3               |

| MOS gate high level output                             | V <sub>OH</sub>                      | 3.5                      | 4.0  | —                    | V    | —                                           | Fig.3               |

| MOS gate low level output                              | V <sub>OL</sub>                      | —                        | 0.1  | 0.3                  | V    | —                                           | Fig.3               |

◎Not designed for radiation resistance.

Recommended maximum oscillator frequency (Ta=25°C), fMax.=800kHz.

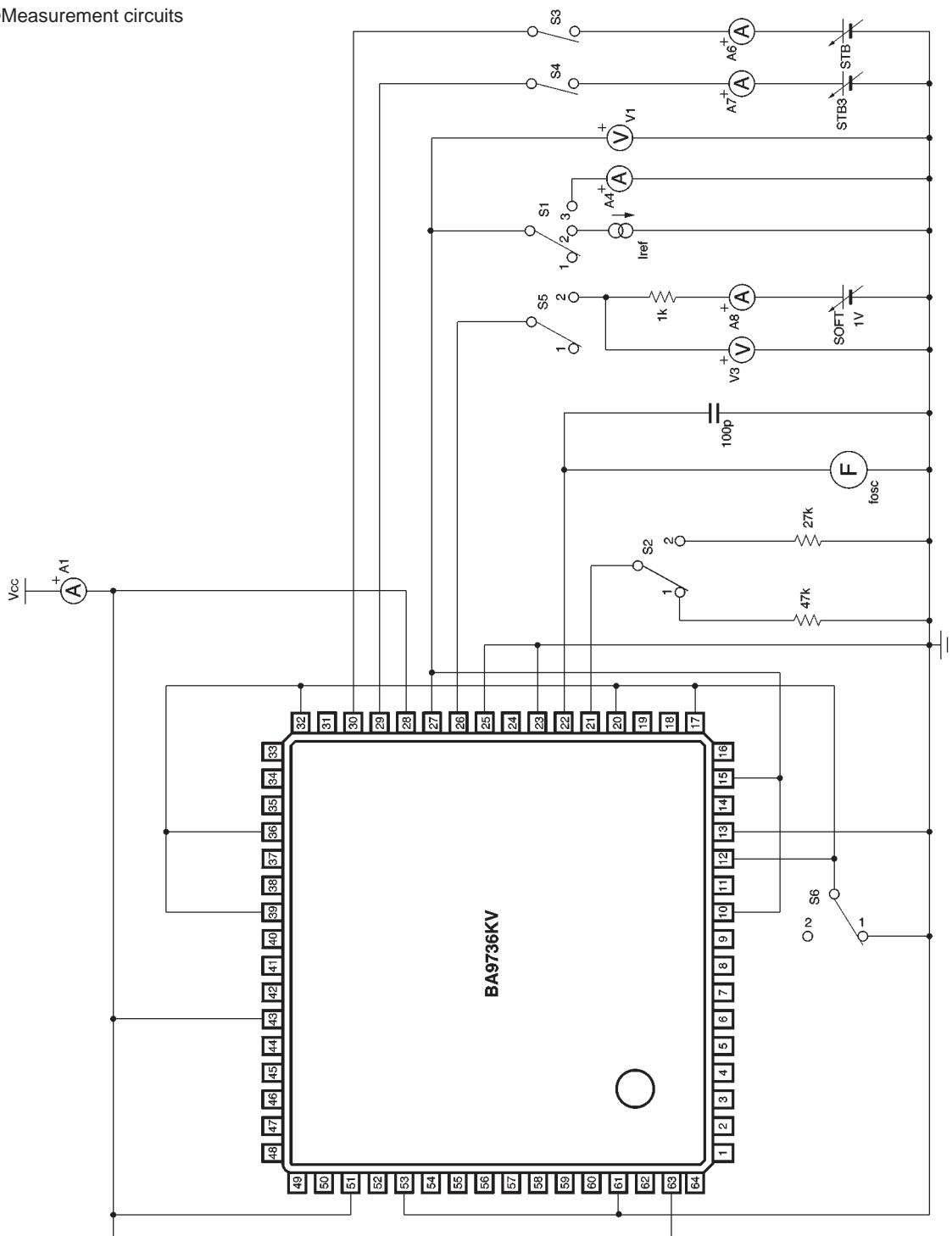

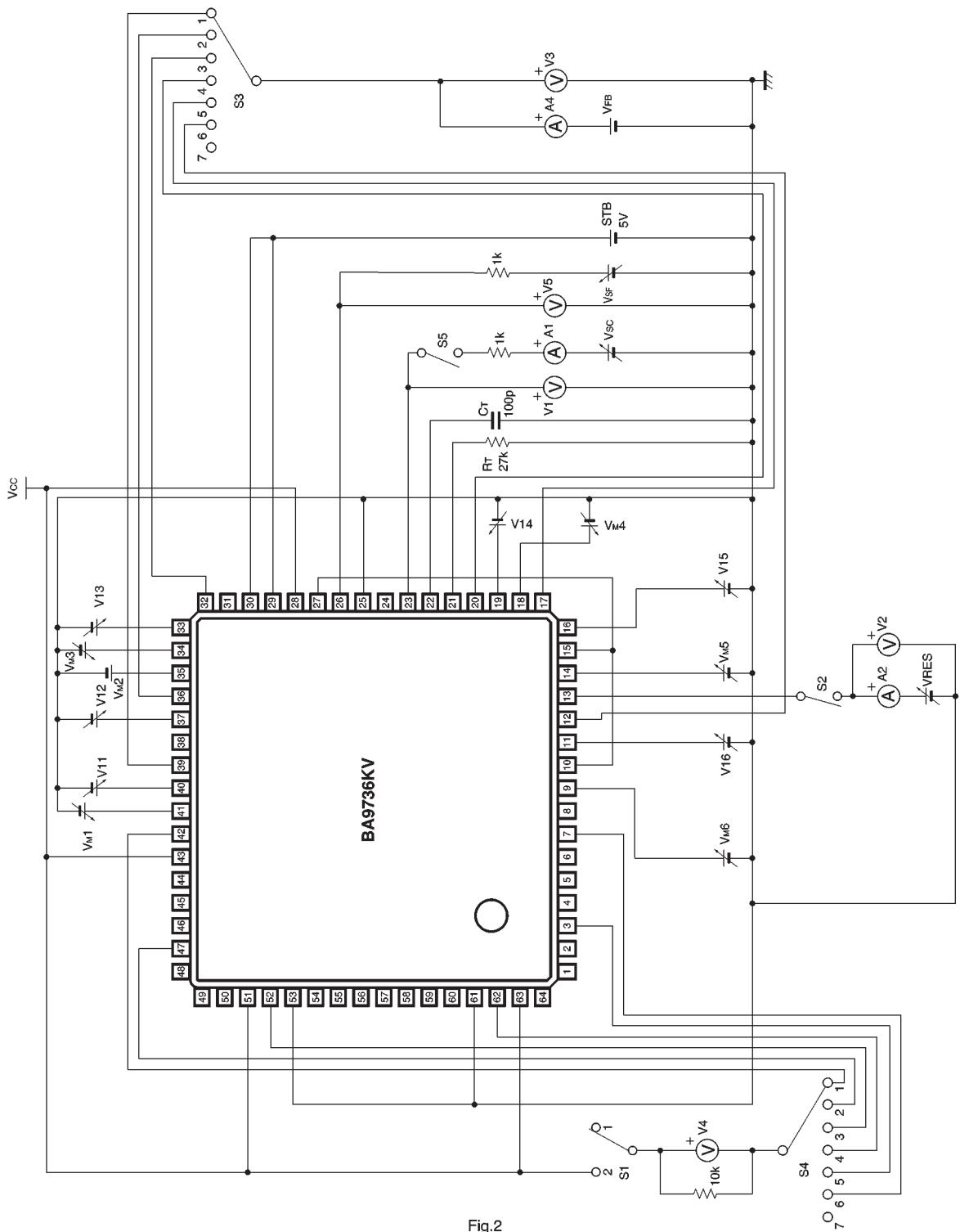

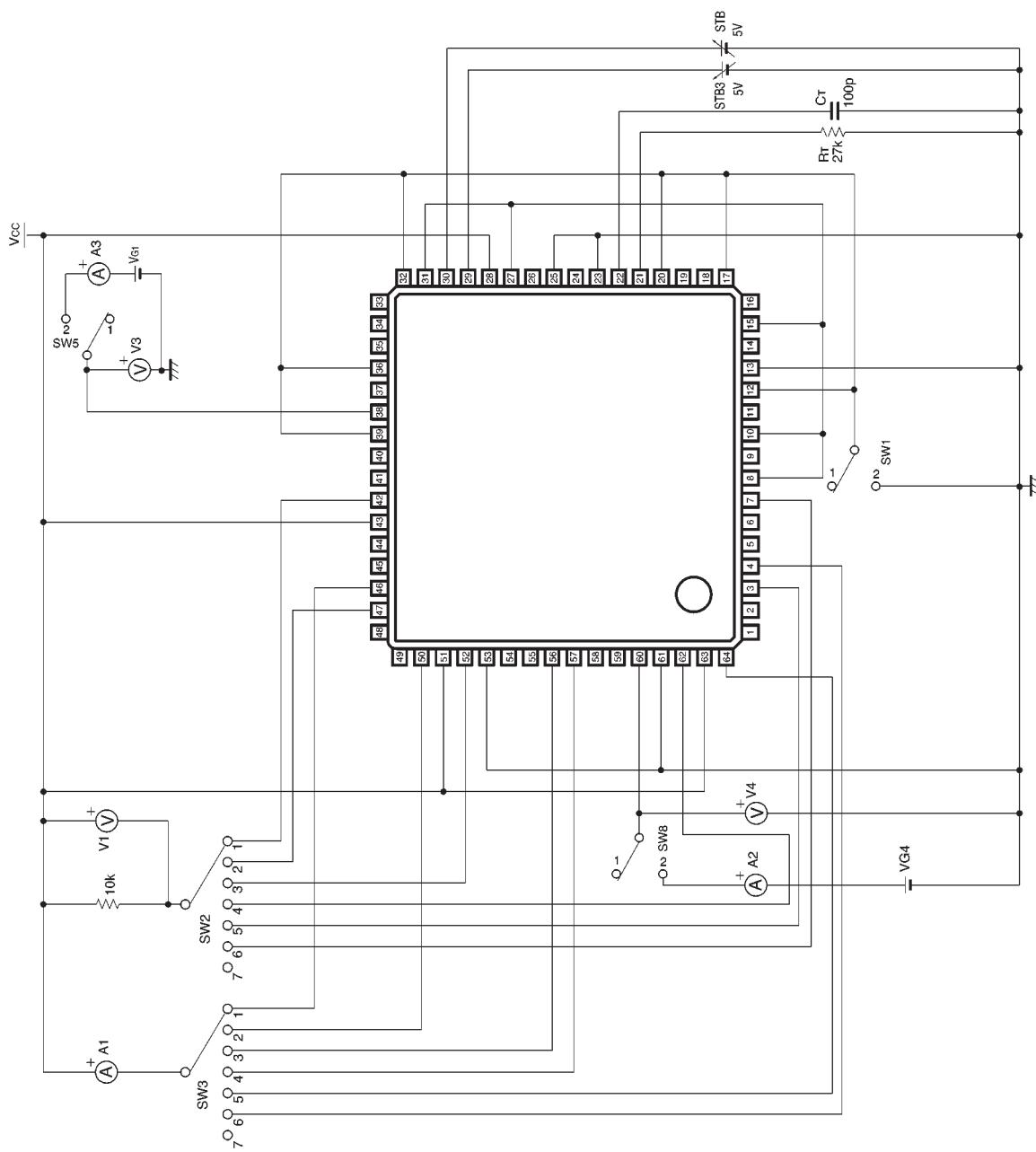

## ● Measurement circuits

Fig.1

Fig.2

Fig.3

## ● Application example

Fig.4

### ● Operation notes

- (1) Set the dead-time input voltage to 0.73V or more.

- (2) Use short and wide wiring tracks for the power supply and ground to keep the mutual impedance as small as possible, and use inductors and capacitors to keep ripple to a minimum.

- (3) Set  $R_{DUTY}$  so that the drive stage and the MOS drive stage for the synchronous rectifier channel are not on at the same time.

- (4) If you are not using the external trigger input (pin 13) for overload output cutoff, pull it up to  $V_{CC}$  (pin 28).

(5) Great care has been paid to the quality of this component. However, if the absolute maximum ratings for temperature and applied voltage are exceeded, the IC may be destroyed. Since it is not possible to predict whether it will be in short mode or open mode if the IC is destroyed, if there is a chance that the maximum ratings of the IC will be exceeded, use appropriate physical protective measures (fuses etc.).

### ● External dimensions (Units: mm)

VQFP64