### Document Number: MC33907-MC33908D2 Rev. 5.0, 10/2016 Data Sheet: Advance Information

## Power system basis chip with high speed CAN and LIN transceivers

The 33907/33908 SMARTMOS devices area multi-output, power supply, integrated circuit, including HSCAN and/or LIN transceivers, dedicated to the automotive market.

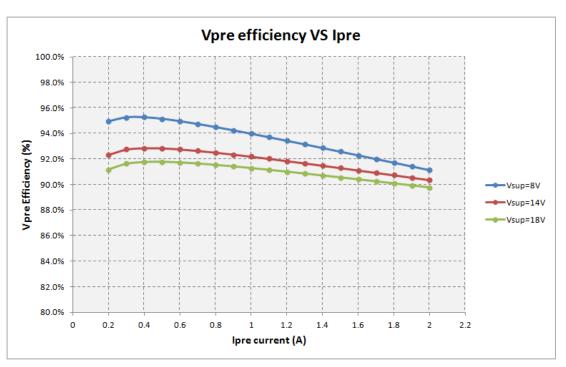

Multiple switching and linear voltage regulators, including low-power mode (32 µA) are available with various wake-up capabilities. An advanced power management scheme is implemented to maintain high efficiency over wide input voltages (down to 2.7 V) and wide output current ranges (up to 1.5 A).

The 33907/33908 include enhanced safety features, with multiple fail-safe outputs, becoming a full part of a safety oriented system partitioning, to reach a high integrity safety level (up to ASIL D).

The built-in enhanced high-speed CAN interface fulfills the ISO11898-2 and -5 standards. The LIN interface fulfills LIN protocol specifications 1.3, 2.0, 2.1, 2.2, and SAEJ2602-2

#### Features

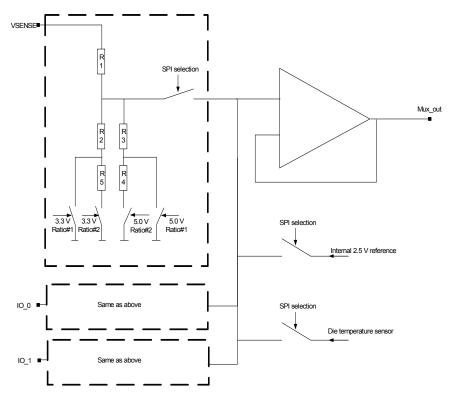

- Battery voltage sensing & MUX output pin

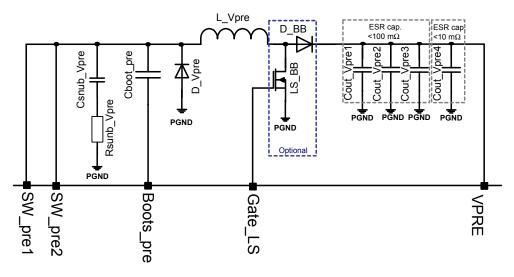

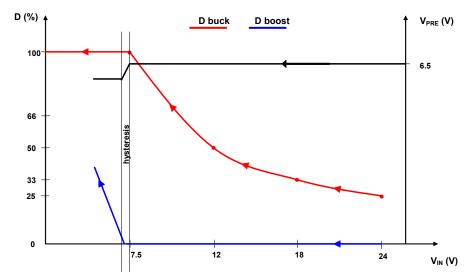

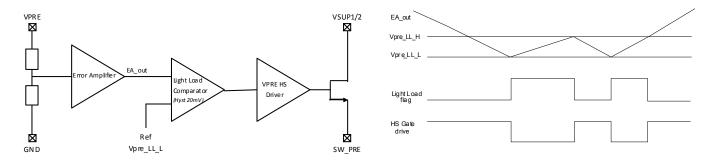

- Highly flexible SMPS pre-regulator, allowing two topologies: non-inverting buck-boost and standard buck

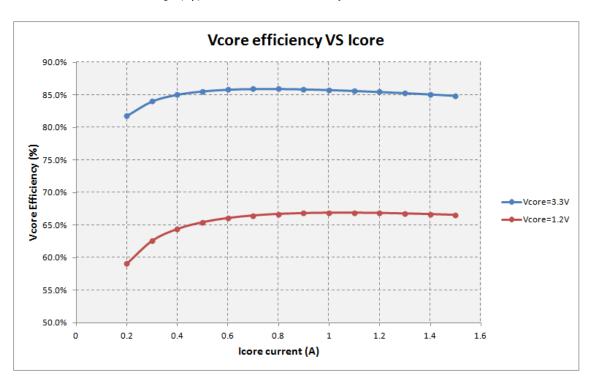

- Switching mode power supply (SMPS) dedicated to MCU core supply, from 1.2 V to 3.3 V delivering up to 1.5 A

- Multiple wake-up sources in low-power mode: CAN, LIN, and/or IOs

- Six configurable I/Os

- Linear voltage regulator dedicated to auxiliary functions, or to a sensor supply (V<sub>CCA</sub> tracker or independent), 5.0 V or 3.3 V

- Linear voltage regulator dedicated to MCU A/D reference voltage or I/Os supply (V<sub>CCA</sub>), 5.0 V or 3.3 V

33907 33908

#### **POWER SYSTEM BASIS CHIP**

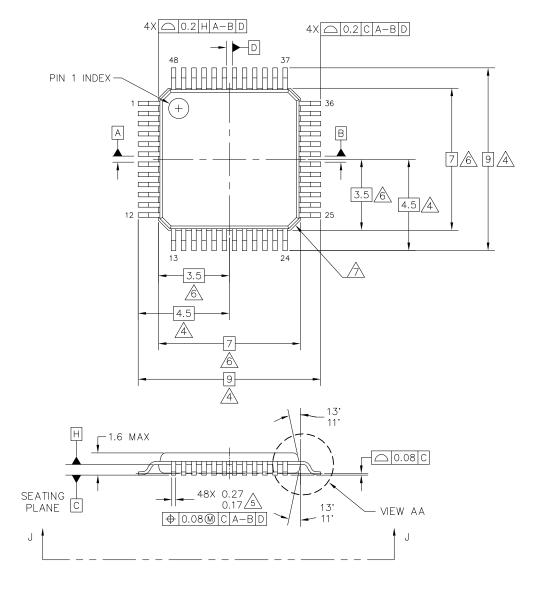

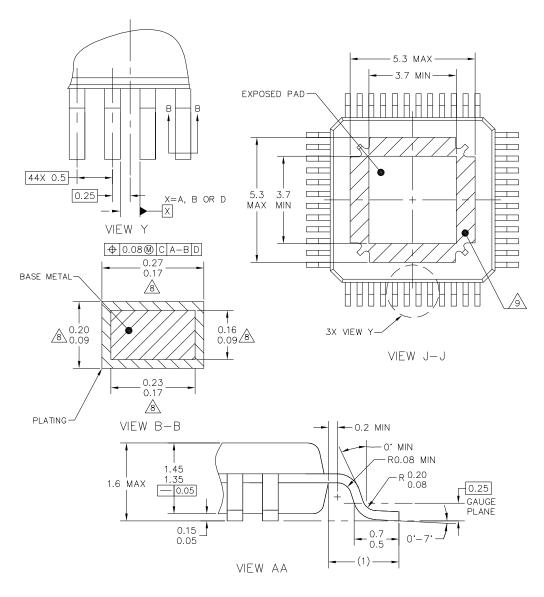

**AE SUFFIX (PB-FREE)** 98ASA00173D **48-PIN LQFP-EP**

#### **Applications**

- Electrical power steering

- Engine management

- Battery management

- Active suspension

- Gear box

- Transmission

- Electrical vehicle (EV), hybrid electrical vehicle (HEV), and inverter

- Advanced driver assistance systems

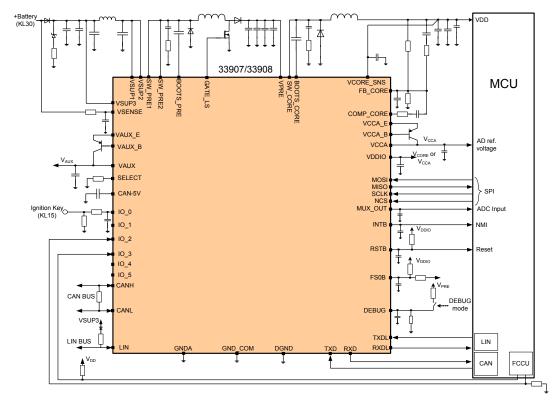

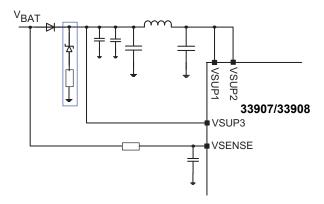

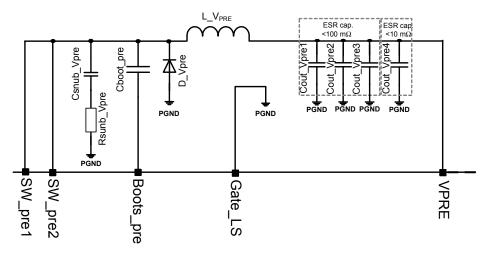

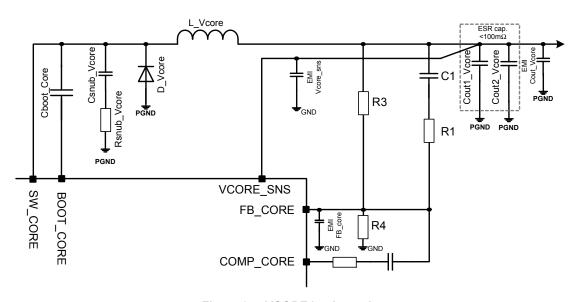

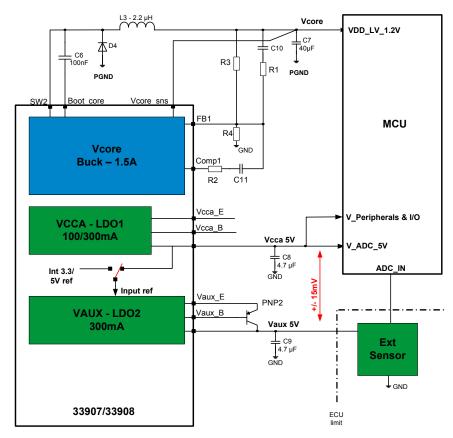

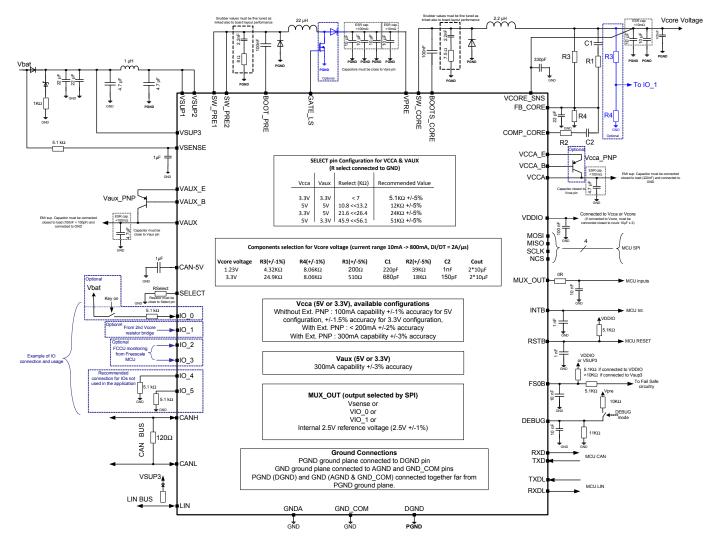

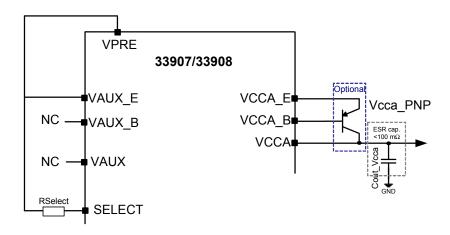

Figure 1. 33907/33908 simplified application diagram - buck boost configuration

This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

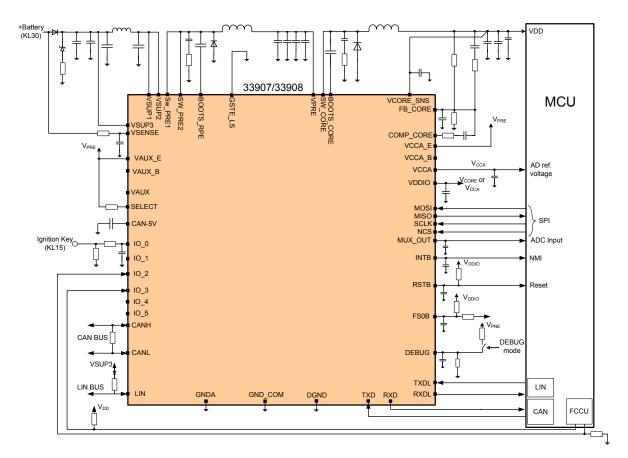

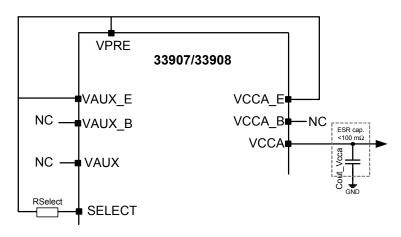

Figure 2. Simplified application diagram - buck configuration,  $V_{AUX}$  not used,  $V_{CCA}$  = 100 mA

# 1 Orderable parts

Table 1. Orderable part variations

| Part number | Temperature (T <sub>A</sub> ) | Package                   | CAN | LIN | V <sub>CORE</sub> | Notes |

|-------------|-------------------------------|---------------------------|-----|-----|-------------------|-------|

| MC33907NAE  | -40 to 125 °C                 | 48-pin LQFP exposed pad   | 1   | 0   | 0.8 A             |       |

| MC33908NAE  |                               |                           |     | 0   | 1.5 A             | (1)   |

| MC33907LAE  |                               | 40-piii EQi F exposed pad | I   | 1   | 0.8 A             | (1)   |

| MC33908LAE  |                               |                           |     | 1   | 1.5 A             |       |

### Notes

<sup>1.</sup> To order parts in Tape & Reel, add the R2 suffix to the part number.

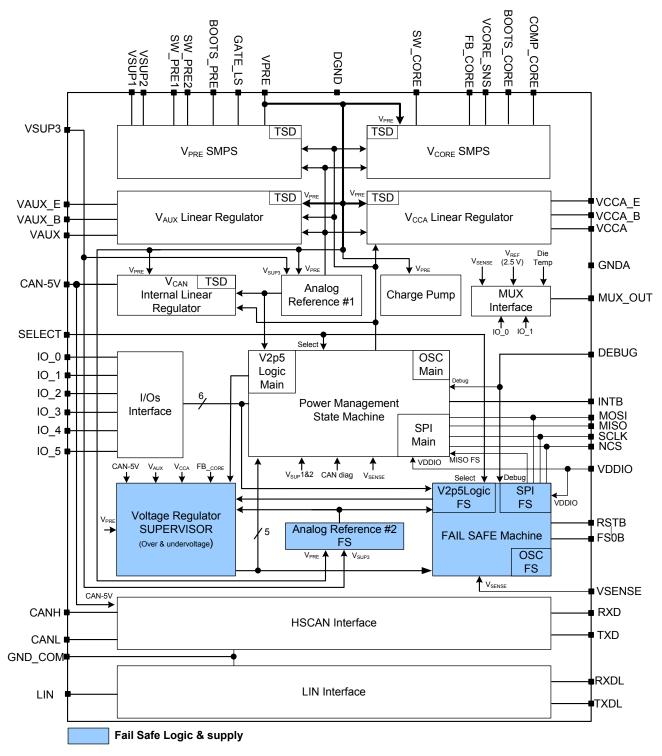

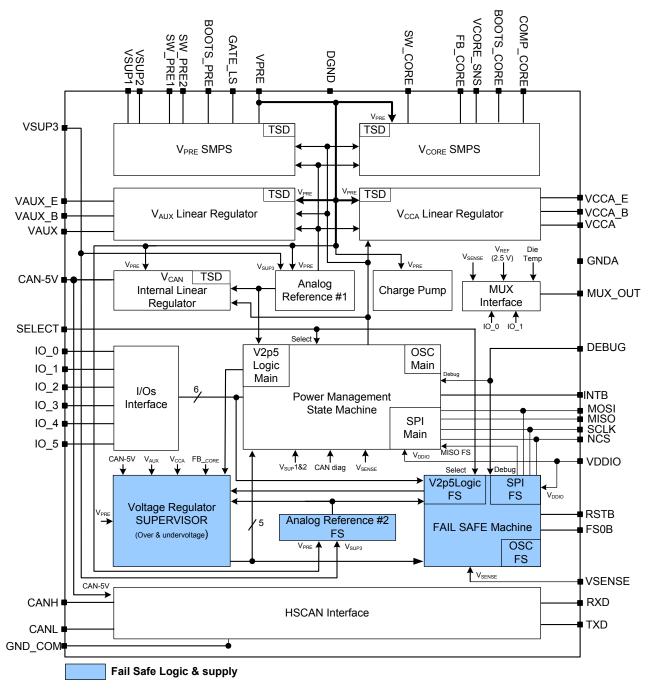

## 2 Internal Block Diagram

Figure 3. 33907L/33908L with CAN and LIN simplified internal block diagram

Figure 4. 33907N/33908N with CAN only simplified internal block diagram

## 3 Pin connections

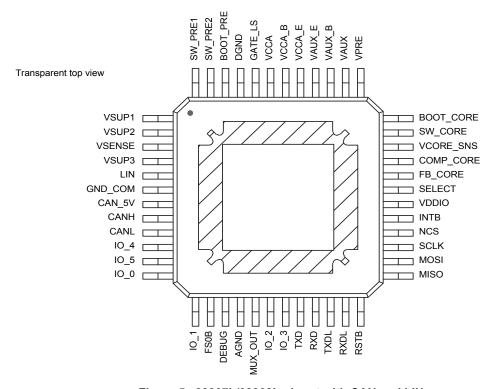

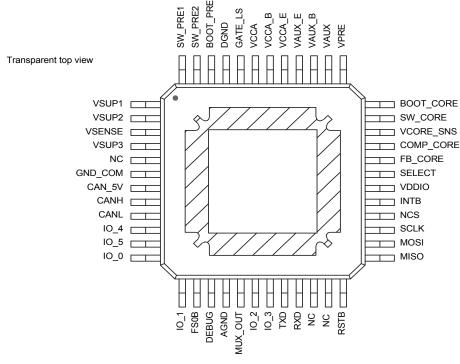

## 3.1 Pinout diagram for 33907/33908

Figure 5. 33907L/33908L pinout with CAN and LIN

Figure 6. 33907N/33908N pinout with CAN only

## 3.2 Pin definitions

A functional description of each pin can be found in the functional pin description section beginning on page 26.

Table 2. 33907/33908 pin definition

| 33907L/<br>33908L<br>pin number | 33907N/<br>33908N<br>pin number | Pin name | Туре          | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|---------------------------------|----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                               | 1                               | VSUP1    | A_IN          | Power supply of the device. An external reverse battery protection diode in series is mandatory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2                               | 2                               | VSUP2    | A_IN          | Second power supply. Protected by the external reverse battery protection diode used for VSUP1. VSUP1 and VSUP2 must be connected together externally.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3                               | 3                               | VSENSE   | A_IN          | Sensing of the battery voltage. Must be connected prior to the reverse battery protection diode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4                               | 4                               | VSUP3    | A_IN          | Third power supply dedicated to the device supply. Protected by the external reverse battery protection diode used for VSUP1. Must be connected between the reverse protection diode and the input PI filter.                                                                                                                                                                                                                                                                                                                                                                           |

| 5                               | NC                              | LIN      | A_IN/OUT      | LIN single-wire bus transmitter and receiver. NC: pin must be left open for 33907N/33908N version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6                               | 6                               | GND_COM  | GND           | Dedicated ground for CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7                               | 7                               | CAN_5V   | A_OUT         | Output voltage for the embedded CAN interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8                               | 8                               | CANH     | A_IN/OUT      | HSCAN output High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9                               | 9                               | CANL     | A_IN/OUT      | HSCAN output Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

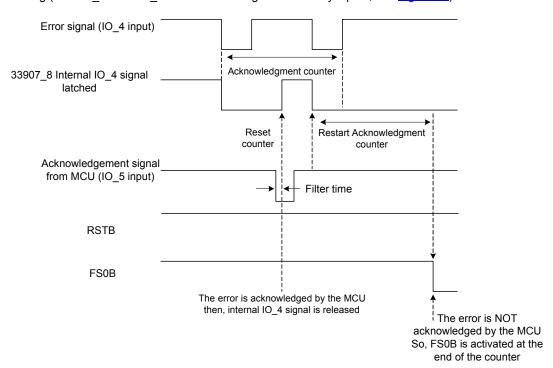

| 10<br>11                        | 10<br>11                        | IO_4:5   | D_IN<br>A_OUT | Can be used as digital input (load dump proof) with wake-up capability or as an output gate driver  Digital input: Pin status can be read through the SPI. Can be used to monitor error signals from another IC for safety purposes.  Wake-up capability: Can be selectable to wake-up on a rising or falling edge, or on a transition  Output gate driver: Can drive a logic level low-side NMOS transistor. Controlled by the SPI.                                                                                                                                                    |

| 12<br>13                        | 12<br>13                        | IO_0:1   | A_IN<br>D_IN  | Can be used as analog or digital input (load dump proof) with wake-up capability (selectable)  Analog input: Pin status can be read through the MUX output pin  Digital input: Pin status can be read through the SPI. Can be used to monitor error signals from another IC for safety purposes  Wake-up capability: Can be selectable to wake-up on a rising or falling edge, or on a transition  Rk: For safety purposes, IO_1 can also be used to monitor the middle point of a redundant resistor bridge connected on Vcore (in parallel to the one used to set the Vcore voltage). |

| 14                              | 14                              | FS0B     | D_OUT         | Output of the safety block (active low). The pin is asserted low at start-up and when a fault condition is detected. Open drain structure.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 15                              | 15                              | DEBUG    | D_IN          | Debug mode entry input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16                              | 16                              | AGND     | GROUND        | Analog ground connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17                              | 17                              | MUX_OUT  | A_OUT         | Multiplexed output to be connected to an MCU ADC input. Selection of the analog parameter is available at MUX-OUT through the SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 18<br>19                        | 18<br>19                        | IO_2:3   | D_IN          | Digital input pin with wake-up capability (logic level compatible)  Digital INPUT: Pin status can be read through the SPI. Can be used to monitor error signals from MCU for safety purposes.  Wake-up capability: Can be selectable to wake-up on a rising or falling edge, or on a transition.                                                                                                                                                                                                                                                                                        |

| 20                              | 20                              | TXD      | D_IN          | Transceiver input from the MCU which controls the state of the HSCAN bus. Internal pull-up to VDDIO. Internal pull-up to VDDIO.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21                              | 21                              | RXD      | D_OUT         | Receiver output which reports the state of the HSCAN bus to the MCU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22                              | NC                              | TXDL     | D_IN          | Transceiver input from the MCU which controls the state of the LIN bus. Internal pull-up to VDDIO. NC: pin must be left open for 33907N/33908N version                                                                                                                                                                                                                                                                                                                                                                                                                                  |

33907/33908

Table 2. 33907/33908 pin definition (continued)

| 33907L/<br>33908L<br>pin number | 33907N/<br>33908N<br>pin number | Pin name  | Туре     | Definition                                                                                                                                                                                                                     |

|---------------------------------|---------------------------------|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23                              | NC                              | RXDL      | D_OUT    | Receiver output which reports the state of the LIN bus to the MCU. NC: pin must be left open for 33907N/33908N version                                                                                                         |

| 24                              | 24                              | RSTB      | D_OUT    | This output is asserted low when the safety block reports a failure. The main function is to reset the MCU. Reset input voltage is also monitored in order to detect external reset and fault condition. Open drain structure. |

| 25                              | 25                              | MISO      | D_OUT    | SPI bus. Master Input Slave Output                                                                                                                                                                                             |

| 26                              | 26                              | MOSI      | D_IN     | SPI bus. Master Output Slave Input                                                                                                                                                                                             |

| 27                              | 27                              | SCLK      | D_IN     | SPI Bus. Serial clock                                                                                                                                                                                                          |

| 28                              | 28                              | NCS       | D_IN     | No Chip Select (Active low)                                                                                                                                                                                                    |

| 29                              | 29                              | INTB      | D_OUT    | This output pin generates a low pulse when an Interrupt condition occurs. Pulse duration is configurable. Internal pull-up to VDDIO.                                                                                           |

| 30                              | 30                              | VDDIO     | A_IN     | Input voltage for MISO output buffer. Allows voltage compatibility with MCU I/Os.                                                                                                                                              |

| 31                              | 31                              | SELECT    | D_IN     | Hardware selection pin for VAUX and VCCA output voltages                                                                                                                                                                       |

| 32                              | 32                              | FB_CORE   | A_IN     | VCORE voltage feedback. Input of the error amplifier.                                                                                                                                                                          |

| 33                              | 33                              | COMP_CORE | A_IN     | Compensation network. Output of the error amplifier.                                                                                                                                                                           |

| 34                              | 34                              | VCORE_SNS | A_IN     | VCORE output voltage sense                                                                                                                                                                                                     |

| 35                              | 35                              | SW_CORE   | A_IN     | VCORE switching point                                                                                                                                                                                                          |

| 36                              | 36                              | BOOT_CORE | A_IN/OUT | Bootstrap capacitor for VCORE internal NMOS gate drive                                                                                                                                                                         |

| 37                              | 37                              | VPRE      | A_OUT    | VPRE output voltage                                                                                                                                                                                                            |

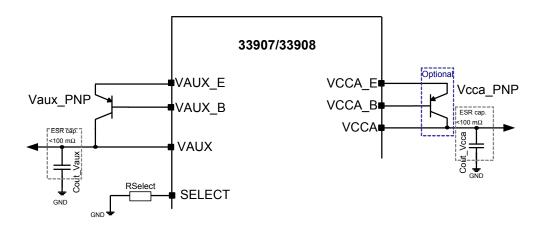

| 38                              | 38                              | VAUX      | A_OUT    | VAUX output voltage. External PNP ballast transistor. Collector connection                                                                                                                                                     |

| 39                              | 39                              | VAUX_B    | A_OUT    | VAUX voltage regulator. External PNP ballast transistor. Base connection                                                                                                                                                       |

| 40                              | 40                              | VAUX_E    | A_OUT    | VAUX voltage regulator. External PNP ballast transistor. Emitter connection                                                                                                                                                    |

| 41                              | 41                              | VCCA_E    | A_OUT    | VCCA voltage regulator. External PNP ballast transistor. Emitter connection                                                                                                                                                    |

| 42                              | 42                              | VCCA_B    | A_OUT    | VCCA voltage regulator. External PNP ballast transistor. Base connection                                                                                                                                                       |

| 43                              | 43                              | VCCA      | A_OUT    | VCCA output voltage. External PNP ballast transistor. Collector connection                                                                                                                                                     |

| 44                              | 44                              | GATE_LS   | A_OUT    | Low-side MOSFET gate drive for "Non-inverting Buck-boost" configuration                                                                                                                                                        |

| 45                              | 45                              | DGND      | GROUND   | Digital ground connection                                                                                                                                                                                                      |

| 46                              | 46                              | BOOT_PRE  | A_IN/OUT | Bootstrap capacitor for the VPRE internal NMOS gate drive                                                                                                                                                                      |

| 47                              | 47                              | SW_PRE2   | A_IN     | Second pre-regulator switching point                                                                                                                                                                                           |

| 48                              | 48                              | SW_PRE1   | A_IN     | First pre-regulator switching point                                                                                                                                                                                            |

# 4 General product characteristics

## 4.1 Maximum ratings

Table 3. Maximum ratings

All voltages are with respect to ground, unless otherwise specified. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                     | Ratings                                                                                    | Value                          | Unit | Notes |

|----------------------------|--------------------------------------------------------------------------------------------|--------------------------------|------|-------|

| Electrical ratings         | •                                                                                          |                                |      | •     |

| V <sub>SUP1/2/3</sub>      | DC Voltage at Power Supply Pins                                                            | -1.0 to 40                     | V    | (2)   |

| V <sub>SENSE</sub>         | DC Voltage at Battery Sense Pin                                                            | -14 to 40                      | V    |       |

| V <sub>SW1,2</sub>         | DC Voltage at SW_PRE1 and SW_PRE2 Pins                                                     | -1.0 to 40                     | V    |       |

| $V_{PRE}$                  | DC Voltage at VPRE Pin                                                                     | -0.3 to 8                      | V    |       |

| V <sub>GATE_LS</sub>       | DC Voltage at Gate_LS pin                                                                  | -0.3 to 8                      | V    |       |

| V <sub>BOOT_PRE</sub>      | DC Voltage at BOOT_PRE pin                                                                 | -1.0 to 50                     | V    |       |

| V <sub>SW_CORE</sub>       | DC Voltage at SW_CORE pin                                                                  | -1.0 to 8.0                    | V    |       |

| V <sub>CORE_SNS</sub>      | DC Voltage at VCORE_SNS pin                                                                | 0.0 to 8.0                     | V    |       |

| V <sub>BOOT_CORE</sub>     | DC Voltage at BOOT_CORE pin                                                                | 0.0 to 15                      | V    |       |

| V <sub>FB_CORE</sub>       | DC Voltage at FB_CORE pin                                                                  | -0.3 to 2.5                    | V    |       |

| V <sub>COMP_CORE</sub>     | DC Voltage at COMP_CORE pin                                                                | -0.3 to 2.5                    | V    |       |

| $V_{AUX\_E,B}$             | DC Voltage at VAUX_E, VAUX_B pin                                                           | -0.3 to 40                     | V    |       |

| V <sub>AUX</sub>           | DC Voltage at VAUX pin                                                                     | -2.0 to 40                     | V    |       |

| V <sub>CCA_B,E</sub>       | DC Voltage at VCCA_B, VCCA_E pin                                                           | -0.3 to 8.0                    | V    |       |

| $V_{CCA}$                  | DC Voltage at VCCA pin                                                                     | -0.3 to 8.0                    | V    |       |

| $V_{\rm DDIO}$             | DC Voltage at VDDIO                                                                        | -0.3 to 8.0                    | V    |       |

| V <sub>FS0</sub>           | DC Voltage at FS0B (with ext R mandatory)                                                  | -0.3 to 40                     | V    |       |

| V <sub>DEBUG</sub>         | DC Voltage at DEBUG                                                                        | -0.3 to 40                     | V    |       |

| V <sub>IO_0,1,4,5</sub>    | DC Voltage at IO_0:1; 4:5 (with ext R = 5.1 kΩ in series mandatory)                        | -0.3 to 40                     | V    |       |

| V <sub>DIG</sub>           | DC Voltage at INTB, RSTB, MISO, MOSI, NCS, SCLK, MUX_OUT, RXD, TXD, RXDL, TXDL, IO_2, IO_3 | -0.3 to V <sub>DDIO</sub> +0.3 | V    |       |

| V <sub>SELECT</sub>        | DC Voltage at SELECT                                                                       | -0.3 to 8.0                    | V    |       |

| V <sub>BUS_CAN</sub>       | DC Voltage on CANL, CANH                                                                   | -27 to 40                      | V    |       |

| V <sub>BUS_LIN</sub>       | DC Voltage on LIN                                                                          | -18 to 40V                     | V    |       |

| V <sub>CAN_5V</sub>        | DC Voltage on CAN_5 V                                                                      | -0.3 to 8.0                    | V    |       |

| I_IO <sub>0, 1, 4, 5</sub> | IOs Maximum Current Capability(IO_0, IO_1, IO_4, IO_5)                                     | -5.0 to 5.0                    | mA   |       |

Notes

<sup>2.</sup> All Vsups (V<sub>SUP1/2/3</sub>) shall be connected to the same supply (<u>Figure 58</u>)

### Table 3. Maximum ratings (continued)

All voltages are with respect to ground, unless otherwise specified. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                 | Ratings                                                                        | Value | Unit | Notes |

|------------------------|--------------------------------------------------------------------------------|-------|------|-------|

|                        | ESD Voltage                                                                    |       |      |       |

|                        | Human Body Model (JESD22/A114) - 100 pF, 1.5 kΩ                                |       |      |       |

| V <sub>ESD-HBM1</sub>  | All pins                                                                       | ±2.0  | kV   |       |

| $V_{ESD-HBM2}$         | VSUP1,VSUP2, VSUP3, VSENSE, VAUX, IO_0:1, IO_4:5,FS0B, DEBUG                   | ±4.0  | kV   |       |

| $V_{ESD-HBM3}$         | • CANH, CANL                                                                   | ±6.0  | kV   |       |

| $V_{ESD-HBM4}$         | • LIN                                                                          | ±8.0  | kV   |       |

|                        | Charge Device Model (JESD22/C101):                                             |       |      |       |

| V <sub>ESD-CDM1</sub>  | All Pins                                                                       | ±500  | V    |       |

| $V_{ESD-CDM2}$         | Corner Pins                                                                    | ±750  | V    |       |

|                        | System level ESD (Gun Test)                                                    |       |      |       |

|                        | <ul> <li>VSUP1, VSUP2, VSUP3, VSENSE, VAUX, IO_0:1, IO_4:5, FS0B</li> </ul>    |       |      |       |

| V <sub>ESD-GUN1</sub>  | 330 $\Omega$ / 150 pF Unpowered According to IEC61000-4-2:                     | ±8.0  | kV   |       |

| V <sub>ESD-GUN2</sub>  | 330 $\Omega$ / 150 pF Unpowered According to OEM LIN, CAN, FLexray Conformance | ±8.0  | kV   | (3)   |

| V <sub>ESD-GUN3</sub>  | 2.0 kΩ / 150 pF Unpowered According to ISO10605.2008                           | ±8.0  | kV   |       |

| $V_{ESD-GUN4}$         | 2.0 kΩ / 330 pF Powered According to ISO10605.2008                             | ±8.0  | kV   |       |

|                        | • CANH, CANL                                                                   |       |      |       |

| V <sub>ESD-GUN5</sub>  | 330 $\Omega$ / 150 pF Unpowered According to IEC61000-4-2:                     | ±15.0 | kV   |       |

| V <sub>ESD-GUN6</sub>  | 330 $\Omega$ / 150 pF Unpowered According to OEM LIN, CAN, FLexray Conformance | ±12.0 | kV   |       |

| V <sub>ESD-GUN7</sub>  | 2.0 kΩ / 150 pF Unpowered According to ISO10605.2008                           | ±15.0 | kV   |       |

| $V_{ESD-GUN8}$         | 2.0 kΩ / 330 pF Powered According to ISO10605.2008                             | ±15.0 | kV   |       |

|                        | • LIN                                                                          |       |      |       |

| V <sub>ESD-GUN9</sub>  | 330 Ω / 150 pF Unpowered According to IEC61000-4-2:                            | ±15.0 | kV   |       |

| V <sub>ESD-GUN10</sub> | 330 $\Omega$ / 150 pF Unpowered According to OEM LIN, CAN, FLexray Conformance | ±15.0 | kV   |       |

| V <sub>ESD-GUN11</sub> | 2.0 kΩ / 150 pF Unpowered According to ISO10605.2008                           | ±12.0 | kV   |       |

| V <sub>ESD-GUN12</sub> | 2.0 kΩ / 330 pF Powered According to ISO10605.2008                             | ±15.0 | kV   |       |

### Thermal ratings

| T <sub>A</sub>   | Ambient Temperature  | -40 to 125 | °C |  |

|------------------|----------------------|------------|----|--|

| TJ               | Junction Temperature | -40 to 150 | °C |  |

| T <sub>STG</sub> | Storage Temperature  | -55 to 150 | °C |  |

### Thermal resistance

| $R_{\theta JA}$         | Thermal Resistance Junction to Ambient     | 30   | °C/W | (4) |

|-------------------------|--------------------------------------------|------|------|-----|

| $R_{\theta JCTOP}$      | Thermal Resistance Junction to Case Top    | 24.2 | °C/W | (5) |

| R <sub>0</sub> JCBOTTOM | Thermal Resistance Junction to Case Bottom | 0.9  | °C/W | (6) |

#### Notes

- 3. Compared to AGND.

- 4. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC 883 Method 1012.1).

- 6. Thermal resistance between the die and the solder par on the bottom of the packaged based on simulation without any interface resistance.

## 4.2 Static electrical characteristics

Table 4. Operating range

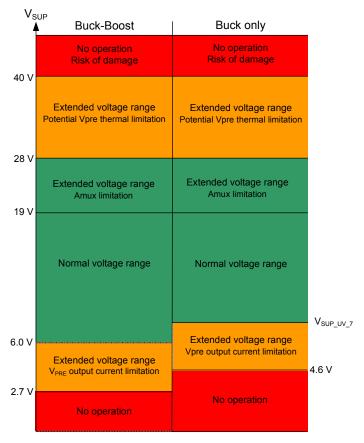

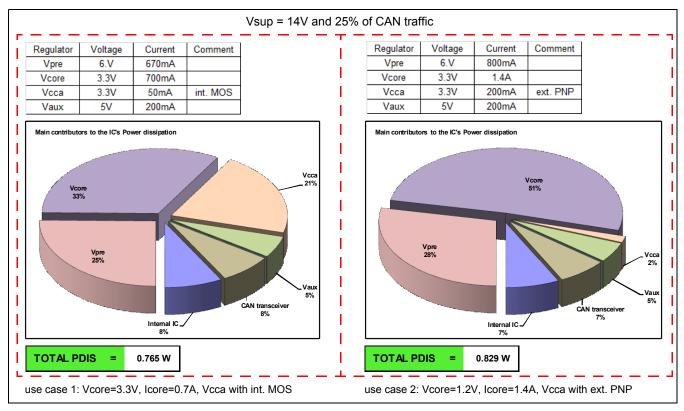

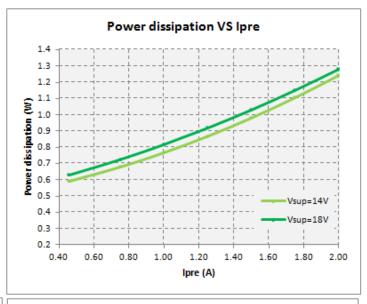

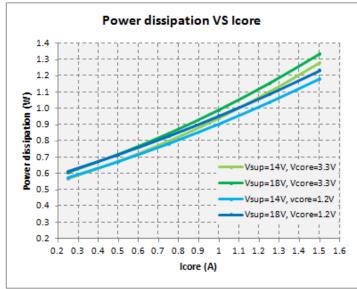

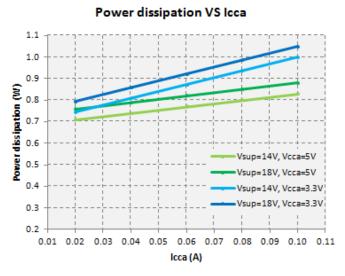

$T_{CASE}$  = -40 °C to 125 °C, unless otherwise specified.  $V_{SUP}$  =  $V_{SUP\_UV\_L}$  to 40 V, unless otherwise specified. All voltages referenced to ground. When 28 V <  $V_{SUP}$  < 40 V, thermal dissipation must be considered (<u>Figure 25)</u>.

| Symbol                        | Parameter                                                                                 | Min. | Тур. | Max.     | Unit | Notes |

|-------------------------------|-------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| Power supply                  |                                                                                           |      |      | ll.      | 1    |       |

| I <sub>SUP123</sub>           | Power Supply Current in Normal Mode (V <sub>SUP</sub> > V <sub>SUP_UV_7</sub> )           | 2.0  | _    | 13.0     | mA   |       |

| I <sub>SUP3</sub>             | Power Supply Current for VSUP3 in Normal Mode (V <sub>SUP</sub> > V <sub>SUP_UV_7</sub> ) | -    | 3.5  | 5.0      | mA   |       |

| I <sub>SUP_LPOFF1</sub>       | Power Supply Current in LPOFF (V <sub>SUP</sub> = 14 V at T <sub>A</sub> = 25 °C)         | -    | 32   | -        | μA   |       |

| I <sub>SUP_LPOFF2</sub>       | Power Supply Current in LPOFF (V <sub>SUP</sub> = 18 V at T <sub>A</sub> = 80 °C)         | -    | 42   | 60       | μA   |       |

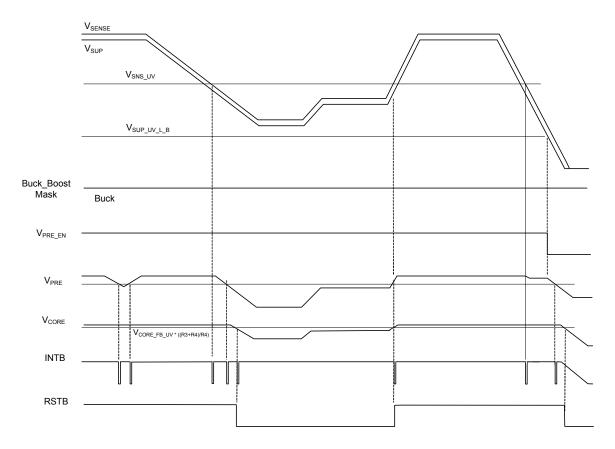

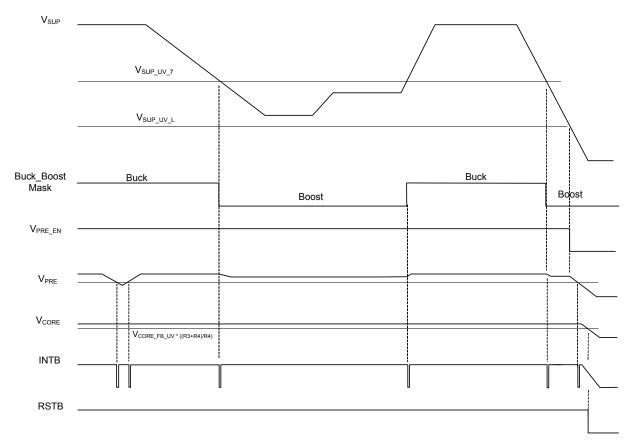

| V <sub>SNS_UV</sub>           | Power Supply Undervoltage Warning                                                         | -    | 8.5  | -        | V    |       |

| V <sub>SNS_UV_HYST</sub>      | Power Supply Undervoltage Warning Hysteresis                                              | 0.1  | -    | -        | V    |       |

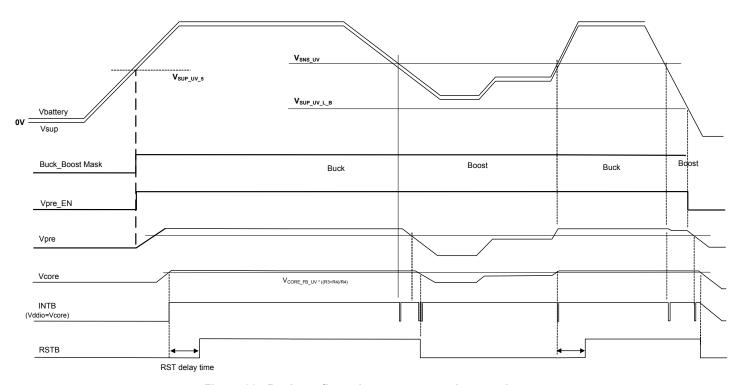

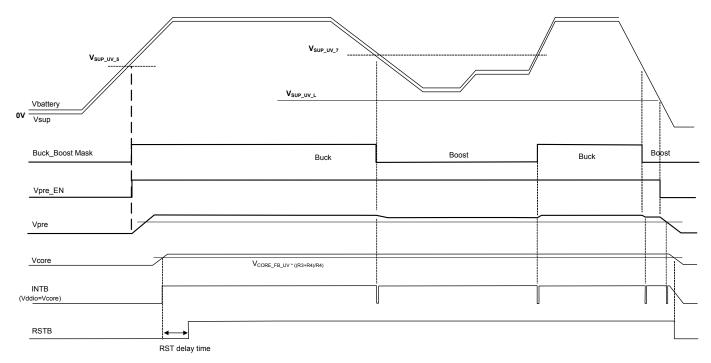

| V <sub>SUP_UV_7</sub>         | Power Supply Undervoltage Lockout (power-up)                                              | 7.0  | -    | 8.0      | V    |       |

| V <sub>SUP_UV_5</sub>         | Power Supply Undervoltage Lockout (power-up)                                              | _    | -    | 5.6      | V    |       |

| V <sub>SUP_UV_L</sub>         | Power Supply Undervoltage Lockout (falling - Boost config.)                               | _    | -    | 2.7      | V    |       |

| V <sub>SUP_UV_L_B</sub>       | Power Supply Undervoltage Lockout (falling - Buck config.)                                | -    | _    | 4.6      | V    | (7)   |

| V <sub>SUP_UV_HYST</sub>      | Power Supply Undervoltage Lockout Hysteresis                                              | -    | 0.1  | -        | V    | (8)   |

| V <sub>PRE</sub> voltage pre- | regulator                                                                                 |      | •    | <u>'</u> |      | •     |

| V <sub>PRE</sub>       | $\begin{aligned} & V_{PRE} \text{ Output Voltage} \\ & \bullet \text{ Buck mode } (V_{SUP} > V_{SUP\_UV\_7}) \\ & \bullet \text{ Buck mode } (V_{SUP\_UV\_7} \ge V_{SUP} \ge 4.6 \text{ V}) \end{aligned}$                                                                                                                                                                                                                                                                     | 6.25<br>V <sub>PRE_UV_4</sub><br>P3 | -<br>V <sub>SUP</sub> -<br>R <sub>DSON_PR</sub><br>E* I <sub>PRE</sub> | 6.75<br>-        | V |     |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------|------------------|---|-----|

|                        | <ul> <li>Boost mode (V<sub>SUP</sub> ≥ 2.7 V)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                       | 6.0                                 | _                                                                      | 7.0              |   |     |

| I <sub>PRE</sub>       | $\begin{split} & V_{PRE} \text{ Maximum Output Current Capability} \\ & \bullet \text{ Buck or Boost with } V_{SUP} > V_{SUP\_UV\_7} \\ & \bullet \text{ Buck with } V_{SUP\_UV\_7} \geq V_{SUP} \geq 4.6 \text{ V} \\ & \bullet \text{ Boost with } V_{SUP\_UV\_7} \geq V_{SUP} \geq 6.0 \text{ V} \\ & \bullet \text{ Boost with } 6.0 \text{ V} \geq V_{SUP} \geq 4.0 \text{ V} \\ & \bullet \text{ Boost with } 4.0 \text{ V} \geq V_{SUP} \geq 2.7 \text{ V} \end{split}$ | 2.0<br>0.5<br>2.0<br>1.0<br>0.3     | _<br>2.0<br>_<br>_<br>_                                                | -<br>-<br>-<br>- | А | (8) |

| I <sub>PRE_LPOFF</sub> | $\begin{split} &V_{PRE} \text{ Maximum Output Current Capability in LPOFF at low V}_{SUP} \\ &\text{voltage} \\ &\bullet \text{ Buck with V}_{SUP\_UV\_7} \geq V_{SUP} \geq 4.6 \text{ V} \\ &\bullet \text{ Boost with V}_{SUP\_UV\_7} \geq V_{SUP} \geq 6.0 \text{ V} \\ &\bullet \text{ Boost with } 6.0 \text{ V} \geq V_{SUP} \geq 4.0 \text{ V} \\ &\bullet \text{ Boost with } 4.0 \text{ V} \geq V_{SUP} \geq 2.7 \text{ V} \end{split}$                               | 0.05<br>2.0<br>1.0<br>0.3           | 1111                                                                   | -<br>-<br>-      | А | (8) |

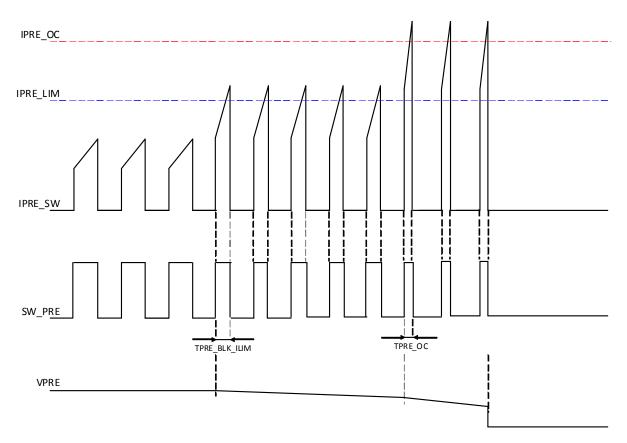

| I <sub>PRE_LIM</sub>   | $V_{PRE}$ Output Current Limitation with $V_{SUP} \le 28 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                            | 3.5                                 | _                                                                      | 1                | Α |     |

| I <sub>PRE_OC</sub>    | $V_{\mbox{\footnotesize{PRE}}}$ Overcurrent Detection Threshold (in buck mode only) with $V_{\mbox{\footnotesize{SUP}}} \leq 28~V$                                                                                                                                                                                                                                                                                                                                             | 5.0                                 | _                                                                      | _                | Α |     |

| V <sub>PRE_UV</sub>    | V <sub>PRE</sub> Undervoltage Detection Threshold (Falling)                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.5                                 | _                                                                      | 6.0              | V |     |

### Notes

- 7.  $V_{SUP\_UV\_L\_B} = V_{PRE\_UV\_4P3} + R_{DSON\_PRE} * I_{PRE}$

- 8. Guaranteed by design

33907/33908

$T_{CASE}$  = -40 °C to 125 °C, unless otherwise specified.  $V_{SUP}$  =  $V_{SUP\_UV\_L}$  to 40 V, unless otherwise specified. All voltages referenced to ground. When 28 V <  $V_{SUP}$  < 40 V, thermal dissipation must be considered (<u>Figure 25)</u>.

| Symbol                                         | Parameter                                                                                                         | Min.                 | Тур.             | Max.                     | Unit | Notes |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|------------------|--------------------------|------|-------|

| V <sub>PRE</sub> voltage pre-                  | regulator (continued)                                                                                             | "                    | I .              | 1                        | 1    |       |

| V <sub>PRE_UV_HYST</sub>                       | V <sub>PRE</sub> Undervoltage Hysteresis                                                                          | 0.05                 | _                | 0.15                     | V    | (9)   |

| V <sub>PRE_UV_4P3</sub>                        | V <sub>PRE</sub> Shut-off Threshold (Falling - buck and buck/boost)                                               | 4.2                  | _                | 4.5                      | V    |       |

| V <sub>PRE_UV_4P3_</sub><br>HYST               | V <sub>PRE</sub> Shut-off Hysteresis                                                                              | 0.05                 | -                | 0.15                     | V    | (9)   |

| R <sub>DSON_PRE</sub>                          | V <sub>PRE</sub> Pass Transistor On Resistance with V <sub>SUP</sub> ≤ 28 V                                       | _                    | -                | 200                      | mΩ   |       |

| L <sub>IR_VPRE</sub>                           | V <sub>PRE</sub> Line Regulation                                                                                  | _                    | 20               | -                        | mV   | (9)   |

| LOR <sub>VPRE_BUCK</sub>                       | V <sub>PRE</sub> Load Regulation for C <sub>OUT</sub> = 57 μF • I <sub>PRE</sub> from 50 mA to 2.0 A - Buck mode  | _                    | 100              | -                        | mV   | (9)   |

| LOR <sub>VPRE_BOOST</sub>                      | V <sub>PRE</sub> Load Regulation for C <sub>OUT</sub> = 57 μF • I <sub>PRE</sub> from 50 mA to 2.0 A - Boost mode | -                    | 500              | -                        | mV   | (9)   |

| V <sub>PRE_LL_H</sub><br>V <sub>PRE_LL_L</sub> | V <sub>PRE</sub> Pulse Skipping Thresholds                                                                        | _<br>_               | 200<br>180       | -<br>-                   | mV   |       |

| T <sub>WARN_PRE</sub>                          | V <sub>PRE</sub> Thermal Warning Threshold                                                                        | _                    | 125              | -                        | °C   |       |

| T <sub>SD_PRE</sub>                            | V <sub>PRE</sub> Thermal Shutdown Threshold                                                                       | 160                  | _                | -                        | °C   |       |

| T <sub>SD_PRE_HYST</sub>                       | V <sub>PRE</sub> Thermal Shutdown Hysteresis                                                                      | _                    | 10               | -                        | °C   | (9)   |

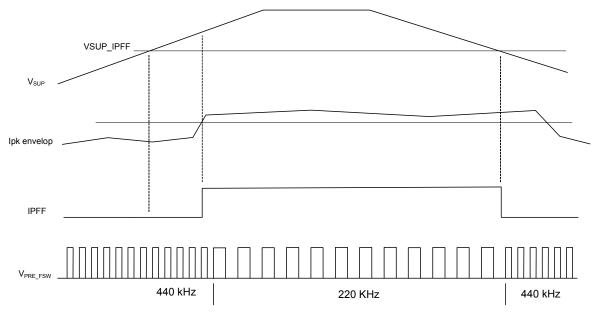

| V <sub>SUP_IPFF</sub>                          | I <sub>PFF</sub> Input Voltage Detection                                                                          | 18                   | -                | 24                       | V    |       |

| V <sub>SUP_IPFF_HYST</sub>                     | I <sub>PFF</sub> Input Voltage Hysteresis                                                                         | 0.2                  | _                | _                        | V    |       |

| I <sub>PRE_IPFF_PK</sub>                       | $I_{PFF}$ High-side Peak Current Detection with $V_{SUP} \le 28 \text{ V}$                                        | 1.7                  | _                | _                        | Α    |       |

| $V_{G_LS_OH}$                                  | LS Gate Driver High Output Voltage (I <sub>OUT</sub> = 50 mA)                                                     | V <sub>PRE</sub> -1  | _                | V <sub>PRE</sub>         | V    |       |

| $V_{G_LS_OL}$                                  | LS Gate driver Low Level (I <sub>OUT</sub> = 50 mA)                                                               | _                    | _                | 0.5                      | V    |       |

| V <sub>core</sub> voltage regu                 | ılator                                                                                                            | •                    |                  |                          |      |       |

| V <sub>CORE_FB</sub>                           | V <sub>CORE</sub> Feedback Input Voltage                                                                          | 0.784                | 0.8              | 0.816                    | V    |       |

| Icore                                          | V <sub>CORE</sub> Output Current Capability in Normal Mode                                                        | -<br>-<br>-<br>-     | -<br>-<br>-<br>- | 0.8<br>1.5<br>0.8<br>1.5 | А    |       |

| I <sub>CORE</sub> LIM                          | V <sub>CORE</sub> Output Current Limitation                                                                       | 1<br>1.8<br>1<br>1.8 | -<br>-<br>-<br>- | 2<br>3.5<br>2<br>3.5     | А    |       |

| R <sub>DSON_CORE</sub>                         | V <sub>CORE</sub> Pass Transistor On Resistance                                                                   | _                    | _                | 200                      | mΩ   |       |

### Notes

9. Guaranteed by design

$T_{CASE}$  = -40 °C to 125 °C, unless otherwise specified.  $V_{SUP}$  =  $V_{SUP\_UV\_L}$  to 40 V, unless otherwise specified. All voltages referenced to ground. When 28 V <  $V_{SUP}$  < 40 V, thermal dissipation must be considered (<u>Figure 25)</u>.

| Symbol                                               | Parameter                                                                                                                                                   | Min.                                            | Тур.                                   | Max.                                            | Unit | Notes      |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------|-------------------------------------------------|------|------------|

| V <sub>core</sub> voltage regu                       | ılator (continued)                                                                                                                                          |                                                 |                                        |                                                 |      |            |

| LOR <sub>VCORE_1.2</sub>                             | V <sub>CORE</sub> Transient Load regulation - 1.2 V range                                                                                                   | -60                                             | -                                      | 60                                              | mV   | (10), (11) |

| LOR <sub>VCORE_3.3</sub>                             | V <sub>CORE</sub> Transient Load regulation - 3.3 V range                                                                                                   | -100                                            | -                                      | 100                                             | mV   | (10), (11) |

| V <sub>CORE_LL_H</sub><br>V <sub>CORE_LL_L</sub>     | V <sub>CORE</sub> Pulse Skipping Thresholds                                                                                                                 |                                                 | 180<br>160                             | _<br>_                                          | mV   |            |

| T <sub>WARN_CORE</sub>                               | V <sub>CORE</sub> Thermal Warning Threshold                                                                                                                 | _                                               | 125                                    | -                                               | °C   |            |

| T <sub>SD_CORE</sub>                                 | V <sub>CORE</sub> Thermal Shutdown Threshold                                                                                                                | 160                                             | _                                      | -                                               | °C   |            |

| T <sub>SD_CORE_HYST</sub>                            | V <sub>CORE</sub> Thermal Shutdown Hysteresis                                                                                                               | _                                               | 10                                     | -                                               | °C   | (10)       |

| V <sub>CCA</sub> voltage regu                        | ılator                                                                                                                                                      | •                                               |                                        | 1                                               |      | •          |

| Vcca                                                 | V <sub>CCA</sub> Output Voltage                                                                                                                             | 4.95<br>4.9<br>4.85<br>3.2505<br>3.234<br>3.201 | 5.0<br>5.0<br>5.0<br>3.3<br>3.3<br>3.3 | 5.05<br>5.1<br>5.15<br>3.3495<br>3.366<br>3.399 | V    | (12)       |

| I <sub>CCA_IN</sub>                                  | V <sub>CCA</sub> Output Current (int. MOSFET)                                                                                                               | _                                               | -                                      | 100                                             | mA   |            |

| I <sub>CCA_OUT</sub>                                 | V <sub>CCA</sub> Output Current (external PNP)                                                                                                              | -                                               | _                                      | 300                                             | mA   |            |

| I <sub>CCA_LIM_INT</sub>                             | V <sub>CCA</sub> Output Current Limitation (int. MOSFET)                                                                                                    | 100                                             | _                                      | 675                                             | mA   |            |

| ICCA_LIM_OUT                                         | V <sub>CCA</sub> Output Current Limitation (external PNP)                                                                                                   | 300                                             | -                                      | 675                                             | mA   |            |

| I <sub>CCA_LIM_FB</sub>                              | V <sub>CCA</sub> Output Current Limitation Foldback                                                                                                         | 80                                              | _                                      | 200                                             | mA   |            |

| V <sub>CCA_LIM_FB</sub>                              | V <sub>CCA</sub> Output Voltage Foldback Threshold                                                                                                          | 0.5                                             | _                                      | 1.1                                             | V    |            |

| V <sub>CCA_LIM_HYST</sub>                            | V <sub>CCA</sub> Output Voltage Foldback Hysteresis                                                                                                         | 0.03                                            | _                                      | 0.3                                             | V    |            |

| I <sub>CCA_BASE_SC</sub><br>I <sub>CCA_BASE_SK</sub> | V <sub>CCA</sub> Base Current Capability                                                                                                                    | _<br>20                                         | -<br>-                                 | 30<br>-                                         | mA   |            |

| T <sub>WARN_CCA</sub>                                | V <sub>CCA</sub> Thermal Warning Threshold (int. MOSFET only)                                                                                               | _                                               | 125                                    | -                                               | °C   |            |

| TSD <sub>CCA</sub>                                   | V <sub>CCA</sub> Thermal Shutdown Threshold (int. MOSFET only)                                                                                              | 160                                             | -                                      | _                                               | °C   |            |

| TSD <sub>CCA_HYST</sub>                              | V <sub>CCA</sub> Thermal Shutdown Hysteresis                                                                                                                | _                                               | 10                                     | _                                               | °C   | (13)       |

| LORT <sub>VCCA</sub>                                 | V <sub>CCA</sub> Transient Load Regulation  • I <sub>CCA</sub> = 10 mA to 100 mA (internal MOSFET)  • I <sub>CCA</sub> = 10 mA to 300 mA (external ballast) | -                                               | -                                      | 1.0                                             | %    | (13)       |

#### Notes

- 10. Guaranteed by design.

- 11.  $C_{OUT}$  = 40  $\mu$ F,  $I_{CORE}$  = 10 mA to 1.5 A,  $dI_{CORE}/dt \leq$  2.0 A/ $\mu$ s

- 12. External PNP gain within 150 to 450

- Guaranteed by design.

33907/33908

$T_{CASE}$  = -40 °C to 125 °C, unless otherwise specified.  $V_{SUP}$  =  $V_{SUP\_UV\_L}$  to 40 V, unless otherwise specified. All voltages referenced to ground. When 28 V <  $V_{SUP}$  < 40 V, thermal dissipation must be considered (<u>Figure 25)</u>.

| Symbol                                            | Parameter                                                                                                                    | Min.     | Тур. | Max.      | Unit | Notes                                         |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------|------|-----------|------|-----------------------------------------------|

| Vaux voltage reg                                  | ulator                                                                                                                       | II.      |      | 1         |      |                                               |

| V <sub>AUX_5</sub>                                | V <sub>AUX</sub> Output Voltage (5.0 V configuration)                                                                        | 4.85     | 5.0  | 5.15      | V    |                                               |

| V <sub>AUX_33</sub>                               | V <sub>AUX</sub> Output Voltage (3.3 V configuration)                                                                        | 3.2      | 3.3  | 3.4       | V    |                                               |

| V <sub>AUX_TRK</sub>                              | V <sub>AUX</sub> Tracking Error (V <sub>AUX_5</sub> and V <sub>AUX_33</sub> )                                                | -15      | _    | +15       | mV   |                                               |

| I <sub>AUX_OUT</sub>                              | V <sub>AUX</sub> Output Current                                                                                              | -        | _    | 300       | mA   |                                               |

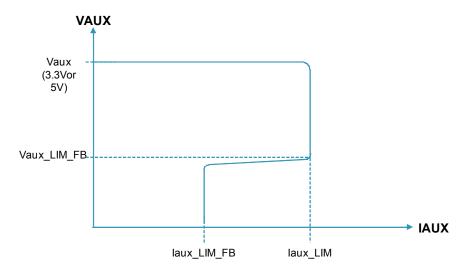

| I <sub>AUX_LIM</sub>                              | V <sub>AUX</sub> Output Current Limitation                                                                                   | 300      | _    | 700       | mA   |                                               |

| I <sub>AUX_LIM_FB</sub>                           | V <sub>AUX</sub> Output Current Limitation Foldback                                                                          | 100      | _    | 530       | mA   |                                               |

| V <sub>AUX_LIM_FB</sub>                           | V <sub>AUX</sub> Output Voltage Foldback Threshold                                                                           | 0.5      | _    | 1.1       | V    |                                               |

| V <sub>AUX_LIM_HYST</sub>                         | V <sub>AUX</sub> Output Voltage Foldback Hysteresis                                                                          | 0.03     | _    | 0.3       | V    |                                               |

| I <sub>AUX_BASE_SC</sub> I <sub>AUX_BASE_SK</sub> | V <sub>AUX</sub> Base Current Capability                                                                                     | -<br>7.0 | -    | -7.0<br>- | mA   |                                               |

| TSD <sub>AUX</sub>                                | V <sub>AUX</sub> Thermal Shutdown Threshold                                                                                  | 160      | _    | -         | °C   |                                               |

| TSD <sub>AUX_HYST</sub>                           | V <sub>AUX</sub> Thermal Shutdown Hysteresis                                                                                 | -        | 10   | -         | °C   | (14)                                          |

| LOR <sub>VAUX</sub>                               | V <sub>AUX</sub> Static Load Regulation (I <sub>AUX_OUT</sub> = 10 mA to 300 mA)                                             | -        | 15   | -         | mV   | (14)                                          |

| LORT <sub>VAUX</sub>                              | V <sub>AUX</sub> Transient Load Regulation • I <sub>AUX_OUT</sub> = 10 mA to 300 mA                                          | -        | -    | 1.0       | %    | (14)                                          |

| CAN_5V voltage                                    | regulator                                                                                                                    | <b>"</b> | •    |           | •    | <u>,                                     </u> |

| $V_{\sf CAN}$                                     | V <sub>CAN</sub> Output Voltage V <sub>SUP</sub> > 6.0 V in Buck mode V <sub>SUP</sub> > V <sub>SUP_UV_L</sub> in Boost mode | 4.8      | 5.0  | 5.2       | V    |                                               |

| I <sub>CAN_OUT</sub>                              | V <sub>CAN</sub> Output Current                                                                                              | -        | _    | 100       | mA   |                                               |

| I <sub>CAN_LIM</sub>                              | V <sub>CAN</sub> Output Current Limitation                                                                                   | 100      | _    | 250       | mA   |                                               |

| TSD <sub>CAN</sub>                                | V <sub>CAN</sub> Thermal Shutdown Threshold                                                                                  | 160      | _    | _         | °C   |                                               |

| TSD <sub>CAN_HYST</sub>                           | V <sub>CAN</sub> Thermal Shutdown Hysteresis                                                                                 | -        | 10   | _         | °C   | (14)                                          |

| V <sub>CAN_UV</sub>                               | V <sub>CAN</sub> Undervoltage Detection Threshold                                                                            | 4.25     | _    | 4.8       | V    |                                               |

| V <sub>CAN_UV_HYST</sub>                          | V <sub>CAN</sub> Undervoltage Hysteresis                                                                                     | 0.07     | _    | 0.22      | V    |                                               |

| V <sub>CAN_OV</sub>                               | V <sub>CAN</sub> Overvoltage Detection Threshold                                                                             | 5.2      | _    | 5.55      | V    |                                               |

| V <sub>CAN_OV_HYST</sub>                          | V <sub>CAN</sub> Overvoltage Hysteresis                                                                                      | 0.07     | _    | 0.22      | V    |                                               |

| LOR <sub>VCAN</sub>                               | V <sub>CAN</sub> Load Regulation (from 0 to 50 mA)                                                                           | -        | 100  | -         | mV   | (14)                                          |

Notes

<sup>14.</sup> Guaranteed by design.

$T_{CASE}$  = -40 °C to 125 °C, unless otherwise specified.  $V_{SUP}$  =  $V_{SUP\_UV\_L}$  to 40 V, unless otherwise specified. All voltages referenced to ground. When 28 V <  $V_{SUP}$  < 40 V, thermal dissipation must be considered (<u>Figure 25)</u>.

| Symbol                           | Parameter                                                                               | Min. | Тур. | Max.  | Unit | Notes |

|----------------------------------|-----------------------------------------------------------------------------------------|------|------|-------|------|-------|

| Fail-safe machine                | voltage supervisor                                                                      |      |      |       |      |       |

| V <sub>PRE_OV</sub>              | V <sub>PRE</sub> Overvoltage Detection Threshold                                        | 7.2  | _    | 8.0   | V    |       |

| V <sub>PRE_OV_HYST</sub>         | V <sub>PRE</sub> Overvoltage Hysteresis                                                 | -    | 0.1  | -     | V    | (15)  |

| V <sub>CORE_FB_UV</sub>          | V <sub>CORE</sub> FB Undervoltage Detection Threshold                                   | 0.67 | -    | 0.773 | V    |       |

| V <sub>CORE_FB_UV_D</sub>        | V <sub>CORE</sub> FB Undervoltage Detection Threshold - Degraded mode                   | 0.45 | _    | 0.58  | V    |       |

| V <sub>CORE_FB_UV_</sub><br>HYST | V <sub>CORE</sub> FB Undervoltage Hysteresis                                            | 10   | _    | 27    | mV   | (15)  |

| V <sub>CORE_FB_OV</sub>          | V <sub>CORE</sub> FB Overvoltage Detection Threshold                                    | 0.84 | _    | 0.905 | V    |       |

| V <sub>CORE_FB_OV_HYS</sub><br>T | V <sub>CORE</sub> FB Overvoltage Hysteresis                                             | 10   | _    | 30    | mV   | (15)  |

| V <sub>CORE_FB_DRIFT</sub>       | V <sub>CORE_FB</sub> Drift versus IO_1                                                  | 50   | 100  | 150   | mV   |       |

| I <sub>PD_CORE</sub>             | V <sub>CORE</sub> Internal Pull-down Current (active when V <sub>CORE</sub> is enabled) | 5.0  | 12   | 25    | mA   |       |

| V <sub>CCA_UV_5</sub>            | V <sub>CCA</sub> Undervoltage Detection Threshold (5.0 V config)                        | 4.5  | _    | 4.75  | V    |       |

| V <sub>CCA_UV_5D</sub>           | V <sub>CCA</sub> Undervoltage Detection Threshold (Degraded 5.0 V)                      | 3.0  | _    | 3.2   | V    |       |

| V <sub>CCA_UV_33</sub>           | V <sub>CCA</sub> Undervoltage Detection Threshold (3.3 V config)                        | 3.0  | _    | 3.2   | V    |       |

| V <sub>CCA_UV_HYST</sub>         | V <sub>CCA</sub> Undervoltage Hysteresis                                                | _    | 0.07 | -     | V    | (15)  |

| V <sub>CCA_OV_5</sub>            | V <sub>CCA</sub> Overvoltage Detection Threshold (5.0 V config)                         | 5.25 | _    | 5.5   | V    |       |

| V <sub>CCA_OV_33</sub>           | V <sub>CCA</sub> Overvoltage Detection Threshold (3.3 V config)                         | 3.4  | _    | 3.6   | V    |       |

| V <sub>CCA_OV_HYST</sub>         | V <sub>CCA</sub> Overvoltage Hysteresis                                                 | _    | 0.15 | -     | V    | (15)  |

| R <sub>PD_CCA</sub>              | V <sub>CCA</sub> Internal Pull-down Resistor (active when V <sub>CCA</sub> is disabled) | 50   | _    | 160   | Ω    |       |

| V <sub>AUX_UV_5</sub>            | V <sub>AUX</sub> Undervoltage Detection Threshold (5.0 V config)                        | 4.5  | _    | 4.75  | V    |       |

| V <sub>AUX_UV_5D</sub>           | V <sub>AUX</sub> Undervoltage Detection Threshold (Degraded 5.0 V)                      | 3.0  | _    | 3.2   | V    |       |

| V <sub>AUX_UV_33</sub>           | V <sub>AUX</sub> Undervoltage Detection Threshold (3.3 V config)                        | 3.0  | _    | 3.2   | V    |       |

| V <sub>AUX_UV_HYST</sub>         | V <sub>AUX</sub> Undervoltage Hysteresis                                                | _    | 0.07 | -     | V    | (15)  |

| V <sub>AUX_OV_5</sub>            | V <sub>AUX</sub> Overvoltage Detection Threshold (5.0 V config)                         | 5.25 | _    | 5.5   | V    |       |

| V <sub>AUX_OV_33</sub>           | V <sub>AUX</sub> Overvoltage Detection Threshold (3.3 V config)                         | 3.4  | _    | 3.6   | V    |       |

| V <sub>AUX_OV_HYST</sub>         | V <sub>AUX</sub> Overvoltage Hysteresis                                                 | _    | 0.07 | _     | V    | (15)  |

| R <sub>PD_AUX</sub>              | V <sub>AUX</sub> Internal Pull-down Resistor (active when V <sub>AUX</sub> is disabled) | 50   | -    | 170   | Ω    |       |

Notes

33907/33908

<sup>15.</sup> Guaranteed by design.

$T_{CASE}$  = -40 °C to 125 °C, unless otherwise specified.  $V_{SUP}$  =  $V_{SUP\_UV\_L}$  to 40 V, unless otherwise specified. All voltages referenced to ground. When 28 V <  $V_{SUP}$  < 40 V, thermal dissipation must be considered (<u>Figure 25</u>).

| Symbol                                           | Parameter                                                                                         | Min.                   | Тур.   | Max.             | Unit | Notes |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------|--------|------------------|------|-------|

| ail-safe outputs                                 |                                                                                                   |                        |        |                  |      |       |

| V <sub>RSTB_OL</sub>                             | Reset Low Output Level (I_RSTB = 2.0 mA and 2.0 V < V <sub>SUP</sub> < 40 V)                      | _                      | _      | 0.5              | V    | (16)  |

| I <sub>RSTB_LIM</sub>                            | Reset Output Current Limitation                                                                   | 12                     | -      | 25               | mA   |       |

| V <sub>RSTB_IL</sub>                             | External Reset Detection Threshold (falling)                                                      | 1.0                    | -      | -                | V    |       |

| V <sub>RSTB_IH</sub>                             | External Reset Detection Threshold (rising)                                                       | -                      | -      | 2.0              | V    |       |

| V <sub>RSTB_IN_HYST</sub>                        | External Reset Input Hysteresis                                                                   | 0.2                    | -      | -                | V    |       |

| V <sub>FS0B_OL</sub>                             | FS0B Low Output Level (I_FS0b = 2.0 mA)                                                           | -                      | -      | 0.5              | V    |       |

| I <sub>FS0B_LK</sub>                             | FS0B Input Current Leakage (V <sub>FS0B</sub> = 28 V)                                             | -                      | -      | 1.0              | μA   |       |

| I <sub>FS0B_LIM</sub>                            | FS0B Output Current Limitation                                                                    | 6.0                    | -      | 12               | mA   |       |

| Analog input - mι                                | ılti-purpose IOs                                                                                  | '                      |        |                  | 11   | -     |

| V <sub>IO_ANA_WD</sub>                           | Measurable Input Voltage (wide range)                                                             | 3.0                    | _      | 19               | V    |       |

| V <sub>IO_ANA_TG</sub>                           | Measurable Input Voltage (tight range)                                                            | 3.0                    | -      | 9.0              | V    |       |

| I <sub>IO_IN_ANA</sub>                           | Input Current                                                                                     | -                      | _      | 100              | μΑ   |       |

| igital input                                     |                                                                                                   |                        |        | II.              |      |       |

| V <sub>IO_IH</sub>                               | Digital High Input voltage level (IO_0:1, IO_4:5)  • Min Limit = 2.7 V at V <sub>SUP</sub> = 40 V | 2.6                    | _      | _                | V    |       |

| V <sub>IO23_IH</sub>                             | Digital High Input voltage level (IO_2, IO_3)                                                     | 2.0                    | _      | _                | V    |       |

| V <sub>IO_IL</sub>                               | Digital Low Input voltage Level (IO_0:1; IO_4:5)                                                  | _                      | _      | 2.1              | V    |       |

| V <sub>IO_HYST</sub>                             | Input Voltage Hysteresis (IO_0:1, IO_4:5)                                                         | 50                     | 120    | 500              | mV   | (17)  |

| V <sub>IO23_IL</sub>                             | Digital Low Input voltage Level (IO_2, IO_3)                                                      | -                      | _      | 0.9              | V    |       |

| V <sub>IO23_HYST</sub>                           | Input Voltage Hysteresis (IO_2, IO_3)                                                             | 200                    | 450    | 700              | mV   | (17)  |

| I <sub>IO_IN_0:1</sub>                           | Input Current for IO_0:1                                                                          | -5.0                   | -      | 100              | μA   |       |

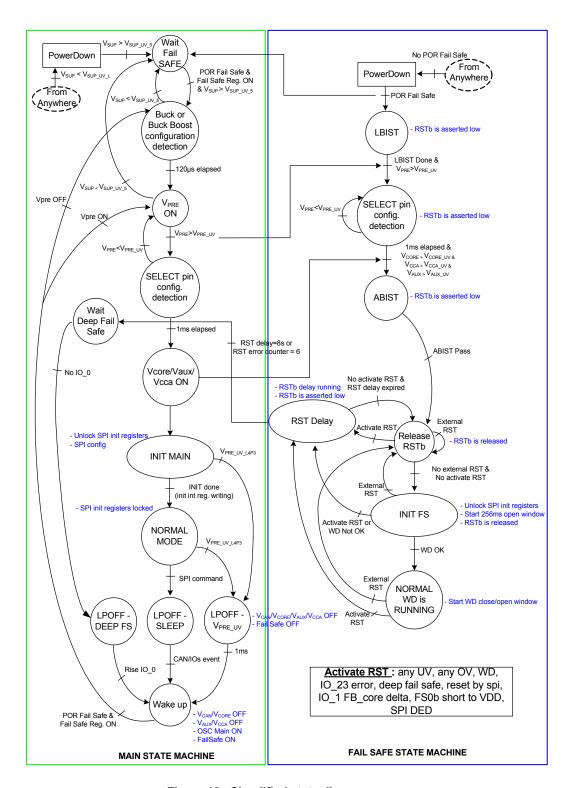

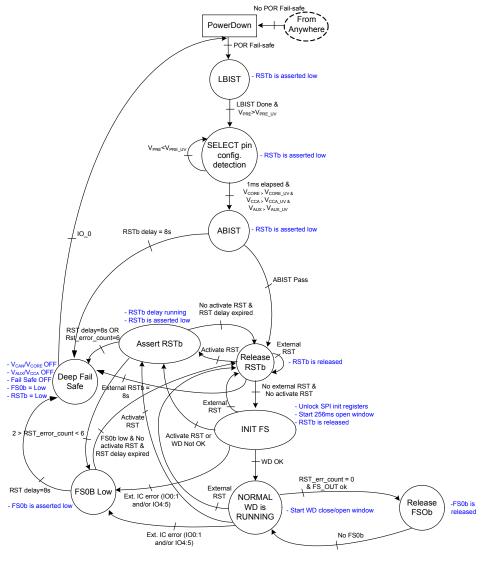

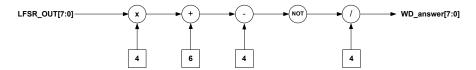

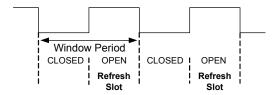

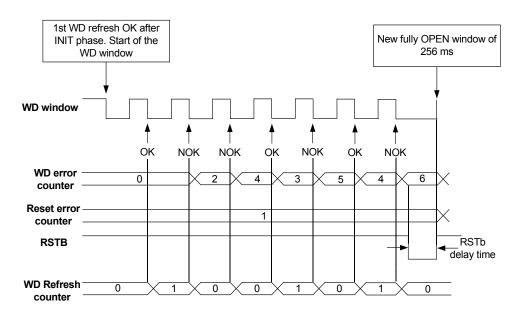

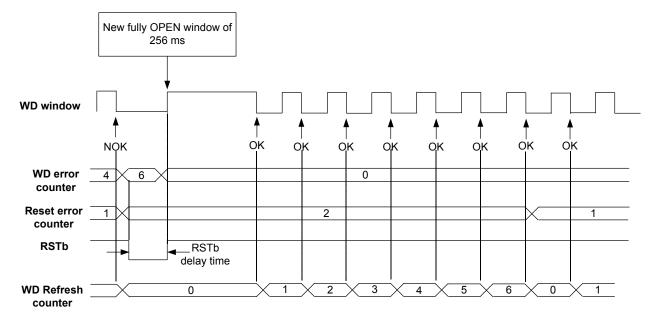

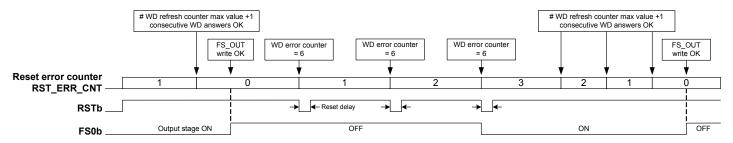

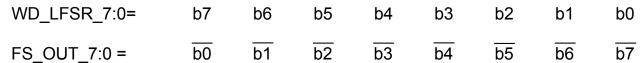

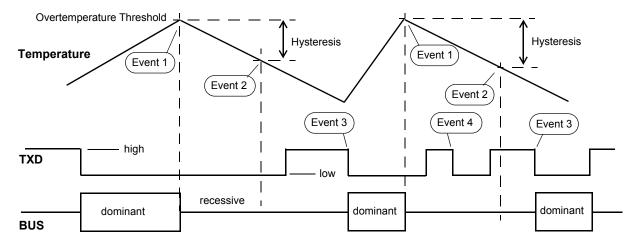

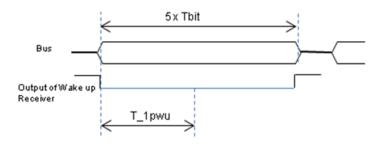

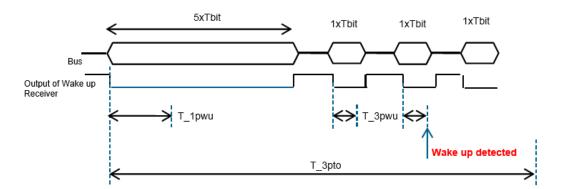

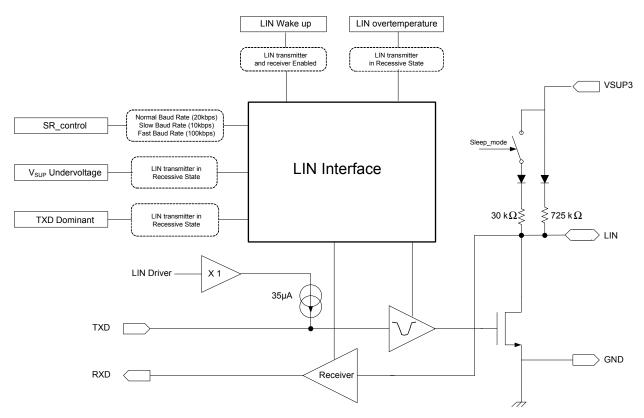

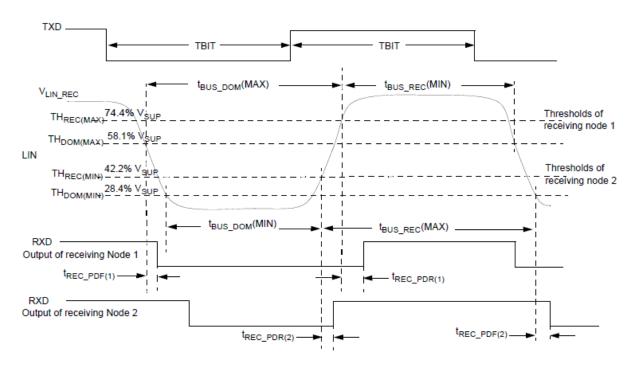

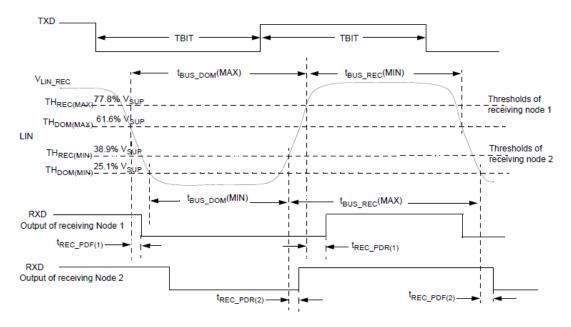

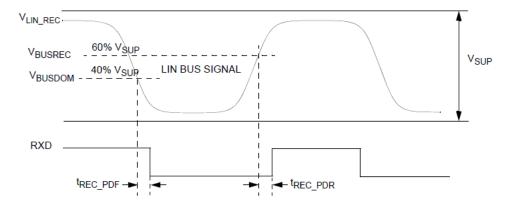

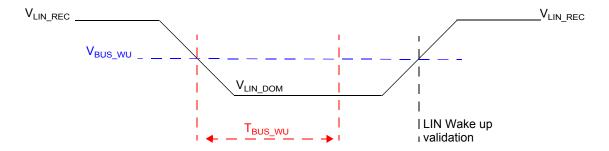

| I <sub>IO_IN_1</sub>                             | Input Current for IO_1 when used for FB_Core monitoring                                           | -1.0                   | _      | 1.0              | μΑ   |       |