#### Typical Applications

The HMC573LC3B is suitable for:

- Clock Generation Applications:

SONET OC-192 & SDH STM-64

- Point-to-Point & VSAT Radios

- Test Instrumentation

- Military & Space

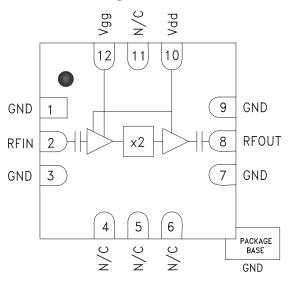

#### **Functional Diagram**

#### **Features**

High Output Power: +12 dBm

Low Input Power Drive: 0 to +6 dBm Fo Isolation: >20 dBc @ Fout= 16 GHz 100 KHz SSB Phase Noise: -134 dBc/Hz

Single Supply: +5V@ 92 mA

RoHS Compliant 3x3 mm SMT Package

#### General Description

The HMC573LC3B is a x2 active broadband frequency multiplier utilizing GaAs PHEMT technology in a leadless RoHS compliant SMT package. When driven by a +5 dBm signal, the multiplier provides +12 dBm typical output power from 8 to 22 GHz. The Fo and 3Fo isolations are >20 dBc and >25 dBc respectively at 16 GHz. The HMC573LC3B is ideal for use in LO multiplier chains for Pt to Pt & VSAT Radios yielding reduced parts count vs. traditional approaches. The low additive SSB Phase Noise of -134 dBc/Hz at 100 kHz offset helps maintain good system noise performance. The RoHS packaged HMC573LC3B eliminates the need for wire bonding, and allows the use of surface mount manufacturing techniques.

### Electrical Specifications, $T_A = +25$ °C, Vdd = +5V, 5 dBm Drive Level

| Parameter                                          |           | Тур. | Max. | Units  |

|----------------------------------------------------|-----------|------|------|--------|

| Frequency Range, Input                             | 4 - 11    |      | GHz  |        |

| Frequency Range, Output                            | 8 - 22    |      |      | GHz    |

| Output Power                                       | ower 9 12 |      | dBm  |        |

| Fo Isolation (with respect to output level)        |           | 20   |      | dBc    |

| 3Fo Isolation (with respect to output level)       |           | 25   |      | dBc    |

| 4Fo Isolation (with respect to output level)       |           | 15   |      | dBc    |

| Input Return Loss                                  |           | 10   |      | dB     |

| Output Return Loss                                 |           | 10   |      | dB     |

| SSB Phase Noise (100 kHz Offset)                   |           | -134 |      | dBc/Hz |

| Supply Current (Idd) (Vdd = 5V, Vgg = -1.25V Typ.) |           | 92   |      | mA     |

<sup>\*</sup>Adjust Vgg between -1.5 and ~1.1V to achieve Idd = 92 mA

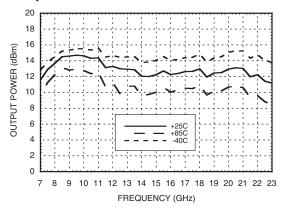

## Output Power vs. Temperature @ 5 dBm Drive Level

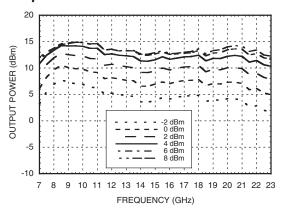

#### **Output Power vs. Drive Level**

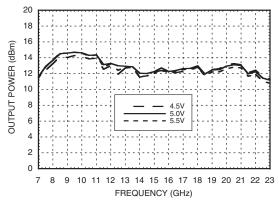

## Output Power vs. Supply Voltage @ 5 dBm Drive Level

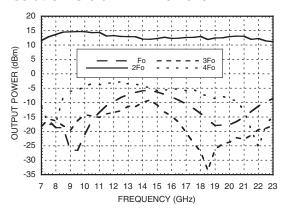

#### Isolation @ 5 dBm Drive Level

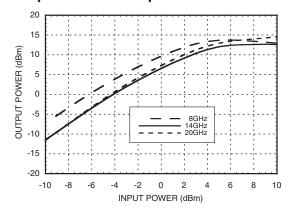

#### **Output Power vs. Input Power**

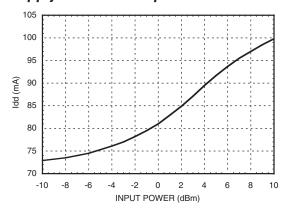

#### Supply Current vs. Input Power

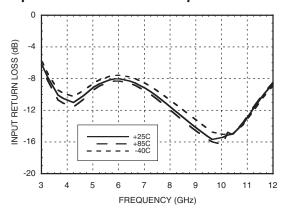

#### Input Return Loss vs. Temperature

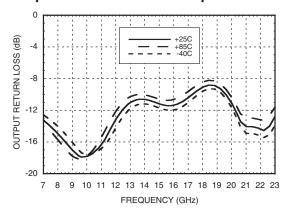

#### **Output Return Loss vs. Temperature**

#### **Absolute Maximum Ratings**

| RF Input (Vdd = +5V)                                          | +10 dBm        |

|---------------------------------------------------------------|----------------|

| Supply Voltage (Vdd)                                          | +6.0 Vdc       |

| Channel Temperature                                           | 175 °C         |

| Continuous Pdiss (T= 85 °C)<br>(derate 8.0 mW/°C above 85 °C) | 719 mW         |

| Thermal Resistance (channel to ground paddle)                 | 125 °C/W       |

| Storage Temperature                                           | -65 to +150 °C |

| Operating Temperature                                         | -40 to +85 °C  |

## Typical Supply Current vs. Vdd

| Vdd (Vdc) | Idd (mA) |  |  |

|-----------|----------|--|--|

| 4.5       | 90       |  |  |

| 5.0       | 92       |  |  |

| 5.5       | 94       |  |  |

#### Note:

Multiplier will operate over full voltage range shown above.

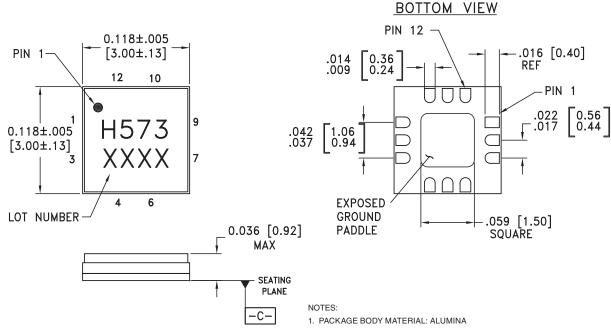

#### **Outline Drawing**

- 2. LEAD AND GROUND PADDLE PLATING: 30-80 MICROINCHES GOLD OVER 50 MICROINCHES MINIMUM NICKEL.

- 3. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 4. LEAD SPACING TOLERANCE IS NON-CUMULATIVE

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm DATUM -C-

- 6. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

- 7. CLASSIFIED AS MOISTURE SENSITIVITY LEVEL (MSL) 1.

## **Pin Description**

| Pin Number | Function | Description                                                                                                                          | Interface Schematic |  |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|

| 1, 3, 7, 9 | GND      | Package bottom must also be connected to RF/DC ground.                                                                               | GND<br>=            |  |

| 2          | RFIN     | Pin is AC coupled and matched to 50 Ohms.                                                                                            | RFIN ○──            |  |

| 4 - 6, 11  | N/C      | These pins are internally not connected; however, this product was specified with these pins connected to RF/ DC ground.             |                     |  |

| 8          | RFOUT    | Pin is AC coupled and matched to 50 Ohms.                                                                                            | —   —○ RFOUT        |  |

| 10         | Vdd      | Supply voltage 5V $\pm$ 0.5V. External bypass capacitors of 100 pF, 1,000 pF and 2.2 $\mu$ F are required.                           | Vdd Vdd             |  |

| 12         | Vgg      | Gate control for amplifier. Adjust to achieve Idd<br>of 92 mA. Please follow "MMIC Amplifier Biasing<br>Procedure" Application note. | Vaa e               |  |

## **Application Circuit**

| Component | Value    |          | J3 (        | ) (     | ) <b>J5</b>         |         |

|-----------|----------|----------|-------------|---------|---------------------|---------|

| C1, C2    | 100 pF   |          | 33 (        |         |                     |         |

| C3, C4    | 1,000 pF | C1 C3 C5 |             |         | C2                  | C4      |

| C5, C6    | 2.2 μF   |          |             |         |                     |         |

|           |          |          | _           |         | _                   |         |

|           |          |          | 12          |         | 10                  | 7       |

|           |          |          | Vg          | g Vd    | d                   |         |

|           |          |          | - RFIN<br>H | MC573LC | RFOUT<br>3B<br>,7,9 | 8<br>J2 |

|           |          |          |             | .14 ±   |                     |         |

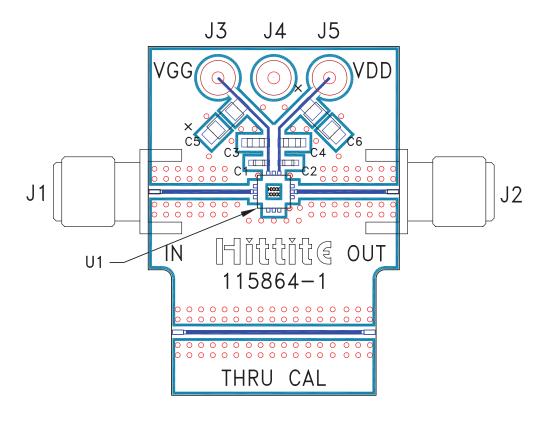

#### **Evaluation PCB**

#### List of Materials for Evaluation PCB 115739 [1]

| Item    | Description                     |

|---------|---------------------------------|

| J1, J2  | PCB Mount SRI K Connector       |

| J3 - J5 | DC Pin                          |

| C1, C2  | 100 pF Capacitor, 0402 Pkg.     |

| C3, C4  | 1,000 pF Capacitor, 0603 Pkg.   |

| C5, C6  | 2.2 µF Tantalum Capacitor       |

| U1      | HMC573LC3B x2 Active Multiplier |

| PCB [2] | 115864 Eval Board               |

<sup>[1]</sup> Reference this number when ordering complete evaluation PCB

The circuit board used in the final application should be generated with proper RF circuit design techniques. Signal lines should have 50 ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

<sup>[2]</sup> Circuit Board Material: Rogers 4350