# Dual Port, Xpressview, 3 GHz HDMI Receiver

Data Sheet ADV7619

#### **FEATURES**

High-Definition Multimedia Interface (HDMI®) 1.4a features supported

All mandatory and additional 3D video formats supported Extended colorimetry, including sYCC601, Adobe® RGB, Adobe YCC601, xvYCC extended gamut color CEC 1.4-compatible

**HDMI 3 GHz receiver**

297 MHz maximum TMDS clock frequency

Supports 4k × 2k resolution

**Xpressview fast switching of HDMI ports**

Up to 48-bit Deep Color with 36-/30-/24-bit support

High-bandwidth Digital Content Protection (HDCP) 1.4 support with internal HDCP keys

HDCP repeater support: up to 127 KSVs supported

**Integrated CEC controller**

Programmable HDMI equalizer

5 V detect and Hot Plug assert for each HDMI port

**Audio support**

Audio support including high bit rate (HBR) and Direct Stream Digital (DSD)

S/PDIF (IEC 60958-compatible) digital audio support

Supports up to four I<sup>2</sup>S outputs

Advanced audio mute feature

Dedicated, flexible audio output port

Super Audio CD® (SACD) with DSD output interface

**HBR** audio

**Dolby® TrueHD**

**DTS-HD Master Audio™**

#### General

Interrupt controller with 2 interrupt outputs

Standard identification (STDI) circuit

Highly flexible, 48-bit pixel output interface

36-bit output for resolutions up to 1080p Deep Color

$2 \times 24$ -bit pass-through outputs for HDMI formats greater than 2.25 GHz

Internal EDID RAM

Any-to-any,  $3 \times 3$  color space conversion (CSC) matrix

128-lead TQFP\_EP, 14 mm × 14 mm package

#### **APPLICATIONS**

**Projectors**

Video conferencing

**HDTV**

**AVR, HTiB**

Soundbar

Video switch

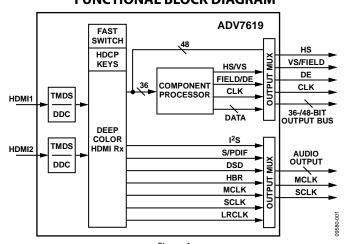

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **Xpressview**...

Fast Switching Technology by Analog Devices

Rev. C

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

| TABLE OF CONTENTS | Š |

|-------------------|---|

|-------------------|---|

| Features                                             | 1  |

|------------------------------------------------------|----|

| Applications                                         | 1  |

| Functional Block Diagram                             | 1  |

| Revision History                                     | 2  |

| General Description                                  | 3  |

| Detailed Functional Block Diagram                    | 3  |

| Specifications                                       | 4  |

| Electrical Characteristics                           | 4  |

| Data and I <sup>2</sup> C Timing Characteristics     | 6  |

| Absolute Maximum Ratings                             | 8  |

| Package Thermal Performance                          | 8  |

| ESD Caution                                          | 8  |

| Pin Configuration and Function Descriptions          | 9  |

| REVISION HISTORY<br>1/14—Rev. B to Rev. C            |    |

| Changes to Table 5                                   | 9  |

| 5/12—Rev. A to Rev. B                                |    |

| Changes to Features Section                          |    |

| Changes to General Description Section and Figure 2  |    |

| Change to Table 1                                    |    |

| Changes to Figure 5; Deleted Figure 6, Renumbered    | 0  |

| Sequentially                                         | 7  |

| Changes to Figure 7                                  |    |

| Changes to Table 5                                   |    |

| Changes to HDMI Receiver Section and Other Features  |    |

| Section                                              | 14 |

| Deleted Time-Division Multiplexed (TDM) Mode Section |    |

| and Figure 9                                         | 15 |

| Power Supply Recommendations                        | . 13 |

|-----------------------------------------------------|------|

| Power-Up Sequence                                   | . 13 |

| Power-Down Sequence                                 | . 13 |

| Current Rating Requirements for Power Supply Design | . 13 |

| Functional Overview                                 | . 14 |

| HDMI Receiver                                       | . 14 |

| Component Processor (CP)                            | . 14 |

| Other Features                                      | . 14 |

| Pixel Input/Output Formatting                       | . 15 |

| Pixel Data Output Mode Features                     | . 15 |

| Outline Dimensions                                  | . 22 |

| Ordering Guide                                      | . 22 |

# 9/11—Rev. 0 to Rev. A

| Changes to General Description Section             | 3        |

|----------------------------------------------------|----------|

| Changes to Data Output Transition Time Typ Values, | Гable 36 |

| Changes to Pin 113 Description                     | 12       |

| Changes to Pixel Input/Output Formatting Section   | 16       |

| Added Endnote 1 to Table 7                         | 17       |

| Added Endnote 1 to Table 12                        | 22       |

| Changes to Ordering Guide                          | 23       |

## 7/11—Revision 0: Initial Version

# **GENERAL DESCRIPTION**

The ADV7619 is a high quality, two input, one output (2:1) multiplexed High-Definition Multimedia Interface (HDMI\*) receiver. The ADV7619 is offered in professional (no HDCP keys) and commercial versions. The operating temperature range is 0°C to 70°C.

The ADV7619 incorporates a dual input HDMI-capable receiver that supports all mandatory 3D TV formats defined in the HDMI 1.4a specification, HDTV formats up to 1080p 36-bit Deep Color/2160p 8-bit, and display resolutions up to  $4k \times 2k$  (3840  $\times$  2160 at 30 Hz). It integrates an HDMI CEC controller that supports the capability discovery and control (CDC) feature.

The ADV7619 incorporates Xpressview<sup>™</sup> fast switching on both input HDMI ports. Using the Analog Devices, Inc., hardware-based HDCP engine to minimize software overhead, Xpressview technology allows fast switching between both HDMI input ports in less than 1 sec.

Each HDMI port has dedicated 5 V detect and Hot Plug<sup>™</sup> assert pins. The HDMI receiver also includes an integrated programmable equalizer that ensures robust operation of the interface with long cables.

The ADV7619 offers a flexible audio output port for audio data extraction from the HDMI stream. HDMI audio formats, including SACD via DSD and HBR, are supported by the ADV7619.

The HDMI receiver has advanced audio functionality, such as a mute controller, that prevents audible extraneous noise in the audio output.

The ADV7619 contains one main component processor (CP), which processes video signals from the HDMI receiver up to 1080p 36-bit Deep Color. It provides features such as contrast, brightness and saturation adjustments, STDI detection block, free-run, and synchronization alignment controls.

For video formats with pixel clocks higher than 170 MHz, the video signals received on the HDMI receiver are output directly to the pixel port output. To accommodate the higher bandwidth required for these higher resolutions, the output on the pixel bus consists of two 24-bit buses running at up to 150 MHz: one bus contains the even pixels, and the other bus contains the odd pixels. When these two buses are combined, they allow the transfer of video data with pixel clocks up to 300 MHz. In this mode, both 4:4:4 RGB 8-bit and 4:2:2 12-bit are supported.

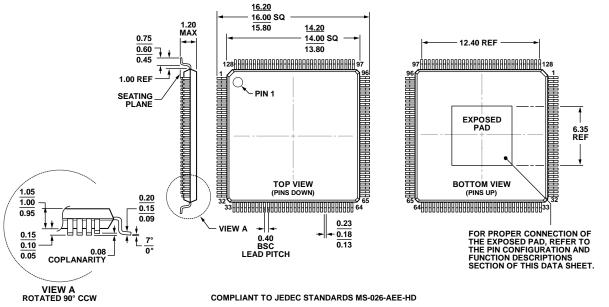

Fabricated in an advanced CMOS process, the ADV7619 is provided in a 14 mm  $\times$  14 mm, 128-lead, surface-mount, RoHS-compliant TQFP\_EP package and is specified over the 0°C to 70°C temperature range.

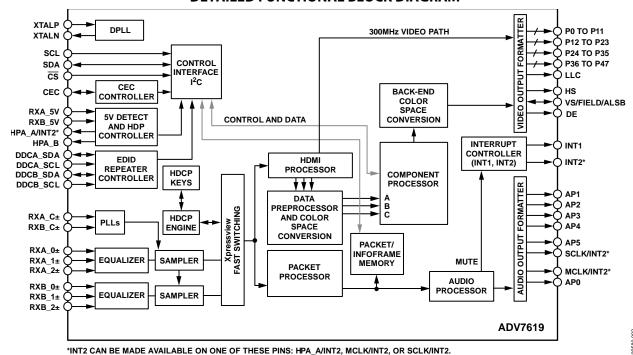

#### **DETAILED FUNCTIONAL BLOCK DIAGRAM**

Fiaure 2.

# **SPECIFICATIONS**

# **ELECTRICAL CHARACTERISTICS**

DVDD = 1.71 V to 1.89 V, DVDDIO = 3.14 V to 3.46 V, PVDD = 1.71 V to 1.89 V, TVDD = 3.14 V to 3.46 V, CVDD = 1.71 V to 1.89 V, operating temperature range, unless otherwise noted.

Table 1.

| Parameter                                  | Symbol               | <b>Test Conditions/Comments</b>                 | Min  | Тур   | Max  | Unit |

|--------------------------------------------|----------------------|-------------------------------------------------|------|-------|------|------|

| DIGITAL INPUTS <sup>1</sup>                |                      |                                                 |      |       |      |      |

| Input High Voltage                         | V <sub>IH</sub>      | XTALN and XTALP pins                            | 1.2  |       |      | V    |

|                                            |                      | Other digital inputs                            | 2    |       |      | V    |

| Input Low Voltage                          | V <sub>IL</sub>      | XTALN and XTALP pins                            |      |       | 0.4  | V    |

|                                            |                      | Other digital inputs                            |      |       | 0.8  | V    |

| Input Current                              | I <sub>IN</sub>      | RESET and CS pins                               |      | ±45   | ±60  | μΑ   |

|                                            |                      | Other digital inputs                            |      | ±10   |      | μΑ   |

| Input Capacitance                          | C <sub>IN</sub>      |                                                 |      |       | 10   | pF   |

| DIGITAL INPUTS (5 V TOLERANT) <sup>1</sup> |                      | DDCA_SCL, DDCA_SDA, DDCB_SCL, and DDCB_SDA pins |      |       |      |      |

| Input High Voltage                         | V <sub>IH</sub>      |                                                 | 2.6  |       |      | V    |

| Input Low Voltage                          | V <sub>IL</sub>      |                                                 |      |       | 0.8  | V    |

| Input Current                              | I <sub>IN</sub>      |                                                 | -70  |       | +70  | μΑ   |

| DIGITAL OUTPUTS <sup>1</sup>               |                      |                                                 | 1    |       |      | 1    |

| Output High Voltage                        | V <sub>OH</sub>      |                                                 | 2.4  |       |      | V    |

| Output Low Voltage                         | Vol                  |                                                 |      |       | 0.4  | V    |

| High Impedance Leakage Current             | I <sub>LEAK</sub>    | VS/FIELD/ALSB pin                               |      | ±35   | ±60  | μA   |

| gpedaee zeaage eae                         | · LE/IIX             | HPA_A/INT2 and HPA_B pins                       |      |       | ±70  | μΑ   |

|                                            |                      | Other digital outputs                           |      | ±10   | _, • | μΑ   |

| Output Capacitance                         | Соит                 |                                                 |      |       | 20   | pF   |

| POWER REQUIREMENTS                         | -001                 |                                                 |      |       |      | F-   |

| Digital Core Power Supply                  | DVDD                 |                                                 | 1.71 | 1.8   | 1.89 | V    |

| Digital I/O Power Supply                   | DVDDIO               |                                                 | 3.14 | 3.3   | 3.46 | v    |

| PLL Power Supply                           | PVDD                 |                                                 | 1.71 | 1.8   | 1.89 | V    |

| Terminator Power Supply                    | TVDD                 |                                                 | 3.14 | 3.3   | 3.46 | v    |

| Comparator Power Supply                    | CVDD                 |                                                 | 1.71 | 1.8   | 1.89 | V    |

| CURRENT CONSUMPTION                        | 0.00                 | See Table 2                                     | ,    |       |      | -    |

| Digital Core Power Supply                  | I <sub>DVDD</sub>    | Test Condition 1                                |      | 268   |      | mA   |

| Digital color ower supply                  | 10000                | Test Condition 2                                |      | 186   |      | mA   |

| Digital I/O Power Supply                   | I <sub>DVDDIO</sub>  | Test Condition 1                                |      | 9     |      | mA   |

| 2.g.a., , 2. 2 2pp.,                       | 1010010              | Test Condition 2                                |      | 10    |      | mA   |

| PLL Power Supply                           | I <sub>PVDD</sub>    | Test Condition 1                                |      | 20    |      | mA   |

| от от ради                                 |                      | Test Condition 2                                |      | 31    |      | mA   |

| Terminator Power Supply                    | I <sub>TVDD</sub>    | Test Condition 1                                |      | 92    |      | mA   |

| Terminater Correct Supply                  | 11400                | Test Condition 2                                |      | 92    |      | mA   |

| Comparator Power Supply                    | I <sub>CVDD</sub>    | Test Condition 1                                |      | 187   |      | mA   |

|                                            |                      | Test Condition 2                                |      | 166   |      | mA   |

| POWER-DOWN CURRENT <sup>2</sup>            |                      | See Table 2, Test Condition 3                   |      |       |      | 1    |

| Digital Core Power Supply                  | I <sub>DVDD PD</sub> |                                                 |      | 1.07  |      | mA   |

| Digital I/O Power Supply                   | DVDDIO PD            |                                                 |      | 0.034 |      | mA   |

| PLL Power Supply                           | I <sub>PVDD PD</sub> |                                                 |      | 0.691 |      | mA   |

| Terminator Power Supply                    | I <sub>TVDD_PD</sub> |                                                 |      | 0.857 |      | mA   |

| Comparator Power Supply                    | I <sub>CVDD_PD</sub> |                                                 |      | 0.053 |      | mA   |

| POWER-UP TIME                              | t <sub>PWRUP</sub>   |                                                 |      | 25    |      | ms   |

$<sup>^{\</sup>rm 1}\,{\rm Data}$  guaranteed by characterization.

<sup>&</sup>lt;sup>2</sup> Data recorded during lab characterization.

**Table 2. Test Conditions for Current Requirements**

| Parameter                               | Value Used                                                                                                                                                                        |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST CONDITION 1                        |                                                                                                                                                                                   |

| Number of HDMI Inputs (Xpressview Mode) | Two inputs                                                                                                                                                                        |

| Xpressview                              | On                                                                                                                                                                                |

| Video Format (Each HDMI Input)          | $4k \times 2k$                                                                                                                                                                    |

| HDCP Decryption                         | Off                                                                                                                                                                               |

| Video Pattern (Each HDMI Input)         | SMPTE                                                                                                                                                                             |

| Temperature                             | 20°C                                                                                                                                                                              |

| Power Supply Voltages                   | Nominal                                                                                                                                                                           |

| TEST CONDITION 2                        |                                                                                                                                                                                   |

| Number of HDMI Inputs (Xpressview Mode) | Two inputs                                                                                                                                                                        |

| Xpressview                              | On                                                                                                                                                                                |

| Video Format (Each HDMI Input)          | 1080p60, 36 bits                                                                                                                                                                  |

| HDCP Decryption                         | Off                                                                                                                                                                               |

| Video Pattern (Each HDMI Input)         | SMPTE                                                                                                                                                                             |

| Temperature                             | 20°C                                                                                                                                                                              |

| Power Supply Voltages                   | Nominal                                                                                                                                                                           |

| TEST CONDITION 3 (POWER-DOWN)           |                                                                                                                                                                                   |

| Number of HDMI Inputs (Xpressview Mode) | N/A                                                                                                                                                                               |

| Xpressview                              | N/A                                                                                                                                                                               |

| Video Format (Each HDMI Input)          | N/A                                                                                                                                                                               |

| HDCP Decryption                         | N/A                                                                                                                                                                               |

| Video Pattern (Each HDMI Input)         | N/A                                                                                                                                                                               |

| Temperature                             | 20°C                                                                                                                                                                              |

| Power Supply Voltages                   | Nominal                                                                                                                                                                           |

| Other Test Parameters                   | Power-Down Mode 0 (IO map, Register 0x0C = 0x62) Ring oscillator powered down (HDMI map, Register 0x48 = 0x01) DDC pads powered off (HDMI map, Register 0x73 = 0x03) <sup>1</sup> |

$<sup>^{\</sup>rm 1}$  For information about these registers, see the Hardware User Guide for the ADV7619 (UG-237).

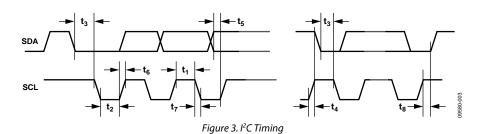

### DATA AND I<sup>2</sup>C TIMING CHARACTERISTICS

Table 3.

| Parameter                                       | Symbol                 | Test Conditions/Comments                  | Min   | Тур      | Max   | Unit         |

|-------------------------------------------------|------------------------|-------------------------------------------|-------|----------|-------|--------------|

| CLOCK AND CRYSTAL                               |                        |                                           |       |          |       |              |

| Crystal Frequency, XTAL                         |                        |                                           |       | 28.63636 |       | MHz          |

| Crystal Frequency Stability                     |                        |                                           |       |          | ±50   | ppm          |

| LLC Frequency Range                             |                        |                                           | 13.5  |          | 170   | MHz          |

| I <sup>2</sup> C PORTS                          |                        |                                           |       |          |       |              |

| SCL Frequency                                   |                        |                                           |       |          | 400   | kHz          |

| SCL Minimum Pulse Width High <sup>1</sup>       | t <sub>1</sub>         |                                           | 600   |          |       | ns           |

| SCL Minimum Pulse Width Low <sup>1</sup>        | $t_2$                  |                                           | 1.3   |          |       | μs           |

| Start Condition Hold Time <sup>1</sup>          | t <sub>3</sub>         |                                           | 600   |          |       | ns           |

| Start Condition Setup Time <sup>1</sup>         | t <sub>4</sub>         |                                           | 600   |          |       | ns           |

| SDA Setup Time <sup>1</sup>                     | <b>t</b> <sub>5</sub>  |                                           | 100   |          |       | ns           |

| SCL and SDA Rise Time <sup>1</sup>              | <b>t</b> 6             |                                           |       |          | 300   | ns           |

| SCL and SDA Fall Time <sup>1</sup>              | <b>t</b> <sub>7</sub>  |                                           |       |          | 300   | ns           |

| Stop Condition Setup Time <sup>1</sup>          | t <sub>8</sub>         |                                           | 0.6   |          |       | μs           |

| RESET FEATURE                                   |                        |                                           |       |          |       |              |

| Reset Pulse Width                               |                        |                                           | 5     |          |       | ms           |

| CLOCK OUTPUTS                                   |                        |                                           |       |          |       |              |

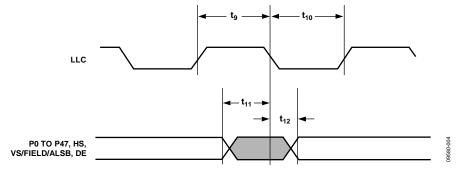

| LLC Mark-Space Ratio <sup>1</sup>               | t9:t10                 |                                           | 45:55 |          | 55:45 | % duty cycle |

| DATA AND CONTROL OUTPUTS <sup>1, 2</sup>        |                        |                                           |       |          |       |              |

| Data Output Transition Time                     | t <sub>11</sub>        | End of valid data to negative LLC edge    |       | 1.0      |       | ns           |

|                                                 | t <sub>12</sub>        | Negative LLC edge to start of valid data  |       | 0.1      |       | ns           |

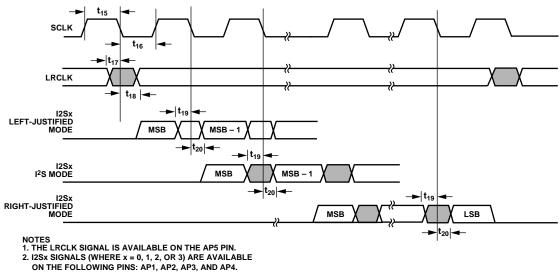

| I <sup>2</sup> S PORT, MASTER MODE <sup>1</sup> |                        |                                           |       |          |       |              |

| SCLK Mark-Space Ratio                           | t15:t16                |                                           | 45:55 |          | 55:45 | % duty cycle |

| LRCLK Data Transition Time                      | t <sub>17</sub>        | End of valid data to negative SCLK edge   |       |          | 10    | ns           |

|                                                 | t <sub>18</sub>        | Negative SCLK edge to start of valid data |       |          | 10    | ns           |

| 12Sx Data Transition Time                       | <b>t</b> <sub>19</sub> | End of valid data to negative SCLK edge   |       |          | 5     | ns           |

|                                                 | t <sub>20</sub>        | Negative SCLK edge to start of valid data |       |          | 5     | ns           |

<sup>&</sup>lt;sup>1</sup> Data guaranteed by characterization. <sup>2</sup> DLL bypassed on clock path.

# Timing Diagrams

Figure 4. Pixel Port and Control SDR Output Timing

Figure 5. I<sup>2</sup>S Timing

# **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                                          | Rating                           |

|----------------------------------------------------|----------------------------------|

| DVDD to GND                                        | 2.2 V                            |

| PVDD to GND                                        | 2.2 V                            |

| DVDDIO to GND                                      | 4.0 V                            |

| CVDD to GND                                        | 2.2 V                            |

| TVDD to GND                                        | 4.0 V                            |

| Digital Inputs to GND                              | GND - 0.3 V to DVDDIO + 0.3 V    |

| 5 V Tolerant Digital Inputs<br>to GND <sup>1</sup> | 5.3 V                            |

| Digital Outputs to GND                             | GND - 0.3 V to DVDDIO + 0.3 V    |

| XTALP, XTALN                                       | −0.3 V to PVDD + 0.3 V           |

| SCL, SDA Data Pins to<br>DVDDIO                    | DVDDIO – 0.3 V to DVDDIO + 3.6 V |

| Maximum Junction Temperature $(T_{JMAX})$          | 125°C                            |

| Storage Temperature Range                          | −60°C to +150°C                  |

| Infrared Reflow Soldering<br>(20 sec)              | 260°                             |

|                                                    |                                  |

<sup>&</sup>lt;sup>1</sup> The following inputs are 3.3 V inputs but are 5 V tolerant: DDCA\_SCL, DDCA\_SDA, DDCB\_SCL, and DDCB\_SDA.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **PACKAGE THERMAL PERFORMANCE**

To reduce power consumption when using the ADV7619, the user is advised to turn off the unused sections of the part.

Due to PCB metal variation and, therefore, variation in PCB heat conductivity, the value of  $\theta_{JA}$  may differ for various PCBs.

The most efficient measurement solution is obtained using the package surface temperature to estimate the die temperature because this solution eliminates the variance associated with the  $\theta_{IA}$  value.

The maximum junction temperature ( $T_{JMAX}$ ) of 125°C must not be exceeded. The following equation calculates the junction temperature using the measured package surface temperature and applies only when no heat sink is used on the device under test (DUT):

$$T_J = T_S + (\Psi_{JT} \times W_{TOTAL})$$

where:

$T_s$  is the package surface temperature (°C).  $\Psi_{JT} = 0.22$ °C/W for the 128-lead TQFP\_EP.

$$W_{TOTAL} = ((PVDD \times I_{PVDD}) + (0.2 \times TVDD \times I_{TVDD}) + (CVDD \times I_{CVDD}) + (DVDD \times I_{DVDDIO}) + (DVDDIO \times I_{DVDDIO}))$$

where 0.2 is 20% of the TVDD power that is dissipated on the part itself.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

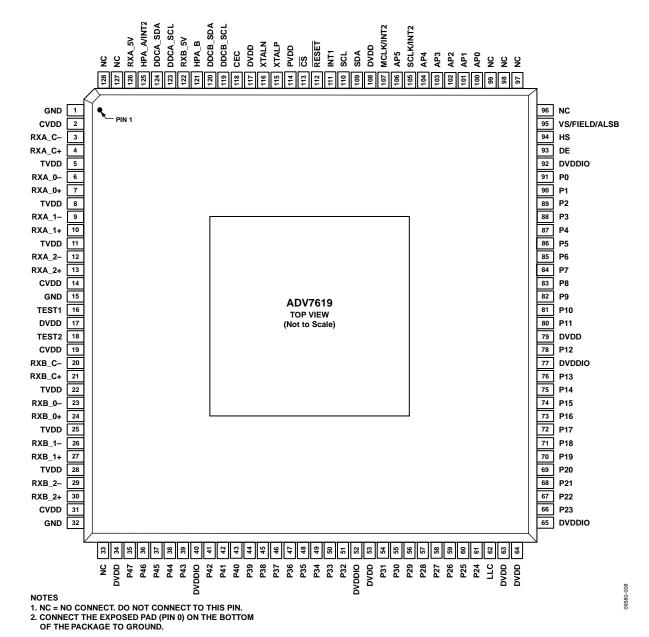

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 6. Pin Configuration

**Table 5. Pin Function Descriptions**

| d. Connect the exposed pad (Pin 0) on the bottom of the package to ground. |

|----------------------------------------------------------------------------|

|                                                                            |

| d.                                                                         |

| Analog Block Supply Voltage (1.8 V).                                       |

| Input Clock Complement of Port A in the HDMI Interface.                    |

| Input Clock True of Port A in the HDMI Interface.                          |

| ator Supply Voltage (3.3 V).                                               |

| Input Channel 0 Complement of Port A in the HDMI Interface.                |

| Input Channel 0 True of Port A in the HDMI Interface.                      |

| ator Supply Voltage (3.3 V).                                               |

| Input Channel 1 Complement of Port A in the HDMI Interface.                |

| Input Channel 1 True of Port A in the HDMI Interface.                      |

| ator Supply Voltage (3.3 V).                                               |

| Input Channel 2 Complement of Port A in the HDMI Interface.                |

| Input Channel 2 True of Port A in the HDMI Interface.                      |

| Analog Block Supply Voltage (1.8 V).                                       |

| d.                                                                         |

| n must be left floating.                                                   |

| Core Supply Voltage (1.8 V).                                               |

| n must be left floating.                                                   |

| Analog Block Supply Voltage (1.8 V).                                       |

| Input Clock Complement of Port B in the HDMI Interface.                    |

| Input Clock True of Port B in the HDMI Interface.                          |

| ator Supply Voltage (3.3 V).                                               |

| Input Channel 0 Complement of Port B in the HDMI Interface.                |

| Input Channel 0 True of Port B in the HDMI Interface.                      |

| ator Supply Voltage (3.3 V).                                               |

| Input Channel 1 Complement of Port B in the HDMI Interface.                |

| Input Channel 1 True of Port B in the HDMI Interface.                      |

| ator Supply Voltage (3.3 V).                                               |

| Input Channel 2 Complement of Port B in the HDMI Interface.                |

| Input Channel 2 True of Port B in the HDMI Interface.                      |

| Analog Block Supply Voltage (1.8 V).                                       |

| d.                                                                         |

| nect. Do not connect to this pin.                                          |

| Core Supply Voltage (1.8 V).                                               |

| Pixel Output Port.                                                         |

| I/O Supply Voltage (3.3 V).                                                |

| Pixel Output Port.                                                         |

|                                                                            |

| Pin No. | Mnemonic      | Туре                  | Description                                                                                                                         |

|---------|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 52      | DVDDIO        | Power                 | Digital I/O Supply Voltage (3.3 V).                                                                                                 |

| 53      | DVDD          | Power                 | Digital Core Supply Voltage (1.8 V).                                                                                                |

| 54      | P31           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 55      | P30           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 56      | P29           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 57      | P28           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 58      | P27           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 59      | P26           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 60      | P25           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 61      | P24           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 62      | LLC           | Digital video output  | Pixel Output Clock for the Pixel Data. The range is from 13.5 MHz to 170 MHz.                                                       |

| 63      | DVDD          | Power                 | Digital Core Supply Voltage (1.8 V).                                                                                                |

| 64      | DVDD          | Power                 | Digital Core Supply Voltage (1.8 V).                                                                                                |

| 65      | DVDDIO        | Power                 | Digital I/O Supply Voltage (3.3 V).                                                                                                 |

| 66      | P23           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 67      | P22           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 68      | P21           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 69      | P20           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 70      | P19           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 71      | P18           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 72      | P17           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 73      | P16           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 74      | P15           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 75      | P14           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 76      | P13           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 77      | DVDDIO        | Power                 | Digital I/O Supply Voltage (3.3 V).                                                                                                 |

| 78      | P12           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 79      | DVDD          | Power                 | Digital Core Supply Voltage (1.8 V).                                                                                                |

| 80      | P11           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 81      | P10           | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 82      | P9            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 83      | P8            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 84      | P7            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 85      | P6            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 86      | P5            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 87      | P4            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 88      | P3            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 89      | P2            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 90      | P1            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 91      | P0            | Digital video output  | Video Pixel Output Port.                                                                                                            |

| 92      | DVDDIO        | Power                 | Digital I/O Supply Voltage (3.3 V).                                                                                                 |

| 93      | DE            | Miscellaneous digital | Data Enable. The DE signal indicates active pixel data.                                                                             |

| 94      | HS            | Digital video output  | Horizontal Synchronization Output Signal.                                                                                           |

| 95      | VS/FIELD/ALSB | Digital video output  | VS is a vertical synchronization output signal. FIELD is a field synchronization output                                             |

|         |               |                       | signal in all interlaced video modes. ALSB allows selection of the I <sup>2</sup> C address.                                        |

| 96      | NC            | No connect            | No Connect. Do not connect to this pin.                                                                                             |

| 97      | NC            | No connect            | No Connect. Do not connect to this pin.                                                                                             |

| 98      | NC            | No connect            | No Connect. Do not connect to this pin.                                                                                             |

| 99      | NC            | No connect            | No Connect. Do not connect to this pin.                                                                                             |

| 100     | AP0           | Miscellaneous         | Audio Output Pin. This pin can be configured to output S/PDIF digital audio, high bit rate (HBR), or Direct Stream Digital® (DSD®). |

| 101     | AP1           | Miscellaneous         | Audio Output Pin. This pin can be configured to output S/PDIF digital audio, high bit rate (HBR), Direct Stream Digital (DSD).      |

| Pin No. | Mnemonic   | Туре                  | Description                                                                                                                                                                                                  |

|---------|------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 102     | AP2        | Miscellaneous         | Audio Output Pin. This pin can be configured to output S/PDIF digital audio, high bit rate (HBR), Direct Stream Digital (DSD), or I <sup>2</sup> S.                                                          |

| 103     | AP3        | Miscellaneous         | Audio Output Pin. This pin can be configured to output S/PDIF digital audio, high bit rate (HBR), Direct Stream Digital (DSD), or I <sup>2</sup> S.                                                          |

| 104     | AP4        | Miscellaneous         | Audio Output Pin. This pin can be configured to output S/PDIF digital audio, high bit rate (HBR), Direct Stream Digital (DSD), or I <sup>2</sup> S.                                                          |

| 105     | SCLK/INT2  | Miscellaneous digital | Serial Clock/Interrupt 2. This dual-function pin can be configured to output the audio serial clock or an Interrupt 2 signal.                                                                                |

| 106     | AP5        | Miscellaneous         | Audio Output Pin. This pin can be configured to output S/PDIF digital audio, high bit rate (HBR), or Direct Stream Digital (DSD). Pin AP5 is typically used to provide the LRCLK for I <sup>2</sup> S modes. |

| 107     | MCLK/INT2  | Miscellaneous digital | Master Clock/Interrupt 2. This dual-function pin can be configured to output the audio master clock or an Interrupt 2 signal.                                                                                |

| 108     | DVDD       | Power                 | Digital Core Supply Voltage (1.8 V).                                                                                                                                                                         |

| 109     | SDA        | Miscellaneous digital | I <sup>2</sup> C Port Serial Data Input/Output Pin. SDA is the data line for the control port.                                                                                                               |

| 110     | SCL        | Miscellaneous digital | I <sup>2</sup> C Port Serial Clock Input. SCL is the clock line for the control port.                                                                                                                        |

| 111     | INT1       | Miscellaneous digital | Interrupt. This pin can be active low or active high. When status bits change, this pin is triggered. The events that trigger an interrupt are user configurable.                                            |

| 112     | RESET      | Miscellaneous digital | System Reset Input. Active low. A minimum low reset pulse width of 5 ms is required to reset the ADV7619 circuitry.                                                                                          |

| 113     | CS         | Miscellaneous digital | Chip Select. This pin has an internal pull-down. Pulling this line up causes I <sup>2</sup> C state machine to ignore I <sup>2</sup> C transmission.                                                         |

| 114     | PVDD       | Power                 | PLL Supply Voltage (1.8 V).                                                                                                                                                                                  |

| 115     | XTALP      | Miscellaneous         | Input Pin for 28.63636 MHz Crystal or External 1.8 V, 28.63636 MHz Clock Oscillator Source to Clock the ADV7619.                                                                                             |

| 116     | XTALN      | Miscellaneous         | Crystal Input. Input pin for 28.63636 MHz crystal.                                                                                                                                                           |

| 117     | DVDD       | Power                 | Digital Core Supply Voltage (1.8 V).                                                                                                                                                                         |

| 118     | CEC        | Digital input/output  | Consumer Electronics Control Channel.                                                                                                                                                                        |

| 119     | DDCB_SCL   | HDMI input            | HDCP Slave Serial Clock Port B. DDCB_SCL is a 3.3 V input that is 5 V tolerant.                                                                                                                              |

| 120     | DDCB_SDA   | HDMI input            | HDCP Slave Serial Data Port B. DDCB_SDA is a 3.3 V input that is 5 V tolerant.                                                                                                                               |

| 121     | HPA_B      | Miscellaneous digital | Hot Plug Assert Signal Output for HDMI Port B. This pin is 5 V tolerant.                                                                                                                                     |

| 122     | RXB_5V     | HDMI input            | 5 V Detect Pin for Port B in the HDMI Interface.                                                                                                                                                             |

| 123     | DDCA_SCL   | HDMI input            | HDCP Slave Serial Clock Port A. DDCA_SCL is a 3.3 V input that is 5 V tolerant.                                                                                                                              |

| 124     | DDCA_SDA   | HDMI input            | HDCP Slave Serial Data Port A. DDCA_SDA is a 3.3 V input that is 5 V tolerant.                                                                                                                               |

| 125     | HPA_A/INT2 | Miscellaneous digital | Hot Plug Assert/Interrupt 2. This dual-function pin can be configured to output the Hot Plug assert signal for HDMI Port A or an Interrupt 2 signal. This pin is 5 V tolerant.                               |

| 126     | RXA_5V     | HDMI input            | 5 V Detect Pin for Port A in the HDMI Interface.                                                                                                                                                             |

| 127     | NC         | No connect            | No Connect. Do not connect to this pin.                                                                                                                                                                      |

| 128     | NC         | No connect            | No Connect. Do not connect to this pin.                                                                                                                                                                      |

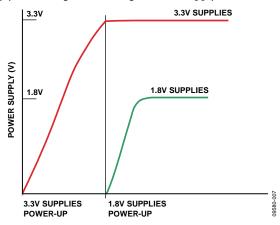

# POWER SUPPLY RECOMMENDATIONS POWER-UP SEQUENCE

The recommended power-up sequence for the ADV7619 is to power up the 3.3 V supplies first, followed by the 1.8 V supplies. RESET should be held low while the supplies are powered up.

Alternatively, the ADV7619 can be powered up by asserting all supplies simultaneously. In this case, care must be taken while the supplies are being established to ensure that a lower rated supply does not go above a higher rated supply level.

Figure 7. Recommended Power-Up Sequence

#### **POWER-DOWN SEQUENCE**

The ADV7619 supplies can be deasserted simultaneously as long as a higher rated supply does not go below a lower rated supply.

# CURRENT RATING REQUIREMENTS FOR POWER SUPPLY DESIGN

Table 6 shows the current rating requirements for power supply design.

Table 6. Current Rating Requirements for Power Supply Design

| Parameter           | Current Rating (mA) |

|---------------------|---------------------|

| l <sub>DVDD</sub>   | 400                 |

| I <sub>DVDDIO</sub> | 300                 |

| I <sub>PVDD</sub>   | 50                  |

| $I_{TVDD}$          | 120                 |

| Icvdd               | 250                 |

# **FUNCTIONAL OVERVIEW**

#### **HDMI RECEIVER**

The HDMI receiver supports all mandatory and many optional 3D video formats defined in the HDMI 1.4a specification, HDTV formats up to 2160p, and all display resolutions up to  $4k \times 2k$  ( $3840 \times 2160$  at 30 Hz).

With the inclusion of HDCP, displays can now receive encrypted video content. The HDMI interface of the ADV7619 allows for authentication of a video receiver, decryption of encoded data at the receiver, and renewability of that authentication during transmission, as specified by the HDCP 1.4 specification.

The HDMI-compatible receiver on the ADV7619 allows active equalization of the HDMI data signals. This equalization compensates for the high frequency losses inherent in HDMI and DVI cabling, especially at longer cable lengths and higher frequencies. The HDMI-compatible receiver is capable of equalizing for cable lengths up to 30 meters to achieve robust receiver performance. The ADV7619 also supports TERC4 error detection, which is used for detection of corrupted HDMI packets following a cable disconnect.

The HDMI receiver offers advanced audio functionality. The receiver contains an audio mute controller that can detect a variety of conditions that may result in audible extraneous noise in the audio output. Upon detection of these conditions, the audio signal can be ramped down or muted to prevent audio clicks or pops. The HDMI receiver supports the reception of all types of audio data described in the HDMI specifications, including

- LPCM (uncompressed audio)

- IEC 61937 (compressed audio)

- DSD audio (1-bit audio)

- HBR audio (high bit rate compressed audio)

Xpressview fast switching can be implemented with full HDCP authentication available on the background port. Synchronization measurement and status information are available for all HDMI inputs. HDMI receiver features include

- 2:1 multiplexed HDMI receiver

- 3D format support

- 297 MHz HDMI receiver

- Support for  $4k \times 2k$  resolutions

- Integrated equalizer for cable lengths up to 30 meters

- High-bandwidth Digital Content Protection (HDCP 1.4) (on background ports, also)

- Internal HDCP keys

- 36-/30-bit Deep Color support (resolutions up to 1080p)

- Audio sample, HBR, DSD packet support

- Repeater support

- Internal EDID RAM

- Hot Plug assert output pin for each HDMI port

CEC controller

#### **COMPONENT PROCESSOR (CP)**

The ADV7619 has two any-to-any,  $3 \times 3$  color space conversion (CSC) matrices. The first CSC block is placed in front of the CP section. The second CSC block is placed at the back of the CP section. Each CSC enables YPrPb-to-RGB and RGB-to-YCrCb conversions. Many other standards of color space can be implemented using the color space converters.

The CP block is available only for video signals with resolution up to 1080p Deep Color (pixel rates up to 170 MHz). For resolutions higher than 1080p, the video signal bypasses the CP block and is routed directly to the pixel bus output as two 24-bit (4:4:4) buses running at up to 150 MHz.

CP features include

- Support for 525i, 625i, 525p, 625p, 720p, 1080i, 1080p, and many other HDTV formats

- Manual adjustments including gain (contrast), offset (brightness), hue, and saturation

- Free-run output mode that provides stable timing when no video input is present

- 170 MHz conversion rate, which supports RGB input resolutions up to  $1600 \times 1200$  at 60 Hz

- Standard identification enabled by STDI block

- RGB that can be color space converted to YCrCb and decimated to a 4:2:2 format for video-centric, back-end IC interfacing

- Data enable (DE) output signal supplied for direct connection to HDMI/DVI transmitter

#### **OTHER FEATURES**

The ADV7619 has HS, VS, FIELD, and DE output signals with programmable position, polarity, and width.

The ADV7619 has two programmable interrupt request output pins: INT1 and INT2 (INT2 is accessible via one of the following pins: MCLK/INT2, SCLK/INT2, or HPA\_A/INT2). The ADV7619 also features a low power power-down mode.

The main I<sup>2</sup>C address can be set to 0x98 or 0x9A. On power-up or after a reset, the I<sup>2</sup>C address is set to 0x98 by default. The address can be changed to 0x9A by pulling up the VS/FIELD/ALSB pin and issuing the I<sup>2</sup>C command SAMPLE\_ALSB. For more information, see the Register Access and Serial Ports Description section in the UG-237.

The ADV7619 is provided in a 128-lead, 14 mm  $\times$  14 mm, RoHS-compliant TQFP\_EP package and is specified over the 0°C to 70°C temperature range.

# PIXEL INPUT/OUTPUT FORMATTING

The output section of the ADV7619 is highly flexible. The pixel output bus can support up to 36-bit 4:4:4 YCrCb or 36-bit 4:4:4 RGB. For resolutions higher than 1080p, the pixel output bus supports two 24-bit 4:4:4 RGB/YCrCb.

Part supports SDR (single data rate) and double data rate (DDR) outputs. SDR is supported up to 170 MHz LLC frequency (UXGA, 1080p60 for any OP\_FORMAT\_SEL or up to 300 MHz HDMI signals output on two 24-bit parallel video sub buses OP\_FORMAT\_SEL = 0x94, 0x95, 0x96, or 0x54; refer to Table 12). DDR can be supported with LLC clock frequency up to 50 MHz (video modes with original pixel clock lower than 100 MHz, such as 1080i60). In SDR mode, 16-/20-/24-bit 4:2:2 or 24-/30-/36-bit 4:4:4 output is possible. In DDR mode, the pixel output port can be configured for 4:2:2 YCrCb or 4:4:4 RGB for data rates up to 27 MHz.

Bus rotation is supported.

Table 7 through Table 12 provide the different output formats that are supported. All output modes are controlled via I<sup>2</sup>C.

For resolutions higher than 1080p, the video signals are routed directly to the pixel bus output as two 24-bit (4:4:4) buses running at up to 150 MHz. In this mode, the output data format is the same as the input format.

#### PIXEL DATA OUTPUT MODE FEATURES

For resolutions up to 1080p Deep Color, the output pixel port features include the following:

- SDR 8-/10-/12-bit ITU-R BT.656 4:2:2 YCrCb with embedded time codes and/or HS, VS, and FIELD output signals

- SDR 16-/20-/24-bit 4:2:2 YCrCb with embedded time codes and/or HS and VS/FIELD pin timing

- SDR 24-/30-/36-bit 4:4:4 YCrCb/RGB with embedded time codes and/or HS and VS/FIELD pin timing

- DDR 8-/10-/12-bit 4:2:2 YCrCb for data rates up to 27 MHz

- DDR 12-/24-/30-/36-bit 4:4:4 RGB for data rates up to 27 MHz

For resolutions greater than 1080p Deep Color (direct passthrough of video signal), the output pixel port features include the following:

- 8-bit 4:4:4 RGB/YCrCb for resolutions up to 2160p

- 12-bit 4:2:2 RGB/YCrCb for resolutions up to 2160p

Table 7. SDR 4:2:2 Output Modes (8-/10-/12-Bit)1

|                                    | SDR 4:2:2—OP_FORMAT_SEL[7:0] =      |                                      |                                      |                                      |                                      |  |  |  |

|------------------------------------|-------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--|--|--|

|                                    | 0x00                                | 0x01                                 | 0x02                                 | 0x06                                 | 0x0A                                 |  |  |  |

| Pixel Output                       | 8-Bit SDR<br>ITU-R BT.656<br>Mode 0 | 10-Bit SDR<br>ITU-R BT.656<br>Mode 0 | 12-Bit SDR<br>ITU-R BT.656<br>Mode 0 | 12-Bit SDR<br>ITU-R BT.656<br>Mode 1 | 12-Bit SDR<br>ITU-R BT.656<br>Mode 2 |  |  |  |

| P47                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| P46                                | _                                   | _                                    | High-Z                               | _                                    | _                                    |  |  |  |

| P45                                | High-Z                              | High-Z                               | _                                    | High-Z                               | High-Z                               |  |  |  |

| P44                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| P44<br>P43                         | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| <sup>2</sup> 43<br><sup>2</sup> 42 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| <sup>2</sup> 42<br><sup>2</sup> 41 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

|                                    | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| P40                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 239                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 238                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 237                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| <sup>2</sup> 36                    | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 235                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | Y3, Cb3, Cr3                         |  |  |  |

| 234                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | Y2, Cb2, Cr2                         |  |  |  |

| 233                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | Y1, Cb1, Cr1                         |  |  |  |

| 232                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | Y0, Cb0, Cr0                         |  |  |  |

| 231                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 230                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 29                                 | High-Z                              | High-Z                               | High-Z                               | Y1, Cb1, Cr1                         | High-Z                               |  |  |  |

| 28                                 | High-Z                              | High-Z                               | High-Z                               | Y0, Cb0, Cr0                         | High-Z                               |  |  |  |

| 27                                 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| P26                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 25                                 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 24                                 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 23                                 | Y7, Cb7, Cr7                        | Y9, Cb9, Cr9                         | Y11, Cb11, Cr11                      | Y11, Cb11, Cr11                      | Y11, Cb11, Cr11                      |  |  |  |

| 222                                | Y6, Cb6, Cr6                        | Y8, Cb8, Cr8                         | Y10, Cb10, Cr10                      | Y10, Cb10, Cr10                      | Y10, Cb10, Cr10                      |  |  |  |

| 21                                 | Y5, Cb5, Cr5                        | Y7, Cb7, Cr7                         | Y9, Cb9, Cr9                         | Y9, Cb9, Cr9                         | Y9, Cb9, Cr9                         |  |  |  |

| 20                                 | Y4, Cb4, Cr4                        | Y6, Cb6, Cr6                         | Y8, Cb8, Cr8                         | Y8, Cb8, Cr8                         | Y8, Cb8, Cr8                         |  |  |  |

| 19                                 | Y3, Cb3, Cr3                        | Y5, Cb5, Cr5                         | Y7, Cb7, Cr7                         | Y7, Cb7, Cr7                         | Y7, Cb7, Cr7                         |  |  |  |

| <sup>2</sup> 18                    | Y2, Cb2, Cr2                        | Y4, Cb4, Cr4                         | Y6, Cb6, Cr6                         | Y6, Cb6, Cr6                         | Y6, Cb6, Cr6                         |  |  |  |

| 17                                 | Y1, Cb1, Cr1                        | Y3, Cb3, Cr3                         | Y5, Cb5, Cr5                         | Y5, Cb5, Cr5                         | Y5, Cb5, Cr5                         |  |  |  |

| P16                                | Y0, Cb0, Cr0                        | Y2, Cb2, Cr2                         | Y4, Cb4, Cr4                         | Y4, Cb4, Cr4                         | Y4, Cb4, Cr4                         |  |  |  |

| P15                                | High-Z                              | Y1, Cb1, Cr1                         | Y3, Cb3, Cr3                         | Y3, Cb3, Cr3                         | High-Z                               |  |  |  |

| P14                                | High-Z                              | Y0, Cb0, Cr0                         | Y2, Cb2, Cr2                         | Y2, Cb2, Cr2                         | High-Z                               |  |  |  |

| P13                                | High-Z                              | High-Z                               | Y1, Cb1, Cr1                         | High-Z                               | High-Z                               |  |  |  |

| 212                                | High-Z                              | High-Z                               | Y0, Cb0, Cr0                         | High-Z                               | High-Z                               |  |  |  |

| P11                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| P10                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 9                                  | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 28                                 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 7                                  | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 26                                 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 25                                 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 24                                 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 23                                 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 2                                  | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 291                                | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

| 20                                 | High-Z                              | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |  |  |

$<sup>^{1}\,</sup>Modes\,require\,additional\,writes\,to\,IO\,map\,Register\,0x19\,(Bits[7:6]\,should\,be\,set\,to\,2'b11)\,and\,IO\,map\,Register\,0x33\,(Bit[6]\,should\,be\,set\,to\,1).$

Table 8. SDR 4:2:2 Output Modes (16-/20-/24-Bit)

|              | 0.00                                 | SEL[7:0] =                           | 0x8A                                 |                                      |                                      |  |

|--------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--|

|              | 0x80                                 | 0x81                                 |                                      | 0x82 0x86                            |                                      |  |

| Pixel Output | 16-Bit SDR<br>ITU-R BT.656<br>Mode 0 | 20-Bit SDR<br>ITU-R BT.656<br>Mode 0 | 24-Bit SDR<br>ITU-R BT.656<br>Mode 0 | 24-Bit SDR<br>ITU-R BT.656<br>Mode 1 | 24-Bit SDR<br>ITU-R BT.656<br>Mode 2 |  |

| P47          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| P46          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| P45          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| P44          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| P43          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| P42          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| P41          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| 240          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| 239          | _                                    | _                                    | _                                    | _                                    | _                                    |  |

|              | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| 238          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| P37          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| P36          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | High-Z                               |  |

| P35          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | Y3                                   |  |

| P34          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | Y2                                   |  |

| 233          | High-Z                               | High-Z                               | High-Z                               | Cb1, Cr1                             | Y1                                   |  |

| 232          | High-Z                               | High-Z                               | High-Z                               | Cb0, Cr0                             | Y0                                   |  |

| P31          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | Cb3, Cr3                             |  |

| P30          | High-Z                               | High-Z                               | High-Z                               | High-Z                               | Cb2, Cr2                             |  |

| P29          | High-Z                               | High-Z                               | High-Z                               | Y1                                   | Cb1, Cr1                             |  |

| P28          | High-Z                               | High-Z                               | High-Z                               | Y0                                   | Cb0, Cr0                             |  |