# **Single Phase Core Controller for VR12.6**

#### ISL95813

The ISL95813 single-phase controller provides a fully compliant VR12.6 power supply solution for Intel™ microprocessors. It provides a tightly regulated output voltage that is programmed through a high speed serial bus interface with the CPU. This interface also allows the CPU to acquire real-time information from the voltage regulator (VR), which includes load current and VR temperature.

Based on Intersil's Robust Ripple Regulator (R3™) technology, the PWM modulator provides faster transient response and settling time when compared against traditional modulation schemes. Its variable frequency topology also allows for natural period stretching discontinuous conduction mode (DCM) for increased efficiency and power savings in light load situations.

The ISL95813 has several other key features that include: DCR current sensing with single NTC thermal compensation; discrete resistor current sensing; differential remote voltage feedback; and user-programmable boot voltage, I<sub>MAX</sub>, T<sub>MAX</sub>, voltage transition slew rate, and switching frequency.

### **Features**

- Full VR12.6 specification compliance

- · Wide input voltage range: 4.6V to 25V

- R3™ control architecture delivers excellent transient response and power state mode transitions

- · Current monitor (IMON) with temperature compensation

- VRHOT# indicator for CPU protection

- · Digitally selectable switching frequency:

- 425kHz, 550kHz, 700kHz with ECO and PRO options

- Enhanced light-load efficiency discontinuous conduction mode operation

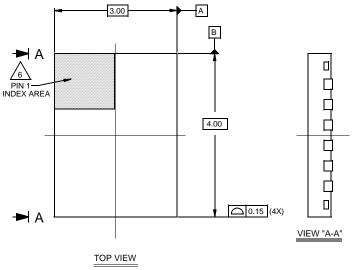

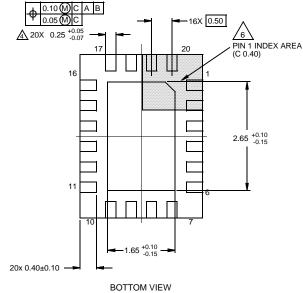

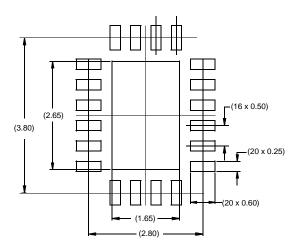

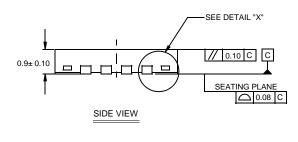

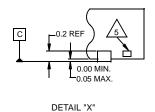

- Ultra-small 20 lead 3mmx4mm QFN package

- · Enable and power-good monitor

### **Applications**

- · Notebook Computers

- . Tablets, Ultrabooks™, and AIO

### **Related Literature**

• AN1846 Designer's Guide to the ISL95813 Evaluation Board

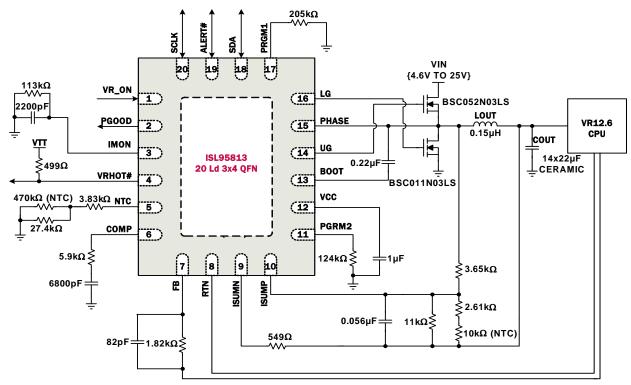

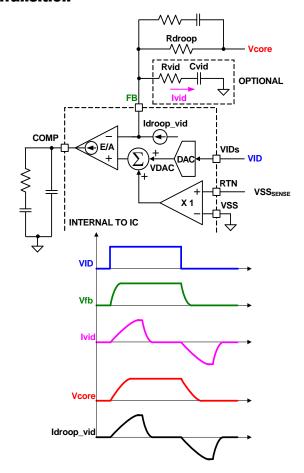

FIGURE 1. TYPICAL 40Amax, 12.6, APPLICATION DIAGRAM

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2) | PART<br>MARKING  | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|-----------------------------|------------------|---------------------|----------------------|----------------|

| ISL95813HRZ                 | 813H             | -10 to +100         | 20 LD 3x4 QFN        | L20.3x4        |

| ISL95813IRZ                 | 8131             | -40 to +100         | 20 LD 3x4 QFN        | L20.3x4        |

| ISL95813EV1Z                | Evaluation Board |                     |                      |                |

#### NOTES:

- 1. Add "-T" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL95813. For more information on MSL, please see tech brief TB363.

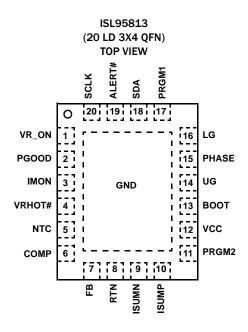

## **Pin Configuration**

### **Pin Descriptions**

| PIN | NAME   |                                  | FUNCTION                                                                                                                                                                                                                                                                                                                                            |

|-----|--------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VR_ON  | Digital Input                    | Enable input for controller. Connect to ground to disable the part. Connect to VCC to initiate soft-start and regulation.                                                                                                                                                                                                                           |

| 2   | PGOOD  | Digital Output                   | Power-Good open-drain output indicating when VR is in regulation with no faults detected. Pull up externally with a 680 $\Omega$ resistor to VCCP or 1.9k $\Omega$ to 3.3V.                                                                                                                                                                         |

| 3   | IMON   | Analog Output:<br>[Small-signal] | VR output current monitor. IMON pin sources a current proportional to the regulator output current. A resistor connected from this pin to ground will set a voltage that is proportional to the load current. This voltage is sampled with an internal ADC to produce a digital IMON signal that can be read through the serial communications bus. |

| 4   | VRHOT# | Digital Output                   | Open drain thermal overload output indicator. Can be considered part of communication bus with CPU.                                                                                                                                                                                                                                                 |

| 5   | NTC    | Analog Input:<br>[Small-Signal]  | Thermistor input to VR_HOT# circuit. Used to monitor VR temperature.                                                                                                                                                                                                                                                                                |

| 6   | COMP   | Analog Output:<br>[Small-signal] | Output of the gm error-amplifier for loop control. Connect to ground through the compensation network.                                                                                                                                                                                                                                              |

FN8449.0 May 15, 2013

# Pin Descriptions (Continued)

| PIN   | NAME   | FUNCTION                        |                                                                                                                                                                                                  |  |  |  |  |  |  |

|-------|--------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7     | FB     | Analog Input:<br>[Small-signal] | Output voltage feedback sensing input for regulation. Connect via resistor to VCC <sub>SENSE</sub> on CPU.                                                                                       |  |  |  |  |  |  |

| 8     | RTN    | Analog Input:<br>[Small-signal] | Ground return for differential remote output voltage sensing.<br>Connect via resistor to $\mbox{VCC}_{\mbox{SENSE}}$ on CPU.                                                                     |  |  |  |  |  |  |

| 9     | ISUMN  | Analog Input:<br>[Small-signal] | VR Loadline, Droop, and DCR sensing input.                                                                                                                                                       |  |  |  |  |  |  |

| 10    | ISUMP  | Analog Input:<br>[Small-signal] | VR Loadline, Droop, and DCR sensing input.                                                                                                                                                       |  |  |  |  |  |  |

| 11    | PRGM2  | Analog Input:<br>[Small-signal] | ADC input to program switching frequency and boot voltage using a resistor to ground. See "PROGRAM 2 Pin" on page 13 for all programming options.                                                |  |  |  |  |  |  |

| 12    | vcc    | Analog Input:<br>[Small-signal] | 5V IC bias supply input. Bypass to ground with a high-quality 0.1μF ceramic capacitor.                                                                                                           |  |  |  |  |  |  |

| 13    | воот   | Analog Input:<br>[Power]        | Floating high-side gate drive voltage supply. Connect to PHASE with a $0.1\mu F$ to $0.22\mu F$ high-quality ceramic capacitor.                                                                  |  |  |  |  |  |  |

| 14    | UG     | Analog Output:<br>[Power]       | Upper MOSFET gate drive. Connect with a wide trace to the gate of the upper switching MOSFET.                                                                                                    |  |  |  |  |  |  |

| 15    | PHASE  | Analog I/0:<br>[Power]          | Switching node and upper MOSFET gate drive return path. Connect with a wide trace to the source of the upper switching MOSFET, the drain of the lower switching MOSFET, and the output inductor. |  |  |  |  |  |  |

| 16    | LG     | Analog Output:<br>[Power]       | Lower MOSFET gate drive. Connect with a wide trace to the gate of the lower switching MOSFET.                                                                                                    |  |  |  |  |  |  |

| 17    | PRGM1  | Analog Input:<br>[Small-signal] | ADC input to program I <sub>CCMAX</sub> and FSEL bit using a resistor to ground. See "PROGRAM 1 Pin" on page 13 for all programming options.                                                     |  |  |  |  |  |  |

| 18    | SDA    | Digital I/O                     | Data input/output for CPU serial interface.                                                                                                                                                      |  |  |  |  |  |  |

| 19    | ALERT# | Digital Output                  | Alert signal for CPU serial interface.                                                                                                                                                           |  |  |  |  |  |  |

| 20    | SCLK   | Digital Input                   | Clock input for CPU serial interface.                                                                                                                                                            |  |  |  |  |  |  |

| e-pad | GND    | Analog Input:<br>[Power]        | Ground reference for IC as well as gate drive power ground return path. Connect to system ground plane with multiple vias.                                                                       |  |  |  |  |  |  |

### **Absolute Maximum Ratings**

| Supply Voltage, VCC                  | 0.3V to +7V                        |

|--------------------------------------|------------------------------------|

| Battery Voltage, VIN                 | +28V                               |

| Boot Voltage (BOOT)                  | 0.3V to +33V                       |

| Boot to Phase Voltage (BOOT-PHASE) . | 0.3V to +7V(DC)                    |

|                                      | 0.3V to +9V(<10ns)                 |

| Phase Voltage (PHASE)                | 7V (<20ns Pulse Width, 10 $\mu$ J) |

| UGATE Voltage (UGATE)                | PHASE-0.3V (DC) to BOOT            |

| PHASE-5V (                           | <20ns Pulse Width, 10µJ) to BOOT   |

| LGATE Voltage                        |                                    |

| 2.5V (<20ı                           | ns Pulse Width, 5µJ) to VDD + 0.3V |

| All Other Pins                       | 0.3V to (VDD + 0.3V)               |

| Open Drain Outputs, PGOOD, VR HOT#   | £ ALERT#0.3V to +7V                |

#### **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (° C/W) |

|-------------------------------------------|----------------------|-----------------------|

| 20 Ld QFN Package (Notes 4, 5)            | 44                   | 6                     |

| Maximum Junction Temperature              |                      | +150°C                |

| Maximum Storage Temperature Range         | 6!                   | 5°C to +150°C         |

| Maximum Junction Temperature (Plastic Pac | kage)                | +150°C                |

| Storage Temperature Range                 | 6!                   | 5°C to +150°C         |

| Pb-Free Reflow Profile                    |                      | see link below        |

| http://www.intersil.com/pbfree/Pb-FreeRe  | eflow.asp            |                       |

#### **Recommended Operating Conditions**

| Supply Voltage, VCC  |                |

|----------------------|----------------|

| Ambient Temperature  |                |

| HRZ                  | 10°C to +100°C |

| IRZ                  | 40°C to +100°C |

| Junction Temperature |                |

| HRZ                  | 10°C to +125°C |

| IRZ                  | 40°C to +125°C |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Operating Conditions: VDD = 5V,  $T_A = -10^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$  or  $-40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ ,  $f_{SW} = 700\text{kHz}$ , unless otherwise noted. Boldface limits apply over the operating temperature range for High Temp Commercial at  $-10^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$  or Industrial Temp at  $-40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ .

| PARAMETER                    | SYMBOL                     | TEST CONDITIONS         | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS |

|------------------------------|----------------------------|-------------------------|-----------------|------|-----------------|-------|

| INPUT POWER SUPPLY           |                            |                         |                 |      |                 |       |

| +5V Supply Current           | I <sub>VDD</sub>           | VR_ON = 1V              |                 | 3.5  | 5               | mA    |

|                              |                            | VR_ON = OV              |                 |      | 1               | μΑ    |

|                              |                            | PS4 State               |                 | 90   | 150             | μΑ    |

| POWER-ON-RESET THRESHOLDS    |                            |                         | ,               |      |                 |       |

| VDD Power-On-Reset Threshold | VDDPOR <sub>r</sub>        | V <sub>DD</sub> rising  |                 | 4.35 | 4.5             | ٧     |

|                              | VDDPOR <sub>f</sub>        | V <sub>DD</sub> falling | 4.00            | 4.15 |                 | V     |

| SYSTEM AND REFERENCES        |                            |                         | ,               |      |                 |       |

| System Accuracy              | HRZ                        | VID = 1.50V to 2.30V    | -0.5            |      | +0.5            | %     |

|                              | %Error (V <sub>OUT)</sub>  | VID = 1.00V to 1.49V    | -8              |      | +8              | mV    |

|                              |                            | VID = 0.50V to 0.99V    | -10             |      | +10             | mV    |

|                              | IRZ                        | VID = 1.50V to 2.30V    | -1              |      | +1              | %     |

|                              | %Error (V <sub>OUT</sub> ) | VID = 1.00V to 1.49V    | -15             |      | +15             | mV    |

|                              |                            | VID = 0.50V to 0.99V    | -20             |      | +20             | m۷    |

| Internal V <sub>BOOT</sub>   |                            | HRTZ (Set by R_PROG2)   | 1.683           | 1.7  | 1.717           | V     |

|                              |                            | IRTZ (Set by R_PROG2)   | 1.675           | 1.7  | 1.725           | V     |

| Maximum Output Voltage       | V <sub>OUT(MAX)</sub>      | VID = [11111111]        |                 | 2.3  |                 | V     |

| Minimum Output Voltage       | V <sub>OUT(MIN)</sub>      | VID = [00000001]        |                 | 0.5  |                 | V     |

**Electrical Specifications** Operating Conditions: VDD = 5V,  $T_A = -10^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$  or  $-40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ ,  $f_{SW} = 700\text{kHz}$ , unless otherwise noted. Boldface limits apply over the operating temperature range for High Temp Commercial at  $-10^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$  or industrial Temp at  $-40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ . (Continued)

| PARAMETER                                 | SYMBOL               | TEST CONDITIONS                        |       |          | MAX<br>(Note 6) | UNITS |

|-------------------------------------------|----------------------|----------------------------------------|-------|----------|-----------------|-------|

| CHANNEL FREQUENCY                         |                      | <u> </u>                               | '     | <u>'</u> |                 |       |

| 425kHz Configuration                      | f <sub>SW_425k</sub> |                                        | 395   | 425      | 455             | kHz   |

| 550kHz Configuration                      | f <sub>SW_550k</sub> | Set by R_PROG1                         | 510   | 550      | 590             | kHz   |

| 700kHz Configuration                      | f <sub>SW_700k</sub> |                                        | 650   | 700      | 750             | kHz   |

| 1000kHz Configuration                     | fsw_1000k            | Set by R_PROG1 (PRO PS2/PS3 only)      | 915   | 985      | 1055            | kHz   |

| AMPLIFIERS                                | <del>-</del>         |                                        |       |          | I.              |       |

| Current-Sense Amplifier Input Offset      |                      | I <sub>FB</sub> = 0A, HRZ              | -0.2  |          | +0.2            | mV    |

|                                           |                      | I <sub>FB</sub> = 0A, IRZ              | -0.3  |          | +0.3            | m۷    |

| Error Amp DC Gain (Note 7)                | A <sub>vO</sub>      |                                        |       | 90       |                 | dB    |

| Error Amp Gain-Bandwidth Product (Note 7) | GBW                  | C <sub>L</sub> = 20pF                  |       | 18       |                 | MHz   |

| POWER-GOOD AND PROTECTION MON             | ITORS                |                                        |       | -        |                 |       |

| PGOOD Low Voltage                         | V <sub>OL</sub>      | I <sub>PGOOD</sub> = 4mA               |       | 0.15     | 0.4             | ٧     |

| PGOOD Leakage Current                     | I <sub>OH</sub>      | PGOOD = 3.3V                           |       |          | 1               | μA    |

| PGOOD Delay                               | tpgd                 | V <sub>BOOT</sub> = 1.7V               |       | 1.2      |                 | ms    |

| ALERT# Low Voltage (Note 6)               |                      |                                        |       | 7        | 12              | Ω     |

| VR_HOT# Low Voltage (Note 6)              |                      |                                        |       | 7        | 12              | Ω     |

| ALERT# Leakage Current                    |                      |                                        |       |          | 1               | μΑ    |

| VR_HOT# Leakage Current                   |                      |                                        |       |          | 1               | μΑ    |

| GATE DRIVER                               |                      |                                        |       |          |                 |       |

| UGATE Pull-Up Resistance (Note 7)         | R <sub>UGPU</sub>    | 200mA Source Current                   |       | 1.0      | 1.5             | Ω     |

| UGATE Source Current (Note 7)             | lugsrc               | UGATE - PHASE = 2.5V                   |       | 2.0      |                 | Α     |

| UGATE Sink Resistance (Note 7)            | R <sub>UGPD</sub>    | 250mA Sink Current                     |       | 1.0      | 1.5             | Ω     |

| UGATE Sink Current (Note 7)               | I <sub>UGSNK</sub>   | UGATE - PHASE = 2.5V                   |       | 2.0      |                 | Α     |

| LGATE Pull-Up Resistance (Note 7)         | R <sub>LGPU</sub>    | 250mA Source Current                   |       | 1.0      | 1.5             | Ω     |

| LGATE Source Current (Note 7)             | I <sub>LGSRC</sub>   | LGATE - GND= 2.5V                      |       | 2.0      |                 | Α     |

| LGATE Sink Resistance (Note 7)            | R <sub>LGPD</sub>    | 250mA Sink Current                     |       | 0.5      | 0.9             | Ω     |

| LGATE Sink Current (Note 7)               | I <sub>LGSNK</sub>   | LGATE - GND = 2.5V                     |       | 4.0      |                 | Α     |

| UGATE to LGATE Deadtime                   | tugflgr              | UGATE falling to LGATE rising, no load |       | 17       |                 | ns    |

| LGATE to UGATE Deadtime                   | t <sub>LGFUGR</sub>  | LGATE falling to UGATE rising, no load |       | 29       |                 | ns    |

| BOOTSTRAP DIODE                           | I.                   |                                        |       |          |                 | 1     |

| ON-Resistance                             | R <sub>F</sub>       |                                        |       | 22       |                 | Ω     |

| Reverse Leakage                           | I <sub>R</sub>       | V <sub>R</sub> = 25V                   |       | 0.2      |                 | μΑ    |

| PROTECTION                                | I.                   |                                        |       |          |                 |       |

| Overvoltage Threshold                     | ov <sub>H</sub>      | ISUMN rising above setpoint for >1µs   | 240   | 300      | 360             | mV    |

| Overcurrent Threshold                     |                      |                                        | 56    | 60       | 64              | μΑ    |

| LOGIC THRESHOLDS                          |                      |                                        |       |          |                 |       |

| VR_ON Input Low                           | V <sub>IL</sub>      |                                        |       |          | 0.3             | V     |

| VR_ON Input High                          | V <sub>IH</sub>      | HRZ                                    | 0.7   |          |                 | V     |

|                                           | V <sub>IH</sub>      | IRZ                                    | 0.75  |          |                 | V     |

| THERMAL MONITOR                           |                      |                                        |       |          |                 | -     |

| NTC Source Current                        |                      | NTC = 1.3V                             | 58    | 60       | 62              | μΑ    |

| VR_HOT# Trip Voltage                      |                      | Falling                                | 0.881 | 0.893    | 0.905           | ٧     |

| VR_HOT# Reset Voltage                     |                      | Rising                                 | 0.924 | 0.936    | 0.948           | V     |

**Electrical Specifications** Operating Conditions: VDD = 5V,  $T_A = -10^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$  or  $-40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ ,  $f_{SW} = 700\text{kHz}$ , unless otherwise noted. Boldface limits apply over the operating temperature range for High Temp Commercial at  $-10^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$  or industrial Temp at  $-40^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$ . (Continued)

| PARAMETER                              | SYMBOL TEST CONDITIONS |                                        | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNITS |  |

|----------------------------------------|------------------------|----------------------------------------|-----------------|-------|-----------------|-------|--|

| Therm_Alert Trip Voltage               |                        | Falling                                | 0.92            | 0.932 | 0.944           | ٧     |  |

| Therm_Alert Reset Voltage              |                        | Rising                                 | 0.962           | 0.974 | 0.986           | V     |  |

| CURRENT MONITOR                        |                        |                                        |                 |       |                 |       |  |

| IMON Output Current                    | I <sub>IMON</sub>      | ISUMN pin current = 40µA               | 9.7             | 10    | 10.3            | μΑ    |  |

|                                        |                        | ISUMN pin current = 20µA               | 4.8             | 5     | 5.2             | μΑ    |  |

|                                        |                        | ISUMN pin current = 4μA                | 0.875           | 1     | 1.125           | μΑ    |  |

| I <sub>CCMAX</sub> Alert Trip Voltage  | V <sub>IMONMAX</sub>   | Rising                                 | 1.185           | 1.2   | 1.215           | V     |  |

| I <sub>CCMAX</sub> Alert Reset Voltage |                        | Falling                                | 1.122           | 1.14  | 1.152           | V     |  |

| INPUTS                                 | •                      |                                        |                 |       | 1               |       |  |

| VR_ON Leakage Current                  | I <sub>VR_ON</sub>     | VR_ON = OV                             | -1              | 0     | 1               | μΑ    |  |

|                                        |                        | VR_ON = 1V                             |                 | 3     | 5               | μΑ    |  |

| SCLK, SDA Leakage                      |                        | VR_ON = 0V, SCLK & SDA = 0V & 1V       | -1              |       | 1               | μΑ    |  |

|                                        |                        | VR_ON = 1V, SCLK & SDA = 1V            | -5              |       | 1               | μΑ    |  |

|                                        |                        | VR_ON = 1V, SCLK & SDA = 0V, SCLK      |                 | -42   |                 | μΑ    |  |

|                                        |                        | VR_ON = 1V, SCLK & SDA = 0V, SDA       |                 | -21   |                 | μΑ    |  |

| SLEW RATE (For VID Change)             | •                      | •                                      | -               | 1     | ı               | 1     |  |

| Fast Slew Rate                         |                        | Set by R_PROG2                         | 12              |       |                 | mV/μs |  |

| Slow Slew Rate                         |                        | Default setting Fast Slew divided by 4 | 3               |       |                 | mV/μs |  |

#### NOTES:

<sup>6.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

$<sup>{\</sup>bf 7. \ \, Limits \ established \ by \ characterization \ and \ are \ not \ production \ tested.}$

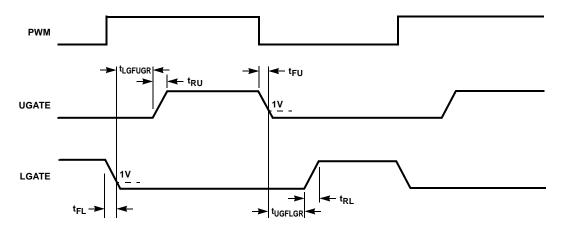

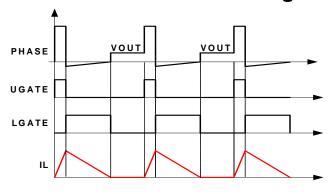

# **Gate Driver Timing Diagram**

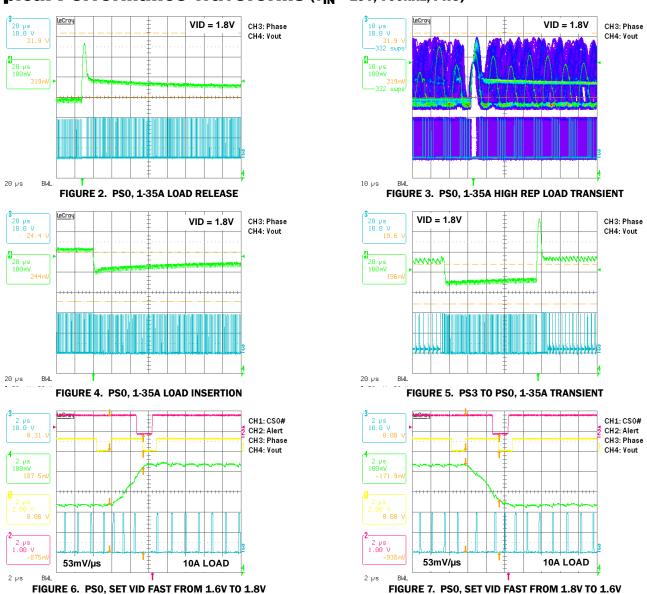

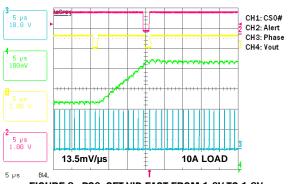

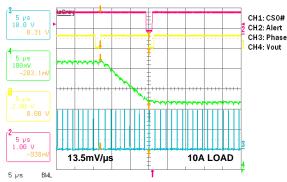

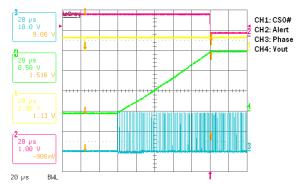

# Typical Performance Waveforms (V<sub>IN</sub> = 19V, 700kHz, PRO)

# Typical Performance Waveforms (VIN = 19V, 700kHz, PRO)

FIGURE 8. PSO, SET VID FAST FROM 1.6V TO 1.8V

FIGURE 9. PS0, SET VID FAST FROM 1.8V TO 1.6V

FIGURE 10. PS4 EXIT TO 1.6V, IO = 1A, SLEWRATE =  $53 \text{mV}/\mu\text{s}$

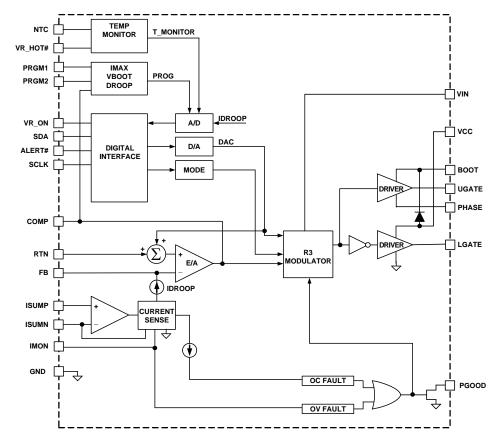

FIGURE 11. BLOCK DIAGRAM

### **Theory of Operation**

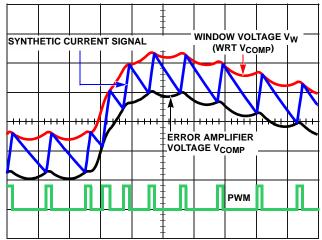

# **R**<sup>3™</sup> Modulator

The R<sup>3™</sup> Modulator is Intersil's proprietary synthetic current-mode hysteretic controller and is a blend of fixed frequency PWM and variable frequency hysteretic control technology. This modulator topology offers high noise immunity and a rapid transient response to dynamic load scenarios. Under static conditions the desired switching frequency is maintained within the entire specified range of input voltages, output voltages, and load currents. During load transients the controller will increase or decrease the PWM pulses and switching frequency to maintain output voltage regulation. Figure 12 illustrates this effect during a load insertion. As the window voltage starts to climb from a load step the time between PWM pulses decreases as f<sub>SW</sub> increases to keep the output within regulation.

FIGURE 12. MODULATOR WAVEFORMS DURING LOAD TRANSIENT

#### **Diode Emulation and Period Stretching**

FIGURE 13. DIODE EMULATION

The ISL95813 can operate in diode emulation (DE) mode to improve light load efficiency. In DE mode, the low-side MOSFET conducts only when the current is flowing from source to drain and does not allow reverse current, emulating a diode like a standard buck regulator. As Figure 13 shows, when LGATE is on, the low-side MOSFET conducts, creating negative voltage on the phase node due to the voltage drop across the ON-resistance. The controller monitors the current through monitoring the phase node voltage. It

turns off LGATE when the phase node voltage reaches zero to prevent the inductor current from reversing direction.

If the load current reaches the critical conduction point the inductor current will reach and stay at zero before the next phase node pulse and the regulator is in discontinuous conduction mode (DCM). Should the load current rise above the critical conduction point, the inductor current will not cross 0A in a switching cycle, and the regulator is in CCM although the controller is in DE mode.Equation 1 below gives the formula for critical conduction, where  $I_{critical}$  is the load current for critical conduction and  $\Delta I_{\rm I}$  is the ripple on the inductor current.

$$I_{critical} = \frac{\Delta I_L}{2}$$

(EQ. 1)

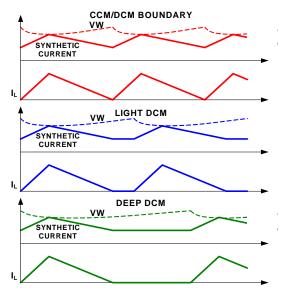

Figure 14 shows the operation principle in diode emulation mode at light load. The load gets incrementally lighter in the three cases from top to bottom. The PWM on-time is determined by the VW window size, therefore is the same, making the peak inductor current the same in the three cases. The controller clamps the synthetic current DE mode to make it mimic the inductor current. It takes the synthesized current longer to hit the lower window voltage, naturally stretching the switching period. The inductor current triangles move further apart from each other such that the inductor current average value is equal to the load current. By reducing the switching frequency in DE mode switching losses are decreased and light load efficiency is improved.

FIGURE 14. PERIOD STRETCHING

#### **ECO and PRO Mode DCM**

The ISL95813 has the ability to set both ECO and PRO mode DCM options for 700kHz switching applications. In ECO mode the time from Upper Gate On to Lower Gate Off is set to  $^1\!/_{700\text{kHz}}$  or 1.43µs. When PRO mode is selected the UG On to LG Off time is reduced to  $^1\!/_{1M\text{Hz}}$  or 1.0µs. For applications where efficiency is important ECO mode should be implemented as the longer switching times reduce the amount of switching loss in the FETs. PRO mode is ideal for applications that require lower DCM ripple as the shorter gate times reduce the amount of output ripple. Because of the reduced ripple in PRO mode the amount of output

capacitance can be reduced, saving both board space and BOM costs.

See "PROGRAM 1 RESISTOR VALUES" on page 13 for the ECO/PRO programming resistor options.

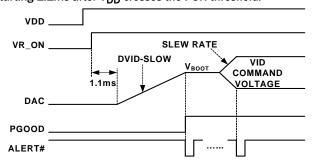

#### **Start-up Timing**

With the controller's  $V_{DD}$  voltage above the POR threshold, the start-up sequence begins when VR\_ON exceeds the logic high threshold. Figure 15 shows the typical start-up timing. The controller uses digital soft-start to ramp-up DAC to the voltage programmed by the SetVID command. PGOOD is asserted high and ALERT# is asserted low at the end of the ramp up. Similar results occur if VR\_ON is tied to  $V_{DD}$ , with the soft-start sequence starting 1.1ms after  $V_{DD}$  crosses the POR threshold.

FIGURE 15. SOFT-START WAVEFORMS

# Voltage Regulation and Load Line Implementation

After the start-up sequence, the controller regulates the output voltage to the value set by the VID information in Table 1. The controller will control the no-load output voltage to an accuracy of  $\pm 0.5\%$  over the VID voltage range. A differential amplifier allows voltage sensing for precise voltage regulation at the microprocessor die. Current silicon maximum VID is set as 2.3V, and any VID command above 2.3V will be rejected.

TABLE 1. VID TABLE

|   |   |   |   |   | V <sub>O</sub> (V) |   |   |   |    |         |

|---|---|---|---|---|--------------------|---|---|---|----|---------|

| 7 | 6 | 5 | 4 | 3 | 2                  | 1 | 0 | Н | ex | VR12.6  |

| 0 | 0 | 0 | 0 | 0 | 0                  | 0 | 0 | 0 | 0  | 0.00000 |

| 0 | 0 | 0 | 0 | 0 | 0                  | 0 | 1 | 0 | 1  | 0.50000 |

| 0 | 0 | 0 | 0 | 0 | 0                  | 1 | 0 | 0 | 2  | 0.51000 |

| 0 | 0 | 0 | 0 | 0 | 0                  | 1 | 1 | 0 | 3  | 0.52000 |

| 0 | 0 | 0 | 0 | 0 | 1                  | 0 | 0 | 0 | 4  | 0.53000 |

| 0 | 0 | 0 | 0 | 0 | 1                  | 0 | 1 | 0 | 5  | 0.54000 |

| 0 | 0 | 0 | 0 | 0 | 1                  | 1 | 0 | 0 | 6  | 0.55000 |

| 0 | 0 | 0 | 0 | 0 | 1                  | 1 | 1 | 0 | 7  | 0.56000 |

| 0 | 0 | 0 | 0 | 1 | 0                  | 0 | 0 | 0 | 8  | 0.57000 |

| 0 | 0 | 0 | 0 | 1 | 0                  | 0 | 1 | 0 | 9  | 0.58000 |

| 0 | 0 | 0 | 0 | 1 | 0                  | 1 | 0 | 0 | Α  | 0.59000 |

| 0 | 0 | 0 | 0 | 1 | 0                  | 1 | 1 | 0 | В  | 0.60000 |

| 0 | 0 | 0 | 0 | 1 | 1                  | 0 | 0 | 0 | С  | 0.61000 |

**TABLE 1. VID TABLE (Continued)**

|   | V | ID |   |   |   |   |   | V <sub>O</sub> (V) |   |         |

|---|---|----|---|---|---|---|---|--------------------|---|---------|

| 7 | 6 | 5  | 4 | 3 | 2 | 1 | 0 | Hex                |   | VR12.6  |

| 0 | 0 | 0  | 0 | 1 | 1 | 0 | 1 | 0                  | D | 0.62000 |

| 0 | 0 | 0  | 0 | 1 | 1 | 1 | 0 | 0                  | E | 0.63000 |

| 0 | 0 | 0  | 0 | 1 | 1 | 1 | 1 | 0                  | F | 0.64000 |

| 0 | 0 | 0  | 1 | 0 | 0 | 0 | 0 | 1                  | 0 | 0.65000 |

| 0 | 0 | 0  | 1 | 0 | 0 | 0 | 1 | 1                  | 1 | 0.66000 |

| 0 | 0 | 0  | 1 | 0 | 0 | 1 | 0 | 1                  | 2 | 0.67000 |

| 0 | 0 | 0  | 1 | 0 | 0 | 1 | 1 | 1                  | 3 | 0.68000 |

| 0 | 0 | 0  | 1 | 0 | 1 | 0 | 0 | 1                  | 4 | 0.69000 |

| 0 | 0 | 0  | 1 | 0 | 1 | 0 | 1 | 1                  | 5 | 0.70000 |

| 0 | 0 | 0  | 1 | 0 | 1 | 1 | 0 | 1                  | 6 | 0.71000 |

| 0 | 0 | 0  | 1 | 0 | 1 | 1 | 1 | 1                  | 7 | 0.72000 |

| 0 | 0 | 0  | 1 | 1 | 0 | 0 | 0 | 1                  | 8 | 0.73000 |

| 0 | 0 | 0  | 1 | 1 | 0 | 0 | 1 | 1                  | 9 | 0.74000 |

| 0 | 0 | 0  | 1 | 1 | 0 | 1 | 0 | 1                  | Α | 0.75000 |

| 0 | 0 | 0  | 1 | 1 | 0 | 1 | 1 | 1                  | В | 0.76000 |

| 0 | 0 | 0  | 1 | 1 | 1 | 0 | 0 | 1                  | С | 0.77000 |

| 0 | 0 | 0  | 1 | 1 | 1 | 0 | 1 | 1                  | D | 0.78000 |

| 0 | 0 | 0  | 1 | 1 | 1 | 1 | 0 | 1                  | E | 0.79000 |

| 0 | 0 | 0  | 1 | 1 | 1 | 1 | 1 | 1                  | F | 0.80000 |

| 0 | 0 | 1  | 0 | 0 | 0 | 0 | 0 | 2                  | 0 | 0.81000 |

| 0 | 0 | 1  | 0 | 0 | 0 | 0 | 1 | 2                  | 1 | 0.82000 |

| 0 | 0 | 1  | 0 | 0 | 0 | 1 | 0 | 2                  | 2 | 0.83000 |

| 0 | 0 | 1  | 0 | 0 | 0 | 1 | 1 | 2                  | 3 | 0.84000 |

| 0 | 0 | 1  | 0 | 0 | 1 | 0 | 0 | 2                  | 4 | 0.85000 |

| 0 | 0 | 1  | 0 | 0 | 1 | 0 | 1 | 2                  | 5 | 0.86000 |

| 0 | 0 | 1  | 0 | 0 | 1 | 1 | 0 | 2                  | 6 | 0.87000 |

| 0 | 0 | 1  | 0 | 0 | 1 | 1 | 1 | 2                  | 7 | 0.88000 |

| 0 | 0 | 1  | 0 | 1 | 0 | 0 | 0 | 2                  | 8 | 0.89000 |

| 0 | 0 | 1  | 0 | 1 | 0 | 0 | 1 | 2                  | 9 | 0.90000 |

| 0 | 0 | 1  | 0 | 1 | 0 | 1 | 0 | 2                  | Α | 0.91000 |

| 0 | 0 | 1  | 0 | 1 | 0 | 1 | 1 | 2                  | В | 0.92000 |

| 0 | 0 | 1  | 0 | 1 | 1 | 0 | 0 | 2                  | С | 0.93000 |

| 0 | 0 | 1  | 0 | 1 | 1 | 0 | 1 | 2                  | D | 0.94000 |

| 0 | 0 | 1  | 0 | 1 | 1 | 1 | 0 | 2                  | Е | 0.95000 |

| 0 | 0 | 1  | 0 | 1 | 1 | 1 | 1 | 2                  | F | 0.96000 |

| 0 | 0 | 1  | 1 | 0 | 0 | 0 | 0 | 3                  | 0 | 0.97000 |

| 0 | 0 | 1  | 1 | 0 | 0 | 0 | 1 | 3                  | 1 | 0.98000 |

| 0 | 0 | 1  | 1 | 0 | 0 | 1 | 0 | 3                  | 2 | 0.99000 |

| 0 | 0 | 1  | 1 | 0 | 0 | 1 | 1 | 3                  | 3 | 1.00000 |

#### **TABLE 1. VID TABLE (Continued)**

#### **VID** V<sub>O</sub> (V) Hex VR12.6 1.01000 1.02000 1.03000 1.04000 1.05000 1.06000 Α 1.07000 В 1.08000 С 1.09000 D 1.10000 Ε 1.11000 F 1.12000 1.13000 1.14000 1.15000 1.16000 1.17000 1.18000 1.19000 1.20000 1.21000 1.22000 Α 1.23000 В 1.24000 С 1.25000 D 1.26000 Ε 1.27000 F 1.28000 1.29000 1.30000 1.31000 1.32000 1.33000 1.34000 1.35000 1.36000 1.37000 1.38000

#### **TABLE 1. VID TABLE (Continued)**

| VID |   |   |   |   |   |   |   |     |   | V <sub>O</sub> (V) |

|-----|---|---|---|---|---|---|---|-----|---|--------------------|

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Hex |   | VR12.6             |

| 0   | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 5   | В | 1.40000            |

| 0   | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 5   | С | 1.41000            |

| 0   | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 5   | D | 1.42000            |

| 0   | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 5   | Е | 1.43000            |

| 0   | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 5   | F | 1.44000            |

| 0   | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 6   | 0 | 1.45000            |

| 0   | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 6   | 1 | 1.46000            |

| 0   | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 6   | 2 | 1.47000            |

| 0   | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 6   | 3 | 1.48000            |

| 0   | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 6   | 4 | 1.49000            |

| 0   | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 6   | 5 | 1.50000            |

| 0   | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 6   | 6 | 1.51000            |

| 0   | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 6   | 7 | 1.52000            |

| 0   | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 6   | 8 | 1.53000            |

| 0   | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 6   | 9 | 1.54000            |

| 0   | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 6   | Α | 1.55000            |

| 0   | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 6   | В | 1.56000            |

| 0   | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 6   | С | 1.57000            |

| 0   | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 6   | D | 1.58000            |

| 0   | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 6   | E | 1.59000            |

| 0   | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 6   | F | 1.60000            |

| 0   | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 7   | 0 | 1.61000            |

| 0   | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 7   | 1 | 1.62000            |

| 0   | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 7   | 2 | 1.63000            |

| 0   | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 7   | 3 | 1.64000            |

| 0   | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 7   | 4 | 1.65000            |

| 0   | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 7   | 5 | 1.66000            |

| 0   | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 7   | 6 | 1.67000            |

| 0   | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 7   | 7 | 1.68000            |

| 0   | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 7   | 8 | 1.69000            |

| 0   | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 7   | 9 | 1.70000            |

| 0   | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 7   | Α | 1.71000            |

| 0   | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 7   | В | 1.72000            |

| 0   | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 7   | С | 1.73000            |

| 0   | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 7   | D | 1.74000            |

| 0   | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 7   | E | 1.75000            |

| 0   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 7   | F | 1.76000            |

| 1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 8   | 0 | 1.77000            |

| 1   | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 8   | 1 | 1.78000            |

1.39000

1 0 5 A

0 1 1 0

**TABLE 1. VID TABLE (Continued)**

| VID |   |   |   |   |   |   |   | V <sub>O</sub> (V) |    |         |

|-----|---|---|---|---|---|---|---|--------------------|----|---------|

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Н                  | ex | VR12.6  |

| 1   | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 8                  | 2  | 1.79000 |

| 1   | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 8                  | 3  | 1.80000 |

| 1   | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 8                  | 4  | 1.81000 |

| 1   | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 8                  | 5  | 1.82000 |

| 1   | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 8                  | 6  | 1.83000 |

| 1   | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 8                  | 7  | 1.84000 |

| 1   | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 8                  | 8  | 1.85000 |

| 1   | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 8                  | 9  | 1.86000 |

| 1   | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 8                  | Α  | 1.87000 |

| 1   | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 8                  | В  | 1.88000 |

| 1   | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 8                  | С  | 1.89000 |

| 1   | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 8                  | D  | 1.90000 |

| 1   | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 8                  | E  | 1.91000 |

| 1   | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 8                  | F  | 1.92000 |

| 1   | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 9                  | 0  | 1.93000 |

| 1   | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 9                  | 1  | 1.94000 |

| 1   | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 9                  | 2  | 1.95000 |

| 1   | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 9                  | 3  | 1.96000 |

| 1   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 9                  | 4  | 1.97000 |

| 1   | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 9                  | 5  | 1.98000 |

| 1   | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 9                  | 6  | 1.99000 |

| 1   | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 9                  | 7  | 2.00000 |

| 1   | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 9                  | 8  | 2.01000 |

| 1   | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 9                  | 9  | 2.02000 |

| 1   | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 9                  | Α  | 2.03000 |

| 1   | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 9                  | В  | 2.04000 |

| 1   | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 9                  | С  | 2.05000 |

| 1   | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 9                  | D  | 2.06000 |

| 1   | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 9                  | Е  | 2.07000 |

| 1   | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 9                  | F  | 2.08000 |

| 1   | 0 | 1 | 0 | 0 | 0 | 0 | 0 | Α                  | 0  | 2.09000 |

| 1   | 0 | 1 | 0 | 0 | 0 | 0 | 1 | Α                  | 1  | 2.10000 |

| 1   | 0 | 1 | 0 | 0 | 0 | 1 | 0 | Α                  | 2  | 2.11000 |

| 1   | 0 | 1 | 0 | 0 | 0 | 1 | 1 | Α                  | 3  | 2.12000 |

| 1   | 0 | 1 | 0 | 0 | 1 | 0 | 0 | Α                  | 4  | 2.13000 |

| 1   | 0 | 1 | 0 | 0 | 1 | 0 | 1 | Α                  | 5  | 2.14000 |

| 1   | 0 | 1 | 0 | 0 | 1 | 1 | 0 | Α                  | 6  | 2.15000 |

| 1   | 0 | 1 | 0 | 0 | 1 | 1 | 1 | Α                  | 7  | 2.16000 |

| 1   | 0 | 1 | 0 | 1 | 0 | 0 | 0 | Α                  | 8  | 2.17000 |

**TABLE 1. VID TABLE (Continued)**

|   | VID |   |   |   |   |   |   |   |    | ν <sub>ο</sub> (ν) |

|---|-----|---|---|---|---|---|---|---|----|--------------------|

| 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 | H | ex | VR12.6             |

| 1 | 0   | 1 | 0 | 1 | 0 | 0 | 1 | Α | 9  | 2.18000            |

| 1 | 0   | 1 | 0 | 1 | 0 | 1 | 0 | Α | Α  | 2.19000            |

| 1 | 0   | 1 | 0 | 1 | 0 | 1 | 1 | Α | В  | 2.20000            |

| 1 | 0   | 1 | 0 | 1 | 1 | 0 | 0 | Α | С  | 2.21000            |

| 1 | 0   | 1 | 0 | 1 | 1 | 0 | 1 | Α | D  | 2.22000            |

| 1 | 0   | 1 | 0 | 1 | 1 | 1 | 0 | Α | E  | 2.23000            |

| 1 | 0   | 1 | 0 | 1 | 1 | 1 | 1 | Α | F  | 2.24000            |

| 1 | 0   | 1 | 1 | 0 | 0 | 0 | 0 | В | 0  | 2.25000            |

| 1 | 0   | 1 | 1 | 0 | 0 | 0 | 1 | В | 1  | 2.26000            |

| 1 | 0   | 1 | 1 | 0 | 0 | 1 | 0 | В | 2  | 2.27000            |

| 1 | 0   | 1 | 1 | 0 | 0 | 1 | 1 | В | 3  | 2.28000            |

| 1 | 0   | 1 | 1 | 0 | 1 | 0 | 0 | В | 4  | 2.29000            |

| 1 | 0   | 1 | 1 | 0 | 1 | 0 | 1 | В | 5  | 2.30000            |

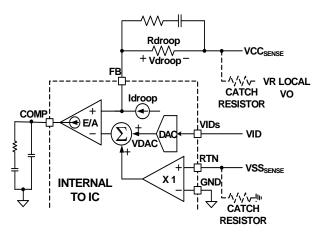

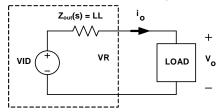

FIGURE 16. DIFFERENTIAL SENSING AND LOAD LINE IMPLEMENTATION

As the load current increases from zero, the output voltage will droop from the VID table value by an amount proportional to the load current to achieve the load line. The controller can sense the inductor current through the intrinsic DC Resistance (DCR) of the inductors as shown in the Typical Applications Diagram or through a current sense resistor in series with the inductor (Figure 24). In both methods, the capacitor  $\mathbf{C}_n$  voltage represents the inductor total current. A droop amplifier converts  $\mathbf{C}_n$  voltage into an internal current source with the gain set by resistor  $\mathbf{R}_i$ . The current source is used for load line implementation, current monitor and overcurrent protection.

$$I_{droop} = \frac{V_{Cn}}{R_i}$$

(EQ. 2)

When using inductor DCR current sensing, a single NTC element is used to compensate the positive temperature coefficient of the copper winding thus sustaining the load line accuracy with reduced cost.

$l_{droop}$  flows through resistor  $R_{droop}$  and creates a voltage drop as shown in Equation 3.

$$V_{droop} = R_{droop} \times I_{droop}$$

(EQ. 3)

$V_{droop}$  is the droop voltage required to implement load line. Changing  $R_{droop}$  or scaling  $I_{droop}$  can both change the load line slope. Since  $I_{droop}$  also sets the overcurrent protection level, it is recommended to first scale  $I_{droop}$  based on OCP requirement, then select an appropriate  $R_{droop}$  value to obtain the desired load line slope.

#### **Differential Voltage Sensing**

Figure 16 also shows the differential voltage sensing scheme. VCC<sub>SENSE</sub> and VSS<sub>SENSE</sub> are the remote voltage sensing signals from the processor die. A unity gain differential amplifier senses the VSS<sub>SENSE</sub> voltage and add it to the DAC output. The error amplifier regulates the inverting and the non-inverting input voltages to be equal as shown in Equation 4:

$$VCC_{SENSE} + V_{droop} = V_{DAC} + VSS_{SENSE}$$

(EQ. 4)

Rewriting Equation 4 and substitution of Equation 3 gives

$$VCC_{SENSE} - VSS_{SENSE} = V_{DAC} - R_{droop} \times I_{droop}$$

(EQ. 5)

Equation 5 is the exact equation required for load line implementation.

The VCC<sub>SENSE</sub> and VSS<sub>SENSE</sub> signals come from the processor die. The feedback will be open circuit in the absence of the processor. As Figure 16 shows, it is recommended to add a "catch" resistor to feed the VR local output voltage back to the compensator, and add another "catch" resistor to connect the VR local output ground to the RTN pin. These resistors, typically  $10\Omega\sim100\Omega$ , will provide voltage feedback if the system is powered up without a processor installed.

#### **CCM Switching Frequency**

The PROG2 pin configures the CCM switching frequency. When the ISL95813 is in continuous conduction mode (CCM), the switching frequency is not absolutely constant due to the nature of the  $R^{3_{TM}}$  modulator. Section " $R3^{TM}$  Modulator" on page 9 explains that the effective switching frequency will increase during load insertion and will decrease during load release to achieve fast response. On the other hand, the switching frequency is relatively constant at steady state. Variation is expected when the power stage condition, such as input voltage, output voltage, load, etc. changes. The variation is usually less than 15% and doesn't have any significant effect on output voltage ripple magnitude.

#### **PROGRAM 1 Pin**

PRGM1 programs I<sub>CCMAX</sub> register and switching frequency. For proper operation, it is recommended the 1% resistor value called out in the table be used in the final application.

**TABLE 2. PROGRAM 1 RESISTOR VALUES**

| R_PROG1<br>(±3%, kΩ) | ICCMAX<br>(A) | f <sub>SW</sub><br>(kHz) |

|----------------------|---------------|--------------------------|

| 1.0                  | 17            |                          |

| 5.76                 | 21            |                          |

| 9.31                 | 28            | 405                      |

| 13.3                 | 33            | 425                      |

| 17.4                 | 35            |                          |

| 21                   | 40            |                          |

| 24.9                 | 17            |                          |

| 28.7                 | 21            |                          |

| 33                   | 28            | EE0.                     |

| 42.2                 | 33            | 550                      |

| 49.9                 | 35            |                          |

| 57.6                 | 40            |                          |

| 64.9                 | 17            |                          |

| 73.2                 | 21            |                          |

| 80.6                 | 28            | 700 500                  |

| 90.9                 | 33            | 700 ECO                  |

| 102                  | 35            |                          |

| 113                  | 40            |                          |

| 124                  | 17            |                          |

| 137                  | 21            |                          |

| 154                  | 28            | 700 PRO                  |

| 169                  | 33            | 700 PRO                  |

| 187                  | 35            |                          |

| 205                  | 40            |                          |

#### **PROGRAM 2 Pin**

PRGM2 pin programs the both boot up voltage  $V_{BOOT}$ , and the VID Slew Rate. For proper operation, it is recommended the 1% resistor value called out in the table be used in the final application.

**TABLE 3. PROGRAM 2 RESISTOR VALUES**

| R_PROG2 (±3%, kΩ) | V <sub>BOOT</sub> (V) | VID Slew<br>(mV/μs) |

|-------------------|-----------------------|---------------------|

| 1.0               | 0                     |                     |

| 5.76              | 1.65                  | 12                  |

| 9.31              | 1.7                   | 12                  |

| 13.3              | 1.75                  |                     |

TABLE 3. PROGRAM 2 RESISTOR VALUES (Continued)

| R_PROG2 (±3%, kΩ) | V <sub>BOOT</sub> (V) | VID Slew<br>(mV/μs) |

|-------------------|-----------------------|---------------------|

| 17.4              | 1.75                  |                     |

| 21                | 1.7                   | 24                  |

| 24.9              | 1.65                  | 24                  |

| 28.7              | 0                     |                     |

| 33                | 0                     |                     |

| 42.2              | 1.65                  | 10                  |

| 49.9              | 1.7                   | 40                  |

| 57.6              | 1.75                  |                     |

| 64.9              | 1.75                  |                     |

| 73.2              | 1.7                   | 4-                  |

| 80.6              | 1.65                  | 45                  |

| 90.9              | 0                     |                     |

| 102               | 0                     |                     |

| 113               | 1.65                  |                     |

| 124               | 1.7                   | 53                  |

| 137               | 1.75                  |                     |

| 154               | 1.75                  |                     |

| 169               | 1.7                   |                     |

| 187               | 1.65                  | 80                  |

| 205               | 0                     |                     |

#### **Power State Modes**

Table 4 shows the power state operation mode.

**TABLE 4. POWER STATE OPERATION MODE**

| POWER STATE | CONFIGURATION        |

|-------------|----------------------|

| PS0         | 1-phase CCM          |

| PS1         | 1-phase CCM          |

| PS2         | 1-phase DE           |

| PS3         | 1-phase DE           |

| PS4         | Very low power state |

For PS0 and PS1, the ISL95813 operates in CCM while in PS2 and PS3 the device enters DCM.

In PS4, ISL95813 enters a very low power state and shuts down all the drivers and internal circuits. In this mode the controller only accepts SetVID-fast and SetVID-slow commands, all other SVID commands will be rejected. ISL95813 quiescent power is about 0.5mW in PS4.

#### **Dynamic Operation**

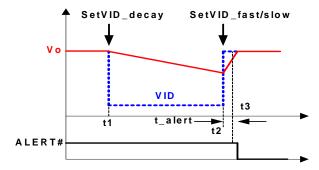

The ISL95813 responds to VID changes by slewing to the new voltage at a slew rate indicated in the SetVID command. There are three SetVID slew rates, namely SetVID\_fast, SetVID\_slow and SetVID\_decay.

SetVID\_fast command prompts the controller to enter CCM and to actively drive the output voltage to the new VID value at a minimum  $12\text{mV}/\mu\text{s}$  slew rate or the fast slew rate set by R\_PROG2.

SetVID\_slow command prompts the controller to enter CCM and to actively drive the output voltage to the new VID value at a minimum 3mV/µs slew rate.

SetVID\_decay command prompts the controller to enter DE mode. The output voltage,  $V_{core}$ , will decay down to the new VID value at a slew rate determined by the load as shown in Equation 6.

$$\frac{dV_{core}}{dt} = \frac{I_{out}}{C_{out}}$$

(EQ. 6)

Overvoltage protection is blanked during VID down transition in DE mode until the output voltage is within 60mV of the VID value. If the voltage decay rate is too fast, the controller will limit the voltage slew rate at SetVID\_slow slew rate.

ALERT# will be asserted low at the end of SetVID\_fast and SetVID\_slow VID transitions.

FIGURE 17. SETVID DECAY PRE-EMPTIVE BEHAVIOR

Figure 17 shows SetVID Decay Pre-Emptive behavior. The controller receives a SetVID\_decay command at t1. The VR enters DE mode and the output voltage Vo decays down slowly. At t2, before Vo reaches the intended VID target of the SetVID\_decay command, the controller receives a SetVID\_fast (or SetVID\_slow) command to go to a voltage higher than the actual Vo. The controller will react immediately and slew Vo to the new target voltage at the slew rate specified by the SetVID command. At t3, Vo reaches the new target voltage and the controller asserts the ALERT# signal.

The R<sup>3™</sup> modulator intrinsically has voltage feed-forward. The output voltage is insensitive to a fast slew rate input voltage change.

#### **Current Monitor**

The controller provides the current monitor function. IMON pin reports the inductor current.

The IMON pin outputs a high-speed analog current source that is 1/4 of the droop current flowing out of the FB pin. Thus becoming Equation 7:

$$I_{\text{IMON}} = 0.25 \times I_{\text{droop}} \tag{EQ. 7}$$

As the Typical Applications Diagram shows in Figure 1, a resistor  ${\rm R}_{imon}$  is connected to the IMON pin to convert the IMON pin

current to voltage. A capacitor should be paralleled with  $R_{imon}$  to filter the voltage information. This voltage is sampled with an internal ADC to produce a digital IMON signal that can be read through the serial communications bus.

The IMON pin voltage range is 0V to 1.2V. The controller monitors the IMON pin voltage and considers that ISL95813 has reached  $I_{CCMAX}$  when IMON pin voltage is 1.2V.

# Adaptive Body Diode Conduction Time Reduction

In DCM, the controller turns off the low-side MOSFET when the inductor current approaches zero. During on-time of the low-side MOSFET, the phase node sits at a negative voltage equal to the MOSFET r<sub>DSON</sub> voltage drop. A phase comparator inside the controller monitors the phase voltage during the on-time of the low-side MOSFET and compares it against a threshold to determine the zero-crossing point of the inductor current. Should the inductor current not reach zero when the lower FET turns off, it will then flow through the low-side MOSFET body diode, decreasing the voltage on the phase node until the inductor current completely decays to zero. When the inductor current finally reaches 0A phase is considered to be in tri-state mode and its voltage floats to the set V<sub>OUT</sub> value.

If the inductor current has crossed zero and reversed the direction when the low-side MOSFET turns off, current will then flow through the high-side MOSFET body diode, causing a voltage spike on phase which will decay to the set  $V_{\mbox{OUT}}$  voltage as phase tri-states.

The controller continues monitoring the phase voltage after turning off the low-side MOSFET and adjusts the phase comparator threshold voltage accordingly in iterative steps such that the low-side MOSFET body diode conducts for approximately 30ns to minimize the body diode-related loss.

#### **Protection**

The ISL95813 provides the designer with overcurrent, overvoltage, and over-temperature protection.

The controller determines overcurrent protection (OCP) by comparing the average value of the droop current  $I_{droop}$  with an internal current source threshold as Table 5 shows. It declares OCP when  $I_{droop}$  is above the threshold for 120µs.

For over temperature and overcurrent faults, the controller takes the same actions: de-assertion of PGOOD and turn-off of all the high-side and low-side power MOSFETs. Any residual inductor current will decay through the MOSFET body diodes or load.

The controller will declare an overvoltage fault and de-assert PGOOD if the output voltage exceeds the VID set value by +300mV. The controller will immediately declare an OV fault, toggle PGOOD to ground. The low-side power MOSFET remains on until the output voltage is pulled down below the VID set value before being shut off, and placing phase into tri-state. If the output voltage rises above the VID set value +300mV again, the protection process is repeated. This behavior provides the maximum amount of protection against shorted high-side power MOSFETs while preventing output ringing below ground.

All the above fault conditions can be reset by toggling VR\_ON low. When VR\_ON is brought back to its high operating levels a soft-start will occur.

Table 5 summarizes the fault protections.

**TABLE 5. FAULT PROTECTION SUMMARY**

| FAULT TYPE            | FAULT DURATION<br>BEFORE<br>PROTECTION | PROTECTION ACTION                                                                                    | FAULT<br>RESET     |

|-----------------------|----------------------------------------|------------------------------------------------------------------------------------------------------|--------------------|

| Overcurrent           | 120µs                                  | PWM tri-state,<br>PGOOD latched low                                                                  | VR_ON<br>toggle or |

| Overvoltage<br>+300mV | Immediately                            | PGOOD latched low.<br>Actively pulls the<br>output voltage to<br>below VID value, then<br>tri-state. | VDD toggle         |

#### **Supported Data And Configuration Registers**

The controller supports the following data and configuration registers.

TABLE 6. SUPPORTED DATA AND CONFIGURATION REGISTERS

| INDEX       | REGISTER<br>NAME      | DESCRIPTION                                                                                                                                                                                                                      | DEFAULT<br>VALUE  |

|-------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 00h         | Vendor ID             | Uniquely identifies the VR vendor.<br>Assigned by Intel.                                                                                                                                                                         | 12h               |

| 01h         | Product ID            | Uniquely identifies the VR product.<br>Intersil assigns this number.                                                                                                                                                             | 0Ch               |

| 02h         | Product<br>Revision   | Uniquely identifies the revision of the VR control IC. Intersil assigns this data.                                                                                                                                               | 04h               |

| 05h         | Protocol ID           | Identifies what revision of SVID protocol the controller supports.                                                                                                                                                               | 03h               |

| 06h         | Capability            | Identifies the SVID VR capabilities and which of the optional telemetry registers are supported.                                                                                                                                 | 81h               |

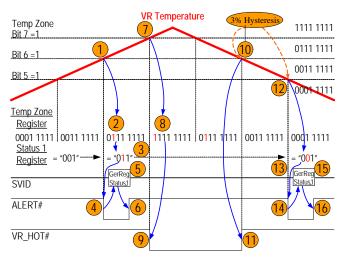

| 10h         | Status_1              | Data register read after ALERT# signal. Indicating if a VR rail has settled, has reached VR_HOT# condition or has reached I <sub>CCMAX</sub> .                                                                                   | 00h               |

| <b>11</b> h | Status_2              | Data register showing Status_2 communication.                                                                                                                                                                                    | 00h               |

| 12h         | Temperature<br>Zone   | Data register showing temperature zones that have been entered.                                                                                                                                                                  | 00h               |

| 1Ch         | Status_2_<br>LastRead | This register contains a copy of the Status_2 data that was last read with the GetReg (Status_2) command.                                                                                                                        | 00h               |

| 21h         | ICCMAX                | Data register containing the I <sub>CCMAX</sub> the platform supports, set at start-up by resistors R_PROG1. The platform design engineer programs this value during the design process. Binary format in amps, i.e., 100A = 64h | Set by<br>R_PROG1 |

| 24h         | SR-fast               | Slew Rate Normal. The fastest slew rate the platform VR can sustain. Binary format in mV/ $\mu$ s. i.e., OCh = 12mV/ $\mu$ s.                                                                                                    | Set by<br>R_PROG2 |

# TABLE 6. SUPPORTED DATA AND CONFIGURATION REGISTERS (Continued)

| INDEX | REGISTER<br>NAME                 | DESCRIPTION                                                                                                                                                                                                                                    | DEFAULT<br>VALUE                            |

|-------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 25h   | SR-slow                          | Default is 4x slower than normal. Binary format in mV/us. i.e., 03h = 3mV/µs. Can be configured by register 2Ah.                                                                                                                               | Set by<br>R_PROG2<br>and<br>Register<br>2Ah |

| 26h   | V <sub>BOOT</sub>                | If programmed by the platform, the VR supports $V_{BOOT}$ voltage during start-up ramp. The VR will ramp to $V_{BOOT}$ and hold at $V_{BOOT}$ until it receives a new SetVID command to move to a different voltage.                           | Set by<br>R_PROG2                           |

| 2Ah   | Slow slew rate selector          | 01h = 1/2 of fast slew rate<br>02h = 1/4 of fast slew rate<br>04h = 1/8 of fast slew rate<br>08h = 1/16 of fast slew rate                                                                                                                      | 02h                                         |

| 2Bh   | PS4 exit<br>latency              | Report 48µs                                                                                                                                                                                                                                    | 76h                                         |

| 2Ch   | PS3 exit<br>latency              |                                                                                                                                                                                                                                                | 38h                                         |

| 2Dh   | Enable to<br>VR_Ready<br>latency |                                                                                                                                                                                                                                                | C2h                                         |

| 30h   | V <sub>OUT</sub> max             | This register is programmed by the master and sets the maximum VID the VR will support. If a higher VID code is received, the VR will respond with "not supported" acknowledge.                                                                | B5h                                         |

| 31h   | VID Setting                      | Data register containing currently programmed VID voltage. VID data format.                                                                                                                                                                    | 00h                                         |

| 32h   | Power State                      | Register containing the current programmed power state.                                                                                                                                                                                        | 00h                                         |

| 33h   | Voltage<br>Offset                | Sets offset in VID steps added to the VID setting for voltage margining. Bit 7 is a sign bit, 0 = positive margin, 1 = negative margin. Remaining 7 bits are # VID steps for the margin. 00h = no margin, 01h = +1 VID step 02h = +2 VID steps | OOh                                         |

| 34h   | Multi VR<br>Config               | Data register that configures multiple VRs behavior on the same SVID bus.                                                                                                                                                                      | 00h                                         |

| 35h   | SetRegADR                        | Serial data bus communication address                                                                                                                                                                                                          | 00h                                         |

# **Key Component Selection**

#### **Inductor DCR Current-Sensing Network**

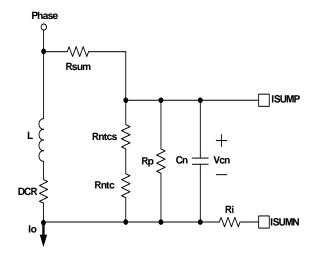

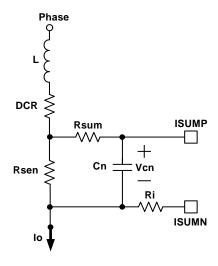

FIGURE 18. DCR CURRENT-SENSING NETWORK

Figure 18 shows the inductor DCR current-sensing network for a single phase solution. This loop monitors the voltage drop across the DCR creating by current flowing in the inductor and feeds that information to the ISL95813 for  $I_{MON}$  and load line purposes.

The summed inductor current information is presented to the capacitor  $\text{C}_n.$  Equations 8 thru 12 describe the frequency-domain relationship between inductor total current  $\text{I}_0(s)$  and  $\text{C}_n$  voltageV $_{\text{Cn}}(s)$ :

$$V_{Cn}(s) = \left(\frac{R_{ntcnet}}{R_{ntcnet} + R_{sum}} \times DCR\right) \times I_{o}(s) \times A_{cs}(s)$$

(EQ. 8)

$$R_{ntcnet} = \frac{(R_{ntcs} + R_{ntc}) \times R_p}{R_{ntcs} + R_{ntc} + R_p}$$

(EQ. 9)

$$A_{CS}(s) = \frac{1 + \frac{s}{\omega_L}}{1 + \frac{s}{\omega_{SNS}}}$$

(EQ. 10)

$$\omega_{L} = \frac{DCR}{L}$$

(EQ. 11)

$$\omega_{\text{sns}} = \frac{1}{\frac{R_{ntcnet} \times R_{sum}}{R_{ntcnet} + R_{sum}} \times C_{n}}$$

(EQ. 12)

In the DCR network, transfer function  $A_c(s)$  has unity gain at DC. As winding temperature increases, the DCR of the inductor increases which causes a higher reading of the DC current flowing through the inductor. To compensate for this effect, the resistance of the NTC  $R_{ntc}$  decreases as its temperature increases. Choosing the remaining components of the DCR network correctly ensures that the capacitor voltage  $V_{cn}$  accurately represents the total DC current through the inductor over the entire operating temperature range.

It is recommended when designing the DCR network to maintain  $V_{cn}$  as the highest feasible fraction of the voltage that is dropped

across the inductor's DCR in order to ensure the droop circuitry on chip has a high signal level to operate with.

While final component values should be fine tuned for a given application, a good starting point for the DCR temperature compensation network is as follows: Rsum =  $3.65 k\Omega$ , Rp =  $11 k\Omega$ , Rntcs =  $2.61 k\Omega$ , and Rntc =  $10 k\Omega$  (ERT-J1VR103J). To check the operation of the compensation network apply the full load DC current and record the output voltage both immediately and once the circuit has reached its thermal equilibrium. A well designed NTC network can limit the amount of drift on the output voltage to within 2 mV.

In order to achieve proper transient response it is also crucial that  $V_{Cn}(s)$  represents real-time  $I_o(s)$  of the controller. This is done by matching the pole and zero present in  $A_{cs}(s)$  to one another which sets the transfer function to unity gain for all frequencies. To ensure unity gain force  $\omega_L$  equal to  $\omega_{sns}$  and solve for  $C_n$  as seen in Equation 13.

$$C_{n} = \frac{L}{\frac{R_{ntcnet} \times R_{sum}}{R_{ntcnet} + R_{sum}} \times DCR}$$

(EQ. 13)

For example, with R<sub>sum</sub> =  $3.65k\Omega$ , R<sub>p</sub> =  $11k\Omega$ , R<sub>ntcs</sub> =  $2.61k\Omega$ , R<sub>ntc</sub> =  $10k\Omega$ , DCR =  $1m\Omega$ , and L =  $0.2\mu$ H, Equation 13 gives C<sub>n</sub> =  $0.088\mu$ F.

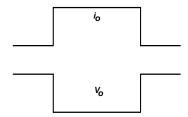

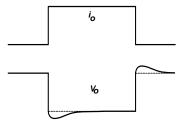

With proper compensator design, Figure 19 shows the expected load transient response waveforms. When the load current  $i_0$  has a square change, the output voltage  $V_0$  also has a square response.

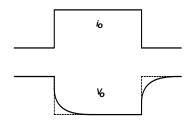

If  $C_n$  value is too large or too small,  $V_{Cn}(s)$  will not accurately represent real-time  $i_0(s)$  and the transient response of the controller will degrade. When  $C_n$  is too small,  $V_0$  will sag excessively as seen in Figure 20 and potentially trigger a system failure. Figure 21 shows the transient response when  $C_n$  is sized too large. In this case  $V_0$  will reach its expected droop voltage much too slowly with respect to the load insertion. Should a load release occur during this time there will be excessive overshoot on  $V_0$  which may potentially hurt CPU reliability.

FIGURE 19. DESIRED LOAD TRANSIENT RESPONSE WAVEFORMS

FIGURE 20. LOAD TRANSIENT RESPONSE WHEN  $\mathbf{C}_{\mathbf{n}}$  IS TOO SMALL

FIGURE 21. LOAD TRANSIENT RESPONSE WHEN C<sub>n</sub> IS TOO LARGE

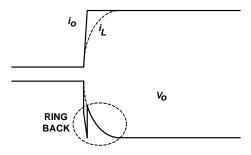

FIGURE 22. OUTPUT VOLTAGE RING BACK PROBLEM

Figure 22 gives an example of ring back on the output voltage during load transient response. Ring back occurs when the load current  $i_0$  has a fast step change, but the inductor current  $i_L$  cannot accurately track it. Instead,  $i_L$  responds in a first order fashion due to the nature of current loop. Instead of the output accurately responding to the load insertion the parasitic ESR and ESL properties of the output capacitors cause an abrupt dip in the voltage. However, the controller regulates  $V_0$  according to the droop current  $i_{droop}$ , which is a real-time representation of  $i_L$ ; therefore it pulls  $V_0$  back to the level dictated by  $i_L$ , introducing the ring back into the response. This phenomenon can be mitigated through the use of very low ESR and ESL ceramic capacitors for the output filter.

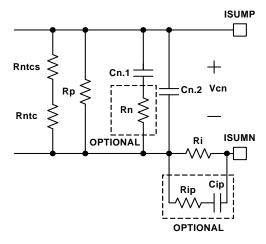

Figure 23 shows two circuits for ring back reduction that can be used in conjunction with low parasitic output filter components if need be. Normally  $C_n$ , the capacitor used to match the inductor time constant, is implemented through the parallel combination of two or more capacitors shown in Figure 23 as  $C_{n.1}$  and  $C_{n.2}$ . The first option to reduce ring back is to add resistor  $R_n$  in series to  $C_{n.1}$ . At steady state operation  $C_{n.1} + C_{n.2}$  provide the desired  $C_n$  capacitance calculated from Equation 11. At the beginning of  $C_n$  change however, the effective capacitance of the matching

network is less because  $R_n$  increases the impedance of the  $C_{n.1}$  branch. As Figure 20 explains,  $V_0$  tends to dip when  $C_n$  is too small which will reduce the amount of ring back seen during load transients. This effect is more pronounced when  $C_{n.1}$  is larger than  $C_{n.2}$  as well as when the value of  $R_n$  is increased. However, when designing the final circuit, care should be taken not to make  $R_n$  larger than necessary or make  $C_{n.1}$  much larger than  $C_{n.2}$  or else excessive ripple will be seen on  $V_{cn}$ . It is recommended to keep  $C_{n.2}$  greater than 2200pF and  $R_n$  in the range of only few ohms. The final values of  $C_{n.1}$ ,  $C_{n.2}$  and  $R_n$  should be determined through tuning the load transient response waveforms on an actual board to be used in the end application.

The second method for ring back reduction is to add the series combination of  $R_{ip}$  and  $C_{ip}$  in parallel with  $R_{i}$ . These components should be sized to provide a lower impedance path than  $\boldsymbol{R}_{\boldsymbol{i}}$  alone at the beginning of an io transient. During steady state operation Rin and Cip do not have any effect on the controller's operation. Through proper selection of Rip and Cip values, idroop can more closely resemble io rather than iL, and ring back on the output voltage will not be seen. The recommended value for  $\textbf{R}_{\text{ip}}$  is 100  $\!\Omega$  while the recommended range for  $\text{C}_{ip}$  is 100pF to 2000pF though final values should be tuned to the final end product board. It should be noted that the R<sub>ip</sub> -C<sub>ip</sub> branch may distort the i<sub>droop</sub> signal by introducing sharp spikes to the normally triangular waveform which may adversely affect the average value detection and therefore may affect OCP accuracy. Discretion is recommended when implementing this second ring back reduction method in order to maintain a robust system.

FIGURE 23. OPTIONAL CIRCUITS FOR RING BACK REDUCTION

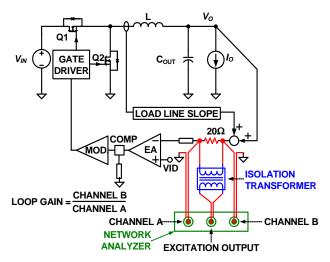

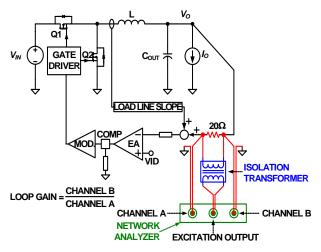

#### **Resistor Current-Sensing Network**