# **General TSB12LV23** (OHCILynx)

# Implementation Guide

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

# **Contents**

| 1   | Produ  | ıct Support                                               |             |

|-----|--------|-----------------------------------------------------------|-------------|

|     | 1.1    | Related Documentation                                     |             |

|     | 1.2    | World Wide Web                                            |             |

|     | 1.3    | TSB12LV23 (OHCI-Lynx) Function and Features               |             |

|     | 1.4    | TSB12LV23 Feature Set                                     |             |

|     | 1.5    | OHCILynx System Implementation                            |             |

|     | 1.6    | Drop-In Compatibility with the TSB12LV22                  |             |

|     |        | 1.6.1 Serial EEPROM Drop-In Compatibility Implementation  |             |

|     |        | 1.6.2 Connecting the Serial EEPROM                        |             |

| 2   | TSB12  | 2LV23 Implementation                                      | 7           |

|     | 2.1    | Passive Component Requirements                            |             |

|     |        | 2.1.1 Required Pullup/Pulldown Resistors                  | 7           |

| 3   | The P  | HY-Link Interface                                         | 8           |

|     |        |                                                           |             |

|     |        | ink Layer - TSB12LV23 OHCI-Lynx                           |             |

| 5   |        | ink Layer - Serial EEPROM                                 |             |

|     | 5.1    |                                                           |             |

|     |        | 5.1.1 Isolation vs Nonisolation                           |             |

|     |        | 5.1.2 Isolated Designs that Require Special Consideration |             |

|     |        | 5.1.3 Special Considerations for Bus Holder Isolation     | 12          |

|     |        | 5.1.4 Standard TSB12LV23 Considerations                   |             |

|     |        | 5.1.5 Power Requirements                                  |             |

|     | 5.2    | Design Check List                                         |             |

|     | J.Z    | 5.2.1 Standard Requirements                               |             |

|     |        | 5.2.2 Design Specific Requirements                        |             |

| A   |        | •                                                         |             |

| Ap  |        | x A PCI Bus Requirements                                  |             |

|     |        | PCI Bus Requirements                                      |             |

|     | A.2    |                                                           |             |

| Apı | pendix | k B Serial EEPROM                                         |             |

|     | B.1    | on to interiore                                           |             |

|     | B.2    | Serial Bus Interface                                      | B-1         |

| Apı | pendix | C Terminal Descriptions and Functions                     | <b>C-</b> 1 |

| 121 | C.1    | •                                                         |             |

|     |        | Terminal Functions                                        |             |

| Λ   |        |                                                           |             |

| Ap  |        | x D Definitions Used with the Application Examples        |             |

|     | 1/1    | IN THE COURT OF MAINTENANCE                               |             |

# **List of Figures**

|                   | SB12LV23 Block Diagram                                                                                                             |                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3 C               | Connecting the Serial EEPROM                                                                                                       | . 6                             |

| 4 L               | ink On                                                                                                                             | . 8                             |

| 5 C               | Clamping Voltage Diagram                                                                                                           | . 9                             |

| 6 T               | SB12LV23 Reset Block Diagram                                                                                                       | 10                              |

| 7 F               | Reset Schematic                                                                                                                    | 10                              |

| 8 S               | Serial EEPROM                                                                                                                      | 11                              |

| B-1               | GPIO2 and GPIO3                                                                                                                    | B-1                             |

| C-1               | 1 Terminal Assignments                                                                                                             | C-1                             |

| D-1               | 1 3-State Bidirectional Buffer                                                                                                     | D-1                             |

|                   | List of Tables  nternal Resistors and OHCI-Lynx Implementation                                                                     |                                 |

|                   | Required Pullup/Pulldown Resistors                                                                                                 |                                 |

|                   | Minimum and Typical PCI Pull-Up Resistor Values                                                                                    |                                 |

|                   | 2 32-Bit PCI Signal System Board Pull-Up Requirements                                                                              |                                 |

|                   | Registers and Bits Loadable through Serial EEPROM                                                                                  |                                 |

|                   | 2 Serial EEPROM Map                                                                                                                | B-2                             |

|                   |                                                                                                                                    |                                 |

|                   | 1 Signals Sorted by Pin Number                                                                                                     |                                 |

| C-3               | 2 Power Supply                                                                                                                     | C-2                             |

|                   | 2 Power Supply       0         3 PCI System       0                                                                                | C-2<br>C-3                      |

| C-4               | 2 Power Supply       0         3 PCI System       0         4 PCI Address and Data       0                                         | C-2<br>C-3<br>C-3               |

| C-4<br>C-5        | 2 Power Supply       0         3 PCI System       0         4 PCI Address and Data       0         5 PCI Interface Control       0 | C-2<br>C-3<br>C-3<br>C-4        |

| C-4<br>C-5<br>C-6 | 2 Power Supply       0         3 PCI System       0         4 PCI Address and Data       0                                         | C-2<br>C-3<br>C-3<br>C-4<br>C-4 |

# General TSB12LV23 (OHCILynx) Implementation Guide

John Mayberry

#### **ABSTRACT**

This implementation guide assists platform hardware developers designing with the TSB12LV23 1394 Open Host Controller Interface (OHCI) Link-Layer Controller (LLC), referred to herein as the OHCI-Lynx.

The document includes an overview of the TSB12LV23 function and features, terminal assignments and pinout illustrations, TSB12LV23 I/O electrical characteristics, identification of required passive components and recommendations for system implementation, and phy/link signal isolation considerations.

# 1 Product Support

#### 1.1 Related Documentation

The following list specifies product names, part numbers, and literature numbers of corresponding TI documentation.

- Galvanic Isolation of the IEEE 1394–1995 Serial Bus, Literature number SLLA001

- Reference Designs for Host System Boards (SLLA049), Adapter Cards, Literature number SLLA048 and SLLA052, and Mobile, Literature number SLLA047

- TSB12LV23 Data Manual, Literature number SLLS328

#### 1.2 World Wide Web

Our World Wide Web site at www.ti.com contains the most up-to-date product information, revisions, and additions. Users registering with TI&ME can build custom information pages and receive new product updates automatically via email.

#### 1.3 TSB12LV23 (OHCI-Lynx) Function and Features

The Texas Instruments TSB12LV23 is a PCI-to-1394 host controller compatible with the latest PCI local bus, PCI bus power management interface, IEEE 1394-1995, and 1394 open host controller interface (OHCI) specifications. The chip provides the IEEE 1394 link function, and is compatible with serial bus data rates of 100 Mbits/s, 200 Mbits/s, and 400 Mbits/s.

As required by the 1394 Open Host Controller Interface (OHCI) and IEEE 1394A Specifications, internal control registers are memory-mapped and non-prefetchable. The PCI configuration header is accessed through configuration cycles specified by PCI, and provides Plug-and-Play (PnP) compatibility. Furthermore, the TSB12LV23 is compliant with the PCI Bus Power Management Interface Specification, per the PC 98 requirements. TSB12LV23 supports the D0, D2, and D3 power states.

The TSB12LV23 design provides PCI bus master bursting, and is capable of transferring a cacheline of data at 132 Mbytes/s after connection to the memory controller. Since PCI latency can be large even on a PCI Revision 2.1 system, deep FIFOs are provided to buffer 1394 data.

The TSB12LV23 provides physical write posting buffers and a highly tuned physical data path for SBP-2 performance. The TSB12LV23 also provides multiple isochronous contexts, multiple cacheline burst transfers, advanced internal arbitration, and bus holding buffers on the PHY/Link interface, thus, making the TSB12LV23 the best-in-class 1394 OHCI solution.

An advanced CMOS process is used to achieve low power consumption while operating at PCI clock rates up to 33 MHz.

#### 1.4 TSB12LV23 Feature Set

- IEEE1394 Open Host Controller Interface Specification 1.0 Compliant

- IEEE1394–1995 and 1394.A Compliant

- PCI Local Bus Specification Revision 2.1 Compliant and PCI 2.2 ready

- PCI Power Management Compliant

- 3.3-V Core Logic with Universal PCI Interface Compatible with 3.3-V and 5-V PCI Signalling Environment

- Supports Serial Bus Data Rates of 100, 200, and 400Mbit/s

- Provides Bus-Hold Buffers on Physical Interface for Low-Cost Single Capacitor Isolation

- Supports Physical Write Posting of up to Three Outstanding Transactions

- Serial ROM Interface Supports 2-Wire Devices

- Supports External Cycle Timer Control for Customized Synchronization

- Implements PCI Burst Transfers and Deep FIFOs to Tolerate Large Host Latency

- Provides Two General-Purpose I/Os

- Fabricated in Advanced Low-Power CMOS Process

- Packaged in 100-Pin (PZ) LQFP Package

- Supports CLKRUN

- Drop-In Replacement for the TSB12LV22

- Supports PCI and CardBus Applications

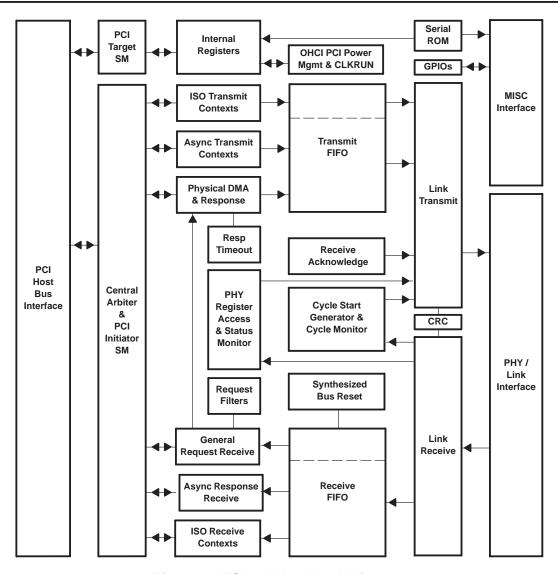

Figure 1. TSB12LV23 Block Diagram

# 1.5 OHCILynx System Implementation

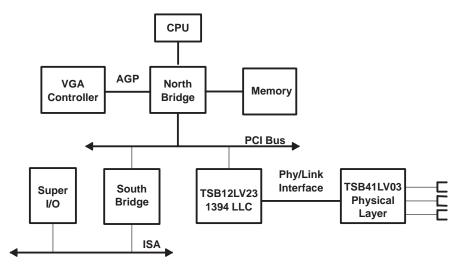

Figure 1 illustrates a platform using the TSB12LV23, which, along with the TSB41LV03, provides the necessary interface to implement a three-port IEEE1394 node.

Figure 2. Typical System Architecture

#### 1.6 Drop-In Compatibility with the TSB12LV22

The TSB12LV23 can be placed on a pad layout for the TSB12LV22 with no changes. It uses the exact same WDM drivers as the TSB12LV22 (i.e., 1394bus.sys and ohci1394.sys), which makes it a direct replacement for the TSB12LV22.

The TSB12LV23 is designed to be drop-in compatible with OHCI-Lynx designs. Some I/Os implement weak pullup or pulldown resistors for drop-in compatibility with OHCI-Lynx. These internal resistors and OHCI-Lynx implementation requirements are noted in the following table.

| TERMINAL         |     | WEAK RESISTOR | DROP-IN COMPATIBILITY NOTE                        |

|------------------|-----|---------------|---------------------------------------------------|

| TERMINAL NAME    | NO. | WEAR RESISTOR | DROF-IN COMPATIBILITY NOTE                        |

| CARDBUS/CYCLEOUT | 77  | Pullup        | OHCI-Lynx CYCLEOUT must be tied high or pulled up |

| CLKRUN           | 7   | Pulldown      | OHCI-Lynx RSVD must be unconnected or pulled down |

| RST              | 10  | Pullup        | OHCI-Lynx TEST EN must be tied high               |

Table 1. Internal Resistors and OHCI-Lynx Implementation

Refer, also, to the *TSB12LV22 (OHCI-Lynx) Implementation Guide* (literature number: SLLA025) for more information.

#### 1.6.1 Serial EEPROM Drop-In Compatibility Implementation

There has been no major change in the implementation of the serial EEPROM. However, The EEPROM programming code will need to be upgraded for the new TSB12LV23 register set.

The EEPROM is used to load the system specific registers, such as the GUID. The data file, which loads the EEPROM, will need to be modified. However, for new boards, the EEPROM should be programmed with the modified data from the start.

For retrofitted boards, the EEPROM should be reprogrammed so it loads all ,of the system specific registers correctly. If the EEPROM is being programmed from BIOS, programming the EEPROM is not a concern.

**NOTE:** Do not set GlobalByte swap bit via the EEPROM data file. This will cause problems (bit 0 at offset 13)

In Addition, use TI's latest version of the EEPROM software to program the EEPROM, and follow these steps.

The EEPROMs of all modified boards must be written, as the new registers beyond EEPROM word address 0xFh are written by the TSB12LV23 and the default value 0xFFh will set the GlobalSwap bit, which will effect operation. The following list of steps is a general procedure and should be used when modifying a PCB from the TSB12LV22 to the TSB12LV23.

**NOTE:** The following procedure assumes that the EEPROM has been previously programmed with valid data. If the EEPROM has not previously been programmed, use the TSB12LV23 data file as a template to edit and program the EEPROM accordingly.

1. After replacing the TSB12LV22 with the TSB12LV23, dump the current contents of the serial EEPROM using TI's EEPROM utility:

```

eelynx /d temp.dat

```

2. Edit the temp.dat file, appending the following register data to the end of the file:

```

010 0x10 ;00010000 Link Enhancement Byte 1

011 0x00 ;00000000 PCI Misc Byte 0

012 0x24 ;00100100 PCI Misc Byte 1

013 0x00 ;00000000 PCI OHCI Control Byte 0

014 0x00 ;00000000 CIS Offset

```

3. Program the EEPROM with the new file using the EELynx utility:

```

eelynx /p temp.dat

```

This procedure will set the proper defaults for the TSB12LV23 and will maintain the existing GUID as previously programmed.

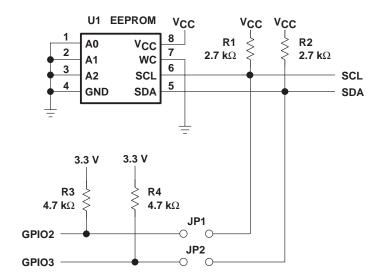

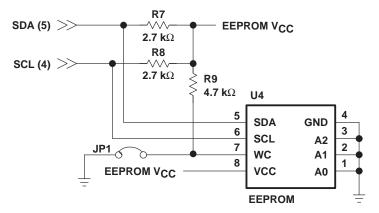

### 1.6.2 Connecting the Serial EEPROM

Implementation requires the connection of GPIO2 to SCL, and GPIO3 to SDA to enable on-board EEPROM programming.

- It is recommended that header and jumpers for SCL and SDA lines be used to meet 1394.a security requirements. Jumpers on the EEPROM with write control can also be used.

- Another alternative is to use a serial EEPROM with software write protection (SGS M34C02).

Figure 3. Connecting the Serial EEPROM

# 2 TSB12LV23 Implementation

# 2.1 Passive Component Requirements

#### 2.1.1 Required Pullup/Pulldown Resistors

Several signals on the TSB12LV23 require a pullup or pulldown resistor. Table 2 provides a list of required resistors.

Table 2. Required Pullup/Pulldown Resistors (see Note 1)

| SIGNAL   | RESISTOR            | RECOMMENDED VALUE $(\Omega)$ | CONDITION                                                                                                                                            |

|----------|---------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA      | Pullup              | 2.7 k                        | Required if implementation includes a serial EEPROM.                                                                                                 |

| SCL      | Pullup              | 2.7 k                        | Required if implementation includes a serial EEPROM.                                                                                                 |

| RST      | Pullup              | 4.7 k                        | If the design does not use the D3_cold Power Management, then this terminal can be pulled up or $\overline{RST}$ can be connected to G_RST directly. |

| ISOLATED | Pullup<br>(Default) | 4.7 k                        | Required when <b>not</b> implementing bus holder isolation                                                                                           |

|          | Pulldown            | 220                          | Required when bus holder isolation is implemented                                                                                                    |

| CYCLEIN  | Pullup              | 4.7 k                        | Required if not implementing optional external 8-kHz clock.                                                                                          |

| GPI02    | Pulldown            | 220                          | Required                                                                                                                                             |

| GPI03    | Pulldown            | 220                          | Required                                                                                                                                             |

NOTE 1: All pullup/pulldown resistor value recommendations are provided as guidelines only. The best value for an individual design may vary depending upon board characteristics, standard design rules and practices, etc.

#### 3 The PHY-Link Interface

The PHY-Link interface follows the IEEE 1394-1995 and 1394.a standards. No isolation is implemented in this schematic. The PHY and Link operate with common power and ground planes.

The schematic shows no adjustment for EMI considerations. To help minimize EMI, we suggest including a  $0-\Omega$  resistor on the SCLK signal as close as possible to the PHY. If EMI issues are a concern, the value of this resistor can be adjusted to reduce emissions. This will also reduce reflections that may occur when the distance between the PHY and Link is large (greater than 4 inches.)

The SCLK is a 49.152-MHz clock provided by the PHY to the Link. SCLK is essential for transactions on the PHY-Link interface as well as transactions within the Link.

The LREQ, or Link Request, signal is an input to the PHY from the Link. The Link uses this to initiate a service request to the PHY. CTL0 and CTL1 are bidirectional signals used to control communication between the PHY and the Link. These terminals should be directly connected between the PHY and Link.

Both the TSB12LV23 (Link layer) and the TSB41LV03 (Phy) are 400-Mbps devices, which use terminals D0–D7 to transport data bidirectionally, and should be connected directly to each other respectively (i.e., D0  $\leftrightarrow$  D0 . . . D7  $\leftrightarrow$  D7).

The Link's PHY\_LPS (Link Power Status) terminal is asserted to indicate that the Link is powered on. The LPS input on the PHY can be tied to either the Link layer's PHY\_LPS terminal or the Link layer's VCC. In addition, the line connecting the Link's PHY\_LPS terminal with the PHY's LPS terminal should be pull down to ground through a  $1-k\Omega$  resistor.

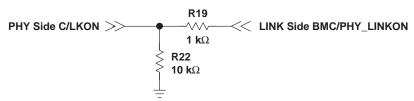

As is shown in Figure 4, the BMC/PHY\_LINKON terminal on the TSB12LV23 is connected to the TSB41LV03 C/LKON terminal through a 1-k $\Omega$  series resistor and 10-k $\Omega$  pulldown resistor on the TSB41LV03 side. The PHY's LKON signal is used to activate (wake) the Link when the Link is not active. This signal is driven low as long as the Link is not active.

Figure 4. Link On

All of the above PHY-Link interface signals could also be connected to test header that would provide test points for new prototype.

8 *SLLA045*

# 4 The Link Layer - TSB12LV23 OHCI-Lynx

The TSB12LV23 is a 400-Mbps Link-layer specifically designed with power management and CARDBUS features.

All of the 3.3-V  $V_{CC}$  power terminals on the TSB12LV23 should be coupled together and grounded through a series of high-frequency decoupling capacitors.

- Place one 0.01-μF and one 0.1-μF capacitor as closely as possible to each power terminal on the Link. This will help minimize switching noise.

- Also use a single 47-μF capacitor to reduce dc ripple.

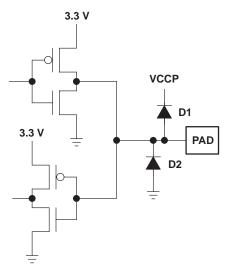

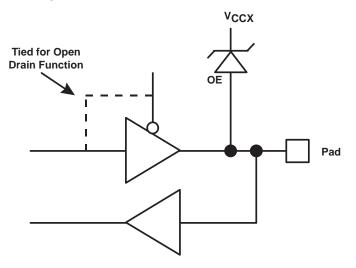

The VCCP power terminals provide a voltage clamping rail for 5-V tolerant inputs. The VCCP voltage is determine by the PCI bus voltage. Figure 5 illustrates the voltage clamping rail.

Figure 5. Clamping Voltage Diagram

If the design uses a 5-V supply, the VCCP terminals should be tied to the 5-V supply. Otherwise, VCCP should be connected to the 3.3-V.

The ISOLATED terminal is used to the enable bus holders for isolated designs. However, for most designs this is not required.

- To disable the bus-holders connect the  $\overline{\text{ISOLATED}}$  terminal to 3.3 V through a 4.7-k $\Omega$  pullup resistor.

- To enable the bus-holders connect the  $\overline{\text{ISOLATED}}$  terminal to GND through a 220- $\Omega$  pulldown resistor.

The CARDBUS/CYCLEOUT terminal is sampled when G\_RST is asserted, and it selects between the PCI and CardBus buffers. After reset, this terminal may also function as CYCLEOUT which provides an 8-kHz cycle timer synchronization signal.

- To use the PCI bus buffers this terminal should be left unconnected, and an internal pullup resistor will enable the PCI buffers.

- To enable the CardBus buffers this terminal should be pulled down with a  $220-\Omega$  resistor. It is important that a weak pulldown resistor be used if the design is going to use the CYCLEOUT feature.

The CYCLEIN terminal can be used to receive an optional external 8-kHz clock used as a cycle timer, which provides synchronization with other system devices. If not implemented, a 4.7-k $\Omega$  pullup resistor should be used to tie this terminal to 3.3 V.

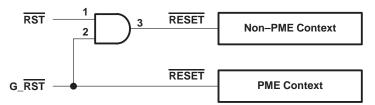

The TSB12LV23's G\_RST terminal allows for retaining context from a D3 to D0 transition when the PCI interface may transition from B3 to B0 and issue a PCI reset. The TSB12LV23 resets are illustrated in Figure 6.

Figure 6. TSB12LV23 Reset Block Diagram

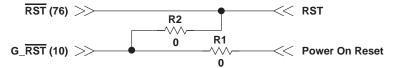

If the design supports D3\_Wake, then the  $\overline{G_RST}$  terminal provides the hardware reset at power on, while the  $\overline{RST}$  terminal should be connected to the PCI Bus  $\overline{RST}$ , which will provides resets that retain the PME context.

For designs that will not support D3\_Wake, the  $\overline{RST}$  terminal can either be pulled up to 3.3 V through a 4.7-k $\Omega$  resistor or tied together with the  $\overline{G}$ \_RST terminal. An example implementation is shown in Figure 7.

NOTE: For normal operation populate R2 and do not populate R1 For Mobile or D3\_Wake operation populate R1 and do not populate R2

#### Figure 7. Reset Schematic

The CLKRUN terminal is used to turn the clock on and off. This is useful in mobile design where conserving power is important. When implementing CLKRUN, this terminal is connected to external circuitry that provides a common CLKRUN control signal. If the clock is never turned off, then this terminal should be left unconnected and an internal pulldown resistor will keep the clock active.

The GPIO2 and GPIO3 are general-purpose I/O terminals that should each be pulled down to GND through a 220- $\Omega$  resistors.

For more information on the TSB12LV23, consult the TI data manual, *TSB12LV23 (OHCI-LYNX) IEEE 1394-1995 Link-Layer Controller* (literature number SLLS328).

# 5 The Link Layer - Serial EEPROM

The Serial EEPROM provides a convenient mechanism to load system-specific data and is detected at reset via SDA and SCL terminals.

The following are the types of data stored in the EEPROM:

- PCI: Max latency, min grant, subsystem VID, subsystem ID, Link enhancements, miscellaneous control, and CIS offset

- OHCI: GUID, HCControl.programPhyEnable

The serial EEPROM is required for adapter cards, but it is optional for implementations where the BIOS is used to load GUID and other system-specific registers.

SDA and SCL should each be pulled up to EEPROM  $V_{CC}$  through 2.7-k $\Omega$  resistors, and then connected to the EPROM's SDA and SCL terminals respectively (as is illustrated in Figure 8). If no serial EEPROM is used, then both the SDA and SCL terminals should be connected to ground through 220- $\Omega$  pulldown resistors.

Figure 8. Serial EEPROM

If the EEPROM has a write enable terminal, it should be connected to EEPROM  $V_{CC}$  with a pullup resistor. In addition, a jumper to GND should be connected in series the pullup, as illustrated in Figure 8. This will allow the EEPROM to be write-enabled and write-disabled.

#### 5.1 Isolation Considerations

#### 5.1.1 Isolation vs Nonisolation

- Isolation provides protection against data corruption and/or physical harm that can be caused by ground potential differences between nodes.

- Typical PC usage models do not require isolation (i.e., all connected devices share a common green-wire ground).

**NOTE:** LAN type environments may be a special case

#### 5.1.2 Isolated Designs that Require Special Consideration

- PHY/Link signal isolation

- Phy/Link ground return

- Isolated power supply

#### 5.1.3 Special Considerations for Bus Holder Isolation

Phy/Link interface signals must be ac coupled.

Single 0.001-μF (non-polarized) decoupled capacitor per signal SCLK, LREQ, CTL0, CTL1, D0 – D7 LPS and LINKON require additional considerations

A current path must be provided between the PHY ground and the Link ground to ensure signal integrity.

#### 5.1.4 Standard TSB12LV23 Considerations

- ISOLATED terminal must be pulled down to enable the bus holders

- VCCP clamp should be tied to 5 V only if a PCI-Bus voltage is 5 V. Otherwise,

VCCP should be tied to 3.3 V.

- The serial EEPROM is required for adapter cards.

#### 5.1.5 Power Requirements

- Alternate power providers

- Requires isolated load output from the power supply Alternate dc-to-dc converter, but expensive for power densities required

- Single diode isolation of power source Standard power provider or alternate power provider with launch voltage > 20 V requires per power diode isolation.

- Per port current limit (1.5 A) required.

- PHY decoupling capacitor considerations apply.

#### 5.1.6 Implementing Galvanic Isolation

For detailed information on galvanic isolation, refer to the *Galvanic Isolation Applications Note* (literature number: SLLA011).

12

#### 5.2 Design Check List

#### 5.2.1 Standard Requirements

- Required pullup and pulldown resistors

- Decoupling capacitors

- Clamping voltage VCCP

- ISOLATED terminal must be pulled up to disable the bus holders

#### 5.2.2 Design Specific Requirements

- Drop-in replacement for the TSB12LV22

- RST should either be pulled up or tied directly to G\_RST terminal (RST was TEST\_EN on the TSB12LV22).

- CARDBUS/CYCLEOUT is pulled up

- CLKRUN unconnected

- Serial EEPROM has been reprogrammed or programmed with the GlobalByte swap bit 0 at offset 13h has been cleared (set = 0)

- Adapter card design

- Serial EEPROM required

- 3.3-V supply for Link Core

- CLKRUN unconnected

- RST should either be pulled up or tied directly to G\_RST terminal (RST was TEST\_EN on the TSB12LV22).

- Mobile or Wake D3\_cold Design

- 3.3-V EEPROM if required

- VCCP = 3.3 V

- G\_RST and RST are configured for D3\_cold

- CLKRUN has optional 0-Ω resistor or has been connected to external CLKRUN circuitry

- Isolated Design

In addition to one of the previous selections, this design will also be isolated.

- ISOLATED terminal must be pulled down to enable the bus holders

- Single 0.001-μF (non-polarized) decoupled capacitor per signal SCLK, LREQ, CTL0, CTL1, D0 – D7 LPS and LINKON require additional considerations

- PHY/Link signal isolation

- Phy/Link ground return

- Isolated power supply

# Appendix A PCI Bus Requirements

#### A.1 PCI Bus Requirements

The following paragraph summarizes paragraph 4.3.3 of the PCI Local Bus Specification Revision 2.1 and is provided for reference only. Please refer to the PCI Local Bus Specification for a full discussion on pull-up resistors required for PCI local bus implementations.

All PCI control signals require pullup resistors on the motherboard to guarantee that they are at a stable state when no agent is actively driving the signal. Pullups should be implemented on the motherboard only. Expansion boards or add-in cards should not provide pullup resistors for the PCI control signals. The following PCI signals require pullup resistors:

- FRAME

- TRDY

- IRDY

- DEVSEL

- STOP

- SERR

- PERR

- LOCK

- INTA

- INTB

- INTC

- INTD

- REQ64 (when used)

- ACK64 (when used)

Pullups are not required on point-to-point or shared 32-bit signals, as bus parking guarantees their stability. If the 64-bit data path expansion signals, AD(63:32), C/BE(7:4)#, and PAR64, are connected they must be pulled-up as well. Table xxx lists the 32-bit PCI signals implemented on the TSB12LV23 that require pullup resistors on the system board.

Minimum and maximum values for required PCI pullup resistors can be calculated using the following formulas:

$$R_{min} = \frac{V_{CC(min)} - V_{ol}}{I_{ol} + (16 \times I_{il})}$$

Where 16 = maximum number of loads

$$R_{min} = \frac{V_{CC(min)} - V_{ol}}{num\_loads \times I_{il}}$$

Where:

$$V_X = 2.7V$$

for 5-V signaling  $V_X = 0.7 \ V_{CC}$  for 3.3-V signaling

Minimum and typical values for both 5-V and 3.3-V signaling environments are shown in the following table.

Table A-1. Minimum and Typical PCI Pull-Up Resistor Values

| SIGNALING<br>RAIL | R <sub>min</sub> | R <sub>typ</sub>               | R <sub>max</sub>                           |

|-------------------|------------------|--------------------------------|--------------------------------------------|

| 5 V               | 963 Ω            | $2.7~\mathrm{k}\Omega\pm10\%$  | Dependent on number of loads (see formula) |

| 3.3 V             | 2.42 kΩ          | $8.2 \text{ k}\Omega \pm 10\%$ | Dependent on number of loads (see formula) |

Table A-2. 32-Bit PCI Signal System Board Pull-Up Requirements

| PCI<br>SIGNAL | PULL-UP<br>VOLTAGE |

|---------------|--------------------|

| FRAME         | V <sub>CCP</sub>   |

| TRDY          | V <sub>CCP</sub>   |

| ĪRDY          | V <sub>CCP</sub>   |

| DEVSEL        | VCCP               |

| STOP          | VCCP               |

| SERR          | VCCP               |

| PERR          | VCCP               |

| ĪNTA          | V <sub>CCP</sub>   |

#### A.2 Bypass Capacitors

Standard design rules for the supply bypass should be followed. Low inductance ceramic chip capacitors are best for bypass capacitors. A value of 0.1  $\mu F$  is recommended for each of the power supply pins:  $V_{CC}$ ,  $V_{CCS}$ ,  $V_{CCP}$ .

# Appendix B Serial EEPROM

#### **B.1** GPIO Interface

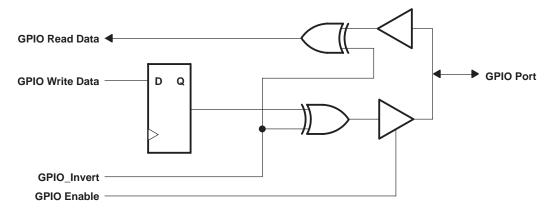

The general-purpose input/output (GPIO) interface consists of two GPIO ports. GPIO2 and GPIO3 power up as general-purpose inputs and are programmable via the GPIO control register. B–1 shows the schematic for GPIO2 and GPIO3 implementation.

GPIO0 and GPIO1 are not implemented in the TSB12LV23. The terminals for these legacy GPIOs from the TSB12LV23 have been dedicated to BMC/LINKON and LPS, respectively.

Figure B-1. GPIO2 and GPIO3

#### **B.2** Serial Bus Interface

The TSB12LV23 provides a serial bus interface to initialize the 1394 global unique ID register and a few PCI configuration registers through a serial EEPROM. The TSB12LV23 communicates with the serial EEPROM via the 2-wire serial interface.

After power-up the serial interface initializes the locations listed in Table B–1. While the TSB12LV23 is accessing the serial ROM, all incoming PCI slave accesses are terminated with retry status. Table B–2 shows the serial ROM memory map required for initializing the TSB12LV23 registers.

| Table B 11 Registers and bits Esdadasis an edgit condition in |                                        |                            |  |  |  |  |

|---------------------------------------------------------------|----------------------------------------|----------------------------|--|--|--|--|

| OFFSET                                                        | REGISTER                               | BITS LOADED<br>FROM EEPROM |  |  |  |  |

| OHCI register (24h)                                           | 1394 GlobalUniqueIDHi                  | 31–0                       |  |  |  |  |

| OHCI register(28h)                                            | 1394 GlobalUniqueIDLo                  | 31–0                       |  |  |  |  |

| OHCI register (50h)                                           | Host control register                  | 23                         |  |  |  |  |

| PCI register (2Ch)                                            | PCI subsystem ID                       | 15–0                       |  |  |  |  |

| PCI register (2Dh)                                            | PCI vendor ID                          | 15–0                       |  |  |  |  |

| PCI register (3Eh)                                            | PCI maximum latency, PCI minimum grant | 15–0                       |  |  |  |  |

| PCI register (F4h)                                            | Link enhancements control register     | 13, 12, 9, 8, 7, 2, 1      |  |  |  |  |

| PCI register (F0h)                                            | PCI miscellaneous register             | 15, 13, 10, 5–0            |  |  |  |  |

| PCI register (40h)                                            | PCI OHCI register                      | 0                          |  |  |  |  |

Table B-1. Registers and Bits Loadable through Serial EEPROM

Table B-2. Serial EEPROM Map

| BYTE<br>ADDRESS | BYTE DESCRIPTION                                    |                                           |                                   |               |                          |                                                 |                                          |                                      |  |  |  |

|-----------------|-----------------------------------------------------|-------------------------------------------|-----------------------------------|---------------|--------------------------|-------------------------------------------------|------------------------------------------|--------------------------------------|--|--|--|

| 00              | PCI maximum latency (0h) PCI_minimum grant (0h)     |                                           |                                   |               |                          |                                                 |                                          |                                      |  |  |  |

| 01              |                                                     |                                           |                                   |               |                          |                                                 |                                          |                                      |  |  |  |

| 02              | PCI vendor ID (msbyte)                              |                                           |                                   |               |                          |                                                 |                                          |                                      |  |  |  |

| 03              | PCI subsystem ID (Isbyte)                           |                                           |                                   |               |                          |                                                 |                                          |                                      |  |  |  |

| 04              |                                                     |                                           |                                   | PCI           | subsysten                | n ID                                            |                                          |                                      |  |  |  |

| 05              | [7] Link_enhancement- Control.enab_unfair           | [6]<br>HCControl.<br>ProgramPhy<br>Enable | [5]<br>RSVD                       | [4]<br>RSVD   | [3]<br>RSVD              | [2] Link_enhancement- Control.enab_ insert_idle | [1] Link_enhancement- Control.enab_accel | [0]<br>RSVD                          |  |  |  |

| 06              |                                                     |                                           | -                                 | Mini          | ROM add                  | ress                                            |                                          |                                      |  |  |  |

| 07              |                                                     |                                           | 13                                | 394 Global    | UniqueIDI                | Hi (Isbyte 0)                                   |                                          |                                      |  |  |  |

| 08              |                                                     |                                           | 1                                 | 394 Globa     | lUniqueID                | Hi (byte 1)                                     |                                          |                                      |  |  |  |

| 09              |                                                     |                                           | 1                                 | 394 Globa     | lUniqueID                | Hi (byte 2)                                     |                                          |                                      |  |  |  |

| 0A              | 1394 GlobalUniqueIDHi (msbyte 3)                    |                                           |                                   |               |                          |                                                 |                                          |                                      |  |  |  |

| 0B              |                                                     |                                           | 13                                | 94 Global     | UniqueIDl                | _o (Isbyte 0)                                   |                                          |                                      |  |  |  |

| 0C              |                                                     |                                           | 1                                 | 394 Globa     | IUniqueID                | Lo (byte 1)                                     |                                          |                                      |  |  |  |

| 0D              |                                                     |                                           | 1                                 | 394 Globa     | IUniqueID                | Lo (byte 2)                                     |                                          |                                      |  |  |  |

| 0E              |                                                     |                                           | 139                               | 94 Globall    | JniqueIDL                | o (msbyte 3)                                    |                                          |                                      |  |  |  |

| 0F              |                                                     |                                           |                                   | (             | Checksum                 |                                                 |                                          |                                      |  |  |  |

| 10              | [15]<br>RSVD                                        | [14]<br>RSVD                              | [13–<br>AT thre                   |               | [11]<br>RSVD             | [10]<br>RSVD                                    | [9]<br>Enable audio<br>timestamp         | [8]<br>Enable<br>DV CIP<br>timestamp |  |  |  |

| 11              |                                                     |                                           | [4]<br>Disable<br>Target<br>Abort | [3]<br>GP2IIC | [2]<br>Disable SCLK gate | [1]<br>Disable PCI gate                         | [0]<br>Keep PCI                          |                                      |  |  |  |

| 12              | [15] [14] [13] [12] PME D3 Cold RSVD PME Support D2 |                                           | [12]<br>RSVD                      | [11]<br>RSVD  | [10]<br>D2 support       | [9]<br>RSVD                                     | [8]<br>RSVD                              |                                      |  |  |  |

| 13              | [7]<br>RSVD                                         | [6]<br>RSVD                               | [5]<br>RSVD                       | [4]<br>RSVD   | [3]<br>RSVD              | [2]<br>RSVD                                     | [1]<br>RSVD                              | [0]<br>Global<br>swap                |  |  |  |

| 14              |                                                     |                                           |                                   | CIS           | offset add               | ress                                            |                                          |                                      |  |  |  |

| 15–1E           |                                                     |                                           |                                   |               | RSVD                     |                                                 |                                          |                                      |  |  |  |

| 1F              |                                                     |                                           |                                   |               | RSVD                     |                                                 |                                          |                                      |  |  |  |

# **Appendix C** Terminal Descriptions and Functions

#### **C.1 Terminal Assignments**

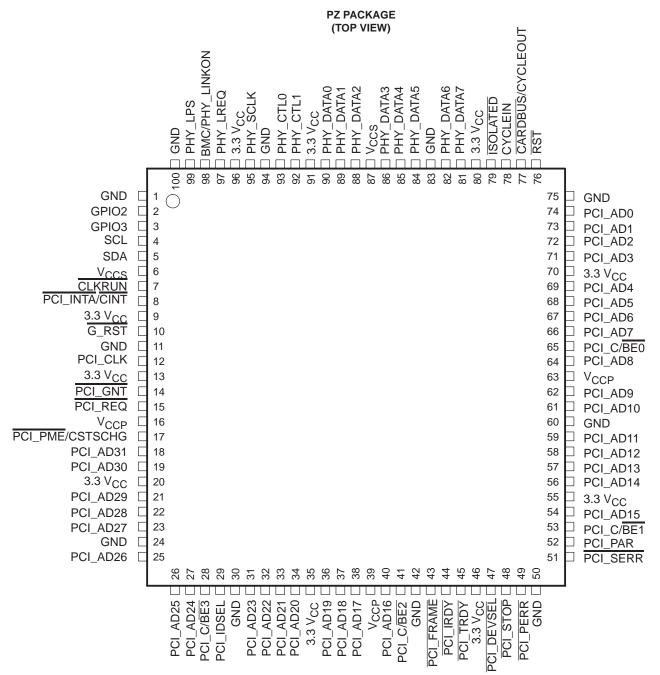

This section provides the terminal assignments for the TSB12LV23.

Figure C-1. Terminal Assignments

Table C-1. Signals Sorted by Pin Number

| NO. | TERMINAL NAME       |

|-----|---------------------|-----|---------------------|-----|---------------------|-----|---------------------|

| 1   | GND                 | 26  | PCI_AD25            | 51  | PCI_SERR            | 76  | RST                 |

| 2   | GPIO2               | 27  | PCI_AD24            | 52  | PCI_PAR             | 77  | CARDBUS/CYCLEOUT    |

| 3   | GPIO3               | 28  | PCI_C/BE3           | 53  | PCI_C/BE1           | 78  | CYCLEIN             |

| 4   | SCL                 | 29  | PCI_IDSEL           | 54  | PCI_AD15            | 79  | ISOLATED            |

| 5   | SDA                 | 30  | GND                 | 55  | 3.3 V <sub>CC</sub> | 80  | 3.3 V <sub>CC</sub> |

| 6   | VCCP                | 31  | PCI_AD23            | 56  | PCI_AD14            | 81  | PHY_DATA7           |

| 7   | CLKRUN              | 32  | PCI_AD22            | 57  | PCI_AD13            | 82  | PHY_DATA6           |

| 8   | PCI_INTA/CINT       | 33  | PCI_AD21            | 58  | PCI_AD12            | 83  | GND                 |

| 9   | 3.3 V <sub>CC</sub> | 34  | PCI_AD20            | 59  | PCI_AD11            | 84  | PHY_DATA5           |

| 10  | G_RST               | 35  | 3.3 V <sub>CC</sub> | 60  | GND                 | 85  | PHY_DATA4           |

| 11  | GND                 | 36  | PCI_AD19            | 61  | PCI_AD10            | 86  | PHY_DATA3           |

| 12  | PCI_CLK             | 37  | PCI_AD18            | 62  | PCI_AD9             | 87  | V <sub>CCP</sub>    |

| 13  | 3.3 V <sub>CC</sub> | 38  | PCI_AD17            | 63  | VCCP                | 88  | PHY_DATA2           |

| 14  | PCI_GNT             | 39  | VCCP                | 64  | PCI_AD8             | 89  | PHY_DATA1           |

| 15  | PCI_REQ             | 40  | PCI_AD16            | 65  | PCI_C/BE0           | 90  | PHY_DATA0           |

| 16  | VCCP                | 41  | PCI_C/BE2           | 66  | PCI_AD7             | 91  | 3.3 V <sub>CC</sub> |

| 17  | PCI_PME/CSTSCHG     | 42  | GND                 | 67  | PCI_AD6             | 92  | PHY_CTL1            |

| 18  | PCI_AD31            | 43  | PCI_FRAME           | 68  | PCI_AD5             | 93  | PHY_CTL0            |

| 19  | PCI_AD30            | 44  | PCI_IRDY            | 69  | PCI_AD4             | 94  | GND                 |

| 20  | 3.3 V <sub>CC</sub> | 45  | PCI_TRDY            | 70  | 3.3 V <sub>CC</sub> | 95  | PHY_SCLK            |

| 21  | PCI_AD29            | 46  | 3.3 V <sub>CC</sub> | 71  | PCI_AD3             | 96  | 3.3 V <sub>CC</sub> |

| 22  | PCI_AD28            | 47  | PCI_DEVSEL          | 72  | PCI_AD2             | 97  | PHY_LREQ            |

| 23  | PCI_AD27            | 48  | PCI_STOP            | 73  | PCI_AD1             | 98  | PHY_LINKON          |

| 24  | GND                 | 49  | PCI_PERR            | 74  | PCI_AD0             | 99  | PHY_LPS             |

| 25  | PCI_AD26            | 50  | GND                 | 75  | GND                 | 100 | GND                 |

#### **C.2 Terminal Functions**

The terminals are grouped in tables by functionality, such as PCI system function, power supply function, etc. The terminal numbers are also listed for convenient reference.

Table C-2. Power Supply

| TERMINAL            |                                                  | 1/0 | DESCRIPTION                                                                                           |  |  |  |

|---------------------|--------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                | NO.                                              | 1/0 | DESCRIPTION                                                                                           |  |  |  |

| GND                 | 1, 11, 24, 30,<br>42, 50, 60, 75,<br>83, 94, 100 | ı   | Device ground terminals                                                                               |  |  |  |

| 3.3 V <sub>CC</sub> | 9, 13, 20, 35,<br>46, 55, 70, 80,<br>91, 96      | _   | 3.3-V power supply terminals                                                                          |  |  |  |

| V <sub>CCP</sub>    | 6, 16, 39, 63,<br>87                             | I   | PCI signaling clamp voltage power input. PCI signals are clamped per the PCI Local Bus Specification. |  |  |  |

# Table C-3. PCI System

| TERMINAL      |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|---------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME          | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| PCI_CLK       | 12  | ı   | PCI bus clock. Provides timing for all transactions on the PCI bus. All PCI signals are sampled at rising edge of PCLK.                                                                                                                                                                                                   |  |  |  |  |

| G_RST         | 10  | ı   | Global power reset. This reset brings all of the TSB12LV23 to its default state, including those registers not eset by RST. When asserted, the device is completely nonfunctional.                                                                                                                                        |  |  |  |  |

| PCI_INTA/CINT | 8   | 0   | Interrupt signal. This output indicates interrupts from the TSB12LV23 to the host. This terminal signals an interrupt based upon the CARDBUS input terminal.                                                                                                                                                              |  |  |  |  |

| RST           | 76  | ı   | PCI or CardBus reset. When this bus reset is asserted, the TSB12LV23 places all output buffers in a high impedance state and resets all internal registers except device power management context- and vendor-specific bits initialized by host power on software. When asserted, the device is completely nonfunctional. |  |  |  |  |

Table C-4. PCI Address and Data

| TERMINA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>AL</b>                                                                                                                                                                              | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NO.                                                                                                                                                                                    | "0  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                  |

| PCI_AD31 PCI_AD30 PCI_AD29 PCI_AD28 PCI_AD26 PCI_AD25 PCI_AD24 PCI_AD23 PCI_AD21 PCI_AD20 PCI_AD21 PCI_AD19 PCI_AD18 PCI_AD15 PCI_AD15 PCI_AD14 PCI_AD15 PCI_AD14 PCI_AD11 PCI_AD10 PCI | 18<br>19<br>21<br>22<br>23<br>25<br>26<br>27<br>31<br>32<br>33<br>34<br>36<br>37<br>38<br>40<br>54<br>56<br>57<br>58<br>61<br>62<br>64<br>66<br>67<br>68<br>69<br>71<br>72<br>73<br>74 | I/O | PCI address/data bus. These signals make up the multiplexed PCI address and data bus on the PCI interface during the address phase of a PCI cycle, AD31–AD0 contain a 32-bit address or other destination information. During the data phase, AD31–AD0 contain data.                                                                                                                         |

| PCI_AD0 PCI_C/BE0 PCI_C/BE1 PCI_C/BE2 PCI_C/BE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65<br>53<br>41<br>28                                                                                                                                                                   | I/O | PCI bus commands and byte enables. The command and byte enable signals are multiplexed on the same PCI terminals. During the address phase of a bus cycle C/BE3–C/BE0 defines the bus command. During the data phase, this 4-bit bus is used as byte enables.                                                                                                                                |

| PCI_PAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52                                                                                                                                                                                     | I/O | PCI parity. In all PCI bus read and write cycles, the TSB12LV23 calculates even parity across the AD and C/BE buses. As an initiator during PCI cycles, the TSB12LV23 outputs this parity indicator with a one PCLK delay. As a target during PCI cycles, the calculated parity is compared to the initiator's parity indicator; a miscompare can result in a parity error assertion (PERR). |

Table C-5. PCI Interface Control

| TERMINAL            |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                    |

|---------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                    |

| PCI_DEVSEL          | 47  | I/O | PCI device select. The TSB12LV23 asserts this signal to claim a PCI cycle as the target device. As a PCI initiator, the TSB12LV23 monitors this signal until a target responds. If no target responds before time-out occurs, then the TSB12LV23 terminates the cycle with an initiator abort. |

| PCI_FRAME           | 43  | I/O | PCI cycle frame. This signal is driven by the initiator of a PCI bus cycle. FRAME is asserted to indicate that a bus transaction is beginning, and data transfers continue until while this signal is asserted. When FRAME is deasserted, the PCI bus transaction is in the final data phase.  |

| PCI_GNT             | 14  | I   | PCI bus grant. This signal is driven by the PCI bus arbiter to grant the TSB12LV23 access to the PCI bus after the current data transaction has completed. This signal may or may not follow a PCI bus request depending upon the PCI bus parking algorithm.                                   |

| PCI_IDSEL           | 29  | ı   | Initialization device select. IDSEL selects the TSB12LV23 during configuration space accesses. IDSEL can be connected to 1 of the upper 24 PCI address lines on the PCI bus.                                                                                                                   |

| PCI_IRDY            | 44  | I/O | PCI initiator ready. IRDY indicates the PCI bus initiator's ability to complete the current data phase of the transaction. A data phase is completed upon a rising edge of PCLK where both IRDY and TRDY are asserted; until which wait states are inserted.                                   |

| PCI_STOP            | 48  | I/O | PCI cycle stop signal. This signal is driven by a PCI target to request the initiator to stop the current PCI bus transaction. This signal is used for target disconnects, and is commonly asserted by target devices which do not support burst data transfers.                               |

| CLKRUN              | 7   | I/O | Clock run. This terminal provides clock control through the CLKRUN protocol. An internal pulldown resistor is implemented on this terminal for TSB12LV22 drop-in compatibility.                                                                                                                |

| PCI_PERR            | 49  | I/O | PCI parity error indicator. This signal is driven by a PCI device to indicate that calculated parity does not match PAR when enabled through the command register.                                                                                                                             |

| PCI_PME/<br>CSTSCHG | 17  | 0   | PME or card status change. This terminal indicates wake events to the host. When in a CardBus configuration, per the CARDBUS sample, the CSTSCHG output is an active high.                                                                                                                     |

| PCI_REQ             | 15  | 0   | PCI bus request. Asserted by the TSB12LV23 to request access to the bus as an initiator. The host arbiter asserts the GNT signal when the TSB12LV23 has been granted access to the bus.                                                                                                        |

| PCI_SERR            | 51  | 0   | PCI system error. Output pulsed from the TSB12LV23 when enabled indicating an address parity error has occurred. The TSB12LV23 needs not be the target of the PCI cycle to assert this signal.                                                                                                 |

| PCI_TRDY            | 45  | I/O | PCI target ready. TRDY indicates the PCI bus target's ability to complete the current data phase of the transaction. A data phase is completed upon a rising edge of PCLK where both IRDY and TRDY are asserted; until which wait states are inserted.                                         |

Table C-6. IEEE1394 PHY/Link

| TERMINAL             |          | 1/0 | DESCRIPTION                                                                                                                                                                                                                        |

|----------------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | NO.      | 1/0 | DESCRIPTION                                                                                                                                                                                                                        |

| PHY_CTL1<br>PHY_CTL0 | 92<br>93 | I/O | Phy-link interface control. These bidirectional signals control passage of information between the two devices. The TSB12LV23 can only drive these terminals after the PHY has granted permission following a link request (LREQ). |

| PHY_DATA7            | 81       |     |                                                                                                                                                                                                                                    |

| PHY_DATA6            | 82       |     |                                                                                                                                                                                                                                    |

| PHY_DATA5            | 84       |     | Phy-link interface data. These bidirectional signals pass data between the TSB12LV23 and the PHY device.                                                                                                                           |

| PHY_DATA4            | 85       | 1/0 | These terminals are driven by the TSB12LV23 on transmissions and are driven by the PHY on reception. Only                                                                                                                          |

| PHY_DATA3            | 86       | 1/0 | DATA1-DATA0 are valid for 100-Mbit speeds, DATA3-DATA0 are valid for 200-Mbit speeds, and                                                                                                                                          |

| PHY_DATA2            | 88       |     | DATA7-DATA0 are valid for 400-Mbit speeds.                                                                                                                                                                                         |

| PHY_DATA1            | 89       |     |                                                                                                                                                                                                                                    |

| PHY_DATA0            | 90       |     |                                                                                                                                                                                                                                    |

| PHY_SCLK             | 95       | I   | System clock. This input from the PHY provides a 49.152 MHz clock signal for data synchronization.                                                                                                                                 |

| PHY_LREQ             | 97       | 0   | Link request. This signal is driven by the TSB12LV23 to initiate a request for the PHY to perform some service.                                                                                                                    |

| PHY_LINKON           | 98       | I/O | LinkOn wake indication. Used and defined by 1394A and 3.3-V signaling is required.                                                                                                                                                 |

| PHY_LPS              | 99       | I/O | Link power status. Used and defined by 1394A and 3.3-V signaling is required.                                                                                                                                                      |

# Table C-7. Miscellaneous

| TERMINAL             |     | I/O | DECORPORTION                                                                                                                                                                                                                                                                                                                                    |

|----------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |