# LM3501

# Synchronous Step-up DC/DC Converter for White LED Applications

# **General Description**

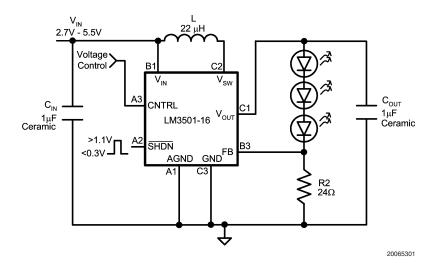

The LM3501 is a fixed frequency synchronous step-up DC/DC converter in a small 8-bump thin micro SMD package. The LM3501 is ideal for white LED applications for cellular phone back-lighting requiring low current and high efficiency. Its fixed 1MHz operating frequency allows the use of small, low ESR capacitors as well as a more predictable frequency spectrum, which is important in cellular phone applications. The LM3501 can drive 2 to 4 white LEDs in series from a single Li-lon battery or 3 cell NiMH with no external rectification diode. For white LED applications, a single external resistor is used to set the maximum LED current. The white LED current can easily be adjusted using an external voltage signal from a DAC or micro-controller. The LM3501 uses special protection circuitry on the output to prevent an overvoltage event if the primary white LED network should be disconnected eliminating the need of an extra protection Zener diode. In shutdown, the LM3501 disconnects the input and output creating a true isolation preventing any LED light from emitting over the full input operating voltage range and temperature.

#### **Features**

- Synchronous rectification, high efficiency and no external schottky diode required

- Uses small surface mount components

- Can drive up to 3 (or 4 low V<sub>F</sub>) white LEDs in series

- 2.7V to 7V input range

- True shutdown isolation, no LED leakage current

- DC voltage LED current control

- Input undervoltage lockout

- Output overvoltage protection, no external zener diode required

- Requires only a small 16V ceramic capacitor at the output

- Thermal Shutdown

- 0.1µA shutdown current

- Small 8-bump thin micro SMD package

## **Applications**

- LCD Bias Supplies

- White LED Back-Lighting

- Handheld Devices

- Digital Cameras

- Portable Applications

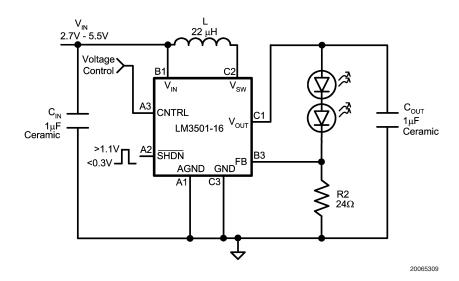

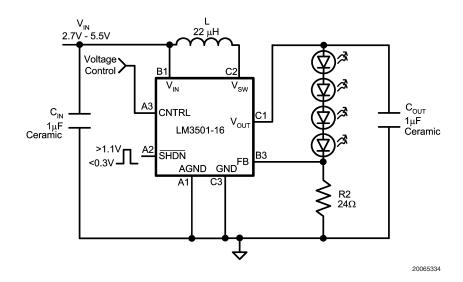

# **Typical Application Circuit**

FIGURE 1. Typical 3 LED Application

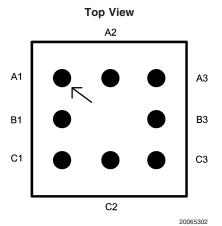

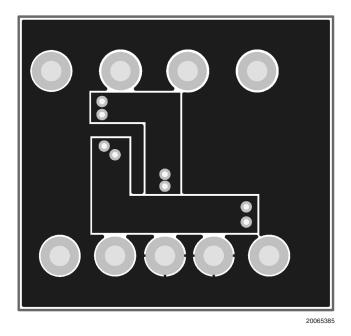

# **Connection Diagram**

8-bump micro SMD

# **Ordering Information**

| Order Number | Package Type | NSC Package Drawing | Top Mark | Supplied As               |

|--------------|--------------|---------------------|----------|---------------------------|

| LM3501TL-16  | micro SMD    | TL08SSA             | C19      | 250 Units, Tape and Reel  |

| LM3501TLX-16 | micro SMD    | TL08SSA             | C19      | 3000 Units, Tape and Reel |

# **Pin Description/Functions**

| Pin | Name             | Function                                                           |

|-----|------------------|--------------------------------------------------------------------|

| A1  | AGND             | Analog ground.                                                     |

| B1  | V <sub>IN</sub>  | Analog and Power supply input.                                     |

| C1  | V <sub>OUT</sub> | PMOS source connection for synchronous rectification.              |

| C2  | V <sub>sw</sub>  | Switch pin. Drain connections of both NMOS and PMOS power devices. |

| C3  | GND              | Power Ground.                                                      |

| B3  | FB               | Output voltage feedback connection.                                |

| A3  | CNTRL            | Analog LED current control.                                        |

| A2  | SHDN             | Shutdown control pin.                                              |

**AGND(pin A1):** Analog ground pin. The analog ground pin should tie directly to the GND pin.

$V_{IN}(pin\ B1):$  Analog and Power supply pin. Bypass this pin with a capacitor, as close to the device as possible, connected between the  $V_{IN}$  and GND pins.

$V_{OUT}$ (pin C1): Source connection of internal PMOS power device. Connect the output capacitor between the  $V_{OUT}$  and GND pins as close as possible to the device.

$V_{sw}$ (pin C2): Drain connection of internal NMOS and PMOS switch devices. Keep the inductor connection close to this pin to minimize EMI radiation.

**GND(pin C3):** Power ground pin. Tie directly to ground plane.

**FB(pin B3):** Output voltage feedback connection. Set the primary White LED network current with a resistor from the FB pin to GND. Keep the current setting resistor close to the device and connected between the FB and GND pins.

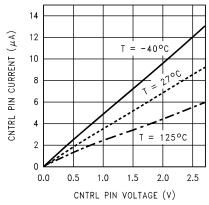

CNTRL(pin A3): Analog control of LED current. A voltage above 125mV will begin to regulate the LED current. Decreasing the voltage below 75mV will turn off the LEDs.

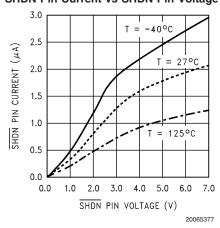

SHDN(pin A2): Shutdown control pin. Disable the device with a voltage less than 0.3V and enable the device with a voltage greater than 1.1V. The white LED current can be controlled using a PWM signal at this pin. There is an internal pull down on the SHDN pin, the device is in a normally off state.

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-0.3V to 7.5V V<sub>OUT</sub> (Note 2) -0.3V to 16V V<sub>SW</sub> (Note 2) -0.3V to  $V_{OUT}+0.3V$ FB Voltage -0.3V to 7.5V SHDN Voltage -0.3V to  $V_{IN}+0.3V$ CNTRL -0.3V to 7.5V 150°C Maximum Junction Temperature Lead Temperature 300°C (Soldering 10 sec.) Vapor Phase (60 sec.) 215°C ESD Ratings (Note 3)

Human Body Model 2kV

Machine Model 200V

# **Operating Conditions**

Junction Temperature

(Note 4)  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  Supply Voltage 2.7V to 7V CNTRL Max. 2.7V

# **Thermal Properties**

Junction to Ambient Thermal  $75^{\circ}$ C/W Resistance ( $\theta_{JA}$ ) (Note 5)

#### **Electrical Characteristics**

Infrared

(15 sec.)

Specifications in standard type face are for  $T_A = 25^{\circ}C$  and those in **boldface type** apply over the **Operating Temperature** Range of  $T_A = -10^{\circ}C$  to +85°C. Unless otherwise specified  $V_{IN} = 2.7V$ .

220°C

| Symbol             | Parameter                                  | Conditions                                 | Min<br>(Note 6) | Typ<br>(Note 7) | Max<br>(Note 6) | Units |

|--------------------|--------------------------------------------|--------------------------------------------|-----------------|-----------------|-----------------|-------|

| I <sub>Q</sub>     | Quiescent Current, Device<br>Not Switching | FB > 0.54V                                 |                 | 0.95            | 1.2             | mA    |

|                    | Quiescent Current, Device<br>Switching     | FB = 0V                                    |                 | 2               | 2.5             |       |

|                    | Shutdown                                   | SHDN = 0V                                  |                 | 0.1             | 2               | μΑ    |

| $V_{FB}$           | FeedbackVoltage                            | CNTRL = 2.7V, V <sub>IN</sub> = 2.7V to 7V | 0.485           | 0.515           | 0.545           |       |

|                    |                                            | CNTRL = 1V, V <sub>IN</sub> = 2.7V to 7V   | 0.14            | 0.19            | 0.24            | V     |

| $\Delta V_{FB}$    | FeedbackVoltage Line<br>Regulation         | V <sub>IN</sub> = 2.7V to 7V               |                 | 0.1             | 0.5             | %/V   |

| I <sub>CL</sub>    | Switch Current Limit                       | V <sub>IN</sub> = 2.7V, Duty Cycle = 80%   | 275             | 400             | 480             | mA    |

|                    |                                            | V <sub>IN</sub> = 3.0V, Duty Cycle = 70%   | 255             | 400             | 530             |       |

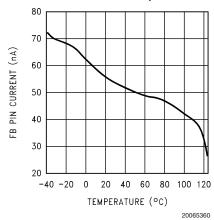

| I <sub>B</sub>     | FB Pin Bias Current                        | FB = 0.5V (Note 8)                         |                 | 45              | 200             | nA    |

| V <sub>IN</sub>    | Input Voltage Range                        |                                            | 2.7             |                 | 7.0             | V     |

| R <sub>DSON</sub>  | NMOS Switch R <sub>DSON</sub>              | $V_{IN} = 2.7V, I_{SW} = 300 \text{mA}$    |                 |                 | 0.43            | Ω     |

|                    | PMOS Switch R <sub>DSON</sub>              | $V_{OUT} = 6V$ , $I_{SW} = 300$ mA         |                 | 1.3             | 2.3             | 52    |

| D <sub>Limit</sub> | Duty Cycle Limit                           | FB = 0V                                    | 80              | 87              |                 | %     |

| F <sub>sw</sub>    | Switching Frequency                        |                                            | 0.85            | 1.0             | 1.15            | MHz   |

| I <sub>SD</sub>    | SHDN Pin Current (Note 9)                  | SHDN = 5.5V                                |                 | 1.8             | 4               |       |

|                    |                                            | SHDN = 2.7V                                |                 | 1               | 2.5             | μΑ    |

|                    |                                            | SHDN = GND                                 |                 | 0.1             |                 |       |

| I <sub>CNTRL</sub> | CNTRL Pin Current (Note 9)                 | V <sub>CNTRL</sub> = 2.7V                  |                 | 10              | 20              | μA    |

|                    |                                            | V <sub>CNTRL</sub> = 1V                    |                 | 4               | 15              |       |

| I <sub>L</sub>     | Switch Leakage Current                     | V <sub>SW</sub> = 15V                      |                 | 0.01            | 0.5             | μΑ    |

| UVP                | Input Undervoltage Lockout                 | ON Threshold                               | 2.4             | 2.5             | 2.6             | V     |

|                    |                                            | OFF Threshold                              | 2.3             | 2.4             | 2.5             |       |

# **Electrical Characteristics** (Continued)

Specifications in standard type face are for  $T_A = 25^{\circ}C$  and those in **boldface type** apply over the **Operating Temperature Range of T\_A = -10^{\circ}C to +85°C.** Unless otherwise specified  $V_{IN} = 2.7V$ .

| Symbol            | Parameter                     | Conditions                                | Min<br>(Note 6) | Typ<br>(Note 7) | Max<br>(Note 6) | Units   |

|-------------------|-------------------------------|-------------------------------------------|-----------------|-----------------|-----------------|---------|

| OVP               | Output Overvoltage            | ON Threshold                              | 15              | 15.5            | 16              | V       |

|                   | Protection                    | OFF Threshold                             | 14              | 14.6            | 15              | V       |

| I <sub>Vout</sub> | V <sub>OUT</sub> Bias Current | $V_{OUT} = 15V, \overline{SHDN} = V_{IN}$ |                 | 260             | 400             | μΑ      |

| $I_{VL}$          | PMOS Switch Leakage           | $V_{OUT} = 15V, V_{SW} = 0V$              |                 | 0.01            | 3               |         |

|                   | Current                       |                                           |                 | 0.01            | 3               | μΑ      |

| CNTRL             |                               | LED power off                             |                 | 75              |                 | , ma) / |

| Threshold         |                               | LED power on                              |                 | 125             |                 | mV      |

| SHDN              | SHDN low                      |                                           |                 | 0.65            | 0.3             | V       |

| Threshold         | SHDN High                     |                                           | 1.1             | 0.65            |                 | ľ       |

Specifications in standard type face are for  $T_J = 25^{\circ}\text{C}$  and those in **boldface type** apply over the full **Operating Temperature** Range ( $T_J = -40^{\circ}\text{C}$  to +125°C). Unless otherwise specified  $V_{IN} = 2.7\text{V}$ .

| Symbol             | Parameter                                  | Conditions                                      | Min<br>(Note 6) | Typ<br>(Note 7) | Max<br>(Note 6) | Units |

|--------------------|--------------------------------------------|-------------------------------------------------|-----------------|-----------------|-----------------|-------|

| IQ                 | Quiescent Current, Device<br>Not Switching | FB > 0.54V                                      |                 | 0.95            | 1.2             | mA    |

|                    | Quiescent Current, Device<br>Switching     | FB = 0V                                         |                 | 2               | 2.5             |       |

|                    | Shutdown                                   | SHDN = 0V                                       |                 | 0.1             | 2               | μΑ    |

| $V_{FB}$           | FeedbackVoltage                            | CNTRL = 2.7V, V <sub>IN</sub> = 2.7V to 7V      | 0.485           | 0.515           | 0.545           |       |

|                    |                                            | CNTRL = 1V, V <sub>IN</sub> = 2.7V to 7V        | 0.14            | 0.19            | 0.24            | V     |

| $\Delta V_{FB}$    | FeedbackVoltage Line<br>Regulation         | V <sub>IN</sub> = 2.7V to 7V                    |                 | 0.1             | 0.5             | %/V   |

| I <sub>CL</sub>    | Switch Current Limit                       | V <sub>IN</sub> = 3.0V, Duty Cycle = 70%        |                 | 400             |                 | mA    |

| I <sub>B</sub>     | FB Pin Bias Current                        | FB = 0.5V (Note 8)                              |                 | 45              | 200             | nA    |

| V <sub>IN</sub>    | Input Voltage Range                        |                                                 | 2.7             |                 | 7.0             | V     |

| R <sub>DSON</sub>  | NMOS Switch R <sub>DSON</sub>              | V <sub>IN</sub> = 2.7V, I <sub>SW</sub> = 300mA |                 |                 | 0.43            | 0     |

|                    | PMOS Switch R <sub>DSON</sub>              | $V_{OUT} = 6V$ , $I_{SW} = 300$ mA              |                 | 1.3             | 2.3             | Ω     |

| D <sub>Limit</sub> | Duty Cycle Limit                           | FB = 0V                                         |                 | 87              |                 | %     |

| F <sub>SW</sub>    | Switching Frequency                        |                                                 | 0.8             | 1.0             | 1.2             | MHz   |

| I <sub>SD</sub>    | SHDN Pin Current (Note 9)                  | SHDN = 5.5V                                     |                 | 1.8             | 4               | μΑ    |

|                    |                                            | SHDN = 2.7V                                     |                 | 1               | 2.5             |       |

|                    |                                            | SHDN = GND                                      |                 | 0.1             |                 |       |

| I <sub>CNTRL</sub> | CNTRL Pin Current (Note 9)                 | V <sub>CNTRL</sub> = 2.7V                       |                 | 10              | 20              |       |

|                    |                                            | V <sub>CNTRL</sub> = 1V                         |                 | 4               | 15              | μΑ    |

| IL                 | Switch Leakage Current                     | V <sub>SW</sub> = 15V                           |                 | 0.01            | 0.5             | μA    |

| UVP                | Input Undervoltage Lockout                 | ON Threshold                                    | 2.4             | 2.5             | 2.6             | V     |

|                    |                                            | OFF Threshold                                   | 2.3             | 2.4             | 2.5             |       |

| OVP                | Output Overvoltage                         | ON Threshold                                    | 15              | 15.5            | 16              | V     |

|                    | Protection                                 | OFF Threshold                                   | 14              | 14.6            | 15              |       |

| I <sub>Vout</sub>  | V <sub>OUT</sub> Leakage Current           | V <sub>OUT</sub> = 15V, SHDN = V <sub>IN</sub>  |                 | 260             | 400             | μΑ    |

| I <sub>VL</sub>    | PMOS Switch Leakage<br>Current             | V <sub>OUT</sub> = 15V, V <sub>SW</sub> = 0V    |                 | 0.01            | 3               | μΑ    |

| CNTRL              |                                            | LED power off                                   |                 | 75              |                 |       |

| Threshold          |                                            | LED power on                                    |                 | 125             |                 | mV    |

#### **Electrical Characteristics** (Continued)

Specifications in standard type face are for  $T_J = 25^{\circ}C$  and those in **boldface type** apply over the full **Operating Temperature Range** ( $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ). Unless otherwise specified  $V_{IN} = 2.7V$ .

| Symbol    | Parameter | Conditions | Min<br>(Note 6) | Typ<br>(Note 7) | Max<br>(Note 6) | Units |

|-----------|-----------|------------|-----------------|-----------------|-----------------|-------|

| SHDN      | SHDN low  |            |                 | 0.65            | 0.3             | \/    |

| Threshold | SHDN High |            | 1.1             | 0.65            |                 | v     |

**Note 1:** Absolute maximum ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is intended to be functional, but device parameter specifications may not be guaranteed. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: This condition applies if  $V_{IN} < V_{OUT}$ . If  $V_{IN} > V_{OUT}$ , a voltage greater than  $V_{IN} + 0.3V$  should not be applied to the  $V_{OUT}$  or  $V_{SW}$  pins.

Note 3: The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

Note 4: The maximum allowable power dissipation is a function of the maximum operating junction temperature,  $T_{J(MAX)}$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . See the *Thermal Properties* section for the thermal resistance. The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_D(MAX) = (T_{J(MAX)} - T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature.

Note 5: Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) is highly application and board-layout dependent. The 75°C/W figure provided was measured on a 4-layer test board conforming to JEDEC standards. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues when designing the board layout.

Note 6: All limits guaranteed at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are production tested, guaranteed through statistical analysis or guaranteed by design. All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 7: Typical numbers are at 25°C and represent the most likely norm.

Note 8: Feedback current flows out of the pin.

Note 9: Current flows into the pin.

# **Typical Performance Characteristics**

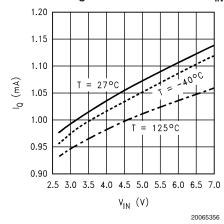

#### Switching Quiescent Current vs VIN

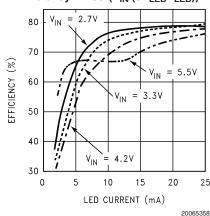

#### 2 LED Efficiency vs Load Current L = Coilcraft DT1608C-223, Efficiency = 100\*(P<sub>IN</sub>/(2V<sub>LED</sub>\*I<sub>LED</sub>))

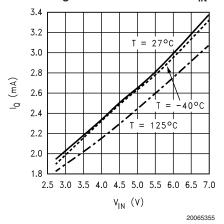

#### Non-Switching Quiescent Current vs VIN

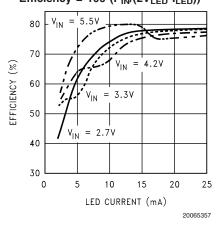

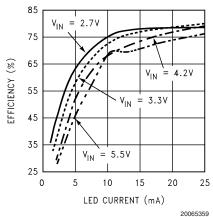

#### 3 LED Efficiency vs Load Current L = Coilcraft DT1608C-223, Efficiency = 100\*(P<sub>IN</sub>/(3V<sub>LED</sub>\*I<sub>LED</sub>))

#### 4 LED Efficiency vs Load Current L = Coilcraft DT1608C-223, Efficiency = 100\*(P<sub>IN</sub>/(4V<sub>LED</sub>\*I<sub>LED</sub>))

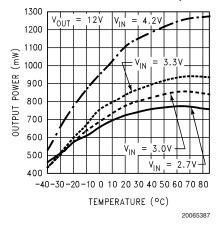

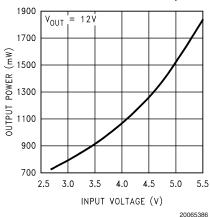

#### Output Power vs Temperature L = Coilcraft DT1608C-223)

#### SHDN Pin Current vs SHDN Pin Voltage

#### Output Power vs V<sub>IN</sub> L = Coilcraft DT1608C-223)

#### FB Pin Current vs Temperature

#### **CNTRL Pin Current vs CNTRL Pin Voltage**

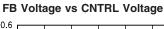

20065378

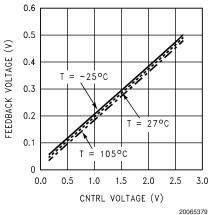

#### Switch Current Limit vs V<sub>IN</sub>

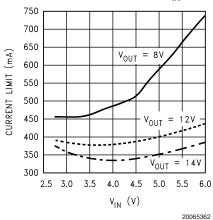

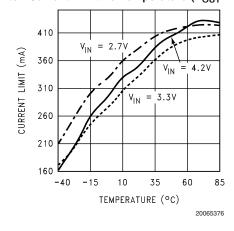

#### Switch Current Limit vs Temperature (V<sub>OUT</sub>=8V)

#### Switch Current Limit vs Temperature (V<sub>OUT</sub>=12V)

## Oscillator Frequency vs V<sub>IN</sub>

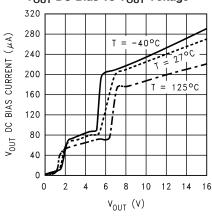

#### ${\rm V_{OUT}}$ DC Bias vs ${\rm V_{OUT}}$ Voltage

20065365

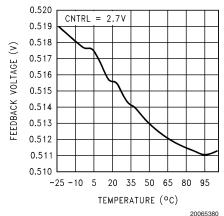

#### FB Voltage vs Temperature

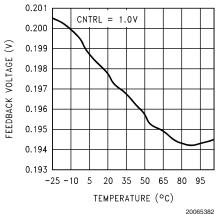

## FB Voltage vs Temperature

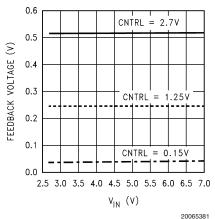

FB Voltage vs V<sub>IN</sub>

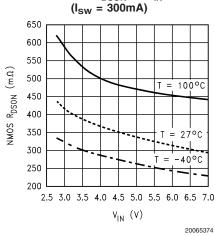

NMOS R<sub>DSON</sub> vs V<sub>IN</sub>

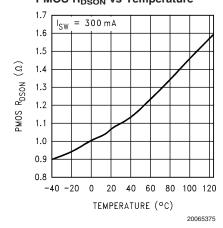

PMOS R<sub>DSON</sub> vs Temperature

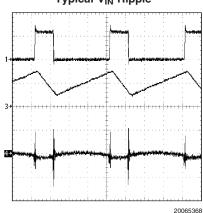

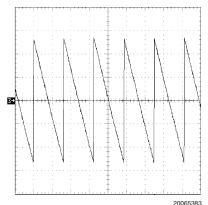

Typical V<sub>IN</sub> Ripple

3 LEDs, R<sub>LED</sub> = 22 $\Omega$ , V<sub>IN</sub> = 3.0V, CNTRL = 2.7V

1) SW, 10V/div, DC

3)  $I_L$ , 100mA/div, DC

4) V<sub>IN</sub>, 100mV/div, AC

T = 250ns/div

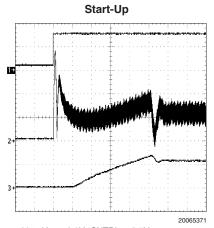

- 3 LEDs,  $R_{LED}$  = 22 $\!\Omega,\,V_{IN}$  = 3.0V, CNTRL = 2.7V

- 1) SHDN, 1V/div, DC

- 2)  $I_L$ , 100 mA/div, DC

- 3)  $I_{\text{LED}}$ , 20mA/div, DC

$T\,=\,100\mu s/div$

### Typical $V_{\text{OUT}}$ Ripple, OVP Functioning

$V_{OUT}$  open circuit and equals approx. 15V DC,  $V_{IN}$  = 3.0V 3)  $V_{OUT}$ , 200mV/div, AC

T = 1ms/div

# **Operation**

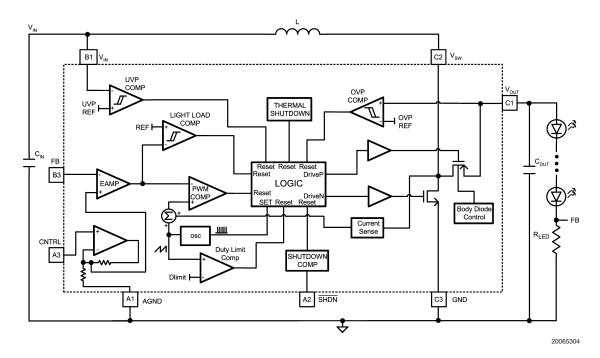

FIGURE 2. LM3501 Block Diagram

The LM3501 utilizes a synchronous Current Mode PWM control scheme to regulate the feedback voltage over almost all load conditions. The DC/DC controller acts as a controlled current source ideal for white LED applications. The LM3501 is internally compensated preventing the use of any external compensation components providing a compact overall solution. The operation can best be understood referring to the block diagram in Figure 2. At the start of each cycle, the oscillator sets the driver logic and turns on the NMOS power device conducting current through the inductor and turns off the PMOS power device isolating the output from the V<sub>SW</sub> pin. The LED current is supplied by the output capacitor when the NMOS power device is active. During this cycle, the output voltage of the EAMP controls the current through the inductor. This voltage will increase for larger loads and decrease for smaller loads limiting the peak current in the inductor minimizing EMI radiation. The EAMP voltage is compared with a voltage ramp and the sensed switch voltage. Once this voltage reaches the EAMP output voltage, the PWM COMP will then reset the logic turning off the NMOS power device and turning on the PMOS power device. The inductor current then flows through the PMOS power device to the white LED load and output capacitor. The inductor current recharges the output capacitor and supplies the current for the white LED branches. The oscillator then sets the driver logic again repeating the process. The Duty Limit Comp is always operational preventing the NMOS power switch from being on more than one cycle and conducting large amounts of current.

The LM3501 has dedicated protection circuitry active during normal operation to protect the IC and the external components. The Thermal Shutdown circuitry turns off both the NMOS and PMOS power devices when the die temperature reaches excessive levels. The LM3501 has a UVP Comp that disables both the NMOS and PMOS power devices when battery voltages are too low preventing an on state of the power devices which could conduct large amounts of current. The OVP Comp prevents the output voltage from increasing beyond 15.5V when the primary white LED network is removed or if there is an LED failure, allowing the use of small 16V ceramic capacitors at the output. This comparator has a 0.9V hysteresis that will regulate the output voltage between 15.5V and 14.6V typically. The LM3501 features a shutdown mode that reduces the supply current to 0.1uA and isolates the input and output of the converter. The CNTRL pin can be used to change the white LED current. A CNTRL voltage above 125mV will enable power to the LEDs and a voltage lower than 75mV will turn off the power to the LEDs.

# **Application Information**

#### **ADJUSTING LED CURRENT**

The maximum White LED current is set using the following equation:

$$I_{LED} = V_{FB(MAX)}/R_{LED}$$

The LED current can be controlled using an external DC voltage. The recommended operating range for the voltage on the CNTRL pin is 0V to 2.7V. When CNTRL is 2.7V, FB = 0.515V (typ.) The FB voltage will continue to increase if CNTRL is brought above 2.7V (not recommended). The voltage on CNTRL should never be above  $V_{\text{IN}}.$  The CNTRL to FB voltage relationship is:

#### FB = 0.191\*CNTRL

The LED current can be controlled using a PWM signal on the  $\overline{SHDN}$  pin with frequencies in the range of 100Hz (greater than visible frequency spectrum) to 1kHz. For controlling LED currents down to the  $\mu A$  levels, it is best to use a PWM signal frequency between 200-500Hz. The LM3501 LED current can be controlled with PWM signal frequencies above 1kHz but the controllable current decreases with higher frequency. The maximum LED current would be achieved using the equation above with 100% duty cycle, ie. the  $\overline{SHDN}$  pin always high.

Applying a voltage greater than 125mV to the CNTRL pin will begin regulating current to the LEDs. A voltage below 75mV will prevent application or regulation of the LED current.

The minimum number of LEDs the LM3501 can drive is 2 in series and the maximum is 4. The LM3501 can also drive multiple strings of white LEDs. When driving 4 LEDs in series the application should use lower forward voltage drop white LEDs to prevent the OVP function from activating during normal operation.

#### **OUTPUT OVERVOLTAGE PROTECTION**

The LM3501 contains dedicated circuitry for monitoring the output voltage. In the event that the primary LED network is disconnected the output will increase and be limited to 15.5V. There is a 900mV hysteresis associated with this circuitry which will cause the output to fluctuate between 15.5V and 14.6V if the primary network is disconnected. In the event that the network is reconnected regulation will begin at the appropriate output voltage. The 15.5V limit allows the use of 16V  $1\mu F$  ceramic output capacitors creating an overall small solution for white LED applications.

#### **RELIABILITY AND THERMAL SHUTDOWN**

The maximum continuous pin current for the 8 pin thin micro SMD package is 535mA. When driving the device near its power output limits the  $V_{\rm SW}$  pin can see a higher DC current than 535mA (see <code>INDUCTOR SELECTION</code> section for average switch current). To preserve the long term reliability of the device the average switch current should not exceed 535mA.

The LM3501 has an internal thermal shutdown function to protect the die from excessive temperatures. The thermal shutdown trip point is typically 150°C. There is a hysteresis of typically 35°C so the die temperature must decrease to approximately 115°C before the LM3501 will return to normal operation.

#### INDUCTOR SELECTION

The inductor used with the LM3501 must have a saturation current greater than the cycle by cycle peak inductor current. Choosing inductors with low DCR decreases power losses and increases efficiency.

The minimum inductor value required for the LM3501 can be calculated using the following equation:

$$L > \frac{V_{IN} R_{DSON}}{0.29} \left( \frac{D}{D'} - 1 \right)$$

where L is in  $\mu$ H,  $V_{IN}$  is the input supply of the chip in Volts,  $R_{DSON}$  is the ON resistance of the NMOS power switch found in the *Typical Performance Characteristics* section in ohms and D is the duty cycle of the switching regulator. The above equation is only valid for D greater than 0.5. An inductor value in the range of  $4.7\mu$ H to  $22\mu$ H is good for most applications, however the value must meet the requirements of the above equation. The duty cycle, D, is given by the following equation:

$$D' = \frac{V_{IN}}{V_{OUT}} = 1-D$$

where  $V_{\text{OUT}}$  is the voltage at pin C1. The typical cycle-by-cycle peak inductor current can be calculated from the following equation:

$$I_{PK} \approx \frac{I_{OUT}}{\eta D'} + \frac{V_{IN}D}{2LF_{SW}}$$

where  $I_{OUT}$  is the total load current,  $F_{SW}$  is the switching frequency, L is the inductance and  $\eta$  is the converter efficiency of the total driven load. A good typical number to use for  $\eta$  is 0.8. The value of  $\eta$  can vary with load and duty cycle. The average inductor current, which is also the average  $V_{SW}$  pin current, is given by the following equation:

$$I_{L(AVE)} \approx \frac{I_{OUT}}{\eta D'}$$

The maximum output current capability of the LM3501 can be estimated with the following equation:

$$I_{OUT} \approx \eta D' \left( I_{CL} - \frac{V_{IN}D}{2LF_{SW}} \right)$$

where  $I_{\rm CL}$  is the current limit. Some recommended inductors include but are not limited to:

Coilcraft DT1608C series

Coilcraft DO1608C series TDK VLP4612 series

TDK VLP5610 series

TDK VLF4012A series

# **Application Information** (Continued)

#### CAPACITOR SELECTION

Choose low ESR ceramic capacitors for the output to minimize output voltage ripple. Multilayer X7R or X5R type ceramic capacitors are the best choice. For most applications, a 1µF ceramic output capacitor is sufficient.

Local bypassing for the input is needed on the LM3501. Multilayer X7R or X5R ceramic capacitors with low ESR are a good choice for this as well. A  $1\mu F$  ceramic capacitor is sufficient for most applications. However, for some applications at least a  $4.7\mu F$  ceramic capacitor may be required for proper startup of the LM3501. Using capacitors with low ESR decreases input voltage ripple. For additional bypassing, a 100nF ceramic capacitor can be used to shunt high frequency ripple on the input. Some recommended capacitors include but are not limited to:

TDK C2012X7R1C105K

Taiyo-Yuden EMK212BJ105 G

Vishay Vitramon VJ1206S105KXJ

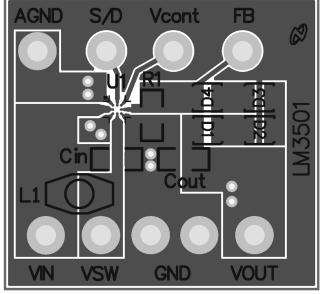

#### LAYOUT CONSIDERATIONS

The input bypass capacitor  $C_{\rm IN}$ , as shown in Figure 2, must be placed close to the device and connect between the  $V_{\rm IN}$

and GND pins. This will reduce copper trace resistance which effects the input voltage ripple of the IC. For additional input voltage filtering, a 100nF bypass capacitor can be placed in parallel with C<sub>IN</sub> to shunt any high frequency noise to ground. The output capacitor,  $C_{\text{OUT}}$ , should also be placed close to the LM3501 and connected directly between the V<sub>OUT</sub> and GND pins. Any copper trace connections for the C<sub>OUT</sub> capacitor can increase the series resistance, which directly effects output voltage ripple and efficiency. The current setting resistor,  $R_{\text{LED}}$ , should be kept close to the FB pin to minimize copper trace connections that can inject noise into the system. The ground connection for the current setting resistor should connect directly to the GND pin. The AGND pin should connect directly to the GND pin. Not connecting the AGND pin directly, as close to the chip as possible, may affect the performance of the LM3501 and limit its current driving capability. Trace connections made to the inductor should be minimized to reduce power dissipation, EMI radiation and increase overall efficiency. It is good practice to keep the V<sub>SW</sub> routing away from sensitive pins such as the FB pin. Failure to do so may inject noise into the FB pin and affect the regulation of the device. See Figure 3 and Figure 4 for an example of a good layout as used for the LM3501 evaluation board.

20065384

FIGURE 3. Evaluation Board Layout (2X Magnification)

Top Layer

# Application Information (Continued)

FIGURE 4. Evaluation Board Layout (2X Magnification)

Bottom Layer (as viewed from the top)

FIGURE 5. 2 White LED Application

# Application Information (Continued)

FIGURE 6. 4 White LED Application

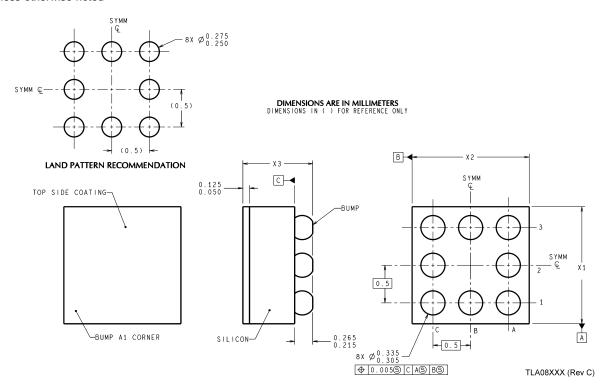

# Physical Dimensions inches (millimeters)

unless otherwise noted

8-Bump Micro SMD Package (TL) For Ordering, Refer to Ordering Information Table **NS Package Number TLA08A** X1 = 1.92mm (±0.03mm), X2 = 1.92mm (±0.03mm), X3 = 0.6mm (±0.075mm)

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com

Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560