## STLC4420A

## Single chip 802.11b/g/a WLAN radio

#### Feature summary

- Extremely small footprint

- Low power consumption

- High performance dual band solution, operating at 2.4 GHz and at 5 GHz

- Fully compliant with the IEEE 802.11b ,802.11g and 802.11a WLAN standards

- Support for 54, 48, 36, 24, 18, 12, 9, and 6Mbps OFDM, 11 and 5.5Mbps CCK and legacy 2 and 1Mbps data rates at 2.4 GHz

- Support for 54, 48, 36, 24, 18, 12, 9, and 6Mbps OFDM at 5 GHz

- Single chip 802.11b/g/a WLAN solution with fully integrated:

- Zero IF (ZIF) transceiver,

- Voltage controlled oscillator (VCO),

- High-speed A/ D and D/A converters,

- Radio power management unit (PMU),

- OFDM and CCK baseband processor,

- ARM9 media access controller (MAC),

- SPI serial host interface (up to 48Mbps)

- PA bias control

- Flexible integrated power management unit

- Glueless FEM interface

- Intelligent power control, including 802.11 power save mode

- Fully integrated Bluetooth coexistence

- Mode selectable SPI or SDIO host interface (up to 48Mbps)

## **Applications**

- Cellular phones

- Personal digital assistants (PDA)

- Portable computers

- Hand-held data transfer devices

- Cameras

# LFBGA228 (12.5x7x1.4mm)

- Computer peripherals

- Cable replacement

#### **Description**

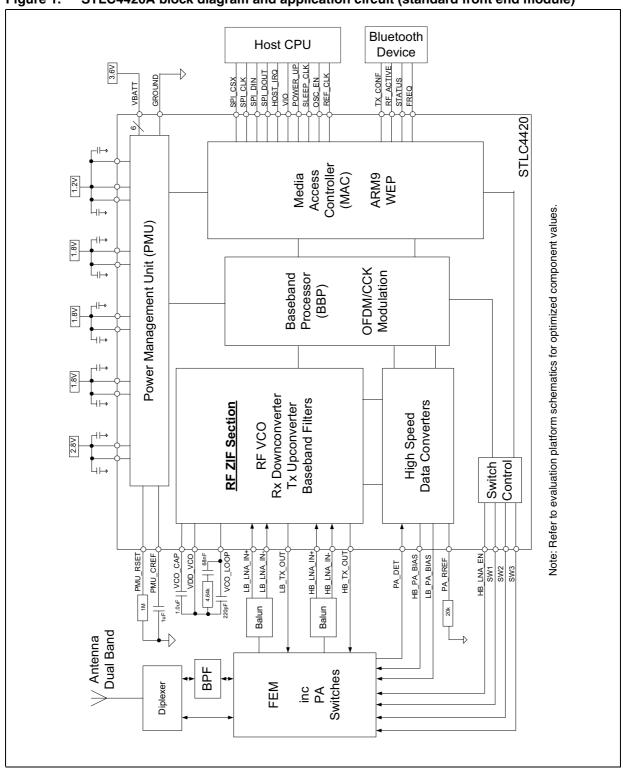

The STLC4420A is a single chip dual band WLAN solution for embedded, low-power, high performance and very small form factor mobile applications. The product conforms to the IEEE 802.11b, 802.11g and 802.11a protocols operating in the 2.4 GHz and 5 GHz frequency band, supporting OFDM data rates of 54, 48, 36, 24, 18, 12, 9, and 6Mbps in the both bands and CCK data rates of 11 and 5.5Mbps and legacy data rates of 2 and 1Mbps at 2.4 GHz.

The STLC4420A is a fully integrated wireless radio including a ZIF transceiver, RF synthesizer/VCO, high-speed data converters, an OFDM/CCK digital baseband processor, an ARM9-based MAC and a complete power management unit with integrated PA bias control. An external dual band FEM completes a highly integrated chip set solution.

Host control is provided by a flexible serial interface (SPI or SDIO) supporting bit rates of 48Mbps. For maximum flexibility, the STLC4420A accepts system reference clock frequencies of 19.2, 26, 38.4 and 40 MHz. A reference design evaluation platform of hardware and software is provided to system integrators to rapidly enable wireless connectivity to mobile platforms.

#### Order codes

| Part number | Op. Temp. range, °C | Package  |

|-------------|---------------------|----------|

| STLC4420A   | -30 to 85           | LFBGA228 |

April 2006 Rev 1 1/40

Contents STLC4420A

# **Contents**

| 1 | Block | k diagram and application circuit               | . 4 |

|---|-------|-------------------------------------------------|-----|

| 2 | Pin d | escriptions                                     | . 5 |

|   | 2.1   | Signal description                              | . 6 |

| 3 | Elect | rical specifications                            | 14  |

| 4 | Seria | Il host interface                               | 21  |

|   | 4.1   | Host pins                                       | 21  |

|   | 4.2   | SPI mode selection                              | 22  |

|   | 4.3   | AHB masters                                     | 24  |

|   | 4.4   | Host registers                                  | 25  |

|   | 4.5   | Host writes                                     | 26  |

|   | 4.6   | Host multi-word writes                          | 27  |

|   | 4.7   | Host reads                                      | 27  |

|   | 4.8   | Host multi-word reads                           | 28  |

|   | 4.9   | ARM AHB slave access                            | 29  |

| 5 | Regis | sters description                               | 30  |

|   | 5.1   | ARM interrupt register                          | 30  |

|   | 5.2   | ARM interrupt acknowledge                       | 30  |

|   | 5.3   | ARM interrupt enable                            | 31  |

|   | 5.4   | Host interrupt register                         | 31  |

|   | 5.5   | Host interrupt enable register                  | 32  |

|   | 5.6   | Host interrupt acknowledge register             | 32  |

|   | 5.7   | General purpose 1 and 2 communication registers | 33  |

|   | 5.8   | Device control/status register                  | 33  |

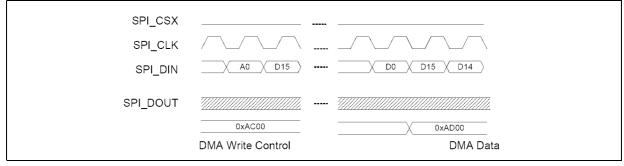

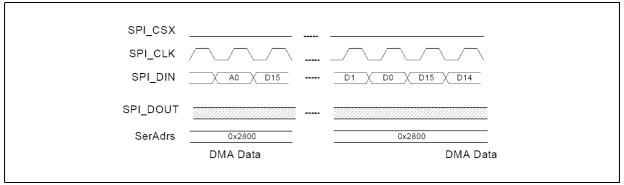

|   | 5.9   | DMA data register                               | 35  |

|   | 5.10  | DMA write control register                      | 35  |

|   | 5.11  | DMA write length register                       | 36  |

|   | 5.12  | DMA write base address register                 | 36  |

|   | 5.13  | DMA read control register                       | 36  |

|   |       |                                                 |     |

| STLC4420 <i>A</i> | 4     |                                | Conte | ents |

|-------------------|-------|--------------------------------|-------|------|

|                   | 5.14  | DMA read length register       |       | 37   |

|                   | 5.15  | DMA read base address register |       | 37   |

| 6                 | Pack  | age information                |       | 38   |

| Revision          | histo | ry                             |       | 39   |

#### Block diagram and application circuit 1

Figure 1. STLC4420A block diagram and application circuit (standard front end module)

STLC4420A Pin descriptions

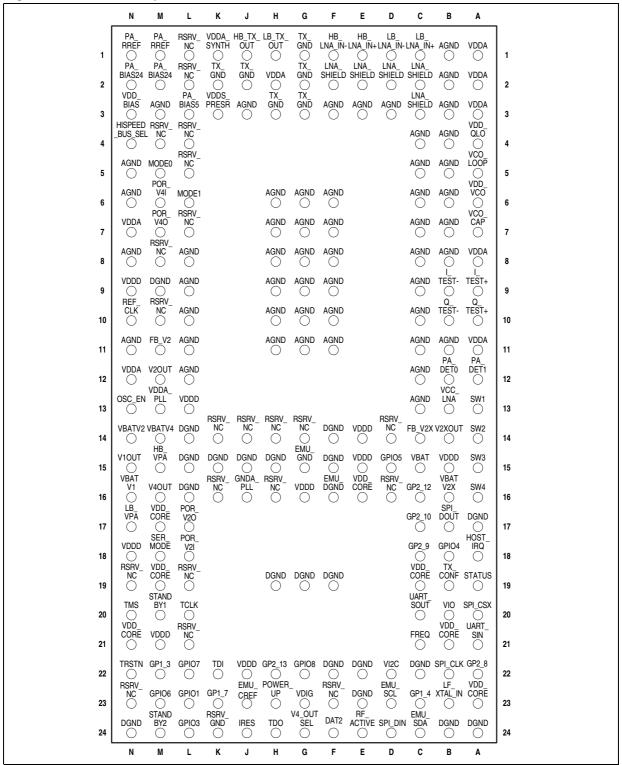

## 2 Pin descriptions

Figure 2. STLC4420A pin connections

Pin descriptions STLC4420A

# 2.1 Signal description

Table 1. STLC4420A signal descriptions

| Pin name        | Pin number           | Туре                             | Internal<br>resistor | Function                                                                                                   |  |  |  |

|-----------------|----------------------|----------------------------------|----------------------|------------------------------------------------------------------------------------------------------------|--|--|--|

| RF front end in | nterface pins        |                                  |                      |                                                                                                            |  |  |  |

| LB_LNA_IN-      | D1                   | RF input                         | 100Ω RF              | Low band (2.4 GHz) 100Ω RF differential RX                                                                 |  |  |  |

| LB_LNA_IN+      | C1                   | RF input                         | Differential         | inputs.                                                                                                    |  |  |  |

| HB_LNA_IN-      | F1                   | RF input                         | 100Ω RF              | High band (5 GHz) 100Ω RF differential RX                                                                  |  |  |  |

| HB_LNA_IN+      | E1                   | RF input                         | Differential         | inputs.                                                                                                    |  |  |  |

| LNA_SHIELD      | C2, C3,D2,<br>E2, F2 | RF shield                        | -                    | Low noise amplifier (LNA) input shield pins.                                                               |  |  |  |

| LB_TX_OUT       | H1                   | RF output                        | -                    | $50\Omega$ RF transmit (TX) low band (2.4 GHz) single ended output.                                        |  |  |  |

| HB_TX_OUT       | J1                   | RF output                        | -                    | $50\Omega$ RF transmit (TX) low band (5 GHz) single ended output.                                          |  |  |  |

| SW1             | A13                  | digital output                   | -                    |                                                                                                            |  |  |  |

| SW2             | A14                  | digital output                   | -                    | Complementary transmit/receive antennaswitch control outputs. I/O level                                    |  |  |  |

| SW3             | A15                  | digital output                   | -                    | determined by VDDA supply input.                                                                           |  |  |  |

| SW4             | A16                  | digital output                   | -                    |                                                                                                            |  |  |  |

| PA_BIAS24       | N2, M2               | analog output                    | -                    | Power amplifier bias control (2.4 GHz). DAC full-scale output current determined by PA_RREF resistor.      |  |  |  |

| PA_BIAS5        | L3                   | analog output                    | -                    | Power amplifier bias control (5 GHz). DAC full-scale output current determined by PA_RREF resistor.        |  |  |  |

| PA_RREF         | N1, M1               | analog reference                 | -                    | Analog reference resistor. A 20K ohm typical resistor sets the PA_BIAS full-scale output current.          |  |  |  |

| PA_DET0         | B12                  | analog input                     | Resistor             | PA Detector Input 0. (2.4 GHz)                                                                             |  |  |  |

| PA_DET1         | A12                  | analog input                     | ladder               | PA Detector Input 1. (5 GHz)                                                                               |  |  |  |

| Host interface  | and clock pins       |                                  |                      |                                                                                                            |  |  |  |

| DAT2            | F24                  | 1.8 V (VIO) digital I/O          |                      | SDIO data I/O bit 2. Not used in SPI mode.                                                                 |  |  |  |

| HOST_IRQ        | A18                  | 1.8 V digital output, VIO domain |                      | Host interrupt request. Typically asserted to request a SPI data transfer. In SDIO mode pin = DAT1.        |  |  |  |

| POWER_UP        | H23                  | 1.8 V digital input              | 1MΩ<br>Pull-Down     | Power up enable from host                                                                                  |  |  |  |

| OSC_EN          | N13                  | 1.8 V digital output             | No Pull              | Oscillator enable output. Initially driven high upon powerup, under firmware control after initialization. |  |  |  |

STLC4420A Pin descriptions

Table 1. STLC4420A signal descriptions (continued)

| Pin name            | Pin number | Туре                         | Internal resistor | Function                                                                                                                                                                                                                                                                                                       |

|---------------------|------------|------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF_CLK             | N10        | Clock input                  | -                 | Reference clock input (19.2, 26.0, 38.4 or 40.0 MHz). Use a 1000pF typical series blocking capacitor.                                                                                                                                                                                                          |

| LF_XTAL_IN          | B23        | 1.8 V (VIO) digital input    |                   | 32KHz typical sleep clock input from host.                                                                                                                                                                                                                                                                     |

| SPI_CLK             | B22        | 1.8 V (VIO) digital input    |                   | SPI clock from host                                                                                                                                                                                                                                                                                            |

| SPI_CSX             | A20        | 1.8V (VIO) digital input     |                   | SPI chip select from host                                                                                                                                                                                                                                                                                      |

| SPI_DIN             | D24        | 1.8 V (VIO) digital I/O      |                   | SPI data input for 4-wire modes. In 3-wire modes, this is the data input/output signal.                                                                                                                                                                                                                        |

| SPI_DOUT            | B17        | 1.8 V (VIO) digital output   |                   | SPI data output for 4-wire modes only. In SDIO mode pin = DAT0.                                                                                                                                                                                                                                                |

| FREQ                | C21        | 1.8 V (VIO) GPIO<br>(input)  | No Pull           | Firmware controlled GPIO typically implementing Bluetooth coexistence FREQ input function. Assigned to ARM MAC GP2-6.                                                                                                                                                                                          |

| RF_ACTIVE           | E24        | 1.8 V (VIO) GPIO<br>(input)  | No Pull           | Firmware controlled GPIO typically implementing Bluetooth coexistence RF_ACTIVE input function. Assigned to ARM MAC GP2-5.                                                                                                                                                                                     |

| STATUS              | A19        | 1.8 V (VIO) GPIO<br>(input)  | No Pull           | Firmware controlled GPIO typically implementing Bluetooth coexistence STATUS input function.  Assigned to ARM MAC GP2-4.                                                                                                                                                                                       |

| TX_CONF             | B19        | 1.8 V (VIO) GPIO<br>(output) | No Pull           | Firmware controlled GPIO typically implementing Bluetooth coexistence TX_CONF output function. Assigned to ARM MAC GP2-3.                                                                                                                                                                                      |

| MODE0               | M5         | 1.8 V digital input          |                   | MODE strapping pins are pimarily used to properly initialize the PLL for following                                                                                                                                                                                                                             |

| MODE1               | L6         | 1.8 V digital input          |                   | REF_CLK frequencies.  Connect appropriate pin to ground plane for a logic 0 input or to 1.8V power plane (through a 4kohm resistor) for a logic 1.  MODE(1:0) = 00 => 19.2 MHz  MODE(1:0) = 01 => 40 MHz default, no pull needed  MODE(1:0) = 10 => 26 MHz  MODE(1:0) = 11 => 38.4 MHz  (Note: M5=RX0, L6=RX1) |

| HISPEED_<br>BUS_SEL | N4         | 1.8 V digital input          |                   | High speed internal bus selection input.  Needs to be pulled down through 2.5K ohm to set the proper high speed bus mode.  (Note: N4 = ANTSELTST+)                                                                                                                                                             |

Pin descriptions STLC4420A

Table 1. STLC4420A signal descriptions (continued)

| Pin name     | Pin number | Туре                        | Internal<br>resistor | Function                                                                                                                                                                |

|--------------|------------|-----------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply | pins       |                             |                      |                                                                                                                                                                         |

| POR_V2O      | L17        | 1.8V (V2) Digital<br>Input  |                      | BB/MAC Power on Reset Input                                                                                                                                             |

| POR_V2I      | L18        | 1.8V (V2) Digital<br>Output |                      | EMU Power on Reset Output. A more detailed description could be added from the ST EMU spec                                                                              |

| POR_V4I      | M6         | 2.8V (V4) Digital<br>Input  |                      | Transceiver Power on Reset Input                                                                                                                                        |

| POR_V4O      | M7         | 2.8V (V4) Digital<br>Output |                      | EMU Power on Reset Output. A more detailed description could be added from the ST EMU spec                                                                              |

| VBATV2X      | B16        |                             |                      | Battery supply inputs for regulator V2X of the EMU. Decouple . Decouple to a solid ground plane using a ceramic capacitor located as close a possible to the VBAT pins. |

| VBATV2       | N24        | Supply Input                |                      | Battery supply inputs for regulator V2 of the EMU. Decouple to a solid ground plane using a ceramic capacitor located as close a possible to the VBAT pins.             |

| VBATV1       | N16        | 3.6V)                       |                      | Battery supply input for regulator V1 of the EMU. Decouple to a solid ground plane using a ceramic capacitor located as close a possible to the VBAT pins.              |

| VBATV4       | M14        |                             |                      | Battery supply input for regulator V4 of the EMU. Decouple to a solid ground plane using a ceramic capacitor located as close a possible to the VBAT pins.              |

| STANDBY1     | M20        | 1.8 Digital Output          |                      | Indicates power regulator standby status with STANDBY_1. A more detailed description should be taken from the ST EMU specification                                      |

| STANDBY2     | M24        | 1.8 Digital Output          |                      | Indicates power regulator standby status with STANDBY_1. A more detailed description should be taken from the ST EMU specification                                      |

| SER_MODE     | M18        | 1.8V (VIO) Digital<br>Input |                      | Selects Serial Host Interface Mode. Set to<br>Logic High for SPI mode, set to Logic Low for<br>SDIO mode                                                                |

| VBAT         | C15        | Supply Input (3.6V)         | -                    | Battery supply inputs. Decouple to a solid ground plane using a ceramic capacitor located as close a possible to the VBAT pins.                                         |

| VDIG         | G23        | Supply Input (3.3V)         | -                    | Supply pin for SW1 to SW4 digital output drivers. (3.6V Nominal)                                                                                                        |

STLC4420A Pin descriptions

Table 1. STLC4420A signal descriptions (continued)

| Pin name   | Pin number                             | Type                 | Internal resistor | Function                                                                                                                                                                               |

|------------|----------------------------------------|----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VI2C       | D22                                    | Digital supply input |                   | Digital 1.8V I/O power supply input pin dedicated to the EMU I2C bus interface. Connect to ground if the I2C interface of the EMU is not connected (EMU_SCL, EMU_SDA)                  |

| VIO        | B20                                    | Supply input (1.8 V) | -                 | Host digital I/O supply input for SPI and Bluetooth interfaces.                                                                                                                        |

| V1OUT      | N15                                    | Regulator output     | -                 | Linear regulator 1.8V output.                                                                                                                                                          |

| V2OUT      | M12                                    | Regulator output     | -                 | Linear regulator 1.8V output.                                                                                                                                                          |

| V2XOUT     | B14                                    | Regulator output     | -                 | Linear regulator 1.2V output.                                                                                                                                                          |

| V4OUT      | M16                                    | Regulator output     | -                 | Linear regulator output selectable for 2.81V or 3.11V. Output voltage controlled by V4_OUTSEL pin G24.                                                                                 |

| V4_OUTSEL  | G24                                    | 1.8 V digital input  | -                 | Control input for selection of V4OUT regulator output voltage. Logic 0 = 0=2.81V, 1= 3.11V                                                                                             |

| FB_V2      | M11                                    | Regulator sense      | -                 | Sense line for V2 regulator. Connect to V2OUT pin M12 with a short trace.                                                                                                              |

| FB_V2X     | C14                                    | Regulator sense      | -                 | Sense line for V2X regulator. Connect to V2XOUT pin B14 with a short trace.                                                                                                            |

| EMU_CREF   | J23                                    | Analog reference     | -                 | Reference capacitor for internal Power Management Unit (PMU). Connect a 1uF capacitor to a solid board gound plane.                                                                    |

| IRES       | J24                                    | Analog reference     |                   | Reference resistor for the internal Power Management Unit (EMU). Connect a $1M\Omega$ resistor to a solid board ground plane.                                                          |

| VDDA       | A1, A2, A3,<br>A8, A11, H2,<br>N7, N12 | Analog supply input  | -                 | Analog 1.8V supply input pins. Decouple to a solid ground plane using ceramic capacitors located as close a possible to the appropriate pins. Refer to evaluation platform schematics. |

| VDDA_SYNTH | K1                                     |                      |                   |                                                                                                                                                                                        |

| VDDS_PRESR | K3                                     |                      |                   |                                                                                                                                                                                        |

| VCC_LNA    | B13                                    |                      |                   |                                                                                                                                                                                        |

| HB_VPA     | M15                                    | 3.0 V digital output |                   | High Band PA Enable                                                                                                                                                                    |

| LB_VBA     | N17                                    | 3.0 V digital output |                   | Low Band PA Enable                                                                                                                                                                     |

| VDDA_PLL   | M13                                    | Analog supply input  | -                 | Phase Locked Loop supply = 1.8V                                                                                                                                                        |

Pin descriptions STLC4420A

Table 1. STLC4420A signal descriptions (continued)

| Pin name | Pin number                                                                                                               | Туре                 | Internal<br>resistor | Function                                                                                                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD_QLO  | A4                                                                                                                       | Analog supply input  | -                    | Analog 1.8V supply input for RF Quadrature Local Oscillator (QLO). Decouple to a solid ground plane using a ceramic capacitor located as close as possible to the pin. Refer to evaluation platform schematics.                                             |

| VDD_VCO  | A6                                                                                                                       | Analog supply input  | -                    | Analog 1.8V supply input for the RF Voltage Controlled Oscillator (VCO). Typically connected to V1OUT pin N15. Decouple to a solid ground plane using a ceramic capacitor located as close as possible to the pin. Refer to evaluation platform schematics. |

| VDD_BIAS | N3                                                                                                                       | Analog supply input  | -                    | Analog supply input for BIAS control ciruits. Typically connected to V4OUT pin M16. Decouple to a solid ground plane using a ceramic capacitor located as close as possible to the pin. Refer to evaluation platform schematics.                            |

| VDDD     | B15, J22,<br>M21, N18,<br>E14, E15,<br>L13, N9,G16                                                                       | Digital supply input | -                    | Digital 1.8V I/O power supply input pins. Decouple to a solid ground plane using ceramic capacitors located as close a possible to the appropriate pins. Refer to evaluation platform schematics.                                                           |

| AGND     | B1-B8,B11,<br>C4-C13, D3,<br>E3, F3, F6-<br>F11,<br>G6-G11, H6-<br>H11, J3, L8-<br>L12, M3, N5,<br>N6, N8, N11           | Analog ground        | -                    | All AGND pins must be connected together through a solid ground plane. For optimal performance, refer to the evaluation platform layout for the proper AGND and DGND grounding scheme.                                                                      |

| TX_GND   | G1, G2, G3,<br>H3, J2, K2                                                                                                | Analog ground        | -                    | All TX_GND pins must be connected together through a solid ground plane. For optimal performance, refer to the evaluation platform layout for the proper grounding scheme.                                                                                  |

| VDD_CORE | A23, B21,<br>C19, E16,<br>M17, M19,<br>N21                                                                               | Digital supply input | -                    | Digital 1.2V core supply. Decouple to a solid ground plane using ceramic capacitors located as close a possible to the appropriate pins. Refer to evaluation platform schematics.                                                                           |

| DGND     | A17,L14, L15,<br>L16, M9, K15,<br>J15, H15,<br>H19, G19,<br>F14, F15,<br>F19, F22,<br>E22, C22,<br>E23, N24,<br>B24, A24 | Digital ground       | -                    | All DGND pins must be connected together through a common solid ground plane. For maximum performance, refer to the evaluation platform layout for the proper AGND and DGND grounding scheme.                                                               |

STLC4420A Pin descriptions

Table 1. STLC4420A signal descriptions (continued)

| Table I. S    |            |                     |                      |                                                                                                                                                                      |  |  |  |

|---------------|------------|---------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin name      | Pin number | Туре                | Internal<br>resistor | Function                                                                                                                                                             |  |  |  |

| EMU_GND       | G15        | Ground              |                      | Ground of the EMU.                                                                                                                                                   |  |  |  |

| EMU_DGND      | F16        | Digital Ground      |                      | Ground of the EMU level shifter.                                                                                                                                     |  |  |  |

| GNDA_PLL      | J16        |                     |                      |                                                                                                                                                                      |  |  |  |

| Miscellaneous | Pins       |                     |                      |                                                                                                                                                                      |  |  |  |

| GPIO8         | G22        | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO Assigned to ARM MAC GP2-11. Float for proper operation.                                                                        |  |  |  |

| GPIO7         | L22        | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO.<br>Assigned to ARM MAC GP2-1. Can<br>optionally be used as a serial data line (SDA)<br>for external 1.8V serial FLASH device. |  |  |  |

| GPIO6         | M23        | 1.8V (VIO) GPIO     | 40uA<br>Pull-Down    | Firmware controlled 1.8V digital GPIO. Assigned to ARM MAC GP2-0. Can optionally be used as a serial clock line (SCL) for external 1.8V serial FLASH device.         |  |  |  |

| GPIO5         | D15        | 1.8V (VIO) GPIO     | Pull-Up              | Firmware controlled 1.8V digital GPIO. Assigned to ARM MAC GP1-13. (Radio_PE). Float for proper operation.                                                           |  |  |  |

| GPIO4         | B18        | 1.8V (VIO) GPIO     | Pull-Up              | Firmware controlled 1.8V digital GPIO float for proper operation. Assigned to ARM MAC GP1-15. (FAAmode_n)                                                            |  |  |  |

| GPIO3         | L24        | 1.8V (VDDD)<br>GPIO | 40uA<br>Pull-Down    | Firmware controlled 1.8V digital GPIO float for proper operation. Assigned to ARM MAC GP2-2. (LED2/TR_SW_Bar)                                                        |  |  |  |

| GPIO1         | L23        | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO float for proper operation. Assigned to ARM MAC GP2-15 (FAA_HDRn).                                                             |  |  |  |

| GP1_3         | M22        | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO Assigned to ARM MAC GP1-3. Float for proper operation.                                                                         |  |  |  |

| GP1_7         | K23        | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO Assigned to ARM MAC GP1-7. Float for proper operation.                                                                         |  |  |  |

| GP2_13        | H22        | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO Assigned to ARM MAC GP2-13. Float for proper operation.                                                                        |  |  |  |

| GP2_12        | C16        | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO Assigned to ARM MAC GP2-12. Float for proper operation.                                                                        |  |  |  |

Pin descriptions STLC4420A

Table 1. STLC4420A signal descriptions (continued)

| Pin name | Pin number                                                                                                               | Туре                | Internal<br>resistor | Function                                                                                                                                                          |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GP2_10   | C17                                                                                                                      | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO Assigned to ARM MAC GP2-10. Float for proper operation.                                                                     |  |  |  |

| GP2_9    | C18                                                                                                                      | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO Assigned to ARM MAC GP2-9. Float for proper operation.                                                                      |  |  |  |

| GP1_4    | C23                                                                                                                      | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO Assigned to ARM MAC GP1-4. Float for proper operation.                                                                      |  |  |  |

| GP2_8    | A22                                                                                                                      | 1.8V (VDDD)<br>GPIO | No Pull              | Firmware controlled 1.8V digital GPIO Assigned to ARM MAC GP2-8. Float for proper operation.                                                                      |  |  |  |

| I_TEST-  | B9                                                                                                                       |                     | -                    |                                                                                                                                                                   |  |  |  |

| I_TEST+  | A9                                                                                                                       | 1                   | -                    | Reserved analog test pins float for proper                                                                                                                        |  |  |  |

| Q_TEST-  | B10                                                                                                                      | Reserved            | -                    | operation.                                                                                                                                                        |  |  |  |

| Q_TEST+  | A10                                                                                                                      |                     | -                    |                                                                                                                                                                   |  |  |  |

| VCO_CAP  | A7                                                                                                                       | Miscellaneous       | -                    | RF VCO core decoupling pin. Decouple this pin through a ceramic capacitor to VDD_VCO pin A6. Refer to evaluation platform schematics for optimal capacitor value. |  |  |  |

| VCO_LOOP | A5                                                                                                                       | Miscellaneous       | -                    | VCO loop filter pin. Connect this pin to thru a loop filter network to VDD_VCO pin A6. Refer to evaluation platform schematics for optimal filter network.        |  |  |  |

| EMU_SCL  | D23                                                                                                                      | Miscellaneous       |                      | Optional EMU programming I2C clock                                                                                                                                |  |  |  |

| EMU_SDA  | C24                                                                                                                      | Miscellaneous       |                      | Optional EMU programming I2C data/address                                                                                                                         |  |  |  |

| RSRV_GND | K24                                                                                                                      | Reserved            | -                    | Reserved pin. Connect to ground plane for proper operation.                                                                                                       |  |  |  |

| RSRV_NC  | D14, D16,<br>G14, H14,<br>H16, J14,<br>K16, L1, L2,<br>L4, L5, L7,<br>M4, M8, M10,<br>N19, N23,<br>F23, L21, L19,<br>K14 | Reserved            | -                    | Reserved pins. Float for proper operation.                                                                                                                        |  |  |  |

| TCLK     | L20                                                                                                                      | JTAG                | Pull-Up              | JTAG clock                                                                                                                                                        |  |  |  |

| TDI      | K22                                                                                                                      | JTAG                | No-Pull              | JTAG data input                                                                                                                                                   |  |  |  |

| TDO      | H24                                                                                                                      | JTAG                | No-Pull              | JTAG data output                                                                                                                                                  |  |  |  |

| TMS      | N20                                                                                                                      | JTAG                | Pull-Up              | JTAG test mode select                                                                                                                                             |  |  |  |

| TRSTN    | N22                                                                                                                      | JTAG                | Pull-Up              | JTAG reset                                                                                                                                                        |  |  |  |

|          | 1                                                                                                                        | I.                  | 1                    | 1                                                                                                                                                                 |  |  |  |

STLC4420A Pin descriptions

Table 1. STLC4420A signal descriptions (continued)

| Pin name  | Pin number | Туре                          | Internal<br>resistor | Function           |

|-----------|------------|-------------------------------|----------------------|--------------------|

| UART_SIN  | A21        | 1.8V (VDDD)<br>digital input  | Pull-Down            | UART serial input  |

| UART_SOUT | C20        | 1.8V (VDDD)<br>digital output | No-Pull              | UART serial output |

# 3 Electrical specifications

Note: The STLC4420 has an ESD classification of Class TBD.

Warning: Stresses above those listed in the "Absolute Maximum

Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied.

Table 2. General electrical specifications

| Parameter                                   |                               | Test condition / comment                                                                                                                                                                  | Min. | Тур. | Max.                  | Units |

|---------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------------|-------|

| Absolute ma                                 | aximum ratings                |                                                                                                                                                                                           |      |      |                       |       |

| PMU VBATT                                   | (V <sub>cc</sub> )            |                                                                                                                                                                                           | -0.3 | -    | 7.0                   | V     |

| Voltage on a                                | ny other pin                  | Within shared voltage rails                                                                                                                                                               | -0.3 | -    | V <sub>cc</sub> + 0.3 | V     |

| V <sub>cc</sub> to V <sub>cc</sub> decouple |                               |                                                                                                                                                                                           | -0.3 | -    | +0.3                  | V     |

| Any GND to                                  | GND                           |                                                                                                                                                                                           | -0.3 | -    | +0.3                  | V     |

| Operating c                                 | onditions and input po        | ower specifications                                                                                                                                                                       |      |      |                       |       |

| Operating                                   | g temperature range           |                                                                                                                                                                                           | -30  |      | 85                    | °C    |

|                                             | Input supply voltage          | Power Management Unit VBATT supply input                                                                                                                                                  | 3.0  | 3.6  | 5.5                   | ٧     |

| VBATT                                       | Average continuous tx current | Continuous Transmitting @ 54Mbps, VBATT = 3.6 V                                                                                                                                           |      | TBD  |                       | mA    |

| supply                                      | Average continue rx current   | Receiving Valid Packets @ 54Mbps, VBATT = 3.6 V                                                                                                                                           |      | TBD  |                       | mA    |

|                                             | Average standby mode current  | VBATT = 3.6 V                                                                                                                                                                             |      | 85   |                       | μΑ    |

| VDIG                                        | Input supply voltage          | Power management unit VDIG supply for digital buffers                                                                                                                                     | 3    | 3.6  | VBATT                 | V     |

| supply                                      | Input supply current          | VDIG = 3.6 V, Typical load is application dependent                                                                                                                                       | -    | -    | -                     | mA    |

| VIO<br>supply                               | Input supply voltage          | VIO input supply determines Host<br>CMOS logic levels for:<br>SPI_CSX, SPI_CLK, SPI_DIN,<br>SPI_DOUT, HOST_IRQ,<br>SLEEP_CLK, FREQ, RF_ACTIVE,<br>STATUS, TX_CONF,<br>GPIO4, GPIO5, GPIO6 | 1.62 | 1.8  | 1.98                  | V     |

|                                             | Input supply current          | VIO = 1.8 V                                                                                                                                                                               | -    | -    | 10                    | mA    |

Table 2. General electrical specifications (continued)

| Parameter                     |                                   | Test condition / comment                                         | Min.                    | Тур.                 | Max.                    | Units |

|-------------------------------|-----------------------------------|------------------------------------------------------------------|-------------------------|----------------------|-------------------------|-------|

| Internal power                | er management unit (              | PMU) specifications                                              | 1                       |                      |                         |       |

| PMU_CREF                      |                                   | PMU reference capacitor                                          | -30%                    | 1                    | +30%                    | uF    |

| PMU_RSET                      |                                   | PMU reference resistor                                           | -1%                     | 1                    | +1%                     | MΩ    |

|                               | Output Voltage                    | Active Mode<br>Low Power Mode                                    | 1.757<br>1.759          | 1.8<br>1.8           | 1.841<br>1.847          | V     |

| V1OUT<br>Linear<br>Regulator  | Peak Output Current               | Active Mode<br>Low Power Mode                                    |                         |                      | 50<br>5                 | mA    |

|                               | External Output<br>Load Capacitor | Typical ESR = 0.1 ohm                                            | -35%                    | 1                    | +35%                    | uF    |

| \ (0.01.IT                    | Output Voltage                    | Active Mode<br>Low Power Mode                                    | 1.759<br>1.74           | 1.8<br>1.8           | 1.844<br>1.860          | ٧     |

| V2OUT<br>Linear<br>Regulator  | Peak Output Current               | Active Mode<br>Low Power Mode                                    |                         |                      | 300<br>5                | mA    |

| 3                             | External Output<br>Load Capacitor | Typical ESR = 0.1 ohm                                            | -35%                    | 2.2                  | +35%                    | uF    |

| VOVOLIT                       | Output Voltage                    | Active Mode<br>Low Power Mode                                    | 1.159<br>1.150          | 1.2<br>1.2           | 1.244<br>1.250          | ٧     |

| V2XOUT<br>Linear<br>Regulator | Peak Output Current               | Active Mode<br>Low Power Mode                                    |                         |                      | 280<br>20               | mA    |

| 3                             | External Output<br>Load Capacitor | Typical ESR = 0.1 ohm                                            | -35%                    | 2.2                  | +35%                    | uF    |

| V4OUT<br>Linear               | Output Voltage                    | Active Mode: V4_OUTSEL=0 V4_OUTSEL=1 Low Power Mode: V4_OUTSEL=0 | 2.726<br>3.016<br>2.726 | 2.81<br>3.11<br>2.81 | 2.894<br>3.203<br>2.894 | V     |

| Regulator                     |                                   | V4_OUTSEL=1                                                      | 3.016                   | 3.11                 | 3.203                   |       |

|                               | Peak Output Current               | Active Mode<br>Low Power Mode                                    |                         |                      | 30<br>5                 | mA    |

|                               | External Output<br>Load Capacitor | Typical ESR = 0.1 ohm                                            | -35%                    | 1                    | +35%                    | uF    |

| Receiver spe                  | cifications 802.11b/g             | (802.11a TBC)                                                    |                         |                      |                         | _     |

|                               | RX RF Frequency                   | 802.11 b/g                                                       | 2300                    |                      | 2500                    | MI-   |

|                               | Range                             | 802.11 a                                                         | 4900                    |                      | 5850                    | MHz   |

|                               | RX LO Frequency<br>Range          |                                                                  | 4600                    |                      | 5000                    | MHz   |

|                               | RF Input VSWR                     | Differential, 100 Ohms reference                                 | 2:1                     |                      |                         |       |

|                               | RX LO Phaser Jitter               | 50KHz to 10MHz, RMS LO/2                                         |                         | 1.25                 |                         | Deg   |

Table 2. General electrical specifications (continued)

| Parameter                                   | Test condition / comment                                      | Min. | Тур. | Max. | Units |

|---------------------------------------------|---------------------------------------------------------------|------|------|------|-------|

| LO to LNA Input                             | At LO/2 Frequency. RF front end properly matched and isolated |      |      | -70  | dBm   |

| Feed through                                | At LO Frequency. RF front end properly matched and isolated   |      |      | -50  | dBm   |

| Maximum RX input<br>Level                   | b/g Band only. RF front end properly matched                  | -23  | -10  |      | dBm   |

| Adjacent                                    | CCK CH6                                                       | 35   | 37   |      |       |

| ChannelRejection                            | OFDM 54Mbits Ch6                                              | -1   | 11   |      |       |

| TX to RX Input<br>Leakage                   | During transmit mode, affecting TX distortion                 |      | +5   |      | dBm   |

| DSB NF                                      | High Gain RX Mode, -90dBm input,                              |      | 5    | 7    | dB    |

| IP3 Input                                   | b and g Band only, front end losses                           | -17  | -16  |      | dBm   |

| IP2 Input                                   | not included                                                  |      | +13  |      | dBm   |

| DSB NF                                      | Low Gain RX Mode, -20dBm input,                               |      | 29.8 |      | dB    |

| IP3 Input                                   | b and g Band only, front end losses                           |      | +9   |      | dBm   |

| IP2 Input                                   | not included                                                  |      | +33  |      | dBm   |

| RF Hi/Lo Gain<br>Switching Point            | b/g Band only. RF front end properly matched.                 |      | -38  |      | dBm   |

|                                             | 6Mbps OFDM, 10% PER                                           | -85  | -90  |      | dBm   |

|                                             | 9Mbps OFDM, 10% PER                                           |      | -88  |      | dBm   |

|                                             | 12Mbps OFDM, 10% PER                                          |      | -87  |      | dBm   |

|                                             | 18Mbps OFDM, 10% PER                                          |      | -84  |      | dBm   |

| Doggive Consistivity                        | 24Mbps OFDM, 10% PER                                          |      | -80  |      | dBm   |

| Receive Sensitivity,<br>b and g band, front | 36Mbps OFDM, 10% PER                                          |      | -76  |      | dBm   |

| end losses not                              | 48Mbps OFDM, 10% PER                                          |      | -73  |      | dBm   |

| included                                    | 54Mbps OFDM, 10% PER                                          | -68  | -71  |      | dBm   |

|                                             | 1Mbps BPSK, 8% PER                                            | -89  | -96  |      | dBm   |

|                                             | 2Mbps QPSK, 8% PER                                            |      | -91  |      | dBm   |

|                                             | 5.5Mbps CCK, 8% PER                                           |      | -90  |      | dBm   |

|                                             | 11Mbps CCK, 8% PER                                            | -82  | -86  |      | dBm   |

Table 2. General electrical specifications (continued)

| Parameter                 |          | Test condition / comment                                | Min. | Тур. | Max.   | Units  |

|---------------------------|----------|---------------------------------------------------------|------|------|--------|--------|

|                           |          | 6Mbps, 10% PER                                          |      | 820  |        | ns     |

|                           |          | 9Mbps, 10% PER                                          |      | 430  |        | ns     |

|                           |          | 12Mbps, 10% PER                                         |      | 630  |        | ns     |

|                           |          | 18Mbps, 10% PER                                         |      | 405  |        | ns     |

| NAL JAIL - ALL D          | la       | 24Mbps, 10% PER                                         |      | 320  |        | ns     |

| Multipath De<br>Spread    | eiay     | 36Mbps, 10% PER                                         |      | 210  |        | ns     |

|                           |          | 48Mbps,10% PER                                          |      | 160  |        | ns     |

|                           |          | 54Mbps, 10% PER                                         |      | 120  |        | ns     |

|                           |          | 1Mbps BPSK and 2Mbps QPSK,<br>8% PER                    |      | 250  |        | ns     |

|                           |          | 5.5 and 11Mbps CCK, 8% PER                              |      | 100  |        | ns     |

| Transmitter specification | s 802.11 | b/g (802.11a <mark>TBC</mark> )                         |      | •    |        |        |

| TX RF Frequ               | iency    | 802.11 b/g                                              | 2300 |      | 2500   |        |

| Range                     | ,        | 802.11 a                                                | 4900 |      | 5850   | MHz    |

| TX LO Frequ<br>Range      | iency    |                                                         | 4600 |      | 5000   | MHz    |

| RF Output V               | SWR      | Note: Over AGC range, b and g<br>Bands only             |      |      | 2:1    |        |

| TX LO Phas                | e Jitter | 50KHz to 10MHz, RMS, LO/2                               |      | 1.25 |        | Deg    |

| TX AGC Cor<br>Dynamic Ra  |          |                                                         | 40   |      |        | dB     |

| TX AGC Cor<br>Step Size   | ntrol    | Monotonic                                               |      |      | 2      | dBm    |

| CCK Output                | Power    | At 0 control attenuation. RF front end properly matched | 5    |      | 8      | dBm    |

| CCK Output                | Power    | Case 1: Set TX AGC to obtain this                       |      | 3    |        | dBm    |

| OFDM Outpu                | ut Power | Pout.                                                   |      | -6   |        | dBm    |

|                           |          |                                                         |      |      | -135   | dBm/Hz |

| Output Noise              | e Floor  | Carrier offsets 0 to 10MHz Carrier offsets >20MHz       |      |      | -138   | dBm/Hz |

| CCK Output                | Power    | Case 2: Set TX AGC to obtain this                       |      | -7   |        | dBm    |

| OFDM Outpu                | ut Power | Pout                                                    |      | -16  |        | dBm    |

|                           |          |                                                         |      |      | -137.5 | dBm/Hz |

| Output Noise              | e Floor  | Carrier offsets 0 to 10MHz Carrier offsets >20MHz       |      |      | -140.5 | dBm/Hz |

Table 2. General electrical specifications (continued)

| Parameter                                                         | Test condition / comment                                               | Min. | Тур. | Max.   | Units  |

|-------------------------------------------------------------------|------------------------------------------------------------------------|------|------|--------|--------|

| CCK Output Power                                                  | Case 3: Set TX AGC to obtain this                                      |      | -17  |        | dBm    |

| OFDM Output Power                                                 | Pout                                                                   |      | -26  |        | dBm    |

|                                                                   |                                                                        |      |      | -140   | dBm/Hz |

| Output Noise Floor                                                | Carrier offsets 0 to 10MHz Carrier offsets >20MHz                      |      |      | -143   | dBm/Hz |

| CCK Output Power                                                  | Case 4: Set TX AGC to obtain this                                      |      | -27  |        | dBm    |

| OFDM Output Power                                                 | Pout                                                                   |      | -36  |        | dBm    |

|                                                                   |                                                                        |      |      | -142.5 | dBm/Hz |

| Output Noise Floor                                                | Carrier offsets 0 to 10 MHz<br>Carrier offsets >20 MHz                 |      |      | -145.5 | dBm/Hz |

| CCK Output Power                                                  | Case 5: Set TX AGC to obtain this                                      |      | -37  |        | dBm    |

| OFDM output power                                                 | Pout                                                                   |      | -46  |        | dBm    |

|                                                                   |                                                                        |      |      | -145   | dBm/Hz |

| Output noise floor                                                | Carrier offsets 0 to 10 MHz Carrier offsets >20 MHz                    |      |      | -148   | dBm/Hz |

| External power amplifier detector                                 | ADC specifications                                                     |      |      | •      |        |

| Full scale input voltage                                          | At input of ADC                                                        | 0    |      | 1.0    | V      |

| Maximum input voltage                                             | At PA_DETx input 16 tap                                                |      |      | VDDA   | V      |

| Input resistance                                                  | resistive divider tap node                                             |      | 30K  |        | Ohm    |

| Input capacitance                                                 |                                                                        |      |      | 0.5    | pF     |

| External power amplifier BIAS DA                                  | C specifications                                                       |      |      | •      |        |

| Full scale output                                                 | At voltage output compliance > 1.8 V                                   |      | 2.5  |        | mA     |

| current                                                           | At voltage output compliance = 1.8 V                                   |      | 5    |        | mA     |

|                                                                   | At -40°C, full scale output<br>current < 2.5mA, VDD_BIAS =<br>3.15 V   |      |      | 2.85   | V      |

| Output voltage compliance Note: An external                       | At +25°C, full scale output<br>current < 2.5mA, VDD_BIAS =<br>3.15 V   |      |      | 2.75   | V      |

| resistor at PA_RREF pin determines the full scale output current. | At +100°C, full scale output<br>current < 2.5mA, VDD_BIAS =<br>3.15 V  |      |      | 2.55   | V      |

|                                                                   | Full temperature range, scale output current <= 5mA, VDD_BIAS = 3.15 V |      |      | 1.8    | V      |

Table 2. General electrical specifications (continued)

| Parameter |                         | Test condition / comment                                                      | Min. | Тур. | Max. | Units |

|-----------|-------------------------|-------------------------------------------------------------------------------|------|------|------|-------|

|           | BIAS DAC supply voltage |                                                                               | 2.8  |      | 3.15 | V     |

| Tdod      | Tdod                    | SPI_DOUT delay from transmit edge of SPI_CLK                                  | 0    |      | 7    | ns    |

| SPI_DOUT  | Tdozh                   | SPI_DOUT delay before HI-Z state from rising edge of SPI_CSX                  | 0    |      |      | ns    |

|           | Tdozd                   | SPI_DOUT delay before driven<br>from HI-Z state on falling edge of<br>SPI_CSX |      |      | 10   | ns    |

Table 3. Host interface specifications

| Table 3.             | Host interface s   | pecifications                          |           |        | 1         |        |

|----------------------|--------------------|----------------------------------------|-----------|--------|-----------|--------|

| Pa                   | rameter            | Test condition / comment               | Min.      | Тур.   | Max.      | Units  |

| Digital interfa      | ce specifications  | 3                                      |           |        |           |        |

| POWER UP             | VIH                | PMU Power up control. Active High.     | 0.8       | -      | VBATT     | V      |

| Input                | VIL                |                                        | 0         | -      | 0.3       | V      |

|                      | Pull-Down          |                                        | -         | 500    | -         | K ohms |

| Host CMOS            | VIH                | VIO supply domain                      | 0.7*VIO   | -      | VIO + 0.3 | V      |

| Inputs               | VIL                | VIO supply domain                      | 0         | -      | 0.3*VIO   | ٧      |

|                      | VOH                | IOH = 0.2mA, VIO supply domain         | VIO - 0.2 | -      | VIO       | V      |

| Host CMOS<br>Outputs | VOL                | IOL = 6mA, VIO supply domain           | 0         | -      | 0.6       | V      |

| Outputs              | Input Current      | VIO supply domain                      | -1.0      | -      | +1.0      | μΑ     |

| OSC_EN               | VOH                | IOH <= 2mA                             | 1.4       | -      | -         | V      |

| Input                | VOL                | IOL <= 2mA                             | -         | -      | 0.4       | V      |

| REF_CLK              | Input Level        | AC accorded                            | 500       | -      | 1000      | mVpp   |

| Input                | Accuracy           | AC coupled                             | -         | -      | 25        | ppm    |

|                      | Frequency          |                                        | -         | 32.768 | -         | kHz    |

| SLEEP_CLK<br>Input   | Accuracy           | VIO supply domain                      | -         | -      | 150       | ppm    |

| pat                  | Duty Cycle         |                                        | 30        | -      | 70        | %      |

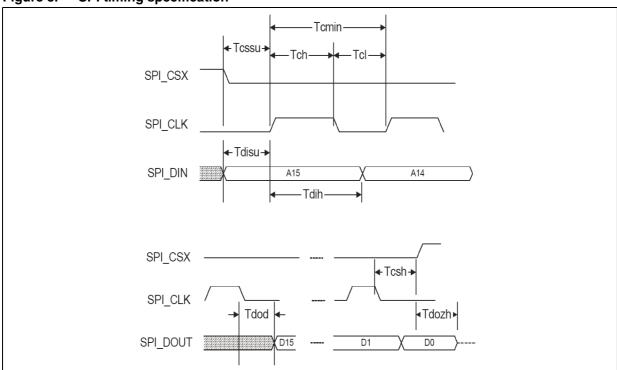

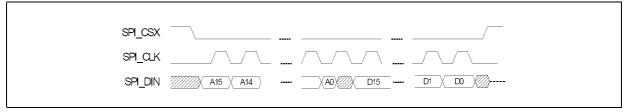

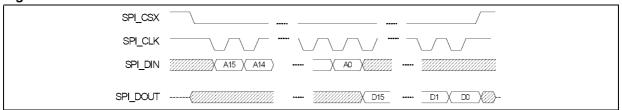

| SPI timing sp        | ecifications (refe | r to <i>Figure 3</i> )                 |           |        |           |        |

|                      | Tcmin              | SPI_CLK Period                         | 20.8      |        |           | ns     |

| SPI_CLK              | Tch                | SPI_CLK High Time                      | 10.4      |        |           | ns     |

|                      | Tcl                | SPI_CLK Low Time                       | 10.4      |        |           | ns     |

| SPI_CSX              | Tcssu              | SPI_CSX Setup time to first clock edge | 10.4      |        |           | ns     |

|                      | Tcsh               | SPI_CSX hold time from last clock edge | 10.4      |        |           | ns     |

Table 3. Host interface specifications

| SPI DIN   | Tdisu | SPI_DIN setup time to receive edge of SPI_CLK | 3 |  | ns |

|-----------|-------|-----------------------------------------------|---|--|----|

| Si I_Diiv | Tdih  | SPI_DIN hold time to receive edge of SPI_CLK  | 0 |  | ns |

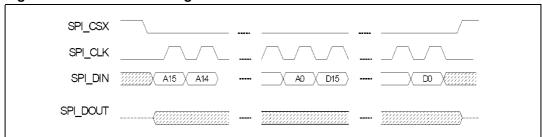

Figure 3. SPI timing specification

STLC4420A Serial host interface

#### 4 Serial host interface

#### 4.1 Host pins

The Serial Host Interface consists of the following pins:

- SPI\_CLK: serial host clock input, 0 to 48 MHz.

- SPI\_DIN: serial host data input, sampled on active edge of SPI\_CLK.

- SPI\_DOUT: serial host data output, driven when asserted low and floating when deasserted. SPI\_DOUT is driven on inactive edge of SPI\_CLK.

- SPI\_CSX: serial host chip select, active low chip select.

- HOST\_IRQ: serial host interrupt, active high interrupt to Host.

The serial host interface has 12 modes of operation controlled by 4 variables. The default 4-Wire mode may be changed by a SPI host write to the device status/ control register. If the host requires a different SPI mode for normal operation, the host may need to toggle the necessary SPI pins using GPIO-style interfacing to perform a 4-Wire write sequence to change the mode.

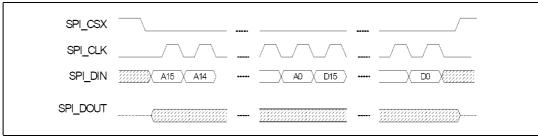

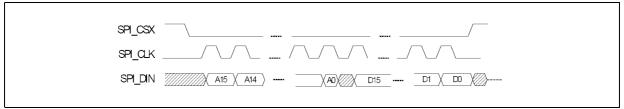

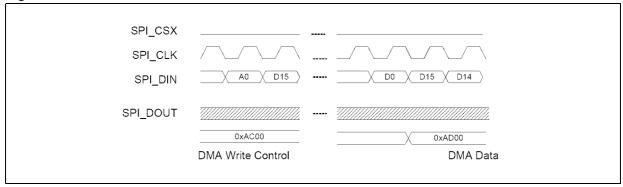

The default 4-Wire single word write is show below in Figure 4.

Figure 4. 4-Wire mode single word write

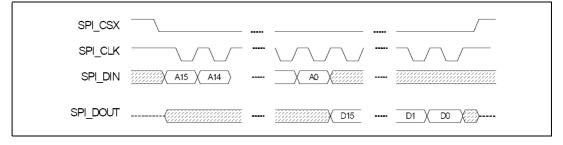

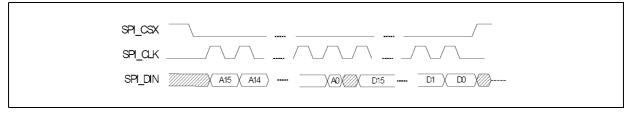

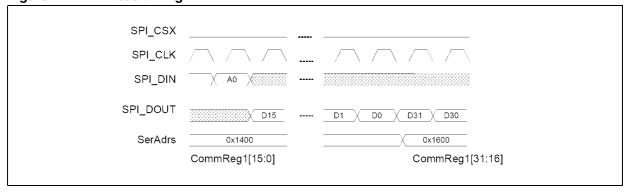

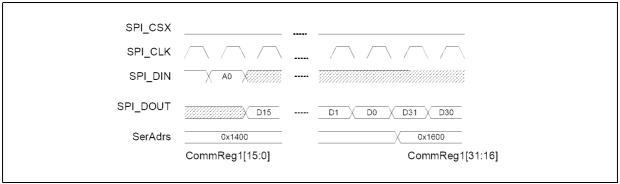

The default 4-Wire single word read is shown below in *Figure 5*.

Figure 5. 4-Wire mode single word read

Serial host interface STLC4420A

#### 4.2 SPI mode selection

As shown in *Table 4*, the 12 modes of operation are controlled by 4 variables in the device status/control register.

Table 4. Serial host modes of operation

| Invert Clock | Phase Shift | 3-Wire-Mode | 3-Wire-Adr DataWait | Name               |

|--------------|-------------|-------------|---------------------|--------------------|

| 0            | 0           | 0           | Х                   | 4-Wire             |

| 1            | 0           | 0           | Х                   | 4-WireInv          |

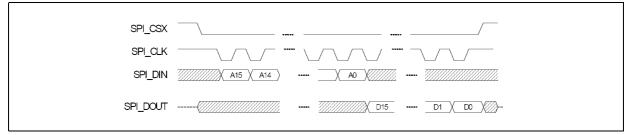

| 0            | 1           | 0           | Х                   | 4WShft             |

| 1            | 1           | 0           | Х                   | 4-WireInvShft      |

| 0            | 0           | 1           | 0                   | 3-Wire             |

| 1            | 0           | 1           | 0                   | 3-Wirelnv          |

| 0            | 1           | 1           | 0                   | 3-WireShft         |

| 1            | 1           | 1           | 0                   | 3-WireInvShft      |

| 0            | 0           | 1           | 1                   | 3-WireWait1        |

| 1            | 0           | 1           | 1                   | 3-WireInvWait1     |

| 0            | 1           | 1           | 1                   | 3-WireShftWait1    |

| 1            | 1           | 1           | 1                   | 3-WireInvShftWait1 |

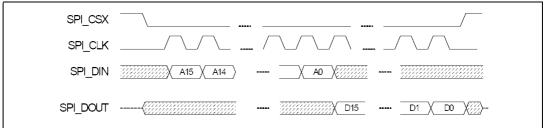

When Invert Clock = 0, SPI\_CLK receive edge is the rising edge and SPI\_CLK transmit edge is the falling edge.

The SPI\_CLK polarity can be reversed by a host write to device status/control register to change the Invert Clock = 1.

In this case, the SPI\_CLK transmit edge becomes the rising edge and SPI\_CLK receive edge becomes the falling edge.

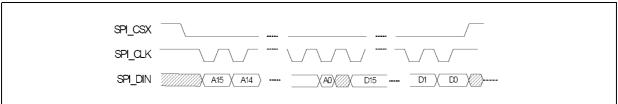

Figure 6. Single Word Read 4-WirelnvMode

Figure 7. Single Word Read 4-WireShftMode

STLC4420A Serial host interface

Figure 8. Single Word Read 4-WirelnvShftMode

Figure 9. 3-Wire

Figure 10. 3-Wirelnv

Figure 11. 3-WireShft

Figure 12. 3-WireInvShft

Figure 13. 3-WireWait1

Serial host interface STLC4420A

Figure 14. 3-WireInvWait1

Figure 15. 3-WireShiftWait1

Figure 16. 3-WireInvShftWait1

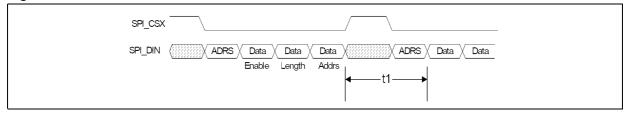

#### 4.3 AHB masters

The DMA engines are contained within the Serial Host interface. The DMA engines access data on the device via a pair of AHB masters. AHB1 is connected to the standard AHB bus which is shared with the CPU and DMA controller AHB masters.

The Serial Host has a second AHB master connected to the AHB Ram directly via a AHB2. The Serial Host AHB2 master and the AHB Ram AHB2 slave are the only master and slave on the AHB2 bus. This guarantees sufficient bandwidth for the serial host interface.

When the AHB master is accessing APB registers the ApbAccess bit must be set to force the master to use word (32-bit) transfers so that the APB registers are not set to an indeterminate state by a pair of half-word (16-bit) transfers.

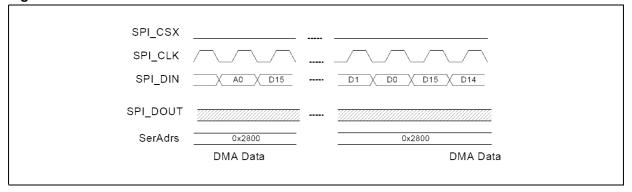

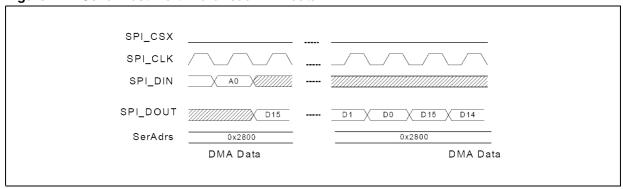

DMA read data is prefetched when the DMA Read Address is written and the DMA Write Enable is asserted. The host must not read DMA Data register before the prefetch completes. There must be 20 ABClock cycles between the end the Data Phase when DMA Read Address is written and the end of Address Phase which selects the DMA Read register.

STLC4420A Serial host interface

Figure 17. AHB bus timing

The read data is registered on the 15 SPI\_CLK of the address phase. SPI\_CSX high time must be 20ABClocks - 15SPI\_CLKs. If ABClock period is 100ns (10 MHz) and SPI\_CLK period is 40ns then the time between writing DMA write address register and reading the DMA data register is (20 \* 100) - (15 \* 40) = 1.4us. If the ABClock period is 25ns (40 MHz) then SPI\_CSX high time is < 0 for Read data to be valid. In this case, only the Min High time for SPI\_CSX must be observed.

#### 4.4 Host registers

The Host can access the registers listed in *Table 5*.

Table 5. Host registers

| Domain  | A14-A8               | Access | Sleep access | Description                | Notes    |

|---------|----------------------|--------|--------------|----------------------------|----------|

| SPI_CLK | X00 0000<br>X00 0010 | RW     | RW           | ARM interrupt              | (1), (2) |