### 1.0625GHz CMOS Fibre Channel Transceiver

### **General Description**

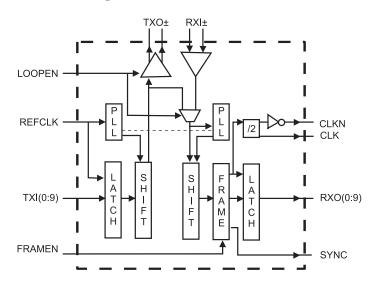

The ICS9536-01 is an integrated 1GHz CMOS fibre channel transceiver, including TX clock generation and 10-bit parallel to serial conversion plus RX clock recovery and serial to 10-bit parallel conversion, with comma character recognition and selectable frame synchronization. An internal loop-back function provides aid in system evaluation and testing.

The ICS9536-01 supports data rates up to 1.0625GHz and is fully compliant with ANSI X3.230-1994 (FC-0) standards. The device is pin compatible with standard transceivers but offers significantly lower cost when compared to bipolar or GaAs technologies.

### **Features**

- CMOS technology provides lowest cost

- Pin compatible with HDMP-1536 (Bipolar) and VSC7125 (GaAs) fibre channel transceivers

- ANSI X3.230-1994 (FC-0) compliant

- 1.0625GHz differential transmit and receive

- 106.25MHz 10-bit parallel data interface

- Integrated PLLs require no external components

- Large Transmit output swing

- 64 pinTQFP package, 10x10mm body, 1mm high

### **Block Diagram**

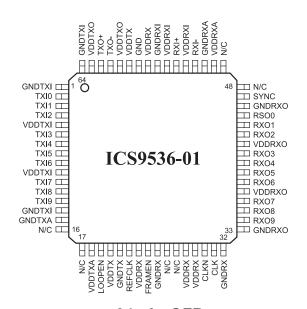

### Pin Configuration

64-pin QFP

### **Functionality**

3.15-3.45V,0-70°C REFCLK=106.25MHz

| LOOPEN | FRAMEN | TXO    | RXI    | SYNC   | OPERATING MODE                  |

|--------|--------|--------|--------|--------|---------------------------------|

| 0      | 0      | Active | Active | Static | TX and RX without Byte Sync     |

| 0      | 1      | Active | Active | Active | TX and RX with Byte Sync        |

| 1      | 0      | Active | Ignore | Static | Internal loopback W/O Byte Sync |

| 1      | 1      | Active | Ignore | Active | Internal loopback W/Byte Sync   |

### **Transmitter Functional Description:**

The transmitter accepts 10-bit wide TTL parallel data over a high speed line, as specified for the FC-0 layer of the Fibre Channel standard. Per the Fibre Channel specification, the parallel data is expected to be coded using an 8B/10B encoding scheme with special reserve characters required for link management purposes.

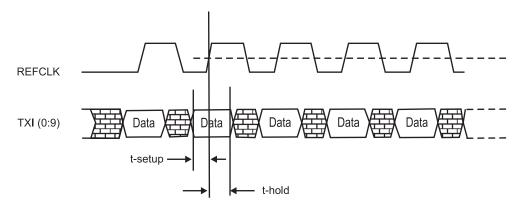

#### **Transmitter Clocking:**

The transmitter clock, REFCLK, is based on a user supplied reference clock. The clock recovery implemented in the receiver multiplies the REFCLK input frequency of 106.25MHz to 1062.5MHz. It is expected to be 106.25MHz and be properly aligned to the incoming parallel 10 bit wide TTL data at inputs TXI (0:9). The Transmitter Section Timing section illustrates clocking data into the transmit input bus which is latched on the positive edge of REFCLK. A PLL clock multiplier from REFCLK is used to synthesize the 1062.5MHz clock necessary for the high speed serial transmitter output.

#### Transmission Character Interface:

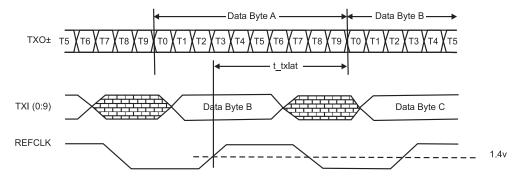

An encoded 10 bit word is defined as a transmission character. This 10 bit character, or transmission character is latched on the rising edge of REFCLK. The data is serialized, where the parallel data, TXI (0:9), is multiplexed into the 1062.5MB serial data stream and transmitted on the TX differential outputs at a baud rate of ten times the frequency of the REFCLK input. TXI (0) is transmitted first and represents the least significant bit, TXI (9) is the most significant bit which is transmitted last.

Figure 1 illustrates the Mapping of the Transmission Character.

(53.125MHz) where a rising transition of either CLK or CLKN corresponds to a new word on the receiver output RXO(0:9). These byte clocks are 180 degrees out of phase with each other and are designed such that demultiplexing of a 10-bit data characters into a 20-bit halfword in the controller chip is straightfoward. The ICS9536-01 will continue to generate all the output clocks even if input data is not present. The CLK and CLKN output frequency cannot differ from their expected frequency by not more than +-1.5%.

#### Frame Demux, Byte Sync

By asserting FRAMEN high, received data synchronization is enabled such that the ICS9536-01 constantly examines the serial data for the presence of the "comma" character, "0011111XXX". Realignment of the 7-bit comma character will occur if the "comma" character's value is shifted in time relative to CLK and CLKN. More specifically, realignment will occur if the comma is not aligned with the rising edge of CLKN (or falling edge of CLK), or the comma straddles the boundary between two 10-bit transmission characters.

When FRAMEN is asserted, a comma character is detected and realignment of the receiver byte clocks , CLK and CKLN, may be necessary. These clocks will be fully aligned by the start of the second 4-byte set of data, such that the second comma character received will be aligned with the rising edge of CLKN. When a comma character is encountered, and comma character is correctly aligned SYNC output is driven high, indicating that a possible realignment of the data may have occurred. The SYNC pulse is driven high, during the comma character, for a duration equal to one word of data, or one half of an CLK period.

Figure 1: Transmission Order and Mapping to Fibre Channel Character

### **Receiver Functional Description:**

The receiver in the ICS9536-01 receives serial input data, and establishes the correct frequency and phase relationships by recovering the bit and byte clocks.

#### **Receiver Clocking:**

The receive PLL phase aligns with the incoming data. The recovered clocks are one twentieth of the receiver data stream

### **Output and Input Selection:**

Enabling LOOPEN provides for internal loopback of the high speed serial input signal to the receiver. When the loop back feature is enabled the transmit output pins (TXO+-) toggles at the incoming data rate and the receiver's input multiplexer switches to receive the transmit serial output. This function is used for system testing exclusive of the transmission medium.

# **Transmitter Timing Characteristics**

$T_a = 0$ °C to +70°C,  $V_{DD} = 3.15$ V to 3.45V

| Symbol                              | Parameter                                                   | Min. | Тур. | Max. | Units |

|-------------------------------------|-------------------------------------------------------------|------|------|------|-------|

| t <sub>setup</sub>                  | Setup Time to Rising Edge of REFCLK                         | 2    |      |      | nsec  |

| t <sub>sdr</sub> , t <sub>sdf</sub> | TXO+/TXO- rise and fall time 20% to 80%, 75 Ohm load to Vss | -    | -    | TBD  | pS    |

| t <sub>rd,TXO</sub>                 | TXO Differential Rise Time                                  | -    | TBD  | -    | nsec  |

| t <sub>fd,TXO</sub>                 | TXO Differential Fall Time                                  | 1    | TBD  | -    | nsec  |

| V <sub>OP, TXO</sub>                | TXO Output Peak-To-Peak Differential Voltage                | -    | TBD  |      | mV    |

| t_txlat1                            | Transmitter Latency                                         |      | TBD  |      | nsec  |

| thold                               | Hold Time to Rising Edge of REFCLK                          | 1.5  |      |      | nsec  |

| t <sub>rj</sub>                     | Data Output Random Jitter                                   | -    | TBD  | -    | pS    |

| t <sub>dj</sub>                     | Data Output Deterministic Jitter                            | -    | TBD  |      | pS    |

Note 1. The transmitter latency, as shown in Figure 3, is defined as the time between the latching in of the parallel data word (as triggered by the rising edge of the transmit byte clock. REFCLK) and the transmission of the first serial bit, TXI (0), of that parallel word (defined by the rising edge of the first bit transmitted).

2. Tested per Fibre Channel 4.5 annex A, test method.

Figure 2: Transmitter Section Timing

Figure 3: Transmitter Latency

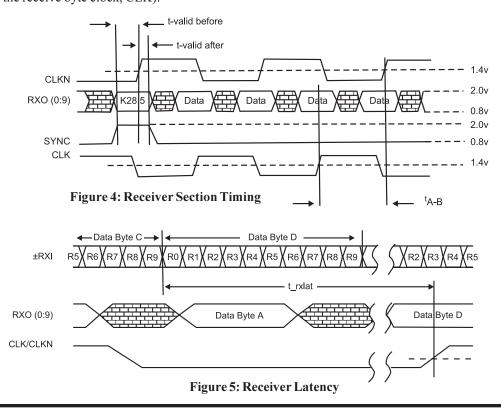

## **Receiver Timing Characteristics**

$T_a=0$ °C to +70°C,  $V_{DD}=3.15$ V to 3.45V

| Symbol                        | Parameter                                                                              |     | Тур. | Max. | Units    |

|-------------------------------|----------------------------------------------------------------------------------------|-----|------|------|----------|

| b_sync1                       | Bit Sync time                                                                          |     |      | 2500 | bits     |

| f_lock                        | Frequency Lock time                                                                    |     |      | 500  | μsec     |

| f_lock_rate                   | Frequency Lock Rate                                                                    |     | TBD  |      | kHz/µsec |

| tvalid_before                 | Time data valid before rising edge of CLK                                              |     | TBD  |      | nsec     |

| tvalid_after                  | Time data valid after rising edge of CLK                                               |     | TBD  |      | nsec     |

| tduty                         | CLK Duty Cycle                                                                         | 40  |      | 60   | %        |

| t <sub>A-B</sub> <sup>2</sup> | Rising Edge time difference, Skew                                                      | 8.9 | 9.4  | 9.9  | nsec     |

| 4 . 3                         | Desciver Leterory                                                                      |     | TBD  |      | nsec     |

| t_rxlat <sup>3</sup>          | Receiver Latency                                                                       |     | TBD  |      | bits     |

| t <sub>4</sub>                | Devation of CLK, CLKN frequency from Nominal. $f_{CLK} = \frac{f_{REFCLK} \pm t_4}{2}$ | -   | TBD  | -    | %        |

#### **Notes:**

- 1. This is the recovery time for input phase jumps.

- 2. The CLK clock skew is calculated as t<sub>A-B</sub>(max) -t<sub>A-B</sub>(min).

- 3. The receiver latency, as shown in Figure 5, is defined as the time between receiving the first serial bit of a parallel data word (as defined as the first edge of the first serial) and the clocking out of that parallel word (defined by the rising edge of the receive byte clock, CLK).

# Pin Description ICS9536-01

| PIN NUMBER                         | PIN NAME  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 14                              | GNDTXI    | GND  | TTL Transmitter Ground: Normally 0 volts.                                                                                                                                                                                                                                                                                                                     |

| 2, 3, 4, 6, 7, 8, 9,<br>11, 12, 13 | TXI (0:9) | IN   | Data Inputs: One, 10 bit, pre-encoded data byte. TXI(0) is the first bit transmitted. TXI(0) is the least significant bit.                                                                                                                                                                                                                                    |

| 5, 10                              | VDDTXI    | PWR  | TTL Power Supply: Normally 3.3V. Used for all TTL transmitter input buffer cells.                                                                                                                                                                                                                                                                             |

| 15                                 | GNDTXA    | PWR  | Analog Ground: Normally 0V. Used to provide a clean ground plane for the PLL and high-speed analog cells.                                                                                                                                                                                                                                                     |

| 16, 17, 48, 49                     | N/C       | N/C  | Not connected                                                                                                                                                                                                                                                                                                                                                 |

| 18                                 | VDDTXA    | PWR  | Analog Power Supply: Normally 3.3V. Used to provide a clean supply line for the PLL and high speed analog cells.                                                                                                                                                                                                                                              |

| 19                                 | LOOPEN    | IN   | Loopback enable Input: When set high, the high speed serial signal is internally wrapped from the transmitter's serial loopback outputs back to the receiver's loopback inputs.                                                                                                                                                                               |

| 20, 59                             | VDDTX     | PWR  | Logic Power Supply: Normally 3.3V. Used for internal transmitter logic. It should be isolated from the noisy TTL supply as well as possible.                                                                                                                                                                                                                  |

| 21, 25, 58                         | GNDTX, RX | PWR  | Logic Ground: Normally 0V. This ground is used for internal logic. It should be isolated from the noisy TTL ground as well as possible. Pin 25 is GNDRX                                                                                                                                                                                                       |

| 22                                 | REFCLK    | IN   | Reference Clock and Transmit Byte Clock: A 106.25MHz clock supplied by the host system. The transmitter section accepts this signal as the frequency clock. It is multiplied by 10 to generate the serial bit clock and other internal clocks. The transmit side also uses this clock as the transmit byte clock for the incoming parallel data TXI(0)TXI(9). |

| 23, 28, 57                         | VDDRX     | PWR  | Logic Power Supply: Normally 3.3V. Used for internal receive logic. It should be isolated from the noisy TTL supply as well as possible.                                                                                                                                                                                                                      |

| 24                                 | FRAMEN    | IN   | Frame Enable Input: When high, turns on the internal byte sync function to allow clock synchronization to a comma character (or a K28.5 character) of positive disparity (0011111010). When the line is low, the function is disabled and will not reset registers and clocks, or strobe the SYNC line.                                                       |

# ICS9536-01

# **Preliminary Product Preview**

# Pin Description ICS9536-01 Continued:

| PIN NUMBER                             | PIN NAME     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29, 37, 42                             | VDDRX        | PWR  | TTL Power Supply: Normally 3.3V. Used for all TTL receiver output buffer cells.                                                                                                                                                                                                                                                         |

| 30, 31                                 | CLK<br>CLKN  | OUT  | Receiver Byte Clocks: The receiver section recovers two 53.125MHz receive byte clocks. These two clocks are approximately 180 degrees out of phase. Their receiver parallel data outputs are alternatively clocked on the rising edge of theese clocks. CLKN aligns and outputs the comma character (for byte alignment) when detected. |

| 32, 33, 46                             | GNDRX        | PWR  | TTL Receiver Ground: Normally 0V. Used for the TTL output cells of the receiver section.                                                                                                                                                                                                                                                |

| 45, 44, 43, 41, 40, 39, 38, 36, 35, 34 | RXO (0:9)    | OUT  | Data Outputs: One 10 bit data byte.                                                                                                                                                                                                                                                                                                     |

| 47                                     | SYNC         | OUT  | Byte Sync Output; An active high output. Used to indicate detection of either a comma character or a K28.5 special character of positive disparity. It is only active when FRAMEN is enable.                                                                                                                                            |

| 50                                     | VDDRXA       | PWR  | Analog Power Supply: Normally 3.3V. Used to provide a clean supply line for the PLL and high speed analog cells.                                                                                                                                                                                                                        |

| 51                                     | GNDRXA       | PWR  | Analog Ground: Normally 0V. Used to provide a clean ground plane for the receiver PLL and high-speed analog cells.                                                                                                                                                                                                                      |

| 52<br>54                               | RXI-<br>RXI+ | IN   | Serial Data Inputs: High speed inputs. Serial data is accepted from the inputs when LOOPEN is low.                                                                                                                                                                                                                                      |

| 53, 55                                 | VDDRXI       | PWR  | High Speed Supply: Normally 3.3V. Used only for the high speed reciever cell. Noise on this line should be minimized for best operation.                                                                                                                                                                                                |

| 56                                     | GNDRXI       | PWR  | Ground: Normally 0V.                                                                                                                                                                                                                                                                                                                    |

| 60, 63                                 | VDDTXO       | PWR  | High Speed Supply: Normally 3.3V. Used by the transmitter side for the high speed circuitry. Noise on this line should be minimized for best operation.                                                                                                                                                                                 |

| 61<br>62                               | +TXO<br>-TXO | OUT  | Serial Data Output                                                                                                                                                                                                                                                                                                                      |

| 64                                     | GNDTX        | PWR  | Ground: Normally 0V.                                                                                                                                                                                                                                                                                                                    |

### **Absolute Maximum Ratings**

Supply Voltage ...... 7.0 V

Logic Inputs . . . . . . . . . . . . . GND –0.5 V to  $\,$  V  $_{DD}$  +0.5 V

Ambient Operating Temperature . . . . . . . 0  $^{\circ}$  C to  $+70\,^{\circ}$  C

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

### **Guaranteed Operating Rates**

Ta=0°C to +70°C,  $V_{DD}=3.15$ V to 3.45V

|        | Clock Rate<br>Hz) | Serial Baud Rate<br>(MBaud) |        |  |  |

|--------|-------------------|-----------------------------|--------|--|--|

| Min.   | Max.              | Min.                        | Max.   |  |  |

| 106.20 | 106.30            | 1062.0                      | 1063.0 |  |  |

### Transceiver Reference Clock Requirements

Ta=0°C to +70°C,  $V_{DD}=3.15$ V to 3.45V

| Symbol | Parameter                                        | Min.   | Тур.   | Max    | Unit |

|--------|--------------------------------------------------|--------|--------|--------|------|

| f      | Nominal Frequency (for Fibre Channel Compliance) | 106.20 | 106.25 | 106.30 | MHz  |

| Ftol   | Frequency Tolerance                              | -100   |        | +100   | ppm  |

| Symm   | Symmetry                                         | 40     |        | 60     | %    |

### **AC Electrical Characteristics**

Ta=0°C to +70°C,  $V_{DD}=3.15$ V to 3.45V

| Symbol                | Parameter                                         | Min. | Typ. | Max | Unit |

|-----------------------|---------------------------------------------------|------|------|-----|------|

| t<br>r,TTLin          | Input TTL Rise Time, 0.8 to 2.0 volts             | -    | TBD  | -   | nsec |

| t <sub>f,TTLin</sub>  | Input TTL Fall Time, 2.0 to 0.8 Volts             | -    | TBD  | -   | nsec |

| t<br>r,TTLout         | Output TTL Rise Time, 0.8 to 2.0 Volts, 10pF load | -    | TBD  | 2.4 | nsec |

| t <sub>f,TTLout</sub> | Output TTL Fall Time, 2.0 to 0.8 Volts, 10pF load | -    | TBD  | 2.4 | nsec |

# ICS9536-01

# **Preliminary Product Preview**

### **DC Electrical Characteristics**

Ta=0°C to +70°C,  $V_{DD}=3.15V$  to 3.45V

| Symbol  | Parameter                                                           | Min. | Тур.  | Max             | Unit    |

|---------|---------------------------------------------------------------------|------|-------|-----------------|---------|

| VIH,TTL | TTL Input High Voltage Level, Guaranteed high signal for all inputs |      |       | Vdd             | V       |

| VIL,TTL | TTL Input Low Voltage Level, Guaranteed low signal for all inputs   | 0.0  |       | 0.8             | V       |

| Voh,ttl | TTL Output High Voltage Level, IOH = 400µA                          | 2.4  |       | V <sub>DD</sub> | V       |

| Vol,ttl | TTL Output Low Voltage Level, IOL = 1mA                             | 0    |       | 0.6             | V       |

| ΔVOUT75 | Serial Output voltage swing (TXO+/TXO-) with 50Ω Load to VSS        | TBD  | -     | TBD             | mV      |

| ΔVIN    | Serial Input voltage swing (RXI+/RXI-)                              | 160  | -     | TBD             | mV      |

| IIH,TTL | Input High Current (Magnitude), VIN = VDD                           | 0.0  | 0.004 | 40              | μA      |

| IIL,TTL | Input Low Current (Magnitude), VIN= 0 volts                         |      | 0.004 | 40              | μA      |

| Idd     | Transceiver VDD Supply Current, Ta = 25°C                           |      | 195   |                 | mA      |

| PD      | Power dissipation                                                   | -    | 625   | 900             | mW      |

| θјс     | Thermal Resistance, Junction to Case                                | -    | TBD   | -               | °C/Watt |

# Application Comparison Between; Vitesse VSC7125, HDMP-1536 and ICS9536-01

#### **Pinout Difference:**

|            | HDM       | P-1536                         | VITES                 | SSE VSC7125                                |                                        |

|------------|-----------|--------------------------------|-----------------------|--------------------------------------------|----------------------------------------|

| PIN NUMBER | PIN LABEL | DESCRIPTION                    | PIN LABEL DESCIRPTION |                                            | TO USE ICS9536<br>YOU MUST<br>PERFORM; |

| 18         | VDDTXA    | TX Analog<br>Supply, 3.3V      | TEST 1                | Factory Test Pin. Nominally tied to +3.3V. | Tie to VDD Note:1                      |

| 20         | VDDTXA    | TX Analog<br>Supply, 3.3V      | TEST2                 | Factory Test Pin. Nominally tied to +3.3V. | Tie to VDD Note:1                      |

| 23         | VDDRX     | RX PECL Logic<br>Supply +3.3V. | TEST3                 | Factory Test Pin. Nominally tied to +3.3V. | Tie to VDD Note:1                      |

| 50         | VDDRXA    | RX Analog Supply +3.3V.        | VDD                   | Digital Supply, +3.3V.                     | Tie to VDD Note:1                      |

| 57         | VDDRX     | RX PECL Logic<br>Supply +3.3V. | VDDANA                | Analog Power Supply +3.3V                  | Tie to VDD Note:1                      |

| 64         | GNDTX     | High Speed Ground              | no connect            | Pin is not used                            | Ground this pin.                       |

#### Note:

### **Comma Detection or Word Alignment:**

The VSC7125 provides 7-bit comma character recognition or word alignment. When an improperly aligned comma is encountered, the internal data is shifted such that the first detected comma character is properly aligned with CLKN.

When a comma character is detected in the ICS9536, realignment of the receiver clocks can be performed. These clocks are stretched, such that correct alignment occurs at the start of the second 4-byte data set. The second comma character, occurring in the second 4-byte data set will be aligned with the rising edge of the byte clock, CLKN.

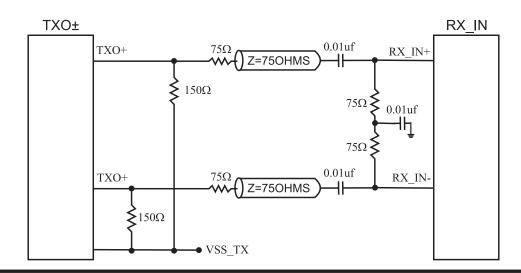

#### **Termination:**

The Vitesse data sheet for the VSC7125 does not explicitly describe termination requirements in a detailed fashion (it specifies  $75\Omega$ ).

The termination required for ICS9536 is:

<sup>1.</sup> Use 0.1μF bypass capacitor.