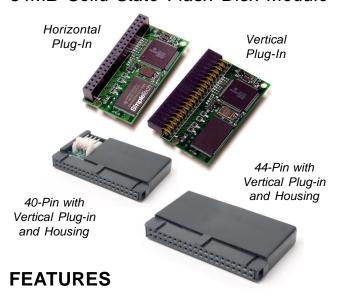

#### 64MB Solid-State Flash Disk Module

- Compact Form Factor designed to plug into standard IDE connector

- 44-pin connector and 40-pin connector available

- Vertical and horizontal plug-in available

- Housing optional for vertical plug-in

- Standard IDE Interface

- Configures as Master or Slave IDE device

- Endurance Guarantee of 2,000,000 Write/Erase Cycles

- Standard 5V Power Supply (also supports a 3.3V power supply)

- Replaces IDE hard drive for applications where tough environments prohibit use of traditional rotating media

- Solid-State (no moving parts)

- High Shock and Vibration Limits

- 512 Byte Sector and ECC Defect Management Compatible to IDE Hard Disk Drives

- No "Spin" Noise Compared to Traditional Rotating Media

- Standard ECC Engine

Web: www.simpletech.com

- 7 Year Warranty

- Other Features Available (inquire for more information)

- Power Down Protection. A built-in feature that protects the module from losing data during a write operation when a lost of power or an unexpected removal from the host system occurred.

- Endurance Status Monitor. A firmware option that allows applications to estimate the remaining life span of the device.

- Password Protection/Write Protection. A custom utility software that allows the administrator and user to set passwords for up to four partitions.

#### **GENERAL DESCRIPTION**

This SimpleTech product is a solid-state Flash Disk Module with a standard IDE interface, common on IDE hard drives.

The module plugs directly into either a 40-pin connector and 4-pin power connector, or a 44 pin connector without need for a cable. This eliminates the installation confusion, the cost, and the potential failures commonly associated with interface cables..

SimpleTech OEM flash disk modules are the product of choice in applications requiring high reliability and high tolerance to shock, vibration, humidity, altitude, and temperature. Because there are no moving parts to service or maintain, flash disk modules are reliable alternatives to mechanical hard disk drives for high availability and mission critical applications.

While the inherent ruggedness and reliability of solid state storage relative to rotating hard drives is intuitive, new applications for OEM flash disk modules are emerging due to the low cost per usable megabyte. Most applications using embedded operating systems such as VxWorks<sup>TM</sup>, Windows XP/embedded<sup>TM</sup>, and Linux<sup>TM</sup> don't have multigigabyte data storage requirements, and therefore a cost savings can be realized when using this robust media.

#### ORDERING INFORMATION

| SimpleTech Part No. | # of Pins | Plug-In/Housing   |

|---------------------|-----------|-------------------|

| SLFDM40LPV-064J     | 40-Pin    | Vertical          |

| SLFDM40LPH-064J     | 40-Pin    | Horizontal        |

| SLFDM40LPVS-064J    | 40-Pin    | Vertical/Housing  |

| SLFDM44V-064J       | 44-Pin    | Vertical          |

| SLFDM44H-064J       | 44-Pin    | Horizontal        |

| SLFDM44LPVS-064J    | 44-Pin    | Vertical /Housing |

|                     |           |                   |

#### **Option Designators**

Options can be selected by using the Option Designators in the part number in the following format:

SLFDMpqr-064J(U)(I)

where p=# of pins, q=LP if low profile, r=plug-in /housing

- U RoHS compliant lead free product

- Commercial Operating Temperature range: 0 to 70°C (designator is BLANK)

Industrial Operating Temperature range: -40 to 85°C (designator=I)

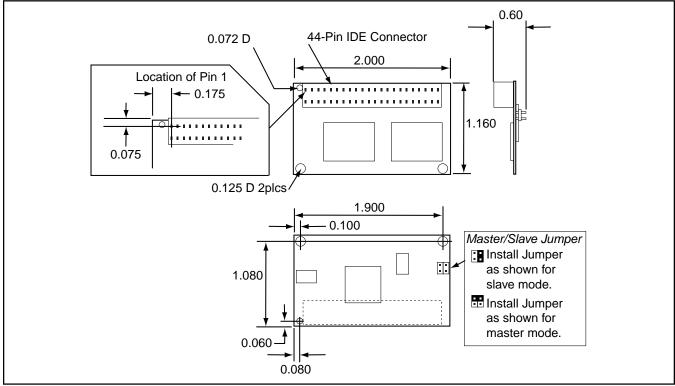

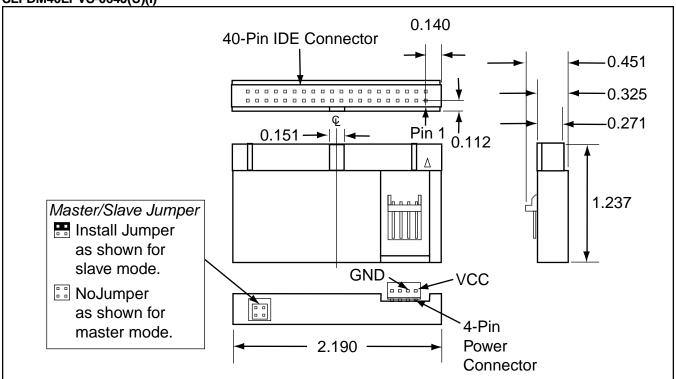

#### **DIMENSIONS AND JUMPERS**

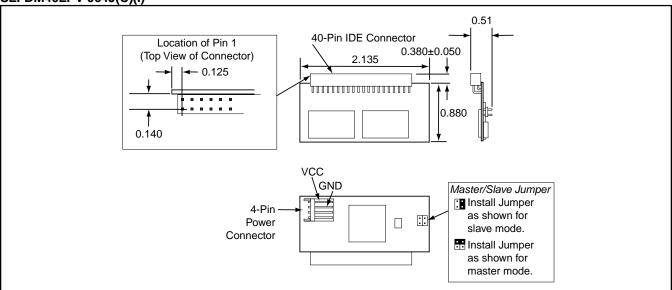

Units are in inches. Tolerances are  $\pm 0.005$ .

#### SLFDM40LPV-064J(U)(I)

#### SLFDM40LPH-064J(U)(I)

(continued)

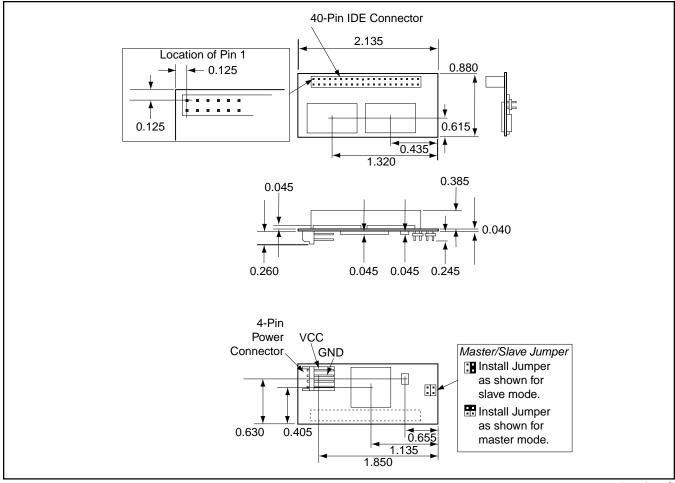

### **DIMENSIONS AND JUMPERS** (continued)

Units are in inches. Tolerances are ±0.005.

#### **SLFDM44V-064J(U)(I)**

#### SLFDM44H-064J(U)(I)

(continued)

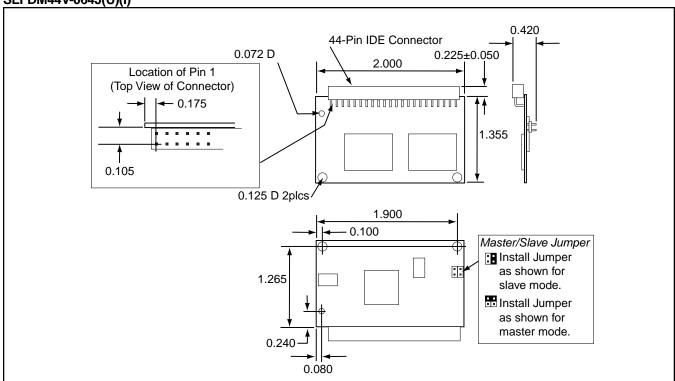

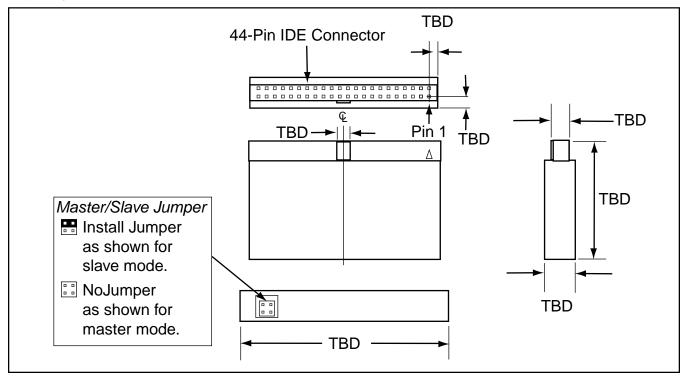

### **DIMENSIONS AND JUMPERS** (continued)

Units are in inches. Tolerances are ±0.005.

#### SLFDM40LPVS-064J(U)(I)

#### SLFDM44LPVS-064J2(U)(I)—Preliminary

(The housing of this product is in design and parameters may change without further notice.)

#### PIN CONFIGURATION

#### **Pinout**

| Pin<br>Num | Pin<br>Symbol | Pin<br>Num | Pin<br>Symbol |

|------------|---------------|------------|---------------|

| 1          | -RESET        | 23         | -IOWR         |

| 2          | GND           | 24         | GND           |

| 3          | D07           | 25         | -IORD         |

| 4          | D08           | 26         | GND           |

| 5          | D06           | 27         | IORDY         |

| 6          | D09           | 28         | -CSEL         |

| 7          | D05           | 29         | -DACK**       |

| 8          | D10           | 30         | GND           |

| 9          | D04           | 31         | INTRQ         |

| 10         | D11           | 32         | -IOIS16       |

| 11         | D03           | 33         | A1            |

| 12         | D12           | 34         | -PDIAG        |

| 13         | D02           | 35         | A0            |

| 14         | D13           | 36         | A2            |

| 15         | D01           | 37         | -CS1          |

| 16         | D14           | 38         | -CS2          |

| 17         | D00           | 39         | -DASP         |

| 18         | D15           | 40         | GND           |

| 19         | GND           | 41         | VCC*          |

| 20         | Key           | 42         | VCC*          |

| 21         | DREQ**        | 43         | GND*          |

| 22         | GND           | 44         | NC*           |

<sup>&</sup>quot;-" indicates signal is active low.

#### **44-Pin Mating Connector**

Compatible mating connectors are available in the following Samtec lines: TMM, TMMH, MTMM, TW, LTMM, MMT, FTW, ZLTMM.

The LTMM series is a shrouded connector, suitable for most applications.

Example Samtec P/N:

- LTMM-122-02-G-D (Through)

- LTMM-122-02-G-D-RA (Right Angle)

- LTMM-122-02-G-D-SM (Surface Mount)

#### **40-Pin Mating Connector**

Compatible mating connectors are available in the following Samtec lines: TSM, TSW, MTSW, MTLW, EW, ZW through ZSS.

The TSS series is a shrouded connector, suitable for most applications.

Example Samtec P/N:

- TSS-120-02-G-D (Through)

- TSS-120-02-G-D-RA (Right Angle)

<sup>\*</sup> Pins 41-44 apply only to the 44-pin products.

<sup>\*\*</sup> Not used. DMA is not supported.

### **Signal Description**

| Signal Name | Dir | Pin                                                              | Description                                                                                                                                                                                                                                                   |

|-------------|-----|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -DASP       | I/O | 39                                                               | This input/output is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.                                                                                                                                                             |

| D15-D00     | I/O | 18, 16, 14, 12,<br>10, 8, 6, 4, 3,<br>5, 7, 9, 11, 13,<br>15, 17 | All Task File operations occur in byte mode on the low order bus D00-D07 while all data transfers are 16 bit using D00-D15.                                                                                                                                   |

| -IOWR       | I   | 23                                                               | The I/O Write strobe pulse is used to clock I/O data on the drive Data bus into the Drive controller registers when the Drive is configured to use the I/O interface. The clocking will occur on the negative to positive edge of the signal (trailing edge). |

| -IORD       | I   | 25                                                               | This is an I/O Read strobe generated by the host. This signal gates I/O data onto the bus from the Drive.                                                                                                                                                     |

| INTRQ       | 0   | 31                                                               | Signal is the active high Interrupt Request to the host.                                                                                                                                                                                                      |

| A2-A0       | I   | 35, 33, 36                                                       | A[2:0] are used to select the one of eight registers in the Task File.                                                                                                                                                                                        |

| -CS1, -CS2  | I   | 37, 38                                                           | -CS1 is the chip select for the task file registers while -CS2 is used to select the Alternate Status Register and the Device Control Register.                                                                                                               |

| -CSEL       | I   | 28                                                               | This internally pulled up signal is used to configure this device as a Master or a Slave. When the pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave                                         |

| -IOIS16     | О   | 32                                                               | Not used.                                                                                                                                                                                                                                                     |

| -PDIAG      | I/O | 34                                                               | This input/output is the Pass Diagnostic signal in the Master/Slave handshake protocol.                                                                                                                                                                       |

| -DREQ       | О   | 21                                                               | Not used.                                                                                                                                                                                                                                                     |

| -DACK       | I   | 29                                                               | Not used.                                                                                                                                                                                                                                                     |

| -IORDY      | 0   | 27                                                               | Not used, and pulled up to VCC through a 4.7K ohm resistor.                                                                                                                                                                                                   |

| -RESET      | I   | 1                                                                | This input pin is the active low hardware reset from the host.                                                                                                                                                                                                |

| VCC         | _   | 41, 42                                                           | Power. Applies to the 44-pin version only.                                                                                                                                                                                                                    |

| GND         | _   | 2, 19, 22, 24,<br>26, 30, 40, 43                                 | Ground. (Pin 43 applies to 44-pin version only.)                                                                                                                                                                                                              |

| NC          | _   | 20, 44                                                           | No connect                                                                                                                                                                                                                                                    |

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                     | Symbol    | Value           | Unit |

|-------------------------------|-----------|-----------------|------|

| Voltage on any pin w.r.t. Vss | Vin, Vout | -0.5 to VCC+0.5 | V    |

| Storage Temperature range     | Tstg      | -65 to +150     | °C   |

### RECOMMENDED OPERATING CONDITIONS

| Parameter                        | Symbol | Min  | Тур | Max   | Unit |

|----------------------------------|--------|------|-----|-------|------|

| Commercial operating temperature | Ta     | 0    | 25  | 70    | °C   |

| Industrial operating temperature | Ta     | -40  | _   | 85    | °C   |

| VCC voltage                      | VCC    | 4.75 | 5.0 | 5.25  | V    |

| -                                |        | 3.18 | 3.3 | 3.465 |      |

### **PERFORMANCE**

| Item                            | Performance           |

|---------------------------------|-----------------------|

| Data Transfer Rate To/From Host | 16.7 MBytes/s (burst) |

| Sustained Read                  | up to 5 MBytes/s      |

| Sustained Write                 | up to 1.5 MBytes/s    |

### **RELIABILITY**

| Item                       | Value                 |

|----------------------------|-----------------------|

| Data Write/Erase Endurance | 2 million cycles min. |

| Data reliability           | 1 in 10¹⁴ bits, read  |

| Data retention             | 10 years              |

### **CHS PARAMETERS**

| Standard CHS Values |          |         |          |  |  |  |

|---------------------|----------|---------|----------|--|--|--|

| Capacity            | С        | Н       | S        |  |  |  |

| 64MB                | 490      | 8       | 32       |  |  |  |

| C=cylinders; l      | H=heads; | S=secto | rs/track |  |  |  |

#### **ENVIRONMENTAL CHARACTERISTICS**

| Leaded Card | Leaded Cards (without the "U" option)                       |  |  |  |  |

|-------------|-------------------------------------------------------------|--|--|--|--|

| Shock:      | 2K G, half-sine, 0.330 ms to 0.750 ms                       |  |  |  |  |

|             | (per MIL-STD-202G Method 213B, Condition A)                 |  |  |  |  |

| Vibration:  | 30 G 10Hz-2KHz                                              |  |  |  |  |

|             | (per MIL-STD-202G Method 204D 20 min/sweep, 12 sweeps/axis) |  |  |  |  |

| Humidity:   | 85°C 95% RH, 5.5V, 500 hrs                                  |  |  |  |  |

| RoHS Comp   | liant Lead Free Cards (with the "U" option)                 |  |  |  |  |

| Shock:      | 1K G, half-sine, 0.330 ms to 0.750 ms                       |  |  |  |  |

|             | (per MIL-STD-202G Method 213B, Condition A)                 |  |  |  |  |

| Vibration:  | 15 G 10Hz-2KHz                                              |  |  |  |  |

|             | (per MIL-STD-202G Method 204D 20 min/sweep, 12 sweeps/axis) |  |  |  |  |

| Humidity:   | 85°C 95% RH, 5.5V, 500 hrs                                  |  |  |  |  |

#### **DC CHARACTERISTICS-1**

(Ta=  $0^{\circ}$ C to  $70^{\circ}$ C for commercial temperature parts, or Ta =  $-40^{\circ}$ C to  $85^{\circ}$ C for industrial temperature parts; VCC = 3.3V + 5% or -3.6%)

| Symbol | Parameter                                    | Min  | Max       | Units    | Notes  |

|--------|----------------------------------------------|------|-----------|----------|--------|

| VIL    | Input LOW Voltage                            | -0.3 | +0.8      | V        |        |

| VIH    | Input HIGH Voltage                           | 2.0  | VCC+0.3   | V        |        |

| VOL    | Output LOW Voltage                           |      | 0.45      | V        | at 4mA |

| VOH    | Output HIGH Voltage                          | 2.4  |           | V        | at 1mA |

| ICC    | Operating Current<br>Sleep mode<br>Operating |      | 800<br>30 | μA<br>mA |        |

| ILI    | Input Leakage Current                        |      | 10        | μΑ       |        |

| ILO    | Output Leakage Current                       |      | 1         | μΑ       |        |

| CI/O   | Input/output Capacitance                     |      | 25        | рF       |        |

### **DC CHARACTERISTICS-2**

(Ta= 0°C to 70°C for commercial temperature parts, or Ta = -40°C to 85°C for industrial temperature parts; VCC =  $5V\pm5\%$ )

| Symbol | Parameter                                              | Min  | Max        | Units    | Notes  |

|--------|--------------------------------------------------------|------|------------|----------|--------|

| VIL    | Input LOW Voltage                                      | -0.3 | +0.8       | V        |        |

| VIH    | Input HIGH Voltage                                     | 2.0  | VCC+0.3    | V        |        |

| VOL    | Output LOW Voltage                                     |      | 0.8        | V        | at 4mA |

| VOH    | Output HIGH Voltage                                    | 4.0  |            | V        | at 1mA |

| ICC    | Operating Current, VCC=5.0V<br>Sleep mode<br>Operating |      | 1200<br>30 | μA<br>mA |        |

| ILI    | Input Leakage Current                                  |      | 10         | μΑ       |        |

| ILO    | Output Leakage Current                                 |      | 2          | μΑ       |        |

| CI/O   | Input/output Capacitance                               |      | 25         | рF       |        |

#### **AC CHARACTERISTICS**

(Ta = 0°C to 70°C for commercial temperature parts, Ta = -40°C to 85°C for industrial temperature parts; VCC =  $5V\pm5\%$  or VCC = 3.3V+5% or -3.6%)

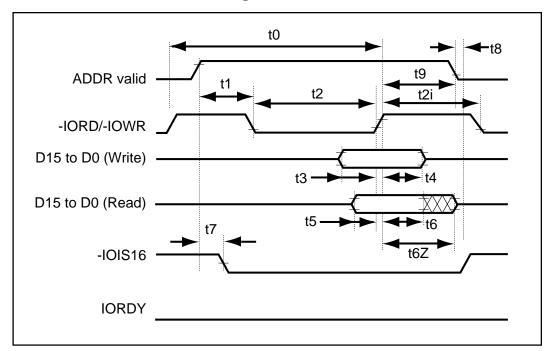

### **Register Access AC Characteristics for True IDE**

| Parameter                        |        | Symbol          | Mode0 | Mode1 | Mode2 | Mode3 | Mode4 | Unit |

|----------------------------------|--------|-----------------|-------|-------|-------|-------|-------|------|

| Cycle time                       | (min)  | t <sub>0</sub>  | 600   | 383   | 330   | 180   | 120   | ns   |

| Address valid to -IORD/-IOWR     | (min)  | t <sub>1</sub>  | 70    | 50    | 30    | 30    | 25    | ns   |

| setup                            |        |                 |       |       |       |       |       |      |

| -IORD/-IOWR pulse width 8bit     | (min)  | t <sub>2</sub>  | 290   | 290   | 290   | 80    | 70    | ns   |

| -IORD/-IOWR recovery time        | (min)  | t2i             | _     | _     | _     | 70    | 25    | ns   |

| -IOWR data setup                 | (min)  | t3              | 60    | 45    | 30    | 30    | 20    | ns   |

| -IOWR data hold                  | (min)  | t4              | 30    | 20    | 15    | 10    | 10    | ns   |

| -IORD data setup                 | (min)  | t5              | 50    | 35    | 20    | 20    | 20    | ns   |

| -IORD data hold                  | (min)  | t6              | 5     | 5     | 5     | 5     | 5     | ns   |

| -IORD data tristate              | (max)  | t <sub>6z</sub> | 30    | 30    | 30    | 30    | 30    | ns   |

| Address valid to -IOCS16 assert. | (max)  | t7              | 90    | 50    | 40    | n/a   | n/a   | ns   |

| Address valid to -IOCS16 release | e(max) | t8              | 60    | 45    | 30    | n/a   | n/a   | ns   |

| -IORD/-IOWR to address valid     |        | t9              | 20    | 15    | 10    | 10    | 10    | ns   |

| hold                             |        |                 |       |       |       |       |       |      |

#### PIO Mode Access AC Characteristics for True IDE

| Parameter                           |      | Symbol          | Mode0 | Mode1 | Mode2 | Mode3 | Mode4 | Unit |

|-------------------------------------|------|-----------------|-------|-------|-------|-------|-------|------|

| Cycle time (:                       | min) | t <sub>0</sub>  | 600   | 383   | 240   | 180   | 120   | ns   |

| Address valid to -IORD/-IOWR (setup | min) | t <sub>1</sub>  | 70    | 50    | 30    | 30    | 25    | ns   |

| -IORD/-IOWR pulse width 16bit (     | min) | t2              | 165   | 125   | 100   | 80    | 70    | ns   |

| -IORD/-IOWR recovery time (         | min) | t2i             | -     | -     | -     | 70    | 25    | ns   |

| -IOWR data setup (:                 | min) | t3              | 60    | 45    | 30    | 30    | 20    | ns   |

| IOWR data hold (:                   | min) | t4              | 30    | 20    | 15    | 10    | 10    | ns   |

| -IORD data setup (:                 | min) | t5              | 50    | 35    | 20    | 20    | 20    | ns   |

| -IORD data hold (:                  | min) | t <sub>6</sub>  | 5     | 5     | 5     | 5     | 5     | ns   |

| -IORD data tristate (1              | max) | t <sub>6z</sub> | 30    | 30    | 30    | 30    | 30    | ns   |

| Address valid to -IOCS16 assert. (1 | max) | t7              | 90    | 50    | 40    | n/a   | n/a   | ns   |

| Address valid to -IOCS16 release(1  | max) | t8              | 60    | 45    | 30    | n/a   | n/a   | ns   |

| -IORD/-IOWR to address valid hold   |      | t9              | 20    | 15    | 10    | 10    | 10    | ns   |

(continued)

### AC CHARACTERISTICS (continued)

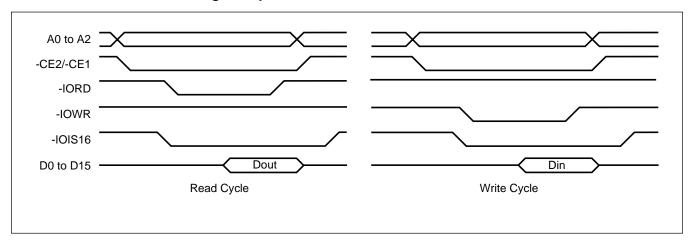

### **True IDE Mode Access Read/Write Timings**

#### TRUE IDE MODE

The drive is configured in a True IDE mode at power up. The data register is accessed in word (16-bit) mode at power up. The drive permits 8-bit accesses if the host issues a Set Feature Command to put the device in 8-bit mode.

#### **True IDE Mode Read I/O Function**

| Mode                    | -CE2 | -CE1 | A0 to A2 | -IORD | -IOWR | D15-D8   | D7-D0      |

|-------------------------|------|------|----------|-------|-------|----------|------------|

| Invalid Mode            | L    | L    | х        | х     | х     | High Z   | High Z     |

| Standby Mode            | Н    | Н    | х        | х     | х     | High Z   | High Z     |

| Data Register Access    | Н    | L    | 0        | L     | Н     | Odd-Byte | Even-Byte  |

| Alternate Status Access | L    | Н    | 6h       | L     | Н     | High Z   | Status Out |

| Other Task File Access  | Н    | L    | 1-7h     | L     | Н     | High Z   | Data       |

| x: L or H               |      |      |          |       |       |          |            |

#### **True IDE Mode Write I/O Function**

| Mode                    | -CE2 | -CE1 | A0 to A2 | -IORD | -IOWR | D15-D8     | D7-D0      |

|-------------------------|------|------|----------|-------|-------|------------|------------|

| Invalid Mode            | L    | L    | x        | х     | х     | Don't Care | Don't Care |

| Standby Mode            | Н    | Н    | х        | х     | х     | Don't Care | Don't Care |

| Data Register Access    | Н    | L    | 0        | Н     | L     | Odd-Byte   | Even-Byte  |

| Control Register Access | L    | Н    | 6h       | Н     | L     | Don't Care | Control In |

| Other Task File Access  | Н    | L    | 1-7h     | Н     | L     | Don't Care | Data       |

| x: L or H               | •    |      |          |       |       |            |            |

#### True IDE Mode I/O Access Timing Example

# TASK FILE REGISTER SPECIFICATION

These registers are used for reading and writing data to the drive.

### True IDE Mode I/O Map

| -CE2 | -CE1 | <b>A2</b> | <b>A1</b> | A0 | -IORD=0                | -IOWR=0                 |

|------|------|-----------|-----------|----|------------------------|-------------------------|

| 1    | 0    | 0         | 0         | 0  | Data register          | Data register           |

| 1    | 0    | 0         | 0         | 1  | Error register         | Feature register        |

| 1    | 0    | 0         | 1         | 0  | Sector Count register  | Sector Count register   |

| 1    | 0    | 0         | 1         | 1  | Sector No. register    | Sector No. register     |

| 1    | 0    | 1         | 0         | 0  | Cylinder Low register  | Cylinder Low register   |

| 1    | 0    | 1         | 0         | 1  | Cylinder High register | Cylinder High register  |

| 1    | 0    | 1         | 1         | 0  | Drive Head register    | Drive Head register     |

| 1    | 0    | 1         | 1         | 1  | Status register        | Command register        |

| 0    | 1    | 1         | 1         | 0  | Alt Status register    | Device Control register |

| 0    | 1    | 1         | 1         | 1  | Drive Address register | Reserved                |

#### **Data Register**

The Data Register is a 16 bit read/write register used for transferring data between the drive and the host. This register can be accessed in word mode and byte mode.

| bit15 bit14 bit13 bit12 bit11 | bit10 | bit9 | bit8    | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|-------------------------------|-------|------|---------|------|------|------|------|------|------|------|------|

|                               |       |      | D0 to D | D15  |      |      |      |      |      |      |      |

#### **Error Register**

This read only register is used for analyzing an error. This register is valid when the BSY bit in the Status register and Alternate Status register are set to "0" (Ready).

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| BBK  | UNC  | 0    | IDNF | 0    | ABRT | 0    | AMNF |

| bit | Name                          | Function                                                                         |

|-----|-------------------------------|----------------------------------------------------------------------------------|

| 7   | BBK (Bad Block Detected)      | This bit is set when a Bad Block is detected in requested ID field—not supported |

| 6   | UNC (Data ECC Error)          | This bit is set when an Uncorrectable error has occurred when reading the drive. |

| 4   | IDNF (ID Not Found)           | The requested sector ID is in error or cannot be found.                          |

| 2   | ABRT (ABoRTed Command)        | Drive status error or Aborted invalid command                                    |

| 0   | AMNF (Address Mark Not Found) | This bit is set in case of a general error.                                      |

| Diagnostic Code | Description               |

|-----------------|---------------------------|

| 01h             | No error detected         |

| 02h             | Formatting error          |

| 03h             | Sector buffer error       |

| 04h             | ECC error                 |

| 05h             | Microprocessor error      |

| 8xh             | Drive 1 failed (not used) |

#### **Feature Register**

This write only register provides information regarding the features of the drive which the host wishes to utilize. See details under the SET FEATURE command.

| bit7 | bit6 | bit5 | bit4 | bit3     | bit2 | bit1 | bit0 |

|------|------|------|------|----------|------|------|------|

|      |      |      | Feat | ure Byte |      |      |      |

#### **Sector Count Register**

This register contains the numbers of sectors of data requested to be transferred on a read or write operation between the host and the drive. If the value in the register is 0, a count of 256 sectors is indicated.

| bit7 | bit6 | bit5 | bit4   | bit3       | bit2 | bit1 | bit0 |

|------|------|------|--------|------------|------|------|------|

|      |      |      | Sector | Count Byte | e    |      |      |

#### **Sector Number Register**

When the LBA bit in the Drive/Head register is 0, this register contains the starting sector number for any media access. When the LBA bit is set to 1, this register contains bits 7:0 of the LBA for any media access.

| bit7 | bit6 | bit5      | bit4      | bit3        | bit2        | bit1 | bit0 |

|------|------|-----------|-----------|-------------|-------------|------|------|

|      |      | Sector Nu | ımber Byt | e or bits 7 | 0 of the LB | A    |      |

#### Cylinder Low Register

In CHS mode (LBA=0), this register contains the low order bits of the starting cylinder address. In LBA mode, it contains bits 15:8 of the LBA.

| bit7 | bit6 | bit5     | bit4     | bit3       | bit2         | bit1 | bit0 |

|------|------|----------|----------|------------|--------------|------|------|

|      |      | Cylinder | Low Byte | or bits 15 | :8 of the LB | A    |      |

#### Cylinder High Register

In CHS mode (LBA=0), this register contains the high order bits of the starting cylinder address. In LBA mode, it contains bits 23:16 of the LBA.

| bit7 | bit6 | bit5       | bit4      | bit3        | bit2         | bit1 | bit0 |

|------|------|------------|-----------|-------------|--------------|------|------|

|      |      | Cylinder I | High Byte | or bits 23: | 16 of the LE | 3A   |      |

#### **Drive/Head Register**

This register select the device address translation (CHS or LBA) and provides head address (CHS) or high order address bits 27:24 for LBA.

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2       | bit1         | bit0 |

|------|------|------|------|------|------------|--------------|------|

| 1    | LBA  | 1    | DRV  | Head | No. or LBA | A bits 27:24 |      |

| bit | Name                  | Function                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 1                     | This bit is set to "1".                                                                                                                                                                                                                                                                                                                                                                                             |

| 6   | LBA                   | LBA is a flag to select either Cylinder/Head/Sector (CHS) or Logical Block Address (LBA) mode. When LBA=0, CHS mode is selected. When LBA=1, LBA mode is selected. In LBA mode, the Logical Block Address is interrupted as follows:  LBA07-LBA00: Sector Number Register D7-D0  LBA15-LBA08: Cylinder Low Register D7-D0  LBA23-LBA16: Cylinder High Register D7-D0  LBA27-LBA24: Drive/Head Register bits HS3-HS0 |

| 5   | 1                     | This bit is set to "1".                                                                                                                                                                                                                                                                                                                                                                                             |

| 4   | DRV (DRiVe select)    | This bit is used for selecting the Master (drive 0) and Slave (drive 1) in Master/Slave organization. The drive is set to be drive 0 or 1 by using DRV# of the Socket and Copy register.                                                                                                                                                                                                                            |

| 3-0 | Head Number (HS3-HS0) | These bits are used for selecting the Head number. Bit 3 is MSB. In LBA mode, these bits represent the LBA address 27:24.                                                                                                                                                                                                                                                                                           |

#### **Status Register**

This read only register indicates status of a command execution. When the BSY bit is "0", the other bits are valid; when the BSY bit is "1", the other bits are not valid. When the register is read, the interrupt (-IREQ pin) is cleared.

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| BSY  | DRDY | DWF  | DSC  | DRQ  | CORR | IDX  | ERR  |

| bit | Name                      | Function                                                                                                                                                                                                                                            |

|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BSY (BuSY)                | This bit is set when the drive internal operation is executing. When this bit is set to "1", other bits in this register are invalid.                                                                                                               |

| 6   | DRDY (Drive ReaDY)        | If this bit and DSC bit are set to "1", the drive is capable of receiving the read and write or seek requests. If this bit is set to "0", the drive prohibits these requests. On error, DRDY changes only after the host reads the Status Register. |

| 5   | DWF (Drive Write Fault)   | This bit is set if the fault occurs during the write process.                                                                                                                                                                                       |

| 4   | DSC (Drive Seek Complete) | This bit is set when the requested sector was found.                                                                                                                                                                                                |

| 3   | DRQ (Data ReQuest)        | This bit is set when information can be transferred between the host and data register.                                                                                                                                                             |

| 2   | CORR (CORRected data)     | This bit is set when a correctable data error has occurred and the data has been corrected.                                                                                                                                                         |

| 1   | IDX (InDeX)               | This bit is always set to "0".                                                                                                                                                                                                                      |

| 0   | ERR (ERRor)               | This bit is set when the previous command has ended in some type of error. The error information is set in the Error register.                                                                                                                      |

#### **Alternate Status Register**

This register is the same as the Status register except that -IREQ is not negated when data is read.

#### **Command Register**

This write only register is used for writing the command that executes the drive's operation. The command code is written in the command register after its parameters are written in the Task File during the drive ready state. See details under the ATA COMMAND SPECIFICATIONS.

#### **Device Control Register**

This write only register is used for controlling the interrupt request and issuing an ATA soft reset to the drive.

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| х    | x    | x    | x    | 1    | SRST | nIEN | 0    |

| bit | Name                    | Function                                                                                                                                                                                                                           |

|-----|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | x                       | Don't care.                                                                                                                                                                                                                        |

| 3   | 1                       | This bit is set to "1".                                                                                                                                                                                                            |

| 2   | SRST (Software ReSeT)   | This bit is set to "1" in order to force the drive to perform an AT disk control soft reset operation.                                                                                                                             |

| 1   | nIEN (Interrupt ENable) | When set to "0", it enables interrupts to the host (using the -IREQ tri-state pin). When inactive (set to "1") or drive is not selected, it disables all pending interrupts (-IREQ in high-Z). This bit is ignored in memory mode. |

| 0   | 0                       | This bit is set to "0".                                                                                                                                                                                                            |

#### **Drive Address Register**

This read only register is used for confirming the drive's status. This register is provided for compatibility with the AT disk drive interface and it is not recommended that this register be mapped into the host's I/O space because of potential conflicts on bit 7.

| bit7   | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|--------|------|------|------|------|------|------|------|

| High-Z | nWTG | nHS3 | nHS2 | nHS1 | nHS0 | nDS1 | nDS0 |

| bit | Name                     | Function                                                                                          |

|-----|--------------------------|---------------------------------------------------------------------------------------------------|

| 7   | X                        | This bit is unused.                                                                               |

| 6   | nWTG (WriTing Gate)      | This bit is unused.                                                                               |

| 5-2 | nHS3-0 (Head Select 3-0) | These bits are the negative value of the Head Select bits (bit 3 to 0) in the Drive/Head register |

| 1   | nDS1 (Drive Select 1)    | When set to "0", drive 1 is active and selected.                                                  |

| 0   | nDS0 (Drive Select 0)    | When set to "0", drive 0 is active and selected.                                                  |

### ATA COMMAND SPECIFICATIONS

This table with the following paragraphs summarizes the ATA command set.

| No. | Command set                 | Code        | FR | SC | SN | CY | DR  | HD | LBA |

|-----|-----------------------------|-------------|----|----|----|----|-----|----|-----|

| 1   | Check Power Mode            | E5h or 98h  | _  | Y  | _  | _  | Y   | _  | _   |

| 2   | Execute Drive Diagnostic    | 90h         | _  | _  | _  | _  | Y** | _  | _   |

| 3   | Erase Sector(s)             | C0h         | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 4   | Format Track                | 50h         | _  | Y  | _  | Y  | Y   | Y  | Y   |

| 5   | Identify Drive              | ECh         | Y  | _  | _  | _  | Y   | _  | _   |

| 6   | Idle                        | E3h or 97h  | _  | Y  | _  | _  | Y   | _  | _   |

| 7   | Idle Immediate              | E1h or 95h  | _  | _  | _  | _  | Y   | _  | _   |

| 8   | Initialize Drive Parameters | 91h         | _  | Y  | _  | _  | Y   | Y  | _   |

| 9   | Read Buffer                 | E4h         | _  | _  | _  | _  | Y   | _  | _   |

| 10  | Read Multiple               | C4h         | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 11  | Read Long Sector            | 22h or 23h* | _  | _  | Y  | Y  | Y   | Y  | Y   |

| 12  | Read Sector(s)              | 20h or 21h* | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 13  | Read Verify Sector(s)       | 40h or 41h* | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 14  | Recalibrate                 | 1Xh         | _  | _  | _  | _  | Y   | _  | _   |

| 15  | Request Sense               | 03h         | _  | _  | _  | _  | Y   | _  | _   |

| 16  | Seek                        | 7Xh         | _  | _  | Y  | Y  | Y   | Y  | Y   |

| 17  | Set Features                | EFh         | _  | Y  | Y  | Y  | Y   | Y  | _   |

| 18  | Set Multiple Mode           | C6h         | _  | Y  | _  | _  | Y   | _  | _   |

| 19  | Set Sleep Mode              | E6h or 99h  | _  | _  | _  | _  | Y   | _  | _   |

| 20  | Stand By                    | E2h or 96h  | _  | Y  | _  | _  | Y   | _  | _   |

| 21  | Stand By Immediate          | E0h or 94h  | _  | _  | _  | _  | Y   | _  | _   |

| 22  | Translate Sector            | 87h         | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 23  | Wear Level                  | F5h         | _  | _  | _  | _  | Y   | Y  | _   |

| 24  | Write Buffer                | E8h         | _  | _  | _  | _  | Y   | _  | _   |

| 25  | Write Long Sector           | 32h or 33h* | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 26  | Write Multiple              | C5h         | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 27  | Write Multiple w/o Erase    | CDh         | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 28  | Write Sector(s)             | 30h or 31h* | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 29  | Write Sector(s) w/o Erase   | 38h         | _  | Y  | Y  | Y  | Y   | Y  | Y   |

| 30  | Write Verify                | 3Ch         | _  | Y  | Y  | Y  | Y   | Y  | Y   |

FR=Features Register, SC=Sector Count Register (00h to FFh), SN=Sector Number Register (01h to 20h), CY=Cylinder Registers, DR=Drive bit of Drive/Head Register, HD=Head no. (0 to 3) of Drive/Head Register, LBA=Logical Block Address Mode Supported.

Y-Set up.

"-" -Not set up.

- \* First command code=with retry,

Second command code=without retry.

- \* Address to drive 0. Both drives execute command

## Check Power Mode (code: E5h or 98h)

This command checks the power mode.

### Execute Drive Diagnostic (code: 90h)

This command performs the internal diagnostic tests implemented by the module. See ERROR register for dianostic codes.

# Erase Sector(s) (code: C0h)

This command is used to pre-erase and condition data sectors in advance.

## Format Track (code: 50h)

This command writes the desired head and cylinder of the selected drive with a vender unique data pattern (typically 00h or FFh). This module accepts a sector buffer of data from the host to follow the command with the same protocol as the Write Sector Command although the information in the buffer is not used.

## Identify Drive (code: ECh)

This command enables the host to receive parameter information from the module. (See tables on the next page.)

#### Idle

#### (code: E3h or 97h)

This command causes the module to set BSY, enter the Idle mode, clear BSY, and generate an interrupt. If the sector count is non-zero, automatic power down mode is enabled. If the sector count is zero, the automatic power down mode is disabled.

## Idle Immediate (code: E1h or 95h)

This command causes the module to set BSY, enter the Idle (Read) mode, clear BSY, and generate an interrupt.

## Initialize Drive Parameters (code: 91h)

This command enables the host to set the number of sectors per track and the number of heads per cylinder.

## Read Buffer (code: E4h)

This command enables the host to read the current contents of the module's sector buffer.

### Read Multiple (code: C4h)

This command performs similarly to the Read Sectors command. Interrupts are not generated on each sector, but on the transfer of a block which contains the number of sectors defined by a Set Multiple command.

## Read Long Sector (code: 22h or 23h)

This command performs similarly to the Read Sector(s) command except that it returns 516 bytes of data instead of 512 bytes.

## Read Sector(s) (code: 20h or 21h)

This command reads from 1 to 256 sectors as specified in the Sector Count register. A sector count of 0 requests 256 sectors. The transfer begins at the sector specified in the Sector Number register.

## Read Verify Sector(s) (code: 40h or 41h)

This command verifies one or more sectors on the module by transferring data from the flash media to the data buffer in the module and verifying that the ECC is correct. This command is identical to the Read Sectors command, except that DRQ is never set and no data is transferred to the host.

# Recalibrate (code: 1Xh)

The module performs only the interface timing and register operations. When this command is issued, the module sets BSY and waits for an appropriate length of time after which it clears BSY and issues an interrupt. When this command ends normally, the module is initialized.

#### **Identify Drive Information (Typical)**

| Word       | Data  | Total | Description                                                                         |

|------------|-------|-------|-------------------------------------------------------------------------------------|

| Address    |       | Bytes |                                                                                     |

| 0          | 044AH | 2     | General configuration bit-significant information                                   |

| 1          | XXXXH | 2     | Default number of cylinders                                                         |

| 2          | 0000H | 2     | Reserved                                                                            |

| 3          | 00XXH | 2     | Default number of heads                                                             |

| 4          | XXXXH | 2     | Do not use this word. Before retirement, was number of unformatted bytes per track  |

| 5          | XXXXH | 2     | Do not use this word. Before retirement, was number of unformatted bytes per sector |

| 6          | XXXXH | 2     | Default number of sectors per track                                                 |

| 7-8        | XXXXH | 4     | Number of sectors per module (word 7 = MSW, word 8 = LSW)                           |

| 9          | 0000H | 2     | Reserved                                                                            |

| 10-19      | XXXXH | 20    | Serial Number (see table below for definition)                                      |

| 20         | XXXXH | 2     | Do not use this word. Before retirement, was buffer type                            |

| 21         | XXXXH | 2     | Do not use this word. Before retirement, was buffer size in 512 byte increments     |

| 22         | 0004H | 2     | # of ECC bytes passed on Read/Write Long commands                                   |

| 23-46      | XXXXH | 48    | Firmware revision and model number in ASCII (see table below for definition)        |

| 47         | 0001H | 2     | Maximum of 1 sector on Read/Write Multiple command                                  |

| 48         | 0000H | 2     | Double Word not supported                                                           |

| 49         | 0200H | 2     | DMA not supported, LBA supported                                                    |

| 50         | 0000H | 2     | Reserved                                                                            |

| 51         | 0200H | 2     | PIO data transfer cycle timing mode                                                 |

| 52         | 0000H | 2     | Single word DMA data transfer cycle timing mode (not supported)                     |

| 53         | 0003h | 2     | Words 54 - 58 and 64 - 70 are valid                                                 |

| 54         | XXXXH | 2     | Number of Current Cylinders                                                         |

| 55         | XXXXH | 2     | Number of Current Heads                                                             |

| 56         | XXXXH | 2     | Number of Current Sectors Per Track                                                 |

| 5 <i>7</i> | XXXXH | 2     | LSW of the Current Capacity in Sectors                                              |

| 58         | XXXXH | 2     | MSW of the Current Capacity in Sectors                                              |

| 59         | 010XH | 2     | Current Setting for Block Count=1 for R/W Multiple commands                         |

| 60-61      | XXXXH | 4     | Total number of sectors addressable in LBA Mode                                     |

| 62         | 0000H | 2     | Single word DMA transfer not supported                                              |

| 63         | 0000H | 2     | Multiword DMA modes not supported                                                   |

| 64         | 0003H | 2     | Advanced PIO modes supported (modes 3 and 4)                                        |

| 65         | 0000H | 2     | Minimum multiword DMA transfer cycle time per word (ns)                             |

| 66         | 0000H | 2     | Recommended multiword DMA transfer cycle time per word (ns)                         |

| 67         | 0078H | 2     | Minimum PIO transfer without flow control                                           |

| 68         | 0078H | 2     | Minimum PIO transfer with IORDY flow control                                        |

| 69-255     | 0000H | 388   | Reserved                                                                            |

XXXXH: These values are dependent upon the the specific module.

### Identify Drive Information (continued) (Serial Number, Firmware Revision, and Model Number)

Serial Number Format (typical): Words 10-19

SimpleTech ProprietaryYr Day Hr Min Sec STI\_J13C0 04 224 09 27 50

Firmware Revision: Words 23-26

mm/dd/yy

Model Number: Words 27-46

$STI\ Flash\ X.Y.Z$

### Request Sense (code: 03h)

This command requests an extended error code after a command ends with an error. Refer to table below.

| Description                                           |

|-------------------------------------------------------|

| No error detected                                     |

| Self test OK (No error)                               |

| Miscellaneous Error - N/A                             |

| Invalid Command                                       |

| Invalid Address (requested<br>Head or Sector invalid) |

| Address Overflow (address too large)                  |

| Supply or generate Voltage<br>Out of Tolerance        |

| Uncorrectable ECC Error                               |

| Correctable ECC Error - N/A                           |

| Self Test Diagnostic Failed                           |

| ID Not Found - N/A                                    |

| Spare Sectors Exhausted                               |

| Data Transfer Error / Aborted<br>Command              |

| Corrupted Media Format - N/A                          |

| Write / Erase Failed - N/A                            |

| Power Level 1 Disabled                                |

|                                                       |

### Seek

(code: 7Xh)

This command is effectively a NOP command to the Card although it does perform a range check.

## Set Features (code: EFh)

This command is used by the host to establish or select certain features.

| Feature | Description                                                                |

|---------|----------------------------------------------------------------------------|

| 01H     | Enable 8-bit data transfers                                                |

| 55H     | Disable Read Look Ahead                                                    |

| 66H     | Disable Power on Reset (POR)<br>establishment of defaults at Soft<br>Reset |

| 81H     | Disable 8-bit data transfers                                               |

| ВВН     | 4bytes of data apply on Read/Write<br>Long commands                        |

| ССН     | Enable Power on Reset (POR)<br>establishment of default at Soft<br>Reset   |

### Set Multiple Mode (code: C6h)

This command enables the module to perform Read and Write Multiple operations and establishes the block count for these commands.

### Set Sleep Mode (code: E6h or 99h)

This is the only command that allows the host to set the module into Sleep mode. When the module is set to sleep mode, the module clears the BSY line and issues an interrupt. The module enters sleep mode and the only method to make the module active again (back to normal operation) is by performing a hardware reset or a software reset.

### Stand By

(code: E2h or 96h)

This command is sets the module in Standby mode. If the Sector Count Register is a value other than 0H, an Auto Power Down is enabled and when the module returns to the idle mode, the timer starts a countdown. The time is set in the Sector Count Register.

## Stand By Immediate (code: E0h or 94h)

This command causes the module to set BSY, enter the Standby mode, clear BSY and return the interrupt immediately.

## Translate Sector (code: 87h)

This command allows the host a method of determining the exact number of times a user sector has been erased and programmed. This command is not supported.

## Wear Level (code: F5h)

This command is effectively a NOP command and only implemented for backward compatibility. The Sector Count Register will always be returned with an 00h indicating Wear Level is not needed.

## Write Buffer (code: E8h)

This command enables the host to overwrite the contents of the module's sector buffer with any data pattern desired.

## Write Long Sector (code: 32h or 33h)

This command is provided for compatibility purposes and is similar to the Write Sector(s) command except that it writes 516 bytes instead of 512 bytes.

## Write Multiple (code: C5h)

This command is similar to the Write Sectors command. Interrupts are not presented on each sector, but on the transfer of a block which contains the number of sectors defined by Set Multiple command.

## Write Multiple without Erase (code: CDh)

This command is similar to the Write Multiple command with the exception that an implied erase before the write operation is not performed. Note that before using this command, it is required to erase the repective sectors using the Erase Sectors command.

## Write Sector(s) (code: 30h or 31h)

This command writes from 1 to 256 sectors as specified in the Sector Count register. A sector count of zero requests 256 sectors. The transfer begins at the sector specified in the Sector Number register.

### Write Sector(s) without Erase (code: 38h)

This command is similar to the Write Sector(s) command with the exception that an implied erase before the write operation is not performed. Note that before using this command, it is required to erase the repective sectors using the Erase Sectors command.

## Write Verify (code: 3Ch)

This command is similar to the Write Sector(s) command except each sector is verified immediately after being written.

#### **REVISION HISTORY**

#### Rev. Change Description from Previous Revision

- -301 5/26/04. Initial Release.

- -302 5/27/04. Missing dimensioning added to 40-pin horizontal plug-in Package Dimensions.

- -303 7/2/04. Pin Description changes: -IOIS16 not used in IDE mode; -IORDY description corrected to not used by module and pulled up by 4.7K ohm resistor. Performance rates for read and write described as sustained read and sustained write. Error register bit 0 Function "not supported" phrase removed. DMA commands removed (paper only error indicated that DMA was supported). Identify Drive Information table updated to reflect DMA not supported. DC Characterists Sleep Mode value changed from 120uA to 1200uA for 5V power supply.

- -304 7/9/04. Endurance increased from 300,000 cycles min to 2 million cycles min.

- -305 7/22/04. "up to" added to sustained read and write data rate performance.

- -306 7/27/04 SLFDM44LPH-064J(I) dimensions corrected to released product. Ordering Information made easy to read.

- -307 7/30/04. P/N SLFDM44LPH-064J(I) corrected to SLFDM44H-064J(I).

- -308 8/23/04. WP Jumpers labeled "Optional." Tolerance of connector protrusion in SLFLD40LPV-xxxJ(I) dimensions changed from 0.005 to 0.050. Environmental Characteristics updated to testing parameters. Definition for Serial #, Firmware Rev., and Model # in the Identify Drive Information table added in callout. Words 0, 4-5, 20-21, 49, and 63 in Drive ID table corrected. SLFLD44V-xxxJ(I) flash disk module added.

- -309 10/21/04. Master/Slave jumpers corrected in dimension illustration.

- -310 10/29/04. Standard ECC, Endurance, and Warranty bullets added to Features on page 1.

- -311 1/31/05. Write speed updated to "up to 1.5MB/s" from 3.4MB/s.

- -312 2/16/05. Shock parameter of 11ms corrected to 0.330 to 0.750ms. WP jumpering removed. 3/14/05 Humidity parameter updated to 95% from 85%. CHS values updated. 4/22/05. U and housing options added.

- -313 4/22/05. This rev of the spec has MWDMA support. 7/20/05. For higher revs of this spec, the MWDMA support has been removed. Product with MWDMA has been given a P/N of SLFDMpqr-064J2(U)(I).

- -314 7/20/05. Separate shock and vibration for U option added. 3.3V op voltage added to specification.

SimpleTech Inc. reserves the right to make changes to specifications and product descriptions such as but not limited to numbers, parameters and other technical information contained herein without notice. Contact SimpleTech Inc. sales office to obtain the latest specifications. SimpleTech Inc. grants no warranty with respect to this Data Sheet, neither explicit nor implied, and it is not liable for direct or indirect damages. Some States do not grant the exclusion of incidental damages and as such this statement may not be valid in such states. The provisions of this Data Sheet do not convey to the purchaser of the device any license under any patent rights or other intellectual property rights of SimpleTech Inc. or others.

### **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STEC:

SLFDM40LPV-064J