# L6918 L6918A

# 5 BIT PROGRAMMABLE MULTIPHASE CONTROLLER

- OUTPUT CURRENT IN EXCESS OF 100A

- ULTRA FAST LOAD TRANSIENT RESPONSE

- REMOTE SENSE BUFFER

- INTEGRATED 2A GATE DRIVERS

- 5 BIT VID VOLTAGE POSITIONING, VRM 9.0

- 0.6% INTERNAL REFERENCE ACCURACY

- DIGITAL 2048 STEP SOFT-START

- OVP & OCP PROTECTIONS

- Rdson or Rsense CURRENT SENSING

- 1200KHz EFFECTIVE SWITCHING FREQUENCY, EXTERNALLY ADJUSTABLE

- POWER GOOD OUTPUT AND INHIBIT

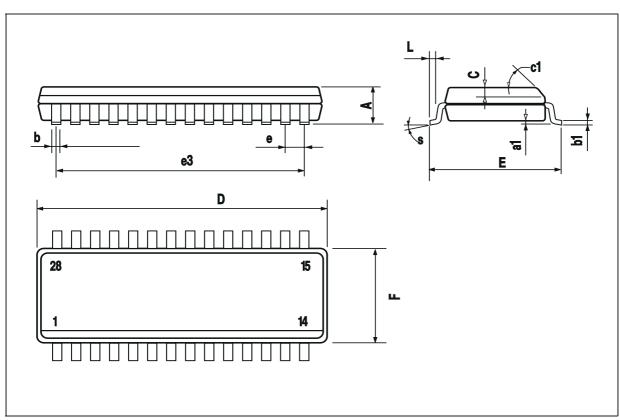

- PACKAGE: SO28

#### **APPLICATIONS**

- HIGH DENSITY DC-DC FOR SERVERS AND WORKSTATIONS

- SUPPLY FOR HIGH CURRENT MICROPROCESSORS

- DISTRIBUTED POWER

#### **DESCRIPTION**

L6918A is a master device that it has to be combined with the L6918,slave, realizing a 4-phases topology, interleaved. The device kit is specifically designed to provide a high performance/high density DC/DC conversion for high current microprocessors and distributed power. Each device implements a dual-phase step-down controller with a 180° phase-shift between each phase.

A precise 5-bit DAC allows adjusting the output voltage from 1.100V to 1.850V with 25mV binary steps. The high peak current gate drives affords to have high system switching frequency, typically of 1200KHz, and higher by external adjustement.

The device kit assure a fast protection against OVP, UVP and OCP. An internal crowbar, by turning on the low side mosfets, eliminates the need of external protection. In case of over-current, the system works in Constant Current mode.

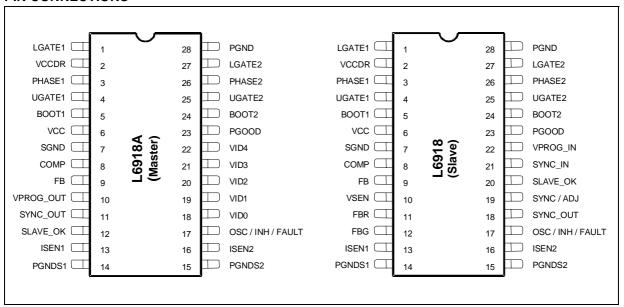

#### PIN CONNECTIONS

October 2002 1/35

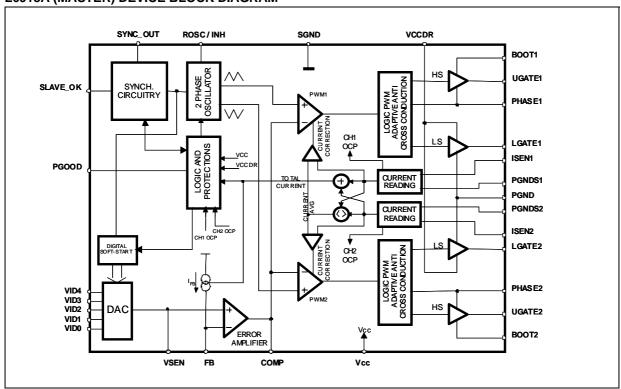

# L6918A (MASTER) DEVICE BLOCK DIAGRAM

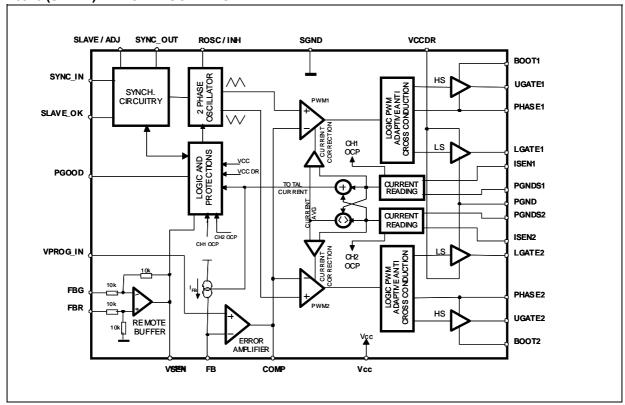

# L6918 (SLAVE) DEVICE BLOCK DIAGRAM

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                                               | Parameter                                | Value           | Unit |

|--------------------------------------------------------------------------------------|------------------------------------------|-----------------|------|

| Vcc, V <sub>CCDR</sub>                                                               | To PGND                                  | 15              | V    |

| V <sub>BOOT</sub> -V <sub>PHASE</sub>                                                | Boot Voltage                             | 15              | V    |

| V <sub>UGATE1</sub> -V <sub>PHASE1</sub><br>V <sub>UGATE2</sub> -V <sub>PHASE2</sub> |                                          | 15              | V    |

|                                                                                      | LGATE1, PHASE1, LGATE2, PHASE2 to PGND   | -0.3 to Vcc+0.3 | V    |

|                                                                                      | VID0 to VID4                             | -0.3 to 5       | V    |

|                                                                                      | All other pins to PGND                   | -0.3 to 7       | V    |

| V <sub>PHASEx</sub>                                                                  | Sustainable Peak Voltage t<20nS @ 600kHz | 26              | V    |

# THERMAL DATA

| Symbol                | Parameter                              | Value      | Unit   |

|-----------------------|----------------------------------------|------------|--------|

| R <sub>th j-amb</sub> | Thermal Resistance Junction to Ambient | 60         | °C / W |

| T <sub>max</sub>      | Maximum junction temperature           | 150        | °C     |

| T <sub>storage</sub>  | Storage temperature range              | -40 to 150 | °C     |

| Tj                    | Junction Temperature Range             | 0 to 125   | °C     |

| P <sub>MAX</sub>      | Max power dissipation at Tamb=25°C     | 2          | W      |

# L6918A (MASTER) PIN FUNCTION

| N. | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | LGATE1    | Channel 1 low side gate driver output.                                                                                                                                                                                                                                                                                                                                                        |

| 2  | VCCDR     | LS Mosfet driver supply. 5V or 12V buses can be used.                                                                                                                                                                                                                                                                                                                                         |

| 3  | PHASE1    | This pin is connected to the Source of the upper mosfet and provides the return path for the high side driver of channel 1.                                                                                                                                                                                                                                                                   |

| 4  | UGATE1    | Channel 1 high side gate driver output.                                                                                                                                                                                                                                                                                                                                                       |

| 5  | BOOT1     | Channel 1 bootstrap capacitor pin. This pin supplies the high side driver. Connect through a capacitor to the PHASE1 pin and through a diode to Vcc (cathode vs. boot).                                                                                                                                                                                                                       |

| 6  | VCC       | Device supply voltage. The operative supply voltage is 12V.                                                                                                                                                                                                                                                                                                                                   |

| 7  | GND       | All the internal references are referred to this pin. Connect it to the PCB signal ground.                                                                                                                                                                                                                                                                                                    |

| 8  | COMP      | This pin is connected to the error amplifier output and is used to compensate the control feedback loop.                                                                                                                                                                                                                                                                                      |

| 9  | FB        | This pin is connected to the error amplifier inverting input and is used to compensate the voltage control feedback loop.  A current proportional to the sum of the current sensed in both channel is sourced from this pin (50µA at full load, 70µA at the Over Current threshold). Connecting a resistor R <sub>FB</sub> between this pin and VSEN pin allows programming the droop effect. |

| 10 | VPROG_OUT | Reference voltage output used for voltage regulation. This pin must be connected together with the slave device VPROG_IN pin. Filter to SGND with 1nF capacitor (a total 30nF distributed capacitance is allowed).                                                                                                                                                                            |

| 11 | SYNC_OUT  | Synchronization output signal. From this pin exits a square - 50% duty cycle - 5Vpp –90 deg phase shifted wave clock signal that the Slave device PLL locks to. Connect this pin to the Slave SYNC_IN pin.                                                                                                                                                                                    |

| 12 | SLAVE_OK  | Open-drain input/output used for start-up and to manage protections as shown in the timing diagram. Internally pulled-up. Connect together with other IC's SLAVE_OK pin. Filter with 1nF capacitor vs. SGND.                                                                                                                                                                                  |

# L6918A (MASTER) PIN FUNCTION (continued)

| N.             | Name             | Description                                                                                                                                                                                                                                                                                                                     |

|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

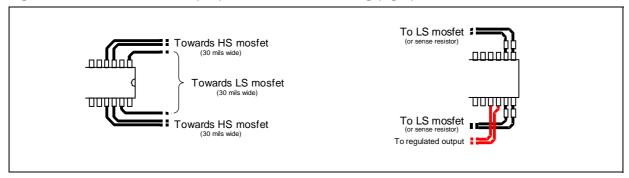

| 13             | ISEN1            | Channel 1 current sense pin. The output current may be sensed across a sense resistor or across the low-side mosfet RdsON. This pin has to be connected to the low-side mosfet drain or to the sense resistor through a resistor Rg in order to program the current intervention for each phase at 140% as follow:              |

|                |                  | $I_{OCPx} = \frac{35\mu A \cdot R_g}{R_{sense}}$                                                                                                                                                                                                                                                                                |

|                |                  | Where $35\mu A$ is the current offset information relative to the Over Current condition (offset at OC threshold minus offset at zero load). The net connecting the pin to the sense point must be routed as close as possible to the PGNDS1 net in order to couple in common mode any picked-up noise.                         |

| 14             | PGNDS1           | Channel 1 Power Ground sense pin. The net connecting the pin to the sense point must be routed as close as possible to the ISEN1 net in order to couple in common mode any picked-up noise.                                                                                                                                     |

| 15             | PGNDS2           | Channel 2 Power Ground sense pin. The net connecting the pin to the sense point must be routed as close as possible to the ISEN2 net in order to couple in common mode any picked-up noise.                                                                                                                                     |

| 16             | ISEN2            | Channel 2 current sense pin. The output current may be sensed across a sense resistor or across the low-side mosfet Rds <sub>ON</sub> . This pin has to be connected to the low-side mosfet drain or to the sense resistor through a resistor Rg in order to program the current intervention for each phase at 140% as follow: |

|                |                  | $I_{OCPx} = \frac{35\mu A \cdot R_g}{R_{sense}}$                                                                                                                                                                                                                                                                                |

|                |                  | Where 35µA is the current offset information relative to the Over Current condition (offset at OC threshold minus offset at zero load). The net connecting the pin to the sense point must be routed as close as possible to the PGNDS2 net in order to couple in common mode any picked-up noise.                              |

| 17             | OSC/INH<br>FAULT | Oscillator switching frequency pin. Connecting an external resistor from this pin to GND, the external frequency is increased according to the equation:                                                                                                                                                                        |

|                |                  | $f_{S} = 300 \text{KHz} + \frac{14.82 \cdot 10^{6}}{R_{OSC}(K\Omega)}$                                                                                                                                                                                                                                                          |

|                |                  | Connecting a resistor from this pin to Vcc (12V), the switching frequency is reduced according to the equation:                                                                                                                                                                                                                 |

|                |                  | $f_{S} = 300 \text{KHz} + \frac{12.91 \cdot 10^{7}}{R_{OSC}(K\Omega)}$                                                                                                                                                                                                                                                          |

|                |                  | If the pin is not connected, the switching frequency is 300KHz. Forcing the pin to a voltage lower than 0.8V, the device stop operation and enter the inhibit state; all mosfets are turned OFF.                                                                                                                                |

| 18<br>to<br>22 | VID0-4           | Voltage Identification pins. These input are internally pulled-up and TTL compatible. They are used to program the output voltage as specified in Table 1 and to set the over voltage and power good thresholds.  Connect to GND to program a '0' while leave floating to program a '1'.                                        |

| 23             | PGOOD            | This pin is an open collector output and is pulled low if the output voltage is not within the above specified thresholds. It must be connected with the Slave's PGOOD pin. If not used may be left floating.                                                                                                                   |

| 24             | BOOT2            | Channel 2 bootstrap capacitor pin. This pin supplies the high side driver. Connect through a capacitor to the PHASE2 pin and through a diode to Vcc (cathode vs. boot).                                                                                                                                                         |

| 25             | UGATE2           | Channel 2 high side gate driver output.                                                                                                                                                                                                                                                                                         |

| 26             | PHASE2           | This pin is connected to the source of the upper mosfet and provides the return path for the high side driver of channel 2.                                                                                                                                                                                                     |

| 27             | LGATE2           | Channel 2 low side gate driver output.                                                                                                                                                                                                                                                                                          |

| 28             | PGND             | Power ground pin. This pin is common to both sections and it must be connected through the closest path to the low side mosfets source pins in order to reduce the noise injection into the device.                                                                                                                             |

# L6918 (SLAVE) PIN FUNCTION

| N. | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | LGATE1 | Channel 1 low side gate driver output.                                                                                                                                                                                                                                                                                                                                                          |

| 2  | VCCDR  | LS Mosfet driver supply. 5V or 12V buses can be used.                                                                                                                                                                                                                                                                                                                                           |

| 3  | PHASE1 | This pin is connected to the Source of the upper mosfet and provides the return path for the high side driver of channel 1.                                                                                                                                                                                                                                                                     |

| 4  | UGATE1 | Channel 1 high side gate driver output.                                                                                                                                                                                                                                                                                                                                                         |

| 5  | BOOT1  | Channel 1 bootstrap capacitor pin. This pin supplies the high side driver. Connect through a capacitor to the PHASE1 pin and through a diode to Vcc (cathode vs. boot).                                                                                                                                                                                                                         |

| 6  | VCC    | Device supply voltage. The operative supply voltage is 12V.                                                                                                                                                                                                                                                                                                                                     |

| 7  | GND    | All the internal references are referred to this pin. Connect it to the PCB signal ground.                                                                                                                                                                                                                                                                                                      |

| 8  | COMP   | This pin is connected to the error amplifier output and is used to compensate the control feedback loop.                                                                                                                                                                                                                                                                                        |

| 9  | FB     | This pin is connected to the error amplifier inverting input and is used to compensate the voltage control feedback loop. A current proportional to the sum of the current sensed in both channel is sourced from this pin $(50\mu A$ at full load, $70\mu A$ at the Over Current threshold). Connecting a resistor $R_{FB}$ between this pin and VSEN pin allows programming the droop effect. |

| 10 | VSEN   | Connected to the output voltage it is able to manage Over & Under-voltage conditions and the PGOOD signal. It is internally connected with the output of the Remote Sense Buffer for Remote Sense of the regulated voltage.  If no Remote Sense is implemented, connect it directly to the regulated voltage in order to manage OVP, UVP and PGOOD.                                             |

| 11 | FBR    | Remote sense buffer non-inverting input. It has to be connected to the positive side of the load to perform a remote sense.  If no remote sense is implemented, connect directly to the output voltage (in this case connect also the VSEN pin directly to the output regulated voltage).                                                                                                       |

| 12 | FBG    | Remote sense buffer inverting input. It has to be connected to the negative side of the load to perform a remote sense.  Pull-down to ground if no remote sense is implemented.                                                                                                                                                                                                                 |

| 13 | ISEN1  | Channel 1 current sense pin. The output current may be sensed across a sense resistor or across the low-side mosfet Rds <sub>ON</sub> . This pin has to be connected to the low-side mosfet drain or to the sense resistor through a resistor Rg in order to program the current intervention for each phase at 140% as follow: $I_{OCPx} = \frac{35 \mu A \cdot R_g}{R_{sense}}$               |

|    |        | Where 35μA is the current offset information relative to the Over Current condition (offset at OC threshold minus offset at zero load).  The net connecting the pin to the sense point must be routed as close as possible to the PGNDS1 net in order to couple in common mode any picked-up noise.                                                                                             |

| 14 | PGNDS1 | Channel 1 Power Ground sense pin. The net connecting the pin to the sense point must be routed as close as possible to the ISEN1 net in order to couple in common mode any picked-up noise.                                                                                                                                                                                                     |

| 15 | PGNDS2 | Channel 2 Power Ground sense pin. The net connecting the pin to the sense point must be routed as close as possible to the ISEN2 net in order to couple in common mode any picked-up noise.                                                                                                                                                                                                     |

# L6918 (SLAVE) PIN FUNCTION (continued)

| N. | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 | ISEN2            | Channel 2 current sense pin. The output current may be sensed across a sense resistor or across the low-side mosfet Rds <sub>ON</sub> . This pin has to be connected to the low-side mosfet drain or to the sense resistor through a resistor Rg in order to program the current intervention for each phase at 140% as follow:                                                                                                                                                                                                                                                                  |

|    |                  | $I_{OCPx} = \frac{35\mu A \cdot R_g}{R_{sense}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    |                  | Where 35µA is the current offset information relative to the Over Current condition (offset at OC threshold minus offset at zero load).  The net connecting the pin to the sense point must be routed as close as possible to the PGNDS2 net in order to couple in common mode any picked-up noise.                                                                                                                                                                                                                                                                                              |

| 17 | OSC/INH<br>FAULT | Oscillator switching frequency pin. Connecting an external resistor from this pin to GND, the external frequency is increased according to the equation:                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    |                  | $f_{S} = 300KHz + \frac{14.82 \cdot 10^{6}}{R_{OSC}(K\Omega)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    |                  | Connecting a resistor from this pin to Vcc (12V), the switching frequency is reduced according to the equation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    |                  | $f_{S} = 300KHz + \frac{12.91 \cdot 10^{7}}{R_{OSC}(K\Omega)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    |                  | If the pin is not connected, the switching frequency is 300KHz. Forcing the pin to a voltage lower than 0.8V, the device stops operation and enters the inhibit state; all mosfets are turned OFF.  The pin is forced high when an over voltage is detected. This condition is latched; to recover it is necessary turn off and on VCC.                                                                                                                                                                                                                                                          |

| 18 | SYNC_OUT         | Output synchronization signal. A 60° phase shift signal exits when the device works as a Slave while no signal exits when the device works as an adjustable.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 19 | SYNC / ADJ       | Slave or Adjustable operation.  Connecting this pin to GND the device becomes an adjustable two-phase controller using an external reference for its regulation. No soft start is implemented in this condition, so it must be performed with external circuitry. The device switches using its internal oscillator according to the frequency set by R <sub>OSC</sub> .  Leaving this pin floating, the device works as a Slave two-phase controller. It uses the reference sourced from the master device and an internal PLL locks the synchronization signal sourced from the master device. |

| 20 | SLAVE_OK         | Open-drain output used for start-up and to manage protections as shown in the timing diagram. Internally pulled-up. Connect together with other IC's SLAVE_OK pin. Filter with 1nF capacitor vs. SGND.                                                                                                                                                                                                                                                                                                                                                                                           |

| 21 | SYNC_IN          | Synchronization input signal locked during the slave operation. Connect to the master SYNC_OUT pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22 | VPROG_IN         | Reference voltage input used for voltage regulation.  This pin must be connected together with the other's slave (if present) to the VPROG_OUT pin of the master device.  Filter to SGND with 1nF capacitor (a total 30nF distributed capacitance is allowed).                                                                                                                                                                                                                                                                                                                                   |

|    |                  | If the device works as an Adjustable (SYNC/ADJ to GND), this is the reference used for the regulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 23 | PGOOD            | This pin is an open collector output and is pulled low if the output voltage is not within the above specified thresholds. It must be connected with the master's PGOOD pin. If not used may be left floating.                                                                                                                                                                                                                                                                                                                                                                                   |

# L6918 (SLAVE) PIN FUNCTION (continued)

| N. | Name   | Description                                                                                                                                                                                         |

|----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24 | BOOT2  | Channel 2 bootstrap capacitor pin. This pin supplies the high side driver. Connect through a capacitor to the PHASE2 pin and through a diode to Vcc (cathode vs. boot).                             |

| 25 | UGATE2 | Channel 2 high side gate driver output.                                                                                                                                                             |

| 26 | PHASE2 | This pin is connected to the Source of the upper mosfet and provides the return path for the high side driver of channel 2.                                                                         |

| 27 | LGATE2 | Channel 2 low side gate driver output.                                                                                                                                                              |

| 28 | PGND   | Power ground pin. This pin is common to both sections and it must be connected through the closest path to the low side mosfets source pins in order to reduce the noise injection into the device. |

# **ELECTRICAL CHARACTERISTCS**

(Vcc=12V±10%, TJ=0°C to 70°C unless otherwise specified)

| Symbol                                     | Parameter                            | Test Condition                                                            | Min.       | Тур. | Max.       | Unit       |

|--------------------------------------------|--------------------------------------|---------------------------------------------------------------------------|------------|------|------------|------------|

| Vcc SUPPL                                  | CURRENT                              |                                                                           |            |      |            | ı          |

| Icc                                        | Vcc supply current                   | HGATEx and LGATEx open V <sub>CCDR</sub> =V <sub>BOOT</sub> =12V          | 7.5        | 10   | 12.5       | mA         |

| I <sub>CCDR</sub>                          | V <sub>CCDR</sub> supply current     | LGATEx open; V <sub>CCDR</sub> =12V                                       | 2          | 3    | 4          | mA         |

| I <sub>BOOTx</sub>                         | Boot supply current                  | HGATEx open; PHASEx to<br>PGND<br>V <sub>CC</sub> =V <sub>BOOT</sub> =12V | 0.5        | 1    | 1.5        | mA         |

| POWER-ON                                   |                                      |                                                                           |            |      | •          |            |

|                                            | Turn-On V <sub>CC</sub> threshold    | V <sub>CC</sub> Rising; V <sub>CCDR</sub> =5V                             | 7.8        | 9    | 10.2       | V          |

|                                            | Turn-Off V <sub>CC</sub> threshold   | V <sub>CC</sub> Falling; V <sub>CCDR</sub> =5V                            | 6.5        | 7.5  | 8.5        | V          |

|                                            | Turn-On V <sub>CCDR</sub> Threshold  | V <sub>CCDR</sub> Rising; V <sub>CC</sub> =12V                            | 4.2        | 4.4  | 4.6        | V          |

|                                            | Turn-Off V <sub>CCDR</sub> Threshold | V <sub>CCDR</sub> Falling; V <sub>CC</sub> =12V                           | 4.0        | 4.2  | 4.4        | V          |

| OSCILLATO                                  | R AND INHIBIT                        |                                                                           |            |      | u.         | I.         |

| fosc                                       | Initial Accuracy                     | OSC = OPEN<br>OSC = OPEN; Tj=0°C to 125°C                                 | 278<br>270 | 300  | 322<br>330 | kHz<br>kHz |

| f <sub>OSC,Rosc</sub>                      | Total Accuracy                       | $R_T$ to GND=74k $\Omega$                                                 | 450        | 500  | 550        | kHz        |

| ΔVosc                                      | Ramp Amplitude                       |                                                                           |            | 2    |            | V          |

| d <sub>MAX</sub>                           | Maximum duty cycle                   | OSC = OPEN                                                                | 45         | 50   | -          | %          |

| INH                                        | Inhibit threshold                    | I <sub>SINK</sub> =5mA                                                    | 0.8        | 0.85 | 0.9        | V          |

| REFERENC                                   | E AND DAC only for L6918A (MA        | ASTER)                                                                    |            | •    | •          |            |

| V <sub>PROG_OUT</sub>                      | Reference Voltage<br>Accuracy        | VID0 to VID4 see Table1                                                   | -0.6       | -    | 0.6        | %          |

| I <sub>DAC</sub>                           | VID pull-up Current                  | VIDx = GND                                                                | 4          | 5    | 6          | μΑ         |

|                                            | VID pull-up Voltage                  | 3.1                                                                       | -          | 3.4  | V          |            |

| ERROR AM                                   | PLIFIER                              |                                                                           |            |      | _          | _          |

|                                            | DC Gain                              |                                                                           |            | 80   |            | dB         |

| SR                                         | Slew-Rate                            | COMP=10pF                                                                 |            | 15   |            | V/μS       |

|                                            | Offset                               |                                                                           | -7         |      | 7          | mV         |

| DIFFERENT                                  | TAL AMPLIFIER (REMOTE BUFF           | ER) only for L6918 (SLAVE)                                                |            |      |            |            |

|                                            | DC Gain                              |                                                                           |            | 1    |            | V/V        |

| CMRR                                       | Common Mode Rejection Ratio          |                                                                           |            | 40   |            | dB         |

|                                            | Input Offset                         | FBR=1.100V to1.850V;<br>FBG=GND                                           | -12        |      | 12         | mV         |

| DIFFERENT                                  | TAL CURRENT SENSING                  |                                                                           |            | _    | 1          |            |

| I <sub>ISEN1</sub> ,<br>I <sub>ISEN2</sub> | Bias Current                         | I <sub>LOAD</sub> = 0%                                                    | 45         | 50   | 55         | μΑ         |

# **ELECTRICAL CHARACTERISTCS** (continued)

(Vcc=12V±10%, TJ=0°C to 70°C unless otherwise specified)

| Symbol                                     | Parameter                                            | Test Condition                                                                       | Min. | Тур. | Max. | Unit |

|--------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>PGNDSx</sub>                        | Bias Current                                         |                                                                                      | 45   | 50   | 55   | μΑ   |

| I <sub>ISEN1</sub> ,<br>I <sub>ISEN2</sub> | Bias Current at Over Current Threshold               |                                                                                      | 80   | 85   | 90   | μА   |

| I <sub>FB</sub>                            | Active Droop Current                                 | I <sub>LOAD</sub> = 0                                                                |      | 0    | 1    | μΑ   |

|                                            |                                                      | I <sub>LOAD</sub> = 100%                                                             | 47.5 | 50   | 52.5 | μΑ   |

| GATE DRIV                                  | ERS                                                  | <u> </u>                                                                             |      | •    | •    |      |

| <sup>t</sup> RISE HGATE                    | High Side<br>Rise Time                               | V <sub>BOOTx</sub> -V <sub>PHASEx</sub> =10V;<br>C <sub>HGATEx</sub> to PHASEx=3.3nF |      | 15   | 30   | nS   |

| I <sub>HGATEx</sub>                        | High Side<br>Source Current                          | V <sub>BOOTx</sub> -V <sub>PHASEx</sub> =10V                                         |      | 2    |      | Α    |

| R <sub>HGATEx</sub>                        | High Side<br>Sink Resistance                         | V <sub>BOOTx</sub> -V <sub>PHASEx</sub> =12V;                                        | 1.5  | 2    | 2.5  | Ω    |

| <sup>t</sup> RISE LGATE                    | Low Side<br>Rise Time                                | V <sub>CCDR</sub> =10V;<br>C <sub>LGATEx</sub> to PGNDx=5.6nF                        |      | 30   | 55   | nS   |

| I <sub>LGATEx</sub>                        | Low Side<br>Source Current                           | V <sub>CCDR</sub> =10V                                                               |      | 1.8  |      | Α    |

| R <sub>LGATEx</sub>                        | Low Side<br>Sink Resistance                          | V <sub>CCDR</sub> =12V                                                               | 0.7  | 1.1  | 1.5  | Ω    |

| PROTECTIO                                  | NS                                                   |                                                                                      |      |      |      |      |

| PGOOD                                      | Upper Threshold<br>(V <sub>SEN</sub> / VPROG_IN)     | V <sub>SEN</sub> Rising                                                              | 109  | 112  | 115  | %    |

| PGOOD                                      | Lower Threshold<br>(V <sub>SEN</sub> / VPROG_IN)     | V <sub>SEN</sub> Falling                                                             | 87   | 90   | 93   | %    |

| OVP                                        | Over Voltage Threshold (V <sub>SEN</sub> / VPROG_IN) | V <sub>SEN</sub> Rising                                                              | 114  | 117  | 120  | %    |

| UVP                                        | Under Voltage Trip<br>(V <sub>SEN</sub> / VPROG_IN)  | V <sub>SEN</sub> Falling                                                             | 55   | 60   | 65   | %    |

| V <sub>PGOOD</sub>                         | PGOOD Voltage Low                                    | I <sub>PGOOD</sub> = -4mA                                                            | 0.3  | 0.4  | 0.5  | V    |

Table 1. VID Settings (only for L6918A)

| VID4 | VID3 | VID2 | VID1 | VID0 | Output<br>Voltage (V) | VID4 | VID3 | VID2 | VID1 | VID0 | Output<br>Voltage (V) |

|------|------|------|------|------|-----------------------|------|------|------|------|------|-----------------------|

| 0    | 0    | 0    | 0    | 0    | 1.850                 | 1    | 0    | 0    | 0    | 0    | 1.450                 |

| 0    | 0    | 0    | 0    | 1    | 1.825                 | 1    | 0    | 0    | 0    | 1    | 1.425                 |

| 0    | 0    | 0    | 1    | 0    | 1.800                 | 1    | 0    | 0    | 1    | 0    | 1.400                 |

| 0    | 0    | 0    | 1    | 1    | 1.775                 | 1    | 0    | 0    | 1    | 1    | 1.375                 |

| 0    | 0    | 1    | 0    | 0    | 1.750                 | 1    | 0    | 1    | 0    | 0    | 1.350                 |

| 0    | 0    | 1    | 0    | 1    | 1.725                 | 1    | 0    | 1    | 0    | 1    | 1.325                 |

| 0    | 0    | 1    | 1    | 0    | 1.700                 | 1    | 0    | 1    | 1    | 0    | 1.300                 |

| 0    | 0    | 1    | 1    | 1    | 1.675                 | 1    | 0    | 1    | 1    | 1    | 1.275                 |

| 0    | 1    | 0    | 0    | 0    | 1.650                 | 1    | 1    | 0    | 0    | 0    | 1.250                 |

| 0    | 1    | 0    | 0    | 1    | 1.625                 | 1    | 1    | 0    | 0    | 1    | 1.225                 |

| 0    | 1    | 0    | 1    | 0    | 1.600                 | 1    | 1    | 0    | 1    | 0    | 1.200                 |

| 0    | 1    | 0    | 1    | 1    | 1.575                 | 1    | 1    | 0    | 1    | 1    | 1.175                 |

| 0    | 1    | 1    | 0    | 0    | 1.550                 | 1    | 1    | 1    | 0    | 0    | 1.150                 |

| 0    | 1    | 1    | 0    | 1    | 1.525                 | 1    | 1    | 1    | 0    | 1    | 1.125                 |

| 0    | 1    | 1    | 1    | 0    | 1.500                 | 1    | 1    | 1    | 1    | 0    | 1.100                 |

| 0    | 1    | 1    | 1    | 1    | 1.475                 | 1    | 1    | 1    | 1    | 1    | Shutdown              |

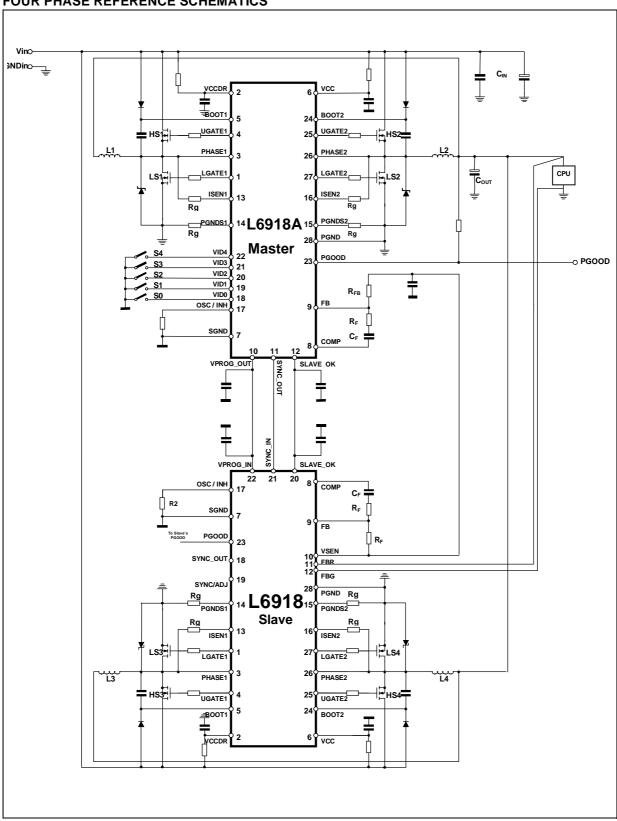

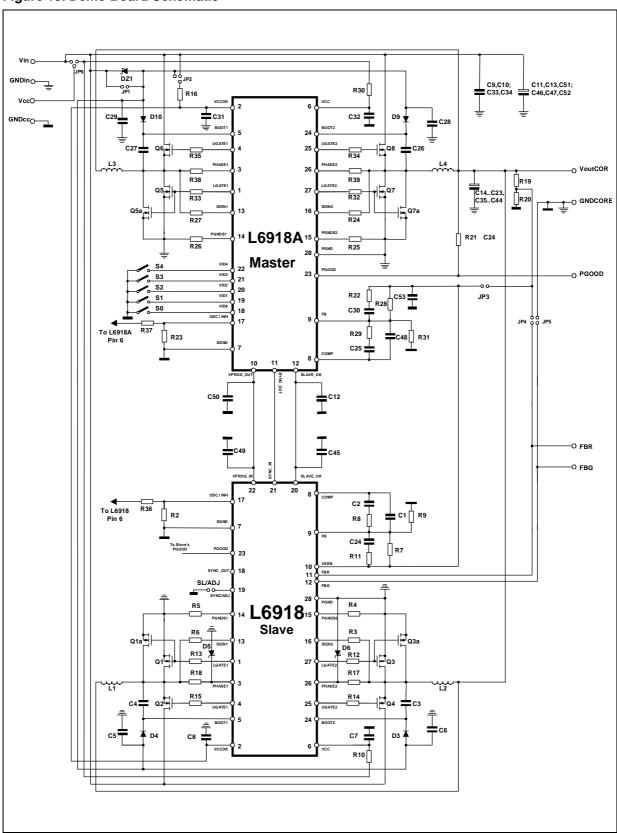

# FOUR PHASE REFERENCE SCHEMATICS

#### **DEVICES DESCRIPTION**

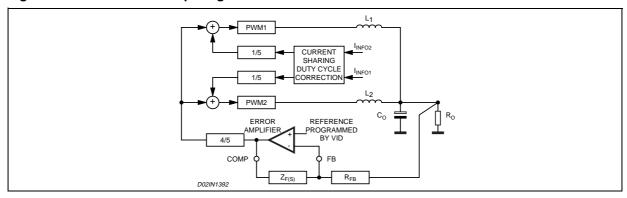

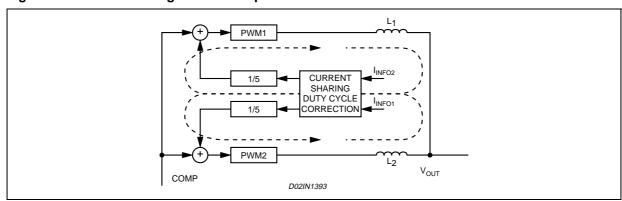

The devices are integrated circuit realized in BCD technology. They provide, in kit, a complete control logic and protections sets for a high performance four-phases step-down DC-DC converter optimized for microprocessors supply and High Density DC-DC converters. They are designed to drive N-Channel mosfets in an interleaved four-phase synchronous-rectified buck topology. Each controller provides a 180 deg phase shift between its two phases and a 90deg phase-shifted synchronization signal is passed from the master to the slave controller that locks the signal through a PLL. The resulting four-phases converter synchronized together results in a 90 deg phase shift on each phase, allowing a consistent reduction of the input capacitors ripple current, minimizing also the size and the power losses. The output voltage of the converter can be precisely regulated, programming the master's VID pins, from 1.100V to 1.850V with 25mV binary steps. The reference for the regulation is passed from the master device to the slave device through apposite pin likewise the synchronization signal. Each device provides an average current-mode control with fast transient response. They include a 300kHz free-running oscillator externally adjustable up to 600kHz, realized in order to multiply by 4 times the equivalent system frequency. The error amplifier features a 15MHz gain-bandwidth product and 10V/µs slew rate that permits high converter bandwidth for fast transient performances. Current information is read in all the devices across the lower mosfets R<sub>DSON</sub> or across a sense resistor in fully differential mode. The current information corrects the PWM output in order to equalize the average current carried the two phases of each device. Current sharing between the two phases of each device is then limited at ±10% over static and dynamic conditions. Current sharing between devices is assured by the droop function. The device protects against over-current, with an OCP threshold for each phase, entering in constant current mode. Since the current is read across the low side mosfets, the constant current keeps constant the bottom of the inductors current triangular waveform. When an under voltage is detected the Slave device latches. The Slave device also perform an over voltage protection that disable immediately both devices turning ON the lower driver and driving high the FAULT pin. Over Load condition are transmitted from the Slave device(s) to the master through the SLAVE OK line.

#### **MASTER - SLAVE INTERACTIONS**

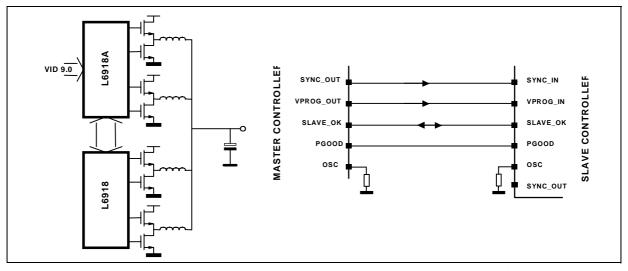

Figure 1. Four Phase connection with L6918 family

Master and slave devices are connected together in order to realize four-phase high performance step-down DC/DC converter. Four-phase converter is implemented using L6918A master and one L6918 slave devices as shown in figure 1.

A communication bus is implemented among all the controllers involved in the regulation. This bus consists in the following lines:

Reference (VPROG\_IN / VPROG\_OUT pins): Unidirectional line.

The devices share the reference for the regulation. The reference is programmed through the master device VID pins. It exits from the master through the VPROG\_OUT pin and enters the slave device through the VPROG\_IN pin(s). Filter externally with at least 1nF capacitor.

- Clock Signal (SYNC\_IN / SYNC\_OUT pins): Unidirectional line.

A synchronization signal exits from the Master device through the SYNC\_OUT pin with 90 deg phase-shift and enters the Slave device through the SYNC\_IN pin. The Slave device locks that signal through an internal PLL for its regulation. An auxiliary synchronization signal exits from the Slave through the SYNC\_OUT.

- SLAVE\_OK Bus (SLAVE\_OK pins): Bi-directional line.

While the supply voltages are increasing, this line is hold to GND by all the devices. The Slave device sets this line free (internally 5V pulled-up) when it is ready for the Soft-Start. After that this line is freed, the Master device starts the Soft Start (for further details about Soft-Start, see the relevant section).

During normal operation, the line is pulled low by the Slave device if an Over / Under voltage is detected (See relevant section).

# - PGOOD pins:

PGOOD pins are connected together and pulled-up. During Soft-Start, the master device hold down this line while during normal regulation the slave device de-assert the line if PGOOD has been lost.

Connections between the devices are shown in figure 1.

#### **OSCILLATOR**

The devices have been designed in order to operate on each phase at the same switching frequency of the internal oscillator. So, input and output resulting frequencies are four times bigger.

The oscillator is present in all the devices. Since the Master oscillator sets the main frequency for the regulation, the Slave oscillator gives an offset to the Slave's PLL. In this way the PLL is able to lock the synchronization signal that enters from its SYNC\_IN pin; it is able to recover up to ±15% offset in the synchronization signal frequency. It is then necessary to program the switching frequency for all the devices involved in the multi-phase conversion as follow.

The switching frequency is internally fixed to 300kHz. The internal oscillator generates the triangular waveform for the PWM charging and discharging with a constant current an internal capacitor. The current delivered to the oscillator is typically  $25\mu A$  (Fsw = 300KHz) and may be varied using an external resistor (R<sub>OSC</sub>) connected between OSC pin and GND or Vcc. Since the OSC pin is maintained at fixed voltage (typ. 1.235V), the frequency is varied proportionally to the current sunk (forced) from (into) the pin considering the internal gain of  $12KHz/\mu A$ .

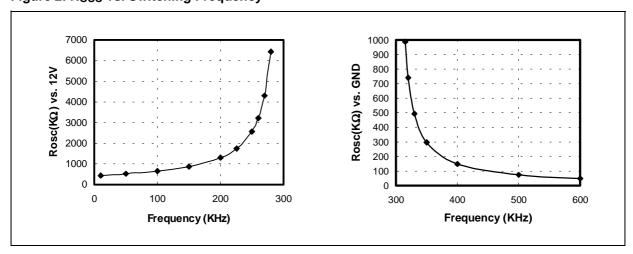

In particular connecting it to GND the frequency is increased (current is sunk from the pin), while connecting ROSC to Vcc=12V the frequency is reduced (current is forced into the pin), according to the following relationships:

$$R_{OSC} \, vs. \; GND: \; f_{S} \; = \; 300 \, kHz \; + \; \frac{1.237}{R_{OSC}(K\Omega)} \cdot \; 12 \\ \frac{KHz}{\mu A} = \; 300 \, KHz \; + \; \frac{14.82 \cdot 10^6}{R_{OSC}(K\Omega)} \; + \; \frac{12.82 \cdot 10^6}{R_{OSC}(K\Omega)} \; + \; \frac{12.827 \cdot 10^6}{R_{OSC}(K\Omega)}$$

$$R_{OSC} \, vs. \, \, 12V: \, \, f_{S} \, = \, 300 \, kHz + \frac{12 - 1.237}{R_{OSC}(K\Omega)} \cdot \, 12 \frac{KHz}{\mu A} = \, 300 \, KHz - \frac{12.918 \cdot 10^7}{R_{OSC}(K\Omega)}$$

Note that forcing a  $25\mu A$  current into this pin, the device stops switching because no current is delivered to the oscillator.

Figure 2 shows the frequency variation vs. the oscillator resistor ROSC considering the above reported relationships.

Figure 2. Rosc vs. Switching Frequency

## DIGITAL TO ANALOG CONVERTER (ONLY FOR MASTER DEVICE L6918A)

The built-in digital to analog converter allows the adjustment of the output voltage from 1.100V to 1.850V with 25mV as shown in the previous table 1. The internal reference is trimmed to ensure the precision of  $\pm 0.6\%$  and a zero temperature coefficient around the 70° C. The internal reference voltage for the regulation is programmed by the voltage identification (VID) pins. These are TTL compatible inputs of an internal DAC that is realized by means of a series of resistors providing a partition of the internal voltage reference. The VID code drives a multiplexer that selects a voltage on a precise point of the divider. The DAC output is delivered to an amplifier obtaining the VPROG voltage reference (i.e. the set-point of the error amplifier). Internal pull-ups are provided for the VID pins (realized with a  $5\mu$ A current generator); in this way, to program a logic "1" it is enough to leave the pin floating, while to program a logic "0" it is enough to short the pin to GND.

The voltage identification (VID) pin configuration also sets the power-good thresholds (PGOOD) and the Over/Under voltage protection (OVP/UVP) thresholds.

The reference for the regulation is generated into the master device and delivered to the slave device through the VPROG\_OUT / VPROG\_IN pins.

Programming the "11111" VID code, the device enters the NOCPU state: both devices keeps all mosfets OFF and the condition is latched. Cycle the power supply to restart operation. Moreover, in this condition, the OVP protection is still active into the slave device with a 0.8V threshold.

## **SOFT START AND INHIBIT**

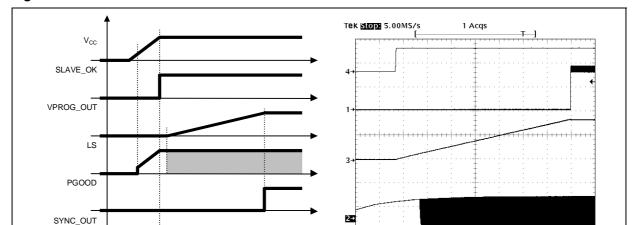

At start-up a ramp is generated from the master device increasing its loop reference from 0V to the final value programmed by VID in 2048 clock periods. The same reference is present on the VPROG\_OUT pin, producing an increasing loop reference also into the slave device. In this way all the devices involved in the multi-phase conversion start together with the same increasing reference (See Figure 3).

Before soft start, the lower power MOS are turned ON after that VCCDR reaches 2V (independently by Vcc value) to discharge the output capacitor and to protect the load from high side mosfet failures. Once soft start begins, the reference is increased and also the upper MOS begins to switch: the output voltage starts to increase with closed loop regulation. At the end of the digital soft start, the Power Good comparator is enabled and the PGOOD signal is then driven high (See fig. 3). The Under Voltage comparator is enabled when the reference voltage reaches 0.8V.

The Soft-Start will not take place, if both VCC and VCCDR pins are not above their own turn-on thresholds. The soft-start takes place, and the Master device starts to increase the reference, only if the SLAVE\_OK bus is at high level. The Slave device keeps this line shorted to GND until it is ready for the start-up while the master keeps this line free before soft-start; anyway, this line is shorted to GND if VCC and VCCDR are not above the turn-ON threshold. During normal operation, if any under-voltage is detected on one of the two supplies, the devices are shutdown.

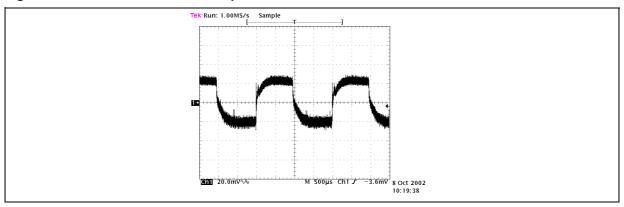

M1.00ms Ch1 🖍

Figure 3. Soft Start

Forcing the master OSC/INH/FAULT pin to a voltage lower than 0.8V, the devices enter in INHIBIT mode: all the power mosfets are turned off until this condition is removed. When this pin is freed, the OSC/INH/FAULT pin reaches the band-gap voltage and the soft start begin as previously explained.

CH1=PGOOD; CH2=LGATEx; CH3=VPROG\_OUT; CH4=SLAVE\_OK

In INHIBIT mode the Slave device still have both OVP and UVP protection active referring the thresholds to the incoming reference present at the VPROG\_IN pin if this one is greater than 0.8V. Otherwise (VPROG\_IN < 0.8V) UVP is disabled and the OVP threshold is fixed at 0.8V.

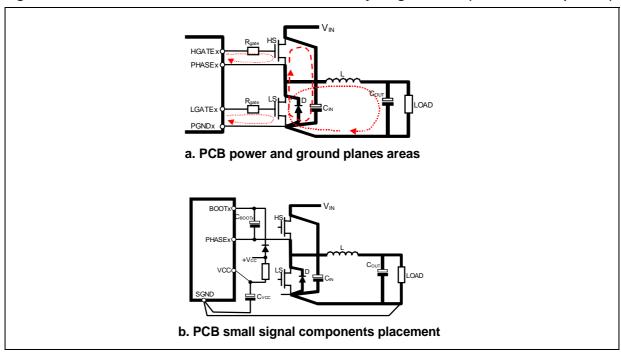

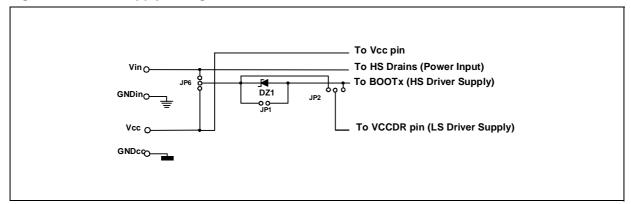

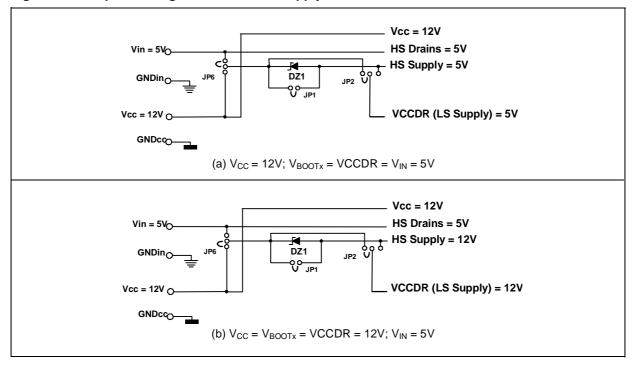

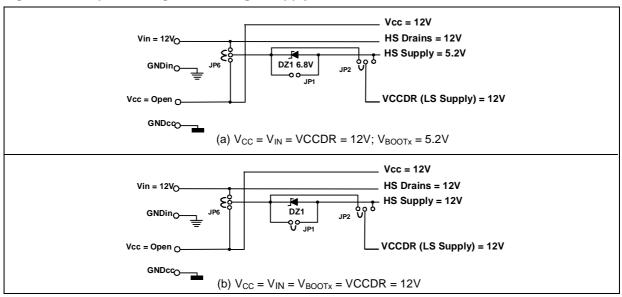

## **DRIVER SECTION**

The integrated high-current drivers allow using different types of power MOS (also multiple MOS to reduce the RDSON), maintaining fast switching transition.

The drivers for the high-side mosfets use BOOT pins for supply and PHASE pins for return. The drivers for the low-side mosfets use VCCDRV pin for supply and PGND pin for return. A minimum voltage of 5V at VCCDRV pin is required to start operations of the device. The controller embodies a sophisticated anti-shoot-through system to minimize low side body diode conduction time so maintaining good efficiency saving the use of Schottky diodes. The conduction time is reduced to few nanoseconds assuring that high-side and low-side mosfets are never switched on simultaneously: when the high-side mosfet turns off, the voltage on its source begins to fall; when the voltage reaches 2V, the low-side mosfet gate drive is applied with 30ns delay. When the low-side mosfet turns off, the voltage at LGATE pin is sensed. When it drops below 1V, the high-side mosfet gate drive is applied with a delay of 30ns. If the current flowing in the inductor is negative, the source of high-side mosfet will never drop. To allow the turning on of the low-side mosfet even in this case, a watchdog controller is enabled: if the source of the high-side mosfet don't drop for more than 240ns, the low side mosfet is switched on so allowing the negative current of the inductor to recirculate. This mechanism allows the system to regulate even if the current is negative.

The BOOT and VCCDRV pins are separated from IC's power supply (VCC pin) as well as signal ground (SGND pin) and power ground (PGND pin) in order to maximize the switching noise immunity.

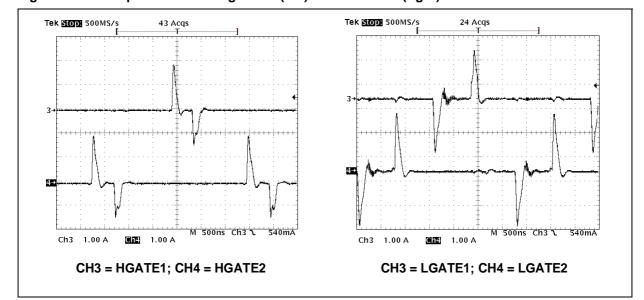

The peak current is shown for both the upper and the lower driver of the two phases in figure 4.A 10nF capacitive load has been used.

For the upper drivers, the source current is 1.9A while the sink current is 1.5A with  $V_{BOOT}$ - $V_{PHASE}$  = 12V; similarly, for the lower drivers, the source current is 2.4A while the sink current is 2A with  $V_{CCDR}$  = 12V.

Figure 4. Drivers peak current: High Side (left) and Low Side (right)

#### **CURRENT READING AND OVER CURRENT**

Each device involved in the four phase conversion has its own current reading circuitry and over current protection. As a results, the OCP network design for each device must be performed fort half of the maximum output current

The current flowing trough each phase is read using the voltage drop across the low side mosfets  $R_{DSON}$  or across a sense resistor ( $R_{SENSE}$ ) and internally converted into a current. The transconductance ratio is issued by the external resistor  $R_{DSON}$  placed outside the chip between ISENx and PGNDSx pins toward the reading points. The full differential current reading rejects noise and allows to place sensing element in different locations without affecting the measurement's accuracy. The current reading circuitry reads the current during the time in which the low-side mosfet is on (OFF Time). During this time, the reaction keeps the pin ISENx and PGNDSx at the same voltage while during the time in which the reading circuitry is off, an internal clamp keeps these two pins at the same voltage sinking from the ISENx pin the necessary current (Needed if low-side mosfet  $R_{dsON}$  sense is implemented to avoid absolute maximum rating overcome on ISENx pin).

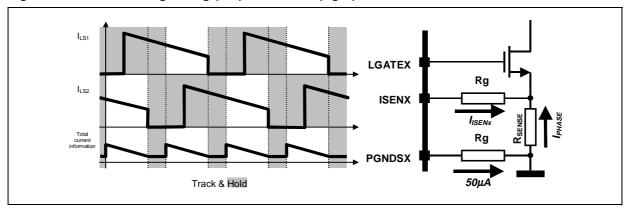

The proprietary current reading circuit allows a very precise and high bandwidth reading for both positive and negative current. This circuit reproduces the current flowing through the sensing element using a high speed Track & Hold Tran conductance amplifier. In particular, it reads the current during the second half of the OFF time reducing noise injection into the device due to the high side mosfet turn-on (See fig. 5). Track time must be at least 200ns to make proper reading of the delivered current.

This circuit sources a constant  $50\mu A$  current from the PGNDSx pin and keeps the pins ISENx and PGNDSx at the same voltage. Referring to figure 5, the current that flows in the ISENx pin is then given by the following equation:

$$I_{ISENx} = 50\mu A + \frac{R_{SENSE} \cdot I_{PHASE}}{R_{\alpha}} = 50\mu A + I_{INFOx}$$

Where R<sub>SENSE</sub> is an external sense resistor or the R<sub>dsON</sub> of the low side mosfet and Rg is the transconductance resistor used between ISENx and PGNDSx pins toward the reading points; I<sub>PHASE</sub> is the current carried by each phase.

The current information reproduced internally is represented by the second term of the previous equation as follow:

$$I_{INFOx} = \frac{R_{SENSE} \cdot I_{PHASE}}{R_{q}}$$

Since the current is read in differential mode, also negative current information is kept; this allow the device to check for dangerous returning current between the two phases assuring the complete equalization between the phase's currents.

Figure 5. Current reading timing (left) and circuit (right)

From the current information for each phase, information about the total current delivered ( $I_{FB}=II_{NFO1}+I_{INFO2}$ ) and the average current for each phase ( $I_{AVG}=(I_{INFO1}+I_{INFO2})/2$ ) is taken.  $I_{INFOX}$  is then compared to  $I_{AVG}$  to give the correction to the PWM output in order to equalize the current carried by the two phases.

The transconductance resistor Rg can be designed in order to have current information of  $25\mu$ A per phase at full nominal load; the over current intervention threshold is set at 140% of the nominal (II<sub>NFOx</sub> =  $35\mu$ A). According to the above relationship, the over current threshold (I<sub>OCPx</sub>) for each phase, which has to be placed at one half of the total delivered maximum current, results:

$$I_{OCPx} = \frac{35\mu A \cdot R_g}{R_{SENSE}} \qquad \quad R_g = \frac{I_{OCPx} \cdot R_{SENSE}}{35\mu A}$$

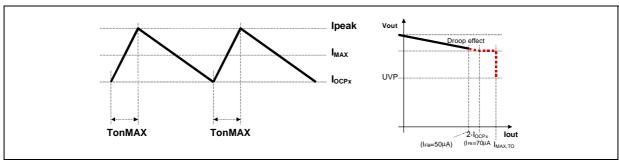

An over current is detected when the current flowing into the sense element is greater than IOCP ( $I_{INFOx}>35\mu A$ ): the device enters in Quasi-Constant-Current operation. The low-side mosfets stays ON until IINFO becomes lower than 35 $\mu A$  skipping clock cycles. The high side mosfets can be turned ON with a  $T_{ON}$  imposed by the control loop at the next available clock cycle and the device works in the usual way until another OCP event is detected.

The device limits the bottom of the inductor current triangular waveform. So the average current delivered can slightly increase also in Over Current condition since the current ripple increases. In fact, the ON time increases due to the OFF time rise because of the current has to reach the I<sub>OCP</sub> bottom. The worst-case condition is when the duty cycle reaches its maximum value (d=50% internally limited). When this happens, the device works in Constant Current and the output voltage decrease as the load increase. Crossing the UVP threshold causes the Slave device to pull down the SLAVE\_OK line. All mosfets are turned off and all the devices involved in the regulation stop working. Cycle the power supply to restart operation.

Figure 6 shows the constant current working condition

Figure 6. Constant Current operation

It can be observed that the peak current (Ipeak) is greater than the 140% but it can be determined as follow:

$$Ipeak = I_{OCPx} + \frac{V_{IN} - Vout_{min}}{L} \cdot Ton_{MAX} = I_{OCPx} + \frac{V_{IN} - Vout_{MIN}}{L} \cdot 0.5 \cdot T$$

Where Vout<sub>MIN</sub> is the minimum output voltage (UVP threshold).

The device works in Constant-Current, and the output voltage decreases as the load increase, until the output voltage reaches the under-voltage threshold (Vout<sub>MIN</sub>). When this threshold is crossed, all mosfets are turned off, the FAULT pin is driven high and the device stops working. Cycle the power supply to restart operation. The maximum average current during the Constant-Current behavior results:

$$I_{MAX,TOT} = 2 \cdot I_{MAX} = 2 \cdot \left(I_{OCPx} + \frac{Ipeak - I_{OCPx}}{2}\right)$$

In this particular situation, the switching frequency results reduced.

The ON time is the maximum allowed (TonMAX) while the OFF time depends on the application:

$$T_{OFF} = L \cdot \frac{Ipeak - I_{OCPx}}{V_{OUT}}$$

$f = \frac{1}{Ton_{MAX} + T_{OFF}}$

Over current is set anyway when  $I_{INFOx}$  reaches  $35\mu A$ . The full load value is only a convention to work with convenient values for  $I_{FB}$ . Since the OCP intervention threshold is fixed, to modify the percentage with respect to the load value, it can be simply considered that, for example, to have on OCP threshold of 170%, this will correspond to  $I_{INFOx} = 35\mu A$  ( $I_{FB} = 70\mu A$ ). The full load current will then correspond to  $I_{INFOx} = 20.5\mu A$  ( $I_{FB} = 41\mu A$ ).

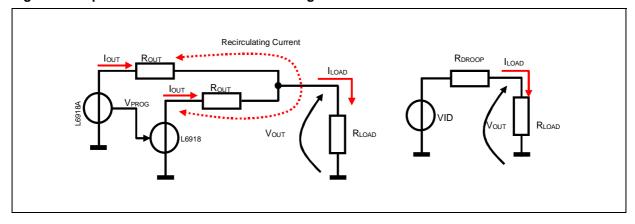

# INTEGRATED DROOP FUNCTION

The devices use the droop function to satisfy the requirements of high performance microprocessors, reducing the size and the cost of the output capacitor.

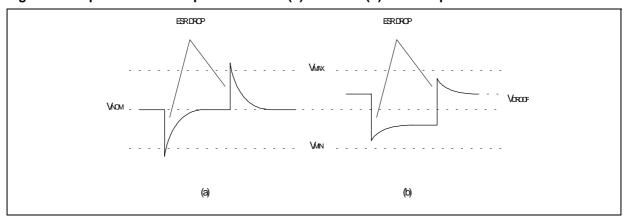

This method "recovers" part of the drop due to the output capacitor ESR in the load transient, introducing a dependence of the output voltage on the load current

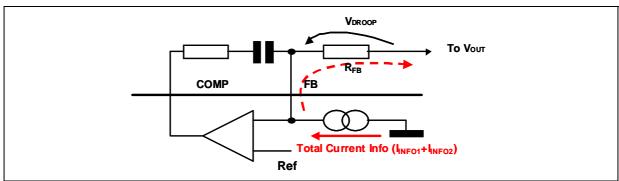

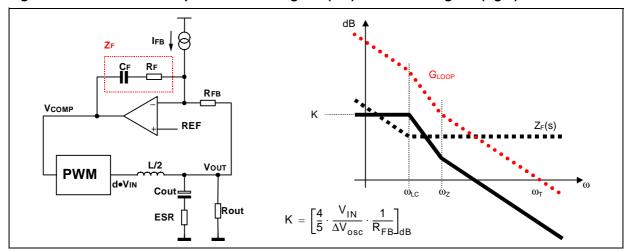

As shown in figure 7, the ESR drop is present in any case, but using the droop function the total deviation of the output voltage is minimized. In practice the droop function introduces a static error proportional to the output current that can be represented by an equivalent output resistance  $R_{OUT}$ . Since the device has an average current mode regulation, the information about the total current delivered is used to implement the Droop Function. This current (equal to the sum of both  $I_{INFOx}$ ) is sourced from the FB pin. Connecting a resistor between this pin and Vout, the total current information flows only in this resistor because the compensation network between

FB and COMP has always a capacitor in series (See fig. 8). The voltage regulated by each device is then equal to:

$$V_{OUT} = VID - R_{FB} \cdot I_{FB} = VID - R_{FB} \cdot \frac{R_{SENSE}}{Rg} \cdot I_{OUT}$$

Where I<sub>OUT</sub> is the output current of each device (equal to the total load current I<sub>LOAD</sub> divided by the number of devices N)

Since I<sub>FB</sub> depends on the current information about the two phases of each device, the output characteristic vs. load current is given by:

$$V_{OUT} = VID - R_{FB} \cdot I_{OUT} = VID - R_{FB} \cdot \frac{R_{SENSE}}{Rg} \cdot I_{OUT} = VID - R_{FB} \cdot \frac{R_{SENSE}}{Rg} \cdot \frac{I_{LOAD}}{2}$$

Where R<sub>OUT</sub> is the equivalent output resistance due to the droop function and I<sub>OUT</sub> is still the output current of each device (that is the total current delivered to the load I<sub>LOAD</sub> divided by 2.

Figure 7. Output transient response without (a) and with (b) the droop function

Figure 8. Active Droop Function Circuit

The feedback current is equal to  $50\mu A$  at nominal full load (I<sub>FB</sub> = I<sub>INFO1</sub> + I<sub>INFO2</sub>) and  $70\mu A$  at the OCP intervention threshold, so the maximum output voltage deviation is equal to:

$$\Delta V_{FULL\ POSITIVE\ LOAD} = +R_{FB} \cdot 50 \mu A$$

$\Delta V_{OL\ INTERVENTION} = +R_{FB} \cdot 70 \mu A$

477

Droop function is provided only for positive load; if negative load is applied, and then IINFOx<0, no current is sunk from the FB pin. The device regulates at the voltage programmed by the VID.

#### **OUTPUT VOLTAGE MONITORING AND PROTECTION: POWER GOOD**

The output voltage is monitored by the Slave device through the pin VSEN. If it is not within +12/-10% (typ.) of the programmed value, the PGOOD output is forced low. PGOOD is always active in the Slave device, also during soft-start. PGOOD in the Master device has the only masking function during soft-start. Since the master has not the output voltage sense, it keeps the PGOOD to GND during soft-start and after this step it is freed.

The Slave device provides Over-Voltage protection: when the voltage sensed by VSEN reaches 117% (typ.) of the reference voltage present at the VPROG\_IN pin, the Slave device stops switching keeping the LS mosfets ON. The FAULT pin is driven high (5V) and the SLAVE\_OK line is pulled low. The master device then stops switching keeping the LS mosfets ON, too. Since the condition is latched, power supply (Vcc) turn off and on is required to restart operations.

Under voltage protection is also provided and still detected by the Slave device. If the output voltage drops below the 60% (typ.) of the reference voltage present at the VPROG\_IN pin for more than one clock period, the Slave device stops switching turning OFF all mosfets and pulling down the SLAVE\_OK line: the Master device stops switching with LS mosfets ON. The OSC/INH/FAULT is not driven high in this case.

Both Over Voltage and Under Voltage are active also during soft start (Under Voltage after than Vout reaches 0.8V). During soft-start the reference voltage used to determine the UV threshold is the increasing voltage driven by the 2048 soft start digital counter. Moreover, OVP is always active, even during INHIBIT (see relevant section).

Over / Under Voltage behavior are shown in Figure 9.

OSC OSC L6918

L8 L6918A

UNDER VOLTAGE LATCH

OVER VOLTAGE LATCH

Figure 9. OVP and UVP latch

# REMOTE VOLTAGE SENSE

A remote sense buffer is integrated into the device to allow output voltage remote sense implementation without any additional external components. In this way, the output voltage programmed is regulated between the remote buffer inputs compensating motherboard trace losses or connector losses if the device is used for a VRM module.

The very low offset amplifier senses the output voltage remotely through the pins FBR and FBG (FBR is for the regulated voltage sense while FBG is for the ground sense) and reports this voltage internally at VSEN pin with unity gain eliminating the errors. Keeping the FBR and FBG traces parallel and guarded by a power plane results in common mode coupling for any picked-up noise.

If remote sense is not required, the output voltage is sensed by the VSEN pin connecting it directly to the output voltage. In this case the FBG and FBR pins must be connected anyway to the regulated voltage

#### **INPUT CAPACITOR**

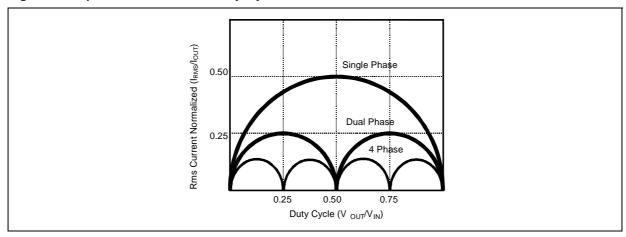

The input capacitor is designed considering mainly the input rms current that depends on the duty cycle as reported in figure. Considering the four phase topology, the input rms current is highly reduced comparing with single or dual phase operation.

It can be observed that the input rms value is one half of the dual-phase equivalent input current in the worst-case condition that happens for D=1/8, 3/8,5/8 and 7/8.

The power dissipated by the input capacitance is then equal to:

$$P_{RMS} = ESR \cdot (I_{RMS})^2$$

Input capacitor is designed in order to sustain the ripple relative to the maximum load duty cycle. To reach the high rms value needed by the CPU power supply application and also to minimize components cost, the input capacitance is realized by more than one physical capacitor. The equivalent rms current is simply the sum of the single capacitor's rms current.

Figure 10. Input rms Current vs. Duty Cycle.

## **OUTPUT CAPACITOR**

Since the microprocessors require a current variation beyond 100A doing load transients, with a slope in the range of tenth  $A/\mu s$ , the output capacitor is a basic component for the fast response of the power supply.

Dual phase topology reduces the amount of output capacitance needed because of faster load transient response (switching frequency is doubled at the load connections). Current ripple cancellation due to the 180° phase shift between the two phases also reduces requirements on the output ESR to sustain a specified voltage ripple.

When a load transient is applied to the converter's output, for first few microseconds the current to the load is supplied by the output capacitors. The controller recognizes immediately the load transient and increases the duty cycle, but the current slope is limited by the inductor value.

The output voltage has a first drop due to the current variation inside the capacitor (neglecting the effect of the ESL):

$$\Delta V_{OLIT} = \Delta I_{OLIT} \cdot ESR$$

A minimum capacitor value is required to sustain the current during the load transient without discharge it. The voltage drop due to the output capacitor discharge is given by the following equation:

$$\Delta V_{OUT} = \frac{\Delta i_{OUT}^2 \cdot L}{2 \cdot C_{OUT} \cdot (V_{INmin} \cdot D_{MAX} - V_{OUT})}$$

Where D<sub>MAX</sub> is the maximum duty cycle value. The lower is the ESR, the lower is the output drop during load transient and the lower is the output voltage static ripple.

#### INDUCTOR DESIGN

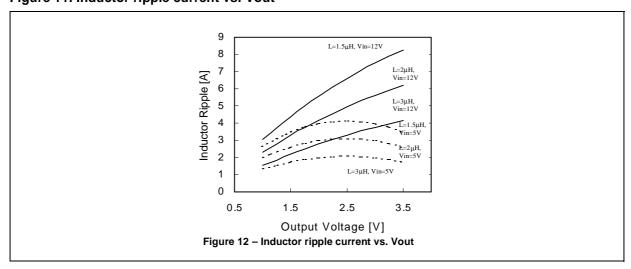

The inductance value is defined by a compromise between the transient response time, the efficiency, the cost and the size. The inductor has to be calculated to sustain the output and the input voltage variation to maintain the ripple current  $\Delta I_L$  between 20% and 30% of the maximum output current. The inductance value can be calculated with this relationship:

$$L \; = \; \frac{V_{IN} - V_{OUT}}{f_{SW} \cdot \Delta I_L} \cdot \frac{V_{OUT}}{V_{IN}} \label{eq:loss}$$

Where f<sub>SW</sub> is the switching frequency, V<sub>IN</sub> is the input voltage and V<sub>OUT</sub> is the output voltage.

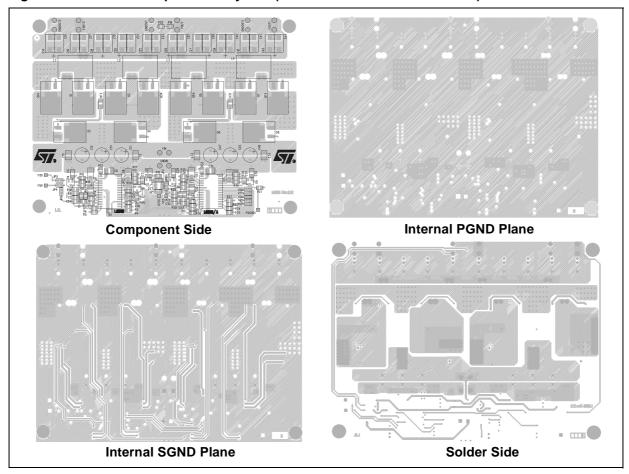

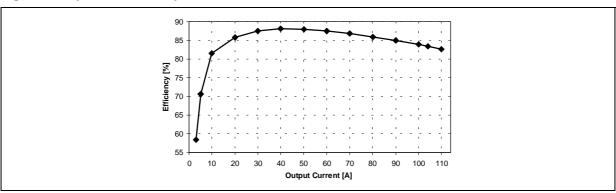

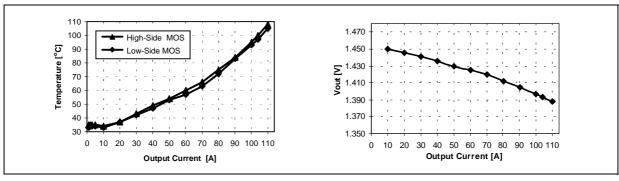

Increasing the value of the inductance reduces the ripple current but, at the same time, reduces the converter response time to a load transient. The response time is the time required by the inductor to change its current from initial to final value. Since the inductor has not finished its charging time, the output current is supplied by the output capacitors. Minimizing the response time can minimize the output capacitance required.