# **Boomer**® Audio Power Amplifier Series

## **Stereo Class D Spatial Array**

### **General Description**

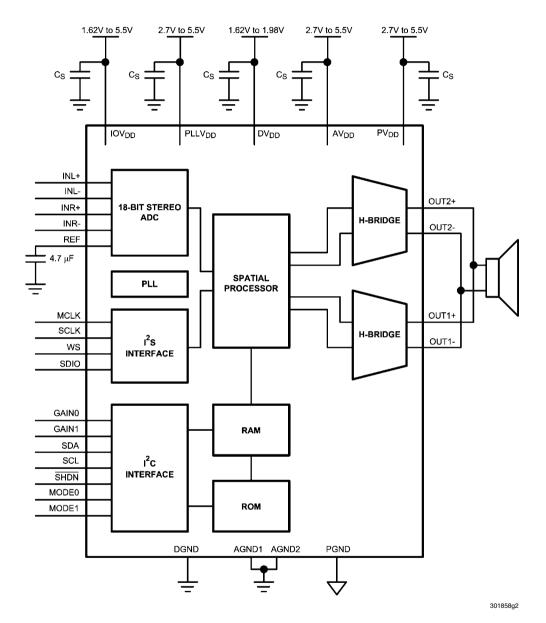

The LM48903 is a stereo Class D amplifier that utilizes TI's proprietary spatial sound processor to create an enhanced sound stage for portable multimedia devices. The Class D output stages feature National's edge rate control (ERC) PWM architecture that significantly reduces RF emissions while preserving audio quality and efficiency.

The LM48903's flexible I<sup>2</sup>S interface is compatible with standard serial audio interfaces. A stereo differential-input ADC gives the device the ability to process analog stereo audio signals.

The LM48903 is configured through an I²C compatible interface and is capable of delivering 1.7W/channel of continuous output power into an  $8\Omega$  load with less than 10% THD+N.

Output short circuit and thermal overload protection prevent the device from being damaged during fault conditions. Click and pop suppression eliminates audible transients on powerup/down and during shutdown. The LM48903 is available in space saving micro SMD package.

### **Key Specifications**

■ PSRR at 217Hz

| SNR (A-Weighted) | 90dBA (typ) |

|------------------|-------------|

■ Output Power/channel, PV<sub>DD</sub> = 5V

| $R_L = 8\Omega$ , THD+N $\leq 1\%$ | 1.3W (typ)  |

|------------------------------------|-------------|

| THD+N                              | 0.08% (typ) |

| Efficiency/Channel                 | 91% (typ)   |

#### **Features**

- Spatial Sound Processing

- I2S Input

- Stereo, Analog, Differential-Input ADC

- Edge Rate Control

- Short Circuit and Thermal Overload Protection

- Minimum external components

- Click and Pop suppression

- Micro-power shutdown

- Available in space-saving micro SMD package

### **Applications**

- Smart Phones

- Portable Gaming

- Tablets

69dB (typ)

- Multimedia Devices

- MP3 Player Accessories

Boomer® is a registered trademark of National Semiconductor Corporation.

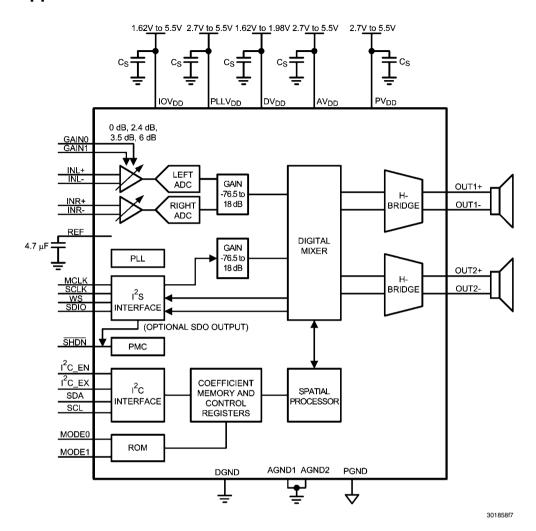

# **Typical Application**

FIGURE 1. Typical Audio Amplifier Application Circuit

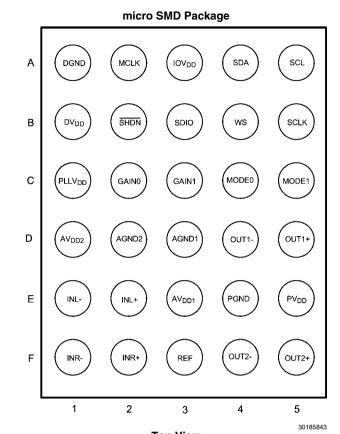

## **Connection Diagrams**

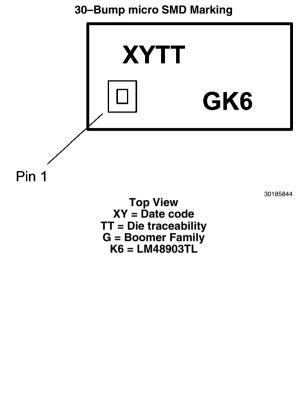

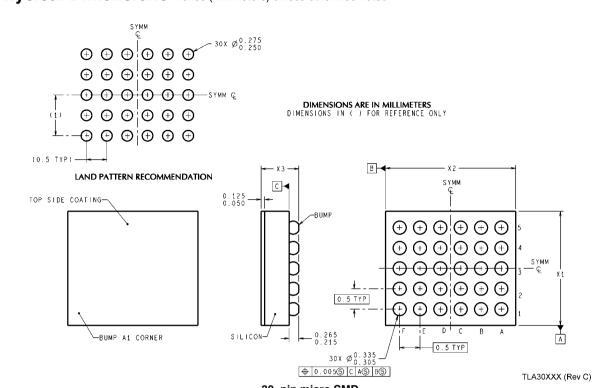

Top View Order NumberLM48903TL See NS Package Number TLA30HHA

## **Ordering Information**

#### **Ordering Information Table**

| Order Number | Package   | Package<br>Drawing<br>Number | Transport Media                        | MSL<br>Level | Green Status    |

|--------------|-----------|------------------------------|----------------------------------------|--------------|-----------------|

| LM48903TL    | micro SMD | TLA30HHA                     | 250 and 2500 units<br>on tape and reel | 1            | RoHS & no Sb/Br |

#### **TABLE 1. Bump Description**

| BUMP | NAME               | DESCRIPTION                                                        |

|------|--------------------|--------------------------------------------------------------------|

| A1   | DGND               | Digital Ground                                                     |

| A2   | MCLK               | Master Clock                                                       |

| A3   | IOV <sub>DD</sub>  | Digital Interface Power Supply                                     |

| A4   | SDA                | I <sup>2</sup> C Serial Data Input                                 |

| A5   | SCL                | I <sup>2</sup> C Clock Input                                       |

| B1   | $DV_DD$            | Digital Power Supply                                               |

| B2   | SHDN               | Active Low Shutdown. Connect to VDD for normal operation.          |

| B3   | SDIO               | I <sup>2</sup> S Serial Data Input/Output                          |

| B4   | WS                 | I <sup>2</sup> S Word Select Input                                 |

| B5   | SCLK               | Serial Clock Input                                                 |

| C1   | PLLV <sub>DD</sub> | PLL Power Supply                                                   |

| C2   | GAIN0              | Gain Setting Input 0                                               |

| C3   | GAIN1              | Gain Setting Input 1                                               |

| C4   | MODE0              | Spatial Mode Control Input 0                                       |

| C5   | MODE1              | Spatial Mode Control Input 1                                       |

| D1   | AV <sub>DD2</sub>  | ADC Analog Power Supply                                            |

| D2   | AGND2              | ADC Analog Ground                                                  |

| D3   | AGND1              | Modulator Analog Ground                                            |

| D4   | OUT1-              | Channel 1 Inverting Output. Connect to OUT2- in Parallel Mode      |

| D5   | OUT1+              | Channel 1 Non-Inverting Output. Connect to OUT2+ in Parallel Mode  |

| E1   | INL-               | Left Channel Inverting Analog Input                                |

| E2   | INL+               | Left Channel Non-Inverting Analog Input                            |

| E3   | AV <sub>DD1</sub>  | Modulator Analog Power Supply                                      |

| E4   | PGND               | Power Ground                                                       |

| E5   | PV <sub>DD</sub>   | Class D Power Supply                                               |

| F1   | INR-               | Right Channel Inverting Analog Input                               |

| F2   | INR+               | Right Channel Non-Inverting Analog Input                           |

| F3   | REF                | ADC Reference Bypass                                               |

| F4   | OUT2-              | Channel 2 Inverting Output. Connect to OUT1- in Parallel Mode.     |

| F5   | OUT2+              | Channel 2 Non-Inverting Output. Connect to OUT1+ in Parallel Mode. |

### Absolute Maximum Ratings (Note 1, Note

*2*)

If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

Supply Voltage  $AV_{DD}$ ,  $PV_{DD}$ ,  $PLV_{DD}$ ,  $IOV_{DD}$  (*Note 1*) 6V Supply Voltage, DV<sub>DD</sub> (*Note 1*) 2.2V Storage Temperature -65°C to + 150°C Input Voltage -0.3V to  $V_{DD} + 0.3V$ Power Dissipation (Note 3) Internally limited ESD Susceptibility (Note 4) 2000V ESD Susceptibility (Note 5) 150V Junction Temperature 150°C

Thermal Resistance θ<sub>1A</sub> (TLA30)

(TLA30) 54°C/W

### **Operating Ratings**

Temperature Range

$$\begin{split} & T_{\text{MIN}} \leq T_{\text{A}} \leq T_{\text{MAX}} & -40^{\circ}\text{C} \leq T_{\text{A}} \leq +85^{\circ}\text{C} \\ & \text{Supply Voltage} \\ & \text{AV}_{\text{DD}} & 2.7\text{V} \leq \text{AV}_{\text{DD}} \leq 5.5\text{V} \\ & \text{PV}_{\text{DD}} & 2.7\text{V} \leq \text{PV}_{\text{DD}} \leq 5.5\text{V} \\ & \text{PLLV}_{\text{DD}} & 2.7\text{V} \leq \text{PLLV}_{\text{DD}} \leq 5.5\text{V} \\ & \text{IOV}_{\text{DD}} & 1.62\text{V} \leq \text{IOV}_{\text{DD}} \leq 5.5\text{V} \\ & \text{DV}_{\text{DD}} & 1.62\text{V} \leq \text{DV}_{\text{DD}} \leq 1.98\text{V} \end{split}$$

# Electrical Characteristics $PV_{DD} = AV_{DD}$ , $IOV_{DD} = PLLV_{DD} = 3.6V$ , $DV_{DD} = 1.8$

(Note 2, Note 8)

The following specifications apply for  $A_V = 0$ dB,  $C_{REF} = 4.7 \mu F$ ,  $R_L = 8 \Omega$ , f = 1kHz, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

|                      |                                                          |                                  |                 | LM48903         |                 | Units    |  |

|----------------------|----------------------------------------------------------|----------------------------------|-----------------|-----------------|-----------------|----------|--|

| Symbol               | Parameter                                                | Conditions                       | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8) | (Limits) |  |

| $AV_{DD}$            | Analog Supply Voltage Range                              |                                  | 2.7             |                 | 5.5             | V        |  |

| PV <sub>DD</sub>     | Amplifier Supply Voltage Range                           |                                  | 2.7             |                 | 5.5             | V        |  |

| PLLV <sub>DD</sub>   | PLL Supply Voltage Range                                 |                                  | 2.7             |                 | 5.5             | V        |  |

| IOV <sub>DD</sub>    | Interface Supply Voltage Range                           |                                  | 1.62            |                 | 5.5             | V        |  |

| $\overline{DV_{DD}}$ | Digital Supply Voltage Range                             |                                  | 1.62            |                 | 1.98            | V        |  |

| Al <sub>DD</sub>     | Analog Quiescent Supply Current                          |                                  |                 | 15.2            | 19              | mA       |  |

| PI <sub>DD</sub>     | Amplifier Quiescent Supply<br>Current                    | $R_L = 8\Omega$                  |                 | 2.6             |                 | mA       |  |

| PLLI <sub>DD</sub>   | PLL Quiescent Supply Current                             |                                  |                 | 1.3             |                 | mA       |  |

| DI <sub>DD</sub>     | Quiescent Digital Power Supply<br>Current                |                                  |                 | 5.4             | 5.8             | mA       |  |

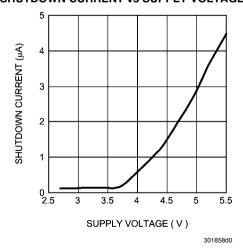

| I <sub>SD</sub>      | Shutdown Current (Analog,<br>Amplifier and PLL Supplies) | Shutdown Enabled                 |                 | 0.4             | 3.5             | μΑ       |  |

| DI <sub>STBY</sub>   | Digital Standby Current                                  |                                  |                 | 30              |                 | μΑ       |  |

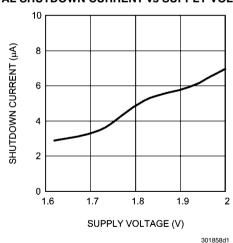

| DI <sub>SD</sub>     | Digital Shutdown Current                                 | Shutdown Enabled                 |                 | 6.6             | 10              | μA       |  |

| V <sub>OS</sub>      | Differential Output Offset Voltage                       | V <sub>IN</sub> = 0              | -7.5            | 0.8             | 7.5             | mV       |  |

| т                    | Wake up Time                                             | Power Up (Device Initialization) |                 | 150             |                 | ms       |  |

| T <sub>WU</sub>      | Wake-up Time                                             | From Shutdown                    |                 | 28.5            |                 | ms       |  |

| f <sub>SW</sub>      | Switching Frequency                                      | $f_S = 48kHz$                    |                 | 384             |                 | kHz      |  |

|                |                                      |                                                                            |                          | LM48903                  |                          | Units    |  |  |

|----------------|--------------------------------------|----------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|----------|--|--|

| Symbol         | Parameter                            | Conditions                                                                 | Min<br>( <i>Note 8</i> ) | Typ<br>( <i>Note 7</i> ) | Max<br>( <i>Note 8</i> ) | (Limits) |  |  |

|                |                                      | $R_L = 4\Omega$ , THD+N = 10%                                              |                          |                          |                          |          |  |  |

|                |                                      | f = 1kHz, 22kHz BW                                                         |                          | _                        |                          |          |  |  |

|                |                                      | $V_{DD} = 5V$                                                              |                          | 2.8                      |                          | W        |  |  |

|                |                                      | V <sub>DD</sub> = 3.6V                                                     |                          | 1.4                      |                          | W        |  |  |

|                |                                      | $R_L = 4\Omega$ , THD+N = 1%                                               |                          |                          |                          |          |  |  |

|                |                                      | f = 1kHz, 22kHz BW                                                         |                          |                          | î .                      | 1        |  |  |

|                |                                      | $V_{DD} = 5V$                                                              |                          | 2.2                      |                          | W        |  |  |

| $P_{O}$        | Output Power/Channel                 | V <sub>DD</sub> = 3.6V                                                     |                          | 1.2                      |                          | W        |  |  |

| . 0            | Catpat i ewel/ename                  | $R_L = 8\Omega$ , THD+N = 10%                                              |                          |                          |                          |          |  |  |

|                |                                      | f = 1kHz, 22kHz BW                                                         |                          |                          | Γ                        |          |  |  |

|                |                                      | V <sub>DD</sub> = 5V                                                       |                          | 1.7                      |                          | W        |  |  |

|                |                                      | V <sub>DD</sub> = 3.6V                                                     |                          | 860                      |                          | mW       |  |  |

|                |                                      | $R_L = 8\Omega$ , THD+N = 1%                                               |                          |                          |                          |          |  |  |

|                |                                      | f = 1kHz, 22kHz BW                                                         |                          | _                        | 1                        |          |  |  |

|                |                                      | $V_{DD} = 5V$                                                              |                          | 1.3                      |                          | W        |  |  |

|                |                                      | V <sub>DD</sub> = 3.6V                                                     | 500                      | 650                      |                          | mW       |  |  |

|                |                                      | $R_L = 4\Omega$ , THD+N = 10%, f = 1kHz                                    | , 22kHz BW               |                          |                          |          |  |  |

| P <sub>O</sub> |                                      | $V_{DD} = 5V$                                                              |                          | 3.3                      |                          | W        |  |  |

|                | Output Power (Parallel Mode)         | $V_{DD} = 3.6V$                                                            |                          | 1.7                      |                          | W        |  |  |

|                | Cutput i ower (i araner Mode)        | $R_L = 4\Omega$ , THD+N = 1%, f = 1kHz,                                    | 22kHz BW                 |                          |                          |          |  |  |

|                |                                      | $V_{DD} = 5V$                                                              |                          | 2.5                      |                          | W        |  |  |

|                |                                      | V <sub>DD</sub> = 3.6V                                                     |                          | 1.2                      |                          | w        |  |  |

| THD+N          | Total Harmonic Distortion +<br>Noise | $P_{O} = 350 \text{mW}, f = 1 \text{kHz}, R_{L} = 8\Omega$                 |                          | 0.08                     |                          | %        |  |  |

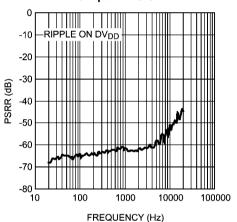

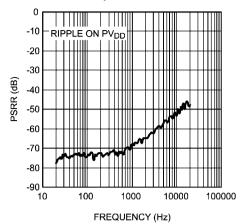

|                |                                      | $V_{RIPPLE} = 200 \text{mV}_{P-P}$ sine, Inputs AC GND, $C_{IN} = 1 \mu F$ |                          |                          |                          |          |  |  |

|                |                                      | f <sub>BIPPLE</sub> = 217Hz, Applied to PV <sub>DD</sub>                   |                          | 69                       |                          | dB       |  |  |

|                |                                      | f <sub>BIPPLE</sub> = 217Hz, Applied to DV <sub>DD</sub>                   |                          | 64                       |                          | dB       |  |  |

| PSRR           | Power Supply Rejection Ratio         | $f_{RIPPLE} = 1kHz$ , Applied to $PV_{DD}$                                 | 60                       | 68                       |                          | dB       |  |  |

|                | (ADC Path)                           | $f_{RIPPLE} = 1kHz$ , Applied to $DV_{DD}$                                 | 56                       | 62                       |                          | dB       |  |  |

|                |                                      | f <sub>RIPPLE</sub> = 10kHz, Applied to PV <sub>DD</sub>                   |                          | 62                       |                          | dB       |  |  |

|                |                                      | $f_{RIPPLE} = 10kHz$ , Applied to $DV_{DD}$                                |                          | 52                       |                          | dB       |  |  |

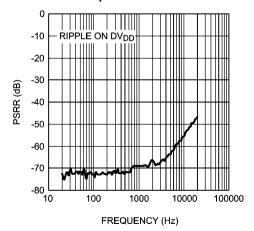

|                |                                      | V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub> sine, Inputs –                  | ∞dBFS                    |                          |                          | l .      |  |  |

|                |                                      | $f_{RIPPLE} = 217Hz$ , Applied to $PV_{DD}$                                |                          | 68                       |                          | dB       |  |  |

|                |                                      | $f_{RIPPLE} = 217Hz$ , Applied to $DV_{DD}$                                |                          | 72                       |                          | dB       |  |  |

| PSRR           | Power Supply Rejection Ratio         | $f_{RIPPLE} = 1kHz$ , Applied to $PV_{DD}$                                 | 60                       | 67                       |                          | dB       |  |  |

|                | (I2S Path)                           | $f_{RIPPLE} = 1kHz$ , Applied to $DV_{DD}$                                 | 55                       | 69                       |                          | dB       |  |  |

|                |                                      | $f_{RIPPLE} = 10kHz$ , Applied to $PV_{DD}$                                |                          | 58                       |                          | dB       |  |  |

|                |                                      | $f_{RIPPLE} = 10kHz$ , Applied to $DV_{DD}$                                |                          | 56                       |                          | dB       |  |  |

|                |                                      | $V_{\text{RIPPLE}} = 1V_{\text{P-P}}, f_{\text{RIPPLE}} = 217\text{Hz},$   |                          | 30                       |                          | ub       |  |  |

| CMRR           | Common Mode Rejection Ratio          | $A_V = 0dB$                                                                |                          | 78                       |                          | dB       |  |  |

| η              | Efficiency/Channel                   | $V_{DD} = 5V, P_{O} = 1.1W$                                                |                          | 91                       |                          | %        |  |  |

| 1              |                                      | $V_{DD} = 3.6V, P_{O} = 400mW$                                             |                          | 90                       |                          | %        |  |  |

| n              | Efficiency                           | $V_{DD} = 5V, P_{O} = 1.1W$                                                |                          | 86                       |                          | %        |  |  |

| η              |                                      | $V_{DD} = 3.6V, P_{O} = 400mW$                                             |                          | 83                       |                          | %        |  |  |

| SNR            | Signal-to-NoiseRatio                 | ADC Input, P <sub>O</sub> = 1W                                             |                          | 89                       |                          | dB       |  |  |

| J. 11 1        | Orginal to 1401501 tatio             | I2S Input, P <sub>O</sub> = 1W                                             |                          | 90                       |                          | dB       |  |  |

|                                 |           |                                                    |                 | Huita           |                 |                   |

|---------------------------------|-----------|----------------------------------------------------|-----------------|-----------------|-----------------|-------------------|

| Symbol                          | Parameter | Conditions                                         | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8) | Units<br>(Limits) |

| $\epsilon_{ m OS}$ Output Noise |           | Inputs AC GND, A-weighted,<br>A <sub>V</sub> = 0dB |                 | 130             |                 | μV                |

|                                 |           | I2S Input                                          |                 | 72              |                 | μV                |

| X <sub>TALK</sub>               | Crosstalk |                                                    |                 | 72              |                 | dB                |

### I<sup>2</sup>C Interface Characteristics (Note 1, Note 2)

The following specifications apply for  $R_{PU}$  = 1k $\Omega$  to IOV<sub>DD</sub>, unless otherwise specified. Limits apply for  $T_A$  = 25°C.

|                 |                                                |                               |                       | LM48903         |                 |       |

|-----------------|------------------------------------------------|-------------------------------|-----------------------|-----------------|-----------------|-------|

| Symbol          | Parameter                                      | Conditions                    | Min<br>(Note 7)       | Typ<br>(Note 6) | Max<br>(Note 7) | Units |

| V <sub>IH</sub> | Logic Input High Threshold                     | SDA, SCL                      | 0.7*IOV <sub>DD</sub> |                 |                 | V     |

| V <sub>IL</sub> | Logic Input Low Threshold                      | SDA, SCL                      |                       |                 | 0.3             | mV    |

| V <sub>OL</sub> | Logic Output Low Threshold                     | SDA, I <sub>SDA</sub> = 3.6mA |                       |                 | 0.35            | V     |

| I <sub>OH</sub> | Logic Output High Current                      | SDA, SCL                      |                       |                 | 2               | μΑ    |

|                 | SCL Frequency                                  |                               |                       |                 | 400             | kHz   |

| 1               | Hold Time (repeated START Condition)           |                               | 0.6                   |                 |                 | μs    |

| 2               | Clock Low Time                                 |                               | 1.3                   |                 |                 | μs    |

| 3               | Clock High Time                                |                               | 600                   |                 |                 | ns    |

| 4               | Setup Time for Repeated START condition        |                               | 600                   |                 |                 | ns    |

| 5               | Data Hold Time                                 | Output                        | 300                   |                 | 900             | ns    |

| 6               | Data Setup Time                                |                               | 100                   |                 |                 | ns    |

| 7               | SDA Rise Time                                  |                               |                       |                 | 300             | ns    |

| 8               | SDA Fall Time                                  |                               |                       |                 | 300             | ns    |

| 9               | Setup Time for STOP Condition                  |                               | 600                   |                 |                 | ns    |

| 10              | Bus Free Time Between STOP and START Condition |                               | 1.3                   |                 |                 | μs    |

### I2S Timing Characteristics (Note 2, Note 8)

The following specifications apply for  $DV_{DD} = 1.8V$ , unless otherwise specified. Limits apply for  $T_A = 25$ °C.

|                     |                                              |            |                 | LM48903                  |                 | l leite           |

|---------------------|----------------------------------------------|------------|-----------------|--------------------------|-----------------|-------------------|

| Symbol              | Parameter                                    | Conditions | Min<br>(Note 7) | Typ<br>( <i>Note 6</i> ) | Max<br>(Note 7) | Units<br>(Limits) |

| t <sub>MCLKL</sub>  | MCLK Pulse Width Low                         |            | 16              |                          |                 | ns                |

| t <sub>MCLKH</sub>  | MCLK Pulse Width High                        |            | 16              |                          |                 | ns                |

| t <sub>MCLKY</sub>  | MCLK Period                                  |            | 27              |                          |                 | ns                |

| t <sub>BCLKR</sub>  | SCLK rise time                               |            |                 |                          | 3               | ns                |

| t <sub>BCLKCF</sub> | SCLK fall time                               |            |                 |                          | 3               | ns                |

| t <sub>BCLKDS</sub> | SCLK Duty Cycle                              |            |                 | 50                       |                 | %                 |

| T <sub>DL</sub>     | LRC Propagation Delay from SCLK falling edge |            |                 |                          | 10              | ns                |

| T <sub>DST</sub>    | DATA Setup Time to SCLK<br>Rising Edge       |            | 10              |                          |                 | ns                |

| T <sub>DHT</sub>    | DATA Hold Time from SCLK<br>Rising Edge      |            | 10              |                          |                 | ns                |

Note 1: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

Note 2: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the given in *Absolute Maximum Ratings*, whichever is lower.

Note 4: Human body model, applicable std. JESD22-A114C.

Note 5: Machine model, applicable std. JESD22-A115-A.

Note 6: Typical values represent most likely parametric norms at  $T_A = +25^{\circ}C$ , and at the *Recommended Operation Conditions* at the time of product characterization and are not guaranteed.

Note 7: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

**Note 8:**  $R_L$  is a resistive load in series with two inductors to simulate an actual speaker load. For  $R_L$  = 8 $\Omega$ , the load is 15 $\mu$ H+8 $\Omega$ +15 $\mu$ H. For  $R_L$  = 4 $\Omega$ , the load is 15 $\mu$ H+4 $\Omega$ +15 $\mu$ H.

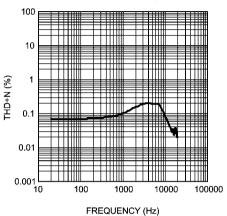

### **Typical Performance Characteristics**

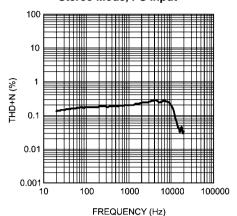

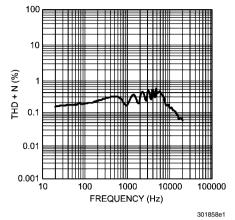

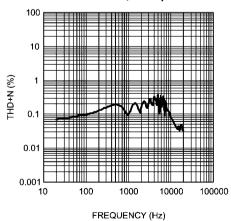

THD+N vs FREQUENCY  $\begin{aligned} \text{V}_{\text{DD}} &= 3.6\text{V}, \, \text{P}_{\text{OUT}} = 400\text{mW}, \, \text{R}_{\text{L}} = 8\Omega \\ \text{Stereo Mode, I}^2\text{S Input} \end{aligned}$

301858e4

THD+N vs FREQUENCY  $\label{eq:VDD} V_{DD} = 3.6V,\, P_{OUT} = 250mW,\, R_L = 4\Omega$

NCA

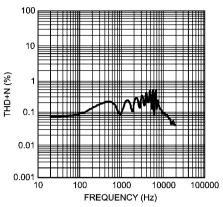

THD+N vs FREQUENCY  $\begin{aligned} \text{V}_{\text{DD}} &= 5\text{V}, \, \text{P}_{\text{OUT}} = 1.2\text{W}, \, \text{R}_{\text{L}} = 4\Omega \\ \text{Stereo Mode, } \text{l}^2\text{S Input} \end{aligned}$

301858e7

THD+N vs FREQUENCY  $\begin{aligned} \text{V}_{\text{DD}} &= 3.6\text{V}, \, \text{P}_{\text{OUT}} = 500\text{mW}, \, \text{R}_{\text{L}} = 4\Omega \\ \text{Stereo Mode, I}^2\text{S Input} \end{aligned}$

301858e6

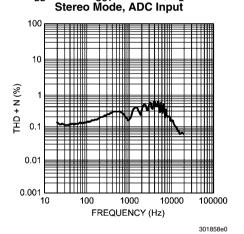

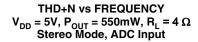

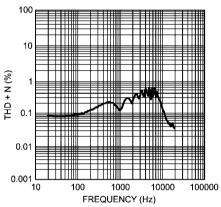

THD+N vs FREQUENCY  $V_{DD} = 3.6V, P_{OUT} = 200$ mW,  $R_{L} = 8\Omega$  Stereo Mode, ADC Input

301858d9

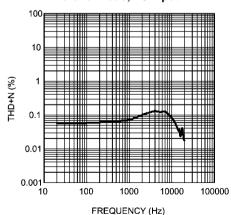

THD+N vs FREQUENCY  $\begin{aligned} \mathbf{V}_{\mathrm{DD}} &= 5\mathbf{V}, \, \mathbf{P}_{\mathrm{OUT}} = 800 \mathrm{mW}, \, \mathbf{R}_{\mathrm{L}} = 8\Omega \\ &\text{Stereo Mode, I}^2 \mathbf{S} \, \mathbf{Input} \end{aligned}$

301858e5

THD+N vs FREQUENCY  $\begin{aligned} \text{V}_{\text{DD}} &= 3.6\text{V}, \, \text{P}_{\text{OUT}} = 800\text{mW}, \, \text{R}_{\text{L}} = 4\Omega \\ \text{Parallel Mode, I}^2\text{S Input} \end{aligned}$

301858e8

# THD+N vs FREQUENCY $V_{DD}$ = 5V, $P_{OUT}$ = 800mW, $R_{L}$ = $4\Omega$ Parallel Mode, I<sup>2</sup>S Input

301858e3

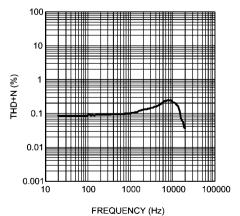

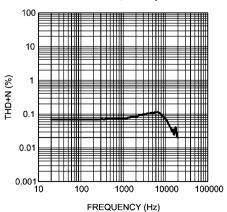

THD+N vs FREQUENCY  $V_{DD} = 5V$ ,  $P_{OUT} = 350 mW$ ,  $R_{L} = 8\Omega$  Stereo Mode, ADC Input

30185857

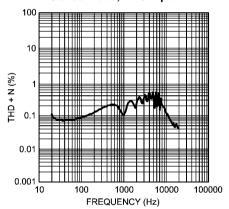

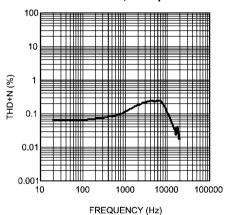

THD+N vs FREQUENCY  $\begin{aligned} \text{V}_{\text{DD}} &= 3.6\text{V}, \, \text{P}_{\text{OUT}} = 350\text{mW}, \, \text{R}_{\text{L}} = 4\Omega \\ \text{Parallel Mode, ADC Input} \end{aligned}$

301858e2

# THD+N vs FREQUENCY $V_{DD}$ = 5V, $P_{OUT}$ = 1.7W, $R_L$ = $4\Omega$ Parallel Mode, I<sup>2</sup>S Input

301858e9

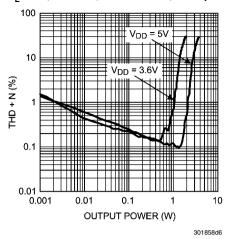

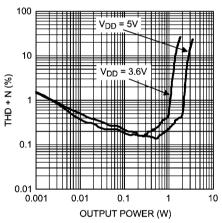

# THD+N vs OUTPUT POWER $R_1 = 4\Omega$ , f = 1kHz, Stereo Mode, I<sup>2</sup>S Input

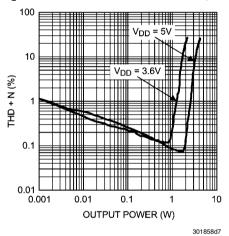

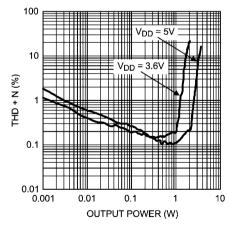

# THD+N vs OUTPUT POWER $R_L = 4\Omega, \, f = 1 \text{kHz}, \, \text{Parallel Mode, } \, l^2 \text{S Input}$

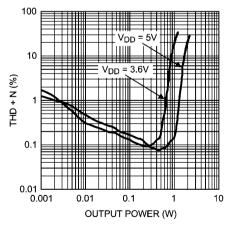

# THD+N vs OUTPUT POWER $R_L = 8\Omega, \, f = 1 \text{kHz}, \, \text{Stereo Mode, ADC Input}$

301858d2

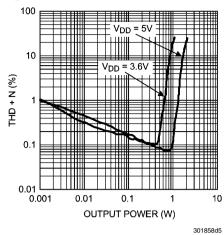

# THD+N vs OUTPUT POWER $R_L = 8\Omega, \, f = 1 \text{kHz}, \, \text{Stereo Mode, } \, l^2 \text{S Input}$

# THD+N vs OUTPUT POWER $R_L = 4\Omega, \, f = 1 \text{kHz}, \, \text{Stereo Mode, ADC Input}$

# THD+N vs OUTPUT POWER $R_{L} = 4\Omega, \, f = 1 \text{kHz}, \, \text{Parallel Mode, ADC Input}$

301858d4

301858d3

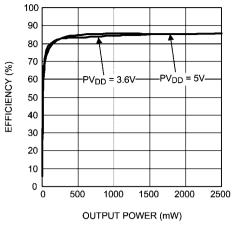

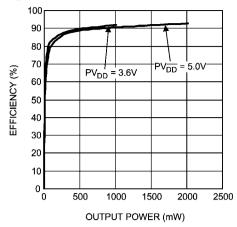

# EFFICIENCY vs OUTPUT POWER $R_1 = 4\Omega$ , f = 1kHz, Stereo Mode, ADC Input

301858f1

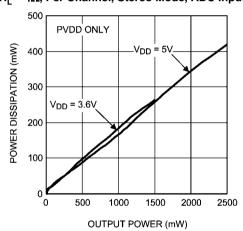

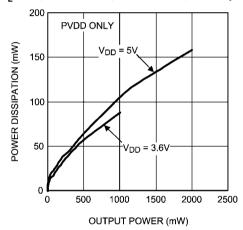

# POWER DISSIPATION vs OUTPUT POWER $R_1 = 4\Omega$ , Per Channel, Stereo Mode, ADC Input

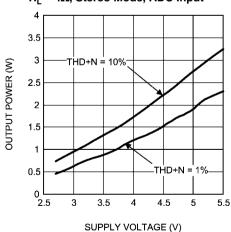

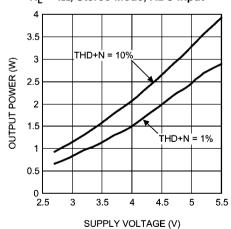

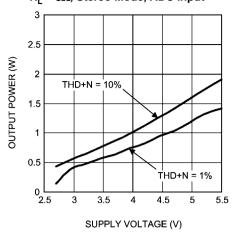

# OUTPUT POWER vs SUPPLY VOLTAGE $R_L = 4\Omega$ , Stereo Mode, ADC Input

301858f4

301858f3

# EFFICIENCY vs OUTPUT POWER $R_1 = 8\Omega$ , f = 1kHz, Stereo Mode, ADC Input

301858f0

# POWER DISSIPATION vs OUTPUT POWER $R_1 = 8\Omega$ , Per Channel, Stereo Mode, ADC Input

301858f2

# OUTPUT POWER vs SUPPLY VOLTAGE $R_L = 4\Omega$ , Stereo Mode, ADC Input

301858f5

# OUTPUT POWER vs SUPPLY VOLTAGE $R_1 = 8\Omega$ , Stereo Mode, ADC Input

301858f6

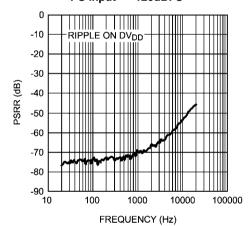

# $\begin{array}{c} {\rm PSRR~vs~FREQUENCY} \\ {\rm DV_{DD}=1.8V,~V_{RIPPLE}=200mV_{p,p},~R_L=8\Omega,} \\ {\rm ADC~Input=AC~GND} \end{array}$

301858c2

$\begin{array}{c} {\rm PSRR~vs~FREQUENCY} \\ {\rm DV_{DD}=1.8V,~V_{RIPPLE}=200mV_{P,P},~R_L=8\Omega,} \\ {\rm I^2S~input=-120dBFS} \end{array}$

301858c4

$\begin{array}{c} {\rm PSRR~vs~FREQUENCY} \\ {\rm PV_{DD}=5V,~V_{RIPPLE}=200mV_{P.P},~R_L=8\Omega,} \\ {\rm ADC~Input=AC~GND} \end{array}$

301858c1

$\begin{array}{c} \text{PSRR vs FREQUENCY} \\ \text{PV}_{\text{DD}} = 5\text{V}, \, \text{V}_{\text{RIPPLE}} = 200\text{mV}_{\text{P.p.}}, \, \text{R}_{\text{L}} = 8\Omega, \\ \text{I}^2\text{S input} = -120\text{dBFS} \end{array}$

301858c3

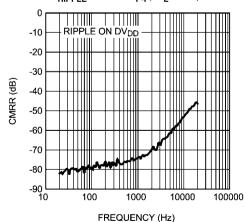

# CMRR vs FREQUENCY $V_{RIPPLE} = 200 \text{mV}_{P-P}, R_L = 8\Omega,$

301858c5

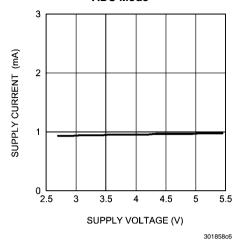

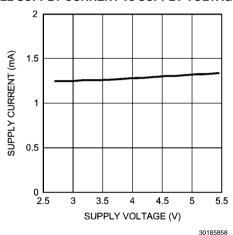

# SUPPLY CURRENT vs SUPPLY VOLTAGE ADC Mode

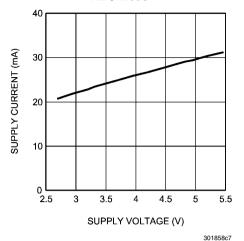

# ANALOG SUPPLY CURRENT vs SUPPLY VOLTAGE ADC Mode

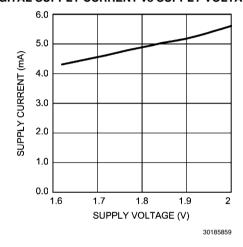

#### PLL SUPPLY CURRENT vs SUPPLY VOLTAGE

#### **DIGITAL SUPPLY CURRENT vs SUPPLY VOLTAGE**

#### SHUTDOWN CURRENT vs SUPPLY VOLTAGE

#### **DIGITAL SHUTDOWN CURRENT vs SUPPLY VOLTAGE**

### **Application Information**

#### **I2C COMPATIBLE INTERFACE**

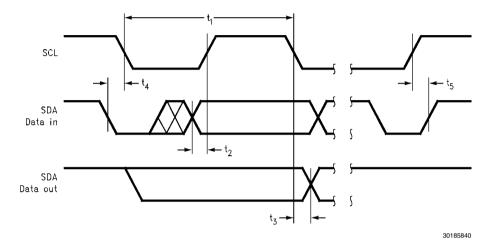

The LM48903 is controlled through an I<sup>2</sup>C compatible serial interface that consists of a serial data line (SDA) and a serial clock (SCL). The clock and data lines are bi-directional (open drain). The LM48903 communicates at clock rates up to 400kHz. *Figure 2* shows the I<sup>2</sup>C interface timing diagram. Data on the SDA line must be stable during the HIGH period of SCL. The LM48903 is a transmit/receive device, and can act

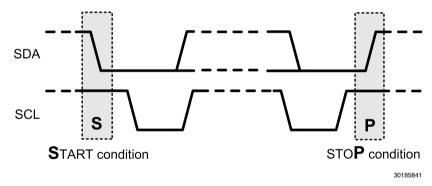

as the I<sup>2</sup>C master, generating the SCL signal. Each transmission sequence is framed by a START condition and a STOP condition *Figure 3*.

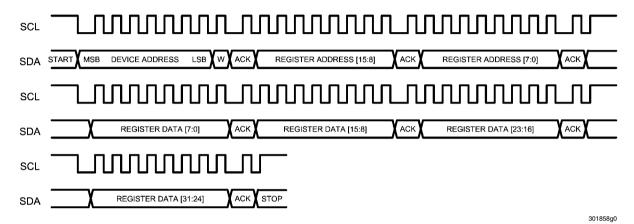

Due to the number of data registers, the LM48903 employs a page mode scheme. Each data write consists of 7, 8 bit data bytes, device address (1 byte), 16 bit register address (2 bytes), and 32 bit register data (4 bytes). Each byte is followed by an acknowledge pulse *Figure 4*. Single byte read and write commands are ignored. The LM48903 device address is 0110000X.

FIGURE 2. I2C Timing Diagram

FIGURE 3. Start and Stop Diagram

#### WRITE SEQUENCE

The example write sequence is shown in *Figure 4*. The START signal, the transition of SDA from HIGH to LOW while SDA is HIGH, is generated, altering all devices on the bus that a device address is being written to the bus.

The 7-bit device address is written to the bus, most significant bit (MSB) first, followed by the  $R/\overline{W}$  bit ( $R/\overline{W}=0$  indicating the master is writing to the LM48903). The data is latched in on the rising edge of the clock. Each address bit must be stable while SDA is HIGH. After the R/W bit is transmitted, the master device releases SDA, during which time, an acknowledge clock pulse is generated by the slave device. If the LM48903 receives the correct address, the device pulls the SDA line low, generating and acknowledge bit (ACK).

Once the master device registers the ACK bit, the first 8-bit register address word is sent, MSB first [15:8]. Each data bit should be stable while SCL is HIGH. After the first 8-bit register address is sent, the LM48903 sends another ACK bit. Upon receipt of acknowledge, the second 8-bit register address word is sent [7:0], followed by another ACK bit. The register data is sent, 8-bits at a time, MSB first in the following order [7:0], [15:8], [23:16], [31.24]. Each 8-bit word is followed by an ACK, upon receipt of which the successive 8-bit word is sent. Following the acknowledgement of the last register data word [31:24], the master issues a STOP bit, allowing SDA to go high while SDA is high.

FIGURE 4. Example I<sup>2</sup>C Write Sequence

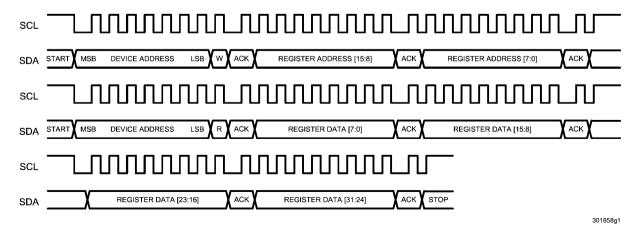

#### **READ SEQUENCE**

The example read sequence is shown in *Figure 5*. The START signal, the transition of SDA from HIGH to LOW while SDA is HIGH, is generated, altering all devices on the bus that a device address is being written to the bus.

The 7-bit device address is written to the bus, followed by the  $R/\overline{W} = 0$ . After the  $R/\overline{W}$  bit is transmitted, the master device releases SDA, during which time, an acknowledge clock pulse is generated by the slave device. If the LM48903 receives the correct address, the device pulls the SDA line low, generating and acknowledge bit (ACK). Once the master device registers the ACK bit, the first 8-bit register address word is sent, MSB first [15:8], followed by and ACK from the

LM48903. Upon receipt of the acknowledge, the second 8-bit register address word is sent [7:0], followed by another ACK bit. Following the acknowledgment of the last register address, the master initiates a REPEATED START, followed by the 7-bit device address, followed by  $R/\overline{W}=1$  ( $R/\overline{W}=1$  indicating the master wants to read data from the LM48903). The LM48903 sends an ACK, followed by the selected register data. The register data is sent, 8-bits at a time, MSB first in the following order [7:0], [15:8], [23:16], [31:24]. Each 8-bit word is followed by an ACK, upon receipt of which the successive 8-bit word is sent. Following the acknowledgement of the last register data word [7:0], the master issues a STOP bit, allowing SDA to go high while SDA is high.

FIGURE 5. Example I2C Read Sequence

#### **12S DATA FORMAT**

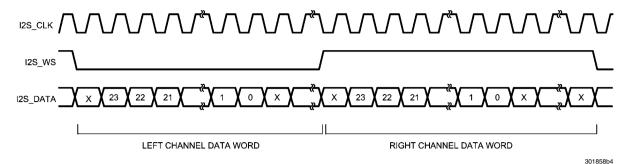

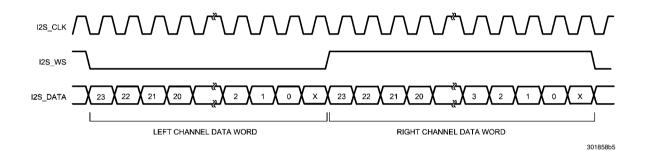

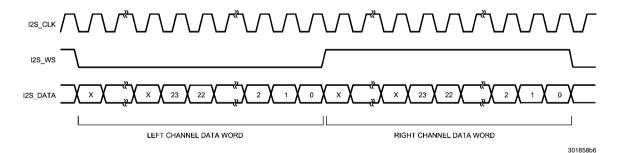

The LM48903 supports three I2S formats: Normal Mode *Figure 6*, Left Justified Mode *Figure 7*, and Right Justified Mode *Figure 8*. In Normal Mode, the audio data is transmitted MSB first, with the unused bits following the LSB. In Left Justified

Mode, the audio data format is similar to the Normal Mode, without the delay between the LSB and the change in I<sup>2</sup>S\_WS. In Right Justified Mode, the audio data MSB is transmitted after a delay of a preset number of bits.

FIGURE 6. I2S Normal Input Format

FIGURE 7. I2S Left Justified Input Format

FIGURE 8. I2S Right Justified Input Format

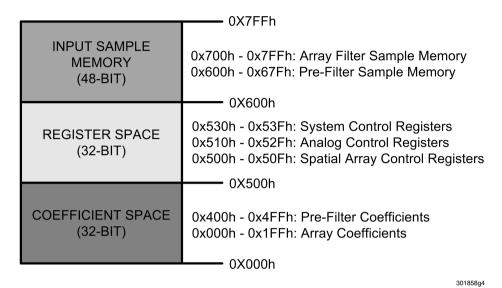

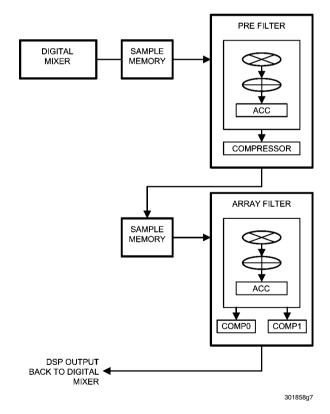

#### **MEMORY ORGANIZATION**

The LM48903 memory is organized into three main regions: a 32-bit wide Coefficient Space that holds the spatial coefficients, a 32-bit wide Register Space that holds the device

configuration settings, and a 48-bit wide Audio Sample Space that holds the current audio data sampled from either the ADCs or the I2S interface, organized as shown in *Figure 9*.

FIGURE 9. LM48903 Memory Organization

**COEFFICIENT MEMORY**

The device must be in Debug mode in order to write to the Coefficient memory. Set Bit 7 (DBG\_ENABLE) in Filter Debug

Register 1 (0x504h) = 1 to enable Debug mode. The Coefficient Memory Space is organized as follows.

**TABLE 2. Coefficient Memory Space**

| REGISTER ADDRESS         | REG                          | GISTER CONTENTS                  |

|--------------------------|------------------------------|----------------------------------|

|                          | (31:16)                      | (15:0)                           |

| 0x000h - 0x0FFh          | 256x16 bit Array Taps        | 256x16 bit Array Taps            |

| OXOOOII - OXOFFII        | (Right Input to OUT2)        | (Left Input to OUT2)             |

| 0x100h - 0x1FFh          | 256x16 bit Array Taps        | 256x16 bit Array Taps            |

| 0.2.10011 - 0.2.17-11    | (Right Input to OUT1)        | (Left Input to OUT1)             |

| 0x400h - 0x47Eh (EVEN)   | C2 128x16 bit Prefilter Taps | C0 128x16 bit Prefilter FIR Taps |

| 0x400ii - 0x47Eii (EVEN) | (Right to Right)             | (Left to Left)                   |

| 0x441h - 0x47Fh (ODD)    | C3 128x16 bit Prefilter Taps | C1 128x16 bit Prefilter FIR Taps |

| 0x44111 - 0x47111 (ODD)  | (Right to Left)              | (Left to Right)                  |

#### **CONTROL REGISTERS**

#### **TABLE 3. Register Map**

| Register<br>Name | Register<br>Address | Default<br>Value | 7                | 6                 | 5                | 4                 | 3                 | 2               | 1       | 0    |

|------------------|---------------------|------------------|------------------|-------------------|------------------|-------------------|-------------------|-----------------|---------|------|

|                  | 0x500h<br>[7:0]     | 0xFFh            |                  |                   |                  | ARRAY             | _TAP              |                 |         |      |

| FILTER           | 0x500h<br>[15:8]    | 0x7Fh            | UNUSED           |                   |                  |                   | PRE_TAP           |                 |         |      |

| CONTRO<br>L      | 0x500h<br>[23:16]   | 0xE4h            |                  | UNUSED            |                  |                   | CH2_              | SEL             | CH1     | _SEL |

|                  | 0x500h<br>[31:24]   | 0xC1h            | ARRAY_<br>ENABLE | PRE_<br>ENABLE    | ARRAY_<br>BYPASS | PRE_<br>BYPASS    |                   | UNU             | SED     |      |

|                  | 0x501h<br>[7:0]     | 0x98h            |                  | G1_GAIN           |                  |                   | (                 | COMP_TH         |         |      |

| FILTER           | 0x501h<br>[15:8]    | 0x11h            | UNUSED           |                   | POST_GAIN        |                   | UNUSED            | С               | OMP_RAT | Ю    |

| COMP1            | 0x501h<br>[23:16]   | 0x00h            |                  | ARRAY_COMP_SELECT |                  |                   |                   |                 |         |      |

|                  | 0x501h<br>[31:24]   | 0x00h            |                  |                   |                  | UNUS              | SED               |                 |         |      |

|                  | 0x502h<br>[7:0]     | 0XB8h            |                  | G1_GAIN           |                  |                   | (                 | COMP_TH         |         |      |

| FILTER<br>COMP2  | 0x502h<br>[15:8]    | 0x11h            | UNUSED           | INUSED POST_GAIN  |                  |                   | UNUSED            | USED COMP_RATIO |         |      |

|                  | 0x502h<br>[23:16]   | 0XB8h            | G1_GAIN          |                   |                  |                   | COMP_TH           |                 |         |      |

|                  | 0x502h<br>[31:24]   | 0x11h            | UNUSED           | USED POST_GAIN    |                  |                   | UNUSED COMP_RATIO |                 |         |      |

|                  | 0x503h<br>[7:0]     | 0x00h            |                  | DBG_DATA [7:0]    |                  |                   |                   |                 |         |      |

| FILTER           | 0x503h<br>[15:8]    | 0x00h            |                  | DBG_DATA [15:8]   |                  |                   |                   |                 |         |      |

| DEBUG0           | 0x503h<br>[23:16]   | 0x00h            |                  |                   |                  | DBG_DAT           | A [23:16]         |                 |         |      |

|                  | 0x503h<br>[31:24]   | 0x00h            |                  |                   | Τ                | UNUS              | SED               |                 |         |      |

|                  | 0x504h<br>[7:0]     | 0x00h            | DBG_<br>ENABLE   | STEP_<br>ENABLE   | UNUSED           | FILTER_<br>SELECT |                   | ACC_/           | ADDR    |      |

| FILTER           | 0x504h<br>[15:8]    | 0x00h            |                  |                   |                  | UNUS              | SED               |                 |         |      |

| DEBUG1           | 0x504h<br>[23:16]   | 0x00h            |                  |                   |                  | UNUS              | SED               |                 |         |      |

|                  | 0x504h<br>[31:24]   | 0x00h            |                  |                   |                  | UNUS              | SED               |                 |         |      |

|                  | 0x505h<br>[7:0]     | 0x00h            |                  | PCOUNT            | Γ1_MODE          |                   |                   | PCH_            | SEL     |      |

| FILTER           | 0x505h<br>[15:8]    | 0x80h            | PCLEAR           |                   | UNUSED           |                   |                   | PCOUNT          | 2_MODE  |      |

| STATS            | 0x505h<br>[23:16]   | 0x00h            |                  | ACOUNT            | Γ1_MODE          |                   | ACH_SEL           |                 |         |      |

|                  | 0x505h<br>[31:24]   | 0x80h            | ACLEAR           |                   | UNUSED           |                   |                   | ACOUNT          | 2_MODE  |      |

| Register<br>Name                   | Register<br>Address | Default<br>Value | 7 | 6                | 5 | 4        | 3         | 2 | 1 | 0 |  |  |

|------------------------------------|---------------------|------------------|---|------------------|---|----------|-----------|---|---|---|--|--|

|                                    | 0x506h<br>[7:0]     | 0x00h            |   |                  | • | DBG_DA   | ΓA [7:0]  |   |   |   |  |  |

| FILTER                             | 0x506h<br>[15:8]    | 0x00h            |   | DBG_DATA [15:8]  |   |          |           |   |   |   |  |  |

| DEBUG1                             | 0x506h<br>[23:16]   | 0x00h            |   |                  |   | DBG_DATA | A [23:16] |   |   |   |  |  |

|                                    | 0x506h<br>[31:24]   | 0x00h            |   | DBG_DATA [31:24] |   |          |           |   |   |   |  |  |

|                                    | 0x509h<br>[7:0]     | 0xXXh            |   | DBG_ACCL [7:0]   |   |          |           |   |   |   |  |  |

| ACCUML<br>DEBUG<br>(READ-<br>ONLY) | 0x509h<br>[15:8]    | 0xXXh            |   |                  |   | DBG_ACC  | L [15:8]  |   |   |   |  |  |

|                                    | 0x509h<br>[23:16]   | 0xXXh            |   |                  |   | DBG_ACC  | L [23:16] |   |   |   |  |  |

| ,                                  | 0x509h<br>[31:24]   | 0xXXh            |   | DBG_ACCL [31:24] |   |          |           |   |   |   |  |  |

|                                    | 0x50Ah<br>[7:0]     | 0xXXh            |   |                  |   | DBG_ACC  | [39:32]   |   |   |   |  |  |

| ACCUMH<br>DEBUG<br>(READ-<br>ONLY) | 0x50Ah<br>[15:8]    | 0xXXh            |   |                  |   | DBG_ACC  | [47:40]   |   |   |   |  |  |

|                                    | 0x50Ah<br>[23:16]   | 0xXXh            |   | UNUSED           |   |          |           |   |   |   |  |  |

|                                    | 0x50Ah<br>[31:24]   | 0xXXh            |   | UNUSED           |   |          |           |   |   |   |  |  |

|                                    | 0x50Bh<br>[7:0]     | 0xXXh            |   |                  |   | DBG_SA   | T [7:0]   |   |   |   |  |  |

| DBG<br>SAT                         | 0x50Bh<br>[15:8]    | 0xXXh            |   |                  |   | DBG_SA   | Γ [15:8]  |   |   |   |  |  |

| (READ-<br>ONLY)                    | 0x50Bh<br>[23:16]   | 0xXXh            |   |                  |   | DBG_SAT  | [23:16]   |   |   |   |  |  |

|                                    | 0x50Bh<br>[31:24]   | 0xXXh            |   |                  |   | UNUS     | SED       |   |   |   |  |  |

|                                    | 0x50Ch<br>[7:0]     | 0xXXh            |   |                  |   | COUNT    | [7:0]     |   |   |   |  |  |

| STAT<br>PCNT1                      | 0x50Ch<br>[15:8]    | 0xXXh            |   |                  |   | COUNT    | [15:8]    |   |   |   |  |  |

| (READ-<br>ONLY)                    | 0x50Ch<br>[23:16]   | 0xXXh            |   |                  |   | COUNT    | [23:16]   |   |   |   |  |  |

|                                    | 0x50Ch<br>[31:24]   | 0xXXh            |   |                  |   | COUNT    | [31:24]   |   |   |   |  |  |

|                                    | 0x50Dh<br>[7:0]     | 0xXXh            |   |                  |   | COUNT    | [7:0]     |   |   |   |  |  |

| STAT<br>PCNT2                      | 0x50Dh<br>[15:8]    | 0xXXh            |   |                  |   | COUNT    | [15:8]    |   |   |   |  |  |

| (READ-<br>ONLY)                    | 0x50Dh<br>[23:16]   | 0xXXh            |   |                  |   | COUNT    | [23:16]   |   |   |   |  |  |

|                                    | 0x50Dh<br>[31:24]   | 0xXXh            |   |                  |   | COUNT    | [31:24]   |   |   |   |  |  |

| Register<br>Name         | Register<br>Address | Default<br>Value | 7                | 6                    | 5              | 4                      | 3                  | 2       | 1        | 0        |

|--------------------------|---------------------|------------------|------------------|----------------------|----------------|------------------------|--------------------|---------|----------|----------|

|                          | 0x50Eh<br>[7:0]     | 0xXXh            |                  |                      |                | COUNT                  | [7:0]              |         |          |          |

| STAT<br>ACNT1            | 0x50Eh<br>[15:8]    | 0xXXh            |                  | COUNT [15:8]         |                |                        |                    |         |          |          |

| (READ-<br>ONLY)          | 0x50Eh<br>[23:16]   | 0xXXh            |                  |                      |                | COUNT                  | [23:16]            |         |          |          |

| - ,                      | 0x50Eh<br>[31:24]   | 0xXXh            |                  |                      |                | COUNT                  | [31:24]            |         |          |          |

|                          | 0x50Fh<br>[7:0]     | 0xXXh            |                  |                      |                | COUNT                  | [7:0]              |         |          |          |

| STAT                     | 0x50Fh              | 0xXXh            |                  |                      |                | COUNT                  | [15:8]             |         |          |          |

| ACNT2<br>(READ-<br>ONLY) | [15:8]<br>0x50Fh    | 0xXXh            |                  |                      |                | COUNT                  | [23:16]            |         |          |          |

| ONLT                     | [23:16]<br>0x50Fh   | 0xXXh            |                  |                      |                | COUNT                  | [31:24]            |         |          |          |

|                          | [31:24]<br>0x510h   | 0X00h            |                  |                      |                | ADCR_V                 | OS [7:0]           |         |          |          |

|                          | [7:0]<br>0x510h     | 0X00h            |                  |                      |                | ADCR_VC                |                    |         |          |          |

| ADC<br>OFFSET            | [15:8]<br>0x510h    | 0X00h            |                  |                      |                | ADCL_V                 |                    |         |          |          |

|                          | [23:16]<br>0x510h   | 0X00h            |                  |                      |                | ADCL_VC                |                    |         |          |          |

|                          | [31:24]<br>0x511h   |                  |                  |                      |                | ADOL_VC                |                    |         |          |          |

|                          | [7:0]<br>0x511h     | 0X00h            |                  |                      |                | OUT1_V                 | OS [7:0]           |         |          |          |

| CLASS D<br>OFFSET        | [15:8]<br>0x511h    | 0X00h            |                  |                      |                | OUT1_VC                | S [15:8]           |         |          |          |

|                          | [23:16]<br>0x511h   | 0X00h            |                  |                      |                | OUT2_V                 | OS [7:0]           |         |          |          |

|                          | [31:24]             | 0X00h            |                  |                      |                | OUT2_VC                | S [15:8]           |         |          |          |

|                          | 0x520h<br>[7:0]     | 0x06h            |                  |                      | Р              | OWER_UP_               | DELAY [7:0]        |         |          |          |

| DELAY                    | 0x520h<br>[15:8]    | 0x00h            |                  |                      | P              | OWER_UP_[              | DELAY [15:8]       |         |          |          |

|                          | 0x520h<br>[23:16]   | 0x20h            |                  |                      |                | DEGLITCH               | I_DELAY            |         |          |          |

|                          | 0x520h<br>[31:24]   | 0x09h            |                  |                      |                | STATE_I                | DELAY              |         |          |          |

|                          | 0x521h<br>[7:0]     | 0x00h            | ADC_SYN<br>C_SEL | ADC_DC_<br>CORRECT   | ADC_DC_<br>CAL | PWM_DC<br>_CORREC<br>T | VREF_<br>DELAY     | PULSE   | FORCE    | ENABLE   |

| ENABLE &                 | 0x521h<br>[15:8]    | 0x20h            | QSA_MBI<br>ST    | QSA_<br>CLK_STO<br>P | HIFI           | PCM_<br>CLK_SEL        | I2S_CLK            | 1       | MCLK_RAT | E        |

| CLOCKS                   | 0x521h<br>[23:16]   | 0x00h            |                  | UNUSED               | •              | ADC_HPF<br>_TO_1_4     | ADC_HPF<br>_ENABLE | AD      | C_HPF_M( | DDE      |

|                          | 0x521h<br>[31:24]   | 0x00h            |                  |                      | UNUSED         |                        |                    | OFFSET_ | READBAC  | K_SELECT |

| Register<br>Name | Register<br>Address | Default<br>Value | 7                       | 6                         | 5               | 4            | 3               | 2             | 1             | 0                 |

|------------------|---------------------|------------------|-------------------------|---------------------------|-----------------|--------------|-----------------|---------------|---------------|-------------------|

|                  | 0x522h<br>[7:0]     | 0x33h            | ZERO_<br>CROSS          | MUTE                      |                 |              | ADC_I           | LVL           |               |                   |

| DIGITAL          | 0x522h<br>[15:8]    | 0x33h            | UNL                     | JSED                      | I2S_LVL         |              |                 |               |               |                   |

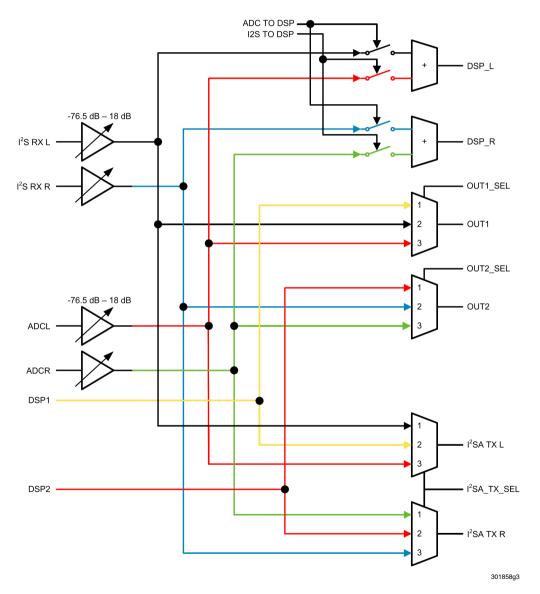

| MIXER            | 0x522h<br>[23:16]   | 0x02h            |                         | UNL                       | JSED            |              | I2SA_T          | X_SEL         | ADC_DS<br>P   | I2S_DSP           |

|                  | 0x522h<br>[31:24]   | 0x05h            |                         | UNL                       | JSED            |              | OUT2            | _SEL          | OUT1          | _SEL              |

|                  | 0x523h<br>[7:0]     | 0x00h            | BYPASS_<br>MOD          | AUTO_SD                   | ADCTRIM         | ZERO_DI<br>G | ZERO_AN<br>A    | PARALL<br>EL  | ANA           | _LVL              |

|                  | 0x523h<br>[15:8]    | 0x10h            | UNL                     | JSED                      | SCAN_TRI<br>G   | SE_MOD       | PMC_<br>TEST    | TSD_DIS       | SCKT_DI<br>S  | TST_SHT           |

| ANALOG           | 0x523h<br>[23:16]   | 0x00h            |                         |                           | ļ               | UNUS         | Į               | <u>I</u>      | <u>I</u>      | !                 |

|                  | 0x523h<br>[31:24]   | 0x00h            |                         |                           |                 | UNUSED       |                 |               |               | I2C_ANA<br>_LEVEL |

|                  | 0x524h<br>[7:0]     | 0x01h            | SYNC_<br>MODE           | STEREO_<br>SYNC_<br>PHASE | CLOCK_<br>PHASE | SYNC_MS      | CLK_MS          | TX_<br>ENABLE | RX_<br>ENABLE | STEREO            |

|                  | 0x524h<br>[15:8]    | 0x00h            | UNL                     | UNUSED HALF_CYCLE_DIVIDER |                 |              |                 | <u>I</u>      | ļ.            |                   |

|                  | 0x524h<br>[23:14]   | 0x00h            |                         | UNUSED                    |                 |              | SYNTH_<br>DENOM | S             | SYNTH_NU      | М                 |

|                  | 0x524h<br>[31:24]   | 0x00h            | UNL                     | UNUSED MONO_SYNC_WIDT     |                 | /IDTH        | 5               | SYNC_RAT      | E             |                   |

| I2S PORT         | 0x525h<br>[7:0]     | 0x00h            | TX.                     | _BIT                      |                 | TX_WIDTH     | _WIDTH          |               |               | I                 |

|                  | 0x525h<br>[15:8]    | 0x02h            | RX_<br>A/µLAW           | RX_<br>COMPAN<br>D        |                 | RX_N         | MSB_POSITI      | ON            |               | RX_MOD<br>E       |

|                  | 0x525h<br>[23:16]   | 0x02h            | TX_<br>A/µLAW           | TX_<br>COMPAN<br>D        |                 | TX_N         | /ISB_POSITI     | ON            |               | TX_MOD<br>E       |

|                  | 0x525h<br>[31:24]   | 0x00h            |                         |                           |                 | UNUS         | SED             |               |               |                   |

|                  | 0x526h<br>[7:0]     | 0x00h            |                         |                           | ADO             | C_COMP_C     | DEFF_C0 [7:     | 0]            |               |                   |

|                  | 0x526h<br>[15:8]    | 0x00h            |                         |                           | ADC             | _COMP_CC     | EFF_C0 [15      | :8]           |               |                   |

|                  | 0x526h<br>[23:14]   | 0x00h            |                         |                           | ADO             | C_COMP_C     | DEFF_C1 [7:     | 0]            |               |                   |

| ADC<br>TRIM      | 0x526h<br>[31:24]   | 0x00h            |                         |                           | ADC             | _COMP_CC     | EFF_C1 [15      | :8]           |               |                   |

| CO-EF<br>FICIENT | 0x527h<br>[7:0]     | 0x00h            | ADC_COMP_COEFF_C2 [7:0] |                           |                 |              |                 |               |               |                   |

|                  | 0x527h<br>[15:8]    | 0x00h            |                         |                           | ADC             | _COMP_CC     | EFF_C2 [15      | :8]           |               |                   |

|                  | 0x527h<br>[23:16]   | 0x00h            |                         |                           |                 | UNUS         | SED             |               |               |                   |

|                  | 0x527h<br>[31:24]   | 0x00h            |                         |                           |                 | UNUS         | SED             |               |               |                   |

| Register<br>Name | Register<br>Address | Default<br>Value | 7                       | 6                       | 5                  | 4                       | 3                   | 2                       | 1                       | 0                |  |

|------------------|---------------------|------------------|-------------------------|-------------------------|--------------------|-------------------------|---------------------|-------------------------|-------------------------|------------------|--|

|                  | 0x528h<br>[7:0]     | 0x00h            | UNL                     | JSED                    | I2SL_LVL<br>CLIP   | I2SR_LVL<br>CLIP        | ADCL_LVL            | ADCR_L<br>VL<br>CLIP    | ADCL_                   | ADCR_            |  |

| READ<br>BACK0    | 0x528h<br>[15:8]    | 0x00h            |                         | UNUSED THERMAL          |                    |                         | CLIF                | CLIP                    | SHORT2                  | SHORT1           |  |

| (READ-<br>ONLY)  | 0x528h<br>[23:14]   | 0x00h            |                         |                         |                    | SPA                     | RE                  |                         |                         |                  |  |

|                  | 0x528h<br>[31:24]   | 0x00h            |                         |                         |                    | UNUS                    | SED                 |                         |                         |                  |  |

|                  | 0x529h<br>[7:0]     | 0x00h            |                         | OFF_RD_                 | BACK [3:0]         |                         |                     | CE_S                    | TATE                    |                  |  |

| READ<br>BACK1    | 0x529h<br>[15:8]    | 0x00h            |                         |                         |                    | OFF_RD_B                | ACK [11:4]          |                         |                         |                  |  |

| (READ-<br>ONLY)  | 0x529h<br>[23:14]   | 0x00h            |                         |                         |                    | OFF_RD_BA               | ACK [19:12]         |                         |                         |                  |  |

|                  | 0x529h<br>[31:24]   | 0x00h            |                         |                         |                    | SPARE_R                 | D_BACK              |                         |                         |                  |  |

|                  | 0x530h<br>[7:0]     | 0x30h            | I2C_MCL<br>K_REQ        |                         |                    | Γ                       | DEVICE_ID           |                         |                         |                  |  |

| SYS              | 0x530h<br>[15:8]    | 0x00h            |                         | UNUSED                  |                    |                         | I2C_SP_MOD          |                         | USE_22C<br>_ROM_S<br>EL | USE_RA<br>M      |  |

| CONFIG           | 0x530h<br>[23:16]   | 0x8Ch            | W_CLE UNUSED            |                         |                    |                         |                     |                         |                         |                  |  |

|                  | 0x530h<br>[31:24]   | 0x00h            |                         | I UNUSED                |                    |                         |                     | MBIST1_<br>ENABLE       | MBISTO                  |                  |  |

| SPEAKE           | 0x531h<br>[7:0]     | 0x65h            |                         | ٧                       | V2                 |                         |                     | W                       | <u>'</u> 1              |                  |  |

| R<br>OVER        | 0x531h<br>[15:8]    | 0x43h            | UNUSED                  |                         | RL_RES             |                         | UNUSED AT_RES       |                         |                         |                  |  |

| DRIVE<br>CONTRO  | 0x531h<br>[23:16]   | 0x83h            |                         | MAX_                    | _GAIN              |                         |                     | AT_C                    | AT_GAIN                 |                  |  |

| L                | 0x531h<br>[31:24]   | 0x27h            | SODP_E<br>NABLE         | FS                      | SINP_              | MODE                    | UNUSED              |                         | INT_GAIN                |                  |  |

|                  | 0x532h<br>[7:0]     | 0x70h            |                         |                         |                    | LEVE                    | EL1                 |                         |                         |                  |  |

| SODP<br>THRES    | 0x532h<br>[15:8]    | 0x20h            |                         |                         |                    | LEVE                    | EL2                 |                         |                         |                  |  |

| HOLD             | 0x532h<br>[23:16]   | 0x64h            |                         |                         |                    | INT_                    | ГН1                 |                         |                         |                  |  |

|                  | 0x532h<br>[31:24]   | 0x64h            |                         |                         |                    | INT_                    | ГН2                 |                         |                         |                  |  |

|                  | 0x533h<br>[7:0]     | 0x00h            | UNL                     | JSED                    | LOW_PW             | R_MODE                  | UNUSED              | AUDET                   | _LEVEL                  | AUDET<br>_ENABL  |  |

| LOW<br>POWER     | 0x533h<br>[15:8]    | 0x09h            | Oh ADC_TH [3:0]         |                         |                    |                         | TIMEOUT             | _DELAY                  |                         |                  |  |

| CONTRO           | 0x533h<br>[23:16]   | 0x00h            |                         |                         |                    | ADC_TH                  | I [11:4]            |                         |                         |                  |  |

| _                | 0x533h<br>[31:24]   | 0x00h            | OVR_AD<br>CL_ENAB<br>LE | OVR_ADC<br>R_ENABL<br>E | OVR_PLL<br>_ENABLE | OVR_VRE<br>F_ENABL<br>E | OVR_OUT<br>1_ENABLE | OVR_OU<br>T2_ENAB<br>LE | OVR_OU<br>T1_RST        | OVR_OU<br>T2_RST |  |

| Register<br>Name | Register<br>Address | Default<br>Value | 7               | 6   | 5      | 4       | 3                 | 2             | 1             | 0              |

|------------------|---------------------|------------------|-----------------|-----|--------|---------|-------------------|---------------|---------------|----------------|

|                  | 0x538h<br>[7:0]     | 0x00h            |                 | 2b0 | MBIST_ | ENABLE  | MBIS <sup>-</sup> | T_GO          | MBIST         | _DONE          |

| SYSTEM           | 0x538h<br>[15:8]    | 0x00h            |                 |     | UNUSED |         |                   | CL_ACTI<br>VE | BUS_ER<br>ROR | DEV_EXI<br>STS |

| STATUS           | 0x538h<br>[23:16]   | 0x00h            |                 |     |        | MEM_AD  | DR [7:0]          | •             |               |                |

|                  | 0x538h<br>[31:24]   | 0x00h            |                 |     |        | MEM_ADE | DR [15:8]         |               |               |                |

|                  | 0x539h<br>[7:0]     | 0XA0h            | CHIP_ID [7:0]   |     |        |         |                   |               |               |                |

| DEVICE           | 0x539h<br>[15:8]    | 0x3Ah            | CHIP_ID [15:8]  |     |        |         |                   |               |               |                |

| ID               | 0x539h<br>[23:16]   | 0x90h            |                 |     |        | CHIP_ID | [23:16]           |               |               |                |

|                  | 0x539h<br>[31:24]   | 0x48h            |                 |     |        | CHIP_ID | [31:24]           |               |               |                |

|                  | 0x53Ah<br>[7:0]     |                  |                 |     |        | SODP_IN | NT [7:0]          |               |               |                |

| SPEAKE R<br>OVER | 0x53Ah<br>[15:8]    |                  | SODP_INT [15:8] |     |        |         |                   |               |               |                |

| DRIVE<br>DEBUG   | 0x53Ah<br>[23:16]   |                  | SODP_INT[23:16] |     |        |         |                   |               |               |                |

| DEBOO            | 0x53Ah<br>[31:24]   |                  |                 |     |        | GAIN_IN | T_MAG             |               |               |                |

#### FILTER CONTROL REGISTER (0x500h)

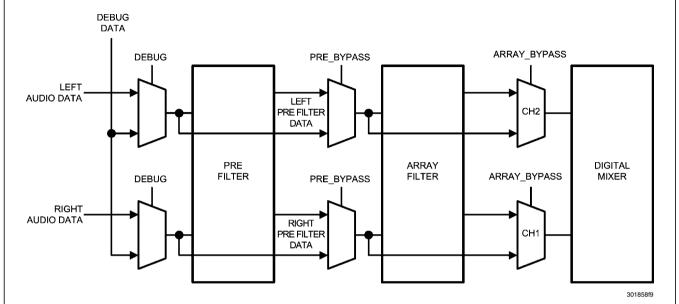

Configures the LM48903 Array and Pre-Array filters (Spatial Engine). The Filter Control Register sets the length of the Array and Pre-Array filter taps, and selects the filter channel source for each audio output. Set PRE\_BYPASS and ARRAY\_BYPASS to 1 to bypass the Spatial Engine, disabling the spatial effect without modifying the coefficients. Set PRE\_ENABLE and ARRAY\_ENABLE to 1 to enable the Spatial Engine. Set PRE\_ENABLE and ARRAY\_ENABLE to 0 to disable the spatial engine. Disabling the Spatial Engine does not affect the register contents. Disable the Spatial Engine during coefficient programming.

**TABLE 4. Filter Control Register**

| BIT   | NAME         | VALUE | DESCRIPTION                                                                                              |

|-------|--------------|-------|----------------------------------------------------------------------------------------------------------|

| 7:0   | ARRAY_TAP    |       | Array Filter Tap Length                                                                                  |

| 14:8  | PRE_TAP      |       | Pre-filter Tap Length. Pre-filter tap length should be less than or equal to the Array filter tap length |

| 15    | UNUSED       |       | , , , ,                                                                                                  |

|       |              |       | Channel 1 Output Routing Selection                                                                       |

| 17:16 | CH1_SEL      | 0     | Array Filter Channel 0 Output Select                                                                     |

|       |              | 1     | Array Filter Channel 1 Output Select                                                                     |

|       |              |       | Channel 2 Output Routing Selection                                                                       |

| 19:18 | CH2_SEL      | 0     | Array Filter Channel 0 Output Select                                                                     |

|       |              | 1     | Array Filter Channel 1 Output Select                                                                     |

| 27:20 | UNUSED       |       |                                                                                                          |

| 00    | DDE DVDACC   | 0     | Pre-Array filter not bypassed                                                                            |

| 28    | PRE_BYPASS   | 1     | Pre-Array filter bypassed                                                                                |

| 00    | ADDAY DVDACC | 0     | Array filter not bypassed                                                                                |

| 29    | ARRAY_BYPASS | 1     | Array filter bypassed                                                                                    |

| BIT | NAME         | VALUE | DESCRIPTION                                                                                                                                                                   |

|-----|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30  | PRE_ENABLE   | 0     | Pre-Array filter disabled. Disable the Pre-Array Filter during filter and coefficient programming. Disabling the Pre-Array Filter does not affect the device memory contents. |

|     |              | 1     | Pre-Array filter enabled                                                                                                                                                      |

| 31  | ARRAY_ENABLE | 0     | Array filter disabled. Disable the Array Filter during filter and coefficient programming. Disabling the Array Filter does not affect the device memory contents.             |

|     |              | 1     | Array filter enabled                                                                                                                                                          |

### COMPRESSOR CONTROL REGISTER 1 (FILTER COMP1) (0x501h)

#### **TABLE 5. Compressor Control Register**

| BIT   | NAME              | VALUE | DESCRIPTION                                      |

|-------|-------------------|-------|--------------------------------------------------|

| 4:0   | COMP_TH           |       | Pre-Filter Compressor Threshold                  |

|       |                   |       | Pre-Compression Gain                             |

|       |                   | 000   | 2                                                |

|       |                   | 001   | 4                                                |

|       |                   | 010   | 8                                                |

| 7:5   | G1_GAIN           | 011   | 16                                               |

|       |                   | 100   | 32                                               |

|       |                   | 101   | 64                                               |

|       |                   | 110   | 128                                              |

|       |                   | 111   | 256                                              |

|       |                   |       | Compression Ratio                                |

|       |                   | 000   | 1:1                                              |

|       |                   | 001   | 2:1                                              |

|       |                   | 010   | 2.66:1                                           |

| 10:8  | COMP_RATIO        | 011   | 4:1                                              |

|       |                   | 100   | 5.33:1                                           |

|       |                   | 101   | 8:1                                              |

|       |                   | 110   | 10.66:1                                          |

|       |                   | 111   | 16:1                                             |

| 11    | UNUSED            |       |                                                  |

|       |                   |       | Post Compression Gain (V/V)                      |

|       |                   | 000   | 1                                                |