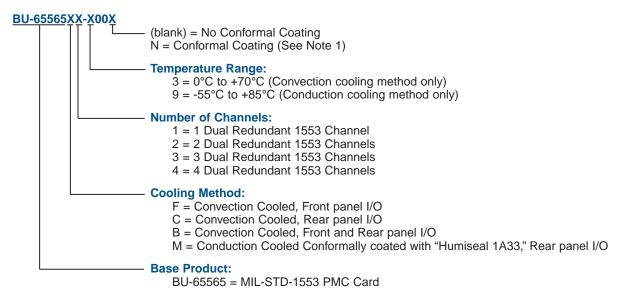

# BU-65565 MIL-STD-1553 PMC Card

## **DESCRIPTION**

The BU-65565 is a single-channel or multi-channel MIL-STD-1553 PMC card. The BU-65565 includes one to four dual redundant 1553 channels, and is available in convection- or conduction-cooled versions. The conduction-cooled version is conformally coated.

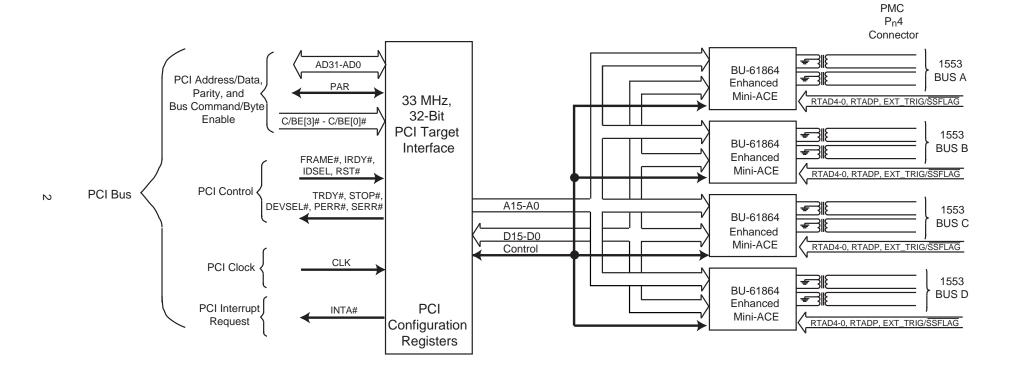

The design of the BU-65565 leverages the Enhanced Mini-ACE. Each channel may be independently programmed for BC, RT, Monitor, or RT/Monitor mode.

Advanced architectural features of the Enhanced Mini-ACE include a highly autonomous bus controller, an RT providing a wide variety of buffering options, and a selective message monitor. Each Enhanced Mini-ACE channel incorporates 64K words of RAM, and utilizes 3.3 volt logic to reduce power consumption.

The conduction-cooled version of the card includes thermal vias connected to a thermal plane to provide improved thermal conduction. Boards have been subjected to multi-axes Shock & Vibration testing.

## **SOFTWARE**

The BU-65565 is supported by free software, including a C++ library, along with VxWorks™ and Linux™ drivers. The library and driver comprise a suite of C function calls that serves to offload a great deal of low-level tasks from the application programmer. This software supports all of the Enhanced Mini-ACE's advanced architectural features.

FEATURES

- 32-Bit/33 MHz PMC Card

- Operates in 3.3V or 5V PCI Signaling Environments

Make sure the next Card you purchase

- One to Four Dual Redundant MIL-STD-1553 Channels

- Conduction or Convection Cooled

- Shock and Vibration Tested

- Enhanced Mini-ACE BC/RT/MT Architecture

- Transformer-Coupled 1553 Channels (Consult Factory for Direct Coupling)

- 64K-word RAM per Channel

- Highly Autonomous Bus Controller Architecture

- Message Scheduling

- Bulk Data Transfers

- Asynchronous Messages

- Retries and Bus Switching

- Data Block Double Buffering

- RT Buffering Options

- Single Buffering

- Double Buffering

- Subaddress Circular Buffering

- Global Circular Buffering

- Selective Message Monitor

- Supports PCI Interrupts

- VxWorks Software Driver

Data Device Corporation 105 Wilbur Place Bohemia, New York 11716 631-567-5600 Fax: 631-567-7358 www.ddc-web.com FOR MORE INFORMATION CONTACT:

Technical Support: 1-800-DDC-5757 ext. 7234

| TABLE 1. BU-65565 S                                                              | PECIF | ICATI | ONS          |          |

|----------------------------------------------------------------------------------|-------|-------|--------------|----------|

| PARAMETER                                                                        | MIN   | TYP   | MAX          | UNITS    |

| ABSOLUTE MAXIMUM RATINGS                                                         |       |       |              |          |

| Supply Voltage (Note 9)<br>+3.3V                                                 | -0.3  |       | 4.6          | V        |

| +5V                                                                              | -0.3  |       | 6.0          | V        |

| Logic Inputs RECEIVER                                                            | -0.3  |       | 5.5          | V        |

| Input Impedance, Transformer                                                     | 1.000 |       |              | Kohm     |

| Coupled (Notes 1-3)                                                              | 0 000 |       |              | \/= =    |

| Threshold Voltage, Transformer Coupled                                           | 0.200 |       | 0.860        | Vp-p     |

| Common Mode Voltage (Note 4)                                                     |       |       | 10           | Vpeak    |

| TRANSMITTER Differential Output Voltage                                          |       |       |              |          |

| Transformer Coupled Across 70                                                    | 18    | 20    | 27           | Vp-p     |

| ohms Output Offset Voltage, Transformer                                          | -250  | 150   | 250          | mVpeak   |

| Coupled Across 70 ohms                                                           | 250   | 130   | 200          | IIIVpcak |

| Rise/Fall Time                                                                   | 100   | 150   | 300          | ns       |

| POWER SUPPLY REQUIREMENTS Voltage/Tolerances                                     |       |       |              |          |

| +3.3V (Logic Power)(Note 9)                                                      | 3.0   | 3.3   | 3.6          | V        |

| +5V (RAM and Transceiver Power) Current Drain                                    | 4.5   | 5.0   | 5.5          | V        |

| BU-65565X1                                                                       |       |       |              |          |

| +5V                                                                              |       |       | 400          | ^        |

| <ul><li>Idle</li><li>25% Duty Transmitter Cycle</li></ul>                        |       |       | 100<br>210   | mA<br>mA |

| <ul> <li>50% Duty Transmitter Cycle</li> </ul>                                   |       |       | 320          | mA       |

| • 100% Duty Transmitter Cycle<br>+3.3V (Logic)                                   |       |       | 540<br>80    | mA<br>mA |

| BU-65565X2                                                                       |       |       |              | '''      |

| +5V                                                                              |       |       |              | A        |

| <ul><li>Idle</li><li>25% Duty Transmitter Cycle</li></ul>                        |       |       | 200<br>420   | mA<br>mA |

| <ul> <li>50% Duty Transmitter Cycle</li> </ul>                                   |       |       | 640          | mA       |

| • 100% Duty Transmitter Cycle<br>+3.3V (Logic)                                   |       |       | 1.08<br>120  | A<br>mA  |

| BU-65565X3 /                                                                     |       |       | 120          |          |

| +5V<br>• Idle                                                                    |       |       | 300          | mA       |

| • 25% Duty Transmitter Cycle                                                     |       |       | 630          | mA       |

| 50% Duty Transmitter Cycle     100% Duty Transmitter Cycle                       |       |       | 960          | mA       |

| • 100% Duty Transmitter Cycle<br>+3.3V (Logic)                                   |       |       | 1.62<br>160  | A<br>mA  |

| BU-65565X4                                                                       |       |       |              |          |

| +5V<br>• Idle                                                                    |       |       | 400          | mA       |

| <ul> <li>25% Duty Transmitter Cycle</li> </ul>                                   |       |       | 840          | mA       |

| <ul><li>50% Duty Transmitter Cycle</li><li>100% Duty Transmitter Cycle</li></ul> |       |       | 1.28<br>2.16 | A<br>A   |

| +3.3V (Logic)                                                                    |       |       | 200          | mA       |

| POWER DISSIPATION (NOTE 10)                                                      |       |       |              |          |

| BU-65565X1<br>• Idle                                                             |       |       | 0.84         | l w      |

| • 25% Duty Transmitter Cycle                                                     |       |       | 1.12         | W        |

| <ul><li>50% Duty Transmitter Cycle</li><li>100% Duty Transmitter Cycle</li></ul> |       |       | 1.41<br>1.98 | W<br>W   |

| BU-65565X2                                                                       |       |       | 1.90         | \ \v     |

| • Idle                                                                           |       |       | 1.53         | W        |

| <ul><li>25% Duty Transmitter Cycle</li><li>50% Duty Transmitter Cycle</li></ul>  |       |       | 2.10<br>2.67 | W<br>W   |

| 100% Duty Transmitter Cycle                                                      |       |       | 3.81         | W        |

| BU-65565X3<br>• Idle                                                             |       |       | 2.23         | l w      |

| <ul> <li>25% Duty Transmitter Cycle</li> </ul>                                   |       |       | 3.08         | W        |

| <ul><li>50% Duty Transmitter Cycle</li><li>100% Duty Transmitter Cycle</li></ul> |       |       | 3.93<br>5.64 | W<br>W   |

| BU-65565X4                                                                       |       |       | 3.04         | l vv     |

| • Idle                                                                           |       |       | 2.92         | W        |

| <ul><li>25% Duty Transmitter Cycle</li><li>50% Duty Transmitter Cycle</li></ul>  |       |       | 4.06<br>5.20 | W<br>W   |

| 100% Duty Transmitter Cycle                                                      |       |       | 7.47         | W        |

| TABLE 1. BU-65565 SPECI                                                                                                                    | FICA                             | TIONS                                         | (CO                              | NT.)                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------|----------------------------------|------------------------------------------|

| PARAMETER                                                                                                                                  | MIN                              | TYP                                           | MAX                              | UNITS                                    |

| POWER DISSIPATION (NOTE 10) (cont.)                                                                                                        |                                  |                                               |                                  |                                          |

| Hottest Die  • Idle  • 25% Duty Transmitter Cycle  • 50% Duty Transmitter Cycle                                                            |                                  |                                               | 0.28<br>0.51                     | W<br>W                                   |

| 100% Duty Transmitter Cycle     100% Duty Transmitter Cycle                                                                                |                                  |                                               | 0.75<br>1.22                     | W<br>W                                   |

| 1553 MESSAGE TIMING Completion of CPU Write (BC Start)-to-Start of Next Message (Non-enhanced BC Mode)                                     |                                  | 2.5                                           |                                  | μs                                       |

| BC Intermessage Gap - (Note 5) Non-Enhanced BC mode (Mini-ACE                                                                              |                                  | 9.5                                           |                                  | μs                                       |

| compatible) Enhanced BC mode (Note 6)                                                                                                      |                                  | 10.1                                          |                                  | μs                                       |

| BC/RT/MT Response Timeout (Note 7) 18.5 nominal 22.5 nominal 50.5 nominal 128.0 nominal RT Response Time (mid-parity to mid-sync) (Note 8) | 17.5<br>21.5<br>49.5<br>127<br>4 | 18.5<br>22.5<br>50.5<br>129.5                 | 19.5<br>23.5<br>51.5<br>131<br>7 | µs<br>µs<br>µs<br>µs                     |

| Transmitter Watchdog Timeout THERMAL                                                                                                       |                                  | 660.5                                         |                                  | μs                                       |

| Thermal Interface (rails) BU-65565XX-900 BU-65565XX-300 Thermal Resistance (BU-65565MX)                                                    | -55<br>0                         |                                               | +85<br>+70                       | °C<br>°C                                 |

| junction-to-thermal rail Operating Junction Temperature Storage Temperature                                                                | -55<br>-65                       |                                               | 39<br>160<br>160                 | °C/W<br>°C<br>°C                         |

| MECHANICAL DESIGN Shock: Three pulses, half sine on six (6) axes                                                                           | 40g's                            | , 11 mse                                      | ec/axes                          |                                          |

| Vibration: Random input, one hour each axes, three hours total, 15 to                                                                      |                                  | 14g's rn                                      | ns                               |                                          |

| 2000 Hz<br>Resonant Frequency: BU-65565M2<br>(calculated)                                                                                  |                                  | 12 Hz                                         |                                  |                                          |

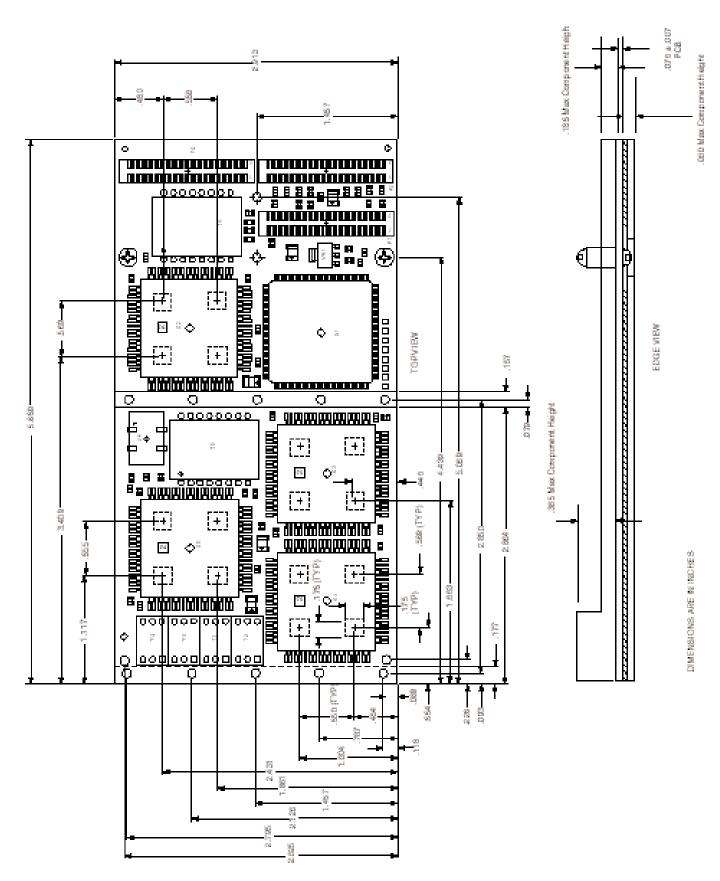

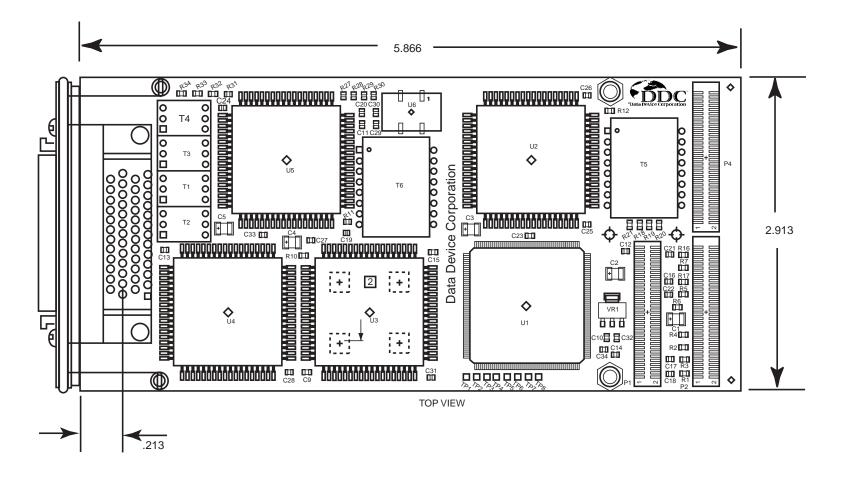

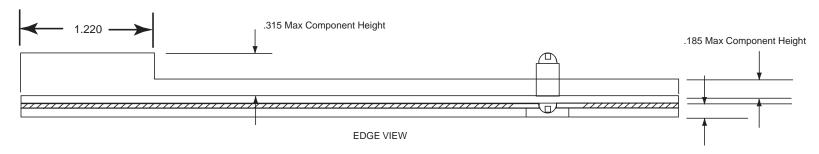

| PHYSICAL CHARACTERISTICS Size                                                                                                              | 5.87 x 2.91<br>(149 x 74)        |                                               |                                  | in.<br>(mm)                              |

| Weight BU-65565X1 BU-65565X2 BU-65565X3 BU-65565X4                                                                                         | 3                                | 2.7 (76.<br>3.3 (93.5<br>3.9 (110<br>1.5 (127 | 56)<br>.6)                       | oz. (g)<br>oz. (g)<br>oz. (g)<br>oz. (g) |

TABLE 1 notes:

(Notes 1 through 3 are applicable to the Input Impedance specification:

- (1) The specifications are applicable for both unpowered and powered conditions. (2) The specifications assume a 2 Volt rms balanced, differential, sinusoidal input. The applicable frequency is 75 kHz to 1 MHz.

- (3) Minimum impedance is guaranteed over the operating range, but is not tested. (4) Assumes a common mode voltage within the frequency range of dc to 2MHz, applied to pins of the isolation transformer on the stub side (transformer coupled), and referenced to signal.

- applied to pins of the isolation transformer on the stub side (transformer coupled), and referenced to signal.

(5) Typical value for minimum intermessage gap time. Under software control, this may be lengthened to 65,535 ms. If ENHANCED CPU ACCESS, bit 14 of Configuration Register #6, is set to logic "1", then host accesses during BC Start-of-Message (SOM) and End-of-Message (EOM) transfer sequences could have the effect of lengthening the intermessage gap time. For each host access during an SOM or EOM sequence, the intermessage gap time will be lengthened by 6 clock cycles. Since there are 7 internal transfers during SOM, and 5 during EOM, this could theoretically lengthen the intermessage gap by up to 72 clock cycles; in A 5 US

- (6) For enhanced BC mode, the typical value for intermessage gap time is approximately 625 ns longer than for the non-enhanced BC mode.

TABLE 1 notes: (cont.)

- (7) Software programmable (4 options). Includes RT-to-RT Timeout (measured mid parity of transmit Command Word to mid-sync of Transmitting RT Status Word)

- (8) Measured from mid-parity crossing of Command Word to mid-sync crossing of RT's Status Word.

- (9) The standard BU-65565 board requires +3.3 Volt and +5 Volt power. For applications where +3.3 Volts is not available, DDC is able to supply a non-standard version of the BU-65565 card requiring only +5 Volts (consult factory).

- (10) Power dissipation specifications assume a transformer coupled configuration with external dissipation (while transmitting) of:

- 0.14 watts for the active isolation transformer,

- 0.08 watts for the active bus coupling transformer,

- 0.45 watts for each of the two bus isolation resistors and

- 0.15 watts for each of the two bus termination resistors.

#### INTRODUCTION

The BU-65565 is a single-channel or multi-channel MIL-STD-1553 PMC card built in accordance with IEEE PMC Physical and Environmental Layers Standard P1386.1/Draft 2.4. The BU-65565 is available with one to four dual redundant 1553 channels on a convection-cooled or conduction-cooled card.

The design of the BU-65565 leverages the BU-61864 Enhanced Mini-ACE. Each channel may be independently programmed for BC, RT, Monitor, or RT/Monitor mode.

Advanced architectural features of the Enhanced Mini-ACE include a highly autonomous bus controller, an RT providing a wide variety of buffering options, and a selective message monitor. Each Enhanced Mini-ACE channel incorporates 3.3 volt logic to reduce power consumption, and includes 64K words of RAM.

The conduction-cooled version of the card includes thermal vias connected to a thermal plane to provide improved thermal conduction.

The BU-65565 card has undergone extensive Shock (3 axes, half-sine shock pulse, input amplitude of 40 g's, duration 11 ms) and Vibration testing (3 axes, 1 hour per axis, random input, 14.0 g's RMS, 15 to 2000 hz.)

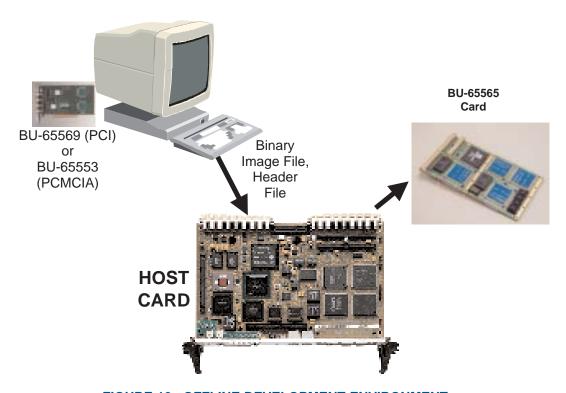

The BU-65565 is supported by the BU-69090 series free software, including a C++ library and a VxWorks driver. The library and driver comprise a suite of C function calls that serves to offload a great deal of low-level tasks from the application programmer. This software supports all of the Enhanced Mini-ACE's advanced architectural features.

## **ENHANCED MINI-ACE**

The BU-65565 PMC card incorporates a PCI bridge, along with between one and four of DDC's BU-61564G3 Enhanced Mini-ACE hybrids. Each Enhanced Mini-ACE comprises a complete, independent interface between the PCI bridge and a MIL-STD-1553 bus. The Enhanced Mini-ACE hybrids provide software

compatibility with DDC's older generation ACE and Mini-ACE (Plus) terminals.

The BU-61564 Enhanced Mini-ACE provides complete multiprotocol support of MIL-STD-1553A/B/McAir and STANAG 3838. These hybrids include dual transceivers; along with protocol, host interface, memory management logic; and 64K X 16 of RAM. There is built-in parity checking for this RAM.

One of the salient features of the Enhanced Mini-ACE is its enhanced bus controller architecture. The Enhanced BC's highly autonomous message sequence control engine provides a means for offloading the host processor for implementing multiframe message scheduling, message retry and bus switching schemes, data double buffering, and asynchronous message insertion. In addition, the Enhanced BC mode includes 8 general purpose flag bits, a general purpose queue, and user-defined interrupts, for the purpose of performing messaging to the host processor.

Another important feature of the Enhanced Mini-ACE is the incorporation of a fully autonomous built-in self-test. This test provides comprehensive testing of the internal protocol logic. A separate test verifies the operation of the Enhanced Mini-ACE's internal 64K RAM. Since the self-tests are fully autonomous, they eliminate the need for the host to write and read stimulus and response vectors.

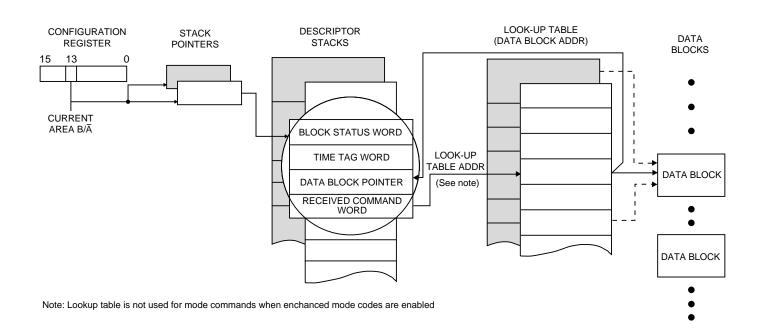

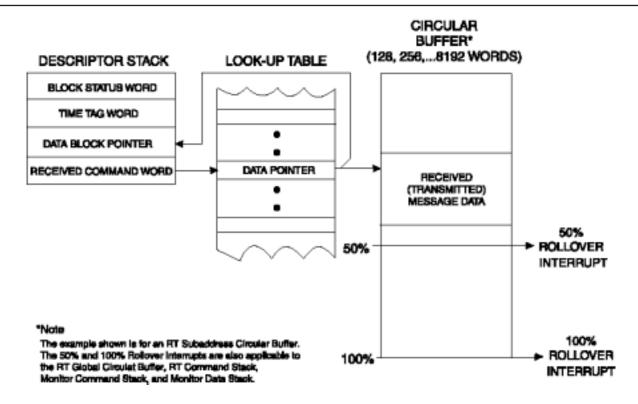

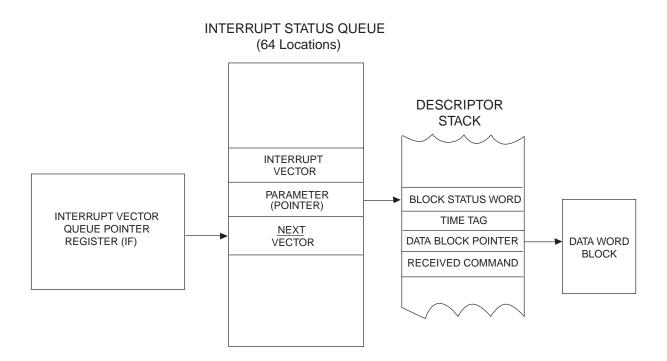

The Enhanced Mini-ACE RT offers the choice of single, double, and circular buffering for individual subaddresses along with a global circular buffering option for multiple (or all) receive subaddresses, a 50% rollover interrupt for circular buffers, an interrupt status queue for logging up to 32 interrupt events, and an option to automatically initialize to RT mode with the Busy bit set following power-up.

The transceivers in the Enhanced Mini-ACE series terminals are fully monolithic, requiring only a +5 volt power input. The transmitters are voltage sources, which provide improved line driving capability over current sources. This serves to improve performance on long buses with many taps. The BU-65565's transmitters may be trimmed to meet the MIL-STD-1760 requirement of a minimum of 20 volts peak-to-peak, transformer coupled (consult factory).

If required, the BU-65565 is also available with an option for McAir compatible transmitters (consult factory).

## THERMAL DESIGN

The thermal design of the conduction-cooled version of the BU-65565 card includes thermal vias located under the Enhanced Mini-ACE transceiver chips. The transceiver chips have the highest heat dissipation on the card: 1.22 watts maximum at 100% transmit duty cycle. Thermally conductive epoxy in the form of a paste adhesive is applied to the PC board in the areas under the

Enhanced Mini-ACE devices. Heat is conducted through the thermal vias to an inner copper plane layer, which functions as a heat spreader. The heat path includes additional thermal vias from the thermal plane layer to the two copper strips which run the width of the card. Thermal rails from the card base may then be bolted to the copper strips, providing a path for removing heat from the card.

The BU-65565 card's total thermal resistance, from transceiver chip junction to the copper strip/thermal rail interface, is 39° C/W max. This includes the  $\theta$ JC of 11° C/W max for the Enhanced Mini-ACE hybrid and a thermal resistance of 28° C/W max for the card, i.e., from the hybrid case to the copper strip/thermal rail interface. With a rail temperature of 85°, this results in a maximum junction temperature of 129° at 100% transmit duty cycle. Since the transmit duty cycle for most 1553 BCs and RTs is significantly less than 100%, this provides ample headroom below the transceiver chip's maximum junction temperature of 160°.

#### **MECHANICAL DESIGN**

Test specimens of the BU-65565 card were subjected to Shock and Random Vibration testing. All devices were non-operational during all phases of testing and exhibited no evidence of physical damage at the conclusion of testing.

Three (3) shock pulses were applied in each of the following six (6) test directions: Horizontal (+X), Horizontal (+Z), Vertical (+Y), Horizontal (-X), Horizontal (-Z), and Vertical (-Y). Each applied shock pulse was Half-Sine in waveshape, at an input amplitude of 40 g's and a duration of 11 milliseconds.

Random Vibration was independently applied for one (1) hour to each of three (3) orthogonal axes resulting in a total test time of three (3) hours. Testing was performed with the input applied along the Horizontal (X), Horizontal (Z) and Vertical (Y) test axes. Test specimens were subjected to a Random input, in the frequency range of 15 to 2000 Hz at an overall RMS level of 14.0g's. The Resonant frequency of the BU-65565M2 was performed and found to be 12 Hz.

The conduction-cooled version of the card is conformally coated with Humiseal 1A33 polyurethane coating.

## **PCI INTERFACE**

As a means of minimizing power consumption and dissipation, the design of the standard BU-65565 board utilizes +3.3 volt power for the PCI interface and 1553 (Enhanced Mini-ACE) logic. The 1553 transceivers and RAM are powered by +5 volts. For applications where +3.3 volt power is not available, DDC is able to supply a non-standard version of the BU-65565 card requiring only +5 volts power (consult factory).

The BU-65565's PCI interface is a fully compliant target (slave) agent, as defined by the PCI Local Bus Specification Revision

| TABLE 2. PCI CONFIGURATION REGISTER SPACE                           |                                                                                                                                    |                              |                              |                                           |  |  |  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|-------------------------------------------|--|--|--|

| ADDRESS                                                             | 31 24                                                                                                                              | 23 16                        | 15 8                         | 7 0                                       |  |  |  |

| 00Н                                                                 | Devic                                                                                                                              | e ID                         |                              | dor ID                                    |  |  |  |

| 0011                                                                | 04h                                                                                                                                | 01h                          |                              | anufacturer<br>ralue (4DDC <sub>H</sub> ) |  |  |  |

| 04H                                                                 | Status R                                                                                                                           | Register                     | Commai                       | nd Register                               |  |  |  |

| 08H                                                                 | Class                                                                                                                              | Code = 078                   | 000 h                        | Rev ID = 01                               |  |  |  |

| 0СН                                                                 | BIST (not implemented)                                                                                                             | Header<br>Type 00h           | Latency<br>Timer             | Cache Line<br>Size                        |  |  |  |

|                                                                     | Base Addre                                                                                                                         |                              | 0 (for Enhand<br>AM)         | ced Mini-ACE                              |  |  |  |

| 10H                                                                 | R/W                                                                                                                                | R/W and<br>0's<br>(see text) | 00h                          | 04h                                       |  |  |  |

| 14H                                                                 | Base Address Register 1 (for Enhanced Mini-ACE registers)                                                                          |                              |                              |                                           |  |  |  |

| 14H                                                                 | R/W                                                                                                                                | R/W                          | R/W and<br>0's<br>(see text) | 04h                                       |  |  |  |

| 18H - 24H BASE<br>ADDRESS<br>REGISTERS 2<br>THROUGH 5<br>(NOT USED) | 0000000h                                                                                                                           |                              |                              |                                           |  |  |  |

| 28H                                                                 |                                                                                                                                    |                              | r (not used) (               |                                           |  |  |  |

| 2CH                                                                 | Subsystem Device and Subsystem Vendor ID Same as Configuration Register 0, Alias Reads to Configuration Register User Configurable |                              |                              |                                           |  |  |  |

| 30H                                                                 | Expansion ROM Base Address (not used, bit 0 = 0)                                                                                   |                              |                              |                                           |  |  |  |

| 34H - 38H                                                           | Reserved                                                                                                                           |                              |                              |                                           |  |  |  |

| зсн                                                                 | Max Lat.<br>00h                                                                                                                    | Min Gnt<br>00h               | Interrupt Pin<br>01h         | Interrupt Line<br>R/W                     |  |  |  |

2.2, using a 32-bit interface that operates at clock speeds of up to 33 MHz, in a 3.3 volt or 5 volt signaling environment. The interface supports PCI interrupts and contains a 32 X 32 FIFO to accelerate burst write transfers from the PCI host. That is, it's possible to perform a burst write of 32 16-bit words (i.e., all of the data words of a 1553 message) by means of sixteen 32-bit PCI transfers in approximately 500 ns.

The BU-65565 contains a single set of PCI configuration registers such that all of the Enhanced Mini-ACE(s) memory and register space may be addressed through a single PCI function. Reference TABLE 2.

Internal registers implement the Subsystem Vendor and Device ID, and control the Fail-Safe operation of the device. There are two Base Address Registers, utilized to implement the Enhanced Mini-ACE memory space (BAR0) and register space (BAR1).

The Base Address Register mapping is contained in PCI configuration register space.

The Enhanced Mini-ACE register mapping is located in PCI memory space, allowing for full PCI access to all 1553 terminals. The BU-65565 configuration registers and the Enhanced Mini-ACE RAM (64K X 16 each) are accessed in 32-bit words, while all ACE registers are accessed as 16- bit words. If a 32-bit read is performed from the PCI bus in ACE register space, only the lower 16 bits of data are valid. ACE memory may also be accessed in 16-bit words, but memory is accessed sequentially, allowing for 32 bits of data to be written to or read from the PCI bus.

That is, if a 32-bit PCI memory read is performed, the first 16 bits of data would be read from the requested address, the next 16 bits of data would be read from the initial address + 2. The BU-65565 supports 32-bit and 16-bit read and write operations only. 8-bit accesses are illegal.

#### **INTERRUPTS**

The Enhanced Mini-ACE's may issue interrupt requests over the PCI bus. PCI Interrupts are generated on the INTA# output signal to the PCI host. The interrupts from each Enhanced Mini-ACE(s) are functionally OR'd together to provide a single interrupt.

## REGISTER AND MEMORY ADDRESSING

The BU-65565 PCI interface contains a set of "Type 00h" PCI configuration registers that are used to map the device into the host system. The PCI configuration register space is mapped in accordance with PCI revision 2.2 specifications.

## **ENHANCED MINI-ACE REGISTER AND**

## **MEMORY ADDRESSING**

The software interface between each Enhanced Mini-ACE and the PCI host consists of 24 internal operational registers for normal operation, an additional space for 40 test mode registers, plus 64K words of shared memory address space.

Enhanced Mini-ACE registers may only be accessed as 16-bit words. If a 32-bit read access is attempted, the upper 16 bits will not be valid. That is, register accesses are on a 32-bit boundary (e.g., 000 = Enhanced Mini-ACE Register 0, 004 = Enhanced Mini-ACE Register 1, 008 = Enhanced Mini-ACE Register 2, ... etc).

Enhanced Mini-ACE memory may be accessed as either single 16-bit words, or as a 32-bit double word. For the latter, a packed pair of 16-bit words at adjacent memory address locations will be accessed.

Note that the addressing for all Enhanced Mini-ACE pointers is word-oriented, while all PCI addressing is byte-oriented. That is, the value of a pointer stored in Enhanced Mini-ACE RAM will be half of the value of the PCI address offset from the base memory address for the particular Enhanced Mini-ACE.

For normal operation, the host processor only needs to access the lower 32 register address locations (00-1F). The next 32 locations (20-3F) should be reserved, since many of these are used for factory test.

## **BUS CONTROLLER (BC) ARCHITECTURE**

The BC functionality for the Enhanced Mini-ACE includes two separate architectures: (1) the older, legacy mode, which provides complete compatibility with the previous ACE and Mini-ACE (Plus) generation products; and (2) the newer, Enhanced BC mode. The Enhanced BC mode offers several new powerful architectural features. These includes the incorporation of a highly autonomous BC message sequence control engine, which greatly serves to offload the operation of the host CPU.

The Enhanced BC's message sequence control engine provides a high degree of flexibility for implementing major and minor frame scheduling; capabilities for inserting asynchronous messages in the middle of a frame; to separate 1553 message data from control/status data for the purpose of implementing double buffering and performing bulk data transfers; for implementing message retry schemes, including the capability for automatic bus channel switchover for failed messages; and for reporting various conditions to the host processor by means of 4 user-defined interrupts and a general purpose queue.

In both the legacy and Enhanced BC modes, the Enhanced Mini-ACE BC implements all MIL-STD-1553B message formats. Message format is programmable on a message-by-message basis by means of the BC Control Word and the  $T/\overline{R}$  bit of the Command Word for the respective message. The BC Control Word allows 1553 message format, 1553A/B type RT, bus channel, self-test, and Status Word masking to be specified on an individual message basis. In addition, automatic retries and/or interrupt requests may be enabled or disabled for individual messages. The BC performs all error checking required by MIL-STD-1553B. This includes validation of response time, sync type and sync encoding, Manchester II encoding, parity, bit count, word count, Status Word RT Address field, and various RT-to-RT transfer errors. The Enhanced Mini-ACE BC response timeout value is programmable with choices of 18, 22, 50, and 130 ms. The longer response timeout values allow for operation over long buses and/or use of the repeaters.

In its legacy mode, the Enhanced Mini-ACE may be programmed to process BC frames of up to 512 messages with no processor intervention. In the Enhanced BC mode, there is no explicit limit to the number of messages that may be processed in a frame. In

both modes, it is possible to program for either single frame or frame auto-repeat operation. In the auto-repeat mode, the frame repetition rate may be controlled either internally, using a programmable BC frame timer, or from an external trigger input.

**Enhanced BC Mode: Message sequence control.** One of the major new architectural features of the Enhanced Mini-ACE series is its advanced capability for BC message sequence control. The Enhanced Mini-ACE supports highly autonomous BC operation, which greatly offloads the operation of the host processor.

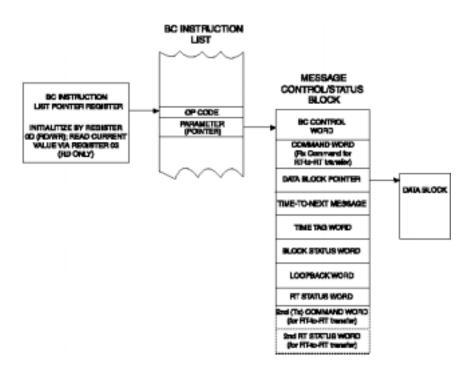

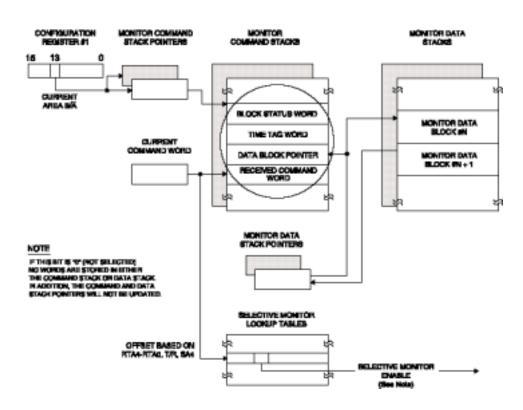

The operation of the Enhanced Mini-ACE's message sequence control engine is illustrated in FIGURE 2. The BC message sequence control involves an instruction list pointer register; an instruction list which contains multiple 2-word entries; a message control/status stack, which contains multiple 8-word or 10-word descriptors; and data blocks for individual messages.

The initial value of the instruction list pointer register is initialized by the host processor (via Register 0D), and is incremented by the BC message sequence processor (host readable via Register 03). During operation, the message sequence control processor fetches the operation referenced by the instruction list pointer register from the instruction list.

Note that the pointer parameter referencing the first word of a message's control/status block (the BC Control Word) must contain an address value that is **modulo 8**. Also, note that if the

message is an RT-to-RT transfer, the pointer parameter must contain an address value that is **modulo 16**.

**Op Codes.** The instruction list pointer register references a pair of words in the BC instruction list: an op code word, followed by a parameter word. The format of the op code word, which is illustrated in FIGURE 3, includes a 5-bit op code field and a 5-bit condition code field. The op code identifies the instruction to be executed by the BC message sequence controller.

Most of the operations are conditional, with execution dependent on the contents of the condition code field. Bits 3-0 of the condition code field identifies the particular condition. Bit 4 of the condition code field identifies the logic sense ("1" or "0") of the selected condition code on which the conditional execution is dependent. TABLE 4 lists all the op codes, along with their respective mnemonic, code value, parameter, and description. TABLE 5 defines all the condition codes.

Eight of the condition codes (8 through F) are set or cleared as the result of the most recent message. The other eight are defined as "General Purpose" condition codes GP0 through GP7. There are three mechanisms for programming the values of the General Purpose Condition Code bits: (1) They may be set, cleared, or toggled by the host processor, by means of the BC GENERAL PURPOSE FLAG REGISTER; (2) they may be set, cleared, or toggled by the BC message sequence control processor, by means of the GP Flag Bits (FLG) instruction; and (3) GP0 and GP1 only (but none of the others) may be set or

FIGURE 2. BC MESSAGE SEQUENCE CONTROL

cleared by means of the BC message sequence control processor's Compare Frame Timer (CFT) or Compare Message Timer (CMT) instructions.

The host processor also has read-only access to the BC condition codes by means of the BC CONDITION CODE REGISTER.

Note that four instructions are **unconditional**. These are Compare to Frame Timer (CFT), Compare to Message Timer (CMT), GP Flag Bits (FLG), and Execute and Flip (XQF). For these instructions, the Condition Code Field is "don't care". That is, these instructions are **always** executed, regardless of the result of the condition code test.

All other instructions are conditional. That is, they will only be executed if the condition code specified by the condition code field in the op code word tests true. If the condition code field tests false, the instruction list pointer will skip down to the next instruction.

As shown in TABLE 4, many of the operations include a single-word parameter. For an XEQ (execute message) operation, the parameter is a pointer to the start of the message's control/status block. For other operations, the parameter may be an address, a time value, an interrupt pattern, a mechanism to set or clear general purpose flag bits, or an immediate value. For several op codes, the parameter is "don't care" (not used).

As described above, some of the op codes will cause the message sequence control processor to execute messages. In this case, the parameter references the first word of a message control/status block. With the exception of RT-to-RT transfer messages, all message status/control blocks are eight words long: a block control word, time-to-next-message parameter, data block pointer, command word, status word, loopback word, block status word, and time tag word.

In the case of an RT-to-RT transfer message, the size of the message control/status block increases to 16 words. However, in this case, the last six words are not used; the ninth and tenth words are for the second command word and second status word.

The third word in the message control/status block is a pointer that references the first word of the message's data word block. Note that the data word block stores only data words, which are to be either transmitted or received by the BC. By segregating data words from command words, status words, and other con-

trol and "housekeeping" functions, this architecture enables the use of convenient, usable data structures, such as circular buffers and double buffers.

Other operations support program flow control; i.e., jump and call capability. The call capability includes maintenance of a call stack which supports a maximum of four (4) entries; there is also a return instruction. In the case of a call stack overrun or underrun, the BC will issue an CALL STACK POINTER REGISTER ERROR interrupt, if enabled.

Other op codes may be used to delay for a specified time; start a new BC frame; wait for an external trigger to start a new frame; do comparisons based on frame time and time-to-next message; load the time tag or frame time registers; halt; and issue host interrupts. In the case of host interrupts, the message control processor passes a 4-bit user-defined interrupt vector to the host, by means of the Enhanced Mini-ACE's Interrupt Status Register.

The purpose of the FLG instruction is to enable the message sequence controller to set, clear, or toggle the value(s) of any or all of the eight general purpose condition flags.

The op code parity bit encompasses all sixteen bits of the op code word. This bit must be programmed for odd parity. If the message sequence control processor fetches an undefined op code word, an op code word with even parity, or bits 9-5 of an op code word do not have a binary pattern of 01010, the message sequence control processor will immediately halt the BC's operation. In addition, if enabled, a BC TRAP OP CODE interrupt will be issued. Also, if enabled, a parity error will result in an OP CODE PARITY ERROR interrupt.

The Enhanced Mini-ACE BC message sequence control capability enables a high degree of offloading of the host processor. This includes using the various timing functions to enable autonomous structuring of major and minor frames. In addition, by implementing conditional jumps and subroutine calls, the message sequence control processor greatly simplifies the insertion of asynchronous, or "out-of-band" messages.

**Execute and Flip Operation.** The Enhanced Mini-ACE BC's XQF, or "Execute and Flip" operation, provides some unique capabilities. Following execution of this unconditional instruction, if the condition code tests TRUE, the BC will modify the value of the current XQF instruction's pointer parameter by toggling bit 4

| 15            | 14 | 13 | 12     | 11   | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3     | 2         | 1       | 0 |

|---------------|----|----|--------|------|----|---|---|---|---|---|---|-------|-----------|---------|---|

| Odd<br>Parity |    | Ор | Code F | ield |    | 0 | 1 | 0 | 1 | 0 |   | Condi | tion Code | e Field |   |

in the pointer. That is, if the selected condition flag tests true, the value of the parameter will be updated to the value = old address XOR 0010h. As a result, the **next** time that this line in the instruction list is executed, the Message Control/Status Block at the **updated** address (**old address XOR 0010h**), rather than the one at the old address, will be processed. The operation of the XQF instruction is illustrated in FIGURE 4.

There are multiple ways of utilizing the "execute and flip" functionality. One is to facilitate the implementation of a double buffering data scheme for individual messages. This allows the message sequence control processor to "ping-pong" between a pair of data buffers for a particular message. By so doing, the host processor can access one of the two Data Word blocks, while the BC reads or writes the alternate Data Word block.

A second application of the "execute and flip" capability is in association with message retries. This allows the BC to not only switch buses when retrying a failed message, but to automatically switch buses **permanently** for all future times that the same message is to be processed. This not only provides a high degree of autonomy from the host CPU, but saves BC band-

width, by eliminating future attempts to process messages on an RT's failed channel.

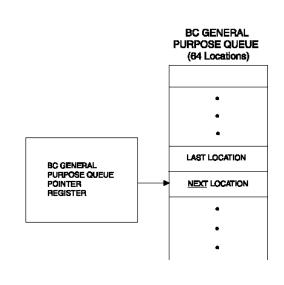

General Purpose Queue. The Enhanced Mini-ACE BC allows for the creation of a general purpose queue. This data structure provides a means for the message sequence processor to convey information to the BC host. The BC op code repertoire provides mechanisms to push various items on this queue. These include the contents of the Time Tag Register, the Block Status Word for the most recent message, an immediate data value, or the contents of a specified memory address.

FIGURE 5 illustrates the operation of the BC General Purpose Queue. Note that the BC General Purpose Queue Pointer Register will always point to the next address location (modulo 64); that is, the location following the last location written by the BC message sequence control engine.

If enabled, a BC GENERAL PURPOSE QUEUE ROLLOVER interrupt will be issued when the value of the queue pointer address rolls over at a 64-word boundary.

FIGURE 4. EXECUTE AND FLIP (XQP) OPERATION

FIGURE 5. BC GENERAL PURPOSE QUEUE

## **ENHANCED MINI-ACE REGISTERS**

The address mapping for the Enhanced Mini-ACE registers is illustrated in TABLE 3:

| ADDRESS         REGISTER           A7         A6         A5         A4         A3         A2         A1         A0         DESCRIPTION / ACCES           0         0         0         0         0         0         0         0/1         Interrupt Mask Register #1 (RD/WR)           0         0         0         0         0         1         0         0/1         Configuration Register #1 (RD/WR)           0         0         0         0         1         1         0         0/1         Configuration Register #2 (RD/WR)           0         0         0         1         1         0         0/1         Start/Reset Register (W/R)           0         0         0         1         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhance           0         0         0         1         0         0/1         BC Control Word/RT Subaddress Control Word Register (I           0         0         0         1         0         0/1         Interrupt Status Register (RD/WR)           0         0         1         1         0         0/1         Configuration Register #1 (RD/WR)           0         0                                                                                                           | ed BC Instruction List Pointer Register (RD) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 0         0         0         0         0         0/1         Interrupt Mask Register #1 (RD/WR)           0         0         0         0         0         1         0         0/1         Configuration Register #1 (RD/WR)           0         0         0         0         1         0         0/1         Configuration Register #1 (RD/WR)           0         0         0         1         1         0         0/1         Start/Reset Register (W/R)           0         0         0         1         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhance           0         0         0         1         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhance           0         0         1         0         0         0/1         BC Control Word/RT Subaddress Control Word Register (I           0         0         1         0         0/1         Interrupt Status Register (RD/WR)           0         0         1         1         0         0/1         Interrupt Status Register #1 (RD)           0         0         1         1         0         0/1         Configuration Register #3 (RD/WR)           0 <t< th=""><th>ed BC Instruction List Pointer Register (RD)</th></t<> | ed BC Instruction List Pointer Register (RD) |

| 0         0         0         0         1         0         0/1         Configuration Register #1 (RD/WR)           0         0         0         0         1         0         0/1         Configuration Register #2 (RD/WR)           0         0         0         1         1         0         0/1         Start/Reset Register (W/R)           0         0         0         1         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhance           0         0         0         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhance           0         0         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhanced           0         0         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhanced           0         0         1         0         0/1         Dold Time Tag Register (RD/WR)           0         0         1         1         0         0/1         Interrupt Status Register #1 (RD)           0         0         1         1         0         0/1         Configuration Register #4 (RD/WR)           0         0         1         0         0/1<                                                      |                                              |

| 0         0         0         0         1         0         0/1         Configuration Register #2 (RD/WR)           0         0         0         1         1         0         0/1         Start/Reset Register (W/R)           0         0         0         1         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhance           0         0         0         1         0         0         0/1         BC Control Word/RT Subaddress Control Word Register (I           0         0         0         1         0         0/1         Time Tag Register (RD/WR)           0         0         0         1         0         0/1         Time Tag Register (RD/WR)           0         0         0         1         1         0         0/1         Interrupt Status Register (RD/WR)           0         0         1         1         0         0/1         Interrupt Status Register #3 (RD/WR)           0         0         1         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0                                                                                  |                                              |

| 0         0         0         1         1         0         0/1         Start/Reset Register (W/R)           0         0         0         1         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhance           0         0         0         1         0         0         0/1         BC Control Word/RT Subaddress Control Word Register (I           0         0         0         1         0         0/1         Time Tag Register (RD/WR)           0         0         0         1         0         0/1         Interrupt Status Register #1 (RD)           0         0         0         1         1         0         0/1         Interrupt Status Register #3 (RD/WR)           0         0         1         1         0         0/1         Configuration Register #4 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         RT/Monitor Data Stack Address Register (RD/WR)           0         0         1         0         0/1         BC Frame Time Remaining Register (RD/WR)           0         0         1         0         0/1                                                                        |                                              |

| 0         0         0         1         1         0         0/1         Non-Enhanced BC or RT Command Stack Pointer/Enhance           0         0         0         1         0         0         0/1         BC Control Word/RT Subaddress Control Word Register (I           0         0         0         1         0         0/1         Time Tag Register (RD/WR)           0         0         0         1         1         0         0/1         Interrupt Status Register #1 (RD)           0         0         0         1         1         0         0/1         Interrupt Status Register #3 (RD/WR)           0         0         1         1         0         0/1         Configuration Register #4 (RD/WR)           0         0         1         0         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         RT/Monitor Data Stack Address Register (RD/WR)           0         0         1         0         0/1         BC Frame Time Remaining Register (RD)           0         0         1         1         0 <t< td=""><td></td></t<>                                             |                                              |

| 0         0         0         1         0         0         0/1         BC Control Word/RT Subaddress Control Word Register (ID)           0         0         0         1         0         0/1         Time Tag Register (RD/WR)           0         0         0         1         1         0         0/1         Interrupt Status Register #1 (RD)           0         0         0         1         1         0         0/1         Configuration Register #3 (RD/WR)           0         0         1         0         0/1         Configuration Register #4 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         RT/Monitor Data Stack Address Register (RD/WR)           0         0         1         0         0/1         BC Frame Time Remaining Register (RD)           0         0         1         1         0         0/1         BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last     <                                         |                                              |

| 0         0         0         1         0         1         0         0/1         Time Tag Register (RD/WR)           0         0         0         1         1         0         0/1         Interrupt Status Register #1 (RD)           0         0         0         1         1         0         0/1         Configuration Register #3 (RD/WR)           0         0         1         0         0         0         0/1         Configuration Register #4 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         RT/Monitor Data Stack Address Register (RD/WR)           0         0         1         0         0/1         BC Frame Time Remaining Register (RD)           0         0         1         1         0         0/1         BC Time Remaining to Next Message Register (RD)           0         0         1         1         0         0/1         BC Frame Time/Enhanced B                                                               | RD/WR)                                       |

| 0         0         0         1         1         0         0         0/1         Interrupt Status Register #1 (RD)           0         0         0         1         1         1         0         0/1         Configuration Register #3 (RD/WR)           0         0         1         0         0         0         0/1         Configuration Register #4 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         RT/Monitor Data Stack Address Register (RD/WR)           0         0         1         0         0/1         BC Frame Time Remaining Register (RD)           0         0         1         1         0         0/1         BC Time Remaining to Next Message Register (RD)           0         0         1         1         0         0/1         BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last           0         0         1         1         0         0/1         RT Status Word Register (RD)           0         0         1         1         1         0         0/1         RT BIT Word Register (RD)           0         1         0         0 </td <td></td>                                                  |                                              |

| 0         0         0         1         1         1         0         0/1         Configuration Register #3 (RD/WR)           0         0         1         0         0         0/1         Configuration Register #4 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         RT/Monitor Data Stack Address Register (RD/WR)           0         0         1         0         0/1         BC Frame Time Remaining Register (RD)           0         0         1         1         0         0/1         BC Time Remaining to Next Message Register (RD)           0         0         1         1         0         0/1         BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last           0         0         1         1         0         0/1         RT Status Word Register (RD)           0         0         1         1         0         0/1         RT BIT Word Register (RD)           0         1         0         0         0         0/1         Test Mode Register 0           0         1         0         0         0         0/1         Test Mode Register 3 <td></td>                                                         |                                              |

| 0         0         1         0         0         0         0/1         Configuration Register #4 (RD/WR)           0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         1         0         0/1         RT/Monitor Data Stack Address Register (RD/WR)           0         0         1         0         1         0         0/1         BC Frame Time Remaining Register (RD)           0         0         1         1         0         0/1         BC Time Remaining to Next Message Register (RD)           0         0         1         1         0         0/1         BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last           0         0         1         1         0         0/1         RT Status Word Register (RD)           0         0         1         1         0         0/1         RT BIT Word Register (RD)           0         1         0         0         0         0/1         Test Mode Register 1           0         1         0         0         0         0/1         Test Mode Register 3           0         1         0         0         0/1         Test Mod                                                                        |                                              |

| 0         0         1         0         0/1         Configuration Register #5 (RD/WR)           0         0         1         0         0/1         RT/Monitor Data Stack Address Register (RD/WR)           0         0         1         0         0/1         BC Frame Time Remaining Register (RD)           0         0         1         1         0         0/1         BC Time Remaining to Next Message Register (RD)           0         0         1         1         0         0/1         BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last           0         0         1         1         0         0/1         RT Status Word Register (RD)           0         0         1         1         0         0/1         RT BIT Word Register (RD)           0         1         0         0         0         0/1         Test Mode Register 0           0         1         0         0         0         0/1         Test Mode Register 2           0         1         0         0         0         0/1         Test Mode Register 4                                                                                                                                                                                                              |                                              |

| 0         0         1         0         1         0         0/1         RT/Monitor Data Stack Address Register (RD/WR)           0         0         1         0         0/1         BC Frame Time Remaining Register (RD)           0         0         1         1         0         0/1         BC Time Remaining to Next Message Register (RD)           0         0         1         1         0         0/1         BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last           0         0         1         1         0         0/1         RT Status Word Register (RD)           0         0         1         1         0         0/1         RT BIT Word Register (RD)           0         1         0         0         0         0/1         Test Mode Register 0           0         1         0         0         0         0/1         Test Mode Register 1           0         1         0         0         0         0/1         Test Mode Register 3           0         1         0         0         0/1         Test Mode Register 4                                                                                                                                                                                                       |                                              |

| 0         0         1         0         1         1         0         0/1         BC Frame Time Remaining Register (RD)           0         0         1         1         0         0         0/1         BC Time Remaining to Next Message Register (RD)           0         0         1         1         0         0/1         BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last           0         0         1         1         0         0/1         RT Status Word Register (RD)           0         0         1         1         1         0         0/1         RT BIT Word Register (RD)           0         1         0         0         0         0/1         Test Mode Register 0           0         1         0         0         0         0/1         Test Mode Register 1           0         1         0         0         0         0/1         Test Mode Register 2           0         1         0         0         0         0/1         Test Mode Register 4                                                                                                                                                                                                                                                                            |                                              |

| 0         0         1         1         0         0         0/1         BC Time Remaining to Next Message Register (RD)           0         0         1         1         0         0/1         BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last           0         0         1         1         1         0         0/1         RT Status Word Register (RD)           0         0         1         1         1         0         0/1         RT BIT Word Register (RD)           0         1         0         0         0         0/1         Test Mode Register 0           0         1         0         0         0         0/1         Test Mode Register 1           0         1         0         0         0         0/1         Test Mode Register 2           0         1         0         0         0         0/1         Test Mode Register 3           0         1         0         1         0         0/1         Test Mode Register 4                                                                                                                                                                                                                                                                                                       |                                              |

| 0         0         1         1         0         1         0         0/1         BC Frame Time/Enhanced BC Initial Instruction Pointer/RT Last           0         0         1         1         1         0         0/1         RT Status Word Register (RD)           0         0         1         1         1         0         0/1         RT BIT Word Register (RD)           0         1         0         0         0         0/1         Test Mode Register 0           0         1         0         0         0         1         Test Mode Register 1           0         1         0         0         0         0/1         Test Mode Register 2           0         1         0         0         0         0/1         Test Mode Register 3           0         1         0         1         0         0         0/1         Test Mode Register 4                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |

| 0         0         1         1         1         0         0         0/1         RT Status Word Register (RD)           0         0         1         1         1         1         0         0/1         RT BIT Word Register (RD)           0         1         0         0         0         0         0/1         Test Mode Register 0           0         1         0         0         1         0         0/1         Test Mode Register 1           0         1         0         0         1         0         0/1         Test Mode Register 2           0         1         0         0         1         0         0/1         Test Mode Register 3           0         1         0         1         0         0         0/1         Test Mode Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

| 0       0       1       1       1       0       0/1       RT BIT Word Register (RD)         0       1       0       0       0       0/1       Test Mode Register 0         0       1       0       0       1       0       0/1       Test Mode Register 1         0       1       0       0       1       1       0       0/1       Test Mode Register 2         0       1       0       0       1       1       0       0/1       Test Mode Register 3         0       1       0       1       0       0       0/1       Test Mode Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Command/MT Trigger Word Register (RD/WR)     |

| 0         1         0         0         0         0         0         0/1         Test Mode Register 0           0         1         0         0         1         0         0/1         Test Mode Register 1           0         1         0         0         1         0         0         0/1         Test Mode Register 2           0         1         0         0         1         1         0         0/1         Test Mode Register 3           0         1         0         1         0         0         0/1         Test Mode Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |

| 0     1     0     0     1     0     0/1     Test Mode Register 1       0     1     0     0     1     0     0/1     Test Mode Register 2       0     1     0     0     1     1     0     0/1     Test Mode Register 3       0     1     0     1     0     0     0/1     Test Mode Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |

| 0     1     0     0     1     0     0 0/1     Test Mode Register 2       0     1     0     0     1     1     0     0/1     Test Mode Register 3       0     1     0     1     0     0     0/1     Test Mode Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |

| 0 1 0 0 1 1 0 0/1 Test Mode Register 3 0 1 0 1 0 0 0 0/1 Test Mode Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| 0 1 0 1 0 0 0 0/1 Test Mode Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |