# TC9329AFAG, TC9329AFCG

## Portable Audio DTS Controller (DTS-21)

The TC9329AFAG/AFCG is a single-chip DTS microcontroller for portable audio incorporating a 230-MHz prescaler, PLL, and LCD driver. In addition to a 20-bit IF counter, 6-bit A/D converter, serial interface, and buzzer function, the device supports an interrupt function, 8-bit timer/counter, and 8-bit pulse counter. The LCD driver features built-in 1/4 duty, 1/2 bias and a 3-V voltage boosting circuit, implementing stable LCD. The power supply voltage ranges from 0.9 to 1.8 V. Because of its low current consumption (CPU: 80  $\mu$ A (max)), the device is suitable for use in digital tuning systems in portable equipment such as headphone stereos.

### Features

- CMOS DTS microcontroller LSI with built-in 230 MHz prescaler, PLL, and LCD driver

- Operating voltage: VDD = 0.9~1.8 V (typ.: 1.5 V)

- Current dissipation:

- CPU in operation: IDD = 40  $\mu$ A typ.

- PLL in operation: IDD = 6 mA typ. (VHF mode)

- Operating temperature range: Ta = -10~60°C

- Program memory (ROM): 16 bits  $\times$  4096 steps

- Data memory (RAM): 4 bits  $\times$  256 words

- Instruction execution time: With crystal oscillator: 40  $\mu$ s

- With CR oscillator: 6  $\mu$ s

(at 1 MHz, VDD = 1.1~1.8 V)

- Crystal oscillator frequency: 75 kHz

- Stack level: 8

- General-purpose IF counter: 20 bit (CMOS input supported)

- A/D converter: 6 bits  $\times$  4-channels

- LCD driver: 1/4 duty, 1/2 bias, 72 segments (max)

- I/O port: CMOS I/O ports: 12

- N-channel open drain I/O ports: 16 (max)

- Output-only port: 1

- Input-only ports: 3 (max)

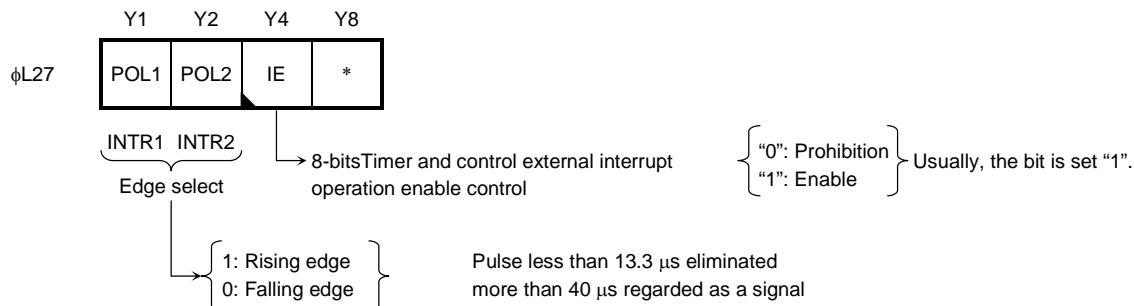

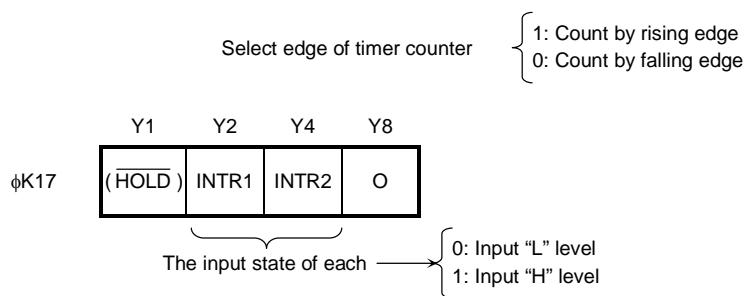

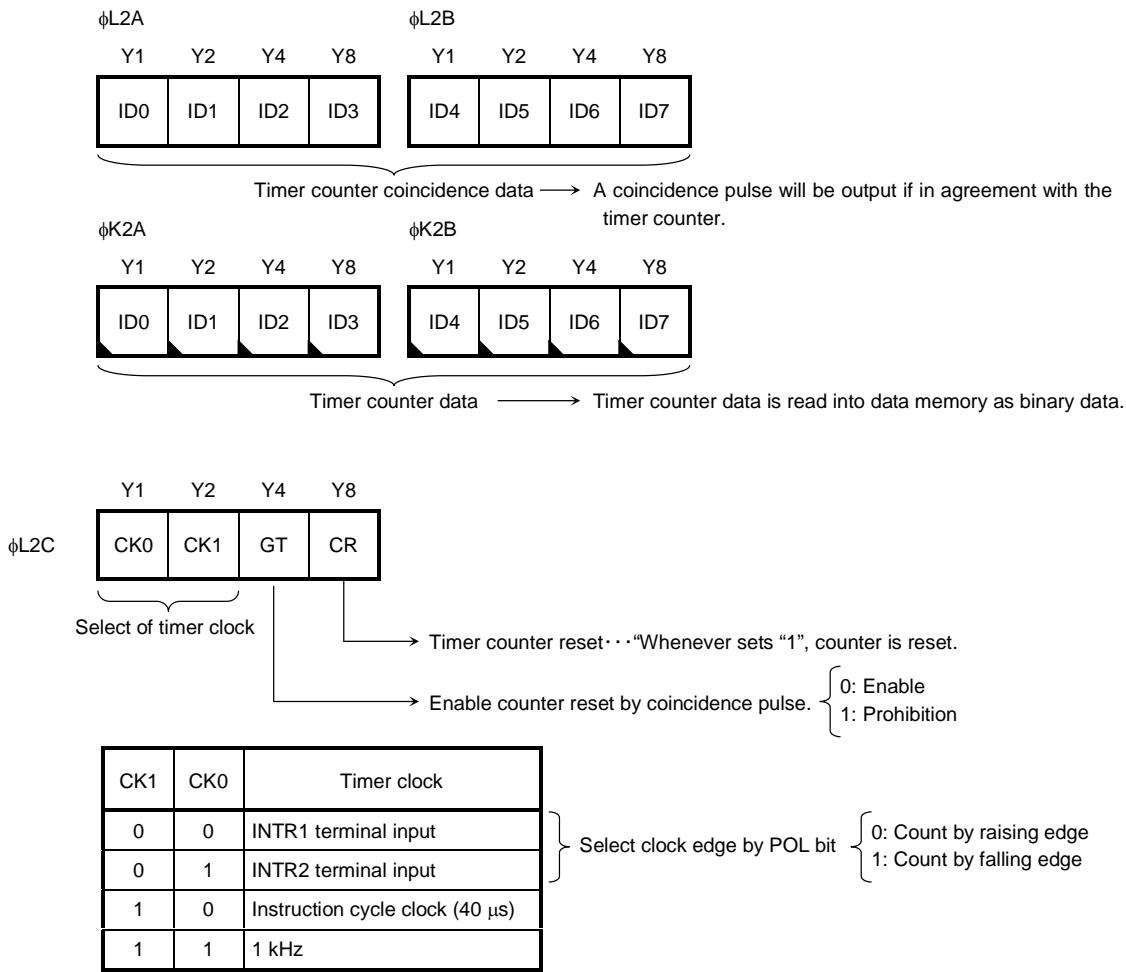

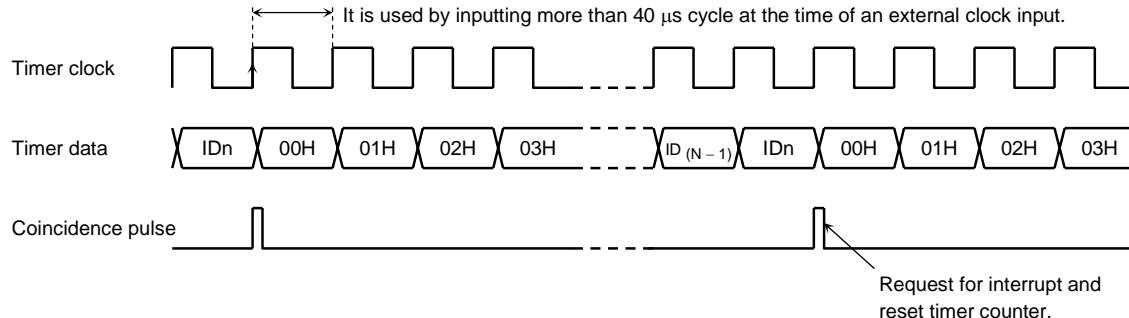

- Timer/counter: 8 bits (as timer clock: INTR1/INTR2; instruction cycle: 1 kHz selectable)

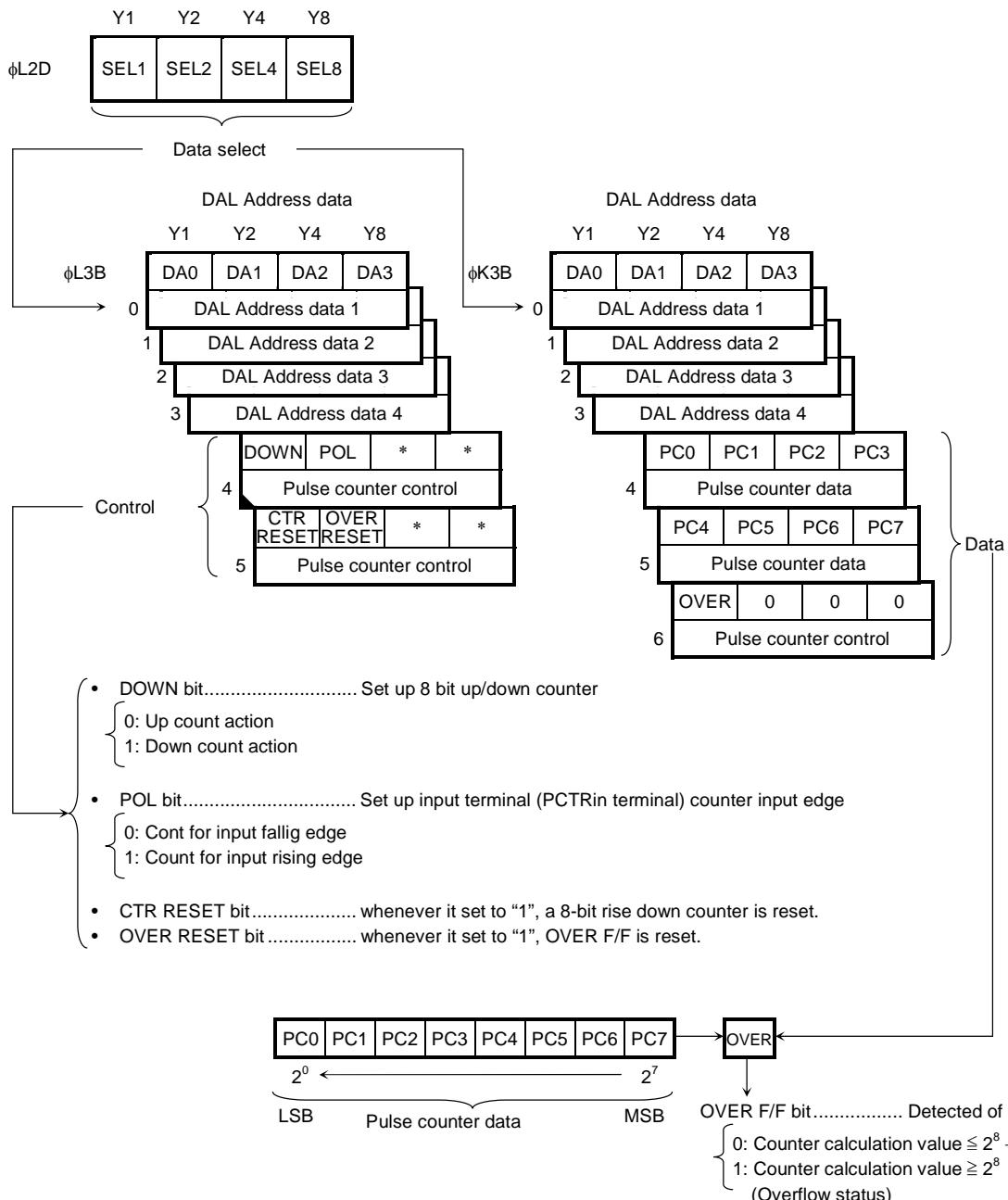

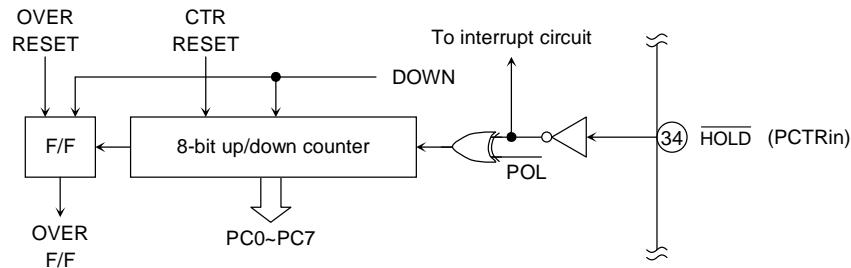

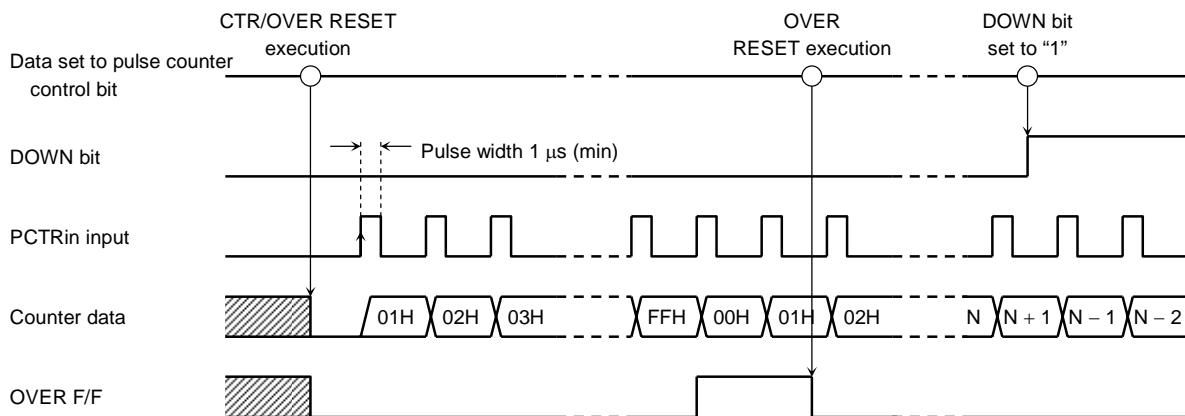

- Pulse counter: 8-bit up/down counter (input via INTR2 pin)

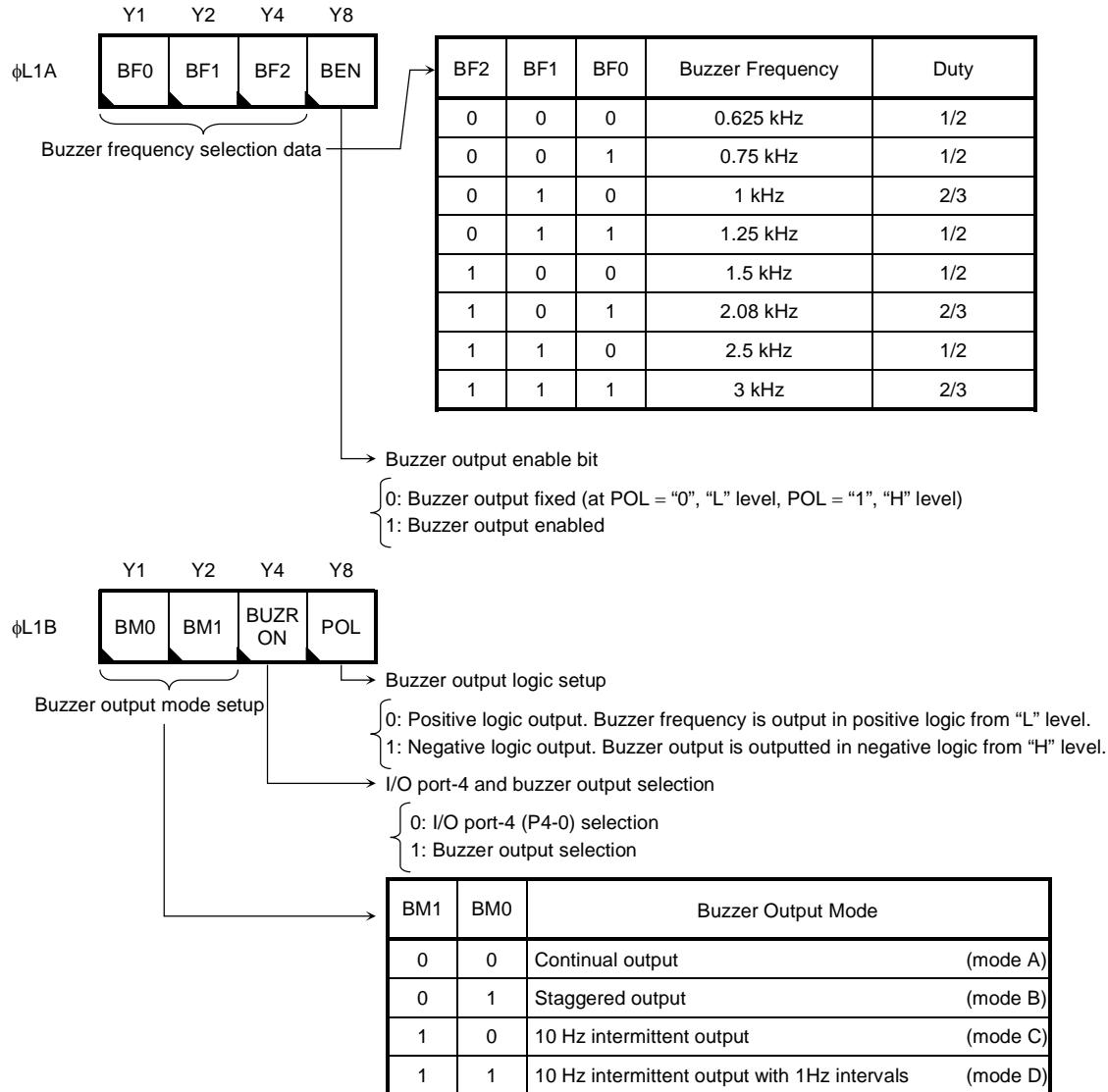

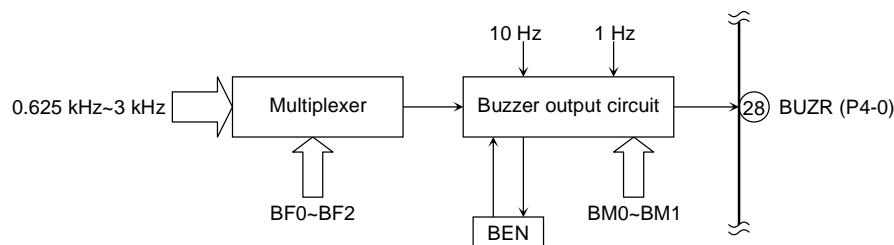

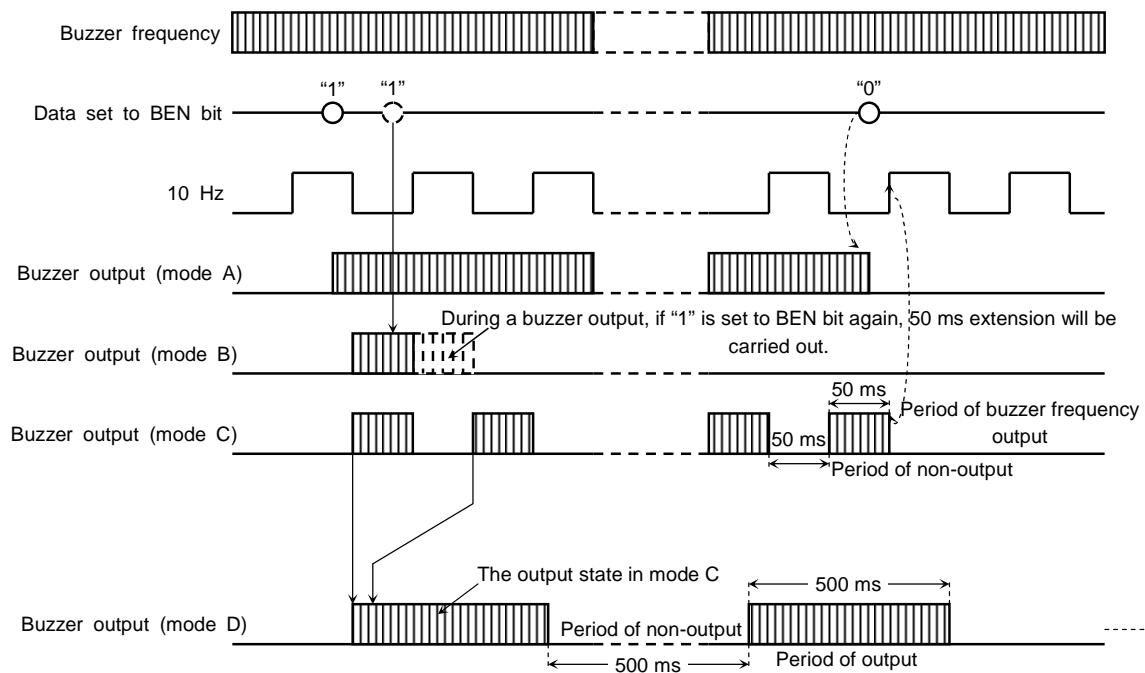

- Buzzer: 8 settings, 0.625~3 kHz; 4 built-in modes consisting of continuous, single-shot, 10 Hz intermittent, or 10 Hz intermittent at 1 Hz intervals.

- Interrupts: 2 external, 2 internal (serial interface, 8-bit timer)

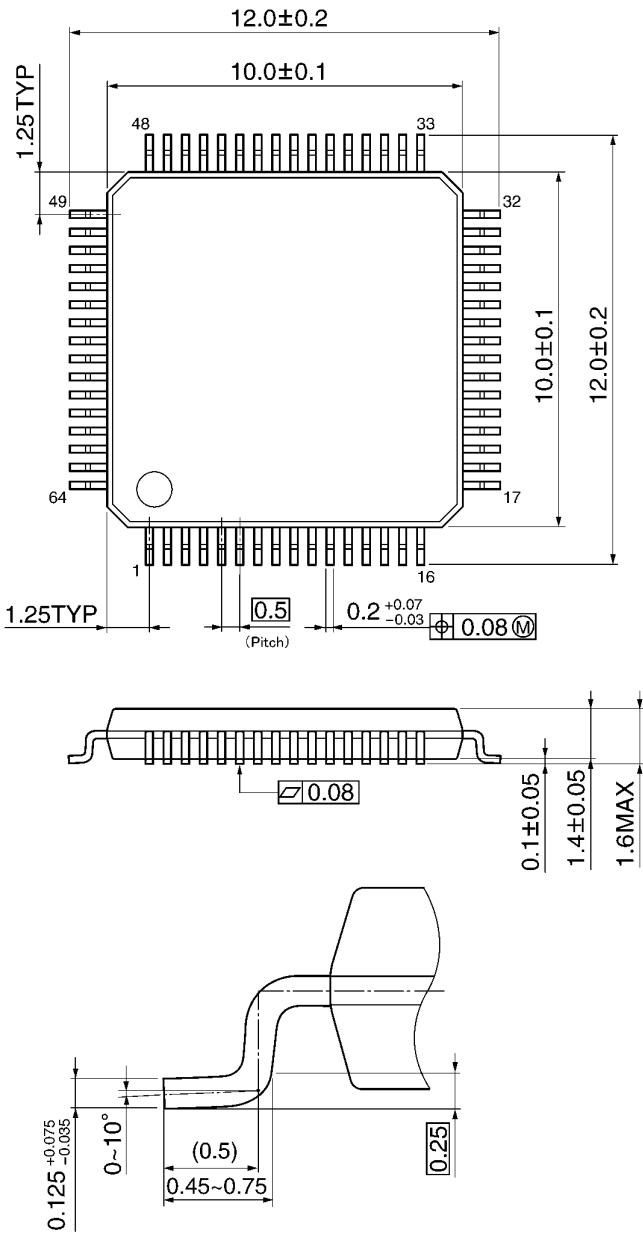

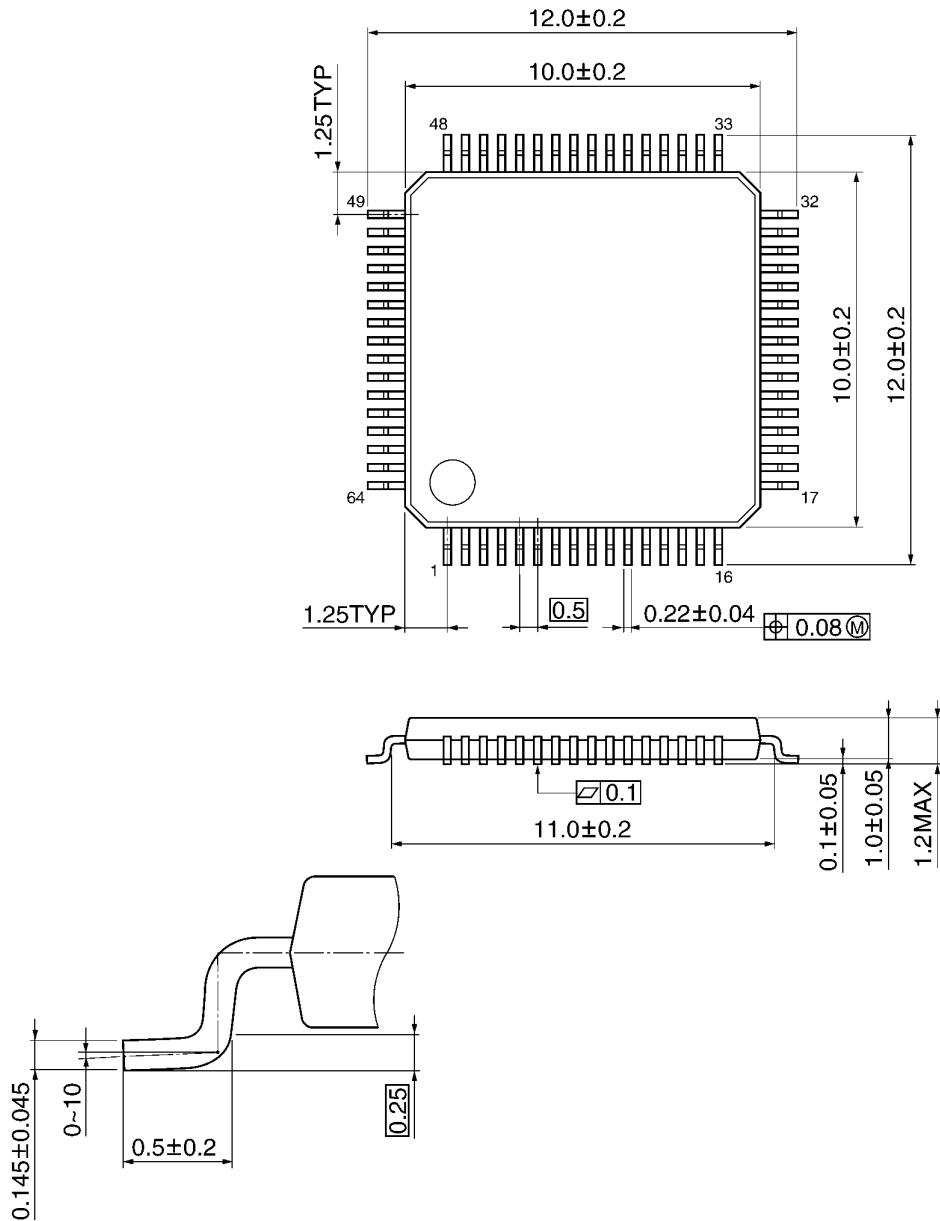

- Package: QFP-64 (0.5-mm/0.65-mm pitch, 1.4-mm thickness)

Note: Handle with care to prevent devices from deteriorating due to electrostatic discharge.

### Weight

LQFP64-P-1010-0.50E : 0.32 g ( typ.)

TQFP64-P-1010-0.50C : 0.26 g ( typ.)

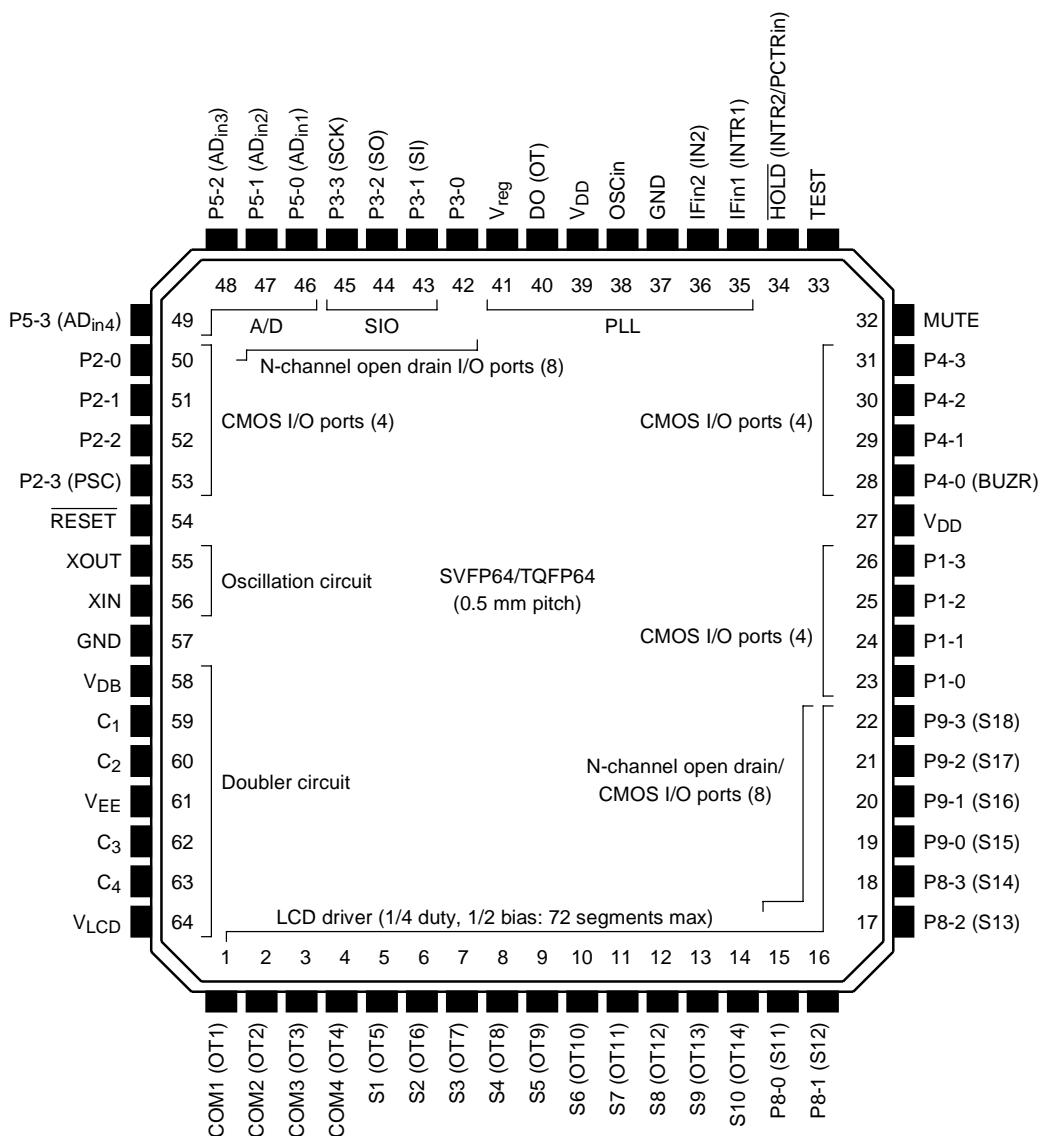

## Pin Assignment (top view)

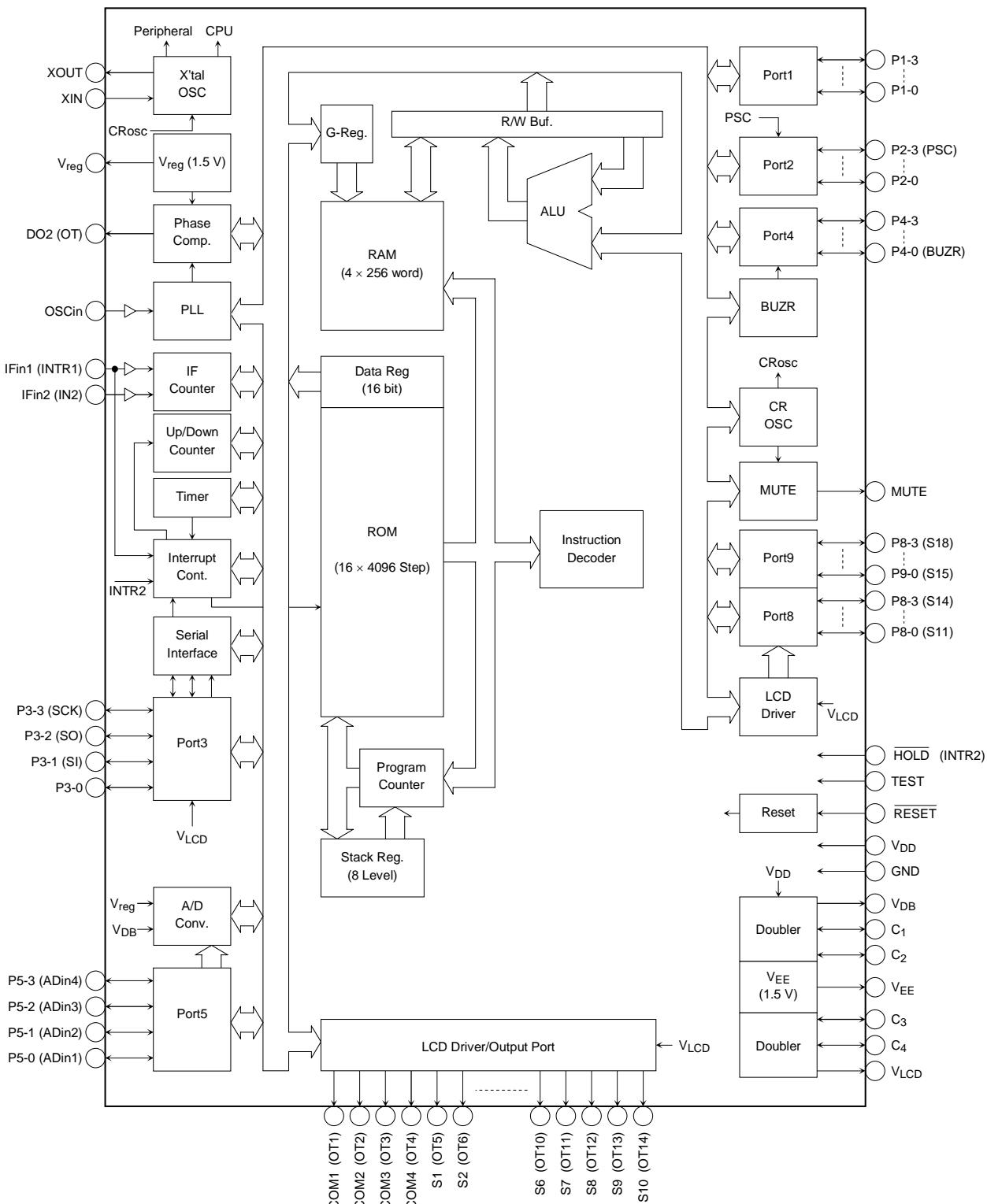

## Block Diagram

## Description of Pin Function

| Pin No. | Symbol            | Pin Name                          | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Remarks                                                                               |

|---------|-------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

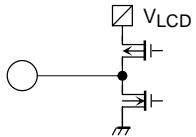

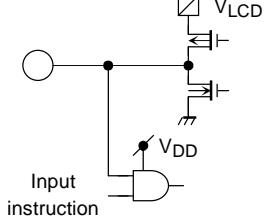

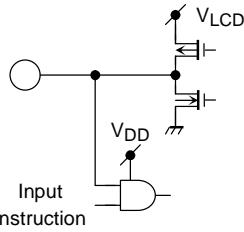

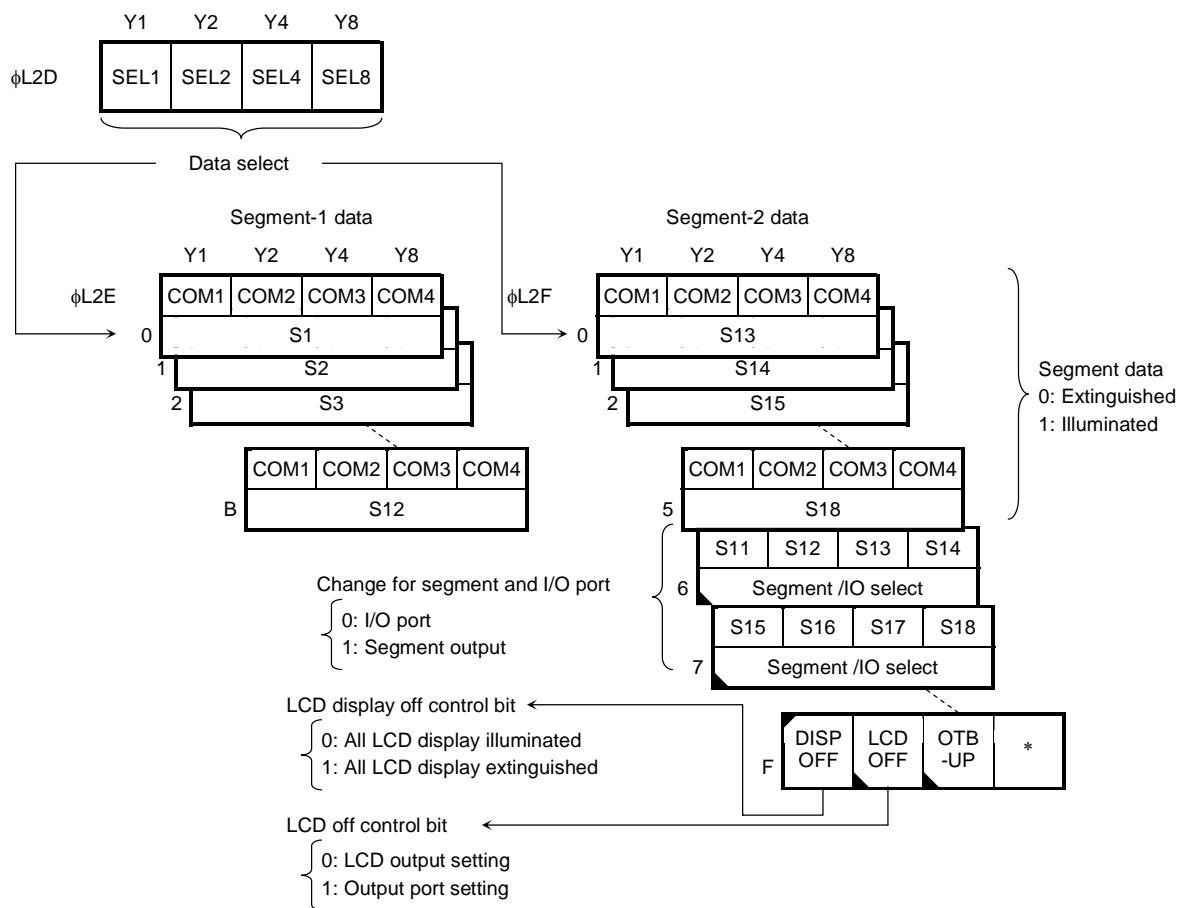

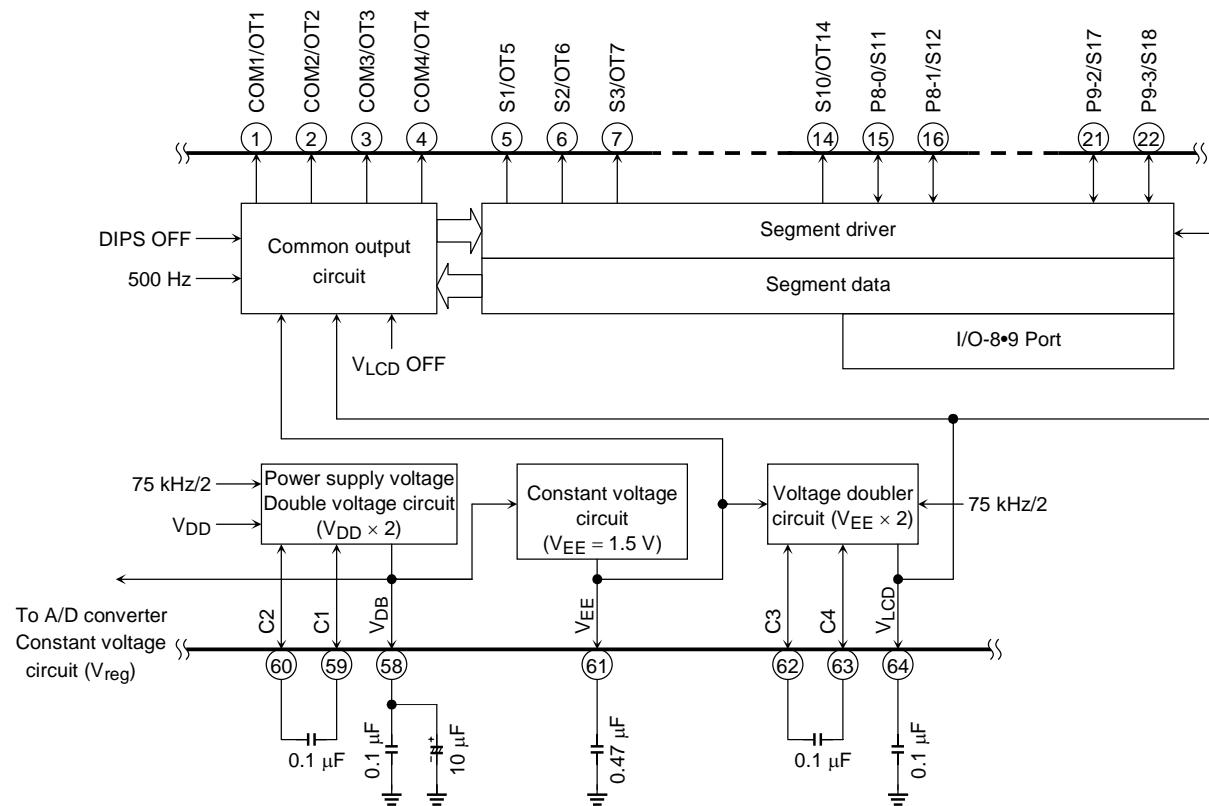

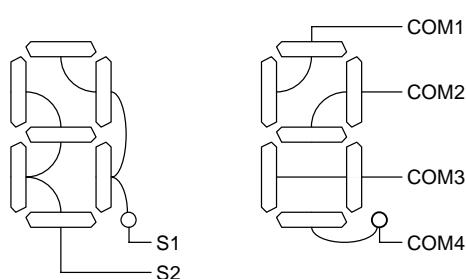

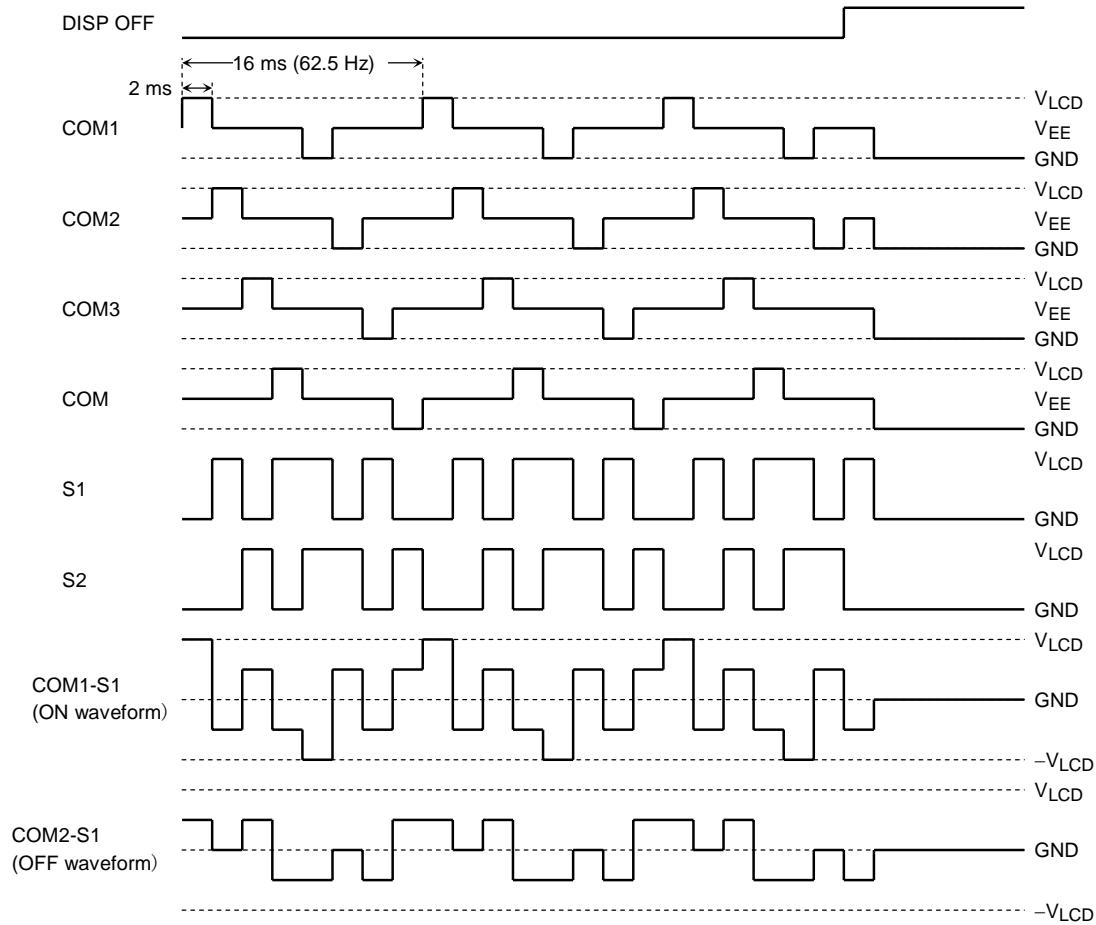

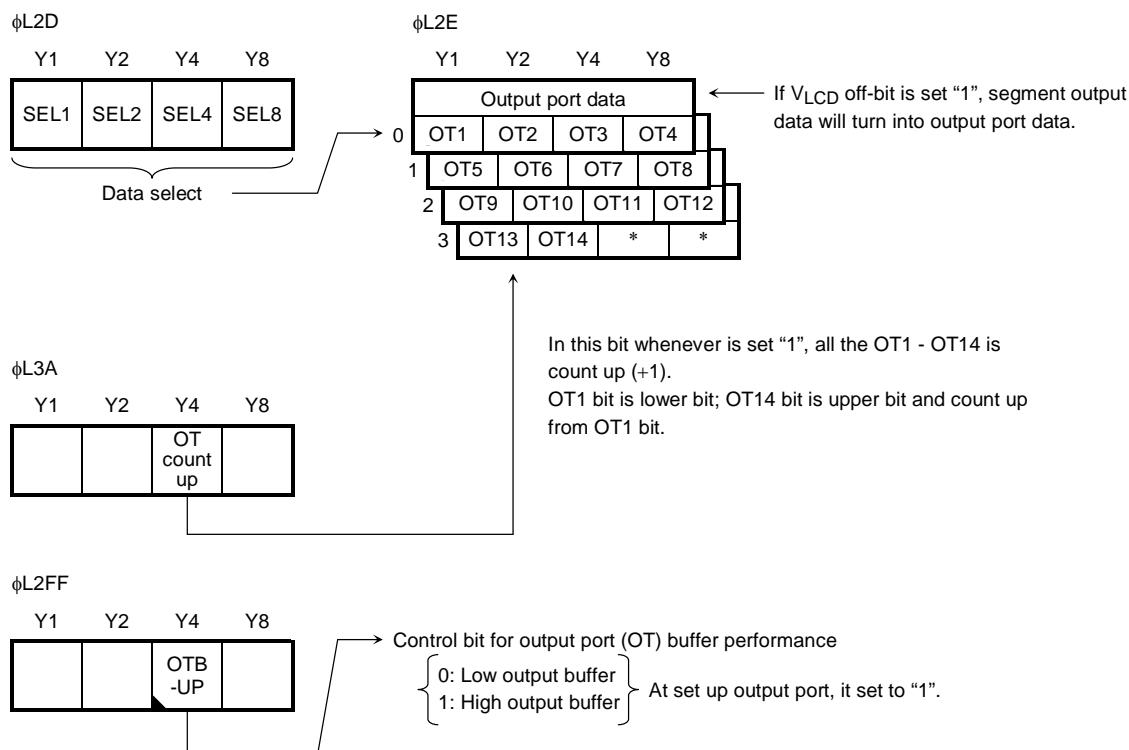

| 1       | COM1/OT1          | LCD common output/Output port     | Outputs common signals to LCD panels. Through a matrix with pins S1 to S18, a maximum of 72 segments can be displayed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 2       | COM2/OT2          |                                   | Three levels, $V_{LCD}$ , $VEE$ ( $1/2 V_{LCD}$ ), and GND, are output at 62.5 Hz every 2 ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                       |

| 3       | COM3/OT3          |                                   | $VEE$ is output after system reset and CLOCK STOP are released, and a common signal is output after the DISP OFF bit is set to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |

| 4       | COM4/OT4          |                                   | These pins can be programmed as output ports (Note 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                       |

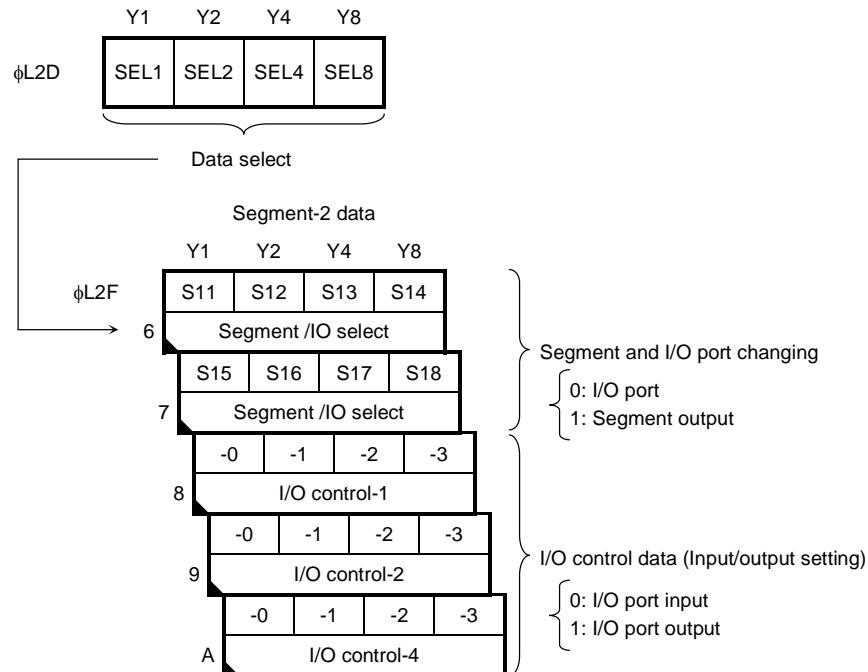

| 5~14    | S1/OT5~S10/OT14   | LCD segment output/Output port    | Segment signal output terminals for LCD panel. Together with COM1 to COM4, a matrix is formed that can display a maximum of 72 segments. $VEE$ is output after system reset and CLOCK STOP are released, and a common signal is output after the DISP OFF bit is set to "0".<br>All pins from S1 to S10 can be programmed as output ports (Note 1), and all pins from S11 to S18 as I/O ports, in units of pins.                                                                                                                                                                          |    |

| 15~22   | P8-0/S13~P9-3/S18 | LCD segment output/ I/O port 8, 9 | When the pins function as output ports, $V_{LCD}$ pin potential and GND potential are output to them. When the pins function as I/O ports, drain output is N-ch open. Because power is supplied from $V_{LCD}$ for the I/O ports, up to $V_{LCD}$ voltage (3 V) can be applied.<br>An instruction increments the data ports (OT1 to OT14) by 1 every time data are accessed. Therefore the ports can be used for external memory address signals, facilitating data access.<br>Note: After system reset, the output port pins are set to LCD output, the I/O port pins to I/O port input. |  |

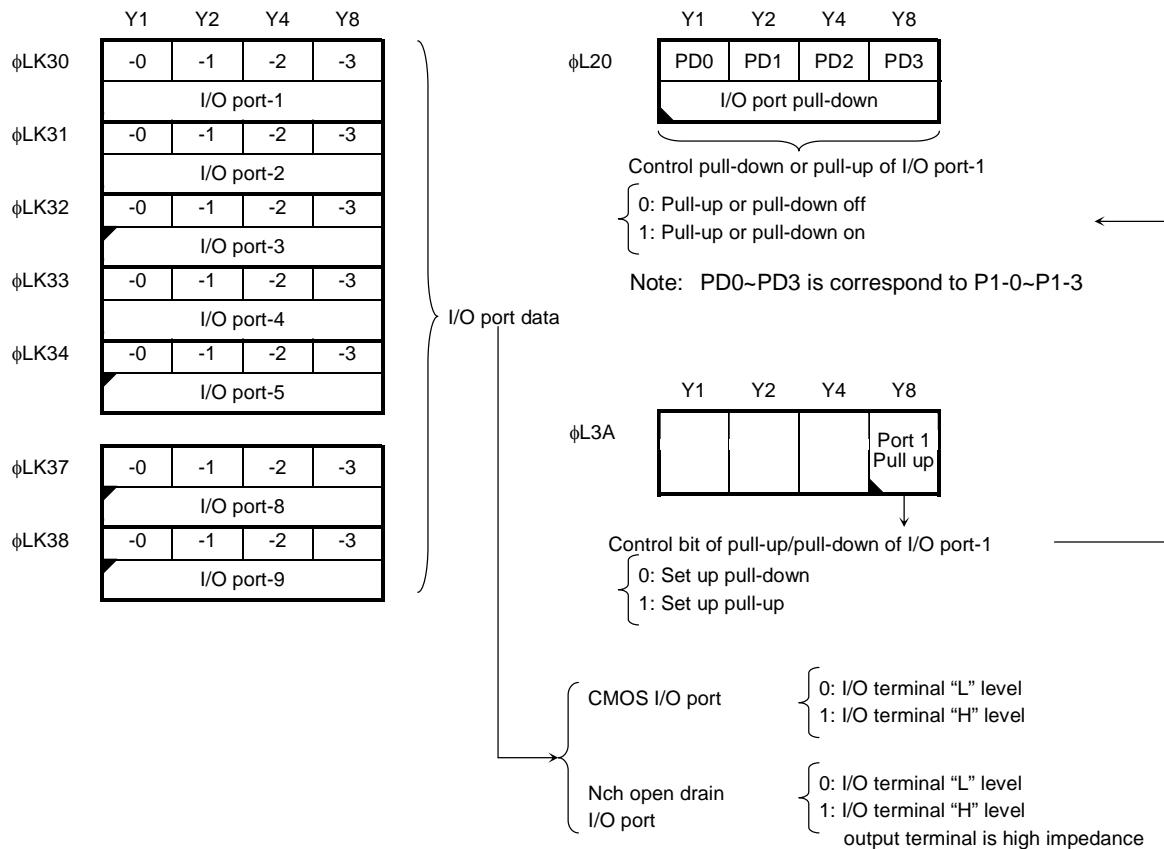

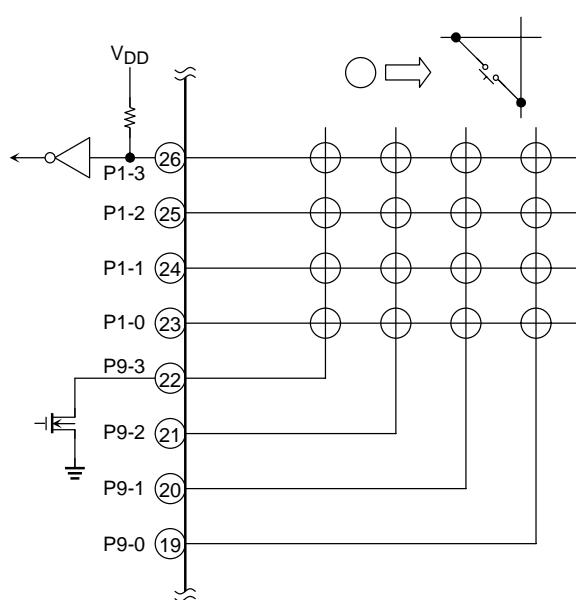

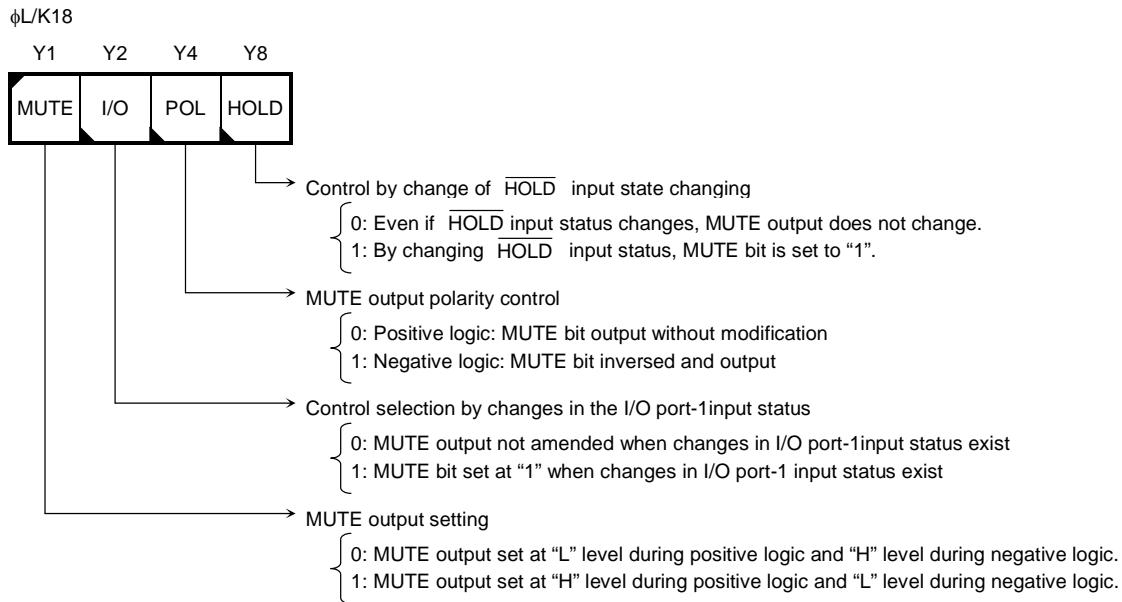

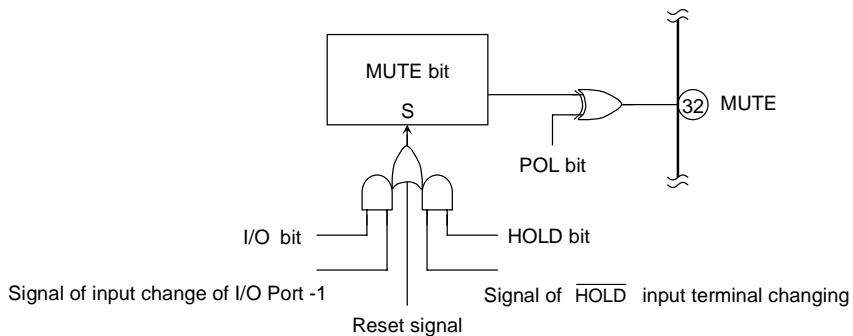

| 23~26   | P1-0~P1-3         | I/O port 1                        | The input and output of these 4-bit I/O ports can be programmed in 1-bit units.<br>These pins can be programmed to be pulled up or down. Thus, they can be used as key input pins.<br>By altering the input of I/O ports set to input, the CLOCK STOP mode or the WAIT mode can be released, and the MUTE bit of the MUTE pin can be set to "1".                                                                                                                                                                                                                                          |  |

Note 1: When the LCD pin is set as an output port, the "H" level output is the doubled voltage  $V_{LCD}$ . Therefore disconnect the voltage boosting capacitor and connect the  $V_{LCD}$  pin to the  $V_{DD}$  pin.

| Pin No. | Symbol                                 | Pin Name                                                                     | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Remarks                                                                                                                                                                          |

|---------|----------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

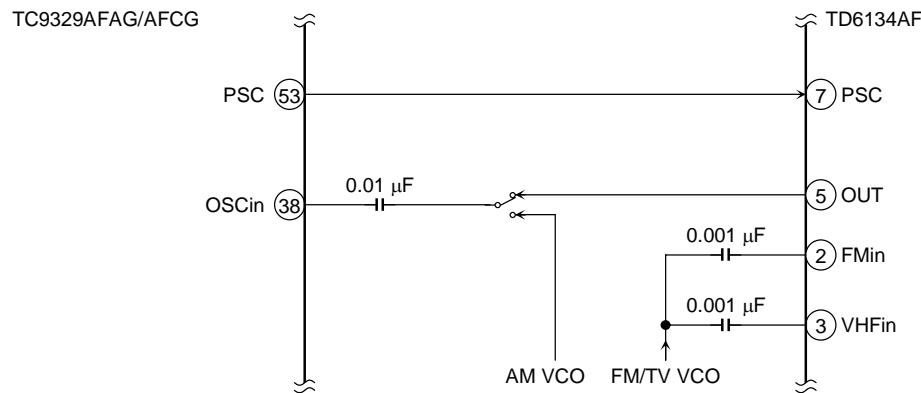

| 50~52   | P2-0~P2-2                              | I/O port 2                                                                   | The input and output of these 4-bit I/O ports can be programmed in 1-bit units. The P2-3 pin is also used as a PLL prescaler/PSC signal output pin. A PLL can be configured using an external prescaler. In such a case, set the pin to I/O port output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                               |

| 53      | P2-3/PSC                               | I/O port 2 /Prescaler /PSC output                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                  |

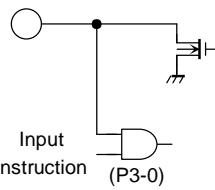

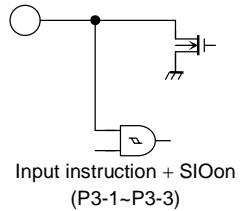

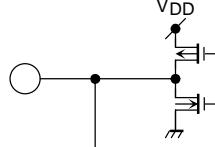

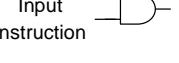

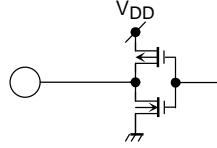

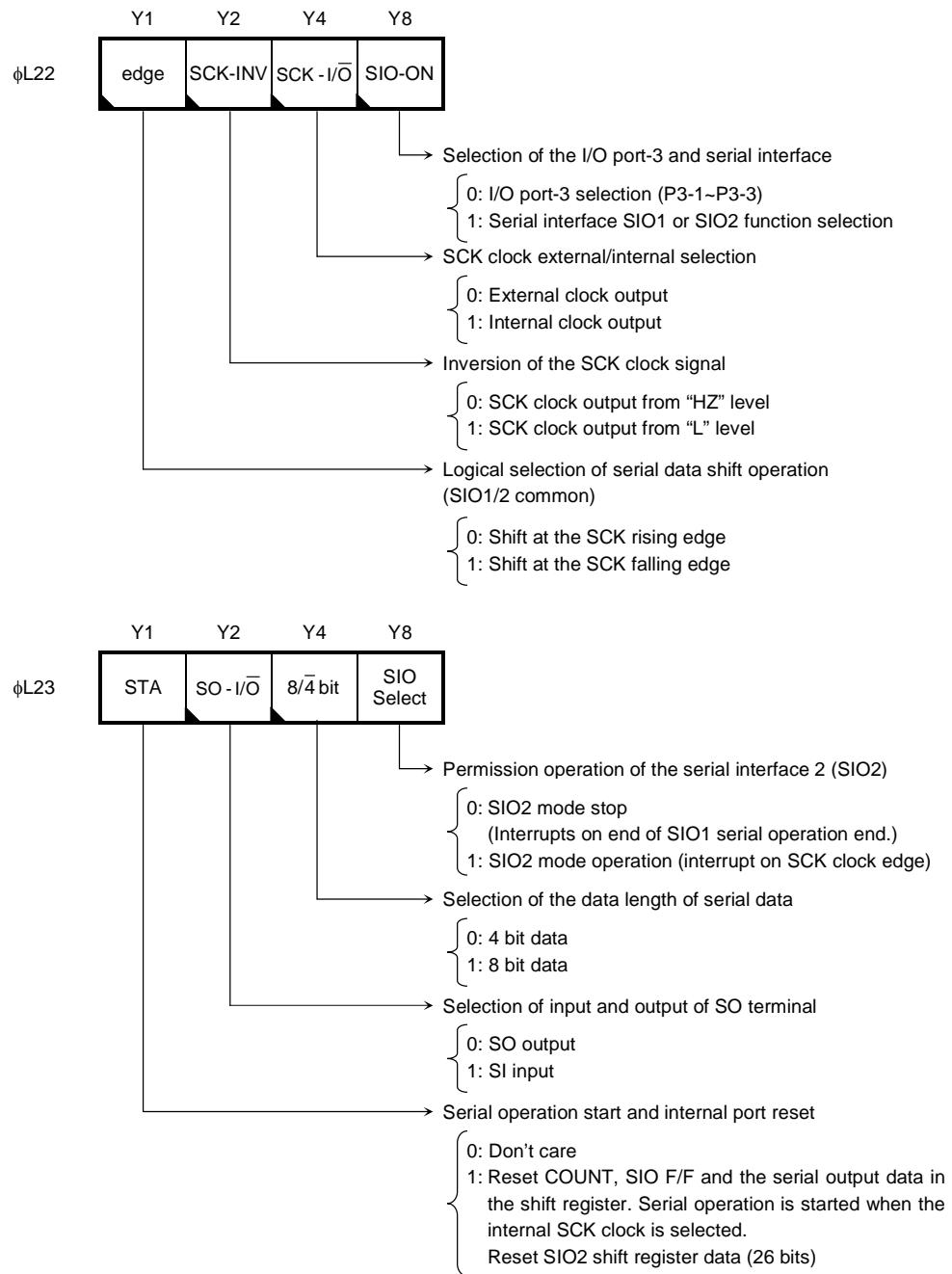

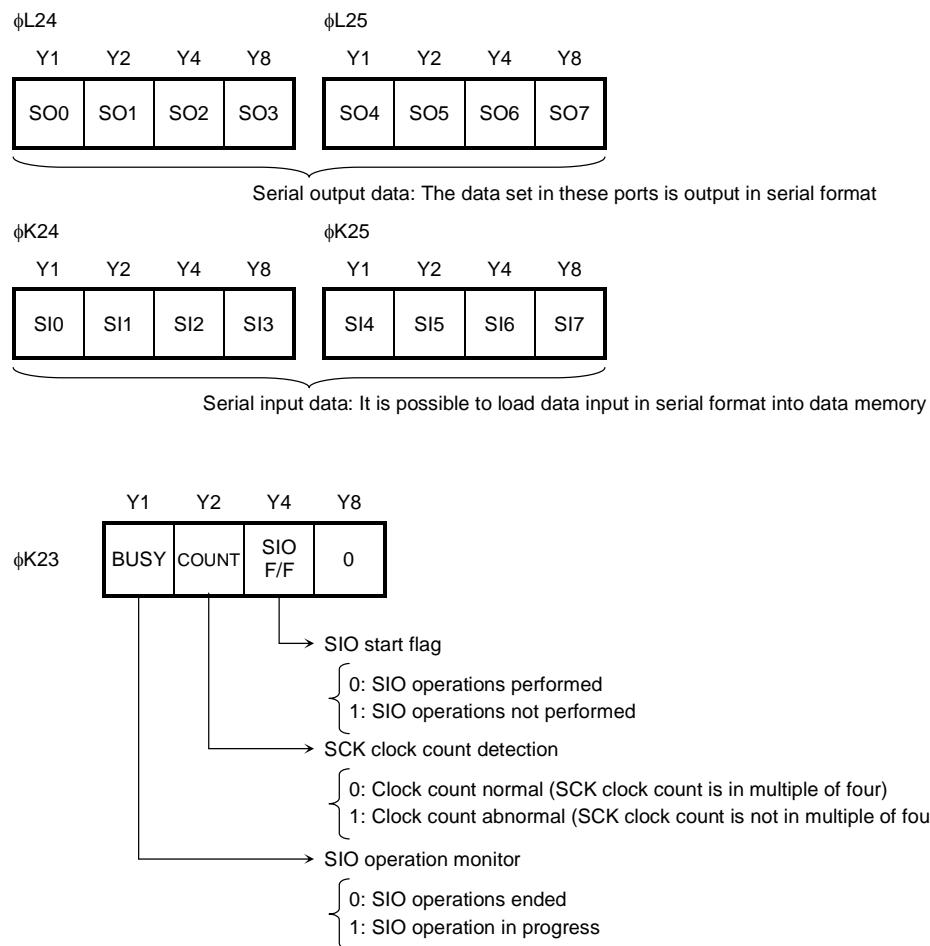

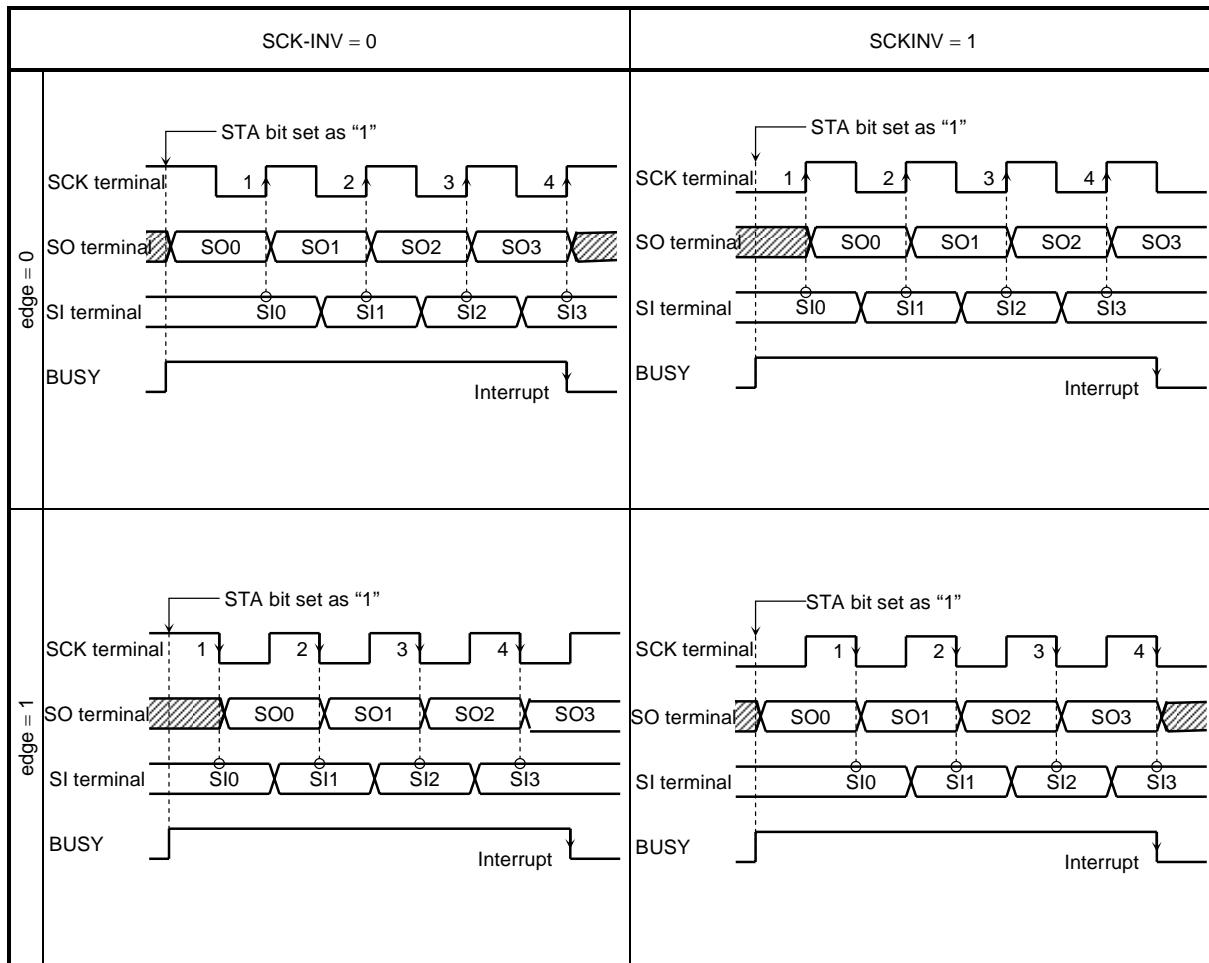

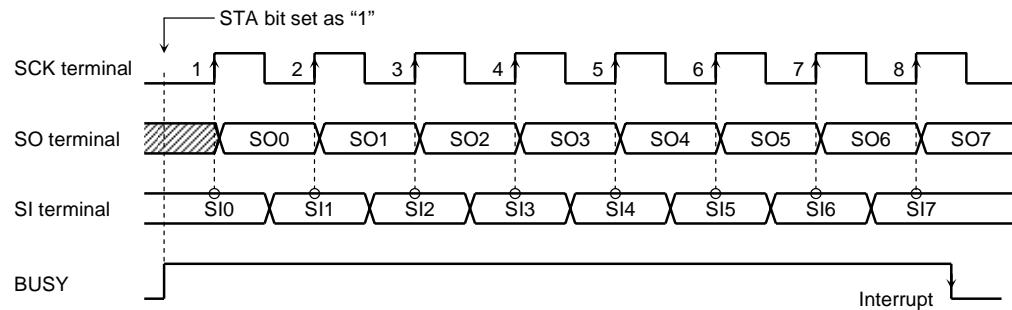

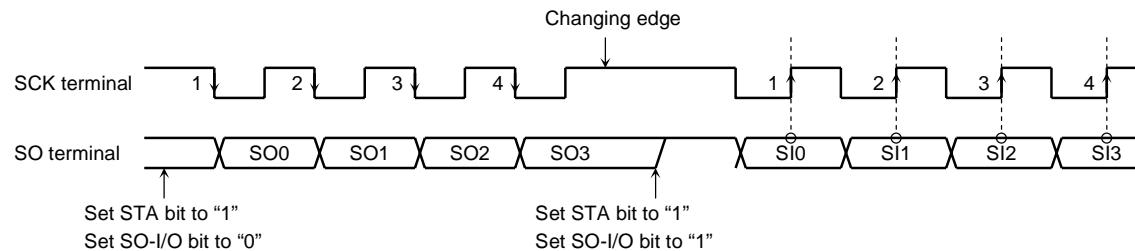

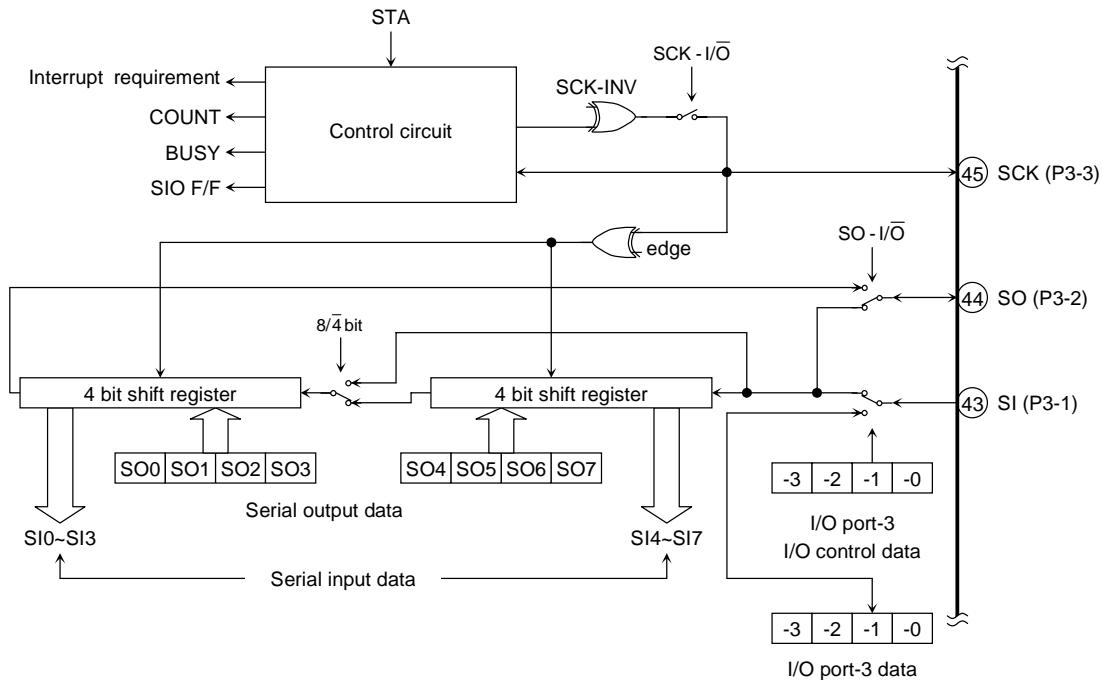

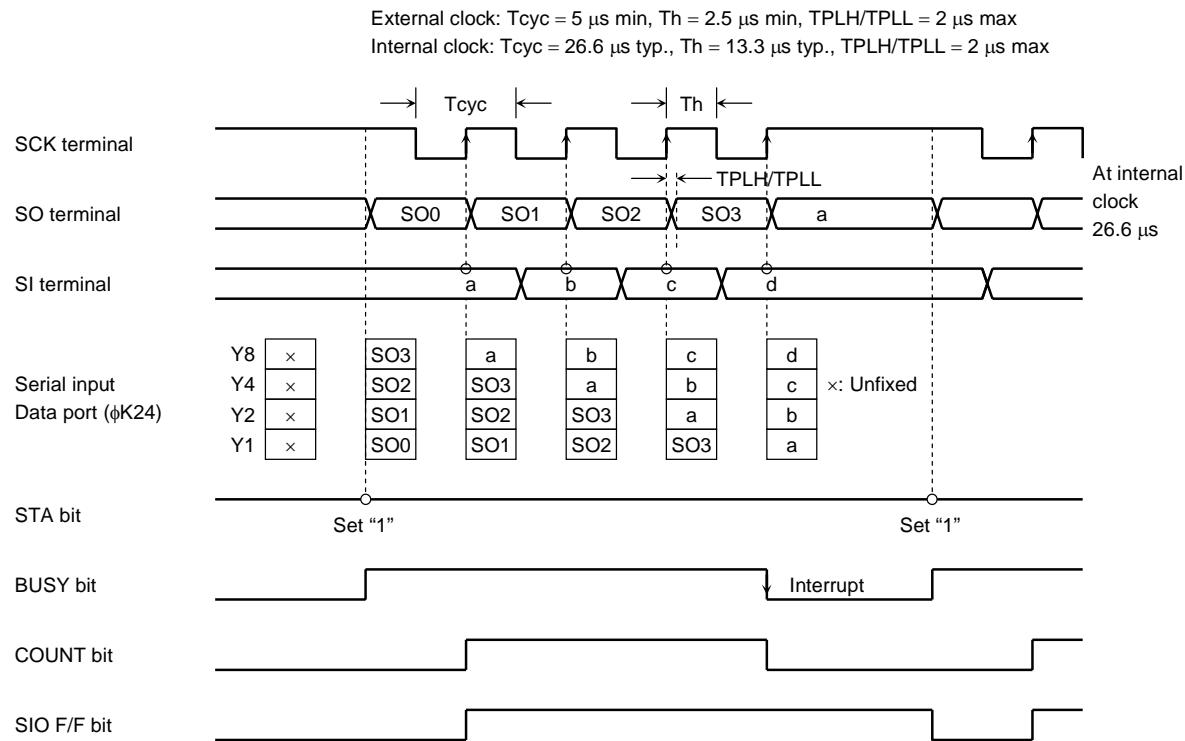

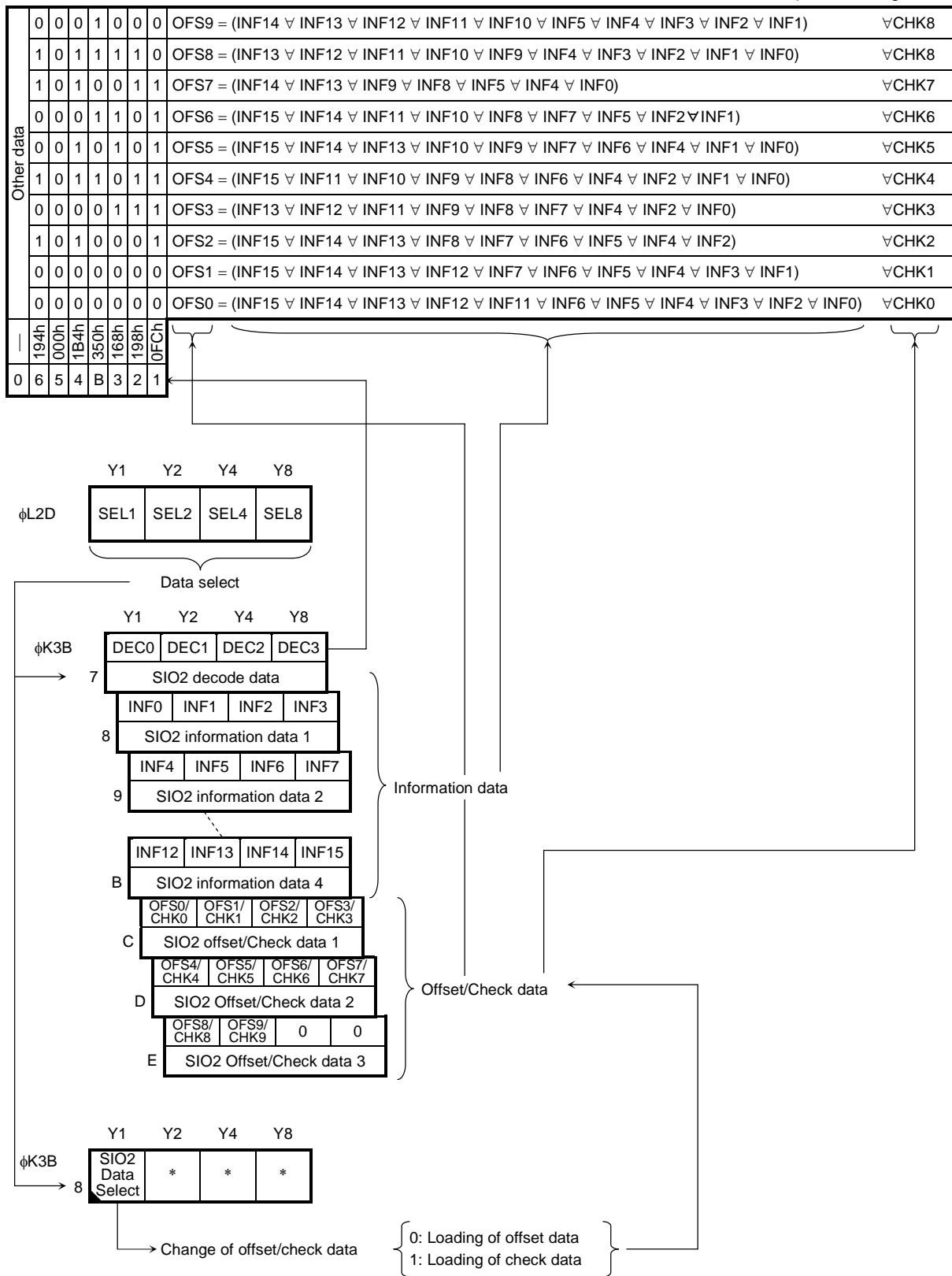

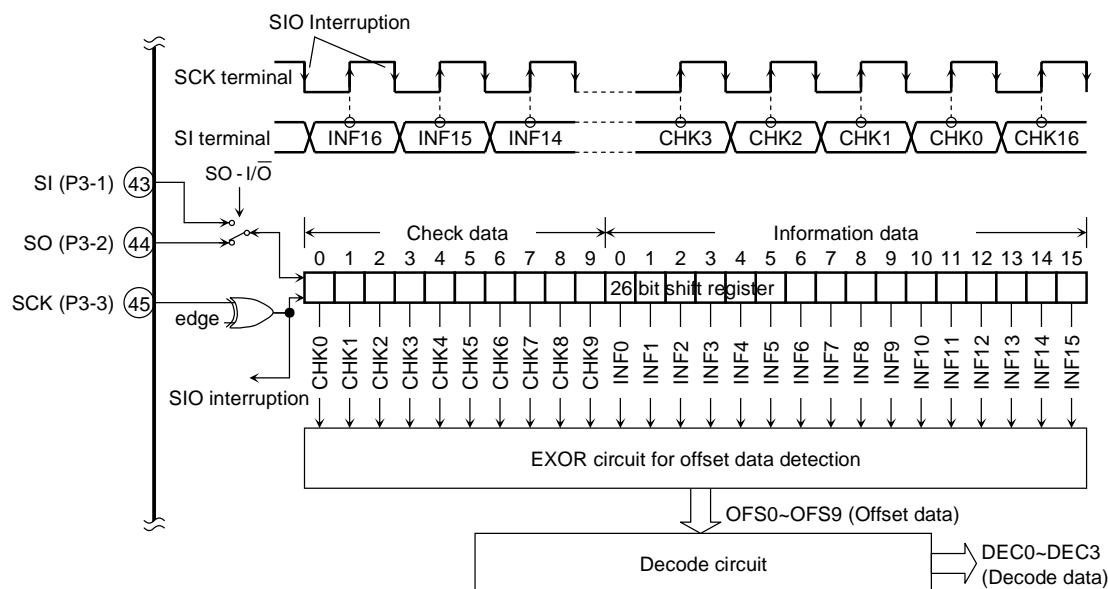

| 42~45   | P3-0<br>P3-1/SI<br>P3-2/SO<br>P3-3/SCK | I/O port 3<br>/Serial data input<br>/Serial data output<br>/Serial clock I/O | 4-bit I/O ports, allowing input and output to be programmed in 1-bit units. The I/O ports are N-ch open drain.<br><br>Up to 3.6 V can be input. Even at low voltage, N-ch high output current (2 mA typ.) can be obtained.<br><br>These pins also function as serial interface circuit (SIO) input/output pins.<br><br>There are two types of serial interface circuit: SIO1 allows 4 or 8-bit input/output and SIO2 allows 26-bit serial data input. SIO1 inputs data of SI pin serially with the edge of the clock of SCK pin, and outputs it to SO pin.<br><br>Internal (SCK = 37.5 kHz), external, or rising/falling shift can be selected as the clock (SCK) for serial operation. The SO pin can be switched to serial input (SI), facilitating LSI control and communication between controllers.<br><br>Setting "1" in the SIO2 bit sets the SCK pin to the SIO2 clock input and the SI/SO pin to SIO2 data input. A synchronization circuit is built-in for SIO2.<br><br>When SIO interrupts are enabled, an interrupt is generated after SIO execution or by SIO2 operating clock input and the program jumps to address 4.<br><br>All SIO inputs use built-in Schmitt circuits.<br><br>SIO and all controls are programmable. | <br><br> |

| 28      | P4-0/BUZR                              | I/O port 4 /Buzzer output                                                    | 4-bit I/O ports, allowing input and output to be programmed in 1-bit units.<br><br>The P4-0 pin is also used for buzzer output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             |

| 29~31   | P4-1~P4-3                              | I/O port 4                                                                   | The buzzer output can select 8 kinds of 0.625 to 3-kHz frequencies with 4 modes: continuous output, single-shot output, 10 Hz intermittent output, and 10 Hz intermittent at 1 Hz intervals output.<br><br>SIO, buzzer, and all associated controls can be programmed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                             |

| Pin No. | Symbol                                         | Pin Name                            | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Remarks                                                                              |

|---------|------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

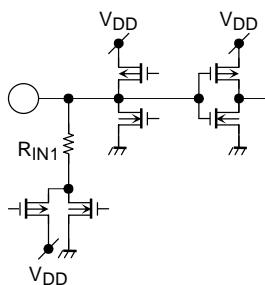

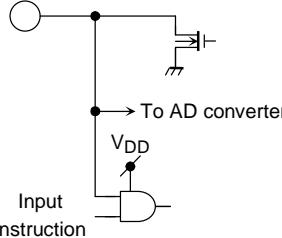

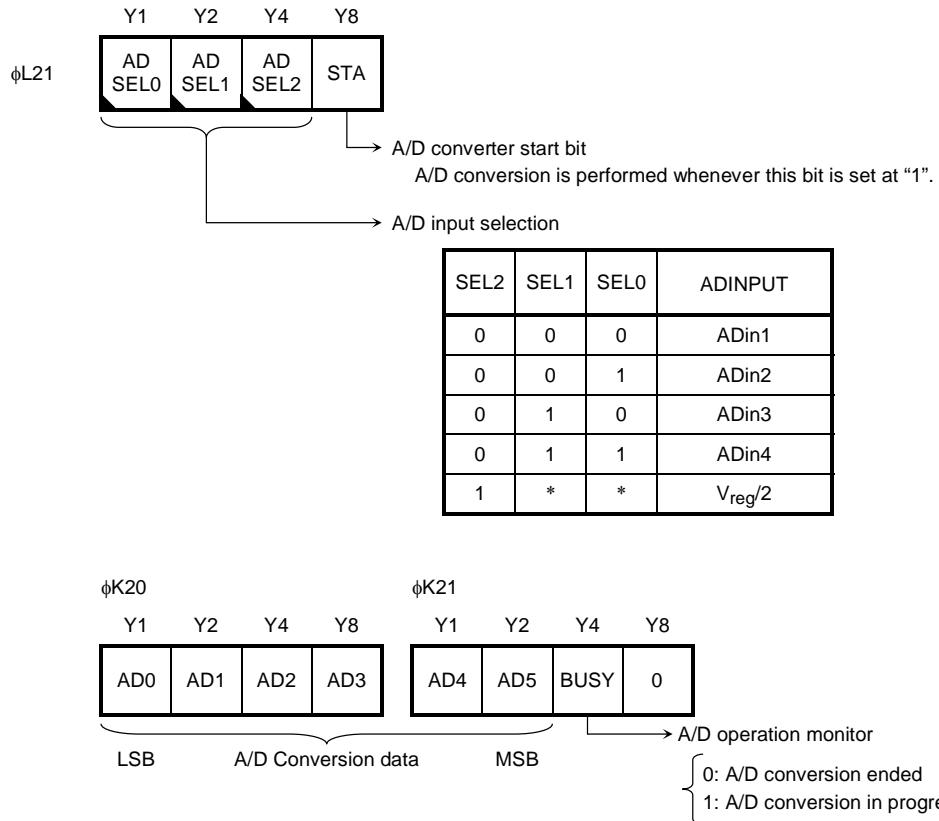

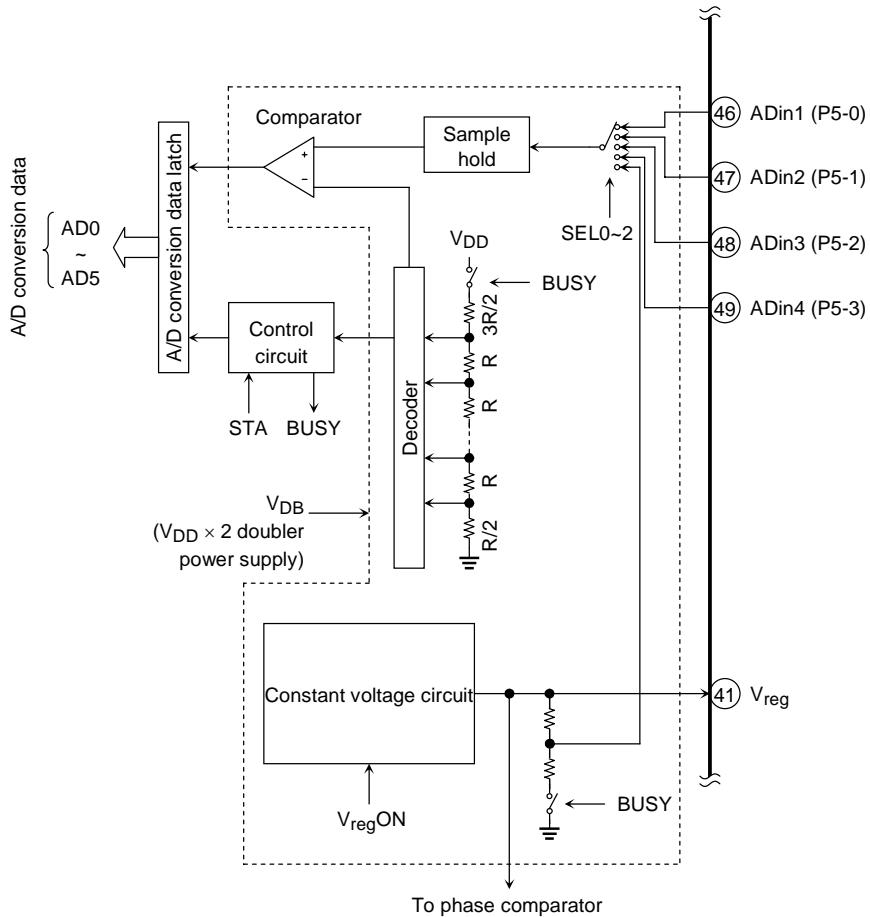

| 46~49   | P5-0/AD <sub>in1</sub> ~P5-3/AD <sub>in4</sub> | I/O port 5 /AD analog voltage input | <p>4-bit I/O ports, allowing input and output to be programmed in 1-bit units.</p> <p>Pins P5-0 to P5-3 can also be used for analog input to the built-in 6 bit, 4-channel AD converter.</p> <p>The conversion time of the built-in AD converter using the successive comparison method is 280 <math>\mu</math>s. The necessary pin can be programmed to AD analog input in 1-bit units. Up to the doubled voltage <math>V_{DB}</math> (<math>V_{DD} \times 2</math>) can be input as the AD input voltage.</p> <p>I/O ports are N-ch open drain output. Up to the <math>V_{DB}</math> voltage can be applied to the AD input pins.</p> <p>The AD converter and all associated controls are performed via software.</p> |   |

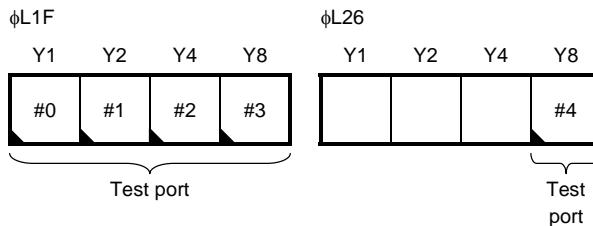

| 32      | MUTE                                           | Muting output port                  | <p>1-bit output port, normally used for muting control signal output.</p> <p>This pin can set the internal MUTE bit to "1" according to change in the input of I/O port 1 and HOLD. The MUTE bit output logic can be changed.</p> <p>The internal CR oscillator clock can be output depending on the contents of the test port.</p>                                                                                                                                                                                                                                                                                                                                                                                     |   |

| 33      | TEST                                           | Test mode control input             | <p>Input pin used for controlling TEST mode.</p> <p>"H" (high) level indicates TEST mode, while "L" (low) indicates normal operation.</p> <p>The pin is normally used at low level or in NC (no connection) state. (A pull-down resistor is built in.)</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Pin No. | Symbol                                         | Pin Name                                                                  | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Remarks                                                                             |

|---------|------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

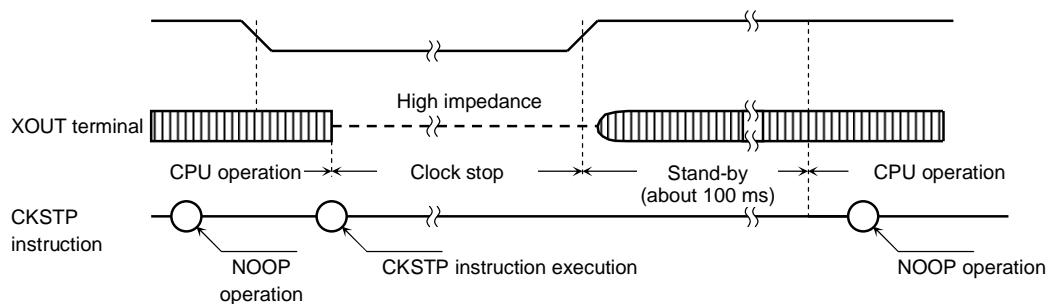

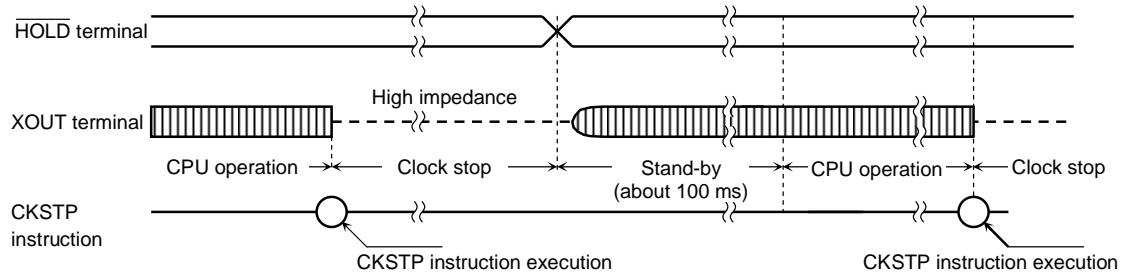

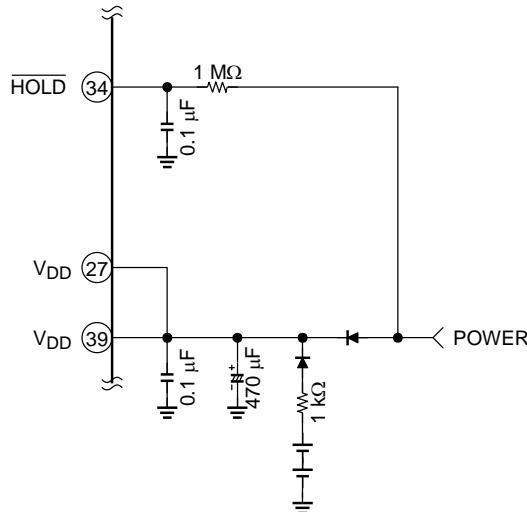

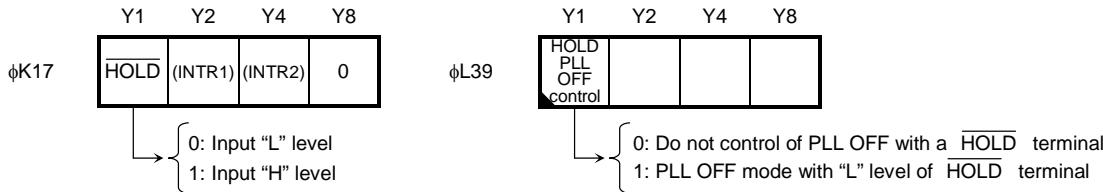

| 34      | <b>HOLD</b><br><b>/INTR2</b><br><b>/PCTRin</b> | Hold mode control input<br>/External interrupt input<br>/Plus count input | <p>Input pin for request/release hold mode. Normally, this pin is used to input radio mode selection signals or battery detection signals.</p> <p>Hold mode includes CLOCK STOP mode (stops crystal oscillation) and WAIT mode (halts CPU). Setting is implemented with the CKSTP instruction or the WAIT instruction.</p> <p>To request Clock Stop mode, either L-level detection on the HOLD pin or forced execution can be programmed. The mode is released by H-level detection on the HOLD pin or input change, respectively. Executing the CKSTP instruction stops the clock generator and the CPU, resulting in entry to memory backup state. In memory backup state, current dissipation becomes low (1 <math>\mu</math>A or less) and the display output/CMOS output ports automatically become L level and N-ch open drain output is set toOff.</p> <p>Regardless of this input state, Wait mode is executed in order to lower power dissipation. Either operation of the crystal oscillator only or CPU suspension can be programmed. For operation of the crystal oscillator only, all displays are at L level and other pins are in hold state. For CPU suspension, the CPU stops and all others retain their states. Wait mode is released by changing HOLD input.</p> <p>The P34 pin is also used for external interrupt input. When interrupts are enabled and a 13.3 to 26.7-<math>\mu</math>A pulse or longer is input to the pin, interrupt INTR1/2 is generated and the program jumps to address 1/2. Input logic or rising/falling edge can be selected for each input interrupt.</p> <p>The internal 8-bit timer clock input can be selected as input to the pins. When the count value reaches the specified value, an interrupt is generated (address 4).</p> <p>The pin is also used for input of an 8-bit pulse counter. Input rising/falling or upcount/downcount can be selected for the counter.</p> |  |

| Pin No.  | Symbol                   | Pin Name                                                                                  | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Remarks                                                                               |

|----------|--------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

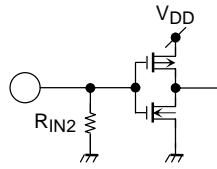

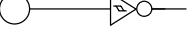

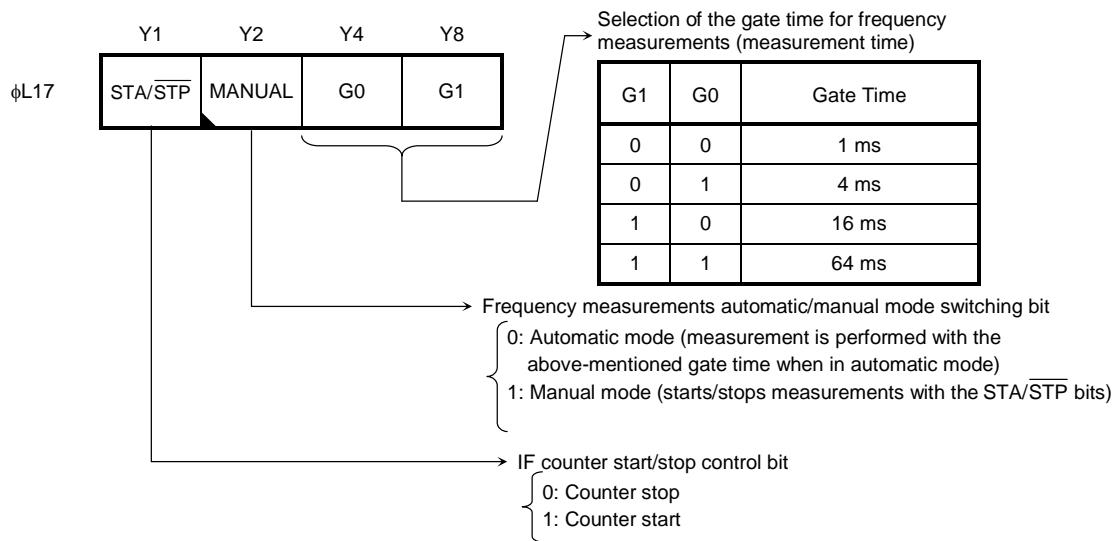

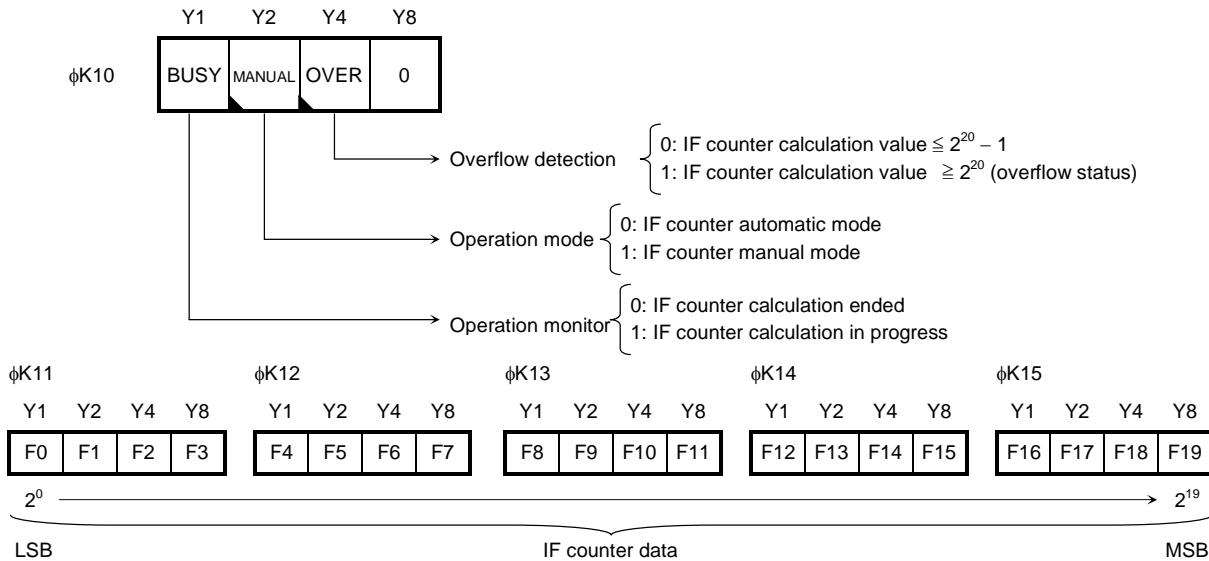

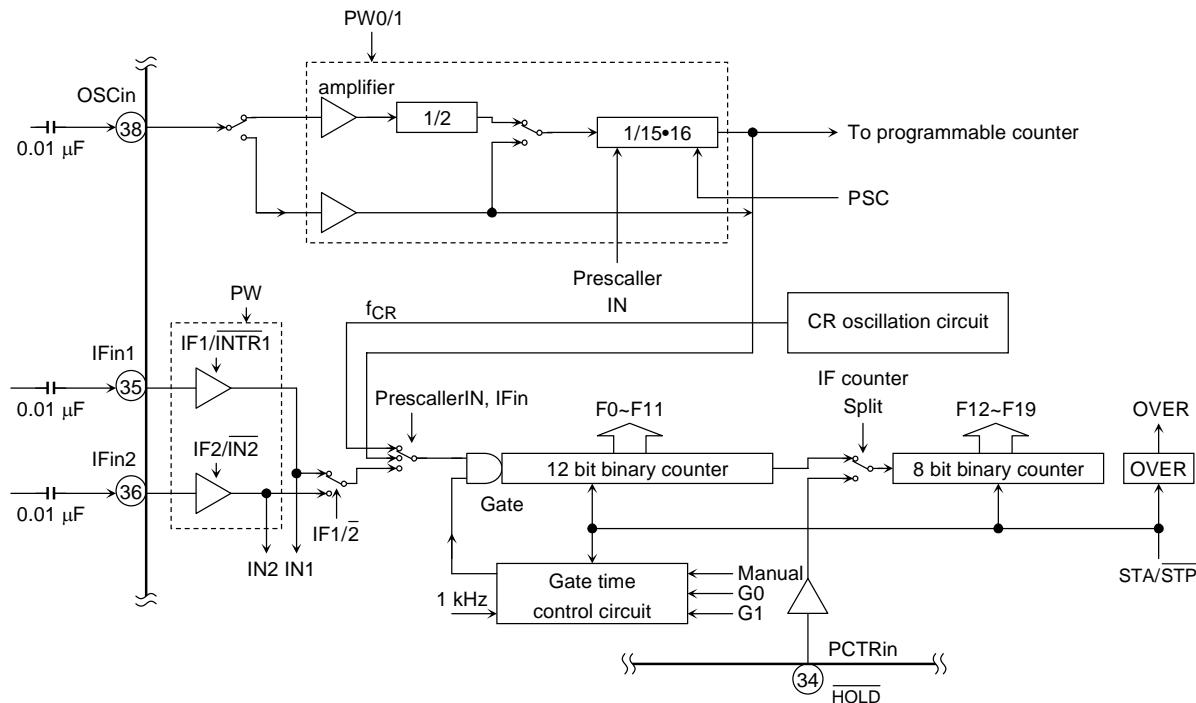

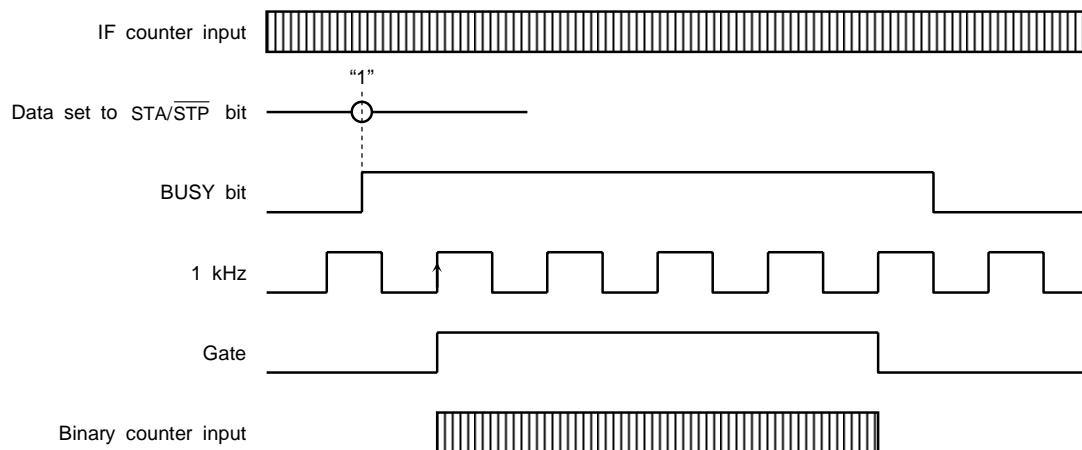

| 35<br>36 | IFin1/INTR1<br>IFin2/IN2 | IF signal 1 input<br>/External interrupt<br>input<br><br>IF signal 2 input<br>/Input port | <p>IF signal input pin for the IF counter to count the IF signals of the FM and AM bands and to detect the automatic stop position.</p> <p>The input frequency is between 0.3 to 12 MHz. A built-in input amp. and C coupling allow operation at low-level input.</p> <p>The IF counter is a 20-bit counter with optional gate times of 1, 4, 16 and 64 ms. 20 bits of data can be readily stored in memory. In Manual mode, gate On/Off or CR oscillator clock frequency count can be performed using an instruction.</p> <p>The input pin can be programmed for use as an input port (IN port). In this case, the pins are CMOS input. They can count input clocks using the IF counter.</p> <p>IFin1 also functions as an external interrupt input pin. When interrupts are enabled and a 13.3 to 26.7-<math>\mu</math>A pulse or longer is input to IFin1, an interrupt is generated and the program jumps to address 1. Input logic or rising/falling edge can be selected for the input interrupt. The internal 8-bit timer clock input can be selected as input to the pin. When the count value reaches the specified value, an interrupt is generated (address 4).</p> <p>Note: When a pin is set to IF input, the input is at high impedance in PLL Off mode or if the pins are not used for input.</p> |    |

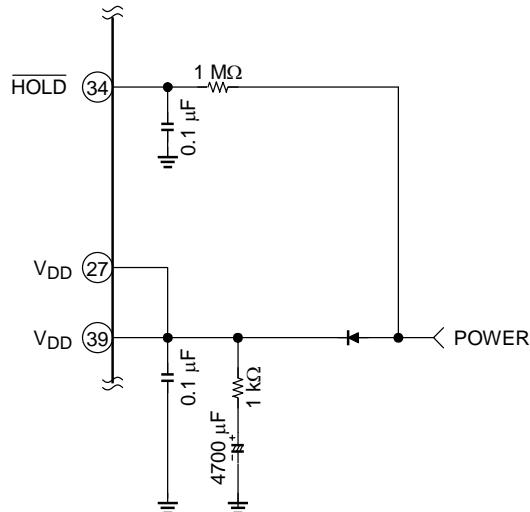

| 27, 39   | V <sub>DD</sub>          | Power-supply pins                                                                         | <p>Pins to which power is applied.</p> <p>Normally, V<sub>DD</sub> = 0.9~1.8 V is applied.</p> <p>In backup state (at execution of the CKSTP instruction), current dissipation drops (1 <math>\mu</math>A or less) and the power supply voltage can be reduced to 0.75 V.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 37, 57   | GND                      |                                                                                           | <p>Note: To operate the power on reset, the power supply should start up in 10~100 ms.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Pin No. | Symbol           | Pin Name                                 | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Remarks                                                                               |

|---------|------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

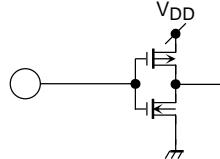

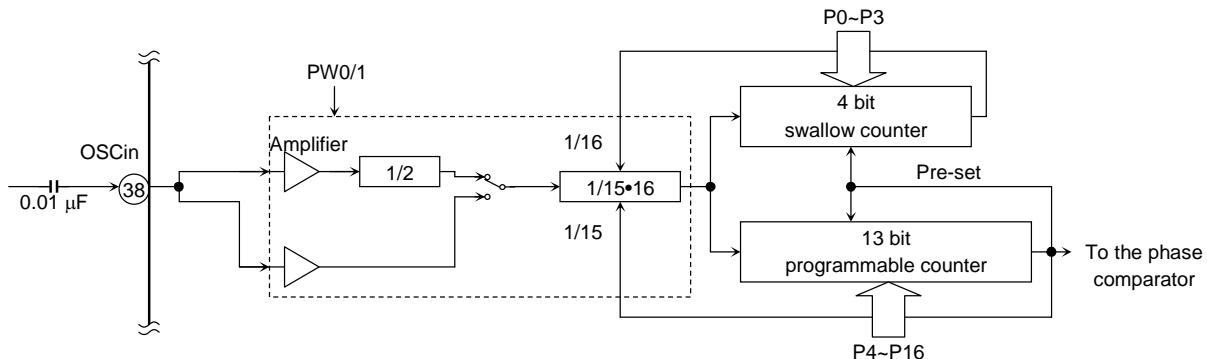

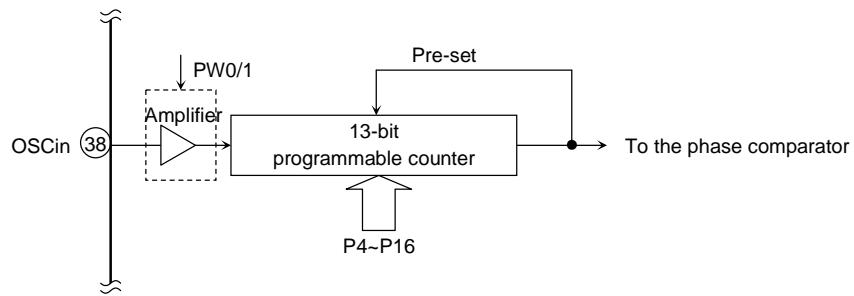

| 38      | OSCin            | local oscillation signal input           | <p>For FM input, mode can be switched between 1/2 + Pulse Swallow VHF and FM mode. For AM input, mode can be switched between Pulse Swallow (HF) and Direct Dividing (LF) mode.</p> <p>Normally, local oscillation output (Voltage-Controlled Oscillator: VCO output) of 80 to 230 MHz is input in VHF mode; 60 to 130 MHz in FM mode; 1 to 30 MHz in HF mode; 0.5 to 8 MHz in LF mode.</p> <p>A PLL can be configured using an external prescaler. In such a case, set the pin to LF, and connect the prescaler divider output to the OSCin input pin and the PSC input to the P2-3 (PSC) output pin.</p> <p>With an input amp incorporated, capacitive-coupling, small-amplitude operation is supported.</p> <p>Note: The input is at high impedance in PLL Off mode.</p> |    |

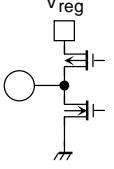

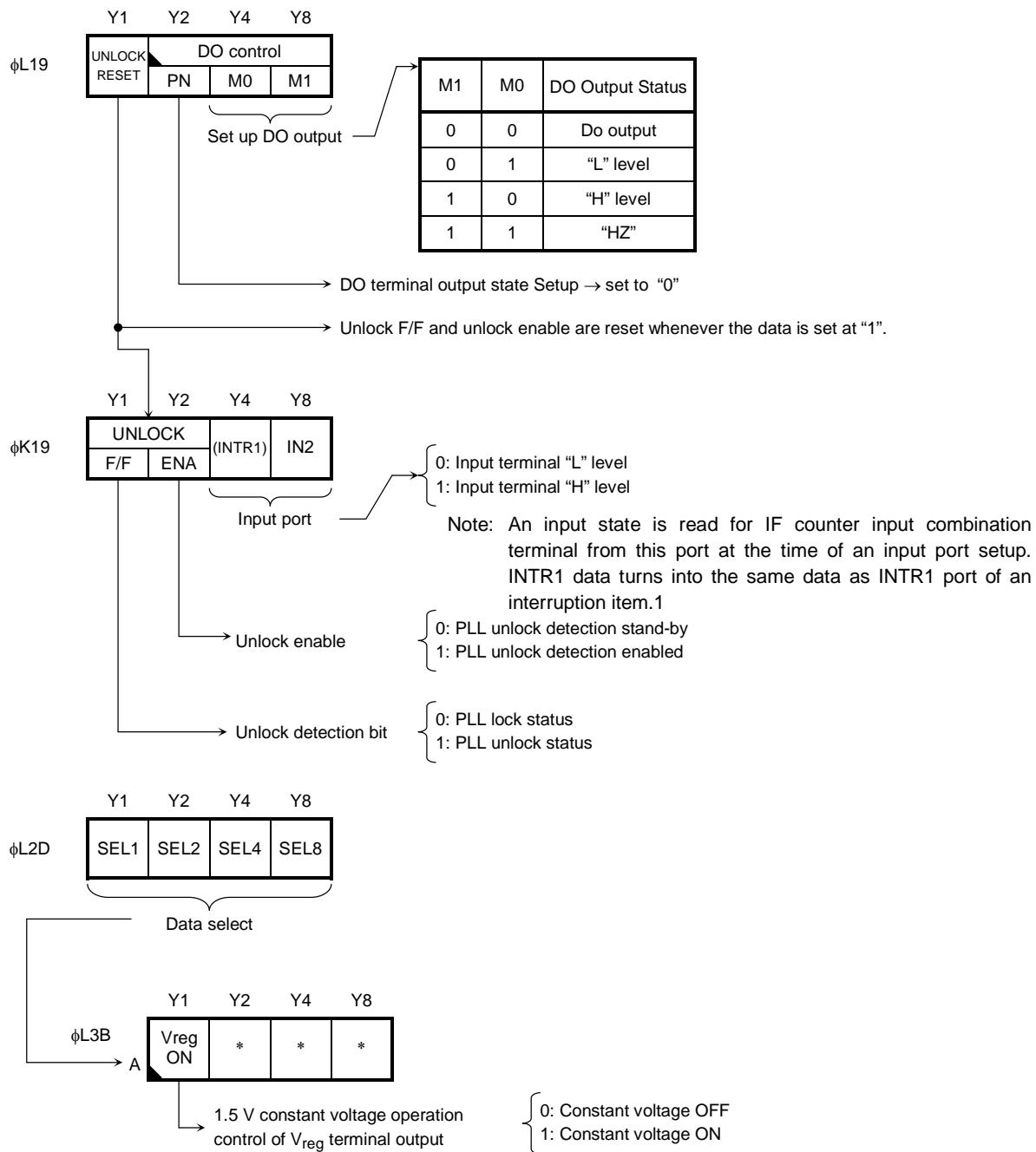

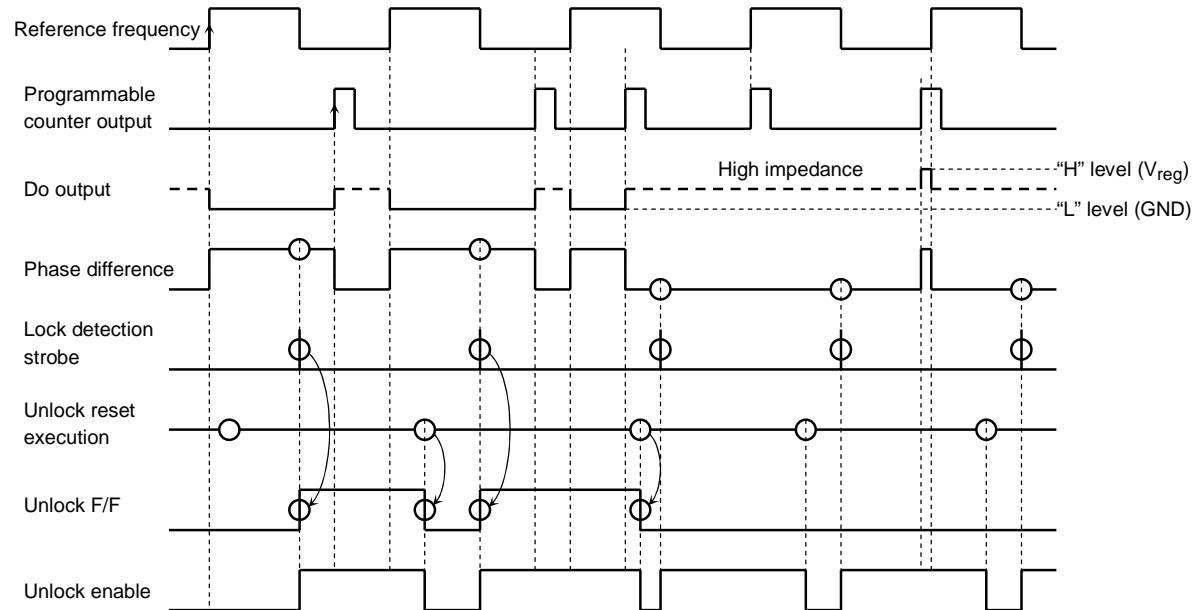

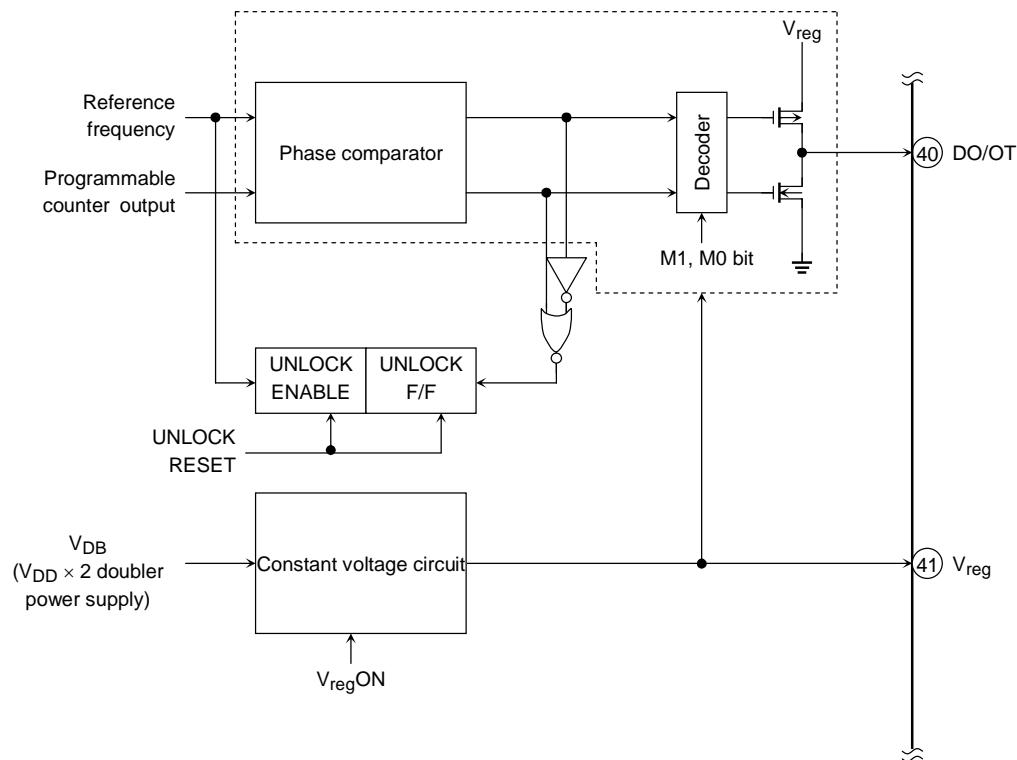

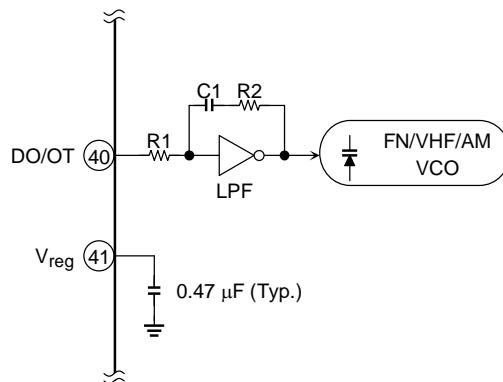

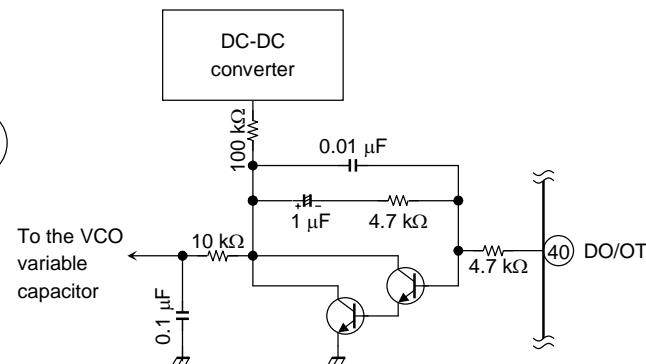

| 40      | DO/OT            | Phase comparator output/output port      | <p>PLL phase comparator output pins.</p> <p>Tristate output. When the program counter divider output is higher than the reference frequency, H level is output; when lower, L level; and when they match, high impedance. For the phase comparator power supply, a 1.5-V constant voltage supply (V<sub>reg</sub> pin) is used. Even if the power supply voltage drops, a stable PLL can be configured.</p> <p>The DO/OT pin can be programmed to high impedance or as an output port (OT).</p> <p>Note: For tristate output, the H-level output uses a constant voltage supply. When H-level output current is required, Toshiba recommend using an external power supply.</p>                                                                                             |   |

| 41      | V <sub>reg</sub> | Phase comparator constant voltage supply | <p>Phase comparator constant voltage supply.</p> <p>When the phase comparator output is tristate output, a constant voltage supply of 1.5 V (typ.) is output to the pin. For this output, connect a stabilizing capacitor (0.47 <math>\mu</math>F typ.). Constant voltage On/Off can be programmed.</p> <p>Because half the voltage potential can be switched to AD converter A/D input, it can be used to detect how much battery remains.</p> <p>At PLL operation, the constant voltage is used for H level phase comparator output. Thus, when H level output current is required, Toshiba recommend using an external power supply. Externally apply 1.8 to 3.6 V to the pin.</p>                                                                                       |  |

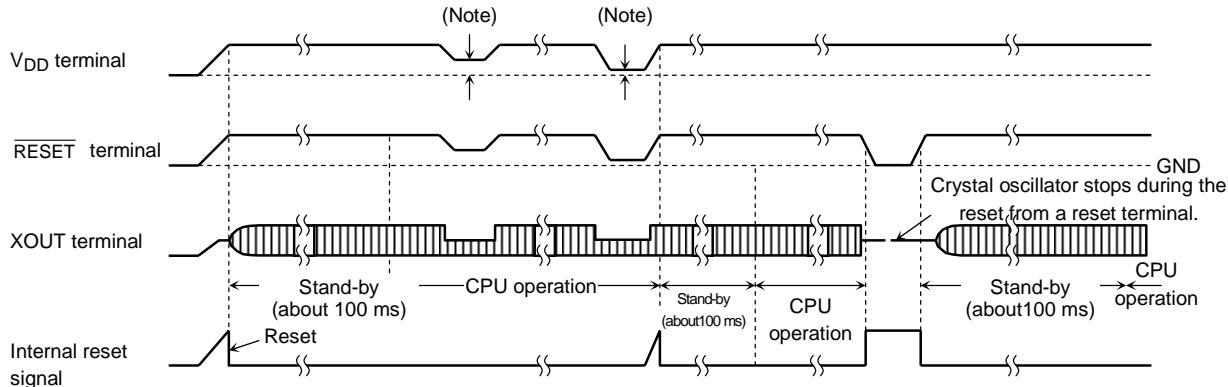

| 54      | <u>RESET</u>     | Reset input                              | <p>Input pin for system reset signals.</p> <p><u>RESET</u> takes place at low level; at high level, the program starts from address "0".</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Pin No. | Symbol | Pin Name                             | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Remarks                                                                             |

|---------|--------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

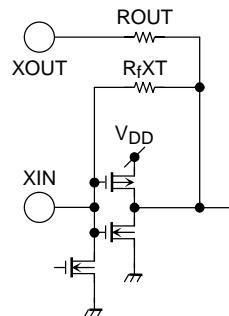

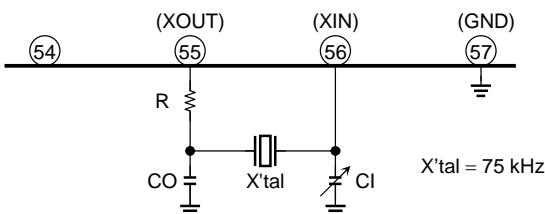

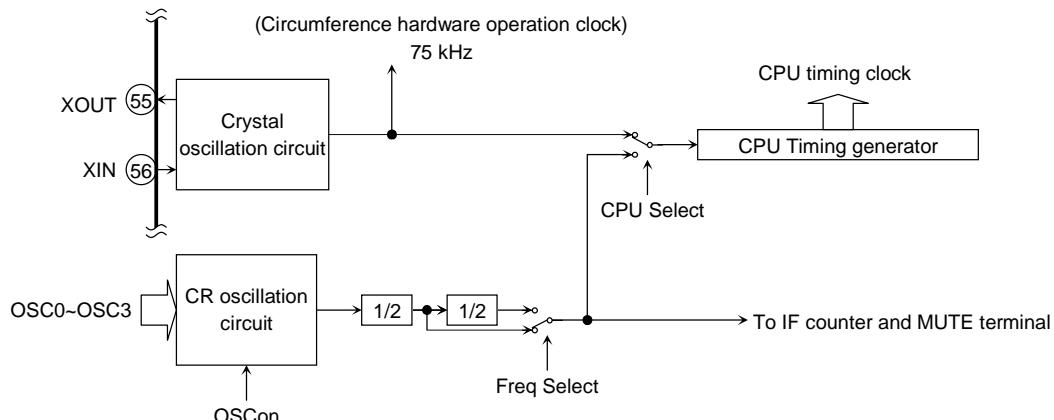

| 55      | XOUT   | Crystal oscillator pin               | Crystal oscillator pins.<br>A reference 75 kHz crystal resonator is connected to the XIN and XOUT pins.<br>The oscillator stops oscillating during CKSTP instruction execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 56      | XIN    |                                      | The VXT pin is the power supply for the crystal oscillator. A stabilizing capacitor (0.47 $\mu$ F typ.) is connected.<br>Usually, the clock of a crystal oscillator is used for the clock for peripheral equipment. Through programming, the built-in VCO can be changed to CPU and CPU only operation can be accelerated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                     |

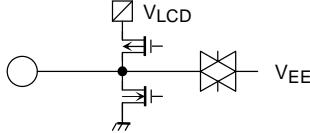

| 58      | VDB    | Voltage doubler boosting output pins | Voltage doubler boosting output pins.<br>The VDB pin doubles the VDD pin voltage using the voltage doubler boosting capacitor between C1 and C2. The doubled voltage is used for the AD converter and constant voltage circuit (V <sub>reg</sub> , V <sub>EE</sub> ) power supply.<br>The VEE pin supplies a constant voltage of 1.5 V from the VDB voltage. The voltage is doubled (to 3 V) using the voltage doubler boosting capacitor between C3 and C4. The doubled voltage is then supplied to the VLCD pin. The VEE potential and the VLCD potential are used to drive the LCD.<br>Connect a stabilizing capacitor between the VDB pin and GND (0.1 $\mu$ F, 10 $\mu$ F typ.), and between the VLCD pin and GND (0.1 $\mu$ F typ.). Connect a voltage doubler boosting capacitor (0.1 $\mu$ F typ.) between C1 and C2, and between C3 and C4. (Note) |  |

| 59      | C1     |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                     |

| 60      | C2     |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                     |

| 61      | VEE    |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                     |

| 62      | C3     |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                     |

| 63      | C4     |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                     |

| 64      | VLCD   |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                     |

Note: When the LCD pin is set as an output port, the "H" level output is the doubled voltage VLCD. Therefore disconnect the voltage boosting capacitor and connect the VLCD pin to the VDD pin.

## Description of Operations

### ○ CPU

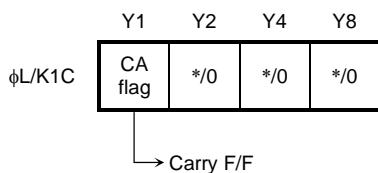

The CPU consists of a program counter, a stack register, an ALU, a program memory, a data memory, a G-register, a data register, a DAL address register, a carry F/F, a judgment circuit, and an interruption circuit.

#### 1. Program Counter (PC)

The program counter consists of a 14-bit binary up-counter and addresses the program memory (ROM). The counter is cleared when the system is reset and the programs start from the 0 address.

Under normal conditions, the counter is increased in increments of one whenever an instruction is executed, but the address specified in the instruction operand is loaded when a JUMP instruction or CALL instruction is executed.

Also, when an instruction that is equipped with the skip function (AIS, SLTI, TMT, RNS instructions, etc.) is executed, and the result of this includes a skip condition, the program counter is increased in increments of two and the subsequent instruction is skipped. Furthermore, if interruption is received, the vector address corresponding to each interruption is loaded.

Note: Addresses 0000H-0FFFH are reserved for the program memory. For this reason, access to addresses outside this range is prohibited.

| Instruction                              | Contents of Program Counter (PC)        |      |      |      |                                  |     |                                  |     |     |                                    |     |     |     |     |   |  |  |  |  |  |  |  |  |

|------------------------------------------|-----------------------------------------|------|------|------|----------------------------------|-----|----------------------------------|-----|-----|------------------------------------|-----|-----|-----|-----|---|--|--|--|--|--|--|--|--|

|                                          | PC13                                    | PC12 | PC11 | PC10 | PC9                              | PC8 | PC7                              | PC6 | PC5 | PC4                                | PC3 | PC2 | PC1 | PC0 |   |  |  |  |  |  |  |  |  |

| JUMP ADDR1                               | ← Operand of instruction (ADDR1) →      |      |      |      |                                  |     |                                  |     |     |                                    |     |     |     |     |   |  |  |  |  |  |  |  |  |

| JUMP ADDR2                               | 0                                       | 0    | 0    | ←    | Operand of instruction (ADDR2) → |     |                                  |     |     |                                    |     |     |     |     |   |  |  |  |  |  |  |  |  |

| Power on reset<br>RESET by reset pin     | 0                                       | 0    | 0    | 0    | 0                                | ←   | Operand of instruction (ADDR3) → |     |     | Contents of general register (r) → |     |     |     |     |   |  |  |  |  |  |  |  |  |

| DAL (DA)<br>(DAL bit = 1)                | ← DAL address register (DA) →           |      |      |      |                                  |     |                                  |     |     |                                    |     |     |     |     |   |  |  |  |  |  |  |  |  |

| RN, RNS, RNI                             | ← Contents of stack register →          |      |      |      |                                  |     |                                  |     |     |                                    |     |     |     |     |   |  |  |  |  |  |  |  |  |

| At the time of an interruption reception | ← Vector address of each interruption → |      |      |      |                                  |     |                                  |     |     |                                    |     |     |     |     |   |  |  |  |  |  |  |  |  |

| Power on reset<br>RESET by reset pin     | 0                                       | 0    | 0    | 0    | 0                                | 0   | 0                                | 0   | 0   | 0                                  | 0   | 0   | 0   | 0   | 0 |  |  |  |  |  |  |  |  |

| Priority | Interruption Factor | Vector Address |

|----------|---------------------|----------------|

| 1        | INTR1 pin           | 0001H          |

| 2        | INTR2 pin           | 0002H          |

| 3        | Serial interface    | 0003H          |

| 4        | Timer counter       | 0004H          |

#### 2. Stack Register

A register consisting of  $8 \times 14$  bits which stores the contents of the program counter +1 (the return address) when a sub-routine call instruction is executed. The contents of the stack register are loaded into the program counter when the return instruction (RN, RNS, RNI instruction) is executed.

There are eight stack levels available and nesting occurs with both levels.

### 3. ALU

ALU is equipped with binary 4-bit parallel add/subtract functions, logical operation, comparison and multiple bit judgment functions. This CPU is not equipped with an accumulator, and all operations are handled directly within the data memory.

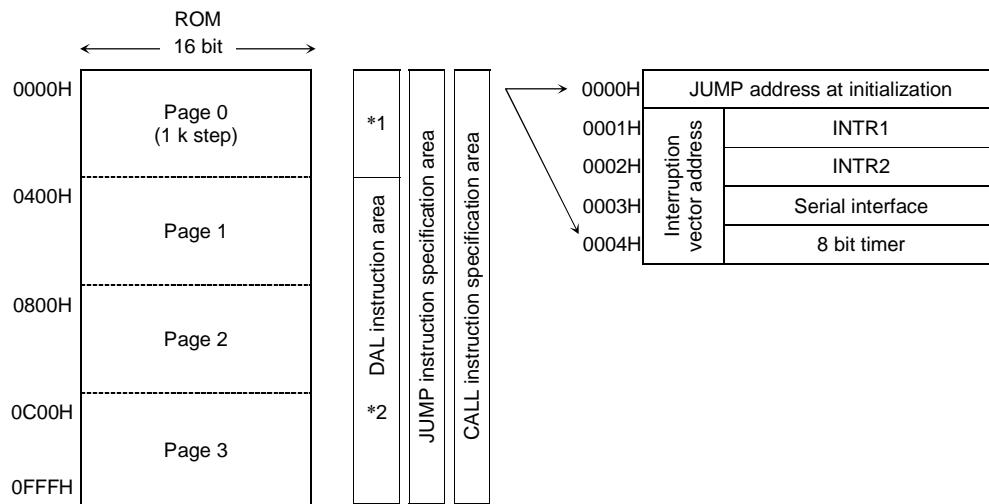

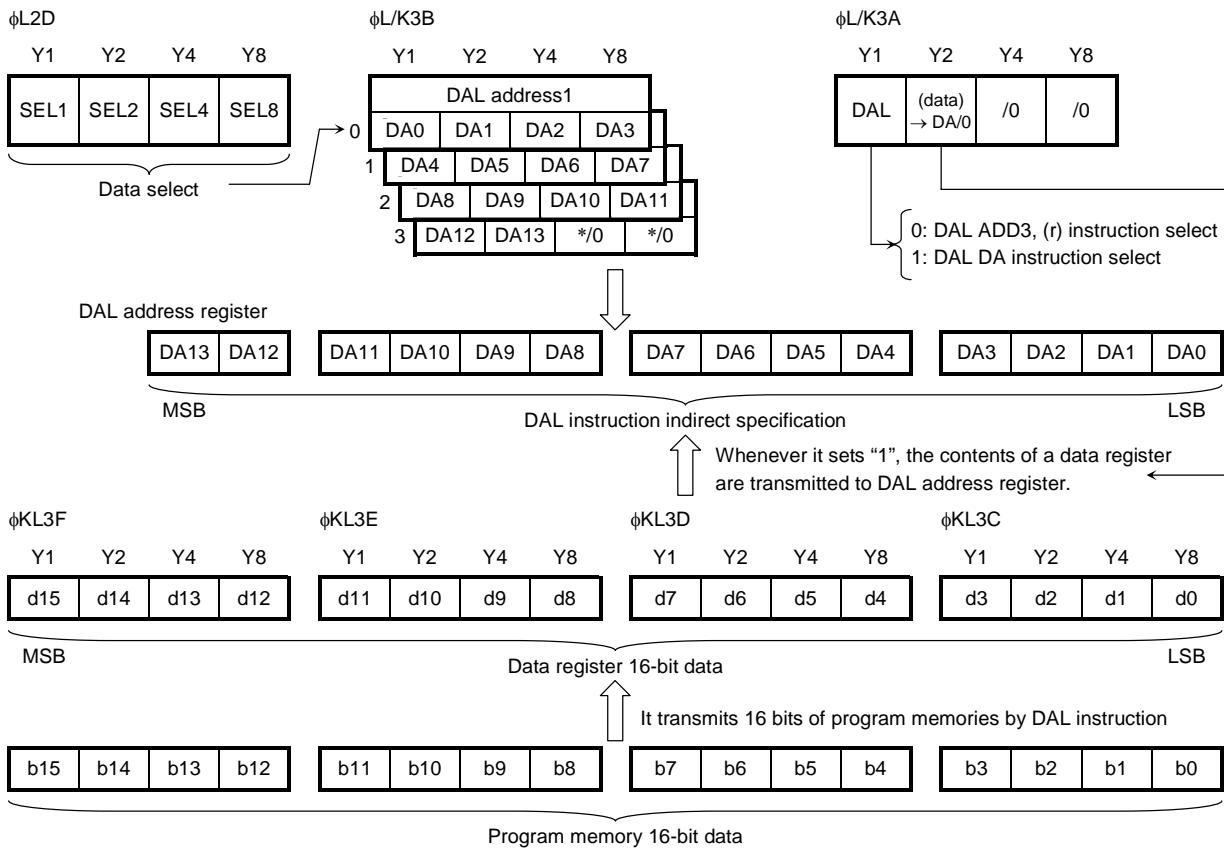

### 4. Program Memory (ROM)

The program memory consists of 16 bits  $\times$  4096 steps and is used for storing programs. The usable address range consists of 4096 steps between address 0000H ~ 0FFFH.

The program memory is divided into 4096 separate steps and consists of page 0 ~ 3. The JUMP instruction and CALL instruction can be freely used throughout all 4096 steps.

In case of setting DAL bit (it arranges on I/O map) "0" (DAL ADDR3, (r) command), the program memory address 0000H ~ 03FFH (page 0) are used as data area and setting DAL bit "1" (DAL (DA) command), the program memory address 0000H to 0FFFH (page 0 ~ 3) are used as data area. The 16 bit contents of this can be loaded into the data register by executing the DAL instruction.

Note: An address outside of the program lop must be set when establishing a data area within the program memory.

\*1: DAL bit = DAL access area at setting "0"

\*2: DAL bit = DAL access area at setting "1"

Note: DAL bit is arranged on I/O map.

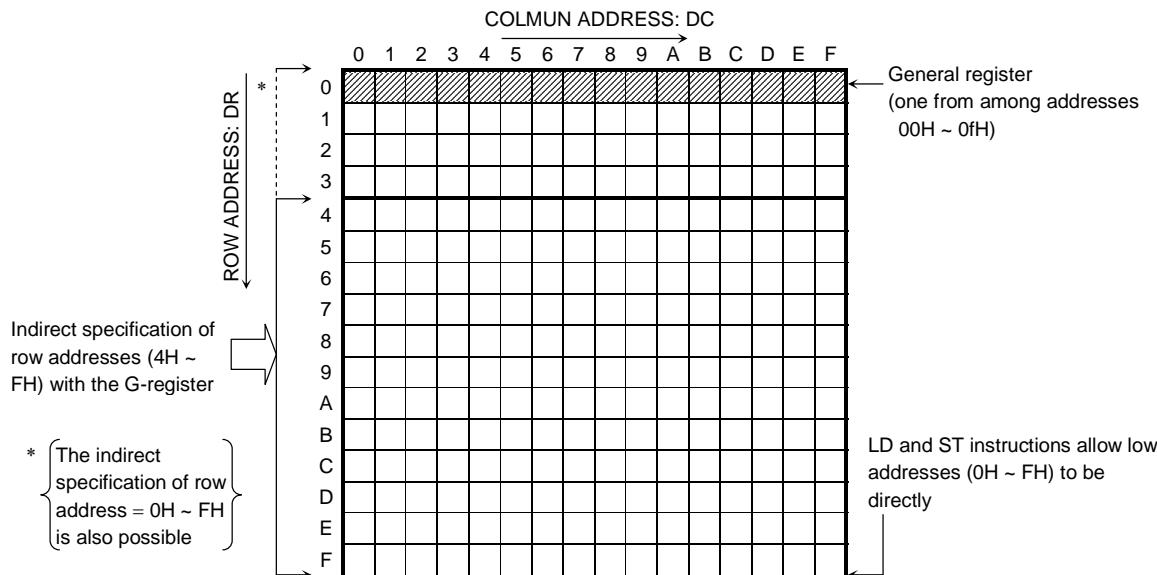

## 5. Data Memory (RAM)

The data memory consists of 4 bit  $\times$  256 words and is used for storing data. These 256 words are expressed in row addresses (4 bits) and column addresses (4 bits). 192 words (row address = address 004H ~ 00FH) within the data memory are addressed indirectly by the G-register. Owing to this, it is necessary to specify the row address with the G-register before the data in this area can be processed.

The address 00H ~ 0FH within the data memory are known as general registers, and these can be used simply by specifying the relevant column address (4 bit). These sixteen general registers can be used for operations and transfers with the data memory, and may also be used as normal data memories.

Note: The column address (4 bit) that specifies the general register is the register number of the general register.

Note: All row address (addresses 0H ~ FH) can be specified indirectly with the G-register.

Note: The data memory is 256 words and 2 bits of the 6-bit higher ranks of G-register row address are used "0" (00H ~ 0FH address).

Note: By using LD and ST instructionss, it can be addressed directly in 256 words (row address = 00H ~ 0FH) in a data memory.

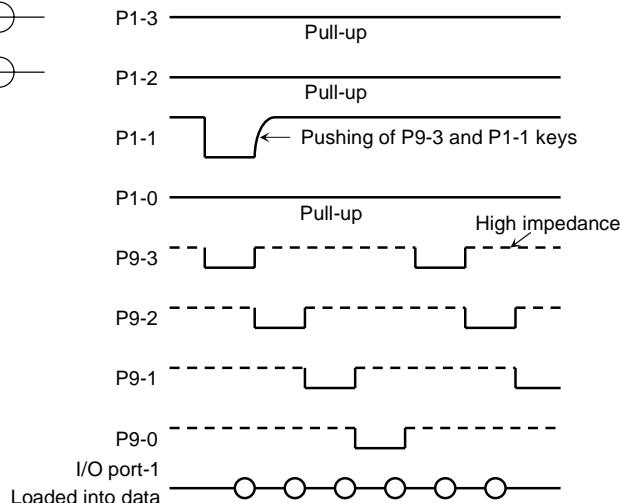

## 6. G-Register (G-REG)

The G-register is a 4 bits register used for addressing the row addresses (DR = 4H ~ FH addresses) of the data memory's 192 words.

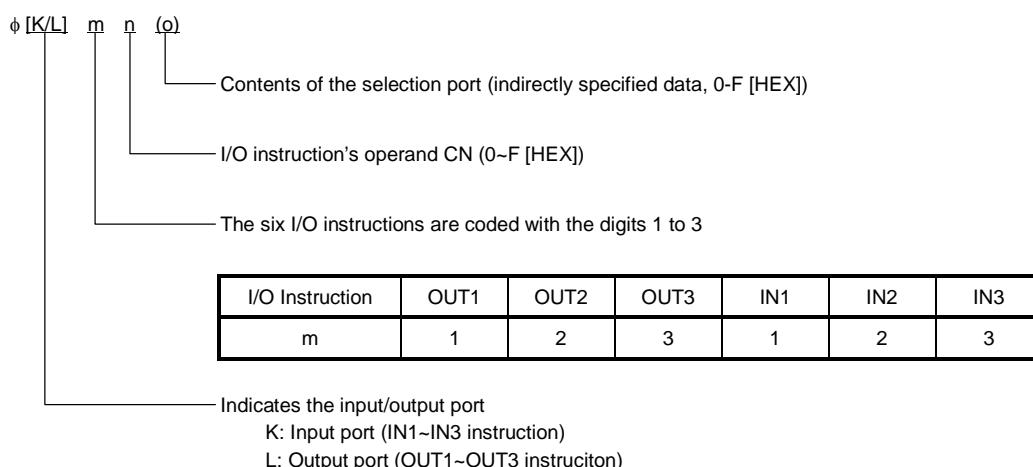

The contents of this register are validated when the MVGD instruction or MVGS instruction are executed, and not affected through the execution of any other instructions. This register is used as one of the ports, and the contents are set when the OUT1 instruction from among the I/O instructions is executed. The 6-bit contents can be directly set by execution of STIG instruction.

(→Refer to the Register Port section.)

## 7. Data Register (DATA REG)

The data register consists of 1 □ 16 bits and stores 16 bits of optional address data. This register is used as one of the ports, and the contents are loaded into the data memory in units of 4 bits when an IN1 instruction from among the I/O instructions is executed. (□ Refer to the Register Port section.)

Moreover, this register supports writing from the data memory and is used for evacuation/return processing of the data at the time of interruption.

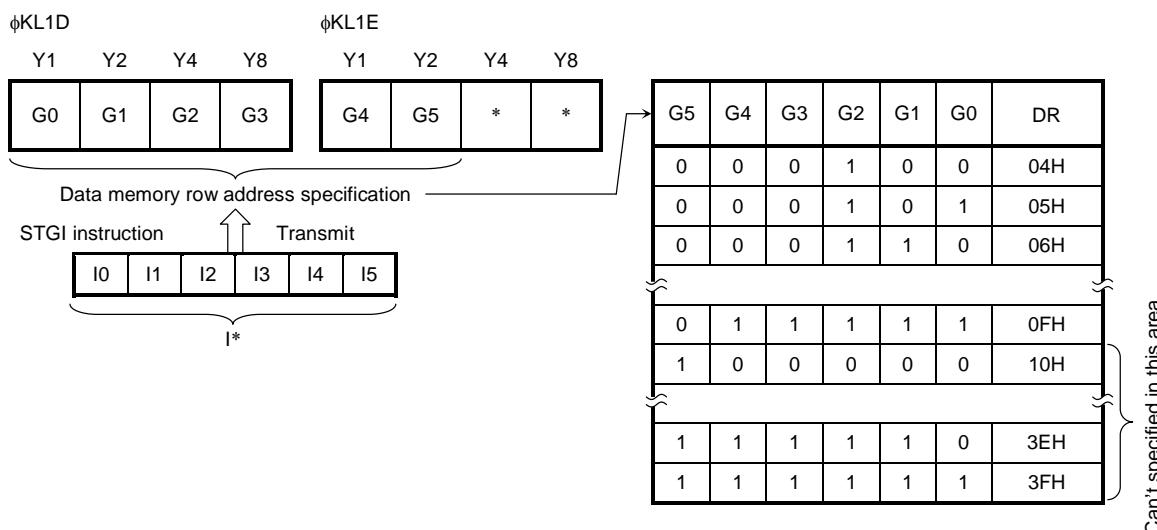

## 8. DAL Address Register (DA)

The data register consists of 1 × 14 bits.

If a DAL instruction is executed when the DAL bit is set to "1", 16 bits of the data of the free addresses in the program memory specified by this DAL address register are loaded. By the setting (DATA) → DA bit to "1", the contents of data register (DATA REG) can be transmitted to DAL address register (DA).

This register and a control bit are treated as a port, and are accessed by IN3/OUT3 instruction of an input-and-output instruction. (→ Refer to section in Register port item)

## 9. Carry F/F (Ca Flag)

This is set when either Carry or Borrow are issued in the result of calculation instruction execution and is reset if neither of these are issued.

The contents of carry F/F can only be amended through the execution addition, subtraction, CLT, CLTC instructions and are not affected by the execution of any other instruction.

The carry F/F can be accessed by the IN1/OUT1 instruction of an input-and-output instruction. For this reason, an input-and-output command performs the evacuation and the return at the time of interruption between data memories. (→ Refer to the Register Port section.)

## 10. Judgment Circuit (J)

This circuit judges the skip conditions when an instruction equipped with the skip function is executed. The program counter is increased in increments of two when the skip conditions are satisfied, and the subsequent instruction is skipped.

There are 15 instructions equipped with a wide variety of skip functions available. (→ Refer to the items marked with a "\*" symbol in the Table Instruction Functions and Operational Instructions)

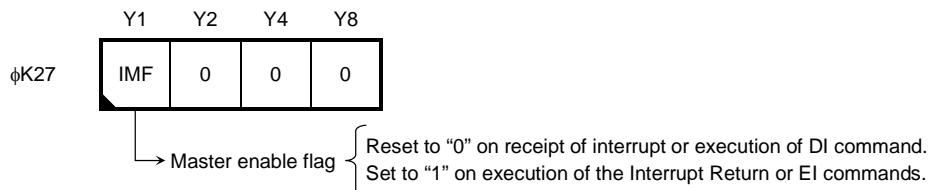

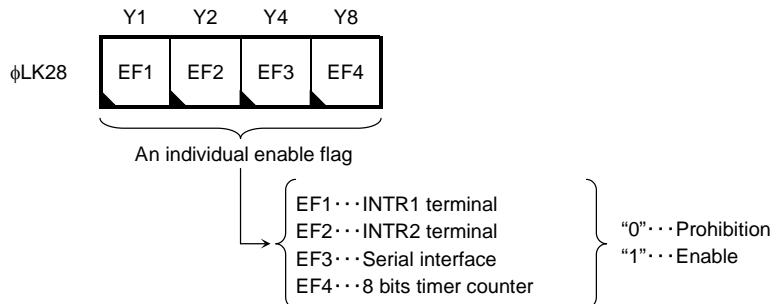

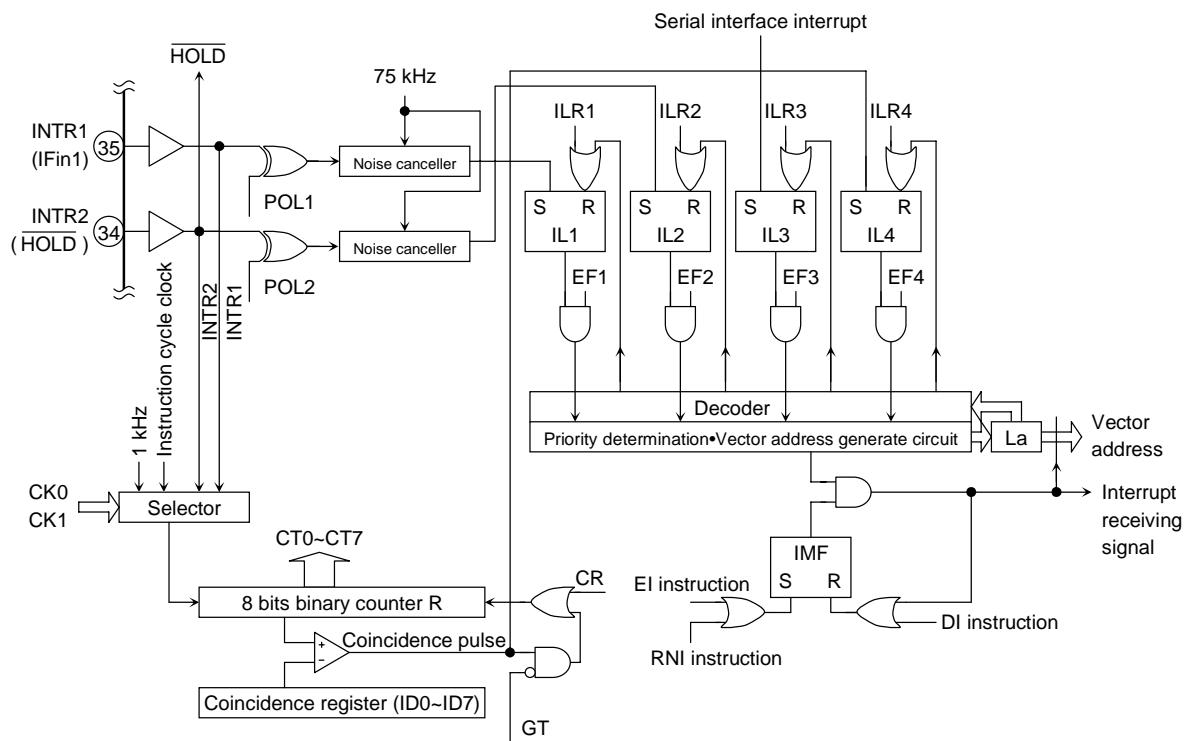

## 11. Interruption Circuit

An interruption circuit branches to each vector address by the demand from circumference hardware, and performs each interruption processing. (→Refer to the interruption function section.)

## 12. Instruction Set Table

A total of 57 instruction sets are available, and all of these are single-word instructions. These instructions are expressed with 6-bit instruction codes.

| High order 2 bit<br>Low order 4 bit |   | 00    |        | 01   |       | 10 |  | 11          |          |

|-------------------------------------|---|-------|--------|------|-------|----|--|-------------|----------|

|                                     |   | 0     |        | 1    |       | 2  |  | 3           |          |

| 0000                                | 0 | AI    | M, I   | TMTR | r, M  |    |  | SLTI        | M, I     |

| 0001                                | 1 | AIC   | M, I   | TMFR | r, M  |    |  | SGEI        | M, I     |

| 0010                                | 2 | SI    | M, I   | SEQ  | r, M  |    |  | SEQI        | M, I     |

| 0011                                | 3 | SIB   | M, I   | SNE  | r, M  |    |  | SNEI        | M, I     |

| 0100                                | 4 | ORIM  | M, I   | LD   | r, M* |    |  | TMTN        | M, N     |

| 0101                                | 5 | ANIM  | M, I   |      |       |    |  | TMT         | M, N     |

| 0110                                | 6 | XORIM | M, I   |      |       |    |  | TMFN        | M, N     |

| 0111                                | 7 | MVIM  | M, I   |      |       |    |  | TMF         | M, N     |

| 1000                                | 8 | AD    | r, M   | ST   | M*, r |    |  | IN1         | M, C     |

| 1001                                | 9 | AC    | r, M   |      |       |    |  | IN2         | M, C     |

| 1010                                | A | SU    | r, M   |      |       |    |  | IN3         | M, C     |

| 1011                                | B | SB    | r, M   |      |       |    |  | OUT1        | M, C     |

| 1100                                | C | ORR   | r, M   | CLT  | r, M  |    |  | OUT2        | M, C     |

| 1101                                | D | ANDR  | r, M   | CLTC | r, M  |    |  | OUT3        | M, C     |

| 1110                                | E | XORR  | r, M   | MVGD | r, M  |    |  | DAL         | ADDR3, r |

| 1111                                | F | MVSR  | M1, M2 | MVGS | M, r  |    |  | SHRC        | M        |

|                                     |   |       |        |      |       |    |  | RORC        | M        |

|                                     |   |       |        |      |       |    |  | STIG        | !*       |

|                                     |   |       |        |      |       |    |  | SKP, SKPN   |          |

|                                     |   |       |        |      |       |    |  | RN, RNS     |          |

|                                     |   |       |        |      |       |    |  | WAIT        | P        |

|                                     |   |       |        |      |       |    |  | CKSTP       |          |

|                                     |   |       |        |      |       |    |  | XCH         | M        |

|                                     |   |       |        |      |       |    |  | DI, EI, RNI |          |

|                                     |   |       |        |      |       |    |  | NOOP        |          |

### 13. Table of Instruction Functions and Operational Instructions

#### (Description of the symbols used in the table)

|               |                                                                                                                                                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M             | : Data memory address.<br>Generally one of the addresses from among addresses 00H to 3FH in the data memory.                                                                       |

| M*            | : Data memory address (256 words)<br>One of the addresses from among addresses 000H to 0FFH in the data memory.<br>(Effective only at the time of ST and LD instruction execution) |

| r             | : General register<br>One of the addresses from among addresses 00H to 00FH in the data memory.                                                                                    |

| PC            | : Program Counter (14 bits)                                                                                                                                                        |

| STACK         | : Stack register (14 bits)                                                                                                                                                         |

| G             | : G-register (6 bits)                                                                                                                                                              |

| DATA          | : Data register (16 bits)                                                                                                                                                          |

| I             | : Immediate data (4 bits)                                                                                                                                                          |

| I*            | : Immediate data (6 bits, effective only at the time of STIG instruction execution)                                                                                                |

| N             | : Bit position (4 bits)                                                                                                                                                            |

| □             | : ALL "0"                                                                                                                                                                          |

| C             | : Port code No. (4 bits)                                                                                                                                                           |

| CN            | : Port code No. (4 bits)                                                                                                                                                           |

| RN            | : General register No. (4 bits)                                                                                                                                                    |

| ADDR1         | : Program memory address (14 bits)                                                                                                                                                 |

| ADDR2         | : Program memory address within page 0 to 3 (12 bits)                                                                                                                              |

| ADDR3         | : High order 6 bits of the program memory address within page 0.                                                                                                                   |

| DA            | : DAL address register<br>(14 bits, effective only DAL instruction at the time of DAL bits is set to "1")                                                                          |

| Ca            | : Carry                                                                                                                                                                            |

| CY            | : Carry flag                                                                                                                                                                       |

| P             | : Wait condition                                                                                                                                                                   |

| b             | : Borrow                                                                                                                                                                           |

| IN1~IN3       | : The ports used during the execution of instructions IN1 to IN3                                                                                                                   |

| OUT1~OUT3     | : The ports used during the execution of instructions OUT1 to OUT3                                                                                                                 |

| ( )           | : Contents of the register or data memory                                                                                                                                          |

| [ ] C         | : Contents of the port indicating code No. C (4 bits)                                                                                                                              |

| [ ]           | : Contents of the data memory indicating the contents of the register or data memory                                                                                               |

| [ ] P         | : Contents of the program memory (16 bits)                                                                                                                                         |

| IC            | : Instruction code (6 bits)                                                                                                                                                        |

| *             | : Commands equipped with the skip function                                                                                                                                         |

| DC            | : Data memory column address (4 bits)                                                                                                                                              |

| DR            | : Data memory row address (2 bits)                                                                                                                                                 |

| DR*           | : Data memory row address<br>(4 bits, effective only at the time of ST and LD instruction execution)                                                                               |

| (M) b0~(M) b3 | : Bits data of the contents of a data memory (1 bit)                                                                                                                               |

| Instruction Group        | Mnemonic  | Skip Function | Function Description                                                              | Operation Description                                                                     | Machine Language (16 bits) |            |            |            |

|--------------------------|-----------|---------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------|------------|------------|------------|

|                          |           |               |                                                                                   |                                                                                           | IC (6 bits)                | A (2 bits) | B (4 bits) | C (4 bits) |

| Addition Instructions    | AI M, I   |               | Add immediate data to memory                                                      | $M \leftarrow (M) + I$                                                                    | 000000                     | DR         | DC         | I          |

|                          | AIC M, I  |               | Add immediate data to memory with carry                                           | $M \leftarrow (M) + I + ca$                                                               | 000001                     | DR         | DC         | I          |

|                          | AD r, M   |               | Add memory to general register                                                    | $r \leftarrow (r) + (M)$                                                                  | 001000                     | DR         | DC         | RN         |

|                          | AC r, M   |               | Add memory to general register with carry                                         | $r \leftarrow (r) + (M) + ca$                                                             | 001001                     | DR         | DC         | RN         |

| Subtraction Instructions | SI M, I   |               | Subtract immediate data from memory                                               | $M \leftarrow (M) - I$                                                                    | 000010                     | DR         | DC         | I          |

|                          | SIB M, I  |               | Subtract immediate data from memory with borrow                                   | $M \leftarrow (M) - I - b$                                                                | 000011                     | DR         | DC         | I          |

|                          | SU r, M   |               | Subtract memory from general register                                             | $r \leftarrow (r) - (M)$                                                                  | 001010                     | DR         | DC         | RN         |

|                          | SB r, M   |               | Subtract memory from general register with borrow                                 | $r \leftarrow (r) - (M) - b$                                                              | 001011                     | DR         | DC         | RN         |

| Comparison Instructions  | SLTI M, I | *             | Skip if memory is less than immediate data                                        | Skip if $(M) < I$                                                                         | 110000                     | DR         | DC         | I          |

|                          | SGEI M, I | *             | Skip if memory is greater than or equal to immediate data                         | Skip if $(M) \geq I$                                                                      | 110001                     | DR         | DC         | I          |

|                          | SEQI M, I | *             | Skip if memory is equal to immediate data                                         | Skip if $(M) = I$                                                                         | 110010                     | DR         | DC         | I          |

|                          | SNEI M, I | *             | Skip if memory is not equal to immediate data                                     | Skip if $(M) \neq I$                                                                      | 110011                     | DR         | DC         | I          |

|                          | SEQ r, M  | *             | Skip if general register is equal to memory                                       | Skip if $(r) = (M)$                                                                       | 010010                     | DR         | DC         | RN         |

|                          | SNE r, M  | *             | Skip if general register is not equal to memory                                   | Skip if $(r) \neq (M)$                                                                    | 010011                     | DR         | DC         | RN         |

|                          | CLT r, M  |               | Set carry flag if general register is less than memory, or reset if not           | $(CY) \leftarrow 1$ if $(r) < (M)$ or $(CY) \leftarrow 0$ if $(r) \geq (M)$               | 011100                     | DR         | DC         | RN         |

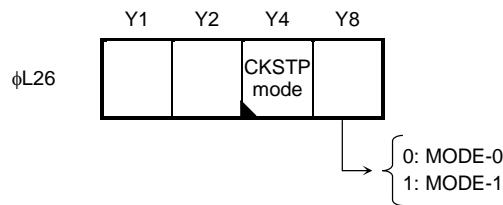

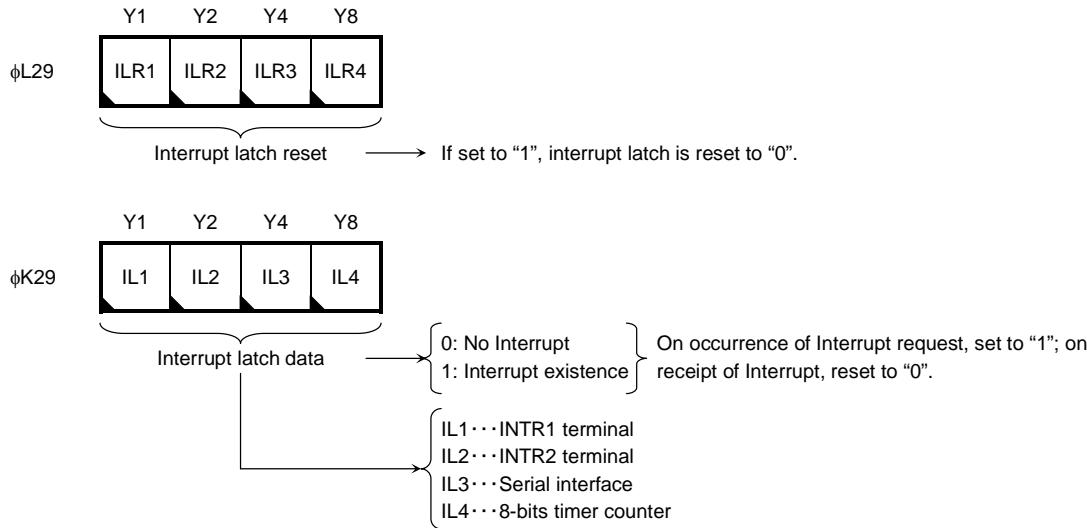

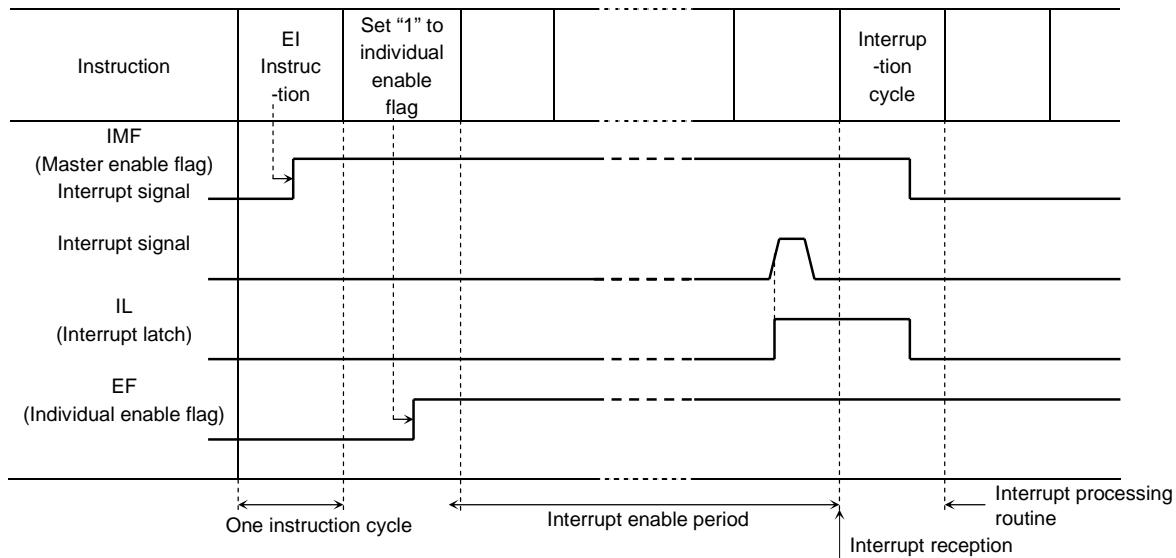

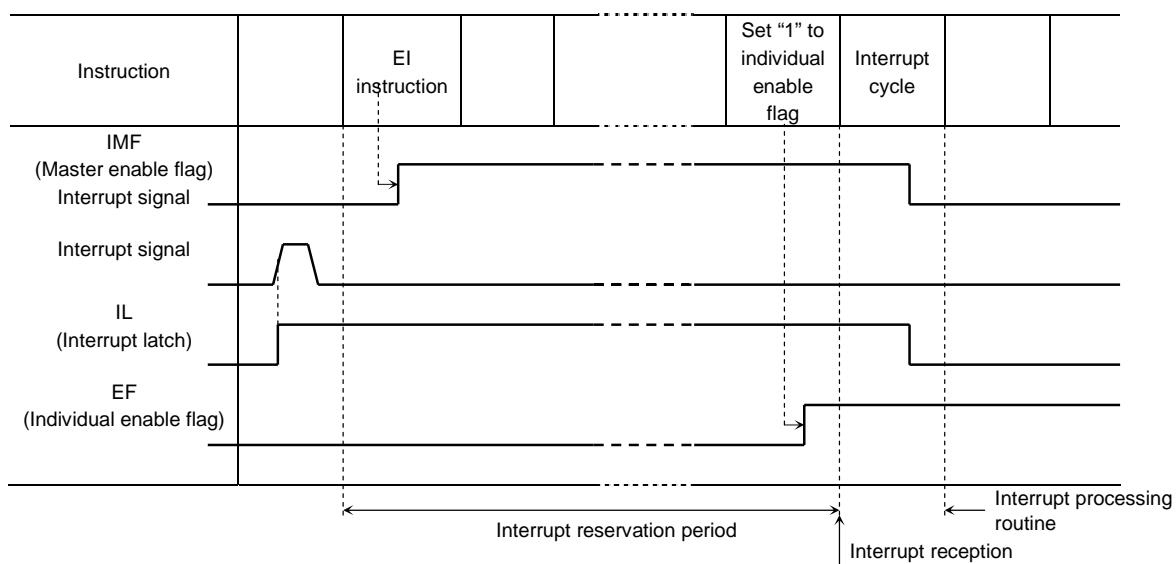

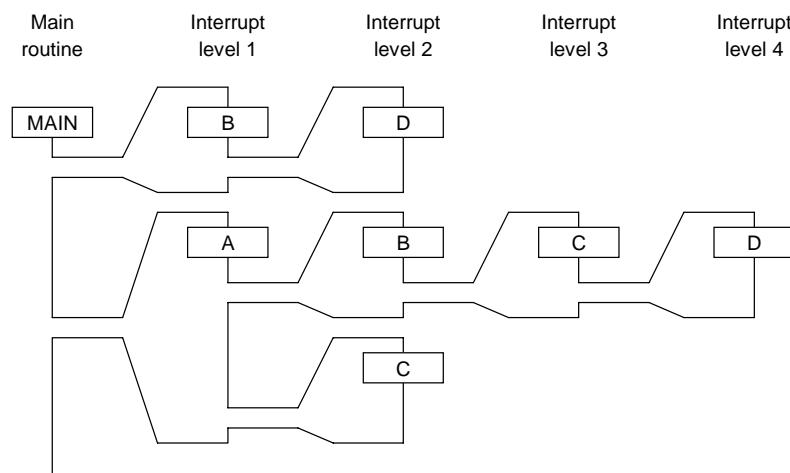

|                          | CLTC r, M |               | Set carry flag if general register is less than memory with carry or reset if not | $(CY) \leftarrow 1$ if $(r) < (M) + (ca)$ or $(CY) \leftarrow 0$ if $(r) \geq (M) + (Ca)$ | 011101                     | DR         | DC         | RN         |