# MEMORY Mobile FCRAM™

**CMOS**

# 16M Bit (1M word x 16 bit)

**Mobile Phone Application Specific Memory**

# MB82D01160-90/90L

## CMOS 1,048,576-WORD x 16 BIT Fast Cycle Random Access Memory with Low Power SRAM Interface

#### **■ DESCRIPTION**

The Fujitsu MB82D01160 is a CMOS Fast Cycle Random Access Memory (FCRAM) with asynchronous Static Random Access Memory (SRAM) interface containing 16,777,216 storages accessible in a 16-bit format. This MB82D01160 is suited for low power applications such as Cellular Handset and PDA.

#### **■ FEATURES**

- Asynchronous SRAM Interface

- Fast Random Cycle Time trc = 90ns

- Low Power Consumption

I<sub>DDS1</sub> = 200μA, 100μA (L version)

- Wide Operating Condition

$V_{DD} = +2.3V \text{ to } +2.7V \text{ or} +2.7V \text{ to } +3.0V$

$T_A = -25^{\circ}C \text{ to } +85^{\circ}C$

- Byte Write Control

- · Dual Chip Enable

#### **■ PRODUCT LINE**

|                           | MB82D01160-90 | MB82D01160-90L |

|---------------------------|---------------|----------------|

| Read Cycle Time (tRc)     | 90ns min      | 90ns min       |

| Standby Current ( IDDS1 ) | 200μA max     | 100μA max      |

#### PACKAGE

Notice: FCRAM is a trademark of Fujitsu Limited, Japan

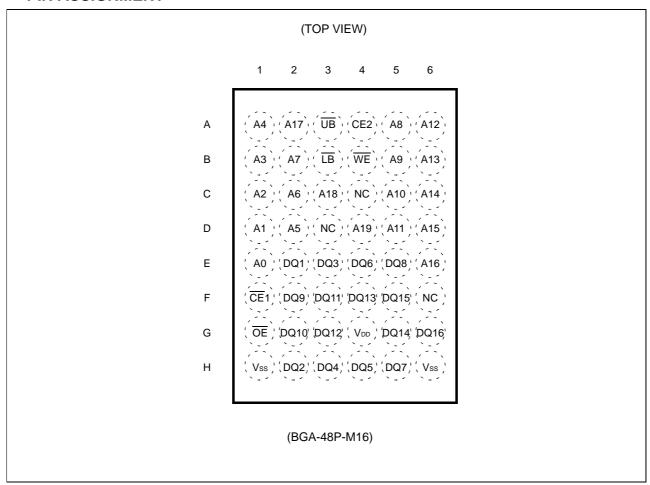

### **■ PIN ASSIGNMENT**

#### **■ PIN DESCRIPTION**

| Pin Name                          | Description                           |

|-----------------------------------|---------------------------------------|

| A <sub>0</sub> to A <sub>19</sub> | Address Input                         |

| CE1                               | Chip Enable (Low Active)              |

| CE2                               | Chip Enable (High Active)             |

| WE                                | Write Enable (Low Active)             |

| ŌĒ                                | Output Enable (Low Active)            |

| <u>ГВ</u>                         | Lower Byte Write Control (Low Active) |

| ŪB                                | Upper Byte Write Control (Low Active) |

| DQ1-8                             | Lower Byte Data Input/Output          |

| DQ9-16                            | Upper Byte Data Input/Output          |

| V <sub>DD</sub>                   | Power Supply                          |

| Vss                               | Ground                                |

| NC                                | No Connection                         |

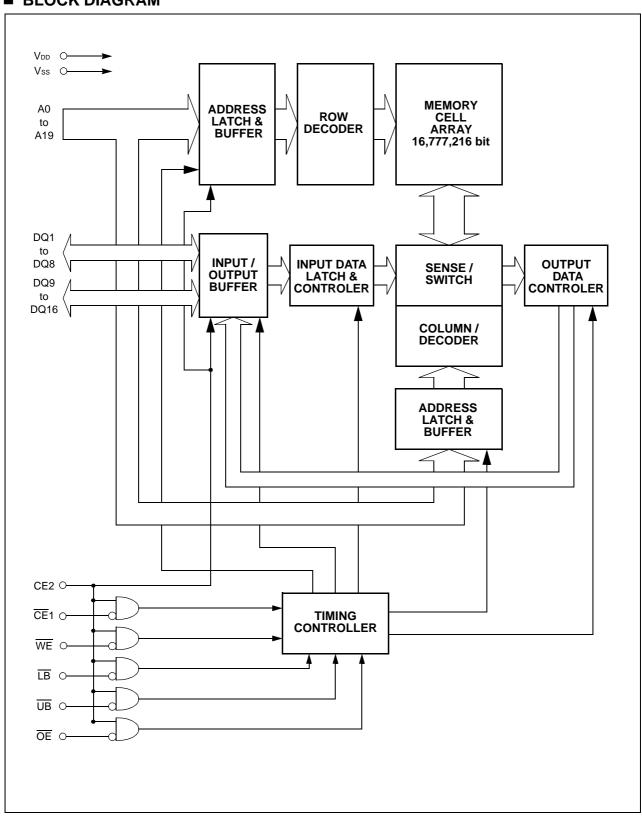

### **■ BLOCK DIAGRAM**

### **■ FUNCTION TRUTH TABLE**

| Mode               | CE1 | CE2 | WE | OE | LB | UB | DQ1-8           | DQ9-16          | IDD  |

|--------------------|-----|-----|----|----|----|----|-----------------|-----------------|------|

| Inhibit *1         | Х   | L   | Х  | Х  | Х  | Х  | High-Z          | High-Z          | IDDS |

| Standby (Deselect) | Н   |     | Х  | Х  | X  | X  | riigii-2        | Tilgii-Z        | IDDS |

| Output Disable *2  |     |     |    | Н  | Х  | Х  | High-Z          | High-Z          |      |

| Read *3            |     |     | Η  | L  | Х  | Х  | Output<br>Valid | Output<br>Valid |      |

| Write              | L   | Н   |    |    | L  | L  | Input<br>Valid  | Input<br>Valid  | Idda |

| Write (Upper Byte) |     |     | L  | Н  | L  | Н  | Input<br>Valid  | Invalid         |      |

| Write (Lower Byte) |     |     |    |    | Н  | L  | Invalid         | Input<br>Valid  |      |

**Note:** L = VIL, H = VIH, X can be either VIL or VIH, High-Z = High Impedance

<sup>\*1:</sup> CE2=L state should only be used at Power-up stage.

$<sup>^{*}2</sup>$ : Output Disable condition should not be kept longer than  $1\mu s$ .

<sup>\*3:</sup> Byte control at Read operation is not supported.

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                                                     | Symbol          | Value        | Unit |

|---------------------------------------------------------------|-----------------|--------------|------|

| Voltage of V <sub>DD</sub> Supply Relative to V <sub>SS</sub> | V <sub>DD</sub> | -0.5 to +3.3 | V    |

| Voltage at Any Pin Relative to Vss                            | VIN, VOUT       | -0.5 to +3.3 | V    |

| Short Circuit Output Current                                  | Іоит            | <u>+</u> 50  | mA   |

| Storage Temperature                                           | Тѕтс            | -55 to +125  | °C   |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### ■ RECOMMENDED OPERATING CONDITIONS (See WARNING below.)

#### (Referenced to Vss)

| Parameter                | Notes | Symbol               | Min. | Max.                 | Unit |

|--------------------------|-------|----------------------|------|----------------------|------|

|                          |       | V <sub>DD</sub> (27) | 2.7  | 3.0                  | V    |

| Supply Voltage           |       | V <sub>DD</sub> (23) | 2.3  | 2.7                  | V    |

|                          |       | Vss                  | 0    | 0                    | V    |

| High Loyal Input Valtage | *1    | V <sub>IH</sub> (27) | 2.3  | V <sub>DD</sub> +0.3 | V    |

| High Level Input Voltage | ı     | V <sub>IH</sub> (23) | 2.0  | V <sub>DD</sub> +0.3 | V    |

| Low Level Input Voltage  | *1    | VıL                  | -0.3 | 0.4                  | V    |

| Ambient Temperature      |       | TA                   | -25  | 85                   | °C   |

Notes: \*1: Minimum DC voltage on input or I/O pins are -0.3V. During voltage transitions, inputs may negative overshoot Vss to -1.0V for periods of up to 5ns. Maximum DC voltage on input and I/O pins are Vpd+0.3V. During voltage transitions, outputs may positive overshoot to Vpd+1.0V for periods of up to 5 ns

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

#### **■ PACKAGE PIN CAPACITANCE**

| Symbol           | Description               | Test Setup           | Тур. | Max. | Unit |

|------------------|---------------------------|----------------------|------|------|------|

| C <sub>IN1</sub> | Address Input Capacitance | Vin = 0V             | _    | 5    | pF   |

| Соит             | Output Capacitance        | Vout = 0V            | _    | 8    | pF   |

| C <sub>IN2</sub> | Control Pin Capacitance   | V <sub>IN</sub> = 0V | _    | 5    | pF   |

**Note:** Test conditions  $T_A = 25$ °C, f = 1.0 MHz

### **■ ELECTRICAL CHARACTERISTICS**

### 1. DC Characteristics

| Paramete                       | er        | Symbol | Test Condition                                                                                                                                                                                                                                                                | าร      | Min.                             | Тур. | Max. | Unit |   |     |

|--------------------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------|------|------|------|---|-----|

| Input Leakage Curr             | ent       | lц     | VIN = Vss to VDD                                                                                                                                                                                                                                                              |         | -1.0                             | _    | +1.0 | μΑ   |   |     |

| Output Leakage Cu              | rrent     | ILO    | Vout = Vss to Vpp, Output                                                                                                                                                                                                                                                     | Disable | -1.0                             | _    | +1.0 | μΑ   |   |     |

| Output High Voltage            | e Level   | Vон    | Iон = −0.5mA                                                                                                                                                                                                                                                                  |         | 1.8                              | _    | _    | V    |   |     |

| Output Low Voltage             | Level     | Vol    | IoL = 1mA                                                                                                                                                                                                                                                                     |         | _                                | _    | 0.4  | V    |   |     |

|                                |           |        | , VDD = VDD max., VIN = VIH or VIL                                                                                                                                                                                                                                            |         | VDD = VDD max., VIN = VIH or VIL |      | _    | 1.5  | 2 | m A |

| V <sub>DD</sub> Standby        | L version | IDDS   | CE1 = CE2 = Vін, Іоит=0m                                                                                                                                                                                                                                                      | nA      |                                  | 1    | 1.5  | mA   |   |     |

| Current                        |           |        | $V_{DD} = V_{DD}$ max., $V_{IN} \le 0.2V$ or $V_{IN} \ge V_{DD} - 0.2V$ , $\overline{CE1} = CE2 \ge V_{DD} - 0.2V$ , $I_{OUT} = 0$ mA                                                                                                                                         |         | _                                | 160  | 200  | ^    |   |     |

|                                | L version | DDS1   |                                                                                                                                                                                                                                                                               |         | _                                | 80   | 100  | μΑ   |   |     |

| V <sub>DD</sub> Active Current | •         | DDA1   | $\begin{array}{c} V_{DD} = V_{DD} \; \text{max.,} \\ \hline V_{IN} = V_{IH} \; \text{or} \; V_{IL}, \\ \hline CE1 = V_{IL} \; \text{and} \; CE2 = V_{IH}, \\ I_{OUT} = 0 \text{mA} \end{array} \qquad \begin{array}{c} t_{RC} \; / \; t_{WC} = \\ \text{minimum} \end{array}$ |         | _                                | 15   | 20   | mA   |   |     |

| Active Current                 |           | IDDA2  |                                                                                                                                                                                                                                                                               |         | _                                | 2.5  | 3.0  | mA   |   |     |

Notes: \*1: All voltages are referenced to Vss.

\*2: DC Characteristics are measured after following POWER-UP timing.

\*3: IDDA depends on the output load conditions.

#### 2. AC Characteristics

### (1) Read Operation

| Parameter                                        | Symbol        | -90/       | -90/-90L |      | Notes |

|--------------------------------------------------|---------------|------------|----------|------|-------|

| Faiailletei                                      | Syllibol      | Min.       | Max.     | Unit | Notes |

| Read Cycle Time                                  | <b>t</b> RC   | 90         | 1000     | ns   | *1    |

| Address Setup Time at CE1 High to Low Transition | tasc          | <b>-</b> 5 | _        | ns   |       |

| Address Hold Time during CE1 Low                 | <b>t</b> ahc  | 90         | _        | ns   | *2    |

| Address Access Time                              | <b>t</b> AA   | _          | 90       | ns   | *3    |

| Chip Enable Access Time                          | <b>t</b> ce   | _          | 90       | ns   | *3    |

| Output Enable Access Time                        | <b>t</b> oe   | _          | 60       | ns   | *3    |

| Output Data Hold Time                            | tон           | 5          | _        | ns   | *3    |

| CE1 Low to Output Low-Z                          | <b>t</b> cLz  | 10         | _        | ns   | *4    |

| OE Low to Output Low-Z                           | <b>t</b> olz  | 0          | _        | ns   | *4    |

| CE1 High to Output High-Z                        | tснz          | _          | 25       | ns   | *4    |

| OE High to Output High-Z                         | tонz          | _          | 15       | ns   | *4    |

| CE1 High Pulse Width                             | <b>t</b> cp   | 10         | _        | ns   |       |

| CE1 High to Address Hold Time                    | <b>t</b> chah | -5         | _        | ns   | *5    |

| Address Invalid Time during Read (CE1=Low)       | tax           | _          | 10       | ns   |       |

**Notes:** \*1: Maximum value is a reference and is applied to Output Disable condition.

<sup>\*2:</sup> tahc must be satisfied every address valid state after tax during CE1=Low.

<sup>\*3:</sup> The output load is 30pF.

<sup>\*4:</sup> The output load is 5pF.

<sup>\*5:</sup> If actual address change before  $\overline{\text{CE}}1$  High transition is earlier than tchah (min), tcp ( $\overline{\text{CE}}1$  High period) should be kept at least trc (min) period.

### 2. AC Characteristics (Continued)

#### (2) Write Operation

| Parameter                     | Symbol        | -90/       | -90L | Unit | Notes  |  |

|-------------------------------|---------------|------------|------|------|--------|--|

| Parameter                     | Symbol        | Min.       | Max. | Unit | 140163 |  |

| Write Cycle Time              | twc           | 90         | 1000 | ns   | *1     |  |

| Address Setup Time            | tas           | 0          | _    | ns   |        |  |

| Address Hold Time             | <b>t</b> AH   | 40         | _    | ns   |        |  |

| CE1 Write Setup Time          | <b>t</b> cs   | 0          | 1000 | ns   | *2     |  |

| CE1 Write Hold Time           | tсн           | 0          | 1000 | ns   | *2     |  |

| WE, LB, UB Setup Time         | <b>t</b> BS   | 0          | _    | ns   |        |  |

| WE, LB, UB Hold Time          | <b>t</b> вн   | 0          | _    | ns   |        |  |

| OE Setup Time                 | toes          | 0          | _    | ns   |        |  |

| OE Hold Time                  | tоен          | 15         | _    | ns   |        |  |

| OE High to CE1 Low Setup Time | <b>t</b> oncl | <b>-</b> 5 | _    | ns   | *3     |  |

| OE High to Address Hold Time  | <b>t</b> онан | 0          | _    | ns   | *4     |  |

| CE1 Write Pulse Width         | <b>t</b> cw   | 60         | _    | ns   | *5, *6 |  |

| WE Write Pulse Width          | <b>t</b> wp   | 60         | _    | ns   | *5, *6 |  |

| CE1 Write Recovery Time       | twrc          | 15         | _    | ns   | *7     |  |

| WE Write Recovery Time        | twr           | 15         | 1000 | ns   | *2, *7 |  |

| Data Setup Time               | tos           | 20         | _    | ns   |        |  |

| Data Hold Time                | tон           | 10         | _    | ns   |        |  |

| CE1 Low to Output in Low-Z    | <b>t</b> cLz  | 10         | _    | ns   | *8     |  |

| OE Low to Output in Low-Z     | tolz          | 0          | _    | ns   | *8     |  |

**Notes:** \*1: Maximum value is a reference and applied to Output Disable condition.

<sup>\*2:</sup> Maximum value is applied to Output Disable condition.

<sup>\*3:</sup> tohcl (min) must be satisfied if read operation is not performed prior to write operation.

In case  $\overline{\text{OE}}$  is disabled after tohcl (min),  $\overline{\text{WE}}$  Low must be asserted after trec (min) from  $\overline{\text{CE}}$ 1 Low.

<sup>\*4:</sup> Applicable if CE1 stays Low after read operation.

<sup>\*5:</sup> twhp (max) must be satisfied for the high pulse noise.

<sup>\*6:</sup> tcw and twp are applied if write operation is initiated by  $\overline{\text{CE}}1$  and  $\overline{\text{WE}}$ , respectively.

<sup>\*7:</sup> twee and twe are applied if write pulse is terminated by  $\overline{\text{CE}}1$  and  $\overline{\text{WE}}$ , respectively.

<sup>\*8:</sup> The output load is 5pF.

## 2. AC Characteristics (Continued)

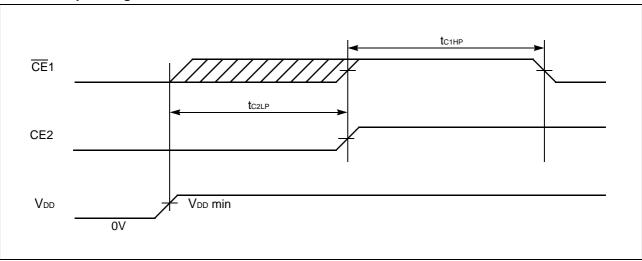

### (3) Other Timing Parameter

| Parameter                                            | Symbol            | -90/- | -90L | Unit  | Note |

|------------------------------------------------------|-------------------|-------|------|-------|------|

| Faiailletei                                          | Syllibol          | Min.  | Max. | Offic | NOLE |

| CE1 High to OE Invalid Time for Standby Entry        | <b>t</b> cнox     | 10    | _    | ns    |      |

| CE1 High to WE Invalid Time for Standby Entry        | <b>t</b> chwx     | 20    | _    | ns    |      |

| CE1 and CE2 Active Glitch Pulse Width                | <b>t</b> CAP      | _     | 5    | ns    | *1   |

| CE1 or WE High Glitch Pulse Width during Write Cycle | <b>t</b> whp      | _     | 5    | ns    | *2   |

| CE2 Low Hold Time after Power-up                     | <b>t</b> C2LP     | 350   | _    | μs    | *3   |

| CE1 High Hold Time following CE2 High after Power-up | t <sub>C1HP</sub> | 300   | _    | μs    | *4   |

**Notes:** \*1: Active means a condition where  $\overline{CE}1 = V_{IL}$  and  $CE2 = V_{IH}$ .

- \*2: Specified to the one time high pulse width during tow or two and excluded 10ns from beginning and end of the write cycle.

- \*3: Requires at least two dummy read cycles.

- \*4: Required when dummy read cycles are not performed.

## (4) AC Test Conditions

| Symbol | Description                    | Test Setup                                    | Value | Unit |

|--------|--------------------------------|-----------------------------------------------|-------|------|

| VIH    | Input High Lovel               | V <sub>DD</sub> = 2.7V to 3.0V                | 2.3   | V    |

| VIH    | Input High Level               | V <sub>DD</sub> = 2.3V to 2.7V                | 2.0   | V    |

| VIL    | Input Low Level                | _                                             | 0.4   | V    |

| Vref   | Input Timing Measurement Level | V <sub>DD</sub> = 2.7V to 3.0V                | 1.3   | V    |

| V REF  | input riming weasurement Level | V <sub>DD</sub> = 2.3V to 2.7V                | 1.1   | V    |

| t⊤     | Input Transition Time          | Between V <sub>I</sub> L and V <sub>I</sub> H | 5     | ns   |

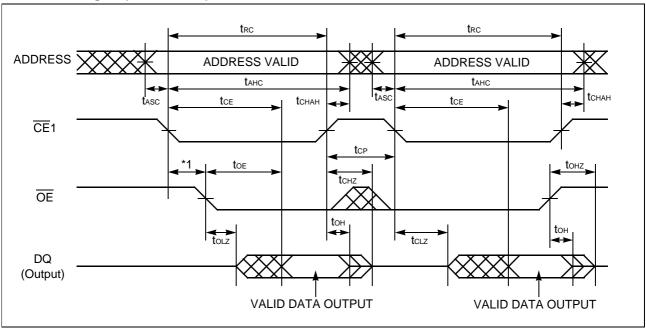

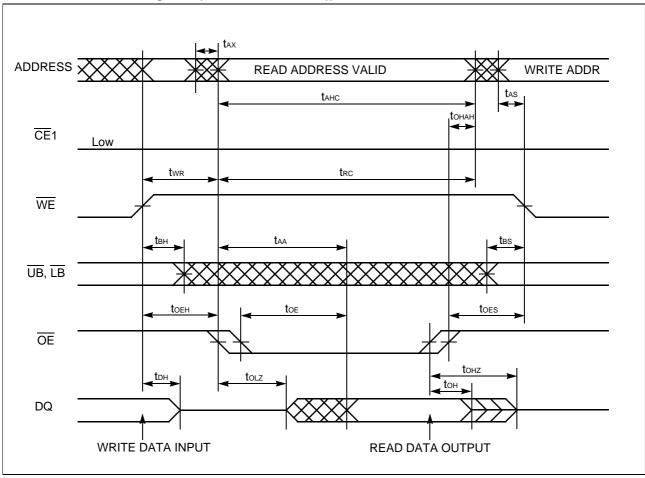

#### **■ TIMING DIAGRAMS**

### 1. READ Timing #1 (CE1 Control)

Note: CE2 and WE must be HIGH for entire read cycle.

\*1: Output Disable condition before new Read data valid should not be kept longer than 1µs.

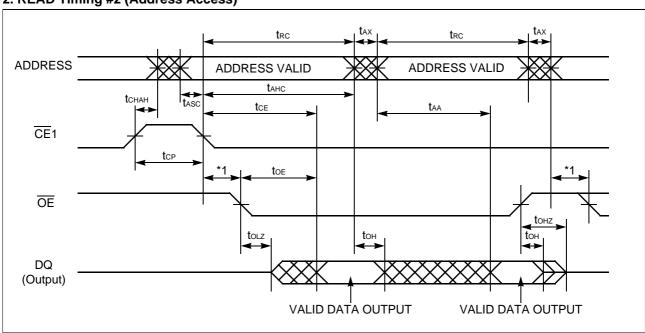

### 2. READ Timing #2 (Address Access)

Note: CE2 and WE must be HIGH for entire read cycle.

\*1: Output Disable condition before new Read data valid should not be kept longer than 1µs.

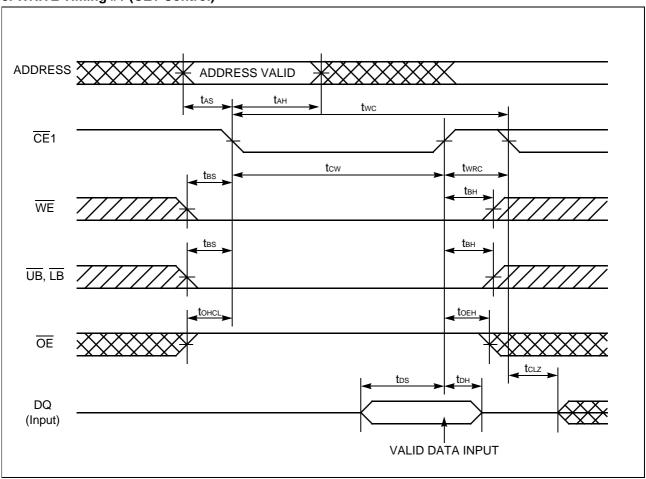

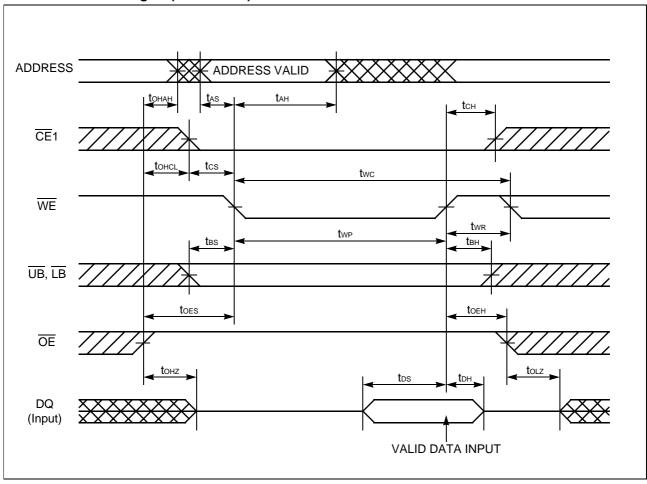

## 3. WRITE Timing #1 (CE1 Control)

Note: CE2 must be HIGH for write cycle.

## **■ TIMING DIAGRAMS (Continued)**

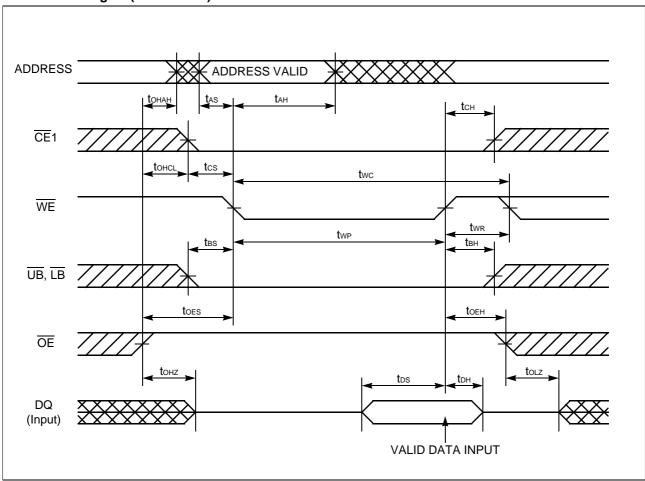

## 4. WRITE Timing #2 (WE Control)

Note: CE2 must be HIGH for write cycle.

## 5. BYTE WRITE Timing #1 (CE1 Control)

**Note:** CE2 must be HIGH and either  $\overline{LB}$  or  $\overline{UB}$  must be LOW for byte write cycle.

## **■ TIMING DIAGRAMS (Continued)**

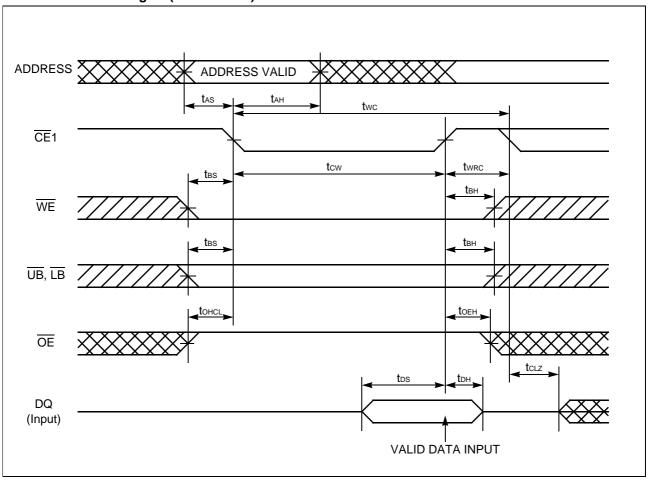

## 6. BYTE WRITE Timing #2 (WE Control)

**Note:** CE2 must be HIGH and either  $\overline{LB}$  or  $\overline{UB}$  must be LOW for byte write cycle.

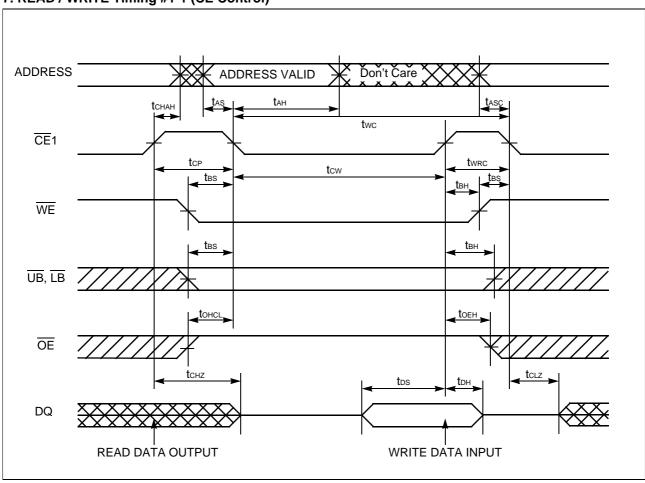

## 7. READ / WRITE Timing #1-1 (CE Control)

**Note:** Write address is edge trigger of either  $\overline{CE}1$  or  $\overline{WE}$  falling edge.

## **■ TIMING DIAGRAMS (Continued)**

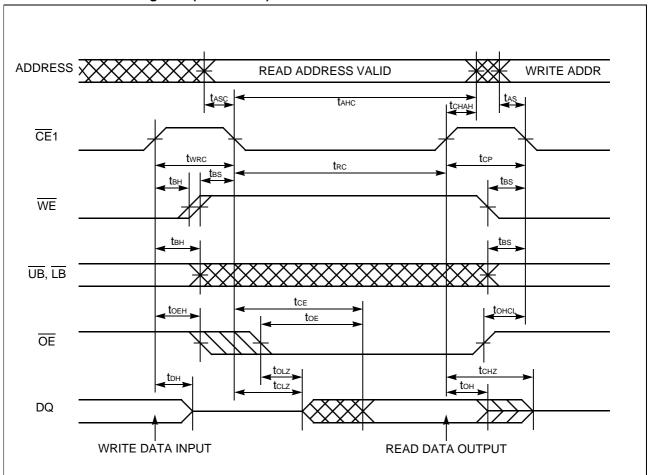

## 8. READ / WRITE Timing #1-2 (CE Control)

**Note:** WE must be HIGH for read cycle.

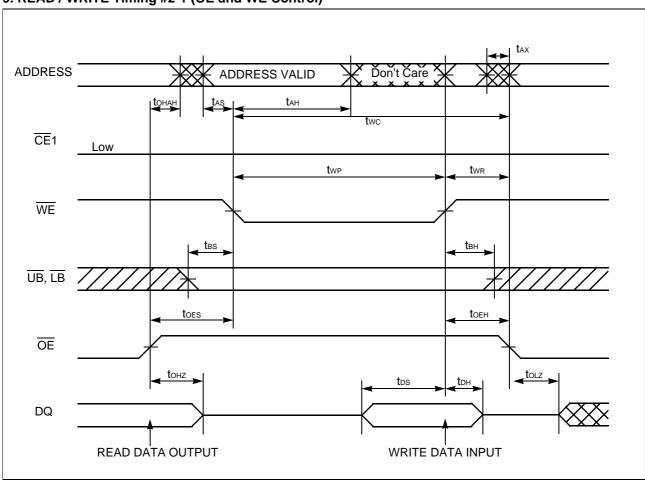

## 9. READ / WRITE Timing #2-1 (OE and WE Control)

**Note:**  $\overline{CE}1$  can be tied to LOW for  $\overline{WE}$  and  $\overline{OE}$  controlled operation.

When CE1 is tied to LOW, output is exclusively controlled by OE and read address can be issued after WE is brought to High.

**WARNING:** The read address following write operation must be changed if  $\overline{\text{CE}}1$  stays LOW.

## **■ TIMING DIAGRAMS (Continued)**

## 10. READ / WRITE Timing #2-2 (OE and WE Control))

**Note:**  $\overline{CE}1$  can be tied to LOW for  $\overline{WE}$  and  $\overline{OE}$  controlled operation.

When CE1 is tied to LOW, output is exclusively controlled by OE and read address can be issued after WE is brought to High.

**WARNING:** The read address following write operation must be changed if  $\overline{\text{CE}}1$  stays LOW.

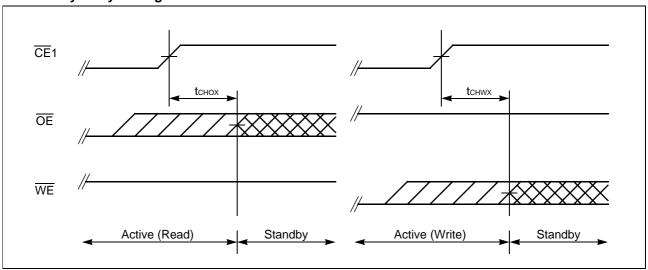

### 11. Standby Entry Timing after Read or Write

Note: Both tchox and tchwx define the earliest entry timing for Standby mode. If either of timing is not satisfied, it takes trac (min) period from either last address transition or CE1 Low to High transition.

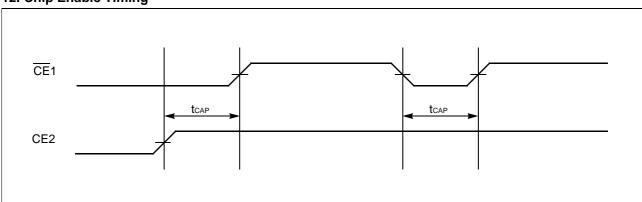

### 12. Chip Enable Timing

**Note:**  $t_{CAP}$  is not applicable CE2 HIGH pulse width while  $\overline{CE}1$  stays LOW and CE2 should not be used for any operation control after Power-up.

## **■ TIMING DIAGRAMS (Continued)**

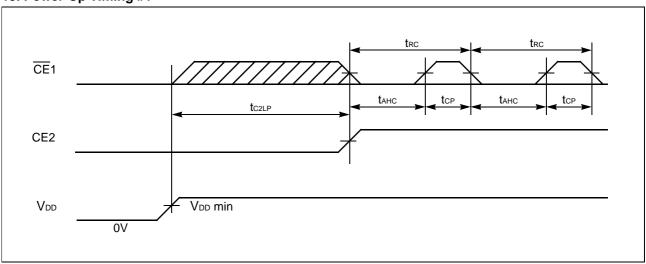

## 13. Power-Up Timing #1

Note: A minimum of two dummy read cycle must be performed prior to regular read and write operation after tc2LP.

## 14. Power-Up Timing #2

**Note:** No dummy read cycle is required if tc1HP is satisfied.

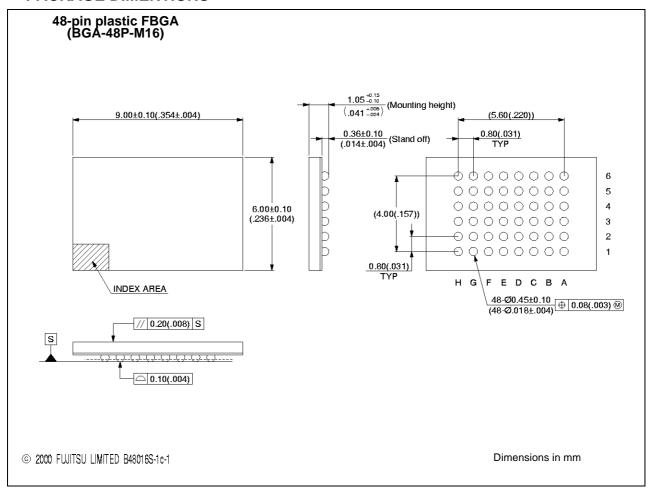

### ■ PACKAGE DIMENTIONS

## ■ ORDERING INFORMATION

| Part Number       | Package                               | Remarks                         |

|-------------------|---------------------------------------|---------------------------------|

| MB82D01160-90PBT  | Plastic FBGA 48-ball<br>(BGA-48P-M16) | I <sub>DDS1</sub> = 200 μA max. |

| MB82D01160-90LPBT | Plastic FBGA 48-ball<br>(BGA-48P-M16) | I <sub>DDS1</sub> = 100 μA max. |

## **FUJITSU LIMITED**

For further information please contact:

#### **Japan**

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices Shinjuku Dai-Ichi Seimei Bldg. 7-1, Nishishinjuku 2-chome, Shinjuku-ku, Tokyo 163-0721, Japan Tel: +81-3-5322-3347

Fax: +81-3-5322-3386

http://edevice.fujitsu.com/

#### **North and South America**

FUJITSU MICROELECTRONICS, INC. 3545 North First Street, San Jose, CA 95134-1804, U.S.A. Tel: +1-408-922-9000

Fax: +1-408-922-9179

Customer Response Center *Mon. - Fri.:* 7 am - 5 pm (*PST*) Tel: +1-800-866-8608

Fax: +1-408-922-9179

http://www.fujitsumicro.com/

#### **Europe**

FUJITSU MICROELECTRONICS EUROPE GmbH Am Siebenstein 6-10.

D-63303 Dreieich-Buchschlag,

Germany

Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://www.fujitsu-fme.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LTD. #05-08, 151 Lorong Chuan, New Tech Park,

Singapore 556741 Tel: +65-281-0770 Fax: +65-281-0220

http://www.fmap.com.sg/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 1702 KOSMO TOWER, 1002 Daechi-Dong, Kangnam-Gu, Seoul 135-280

Korea

Tel: +82-2-3484-7100 Fax: +82-2-3484-7111

F0101

© FUJITSU LIMITED Printed in Japan

All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

The contents of this document may not be reproduced or copied without the permission of FUJITSU LIMITED.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipments, industrial, communications, and measurement equipments, personal or household devices, etc.).

#### CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.