# **TOSHIBA**

**TOSHIBA CORPORATION**

Semiconductor Company

# Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions".

### CMOS 32-bit Micro-controller

# TMP92CM27FG

### Outline and Device Characteristics

TMP92CM27 is high-speed advanced 32-bit micro-controller developed for controlling equipment which processes mass data.

TMP92CM27 is a micro-controller which has a high-performance CPU (TLCS-900/H1 CPU) and various built-in I/Os.

TMP92CM27FG is housed in a 144-pin flat package.

Device characteristics are as follows:

- (1) CPU: 32-bit CPU(TLCS-900/H1 CPU)

- Compatible with TLCS-900/L1 instruction code

- 16Mbytes of linear address space

- · General-purpose register and register banks

- Micro DMA: 8channels (250ns/4bytes at fc = 40MHz, best case)

- (2) Minimum instruction execution time: 50ns(at fc=40MHz)

- (3) Internal memory

- Internal RAM: 32K-byte (32-bit 1 clock access and program execution are possible)

- Internal ROM: None

- (4) External memory expansion

- Expandable up to 16M bytes (shared program/data area)

- Can simultaneously support 8/16-bit width external data bus

- · · · Dynamic data bus sizing

- Separate bus system/

- (5) Memory controller

- Chip select output : 6 channels

030619EBP1

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in

general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility

of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire

system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life,

bodily injury or damage to property.

bodily injury of darnage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal design of the products is the products of the products in the product of the products in the product of the products in the products in the products are products and products in the product in the product

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

Purchase of TOSHIBA I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

92CM27-1 2005-04-20

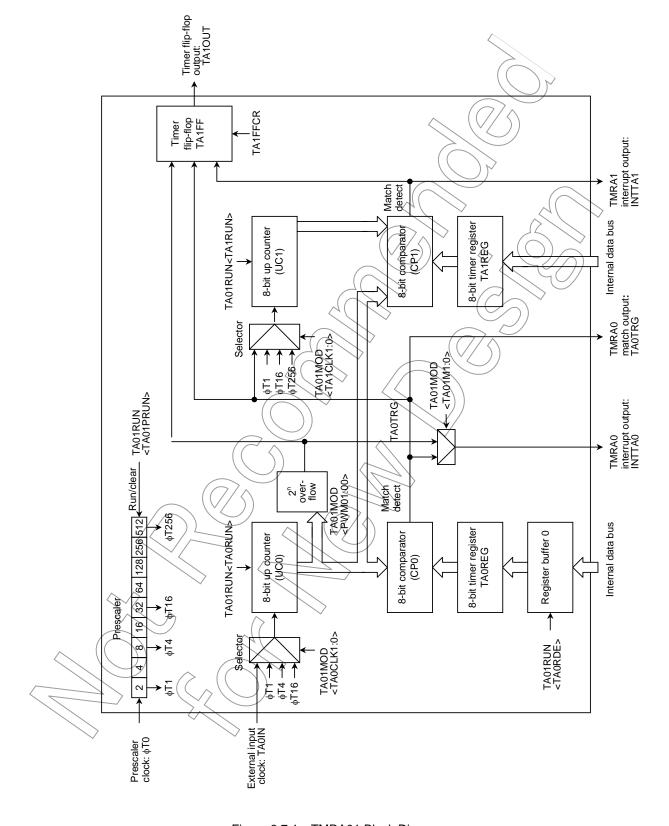

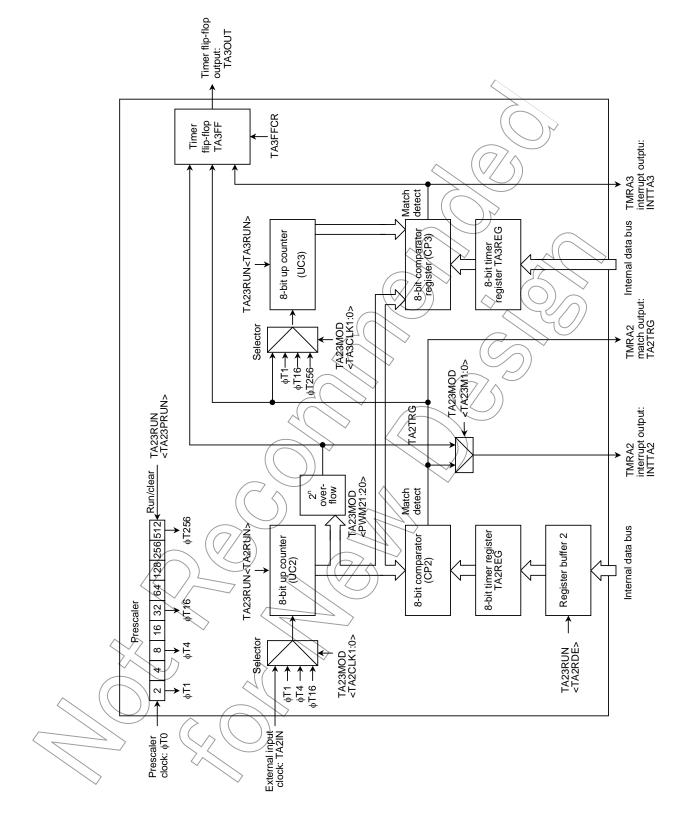

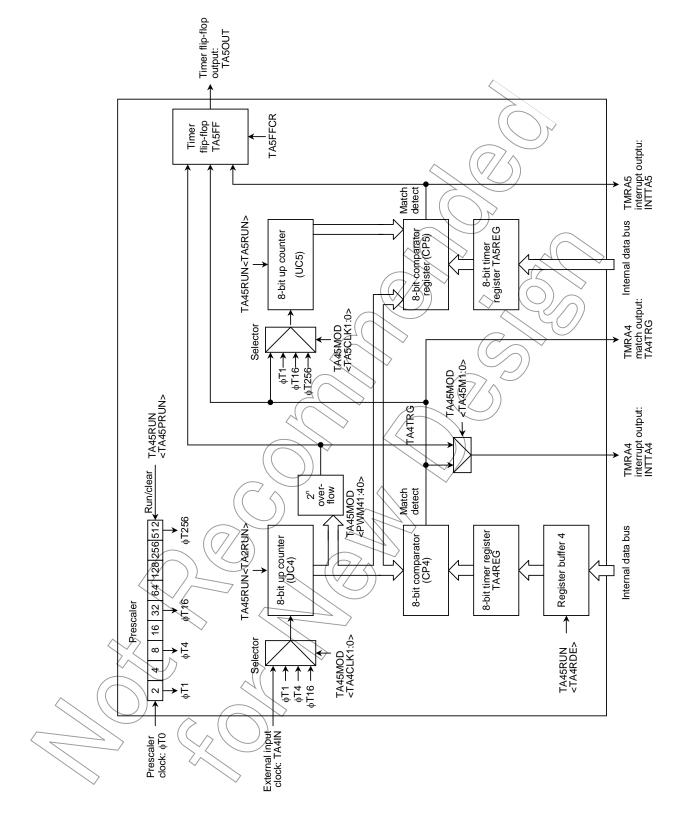

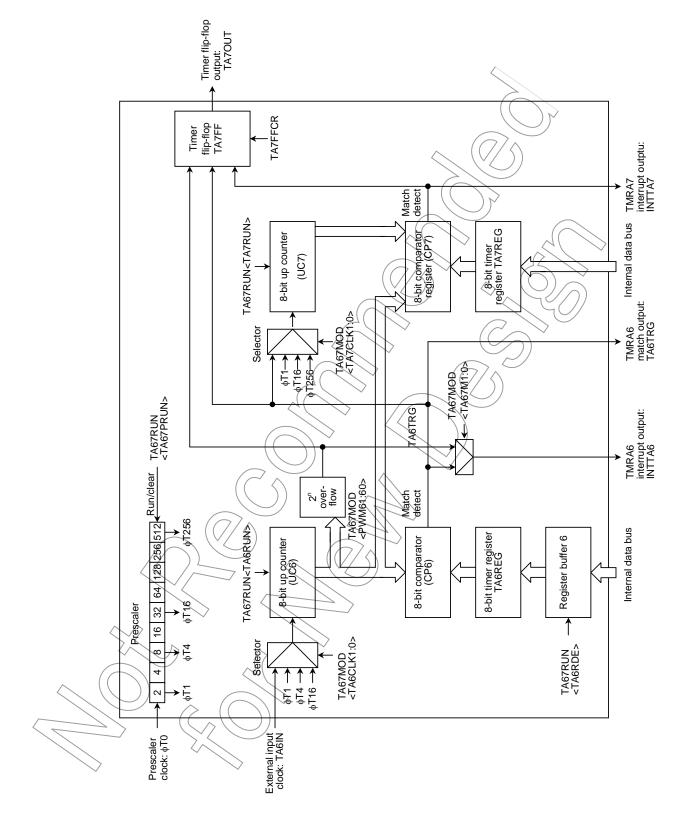

- (6) 8-bit timers: 8 channels

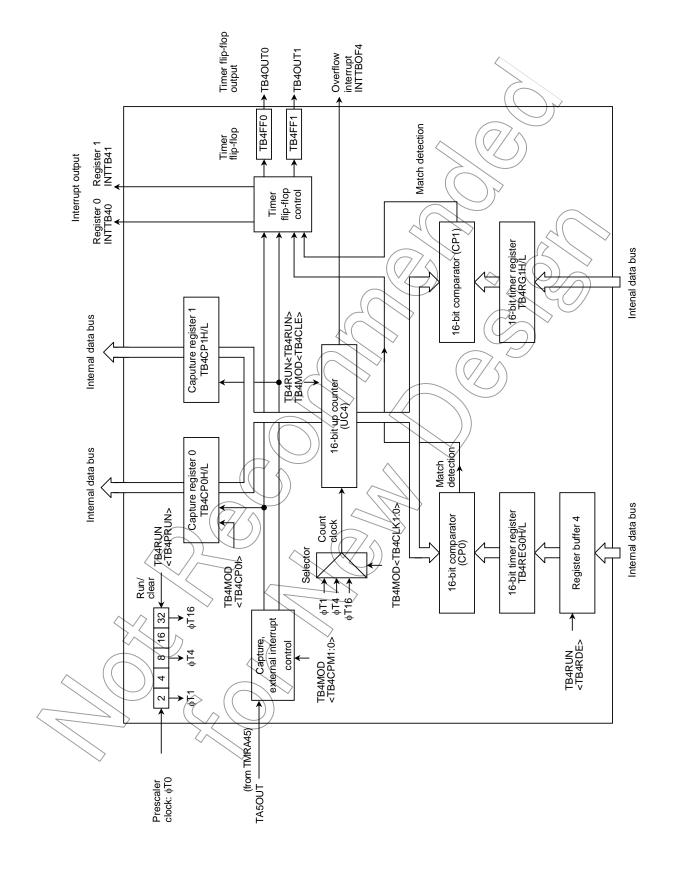

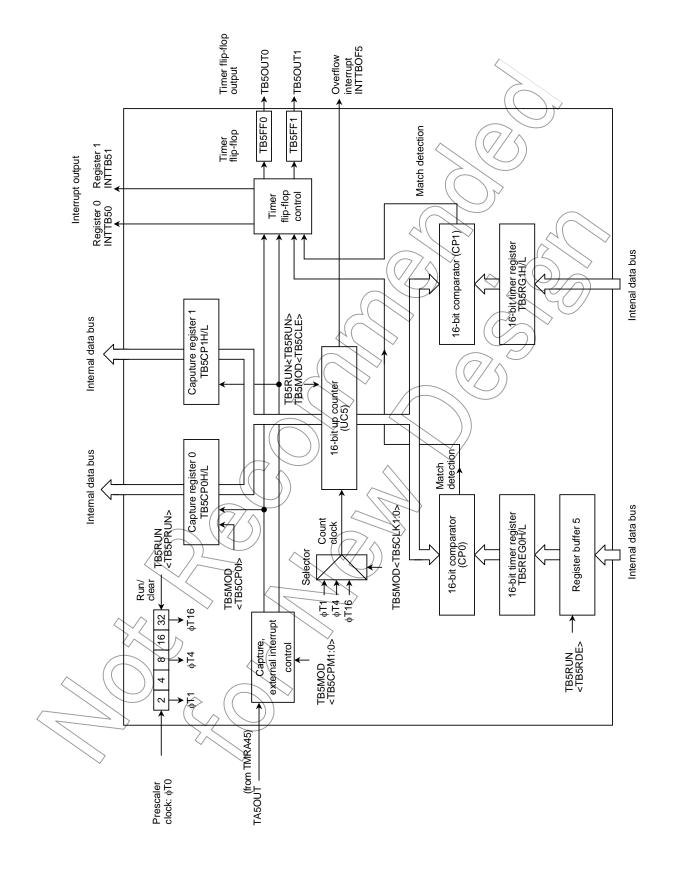

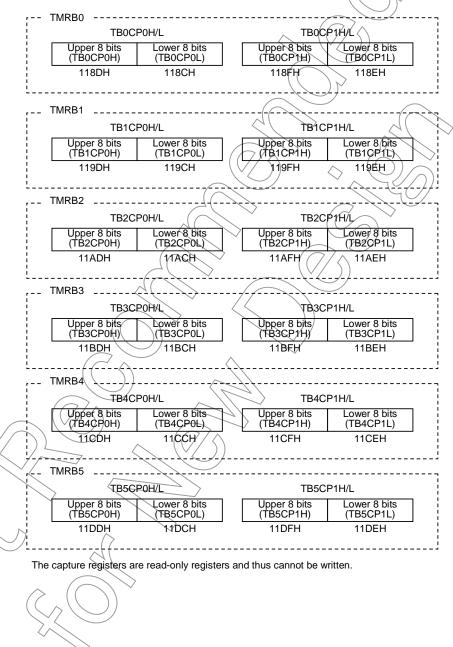

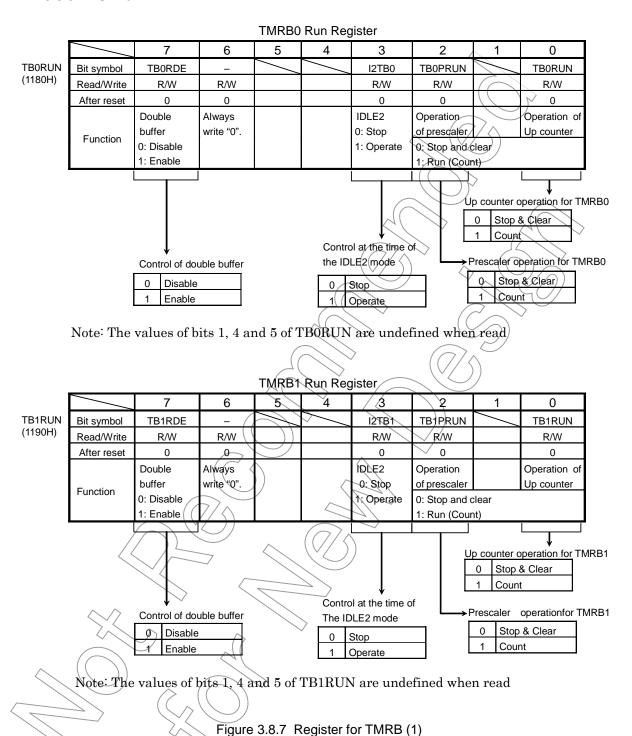

- (7) 16-bit timers: 6 channels

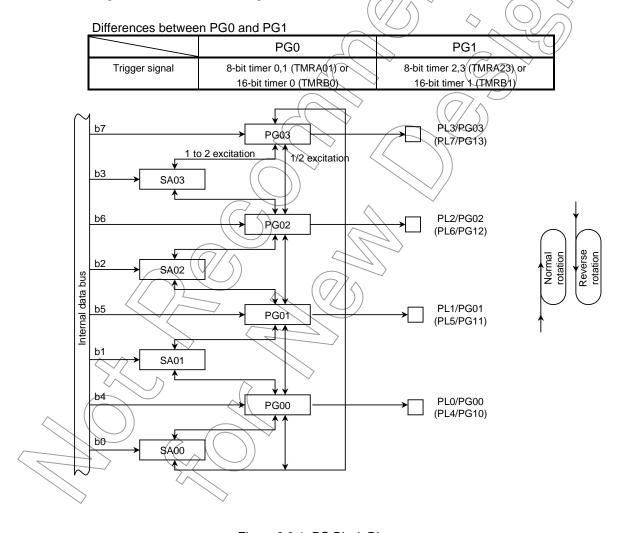

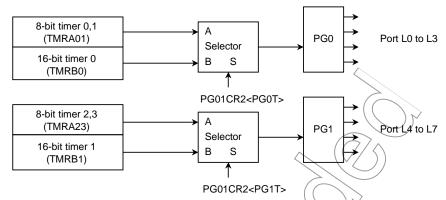

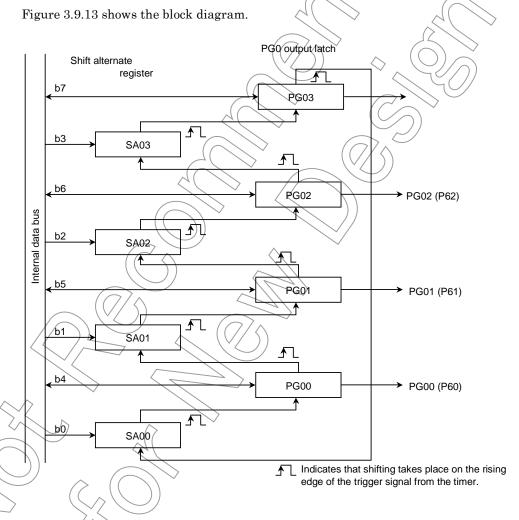

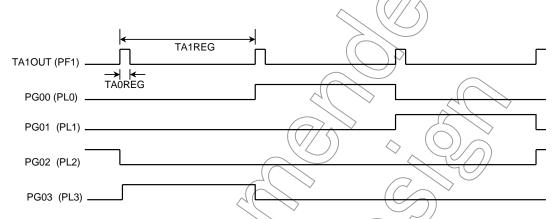

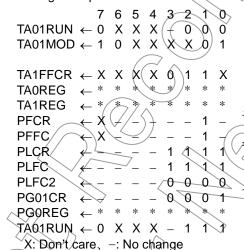

- (8) Pattern generator: 2 channels

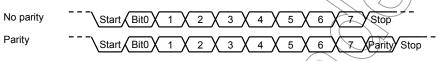

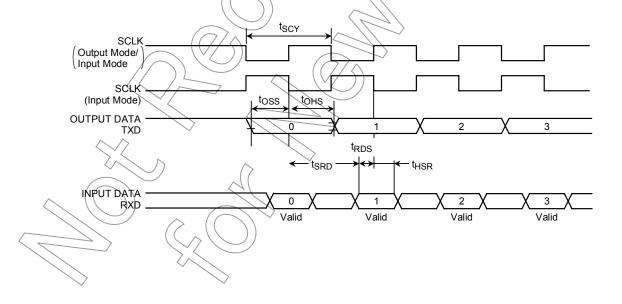

- (9) General-purpose serial interface: 4 channels

- UART/Synchronous mode: 4 channels (ch.0 to ch.3)

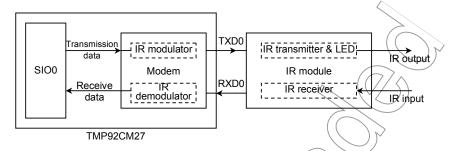

- IrDA Ver.1.0(115kbps) mode selectable : 1 channels (ch.0)

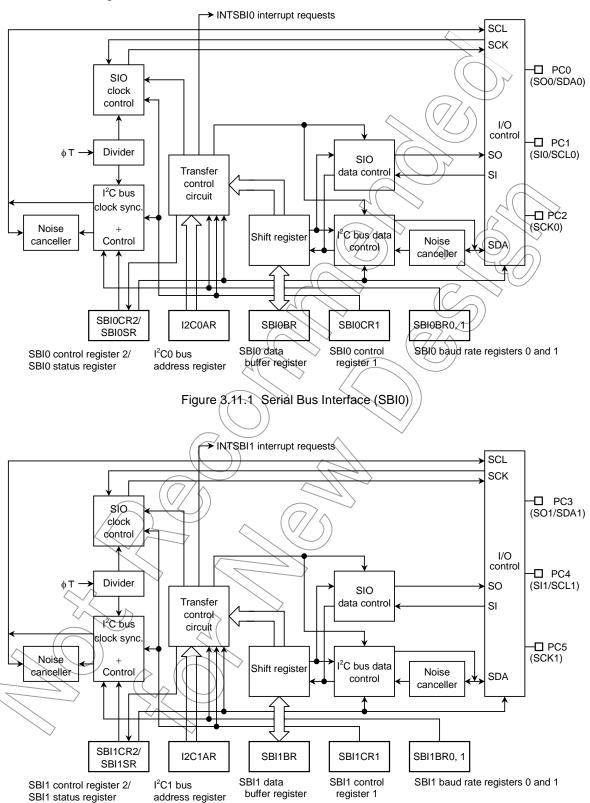

- (10) Serial bus interface: 2 channels

- I<sup>2</sup>C bus mode/clock synchronous mode selectable

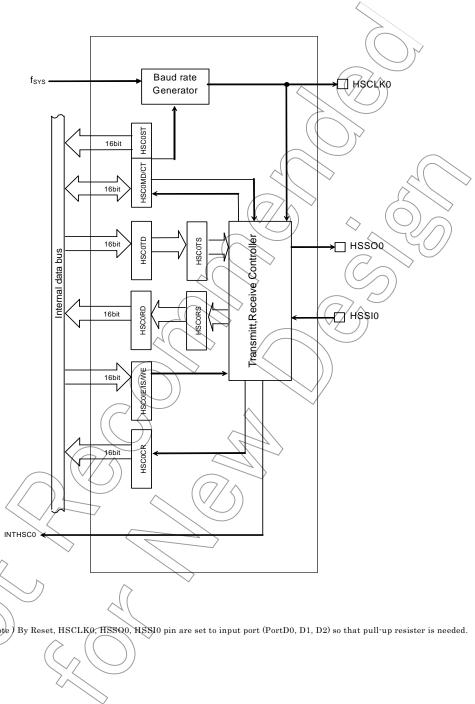

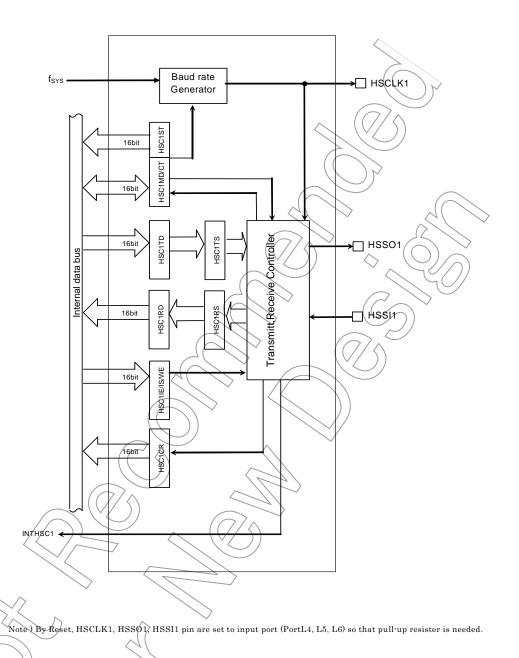

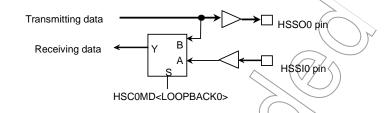

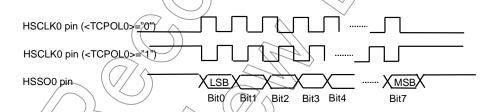

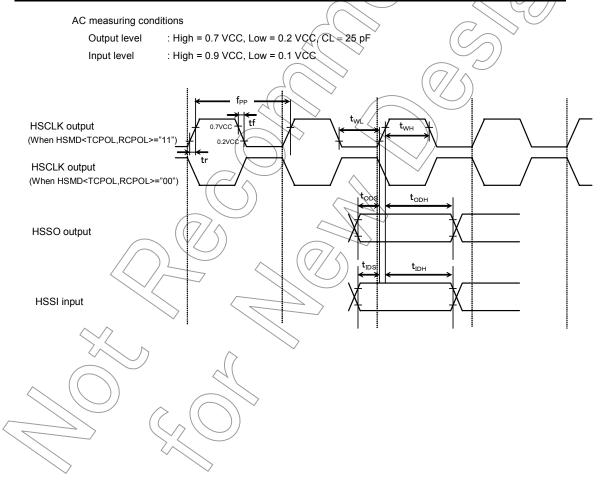

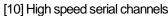

- (11) High Speed serial interface: 2 channels

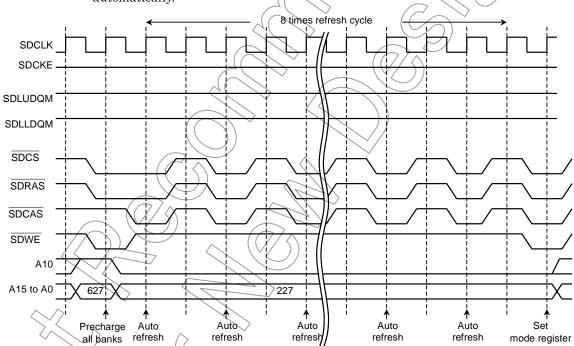

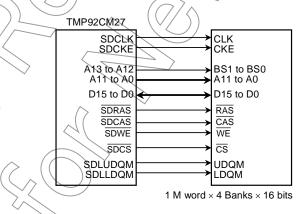

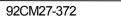

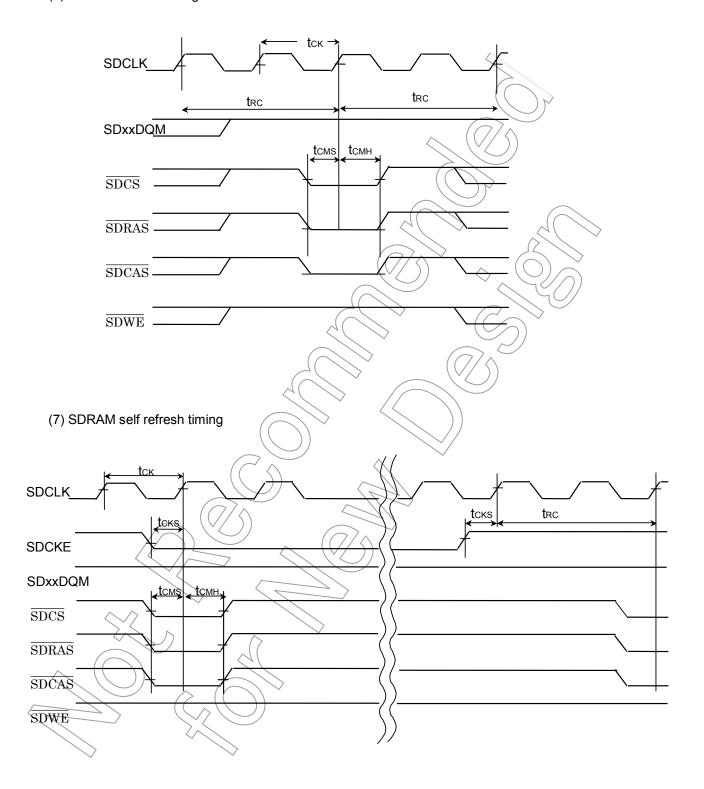

- (12) SDRAM controller: 1 channels

- Supported 16M, 64M-bit SDR (Single Data Rate)-SDRAM

- Supported not only operate as RAM and Data for LCD display but also programming directly from SDRAM

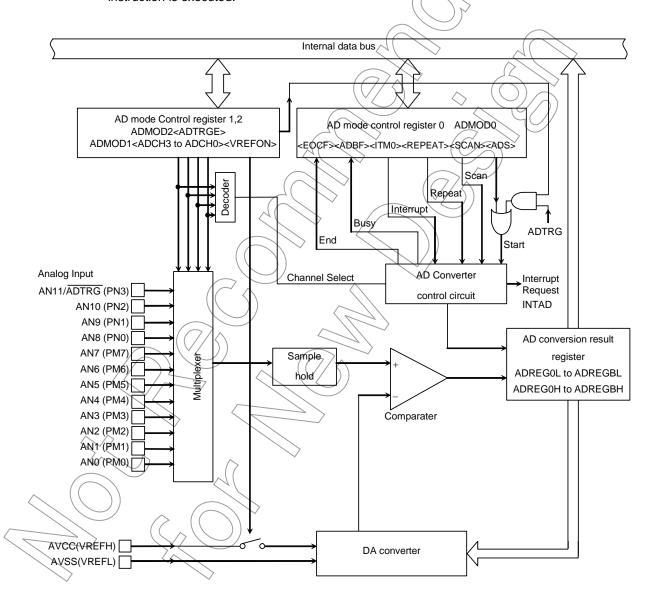

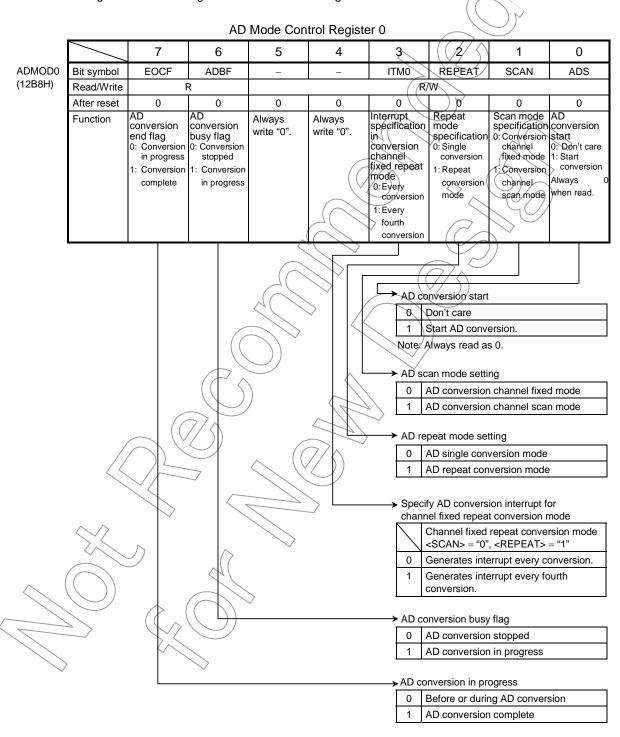

- (13) 10-bit AD converter: 12 channels

- (14) 8-bit DA converter: 2 channels

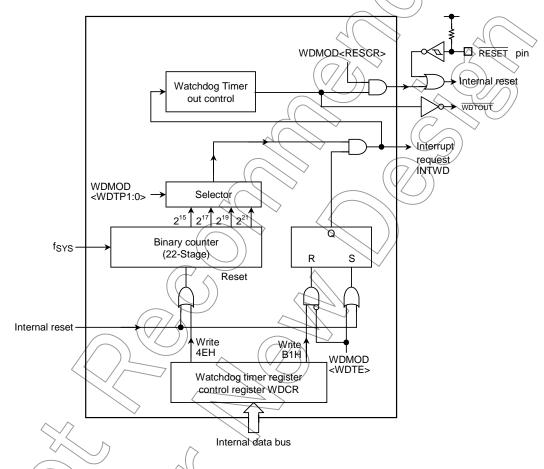

- (15) Watchdog timer

- (16) Key-on wake up (only for HALT release): 8 channels

- (17) Interrupts: 71 interrupts

- 9 CPU interrupts : Software interrupt instruction and illegal instruction

- 49 internal interrupts : Seven selectable priority levels

- 13 external interrupts(INT0 to INTB, NMI): Seven selectable priority levels (INT0 to INTB)

(INT0 to INTB are selectable edge or level interrupt)

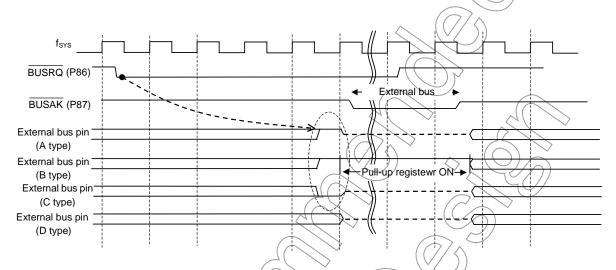

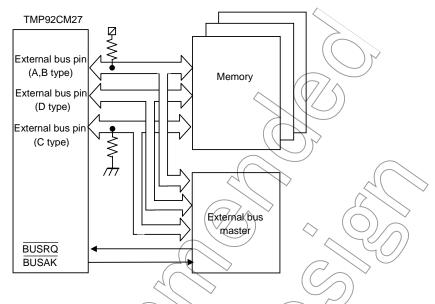

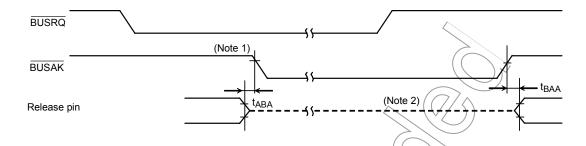

- (18) External bus release function

- (19) Input/output ports: 83 pins

- (20) Stand-by function

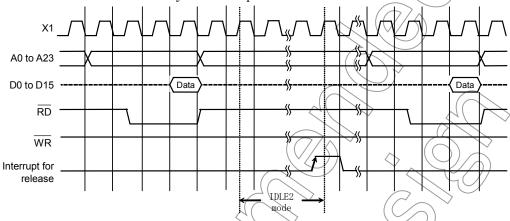

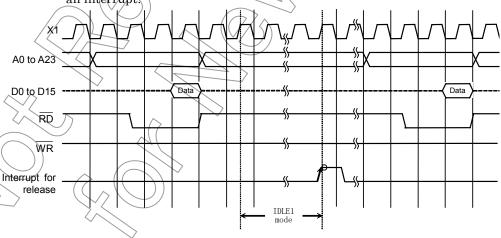

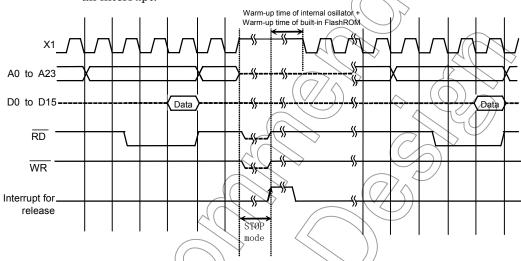

- Three Halt modes: Idle2 (programmable), Idle1, Stop

- (21) Clock controller

- Clock doubler (PLL): fc = f<sub>OSCH</sub>×4 (fc=40MHz @ f<sub>OSCH</sub>=10MHz)

- Clock gear function: Select a High-frequency clock fc to fc/16

- (22) Operating voltage

- VCC = 3.0 V to 3.6 V (fc max = 40MHz)

- (23) Package

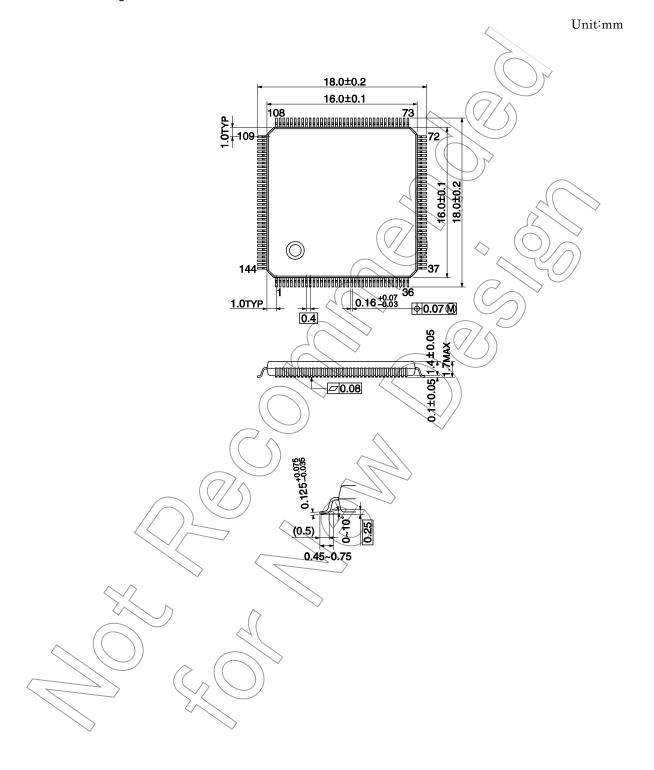

- 144 pin QFP : P-LQFP144-1616-0.40C

92CM27-2 2005-04-20

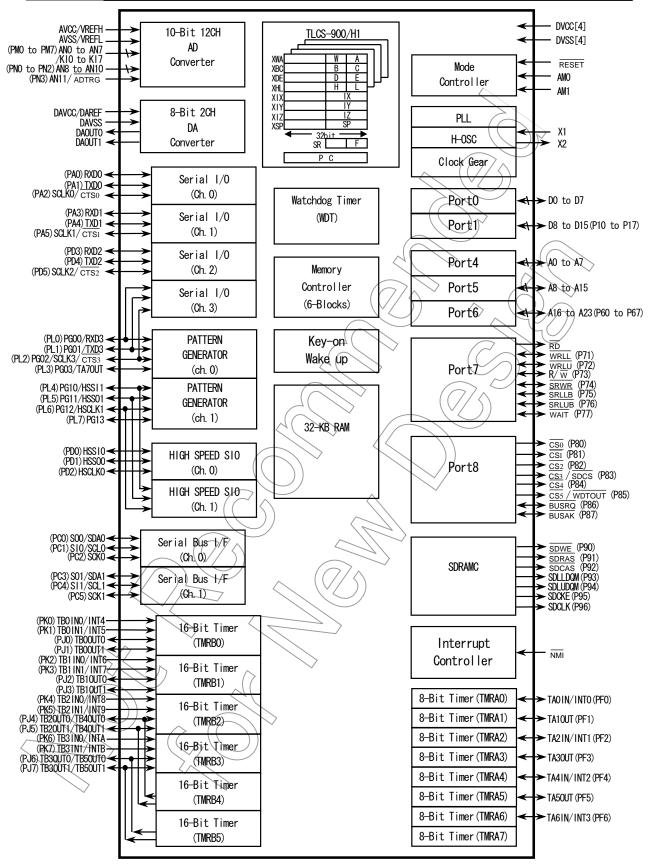

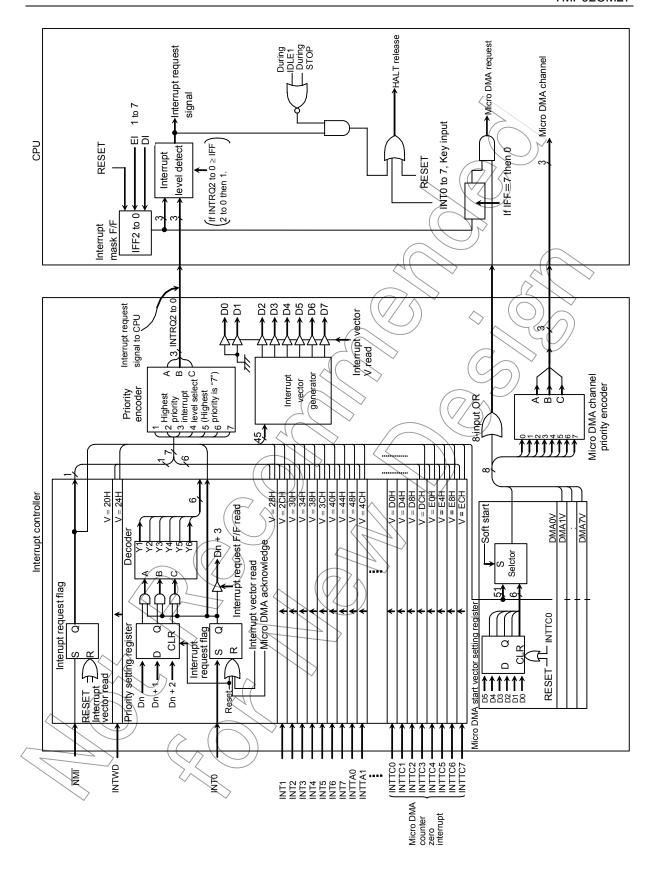

Figure 1.1 TMP92CM27 block diagram

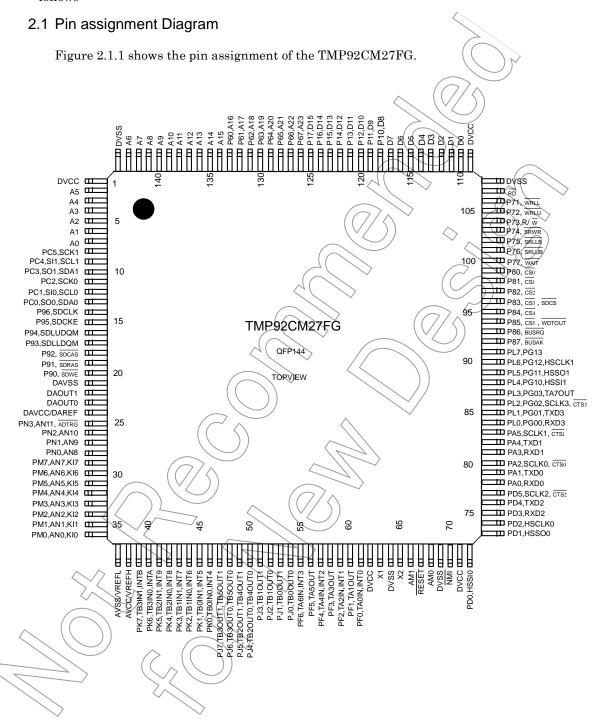

# 2. Pin assignment and pin functions

The assignment of input/output pins for the TMP92CM27, their names and functions are as follows:

Figure 2.1.1 Pin assignment diagram (144 pin LQFP)

92CM27-4 2005-04-20

# 2.2 Pin names and functions

The following table shows the names and functions of the input/output pins  $\,$

Table 2.2.1 Pin names and functions (1/5)

| Pin name                | Number of Pin | I/O        | Function                                                                               |

|-------------------------|---------------|------------|----------------------------------------------------------------------------------------|

| D0 to D7                | 8             | I/O        | Data: Data bus D0 to D7                                                                |

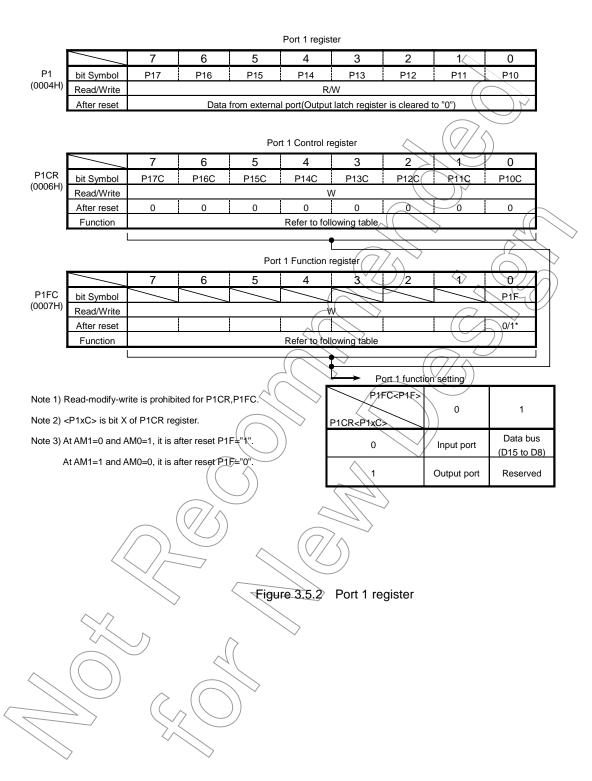

| P10 to P17<br>D8 to D15 | 8             | I/O<br>I/O | Port 1: I/O port Input or output specifiable in units of bits Data: Data bus D8 to D15 |

| A0 to A7                | 8             | Output     | Address: Address bus A0 to A7                                                          |

| A8 to A15               | 8             | Output     | Address: Address bus A8 to A15                                                         |

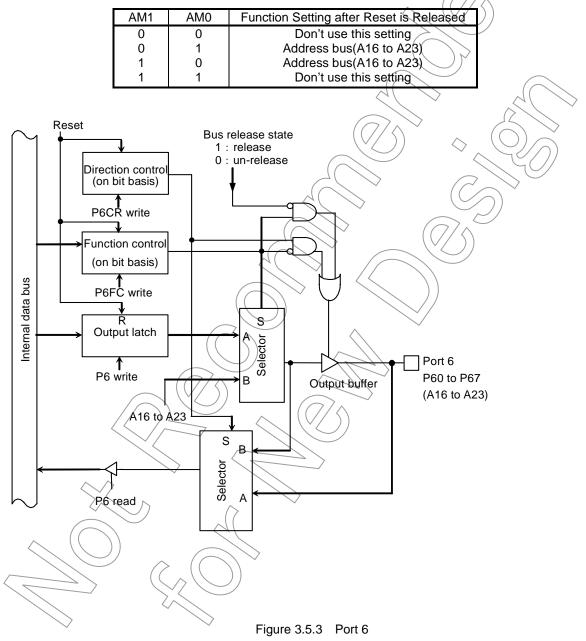

| P60 to P67              | 8             | I/O        | Port 6: I/O port                                                                       |

| A16 to A23              |               | Output     | Address: Address bus A16 to A23                                                        |

| RD                      | 1             | Output     | Read: Outputs strobe signal for read external memory (with pull-up register)           |

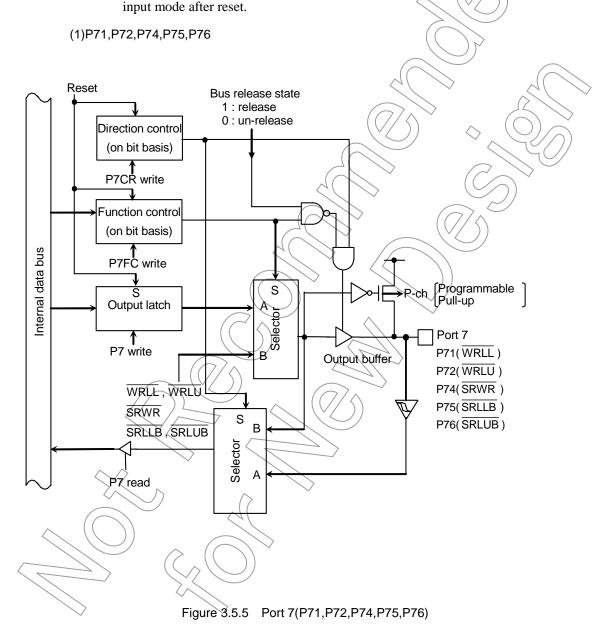

| P71                     | 1             | I/O        | Port 71: I/O port (Schmitt input, with pull-up register)                               |

| WRLL                    |               | Output     | Write: Output strobe signal for writing data on pins D0 to D7                          |

| P72                     | 1             | I/O        | Port 72: I/O port (schmitt/input, with-pull-up register)                               |

| WRLU                    |               | Output     | Write: Output strobe signal for writing data on pins D8 to D15                         |

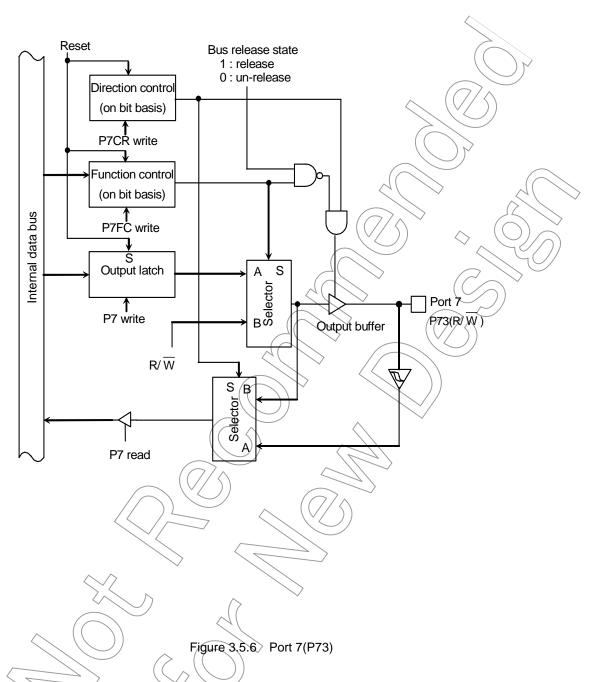

| P73                     | 1             | I/O        | Port 73: I/O port (schmitt input)                                                      |

| R/ W                    |               | Output     | Read/Write: 1 represents read or dummy cycle; 0 represents write cycle                 |

| P74                     | 1             | I/O        | Port 74: I/O port (Schmitt input, with pull-up register)                               |

| SRWR                    |               | Output     | Write enable for SRAM: Strobe signal for writing data                                  |

| P75                     | 1             | I/O        | Port 75: I/O port (Schmitt input, with pull-up register)                               |

| SRLLB                   |               | Output     | Data enable for SRAM on pins D0 to D7                                                  |

| P76                     | 1             | I/O        | Port 76: 1/Q port (Schmitt input, with pull-up register)                               |

| SRLUB                   |               | Output     | Data enable for SRAM on pins D8 to D15                                                 |

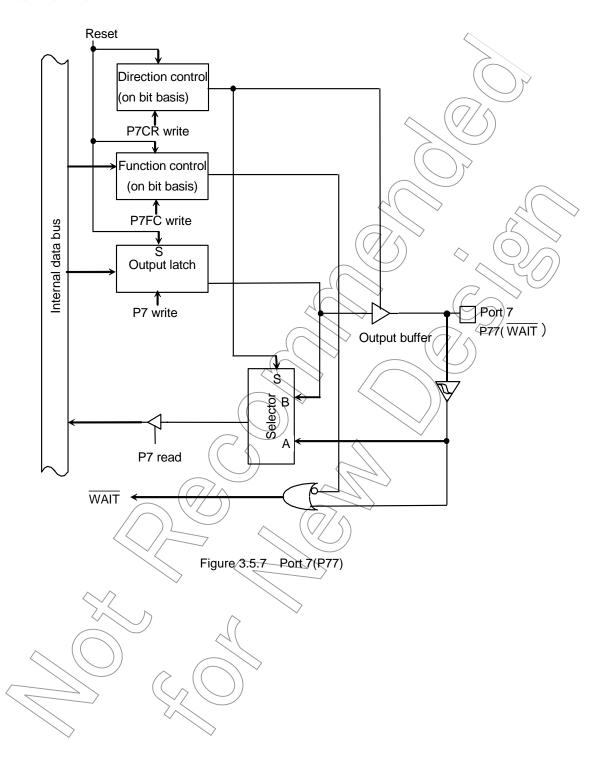

| P77                     | 1             | I/O        | Post 77: I/O port (Schmitt input)                                                      |

| WAIT                    |               | Input      | Wait: Signal used to request CPU bus wait                                              |

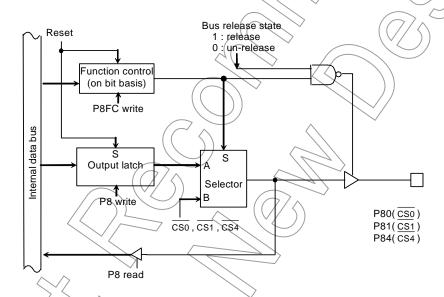

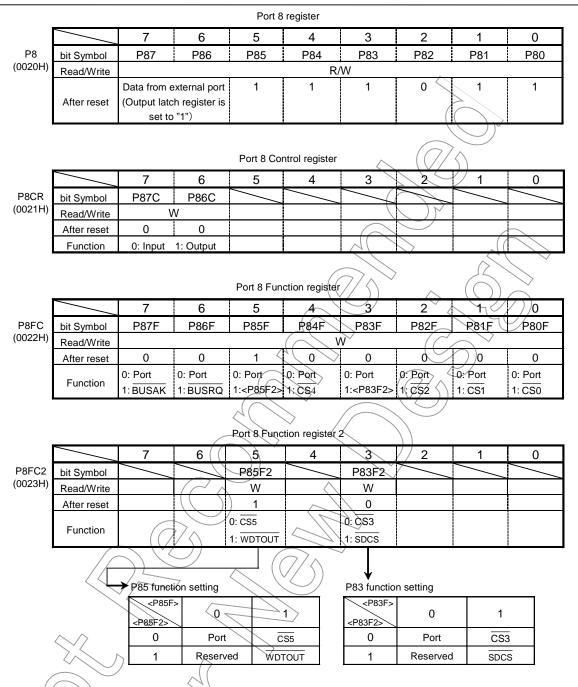

| P80                     | 1             | Output     | Rort 80; Output port                                                                   |

| CS0                     |               | Output     | Chip select 0: Outputs "Low" when address is within specified address area             |

| P81                     | 1 _           | Output/    | Port 81: Output port                                                                   |

| CS1                     |               | Output     | Chip select 1: Outputs "Low" when address is within specified address area             |

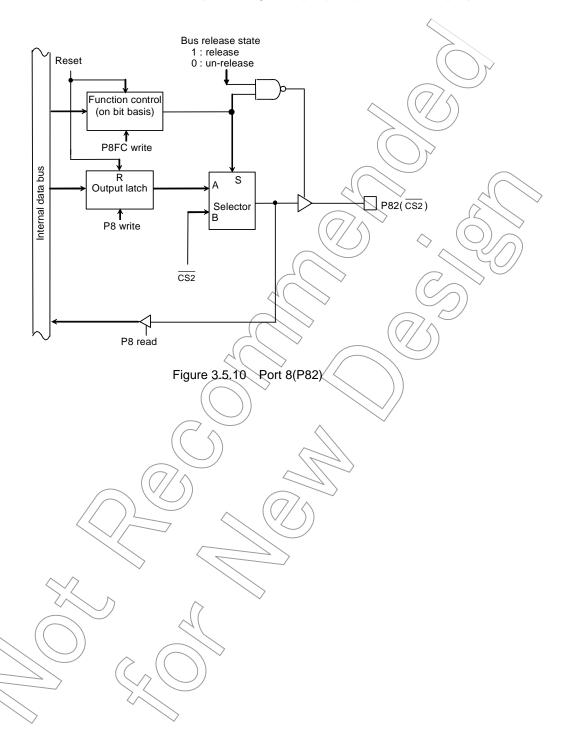

| P82                     | /4            | Output     | Port 82: Output port                                                                   |

| CS2                     |               | Output     | Chip select 2: Outputs "Low" when address is within specified address area             |

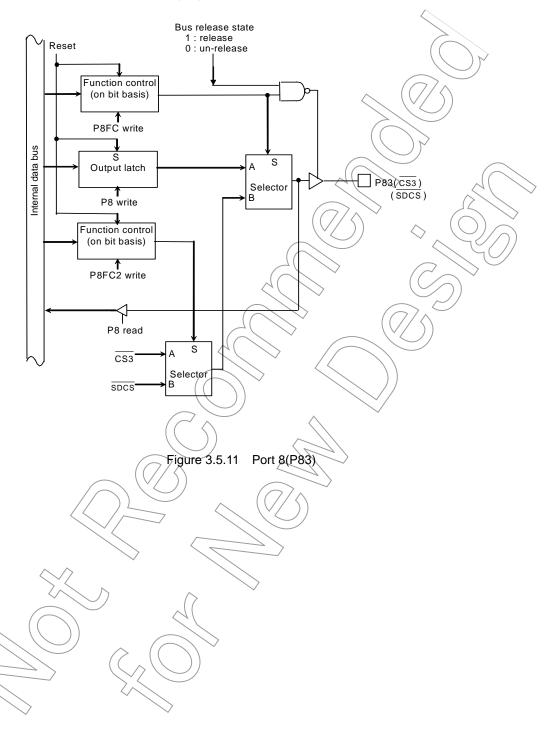

| P83                     | 1             | Qutput     | Port 83: Output port                                                                   |

| CS3                     |               | Output     | Chip select 3: Outputs "Low" when address is within specified address area             |

| SDCS                    | $\Diamond$    | Output     | Chip select for SDRAM: Outputs "Low" when address is within SDRAM address area         |

| P84                     | V1 D          | Output     | Pôrt 84: Output port                                                                   |

| CS4                     |               | Output     | Chip select 4: Outputs "Low" when address is within specified address area             |

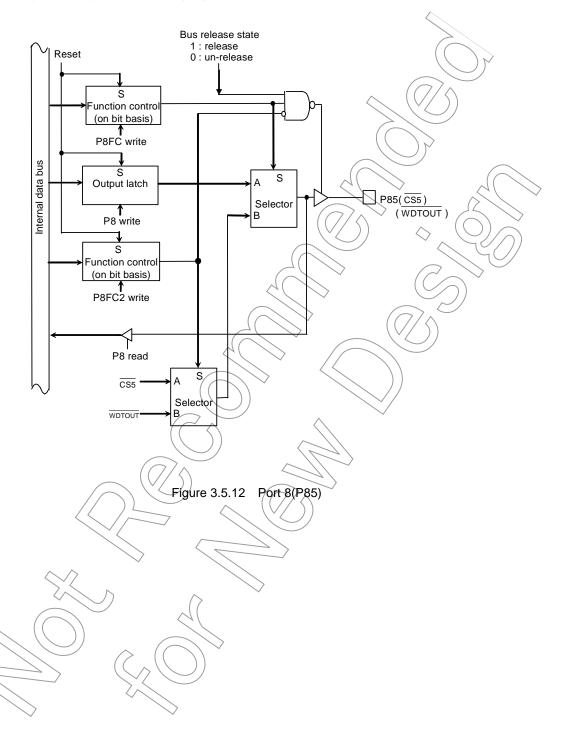

| P85                     | 1             | Output     | Port 85: Output port                                                                   |

| CS5                     | <i>)</i> ) '  | Output     | Chip select 5: Outputs "Low" when address is within specified address area             |

| WDTOUT                  |               | Output     | Watchdog timer output pin                                                              |

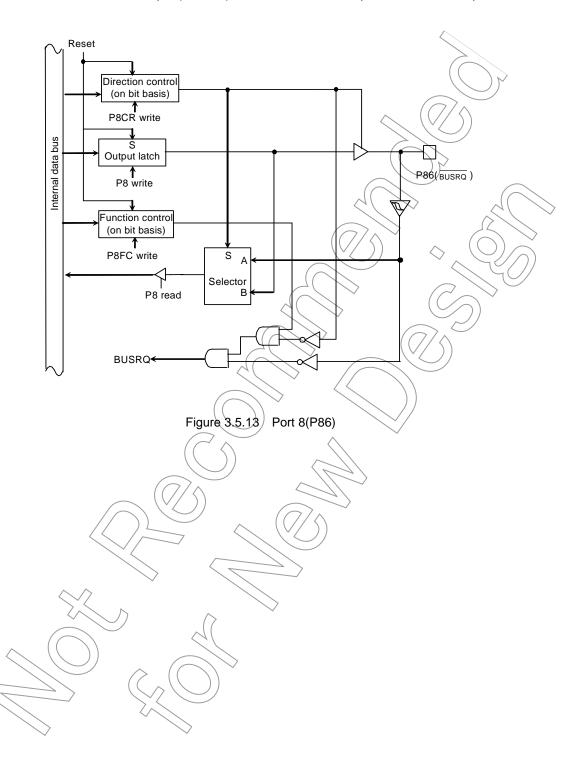

| P86                     | 1             | 160        | Port 86: I/O port (Schmitt input)                                                      |

| BUSRQ                   | '             | Input      | Bus request: request pin that set external memory bus to high-impedance                |

| 2001/0                  |               |            | (for External DMAC)                                                                    |

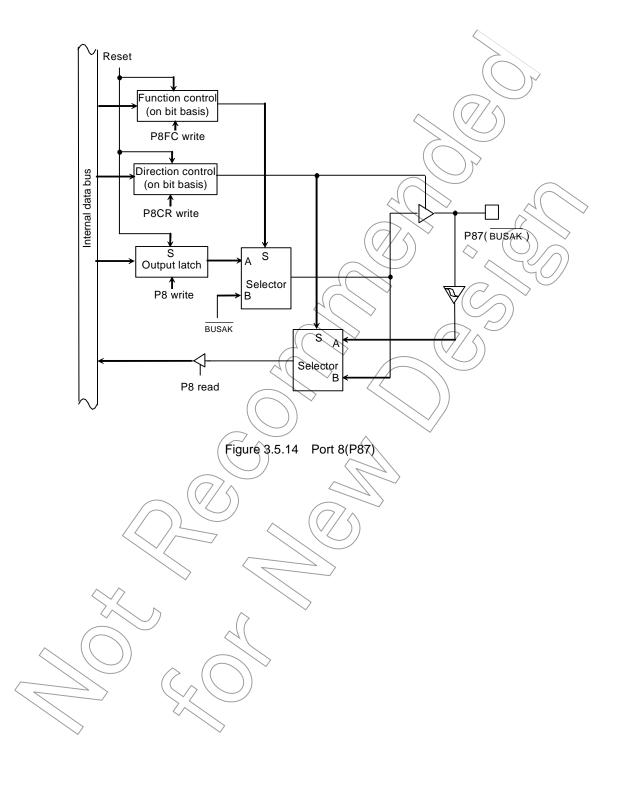

| P87                     | 1             | I/O        | Port 87: I/O port (Schmitt input)                                                      |

| BUSAK                   |               | Output     | Bus acknowledge: this pin show that external memory bus pin is set to high-impedance   |

|                         |               |            | by receiving BUSRQ (for External DMAC)                                                 |

Table 2.2.2 Pin names and functions (2/5)

| Pin name   | Number<br>of Pin | I/O           | Function                                                                                                       |  |  |  |

|------------|------------------|---------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

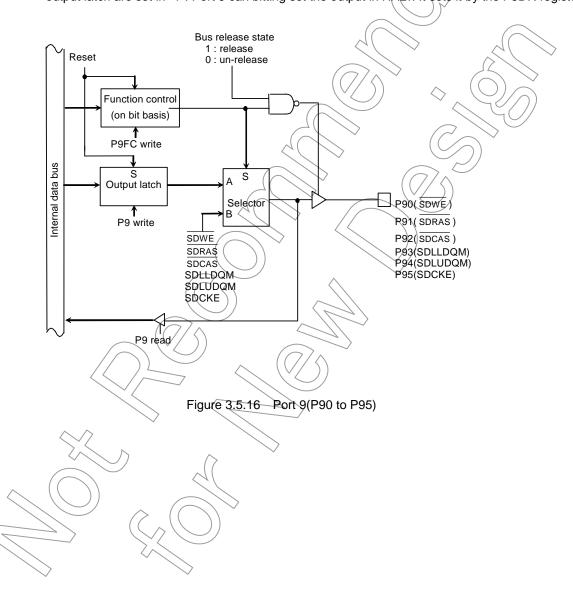

| P90        | 1                | Output        | Port 90: Output port                                                                                           |  |  |  |

| SDWE       |                  | Output        | Write enable for SDRAM                                                                                         |  |  |  |

| P91        | 1                | Output        | Port 91: Output port                                                                                           |  |  |  |

| SDRAS      |                  | Output        | Row address strobe for SDRAM                                                                                   |  |  |  |

| P92        | 1                | Output        | Port 92: Output port                                                                                           |  |  |  |

| SDCAS      |                  | Output        | Column address strobe for SDRAM                                                                                |  |  |  |

| P93        | 1                | Output        | Port 93: Output port                                                                                           |  |  |  |

| SDLLDQM    | · ·              | Output        | Data enable for SDRAM on pins D0 to D7                                                                         |  |  |  |

| P94        | 1                | Output        | Port 94: Output port                                                                                           |  |  |  |

| SDLUDQM    |                  | Output        | Data enable for SDRAM on pins D8 to D15                                                                        |  |  |  |

| P95        | 1                | Output        | Port 95: Output port                                                                                           |  |  |  |

| SDCKE      |                  | Output        | Clock enable for SDRAM                                                                                         |  |  |  |

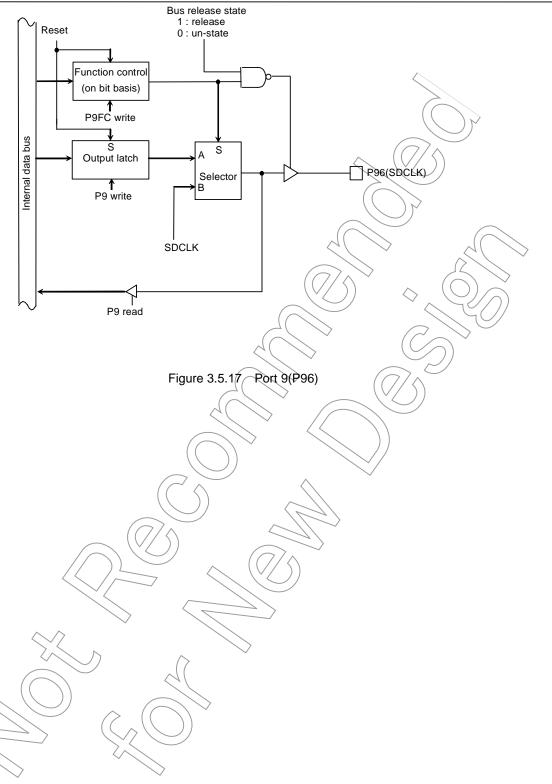

| P96        | 1                | Output        | Port 96: Output port                                                                                           |  |  |  |

| SDCLK      |                  | Output        | Clock for SDRAM                                                                                                |  |  |  |

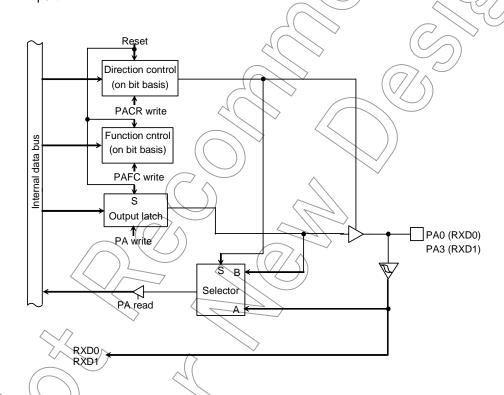

| PA0        | 1                | I/O           | Port A0: I/O port (Schmitt input)                                                                              |  |  |  |

| RXD0       |                  | Input         | Serial 0 receive data                                                                                          |  |  |  |

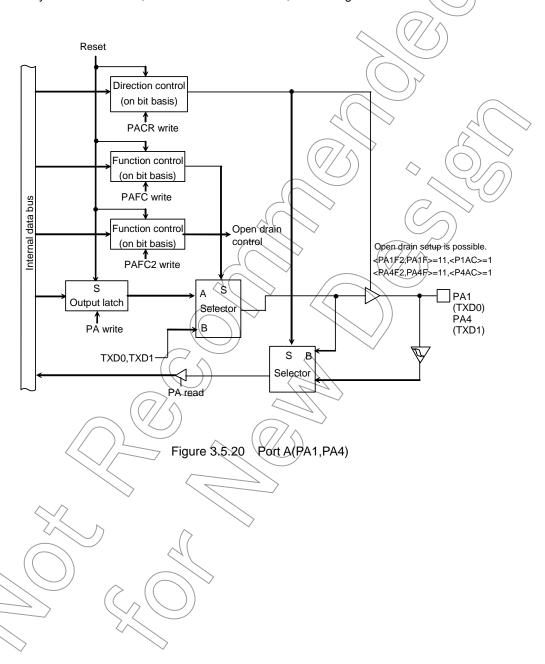

| PA1        | 1                | I/O           | Port A1: I/O port (Schmitt input)                                                                              |  |  |  |

| TXD0       |                  | Output        | Serial 0 send data: Open-drain output programmable                                                             |  |  |  |

| PA2        | 1                | I/O           | Port A2: I/O port (Schmitt input)                                                                              |  |  |  |

| SCLK0      |                  | I/O           | Serial 0 clock I/O                                                                                             |  |  |  |

| CTS0       |                  | Input         | Serial 0 data send enable (Clear To Send)                                                                      |  |  |  |

| PA3        | 1                | I/O           | Port A3: I/O port (Schmitt input)                                                                              |  |  |  |

| RXD1       |                  | Input         | Serial 1 receive data                                                                                          |  |  |  |

| PA4        | 1                | I/O           | Port A4: 1/O port (Schmitt input)                                                                              |  |  |  |

| TXD1       |                  | Output        | Serial 1 send data: Open-drain output programmable                                                             |  |  |  |

| PA5        | 1                | I/O           | Port A5: I/O port (Schmitt input)                                                                              |  |  |  |

| SCLK1      |                  | I/O           | Serial 1 ctock I/O                                                                                             |  |  |  |

| CTS1       |                  | Input         | Serial 1 data send enable (Clear To Send)                                                                      |  |  |  |

| PC0        | 1                | 1/0           | Port C0: I/O port (Schmitt input)                                                                              |  |  |  |

| SO0        |                  | Output /      | Serial bus interface 0 send data at SIO mode                                                                   |  |  |  |

| SDA0       |                  | / N/Q/        | Serial bus interface 0 send/receive data at I <sup>2</sup> C mode                                              |  |  |  |

|            |                  |               | Open-drain output programmable                                                                                 |  |  |  |

| PC1        | (1)              | 770           | Port C1-1/O port (Schmitt input)                                                                               |  |  |  |

| SIO        |                  | Input         | Serial bus interface 0 receive data at SIO mode                                                                |  |  |  |

| SCL0       |                  | 1/0           | Serial bus interface 0 clock I/O data at I <sup>2</sup> C mode                                                 |  |  |  |

| D00 ^      | ^ .              | \<br>\<br>    | Open-drain output programmable                                                                                 |  |  |  |

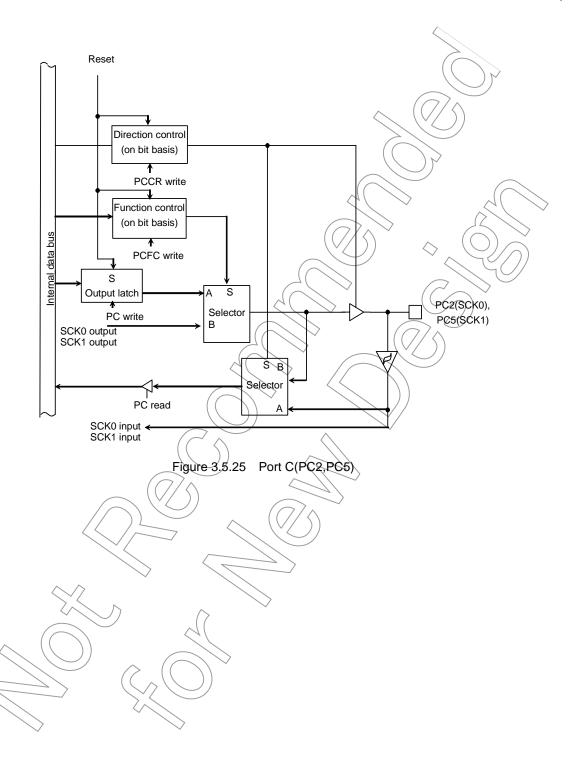

| PC2        | 2 1              | 1/0           | Port C2: I/O port (Schmitt input)                                                                              |  |  |  |

| SCK0       |                  | 1/0           | Serial bus interface 0 clock I/O data at SIO mode                                                              |  |  |  |

| PC3<br>SO1 |                  | I/O<br>Output | Port C3: I/O port (Schmitt input) Serial bus interface 1 send data at SIO mode                                 |  |  |  |

| SDA1       |                  | Output<br>I/O | Serial bus interface 1 send data at SIO mode Serial bus interface 1 send/receive data at I <sup>2</sup> C mode |  |  |  |

| OBA (      |                  | _ ",0         | Open-drain output programmable                                                                                 |  |  |  |

| PC4        | 1 (              | ) ON          | Port/C4: I/O port (Schmitt input)                                                                              |  |  |  |

| SIT        | ·                | Input         | Serial bus interface 1 receive data at SIO mode                                                                |  |  |  |

| SCL1       |                  | 1/0           | Serial bus interface 1 clock I/O data at I <sup>2</sup> C mode                                                 |  |  |  |

|            |                  |               | Open-drain output programmable                                                                                 |  |  |  |

| PC5        | 1                | I/O           | Port C5: I/O port (Schmitt input)                                                                              |  |  |  |

| SCK1       |                  | I/O           | Serial bus interface 1 clock I/O data at SIO mode                                                              |  |  |  |

Table 2.2.3 Pin names and functions (3/5)

|           | Number              |                                        | ,                                                                                          |

|-----------|---------------------|----------------------------------------|--------------------------------------------------------------------------------------------|

| Pin name  | of Pin              | I/O                                    | Function                                                                                   |

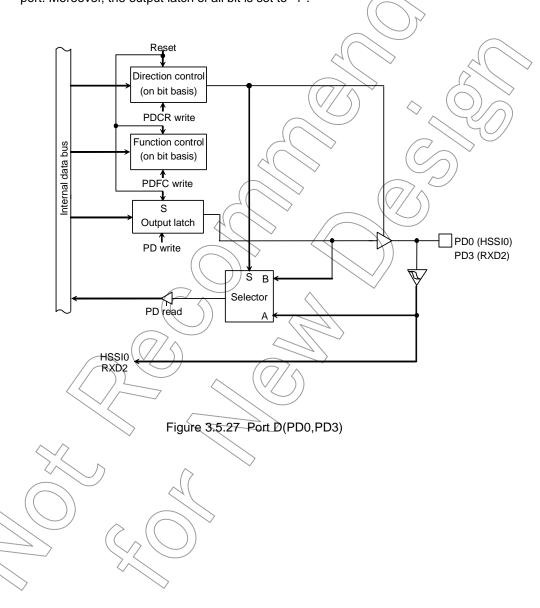

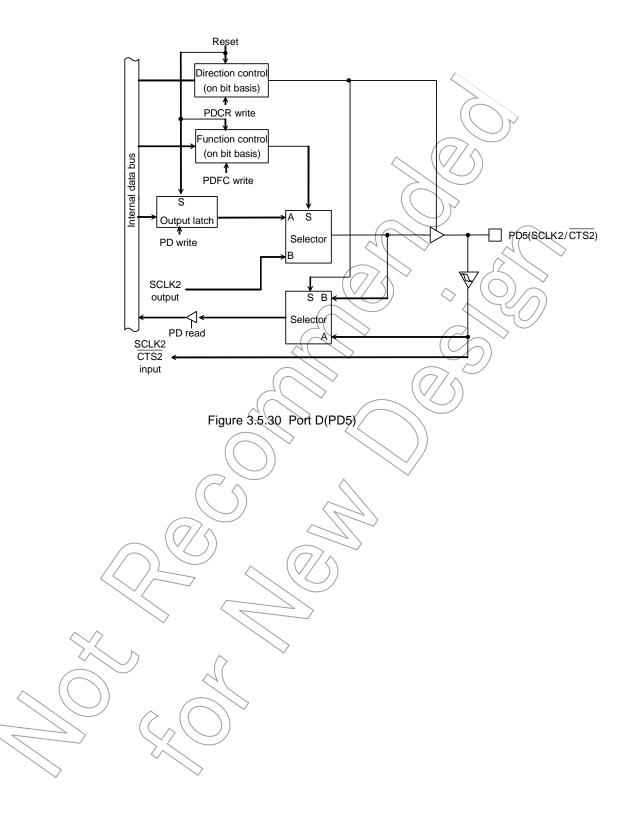

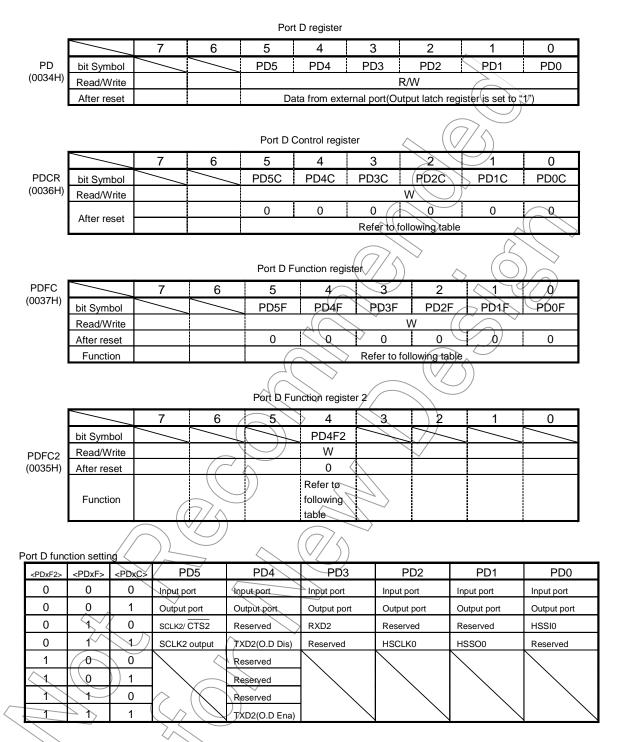

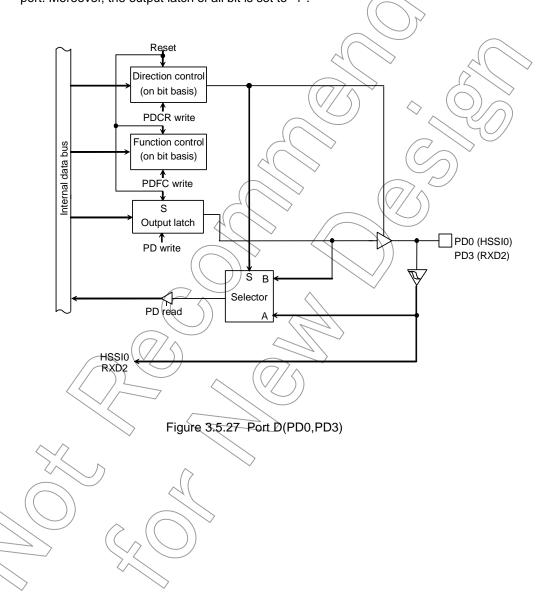

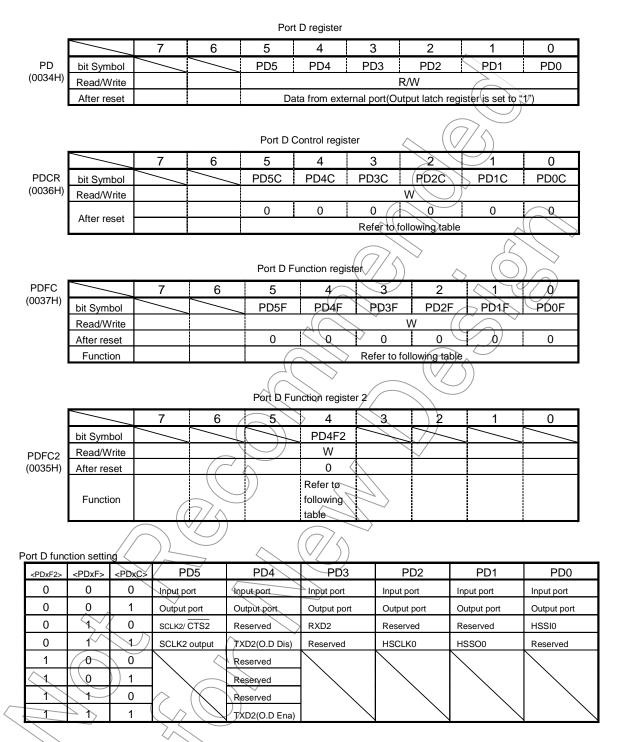

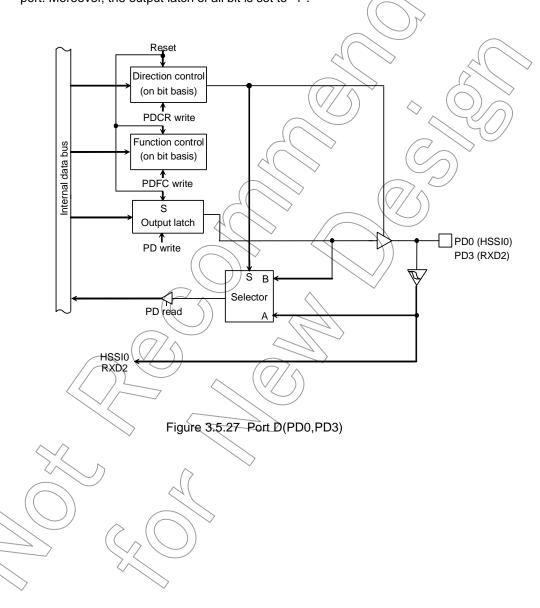

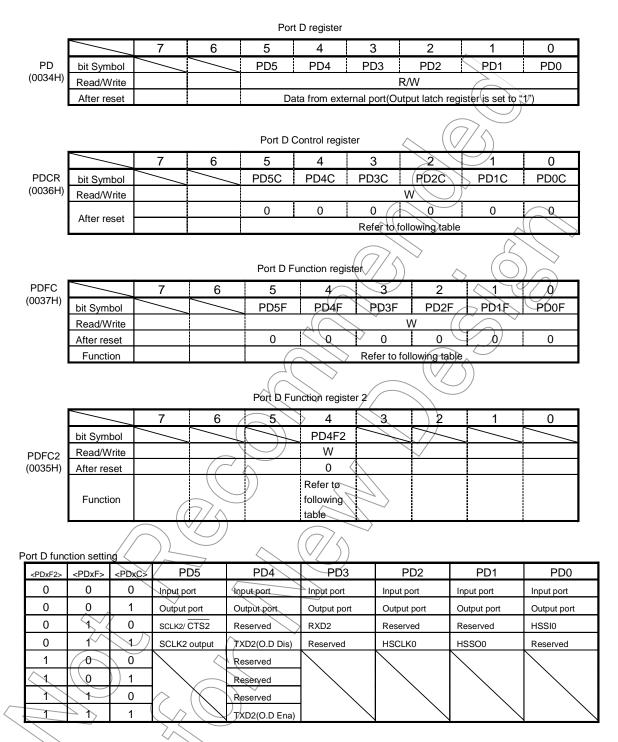

| PD0       | 1                   | I/O                                    | Port D0: I/O port                                                                          |

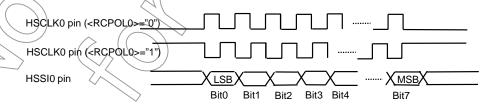

| HSSI0     |                     | Input                                  | High speed Serial 0 receive data                                                           |

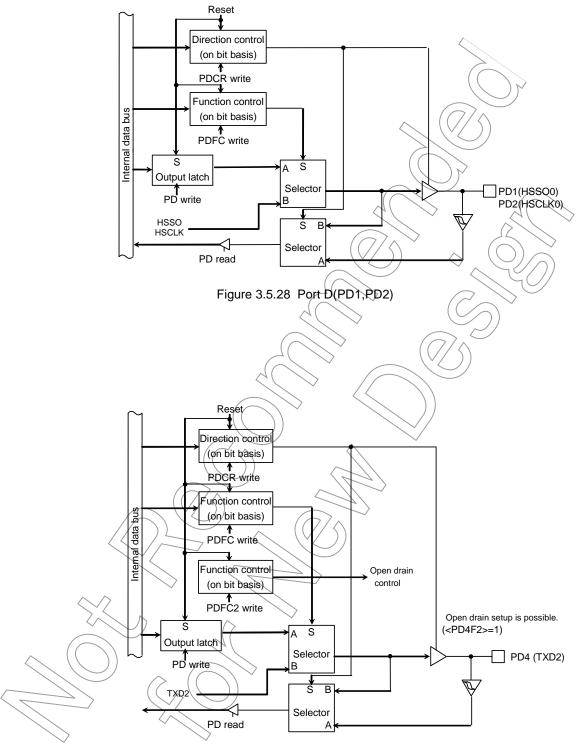

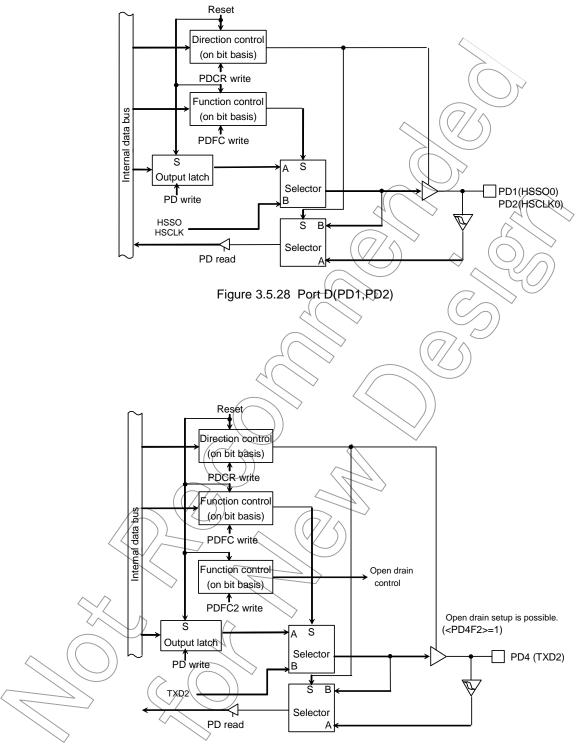

| PD1       | 1                   | I/O                                    | Port D1: I/O port (Schmitt input)                                                          |

| HSSO0     |                     | Output                                 | High speed Serial 0 send data                                                              |

| PD2       | 1                   | I/O                                    | Port D2: I/O port (Schmitt input)                                                          |

| HSCLK0    |                     | Output                                 | High speed Serial 0 clock I/O                                                              |

| PD3       | 1                   | I/O                                    | Port D3: I/O port (Schmitt input)                                                          |

| RXD2      |                     | Input                                  | Serial 2 receive data                                                                      |

| PD4       | 1                   | I/O                                    | Port D4: I/O port (Schmitt input)                                                          |

| TXD2      |                     | Output                                 | Serial 2 send data: Open-drain output programmable                                         |

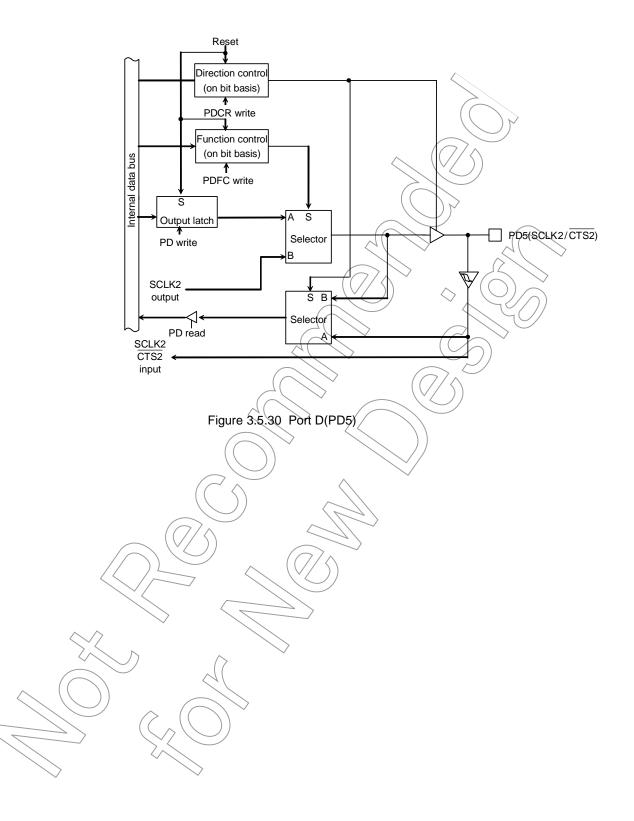

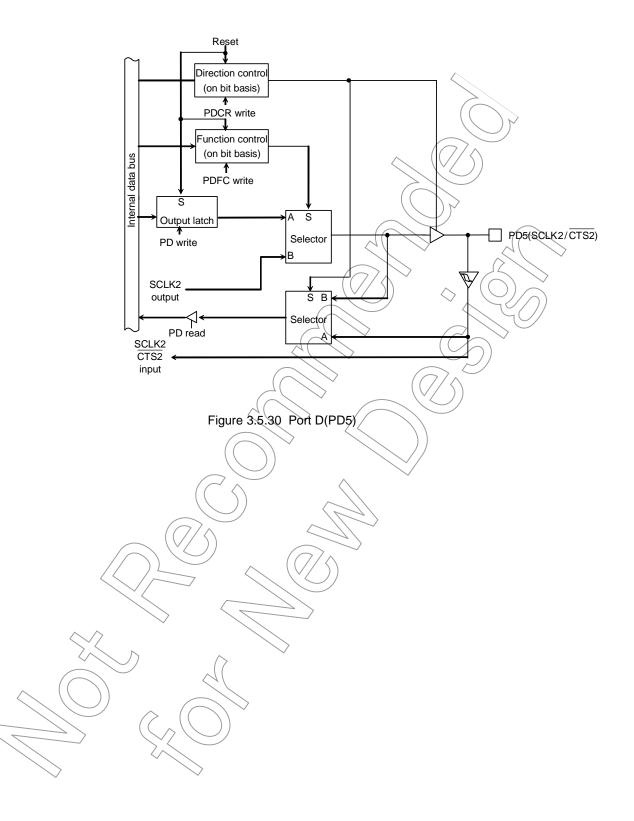

| PD5       | 1                   | I/O                                    | Port D5: I/O port (Schmitt input)                                                          |

| SCLK2     |                     | I/O                                    | Serial 2 clock I/O                                                                         |

| CTS2      |                     | Input                                  | Serial 2 data send enable (Clear To Send)                                                  |

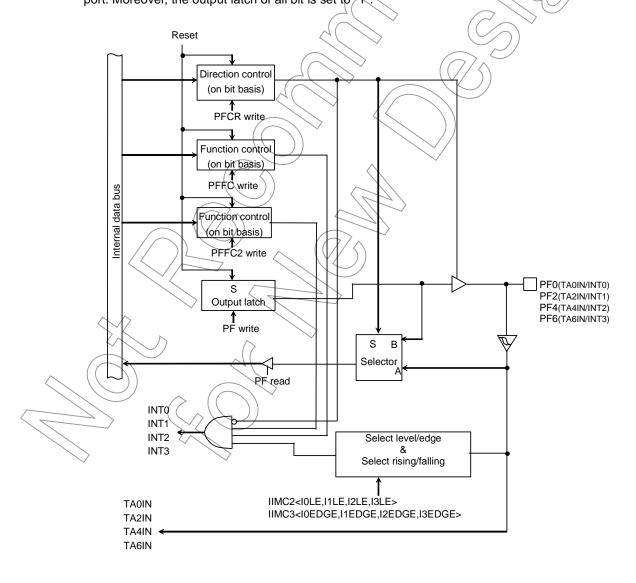

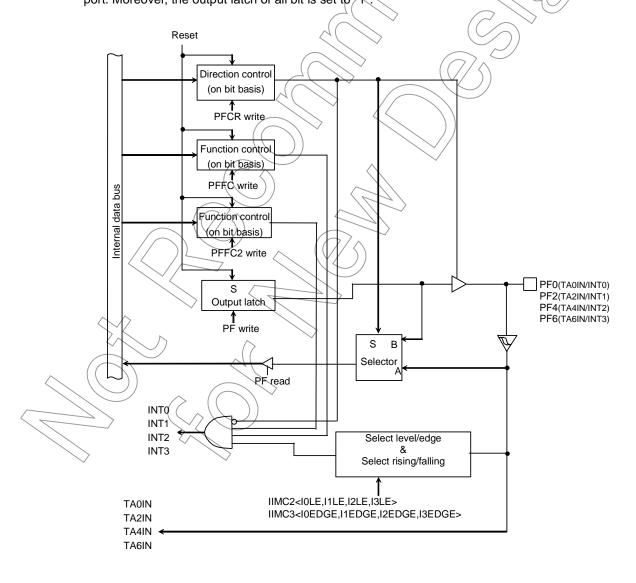

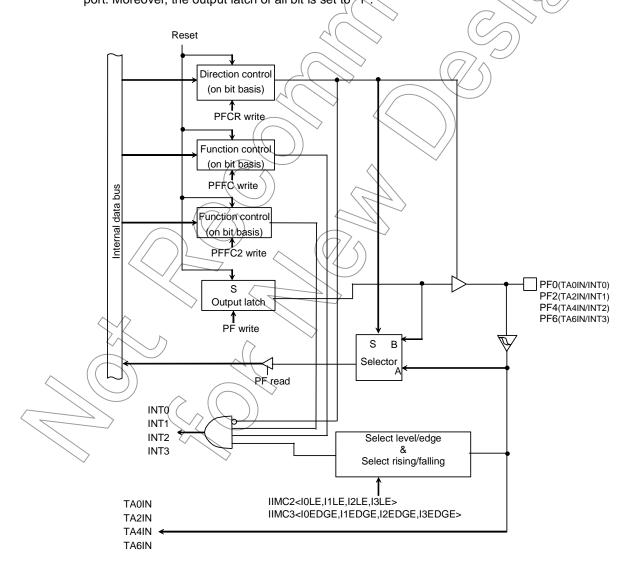

| PF0       | 1                   | I/O                                    | Port F0: I/O port (Schmitt input)                                                          |

| TAOIN     |                     | Input                                  | 8-bit timer 0 input: Input pin of 8-bit timer TMRA0                                        |

| INT0      |                     | Input                                  | Interrupt request pin 0: Interrupt request pin with programmable level/rising/falling edge |

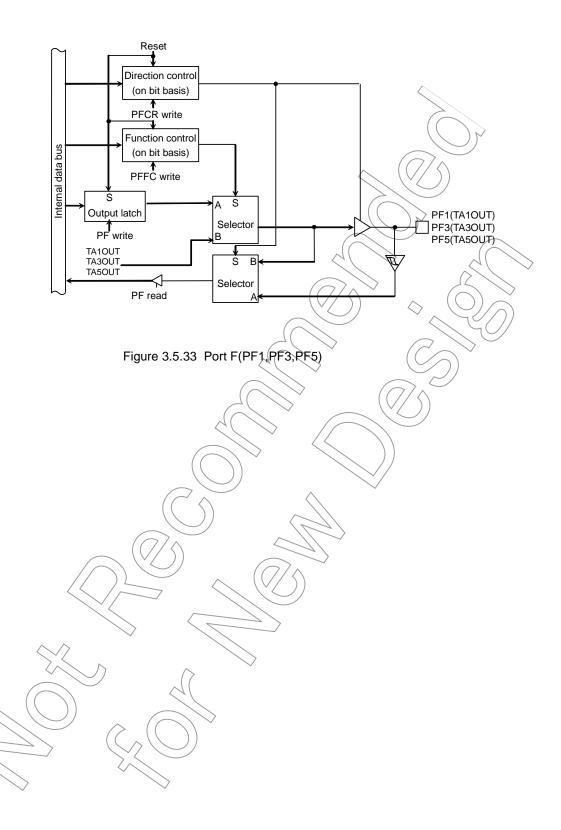

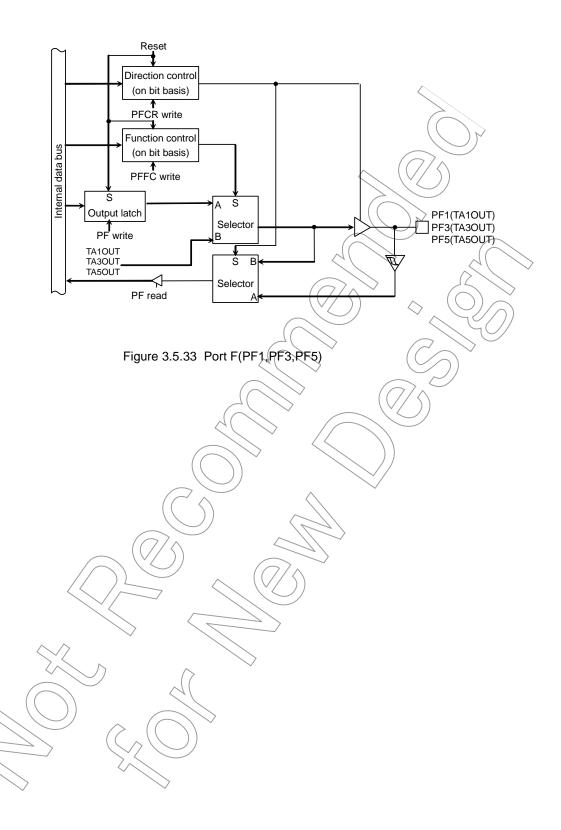

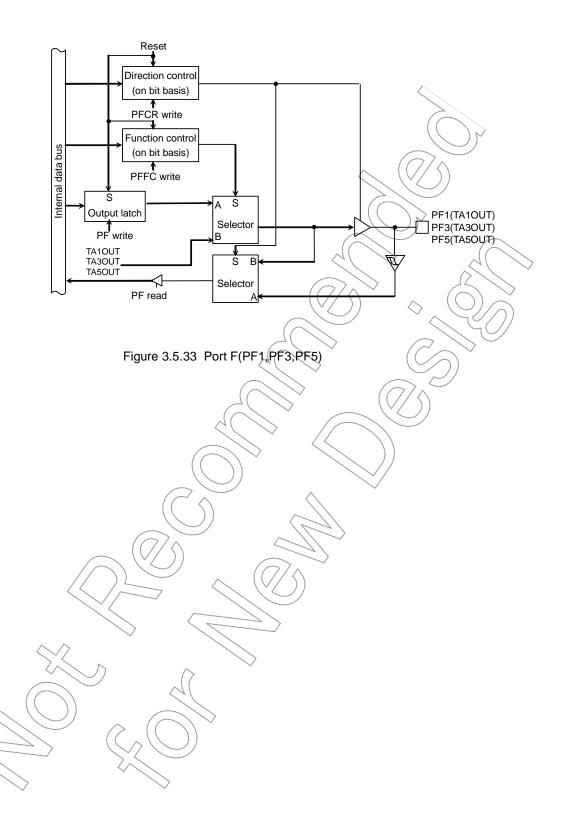

| PF1       | 1                   | I/O                                    | Port F1: I/O port (Schmitt input)                                                          |

| TA1OUT    |                     | Output                                 | 8-bit timer 1 output: Output pin of 8-bit timer TMRA0 or TMRA1                             |

| PF2       | 1                   | I/O                                    | Port F2: I/O port (Schmitt input)                                                          |

| TA2IN     |                     | Input                                  | 8-bit timer 2 input: Input pin of 8-bit timer TMRA2                                        |

| INT1      |                     | Input                                  | Interrupt request pin 1: Interrupt request pin with programmable level/rising/falling edge |

| PF3       | 1                   | I/O                                    | Port F3: I/O port (Schmitt input)                                                          |

| TA3OUT    |                     | Output                                 | 8-bit timer 3 output. Output pin of 8-bit timer TMRA2 or TMRA3                             |

| PF4       | 1                   | I/O                                    | Port F4: I/O port (Schmitt input)                                                          |

| TA4IN     |                     | Input                                  | 8-bit timer 4 input: Input pin of 8-bit timer TMRA4                                        |

| INT2      |                     | Input                                  | Interrupt request pin 2: Interrupt request pin with programmable level/rising/falling edge |

| PF5       | 1                   | I/O                                    | Port F5: 1/O port (Schmitt input)                                                          |

| TA5OUT    |                     | Output /                               | 8-bit timer 5 output: Output pin of 8-bit timer TMRA4 or TMRA5                             |

| PF6       | 1                   | I/O \                                  | Port F6: I/O port (Schmitt input)                                                          |

| TA6IN     |                     | Input                                  | 8-bit timer 6 input: Input pin of 8-bit timer TMRA6                                        |

| INT3      |                     | Input /                                | Interrupt request pin 3: Interrupt request pin with programmable level/rising/falling edge |

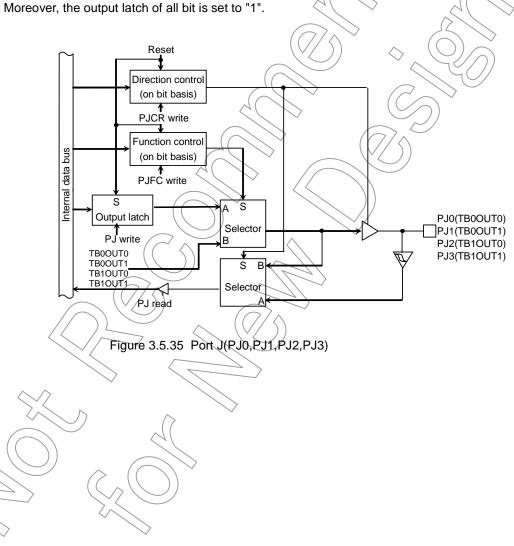

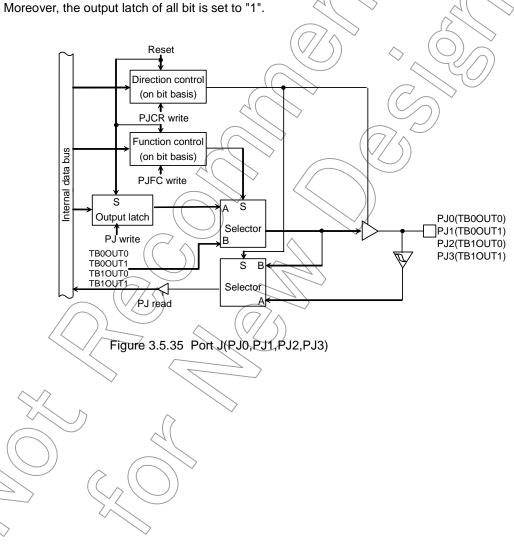

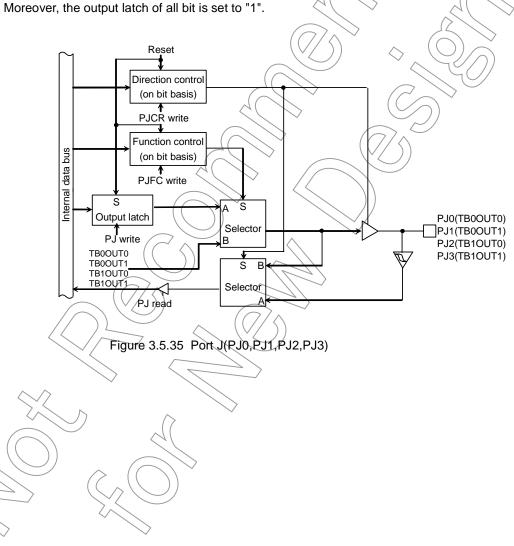

| PJ0       | 1/                  | \ \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | Port J0: I/O port (Schmitt input)                                                          |

| TB0OUT0   |                     | Output                                 | 16-bit timer 0 output 0: Output pin of 16-bit timer TMRB0                                  |

| PJ1       | (\sqrt{})           | \$                                     | Port J1: I/O port (Schmitt-input)                                                          |

| TB0OUT1   |                     | Output                                 | 16-bit timer 0 output 1: Output pin of 16-bit timer TMRB0                                  |

| PJ2       | 1                   | <u> </u>                               | Port J2: I/O port (Schmitt input)                                                          |

| TB1OUT0   | ^-                  | Output                                 | 16-bit timer 1 output 0: Output pin of 16-bit timer TMRB1                                  |

| PJ3       | Z 1                 | I/O                                    | Port J3: I/O port (Schmitt input)                                                          |

| TB1OUT1   |                     | Output                                 | 16-bit timer 1 output 1: Output pin of 16-bit timer TMRB1                                  |

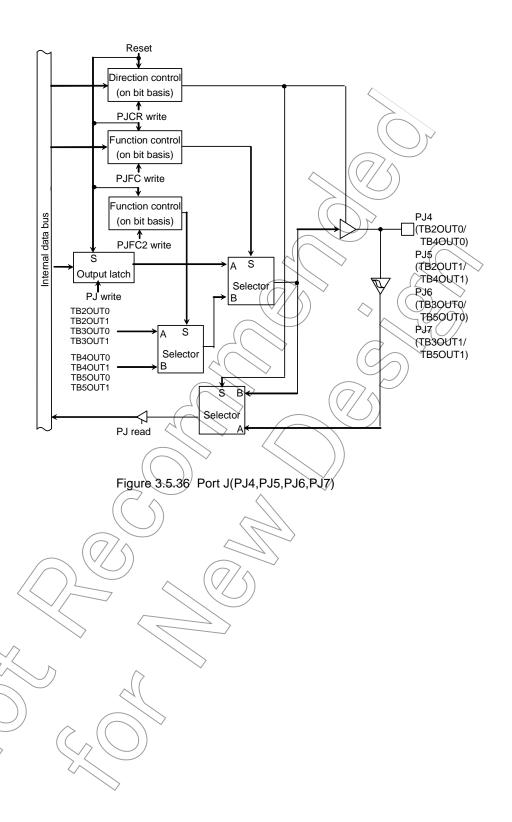

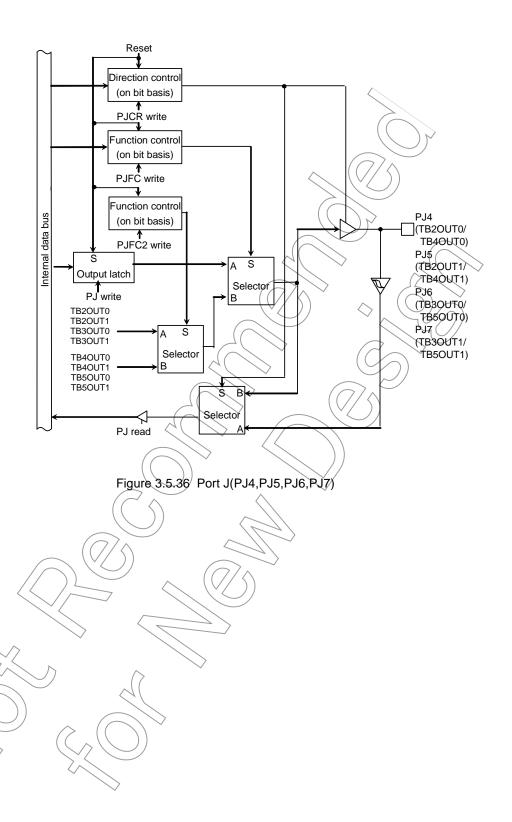

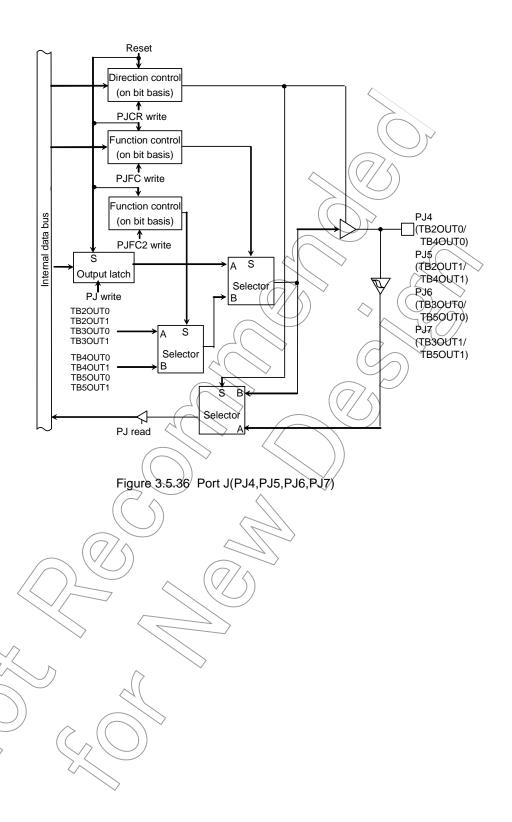

| PJ4       | $\backslash \gamma$ | I/O                                    | Port J4: I/O port (Schmitt input)                                                          |

| тв200т0 ( |                     | Output                                 | 16-bit timer 2 output 0: Output pin of 16-bit timer TMRB2                                  |

| TB4QUT0   | ノノ                  | Output                                 | 16-bit timer 4 output 0: Output pin of 16-bit timer TMRB4                                  |

| PJ5       | 1 /                 | / I/O( (                               | Port J5: I/O port (Schmitt input)                                                          |

| TB2OUT1   | \                   | Output                                 | 16-bit timer 2 output 1: Output pin of 16-bit timer TMRB2                                  |

| TB4OUT1   |                     | Output                                 | 16-bit timer 4 output 1: Output pin of 16-bit timer TMRB4                                  |

| PJ6       | 1                   | 1/0                                    | Port J6: I/O port (Schmitt input)                                                          |

| TB3OUT0   |                     | Output                                 | 16-bit timer 3 output 0: Output pin of 16-bit timer TMRB3                                  |

| TB5OUT0   |                     | Output                                 | 16-bit timer 5 output 0: Output pin of 16-bit timer TMRB5                                  |

| PJ7       | 1                   | I/O                                    | Port J7: I/O port (Schmitt input)                                                          |

| TB3OUT1   |                     | Output                                 | 16-bit timer 3 output 1: Output pin of 16-bit timer TMRB3                                  |

| TB5OUT1   |                     | Output                                 | 16-bit timer 5 output 1: Output pin of 16-bit timer TMRB5                                  |

Table 2.2.4 Pin names and functions (4/5)

| Pin name | Number<br>of Pin | I/O    | Function                                                                                   |

|----------|------------------|--------|--------------------------------------------------------------------------------------------|

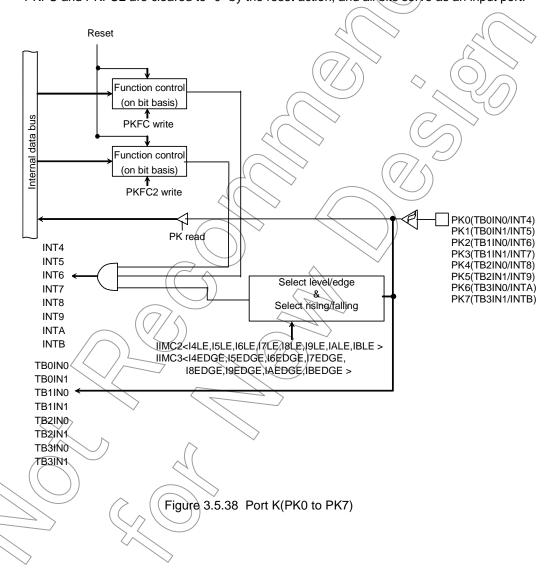

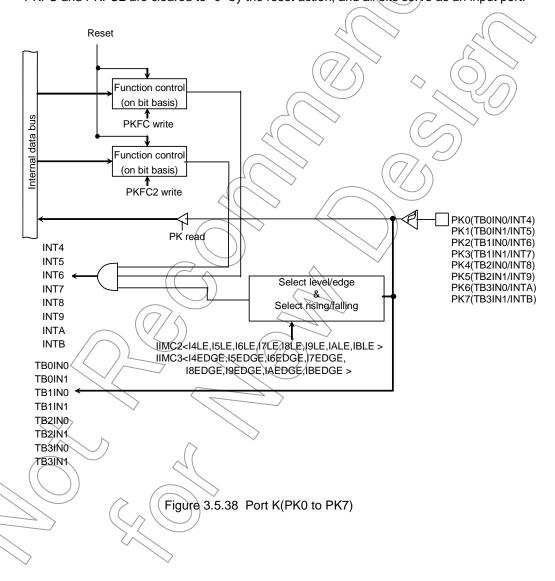

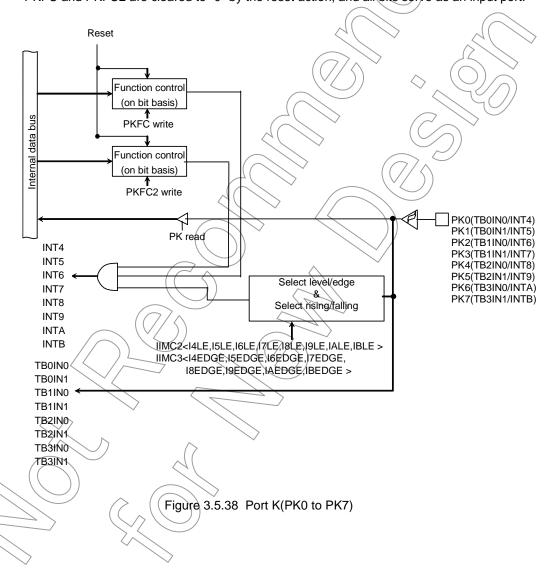

| PK0      | 1                | Input  | Port K0: Input port (Schmitt input)                                                        |

| TB0IN0   |                  | Input  | 16-bit timer 0 input 0: Input of count/capture trigger in 16-bit TMRB0                     |

| INT4     |                  | Input  | Interrupt request pin 4: Interrupt request pin with programmable level/rising/falling edge |

| PK1      | 1                | Input  | Port K1: Input port (Schmitt input)                                                        |

| TB0IN1   |                  | Input  | 16-bit timer 0 input 1: Input of count/capture trigger in 16-bit TMRB0                     |

| INT5     |                  | Input  | Interrupt request pin 5: Interrupt request pin with programmable level/rising/falling edge |

| PK2      | 1                | Input  | Port K2: Input port (Schmitt input)                                                        |

| TB1IN0   |                  | Input  | 16-bit timer 1 input 0: Input of count/capture trigger in 16-bit TMRB1                     |

| INT6     |                  | Input  | Interrupt request pin 6: Interrupt request pin with programmable level/rising/falling edge |

| PK3      | 1                | Input  | Port K3: Input port (Schmitt input)                                                        |

| TB1IN1   |                  | Input  | 16-bit timer 1 input 1: Input of count/capture trigger in 16-bit TMRB1                     |

| INT7     |                  | Input  | Interrupt request pin 7: Interrupt request pin with programmable level/rising/falling edge |

| PK4      | 1                | Input  | Port K4: Input port (Schmitt input)                                                        |

| TB2IN0   |                  | Input  | 16-bit timer 2 input 0: Input of count/capture trigger in 16-bit TMRB2                     |

| INT8     |                  | Input  | Interrupt request pin 8: Interrupt request pin with programmable level/rising/falling edge |

| PK5      | 1                | Input  | Port K5: Input port (Schmitt_input)                                                        |

| TB2IN1   |                  | Input  | 16-bit timer 2 input 1: Input of count/capture trigger in 16-bit TMRB2                     |

| INT9     |                  | Input  | Interrupt request pin 9: Interrupt request pin with programmable level/rising/falling edge |

| PK6      | 1                | Input  | Port K6: Input port (Schmitt-input)                                                        |

| TB3IN0   |                  | Input  | 16-bit timer 3 input 0. Input of count/capture trigger in 16-bit TMRB3                     |

| INTA     |                  | Input  | Interrupt request pin A: Interrupt request pin with programmable level/rising/falling edge |

| PK7      | 1                | Input  | Port K7: Input port (Schmitt input)                                                        |

| TB3IN1   |                  | Input  | 16-bit timer 3 input 1: Input of count/capture trigger in 16-bit TMRB3                     |

| INTB     |                  | Input  | Interrupt request pin B: Interrupt request pin with programmable level/rising/falling edge |

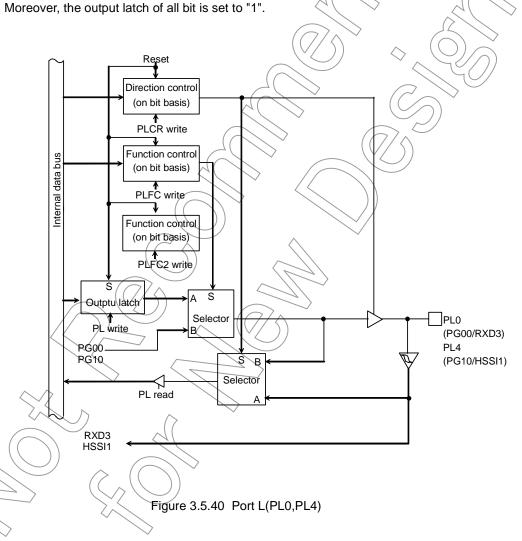

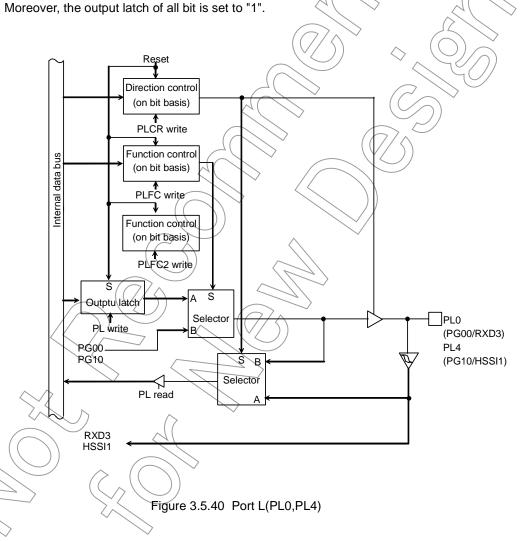

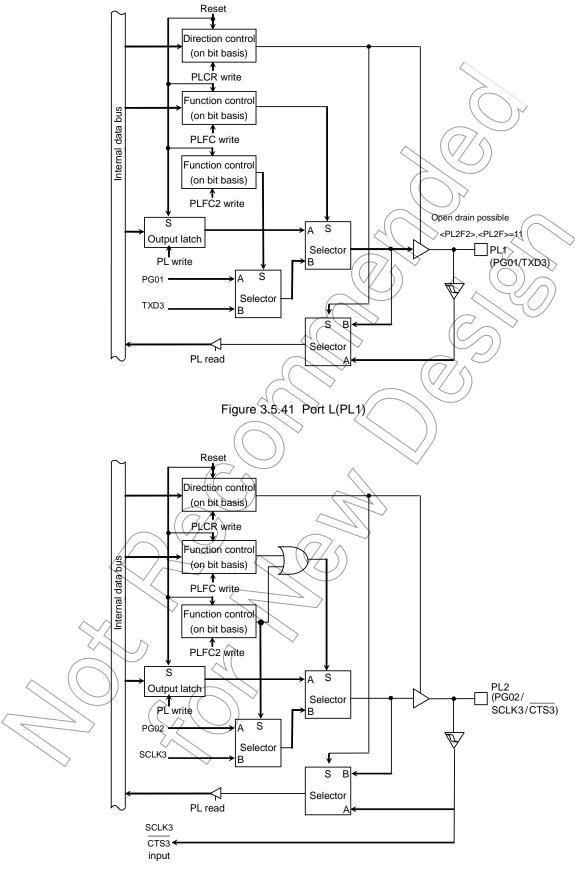

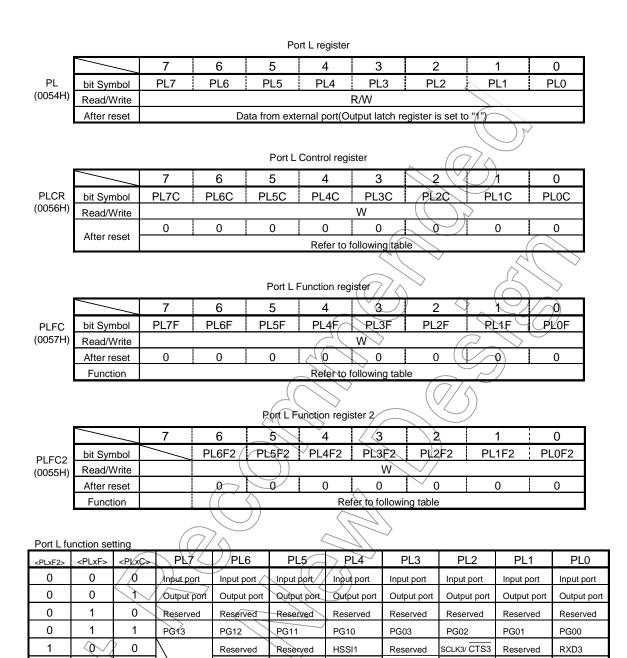

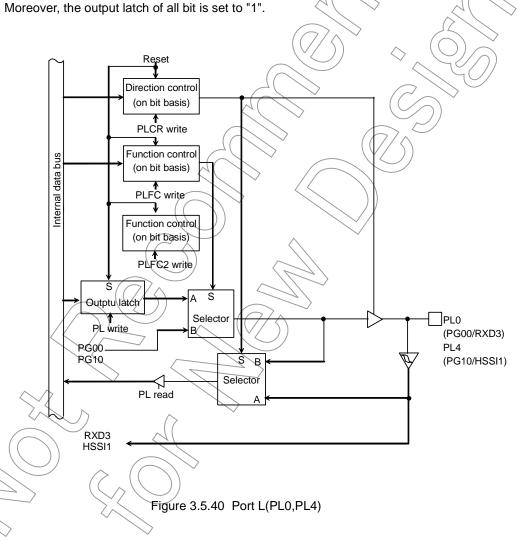

| PL0      | 1                | I/O    | Port, LO: I/O port (Schmitt input)                                                         |

| PG00     |                  | Output | Pattern generator output 00                                                                |

| RXD3     |                  | Input  | Serial 3 receive data                                                                      |

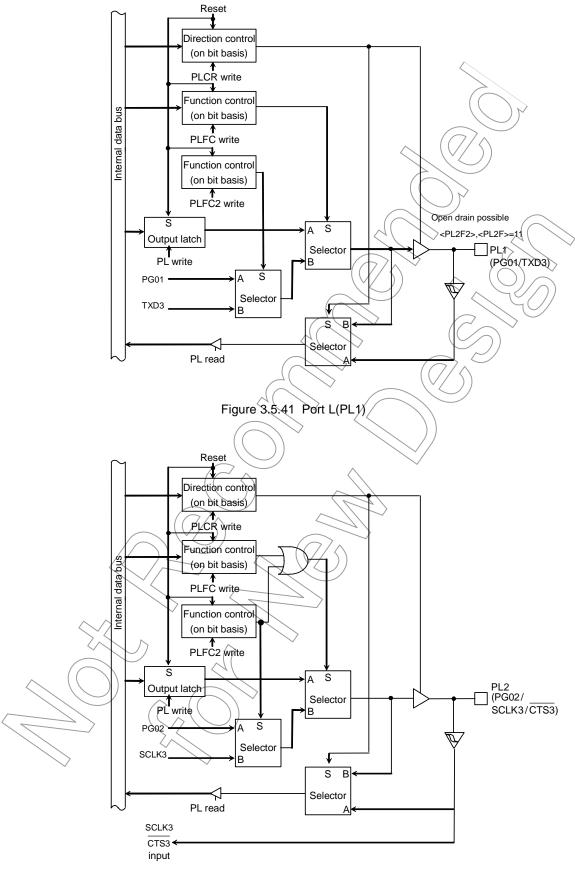

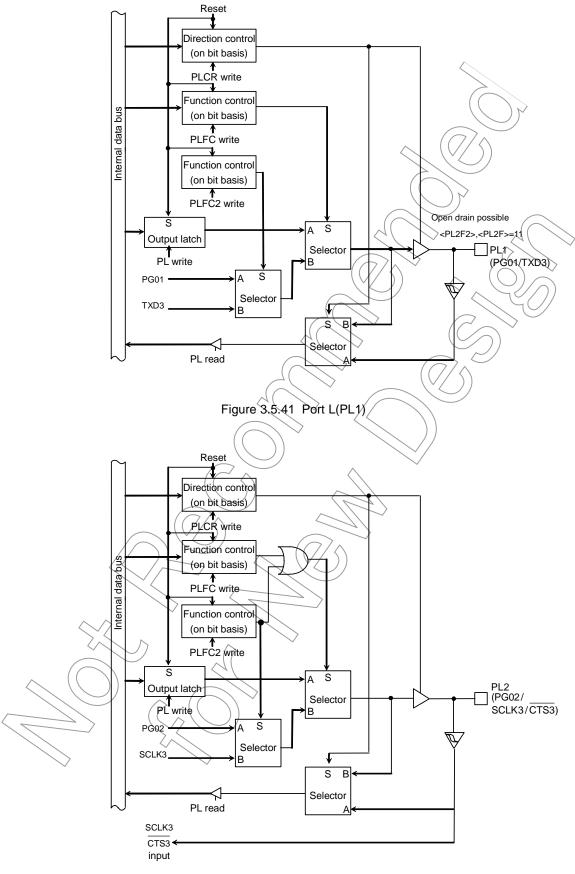

| PL1      | 1                | I/O /  | Port L1: I/O port (Schmitt input)                                                          |

| PG01     |                  | Output | Pattern generator output 01                                                                |

| TXD3     |                  | Output | Serial 3 send data: Open-drain output programmable                                         |

| PL2      | 1                | 1/0    | Port L2: I/O port (Schmitt input)                                                          |

| PG02     |                  | Output | Pattern generator output 02                                                                |

| SCLK3    |                  | // 1/0 | Serial 3 clock I/O                                                                         |

| CTS3     |                  | Input  | Serial 3 data send enable (Clear To Send)                                                  |

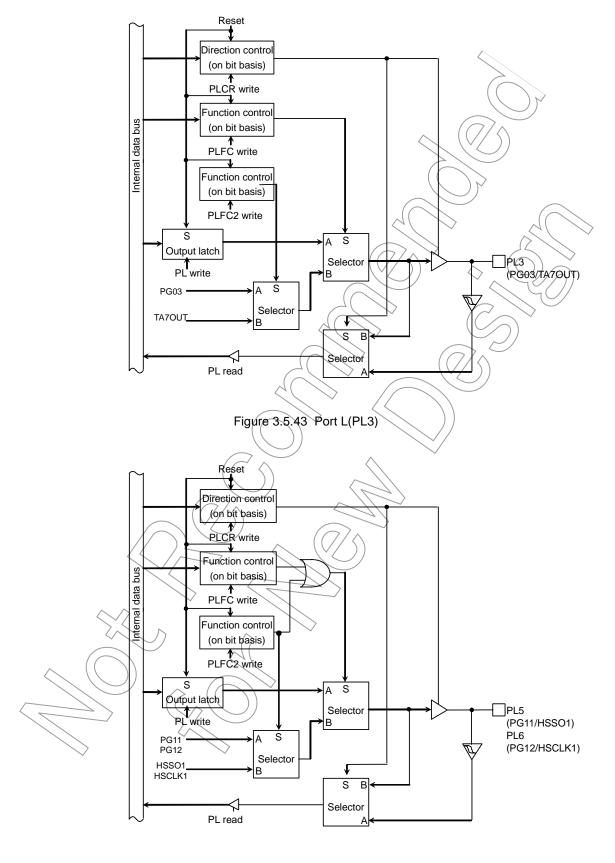

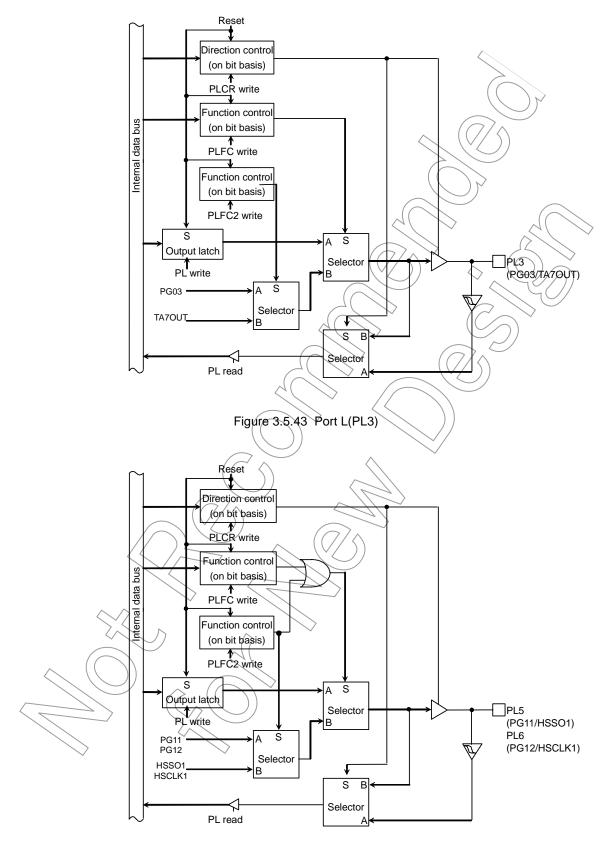

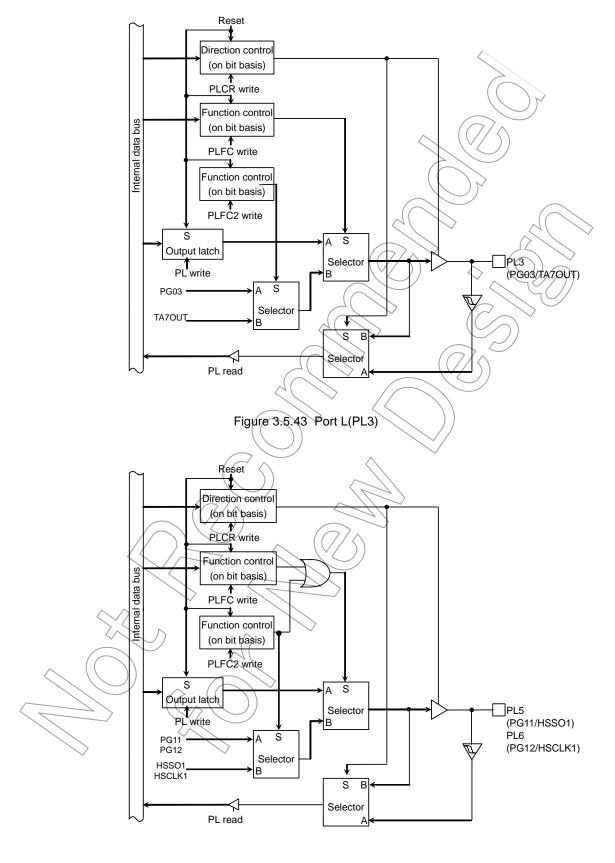

| PL3      | 1                | / I/O  | Port L3: I/O port (Schmitt input)                                                          |

| PG03     |                  | Qutput | Pattern generator output 03                                                                |

| TA7OUT   |                  | Output | 8-bit timer 7 output: Output pin of 8-bit timer TMRA6 or TMRA7                             |

| PL4      |                  | I/O    | Port L4: I/O port                                                                          |

| PG10     | 1                | Output | Pattern generator output 10                                                                |

| HSSI1    |                  | Input  | High speed Serial 1 receive data                                                           |

| PL5      | 1                | I/O    | Rort L5: I/O port (Schmitt input)                                                          |

| PG11     | ))               | Output | Pattern generator output 11                                                                |

| HSSO1    | <u></u>          | Output | High speed Serial 1 send data                                                              |

| PL6      | 1                | / QN   | Pørt/L6: I/O port (Schmitt input)                                                          |

| RG12     |                  | Output | Pattern generator output 12                                                                |

| HSCLKT   |                  | Output | High speed Serial 1 clock I/O                                                              |

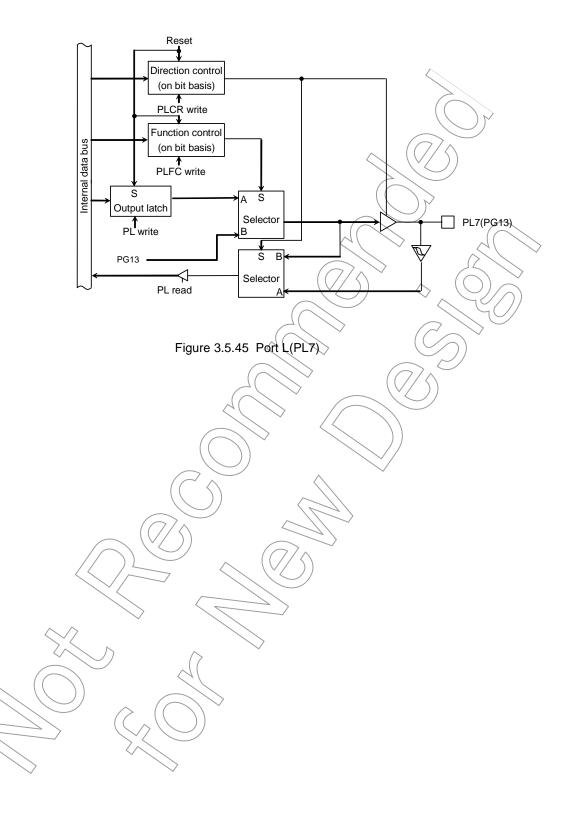

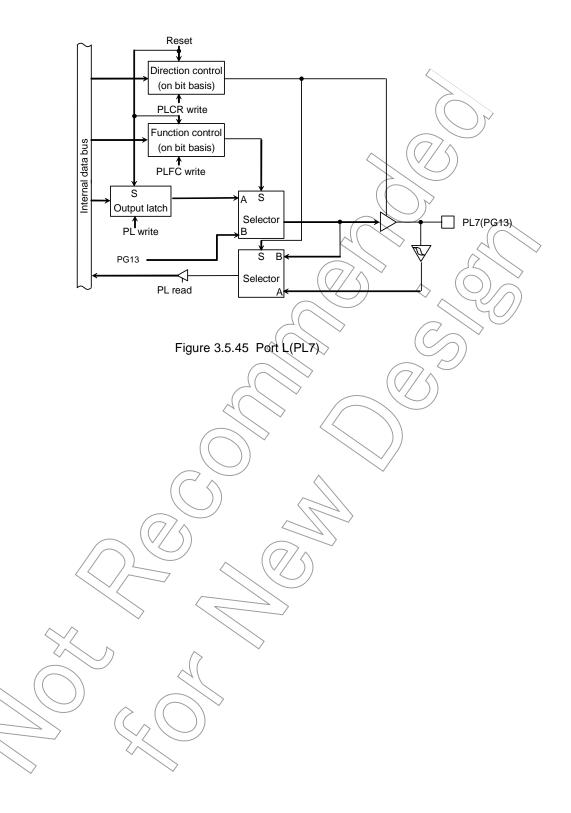

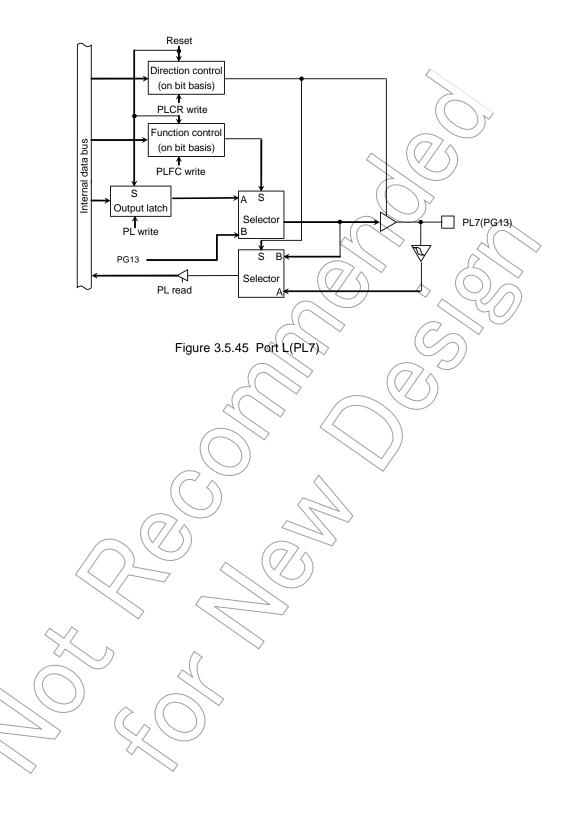

| PL7      | 1                | 1/0    | Port L7: I/O port (Schmitt input)                                                          |

| PG13     | 1                | Output | Pattern generator output 13                                                                |

Table 2.2.5 Pin names and functions (5/5)

| Pin name     | Number<br>of Pin | I/O    | Function                                                                            |

|--------------|------------------|--------|-------------------------------------------------------------------------------------|

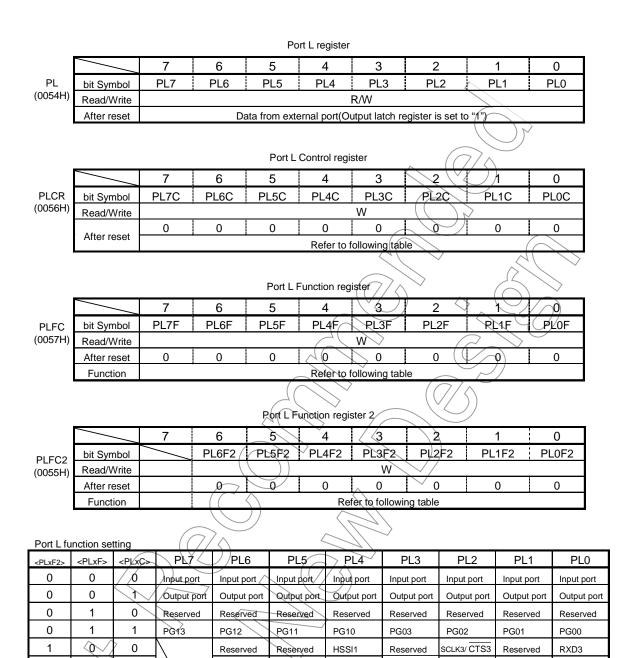

| PM0 to PM7   | 8                | Input  | Port M: Input port (Schmitt input)                                                  |

| AN0 to AN7   |                  |        | Analog input 0 to 7: Pin used to input to AD converter                              |

| KI0 to KI7   |                  |        | Key input 0 to 7: Pin used of Key-on wakeup 0 to 7                                  |

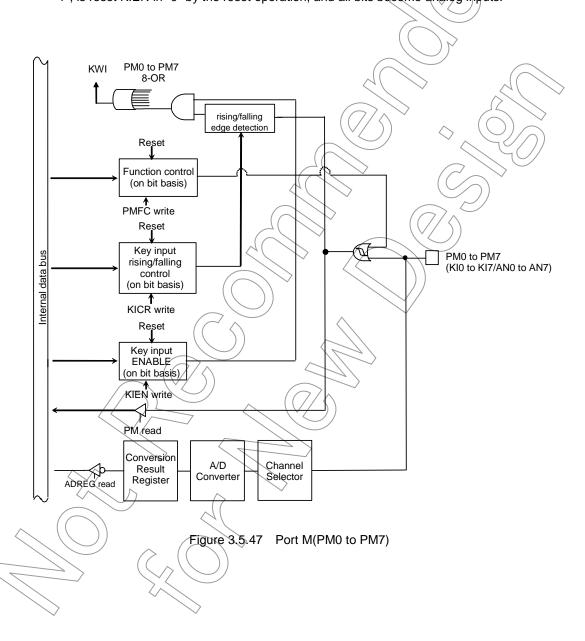

| PN0 to PN3   | 4                | Input  | Port N: Input port (Schmitt input)                                                  |

| AN8 to AN11  |                  |        | Analog input 8 to 11: Pin used to input to AD converter                             |

| ADTRG        |                  |        | AD trigger: Signal used for request AD start (Shared with PN3)                      |

| NMI          | 1                | Input  | Non-maskable interrupt request pin: Interrupt request pin with programmable falling |

|              |                  |        | edge level or with both edge levels programmable (Schmitt input)                    |

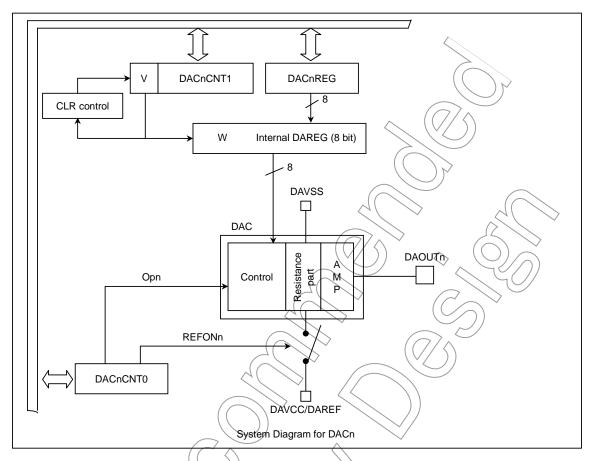

| DAOUT0       | 1                | Output | Digital output 0: Pin used to output to DA converter 0                              |

| DAOUT1       | 1                | Output | Digital output 1: Pin used to output to DA converter 1                              |

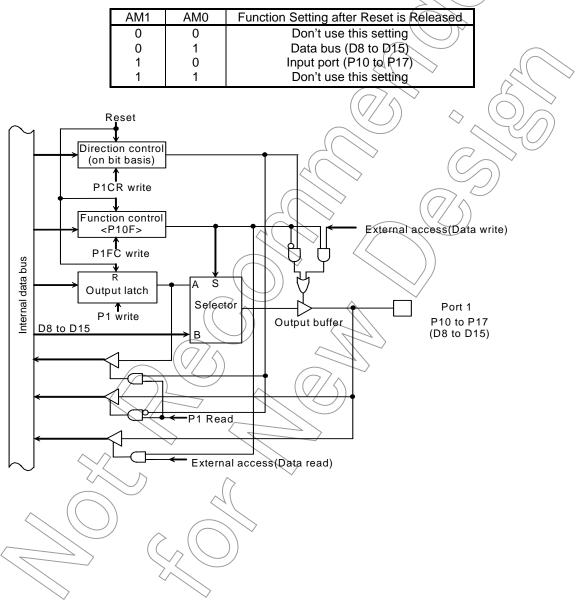

| AM0, AM1     | 2                | Input  | Operation mode:                                                                     |

|              |                  |        | Fixed to AM1="0",AM0="1" External 16-bit bus, start                                 |

|              |                  |        | Fixed to AM1="1",AM0="0" External 8-bit bus start                                   |

|              |                  |        | Fixed to AM1="1",AM0="1" Reserved                                                   |

|              |                  |        | Fixed to AM1="0",AM0="0" Reserved                                                   |

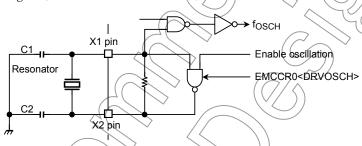

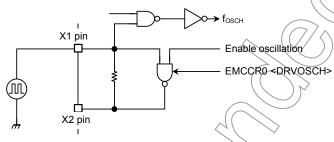

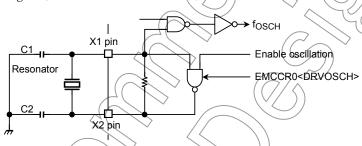

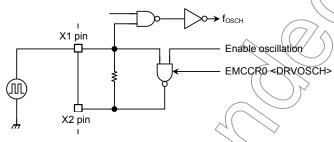

| X1 / X2      | 2                | I/O    | High-frequency oscillator connection 1/O pins                                       |

| RESET        | 1                | Input  | Reset: Initializes TMP92CM27 (Schmitt input, with pull-up register)                 |

| AVCC / VREFH | 1                | Input  | Pin used to both power supply pin for AD converter and standard power supply for AD |

|              |                  |        | converter (H)                                                                       |

| AVSS / VREFL | 1                | Input  | Pin used to both GND pin for AD converter (0V) and standard power supply pin for AD |

|              |                  |        | converter (L)                                                                       |

| DAVCC /      | 1                | Input  | Pin used to both power supply pin for DA converter and standard power supply for DA |

| DAREF        |                  |        | converted                                                                           |

| DAVSS        | 1                | Input  | Pin used to both GND pin for DA converter (0V)                                      |

| DVCC         | 4                | -      | Power supply pin (All DVCC pins should be connected with the power supply pin)      |

| DVSS         | 4                | •      | GND pins (0V) (All DVSS pins should be connected with GND (0V))                     |

# 3. Operation

This section describes the basic components, functions and operation of the TMP92CM27.

# 3.1 CPU

The TMP92CM27 contains an advanced high-speed 32-bit CPU (TLCS-900/H1 CPU)

# 3.1.1 CPU Outline

TLCS-900/H1 CPU is high-speed and high-performance CPU based on TLCS-900/L1 CPU.TLCS-900/H1 CPU has expanded 32-bit internal data bus to process instructions more quickly.

Outline is as follows:

Table 3.1.1 TMP92CM27 Outline

| Parameter  Width of CPU address bus  Width of CPU data bus  Internal operating frequency  Minimum bus cycle  Internal RAM  32-bit 1-clock access  8-bit, 2-clock TMRA, TMRB, PG, SIO, SBI, access SDRAMC, ADC, DAC, WDT  16-bit, 2-clock access  External memory (SRAM etc)  External memory (SDRAM)  Minimum instruction Execution cycle  Conditional jump  Instruction gueue buffer  Instruction set  CPU mode  CPU mode  12 bits  24 bits  24 bits  24 bits  24 bits  24 bits  22 bits  Max 20MHz  CGEAR, INTC, PORT, MEMC, TMRA, TMRB, PG, SIO, SBI, SDRAMC, ADC, DAC, WDT  16-bit 2-clock access (can insert some waits)  1-clock (50ns at f <sub>SYS</sub> = 20MHz)  1-clock (100ns at f <sub>SYS</sub> = 20MHz)  Compatible with TLCS-900/L1 (LDX instruction is deleted)  Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |                                                         |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------|--|--|

| Width of CPU data bus Internal operating frequency Minimum bus cycle Internal RAM  Internal RAM  Internal RAM  Internal I/O  Int | Parameter                    | TMP92CM27                                               |  |  |

| Internal operating frequency  Minimum bus cycle  Internal RAM  32-bit 1-clock access  8-bit, 2-clock TMRA, TMRB, PG, SIO, SBI, 3ccess SDRAMC, ADC, DAC, WDT  16-bit, 2-clock access  External memory (SRAM etc)  External memory (SDRAM)  Minimum instruction Execution cycle  Conditional jump  Instruction set  CPU mode  Max 20MHz  1-clock access (50ns at f <sub>SYS</sub> = 20MHz)  CGEAR, INTC, PORT, MEMC, TMRA, TMRB, PG, SIO, SBI, SDRAMC, ADC, DAC, WDT  16-bit 1-clock access (can insert some waits)  1-clock (50ns at f <sub>SYS</sub> = 20MHz)  2-clock (100ns at f <sub>SYS</sub> = 20MHz)  Compatible with TLCS-900/L1 (LDX instruction is deleted)  Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Width of CPU address bus     | ( // \ ) 24 bits \ ( ) \ \                              |  |  |

| Minimum bus cycle  Internal RAM  32-bit 1-clock access  8-bit,  CGEAR, INTC, PORT, MEMC,  TMRA, TMRB, PG, SIO, SBI,  access  SDRAMC, ADC, DAC, WDT  16-bit,  2-clock  access  External memory  (SRAM etc)  External memory  (SDRAM)  Minimum instruction  Execution cycle  Conditional jump  1-clock (50ns at f <sub>SYS</sub> = 20MHz)  Instruction queue buffer  12 bytes  Compatible with TLCS-900/L1  (LDX instruction is deleted)  CPU mode  1-clock access (50ns at f <sub>SYS</sub> = 20MHz)  CGEAR, INTC, PORT, MEMC,  TMRA, TMRB, PG, SIO, SBI,  SDRAMC, ADC, DAC, WDT  16-bit,  16-bit,  16-bit,  16-bit,  16-bit 1-clock access  (can insert some waits)  1-clock (50ns at f <sub>SYS</sub> = 20MHz)  Compatible with TLCS-900/L1  (LDX instruction is deleted)  Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Width of CPU data bus        | 32 bits \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \           |  |  |

| Internal RAM  8-bit, CGEAR, INTC, PORT, MEMC, TMRA, TMRB, PG, SIO, SBI, saccess SDRAMC, ADC, DAC, WDT  16-bit, 2-clock access (can insert some waits)  External memory (SDRAM)  Minimum instruction Execution cycle  Conditional jump  Instruction set  Instruction set  CPU mode  2-clock access (can insert some waits)  32-bit 1-clock access (CGEAR, INTC, PORT, MEMC, TMRA, TMRB, PG, SIO, SBI, SDRAMC, ADC, DAC, WDT  16-bit, 1-clock access (can insert some waits)  16-bit 1-clock access (can insert some waits)  1-clock(50ns at f <sub>SYS</sub> = 20MHz)  1-clock(100ns at f <sub>SYS</sub> = 20MHz)  Compatible with TLCS-900/L1 (LDX instruction is deleted)  Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Internal operating frequency | Max 20MHz                                               |  |  |

| Internal I/O    Solit, 2-clock access | Minimum bus cycle            | 1-clock access (50ns at f <sub>SYS</sub> = 20MHz)       |  |  |

| Internal I/O  Internal Internal I/O  Internal Internal I/O  Internal Internal Internal | Internal RAM                 |                                                         |  |  |

| External memory (SRAM etc)  External memory (SDRAM)  Minimum instruction Execution cycle  Conditional jump  2-clock (100ns at f <sub>SYS</sub> = 20MHz)  Instruction queue buffer  Compatible with TLCS-900/L1 (LDX instruction is deleted)  CPU mode  External memory (can insert some waits)  16-bit 1-clock access (can insert some waits)  16-bit 1-clock access (can insert some waits)  16-bit 2-clock access (can insert some waits)  16-bit 1-clock access  1-clock (50ns at f <sub>SYS</sub> = 20MHz)  Compatible with TLCS-900/L1 (LDX instruction is deleted)  CPU mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Internal I/O                 | 2-clock TMRA, TMRB, PG, SIO, SBI, SDRAMC, ADC, DAC, WDT |  |  |

| (SRAM etc) (can insert some waits)  External memory (SDRAM)  Minimum instruction Execution cycle  Conditional jump 2-clock(50ns at f <sub>SYS</sub> = 20MHz)  Instruction queue buffer 12 bytes  Compatible with TLCS-900/L1 (LDX instruction is deleted)  CPU mode Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Fidewal manage               | 2-clock access                                          |  |  |

| (SDRAM)  Minimum instruction Execution cycle  Conditional jump  2-clock(50ns at f <sub>SYS</sub> = 20MHz)  Instruction queue buffer  12 bytes  Compatible with TLCS-900/L1 (LDX instruction is deleted)  CPU mode  Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - /                          |                                                         |  |  |

| Execution cycle  Conditional jump  2-clock(100ns at f <sub>SYS</sub> = 20MHz)  Instruction queue buffer  12 bytes  Compatible with TLCS-900/L1  (LDX instruction is deleted)  CPU mode  Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              | 16-bit 1-clock access                                   |  |  |

| Instruction queue buffer  Instruction set  Instruction set  Compatible with TLCS-900/L1 (LDX instruction is deleted)  CPU mode  Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | / _ /                        | 1-clock(50ns at f <sub>SYS</sub> = 20MHz)               |  |  |

| Instruction set  Compatible with TLCS-900/L1 (LDX instruction is deleted)  CPU mode  Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Conditional jump             | 2-clock(100ns at f <sub>SYS</sub> = 20MHz)              |  |  |

| (LDX instruction is deleted)  CPU mode  Only maximum mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Instruction queue buffer     | ((// \) 12 bytes                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Instruction set              |                                                         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CPU mode                     |                                                         |  |  |

| Micro DMA 8 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Micro DMA                    | 8 channel                                               |  |  |

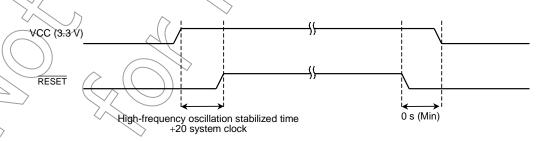

### 3.1.2 Reset Operation

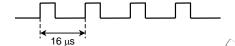

When resetting the TMP92CM27, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the  $\overline{\rm RESET}$  input low for at least 20 system clocks (16  $\mu s$  at fc = 40 MHz).

At reset, since the clock doubler (PLL) is bypassed and clock-gear is set to 1/16, system clock operates at 1.25 MHz (fc = 40 MHz).

When the reset has been accepted, the CPU performs the following:

• Sets the program counter (PC) as follows in accordance with the reset vector stored at address FFFF00H to FFFF02H:

PC<7:0> ← data in location FFFF00H PC<15:8> ← data in location FFFF01H

PC<23:16> ← data in location FFFF02H

- Sets the stack pointer (XSP) to 00000000H.

- Sets bits <IFF2:0> of the status register (SR) to 111"

(thereby setting the interrupt level mask register to level 7)

- Clears bits <RFP1:0> of the status register to "00" (there by selecting register bank 0).

When the reset is released, the CPU starts executing instructions according to the program counter settings. CPU internal registers not mentioned above do not change when the reset is released.

When the reset is accepted, the CPU sets internal I/O, ports and other pins as follows.

- Initializes the internal I/O registers as table of "special function register" in section 5.

- Sets the port pins, including the pins that also act as internal I/O, to general-purpose input or output port mode.

Internal reset is released as soon as external reset is released.

The operation of memory controller cannot be insured until power supply becomes stable after power on reset. The external RAM data provided before turning on the TMP92CM27 may be spoiled because the control signals are unstable until power supply becomes stable after power-on reset.

Figure 3.1.1 Power on Reset Timing Example

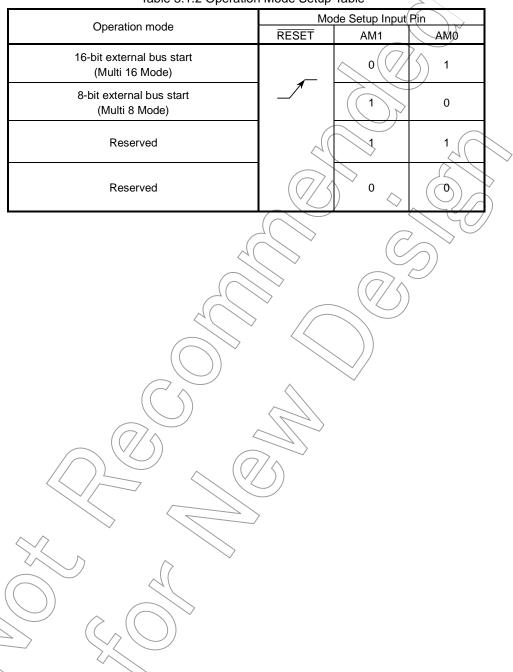

# 3.1.3 Setting of AM0 and AM1

Set AM1 and AM0 pins like Table 3.1.2 according to system usage.

Table 3.1.2 Operation Mode Setup Table

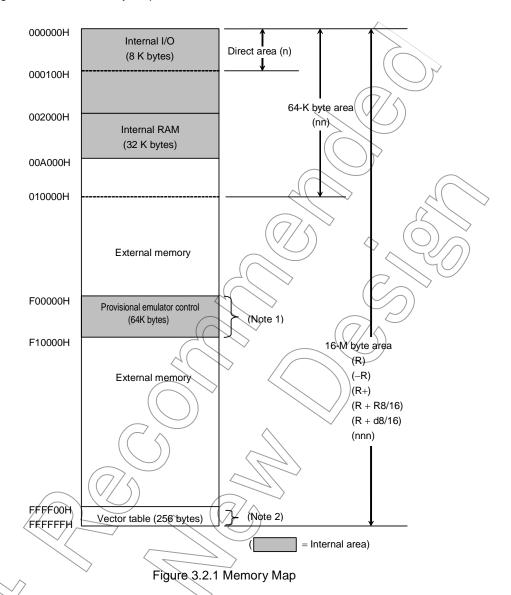

# 3.2 Memory Map

Figure 3.2.1 is a memory map of the TMPP92CM27.

Note 1: Provisional emulator control area is for an emulator, it is mapped F00000H to F0FFFFH after reset. On emulator WR signal and RD signal are asserted, when this area is accessed. Be carefull to use external memory.

Note 2: Don't use the last 16-bytes area (FFFFF0H to FFFFFFH). This area is reserved for an emulator.

# 3.3 Clock Function and Stand-by Function

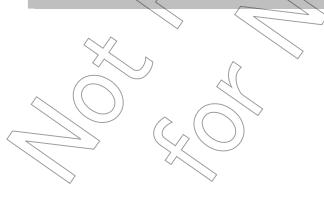

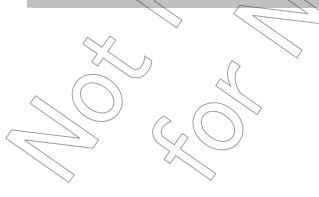

TMP92CM27 contains (1) clock gear, (2) clock doubler (PLL), (3) stand-by controller and (4) noise reducing circuit. They are used for low power, low noise systems.

This chapter is organized as follows: 3.3.1 Block diagram of system clock 3.3.2 3.3.3 System clock controller Clock doubler (PLL) 3.3.4 3.3.5 Noise reducing circuits 3.3.6 Stand-by controller

92CM27-14 2005-04-20

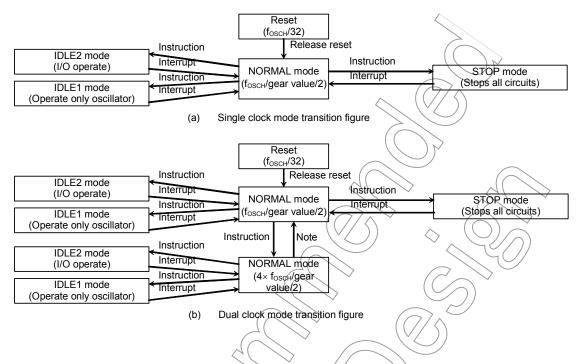

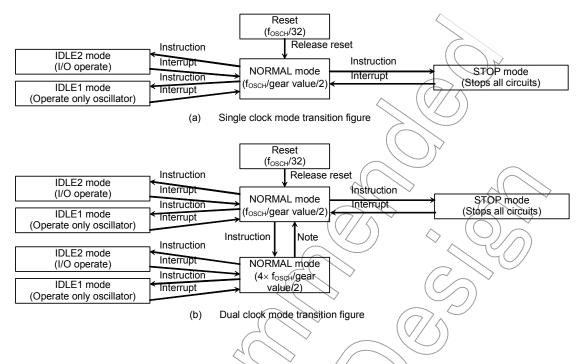

The clock operating modes are as follows: (a) single clock mode (X1, X2 pins only), (b) dual clock mode (X1, X2 pins and PLL).

Figure 3.3.1 shows a transition figure.

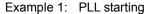

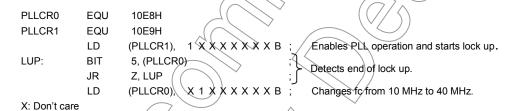

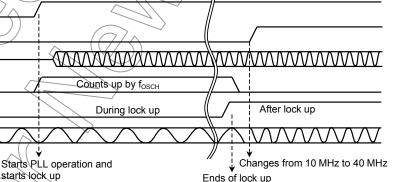

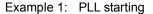

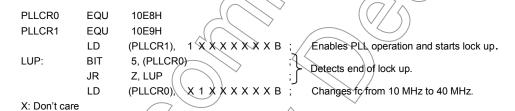

Note 1: If you shift from NORMAL mode with use of PLL to NORMAL mode, execute following setting in the same order.

- 1) Change CPU clock (PLLCR0 <FCSEL> \( \cdot '0")

- 2) Stop PLL circuit (PLLCR1 <PLLON> ("0")

Note 2: It's prohibited to shift from NORMAL mode with use of PLL to STOP mode directly.

You should set NORMAL mode once, and then shift to STOP mode. (You should stop high-frequency oscillator after you stop PLL.)

Figure 3.3.1 System Clock Block Diagram