Publication # 26426 Rev. C Issue Date: October 2003

#### **Preliminary Information**

#### © 2003 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any

#### **Trademarks**

AMD, the AMD Arrow logo, AMD Athlon, AMD Duron, and combinations thereof, AMD-760, 3DNow!, and QuantiSpeed are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

MMX is a trademark of Intel Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Table of Contents**

| Rev | ision H                                                  | listory                                                                                                                                                                                                                                                                                                                                                                          | xi             |

|-----|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1   | Over                                                     | view                                                                                                                                                                                                                                                                                                                                                                             | 1              |

|     | 1.1                                                      | AMD Athlon™ MP Processor Model 10 Key<br>Microarchitecture Summary                                                                                                                                                                                                                                                                                                               | 3              |

| 2   | Inte                                                     | rface Signals                                                                                                                                                                                                                                                                                                                                                                    | 5              |

|     | 2.1<br>2.2<br>2.3                                        | Signaling Technology                                                                                                                                                                                                                                                                                                                                                             | 6              |

| 3   | Logi                                                     | c Symbol Diagram                                                                                                                                                                                                                                                                                                                                                                 | 7              |

| 4   | Powe                                                     | er Management                                                                                                                                                                                                                                                                                                                                                                    | 9              |

|     | 4.1                                                      | Power Management States  Working State.  Halt State.  Stop Grant States.  Probe State.  Connect and Disconnect Protocol                                                                                                                                                                                                                                                          | 10             |

|     | 4.3                                                      | Connect Protocol                                                                                                                                                                                                                                                                                                                                                                 | 17             |

| 5   | CPU                                                      | ID Support                                                                                                                                                                                                                                                                                                                                                                       | 21             |

| 6   | Elec                                                     | trical and Thermal Specifications for the                                                                                                                                                                                                                                                                                                                                        |                |

|     |                                                          | O Athlon <sup>TM</sup> MP Processor Model 10                                                                                                                                                                                                                                                                                                                                     | <b>2</b> 3     |

| 7   |                                                          | trical Data                                                                                                                                                                                                                                                                                                                                                                      |                |

|     | 7.1<br>7.2<br>7.3<br>7.4<br>7.5                          | Conventions                                                                                                                                                                                                                                                                                                                                                                      | 25 26 27       |

|     | 7.6<br>7.7<br>7.8<br>7.9<br>7.10<br>7.11<br>7.12<br>7.13 | Decoupling  V <sub>CC_CORE</sub> Characteristics  Absolute Ratings  SYSCLK and SYSCLK# AC and DC Characteristics  AMD Athlon System Bus AC and DC Characteristics  General AC and DC Characteristics  Open Drain Test Circuit  Thermal Diode Characteristics  Thermal Diode Electrical Characteristics  Thermal Protection Characterization  APIC Pins AC and DC Characteristics | 28303135353838 |

Contents iii

| 8  | Signa | al and Power-Up Requirements                                               | 41 |

|----|-------|----------------------------------------------------------------------------|----|

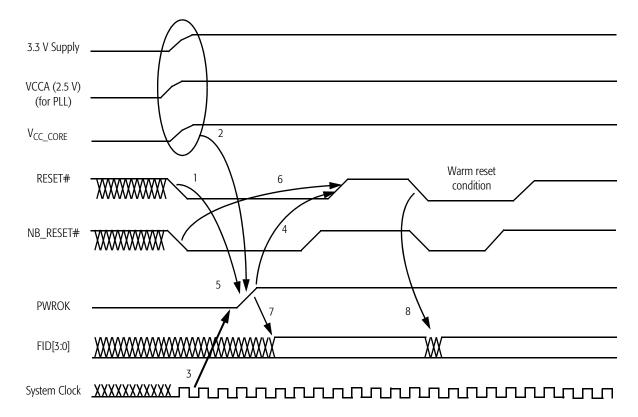

|    | 8.1   | Power-Up Requirements                                                      | 41 |

|    | 8.2   | Processor Warm Reset Requirements                                          | 44 |

| 9  | Mecl  | hanical Data                                                               | 45 |

|    | 9.1   | Die Loading                                                                | 45 |

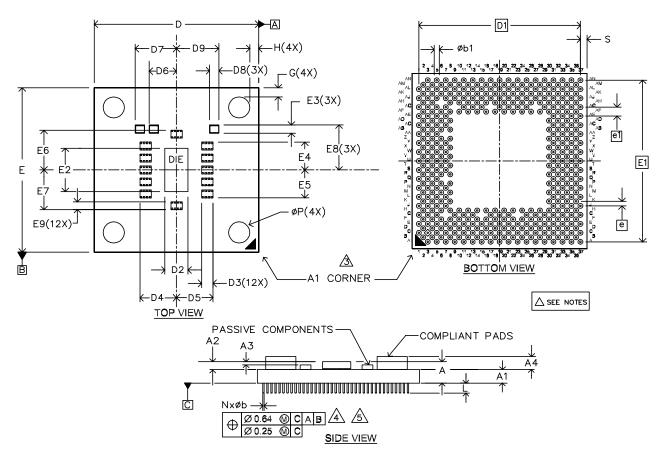

|    | 9.2   | AMD Athlon MP Processor Model 10 Part Number 27488 OPGA Package Dimensions |    |

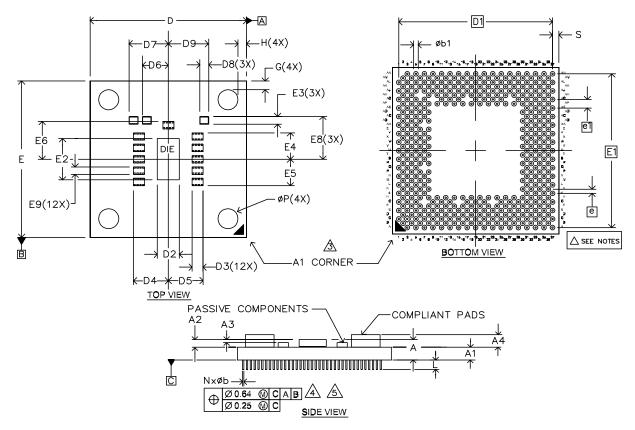

|    | 9.3   | AMD Athlon MP Processor Model 10 Part Number 27493 OPGA Package Dimensions |    |

| 10 | Pin I | Descriptions                                                               | 51 |

|    | 10.1  | Pin Diagram and Pin Name Abbreviations                                     | 51 |

|    | 10.2  | Pin List                                                                   | 61 |

|    | 10.3  | Detailed Pin Descriptions                                                  |    |

|    |       | A20M# Pin                                                                  |    |

|    |       | AMD Pin                                                                    |    |

|    |       | AMD Athlon System Bus Pins                                                 |    |

|    |       | Analog Pin                                                                 |    |

|    |       | CLKFWDRST Pin                                                              |    |

|    |       | CLKIN, RSTCLK (SYSCLK) Pins                                                |    |

|    |       | CONNECT Pin                                                                |    |

|    |       | COREFB and COREFB# Pins                                                    |    |

|    |       | CPU_PRESENCE# Pin                                                          |    |

|    |       | DBRDY and DBREQ# Pins                                                      | 71 |

|    |       | FERR Pin                                                                   | 71 |

|    |       | FID[3:0] Pins                                                              |    |

|    |       | FLUSH# Pin                                                                 |    |

|    |       | IGNNE# Pin                                                                 |    |

|    |       | INIT# Pin                                                                  |    |

|    |       | INTR Pin                                                                   |    |

|    |       | JTAG Pins  K7CLKOUT and K7CLKOUT# Pins                                     |    |

|    |       | Key Pins                                                                   |    |

|    |       | NC Pins                                                                    |    |

|    |       | NMI Pin.                                                                   |    |

|    |       | PGA Orientation Pins                                                       |    |

|    |       | PLL Bypass and Test Pins                                                   |    |

|    |       | PWROK Pin                                                                  |    |

|    |       | SADDIN[1:0]# and SADDOUT[1:0]# Pins                                        |    |

|    |       | Scan Pins                                                                  | 74 |

|    |       | SCHECK[7:0]# Pins                                                          |    |

|    |       | SMI# Pin                                                                   | 75 |

*iv* Contents

# **Preliminary Information**

26426C-October 2003

AMD Athlon™ MP Processor Model 10 Data Sheet for Multiprocessor Platforms

| STPCLK# Pin                              | . 75       |

|------------------------------------------|------------|

| SYSCLK and SYSCLK#                       | . 75       |

| THERMDA and THERMDC Pins                 | . 75       |

| VCCA Pin                                 | . 75       |

| VID[4:0] Pins                            | . 75       |

| VREFSYS Pin                              |            |

| ZN and ZP Pins                           | . 76       |

| 11 Ordering Information                  | 77         |

| Appendix A Thermal Diode Calculations    | <b>7</b> 9 |

| Appendix B Conventions and Abbreviations | 83         |

Contents v

26426C-October 2003

*vi* Contents

# **List of Figures**

| Figure 1.  | Logic Symbol Diagram                                                    | 7    |

|------------|-------------------------------------------------------------------------|------|

| Figure 2.  | AMD Athlon™ MP Processor Model 10 Power  Management States              | 9    |

| Figure 3.  | AMD Athlon System Bus Disconnect Sequence in the Stop Grant State       | . 15 |

| Figure 4.  | Exiting the Stop Grant State and Bus Connect Sequence                   | . 16 |

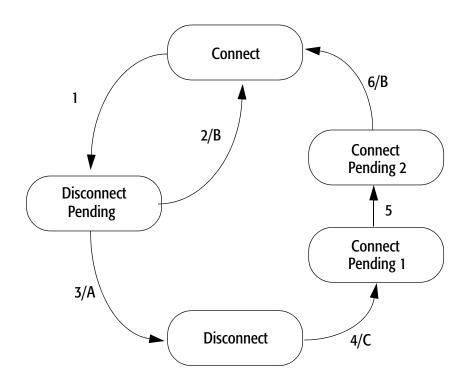

| Figure 5.  | Northbridge Connect State Diagram                                       | . 17 |

| Figure 6.  | Processor Connect State Diagram                                         | . 18 |

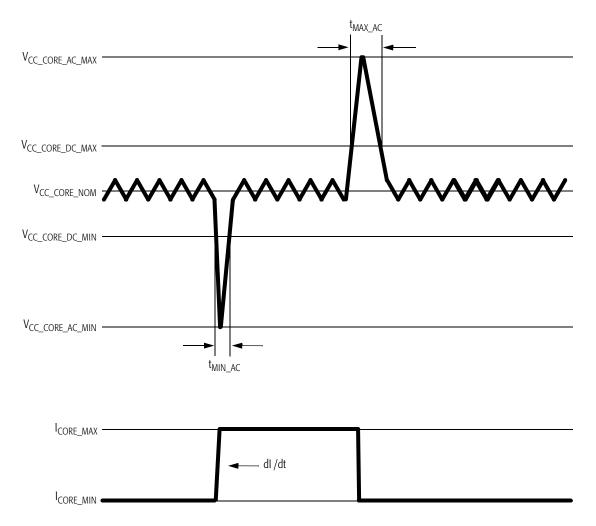

| Figure 7.  | VCC_CORE Voltage Waveform                                               | . 29 |

| Figure 8.  | SYSCLK and SYSCLK# Differential Clock Signals                           | . 31 |

| Figure 9.  | SYSCLK Waveform                                                         | . 32 |

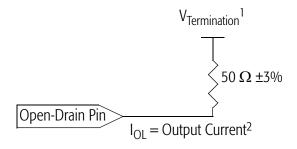

| Figure 10. | General ATE Open-Drain Test Circuit                                     | . 37 |

| Figure 11. | Signal Relationship Requirements During Power-Up Sequence               | . 41 |

| Figure 12. | AMD Athlon MP Processor Model 10 Part Number 27488 OPGA Package Diagram | . 47 |

| Figure 13. | AMD Athlon MP Processor Model 10 Part Number 27493 OPGA Package Diagram | . 49 |

| Figure 14. | AMD Athlon MP Processor Model 10 Pin Diagram —Topside View              | . 52 |

| Figure 15. | AMD Athlon MP Processor Model 10 Pin Diagram —Bottomside View           | . 53 |

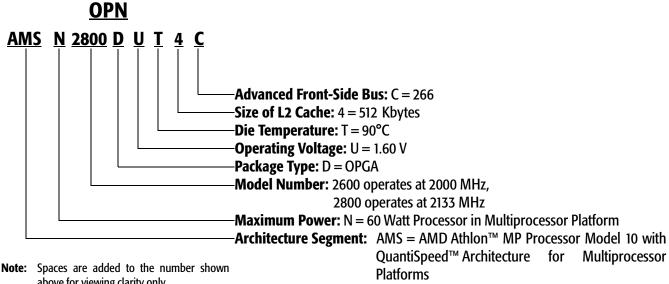

| Figure 16. | OPN Example for the AMD Athlon MP Processor                             | 77   |

List of Figures vii

26426C-October 2003

viii List of Figures

# **List of Tables**

| Table 1.  | Electrical and Thermal Specifications for the AMD Athlon <sup>TM</sup> MP Processor Model 10 | 23 |

|-----------|----------------------------------------------------------------------------------------------|----|

| Table 2.  | Interface Signal Groupings                                                                   |    |

| Table 3.  | VID[4:0] DC Characteristics                                                                  |    |

| Table 4.  | FID[3:0] DC Characteristics                                                                  |    |

| Table 5.  | VCCA AC and DC Characteristics                                                               |    |

| Table 6.  | V <sub>CC_CORE</sub> AC and DC Characteristics                                               | 28 |

| Table 7.  | Absolute Ratings                                                                             |    |

| Table 8.  | SYSCLK and SYSCLK# DC Characteristics                                                        | 31 |

| Table 9.  | SYSCLK and SYSCLK# AC Characteristics                                                        | 32 |

| Table 10. | AMD Athlon System Bus DC Characteristics                                                     | 33 |

| Table 11. | AMD Athlon System Bus AC Characteristics                                                     | 34 |

| Table 12. | General AC and DC Characteristics                                                            | 35 |

| Table 13. | Thermal Diode Electrical Characteristics                                                     | 38 |

| Table 14. | Guidelines for Platform Thermal Protection of the Processor                                  | 39 |

| Table 15. | APIC Pin AC and DC Characteristics                                                           |    |

| Table 16. | Mechanical Loading                                                                           |    |

| Table 17. | Dimensions for the AMD Athlon MP Processor Model 10 Part Number 27488 OPGA Package           |    |

| Table 18. | Dimensions for the AMD Athlon MP Processor Model 10 Part Number 27493 OPGA Package           | 48 |

| Table 19. | Pin Name Abbreviations                                                                       | 54 |

| Table 20. | Cross-Reference by Pin Location                                                              | 62 |

| Table 21. | FID[3:0] Clock Multiplier Encodings                                                          | 72 |

| Table 22. | VID[4:0] Code to Voltage Definition                                                          | 76 |

| Table 23. | Constants and Variables for the Ideal Diode Equation                                         | 79 |

| Table 24. | Constants and Variables Used in Temperature Offset Equations                                 | 80 |

| Table 25. | Abbreviations                                                                                | 85 |

| Table 26  | Acronyms                                                                                     | 86 |

List of Tables ix

26426C-October 2003

x List of Tables

# **Revision History**

| Date         | Rev | Description                                                                                                                        |  |  |  |  |  |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|              |     | Public revision C of the AMD Athlon™ MP Processor Model 10 Data Sheet for Multiprocessor Platforms includes the following changes: |  |  |  |  |  |

| October 2003 | С   | ■ In Chapter 6, revised Table 1, "Electrical and Thermal Specifications for the AMD Athlon™ MP Processor Model 10," on page 23.    |  |  |  |  |  |

|              |     | In Chapter 11, revised Figure 16, "OPN Example for the AMD Athlon™ MP Processor Model 10," on page 77.                             |  |  |  |  |  |

| May 2003     | В   | Initial public release of the AMD Athlon™ MP Processor Model 10 Data Sheet for Multiprocessor Platforms                            |  |  |  |  |  |

Revision History xi

26426C-October 2003

**xii** Revision History

#### 1 Overview

# The AMD Athlon™ MP processor model 10 powers the next generation in computing platforms, delivering compelling performance for cutting-edge applications and an unprecedented computing experience.

The AMD Athlon™ MP processor model 10, based on leadingedge 0.13 micron technology and increased on-chip cache, integrates the innovative design and manufacturing expertise of AMD to deliver improved performance, while maintaining the stable and compatible Socket A infrastructure of the AMD Athlon MP processor. The AMD Athlon MP processor model 10 continues to deliver breakthrough performance in the multiprocessing server and workstation markets. This processor is designed to meet the reliability and computation-intensive requirements of cutting-edge software applications required by workstations and servers.

Delivered in an OPGA package, the AMD Athlon MP processor model 10 delivers the integer, floating-point, and 3D multimedia performance for enterprise applications running on x86 system platforms. The AMD Athlon MP processor model 10 offers compelling performance for productivity software, including workstation-class digital content creation (DCC), electronic design automation (EDA), and computer-aided design (CAD), as well as infrastructure and collaborative server applications. It also offers the scalability and reliability that IT managers and business users require for mission-critical computing.

The AMD Athlon MP processor model 10 features the seventh-generation microarchitecture, including a high-speed execution core that includes multiple x86 instruction decoders, a dual-ported, 128-Kbyte, split level-one (L1) cache, a 512-Kbyte on-chip L2 cache, three independent integer pipelines, three address calculation pipelines, and a superscalar, fully pipelined, out-of-order, three-way floating-point engine. The integrated L2 cache supports the growing processor and system bandwidth requirements of emerging software, graphics, I/O, and memory technologies. The processor also features the advanced modified owner exclusive shared invalid (MOESI) cache coherency protocol to ensure efficient cache integrity in a multiprocessing environment. The floating-point engine is capable of delivering excellent performance on the numerically complex applications typical of servers and workstations.

26426C-October 2003

The key features of the AMD Athlon MP processor model 10 include QuantiSpeed™ architecture, 640 Kbytes of total, high-performance, full-speed, on-chip cache, an advanced 266 front-side bus (FSB), a 2.1-Gigabyte per second system bus, 3DNow!™ Professional technology, and fully featured logic implementation for the multiprocessor configuration.

The AMD Athlon system bus combines the latest technological advances, such as point-to-point topology, source-synchronous packet-based transfers, and low-voltage signaling. The point-to-point front-side bus architecture provides a more efficient, higher bandwidth bus that allows each processor, in a multi-processor configuration, to communicate to the system chipset through two, full-speed, independent buses rather than through a common, shared bus. Combined with the AMD-760<sup>TM</sup> MPX chipset, the processor and the system bus interface with double-data rate (DDR) memory subsystems, providing scalable headroom for bandwidth-hungry applications such as large databases, CAD/CAM modeling, and simulation engines.

The front-side bus of the AMD Athlon MP processor model 10 also provides multiple-bit error detection and single-bit error correction with 8-bit error correction code (ECC). The front-side bus with 8-bit ECC delivers the high reliability and consistency demanded by mission-critical applications.

The AMD Athlon MP processor model 10 is binary-compatible with existing x86 software and backwards compatible with applications optimized for MMX<sup>TM</sup> and 3DNow! technologies. Using a data format and single-instruction multiple-data (SIMD) operations based on the MMX instruction model, the AMD Athlon MP processor model 10 can produce as many as four, 32-bit, single-precision floating-point results per clock cycle. The 3DNow! Professional technology implemented in the AMD Athlon MP processor model 10 includes new integer multimedia instructions and software-directed data movement instructions for optimizing such applications as digital content creation and streaming video for the internet, as well as new instructions for digital signal processing (DSP)/communications applications.

# 1.1 AMD Athlon™ MP Processor Model 10 Key Microarchitecture Summary

The following features summarize the AMD Athlon MP processor model 10 microarchitecture:

- QuantiSpeed architecture:

- An advanced nine-issue, superpipelined, superscalar x86 processor microarchitecture designed for increased instructions per clock cycle (IPC) and high clock frequencies

- Fully pipelined floating-point unit that executes all x87 (floating-point), MMX and 3DNow! professional instructions

- Hardware data pre-fetch that increases and optimizes performance on high-end software applications that utilize high-bandwidth system capability

- Advanced two-level translation look-aside buffer (TLB) structures for enhanced data and instruction address translation. The AMD Athlon MP processor with QuantiSpeed architecture incorporates three TLB optimizations: the L1 DTLB increases from 32 to 40 entries, the L2 ITLB and L2 DTLB both use exclusive architecture, and the TLB entries can be speculatively loaded.

- 3DNow! Professional technology with new instructions to enable improved integer-math calculations for speech or video encoding and improved data movement for internet plug-ins and other streaming applications

- A 266-MHz AMD Athlon system bus enabling leading-edge system bandwidth for data movement-intensive applications

- Point-to-point front-side bus architecture allowing each processor in a multi-processor configuration to communicate to the system chipsets through two, full speed, independent buses

- High-performance cache architecture featuring an integrated 128-Kbyte L1 cache and a 16-way, 256-Kbyte on-chip L2 cache for a total of 640 Kbytes of on-chip cache

- Multiple-bit error detection and single-bit error correction with 8-bit error correction code (ECC)

- Full-featured MP Local APIC implementation

26426C-October 2003

# **2** Interface Signals

The AMD Athlon system bus architecture is designed to deliver superior data movement bandwidth for next-generation x86 platforms as well as the high-performance required by enterprise-class application software. The system bus architecture consists of three high-speed channels (a unidirectional processor request channel, a unidirectional probe channel, and a 72-bit bidirectional data channel, including 8-bit error correction code [ECC] protection), source-synchronous clocking, and a packet-based protocol. In addition, the system bus supports several control, clock, and legacy signals. The interface signals use an impedance controlled push-pull, low-voltage, swing-signaling technology contained within the Socket A socket.

For more information, see "AMD Athlon<sup>TM</sup> System Bus Signals" on page 6, Chapter 10, "Pin Descriptions" on page 51, and the  $AMD\ Athlon^{TM}\ and\ AMD\ Duron^{TM}\ System\ Bus\ Specification,$  order# 21902.

## 2.1 Signaling Technology

The AMD Athlon system bus uses a low-voltage, swing-signaling technology, that has been enhanced to provide larger noise margins, reduced ringing, and variable voltage levels. The signals are push-pull and impedance compensated. The signal inputs use differential receivers that require a reference voltage ( $V_{REF}$ ). The reference signal is used by the receivers to determine if a signal is asserted or deasserted by the source. Termination resistors are not needed because the driver is impedance-matched to the motherboard and a high impedance reflection is used at the receiver to bring the signal past the input threshold.

For more information about pins and signals, see Chapter 10, "Pin Descriptions" on page 51.

26426C-October 2003

#### 2.2 Push-Pull (PP) Drivers

The AMD Athlon MP processor model 10 supports push-pull (PP) drivers. The system logic configures the processor with the configuration parameter called SysPushPull (1=PP). The impedance of the PP drivers is set to match the impedance of the motherboard by two external resistors connected to the ZN and ZP pins.

See "ZN and ZP Pins" on page 76 for more information.

## 2.3 AMD Athlon™ System Bus Signals

The AMD Athlon system bus is a clock-forwarded, point-to-point interface with the following three point-to-point channels:

- A 13-bit unidirectional output address/command channel

- A 13-bit unidirectional input address/command channel

- A 72-bit bidirectional data channel

For more information, see Chapter 7, "Electrical Data" on page 25 and the  $AMD\ Athlon^{\text{TM}}$  and  $AMD\ Duron^{\text{TM}}$  System Bus Specification, order# 21902.

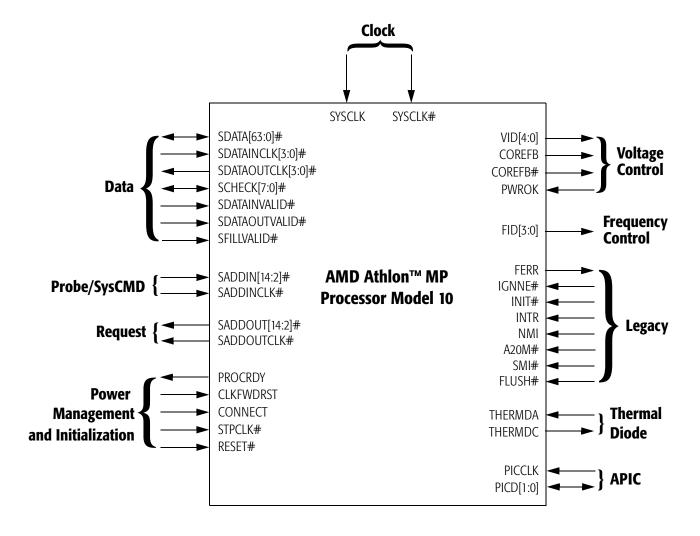

# 3 Logic Symbol Diagram

Figure 1 is the logic symbol diagram of the processor. This diagram shows the logical grouping of the input and output signals.

Figure 1. Logic Symbol Diagram

26426C-October 2003

# 4 Power Management

This chapter describes the power management control system of the AMD Athlon™ MP processor model 10. The power management features of the processor are compliant with the ACPI 1.0b and ACPI 2.0 specifications.

#### 4.1 Power Management States

The AMD Athlon MP processor model 10 supports low-power Halt and Stop Grant states. These states are used by advanced configuration and power interface (ACPI) enabled operating systems for processor power management.

Figure 2 shows the power management states of the processor. The figure includes the ACPI "Cx" naming convention for these states.

Note: The AMD Athlon™ System Bus is connected during the following states:

- 1) The Probe state

- 2) During transitions between the Halt state and the C2 Stop Grant state

- 3) During transitions between the C2 Stop Grant state and the Halt state

- 4) C0 Working state

Figure 2. AMD Athlon™ MP Processor Model 10 Power Management States

26426C-October 2003

The following sections provide an overview of the power management states. For more details, refer to the  $AMD\ Athlon^{TM}$  and  $AMD\ Duron^{TM}$  System Bus Specification, order# 21902.

**Note:** In all power management states that the processor is powered, the system must not stop the system clock (SYSCLK/SYSCLK#) to the processor.

#### **Working State**

The Working state is the state in which the processor is executing instructions.

#### **Halt State**

When the processor executes the HLT instruction, the processor enters the Halt state and issues a Halt special cycle to the AMD Athlon system bus. The processor only enters the low power state dictated by the CLK\_Ctl MSR if the system controller (Northbridge) disconnects the AMD Athlon system bus in response to the Halt special cycle.

If STPCLK# is asserted, the processor will exit the Halt state and enter the Stop Grant state. The processor will initiate a system bus connect, if it is disconnected, then issue a Stop Grant special cycle. When STPCLK# is deasserted, the processor will exit the Stop Grant state and re-enter the Halt state. The processor will issue a Halt special cycle when re-entering the Halt state.

The Halt state is exited when the processor detects the assertion of INIT#, RESET#, SMI#, or an interrupt via the INTR or NMI pins, or via a local APIC interrupt message. When the Halt state is exited, the processor will initiate an AMD Athlon system bus connect if it is disconnected.

#### **Stop Grant States**

The processor enters the Stop Grant state upon recognition of assertion of STPCLK# input. After entering the Stop Grant state, the processor issues a Stop Grant special bus cycle on the AMD Athlon system bus. The processor is not in a low-power state at this time, because the AMD Athlon system bus is still connected. After the Northbridge disconnects the AMD Athlon system bus in response to the Stop Grant special bus cycle, the processor enters a low-power state dictated by the CLK\_Ctl MSR. If the Northbridge needs to probe the processor during the Stop Grant state while the system bus is disconnected, it

must first connect the system bus. Connecting the system bus places the processor into the higher power probe state. After the Northbridge has completed all probes of the processor, the Northbridge must disconnect the AMD Athlon system bus again so that the processor can return to the low-power state. During the Stop Grant states, the processor latches INIT#, INTR, NMI, SMI#, or a local APIC interrupt message, if they are asserted.

The Stop Grant state is exited upon the deassertion of STPCLK# or the assertion of RESET#. When STPCLK# is deasserted, the processor initiates a connect of the AMD Athlon system bus if it is disconnected. After the processor enters the Working state, any pending interrupts are recognized and serviced and the processor resumes execution at the instruction boundary where STPCLK# was initially recognized. If RESET# is sampled asserted during the Stop Grant state, the processor exits the Stop Grant state and the reset process begins.

There are two mechanisms for asserting STPCLK#—hardware and software.

The Southbridge can force STPCLK# assertion for throttling to protect the processor from exceeding its maximum case temperature. This is accomplished by asserting the THERM# input to the Southbridge. Throttling asserts STPCLK# for a percentage of a predefined throttling period: STPCLK# is repetitively asserted and deasserted until THERM# is deasserted.

Software can force the processor into the Stop Grant state by accessing ACPI-defined registers typically located in the Southbridge.

The operating system places the processor into the C2 Stop Grant state by reading the P\_LVL2 register in the Southbridge.

If an ACPI Thermal Zone is defined for the processor, the operating system can initiate throttling with STPCLK# using the ACPI defined P\_CNT register in the Southbridge. The Northbridge connects the AMD Athlon system bus, and the processor enters the Probe state to service cache snoops during Stop Grant for C2 or throttling.

26426C-October 2003

In C2, probes are allowed, as shown in Figure 2 on page 9

The Stop Grant state is also entered for the S1, Powered On Suspend, system sleep state based on a write to the SLP\_TYP and SLP\_EN fields in the ACPI-defined Power Management 1 control register in the Southbridge. During the S1 sleep state, system software ensures no bus master or probe activity occurs. The Southbridge deasserts STPCLK# and brings the processor out of the S1 Stop Grant state when any enabled resume event occurs.

#### **Probe State**

The Probe state is entered when the Northbridge connects the AMD Athlon system bus to probe the processor (for example, to snoop the processor caches) when the processor is in the Halt or Stop Grant state. When in the Probe state, the processor responds to a probe cycle in the same manner as when it is in the Working state. When the probe has been serviced, the processor returns to the same state as when it entered the Probe state (Halt or Stop Grant state). When probe activity is completed the processor only returns to a low-power state after the Northbridge disconnects the AMD Athlon system bus again.

#### 4.2 Connect and Disconnect Protocol

Significant power savings of the processor only occur if the processor is disconnected from the system bus by the Northbridge while in the Halt or Stop Grant state. The Northbridge can optionally initiate a bus disconnect upon the receipt of a Halt or Stop Grant special cycle. The option of disconnecting is controlled by an enable bit in the Northbridge. If the Northbridge requires the processor to service a probe after the system bus has been disconnected, it must first initiate a system bus connect.

#### **Connect Protocol**

In addition to the legacy STPCLK# signal and the Halt and Stop Grant special cycles, the AMD Athlon system bus connect protocol includes the CONNECT, PROCRDY, and CLKFWDRST signals and a Connect special cycle.

AMD Athlon system bus disconnects are initiated by the Northbridge in response to the receipt of a Halt or Stop Grant. Reconnect is initiated by the processor in response to an interrupt for Halt or STPCLK# deassertion. Reconnect is initiated by the Northbridge to probe the processor.

The Northbridge contains BIOS programmable registers to enable the system bus disconnect in response to Halt and Stop Grant special cycles. When the Northbridge receives the Halt or Stop Grant special cycle from the processor and, if there are no outstanding probes or data movements, the Northbridge deasserts CONNECT a minimum of eight SYSCLK periods after the last command sent to the processor. The processor detects the deassertion of CONNECT on a rising edge of SYSCLK and deasserts PROCRDY to the Northbridge. In return, the Northbridge asserts CLKFWDRST in anticipation of reestablishing a connection at some later point.

**Note:** The Northbridge must disconnect the processor from the AMD Athlon system bus before issuing the Stop Grant special cycle to the PCI bus or passing the Stop Grant special cycle to the Southbridge for systems that connect to the Southbridge with HyperTransport<sup>TM</sup> technology.

This note applies to current chipset implementation—alternate chipset implementations that do not require this are possible.

26426C-October 2003

**Note:** In response to Halt special cycles, the Northbridge passes the Halt special cycle to the PCI bus or Southbridge immediately.

The processor can receive an interrupt after it sends a Halt special cycle, or STPCLK# deassertion after it sends a Stop Grant special cycle to the Northbridge but before the disconnect actually occurs. In this case, the processor sends the Connect special cycle to the Northbridge, rather than continuing with the disconnect sequence. In response to the Connect special cycle, the Northbridge cancels the disconnect request.

The system is required to assert the CONNECT signal before returning the C-bit for the connect special cycle (assuming CONNECT has been deasserted).

For more information, see the *AMD Athlon™* and *AMD Duron™* System Bus Specification, order# 21902 for the definition of the C-bit and the Connect special cycle.

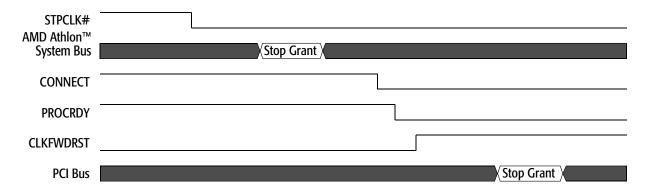

Figure 3 shows STPCLK# assertion resulting in the processor in the Stop Grant state and the AMD Athlon system bus disconnected.

Figure 3. AMD Athlon™ System Bus Disconnect Sequence in the Stop Grant State

An example of the AMD Athlon system bus disconnect sequence is as follows:

- 1. The peripheral controller (Southbridge) asserts STPCLK# to place the processor in the Stop Grant state.

- 2. When the processor recognizes STPCLK# asserted, it enters the Stop Grant state and then issues a Stop Grant special cycle.

- 3. When the special cycle is received by the Northbridge, it deasserts CONNECT, assuming no probes are pending, initiating a bus disconnect to the processor.

- 4. The processor responds to the Northbridge by deasserting PROCRDY.

- 5. The Northbridge asserts CLKFWDRST to complete the bus disconnect sequence.

- 6. After the processor is disconnected from the bus, the processor enters a low-power state. The Northbridge passes the Stop Grant special cycle along to the Southbridge.

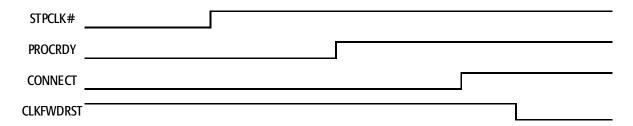

Figure 4 shows the signal sequence of events that takes the processor out of the Stop Grant state, connects the processor to the AMD Athlon system bus, and puts the processor into the Working state.

Figure 4. Exiting the Stop Grant State and Bus Connect Sequence

The following sequence of events removes the processor from the Stop Grant state and connects it to the system bus:

- 1. The Southbridge deasserts STPCLK#, informing the processor of a wake event.

- 2. When the processor recognizes STPCLK# deassertion, it exits the low-power state and asserts PROCRDY, notifying the Northbridge to connect to the bus.

- 3. The Northbridge asserts CONNECT.

- 4. The Northbridge deasserts CLKFWDRST, synchronizing the forwarded clocks between the processor and the Northbridge.

- 5. The processor issues a Connect special cycle on the system bus and resumes operating system and application code execution.

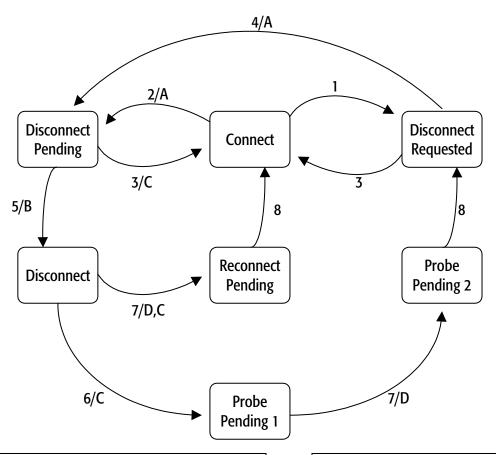

#### Connect State Diagram

Figure 5 below and Figure 6 on page 18 show the Northbridge and processor connect state diagrams, respectively.

|   | Condition                                                                                                                                                                                                                        |  |  |  |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1 | A disconnect is requested and probes are still pending.                                                                                                                                                                          |  |  |  |  |

| 2 | A disconnect is requested and no probes are pending.                                                                                                                                                                             |  |  |  |  |

| 3 | A Connect special cycle from the processor.                                                                                                                                                                                      |  |  |  |  |

| 4 | No probes are pending.                                                                                                                                                                                                           |  |  |  |  |

| 5 | PROCRDY is deasserted.                                                                                                                                                                                                           |  |  |  |  |

| 6 | A probe needs service.                                                                                                                                                                                                           |  |  |  |  |

| 7 | PROCRDY is asserted.                                                                                                                                                                                                             |  |  |  |  |

| 8 | Three SYSCLK periods after CLKFWDRST is deasserted.  Although reconnected to the system interface, the  Northbridge must not issue any non-NOP SysDC  commands for a minimum of four SYSCLK periods after deasserting CLKFWDRST. |  |  |  |  |

|   | Action                                                       |  |  |  |  |

|---|--------------------------------------------------------------|--|--|--|--|

| Α | Deassert CONNECT eight SYSCLK periods after last SysDC sent. |  |  |  |  |

| В | Assert CLKFWDRST.                                            |  |  |  |  |

| С | Assert CONNECT.                                              |  |  |  |  |

| D | Deassert CLKFWDRST.                                          |  |  |  |  |

**Figure 5. Northbridge Connect State Diagram**

|   | Condition                                                                                          |

|---|----------------------------------------------------------------------------------------------------|

| 1 | CONNECT is deasserted by the Northbridge (for a previously sent Halt or Stop Grant special cycle). |

| 2 | Processor receives a wake-up event and must cancel the disconnect request.                         |

| 3 | Deassert PROCRDY and slow down internal clocks.                                                    |

| 4 | Processor wake-up event or CONNECT asserted by Northbridge.                                        |

| 5 | CLKFWDRST is deasserted by the Northbridge.                                                        |

| 6 | Forward clocks start three SYSCLK periods after CLKFWDRST is deasserted.                           |

|     | Action                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Α   | CLKFWDRST is asserted by the Northbridge.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| В   | Issue a Connect special cycle.*                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| С   | Return internal clocks to full speed and assert PROCRDY.                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Not | e:                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|     | * The Connect special cycle is only issued after a processor wake-up event (interrupt or STPCLK# deassertion) occurs. If the AMD Athlon™ system bus is connected so the Northbridge can probe the processor, a Connect special cycle is not issued at that time (it is only issued after a subsequent processor wake-up event). |  |  |  |  |  |

Chapter 4

**Figure 6. Processor Connect State Diagram**

*18*

Power Management

#### 4.3 Clock Control

The processor implements a Clock Control (CLK\_Ctl) MSR (address  $C001\_001Bh$ ) that determines the internal clock divisor when the AMD Athlon system bus is disconnected.

Refer to the  $AMD\ Athlon^{TM}\ and\ AMD\ Duron^{TM}\ Processors\ BIOS$ , Software, and Debug Developers Guide, order# 21656, for more details on the CLK\_Ctl register.

# Preliminary Information

AMD Athlon™ MP Processor Model 10 Data Sheet for Multiprocessor Platforms

26426C-October 2003

# 5 **CPUID Support**

AMD Athlon™ MP processor model 10 version and feature set recognition can be performed through the use of the CPUID instruction, that provides complete information about the processor—vendor, type, name, etc., and its capabilities. Software can make use of this information to accurately tune the system for maximum performance and benefit to users.

For information on the use of the CPUID instruction see the following documents:

- AMD Processor Recognition Application Note, order# 20734

- AMD Athlon<sup>TM</sup> Processor Recognition Application Note Addendum, order# 21922

- *AMD Athlon*<sup>TM</sup> *and AMD Duron*<sup>TM</sup> *Processors BIOS, Software, and Debug Developers Guide,* order# 21656

#### **Preliminary Information**

AMD Athlon™ MP Processor Model 10 Data Sheet for Multiprocessor Platforms

26426C-October 2003

# 6 Electrical and Thermal Specifications for the AMD Athlon™ MP Processor Model 10

This chapter provides the electrical and thermal specifications for the AMD Athlon<sup>TM</sup> MP processor model 10.

Table 1 shows the electrical and thermal specifications in the C0 Working state and the S1 Stop Grant state for the AMD Athlon MP processor model 10.

Table 1. Electrical and Thermal Specifications for the AMD Athlon™ MP Processor Model 10

|                                 | V <sub>CC CORE</sub> | I <sub>CC</sub> (Processor Current)                  |         |                            |         | 71 10 5 |         | Maximum Die<br>Temperature |

|---------------------------------|----------------------|------------------------------------------------------|---------|----------------------------|---------|---------|---------|----------------------------|

| Frequency in MHz (Model Number) | (Core<br>Voltage)    | Working State CO Stop Grant S1 <sup>1, 2, 3, 4</sup> |         | Thermal Power <sup>5</sup> |         |         |         |                            |

| ,                               |                      | Maximum                                              | Typical | Maximum                    | Typical | Maximum | Typical |                            |

| 2000 (2600+)                    | 1.60 V               | 37.5 A                                               | 29.5 A  | 8.75 A                     | 6.88 A  | 60.0 W  | 47.2 W  | 90°C                       |

| 2133 (2800+)                    | 1.00 V               | 31.3 K                                               | 23.3 K  | 0.73 K                     | 0.00 A  | 00.0 W  | 77.2 VV | 30 C                       |

#### Notes:

- 1. See Figure 2, "AMD Athlon™ MP Processor Model 10 Power Management States" on page 9.

- 2. The maximum Stop Grant currents are absolute worst case currents for parts that may yield from the worst case corner of the process and are not representative of the typical Stop Grant current that is currently about one-third of the maximum specified current.

- 3. These currents occur when the AMD Athlon™ system bus is disconnected and a low power ratio of 1/64 is applied to the core clock grid of the processor as dictated by a value of 2003\_D22Fh programmed into the Clock Control (CLK\_Ctl) MSR. For more information, refer to the AMD Athlon™ and AMD Duron™ Processors BIOS, Software, and Debug Developers Guide, order# 21656.

- 4. The Stop Grant current consumption is characterized at 50°C and not tested.

- 5. Thermal design power represents the maximum sustained power dissipated while executing publicly-available software or instruction sequences under normal system operation at nominal V<sub>CC\_CORE</sub>. Thermal solutions must monitor the temperature of the processor to prevent the processor from exceeding its maximum die temperature.

26426C-October 2003

### 7 Electrical Data

This chapter describes the electrical characteristics that apply to the AMD Athlon<sup>TM</sup> MP processor model 10.

### 7.1 Conventions

The conventions used in this chapter are as follows:

- Current specified as being sourced by the processor is *negative*.

- Current specified as being sunk by the processor is *positive*.

### 7.2 Interface Signal Groupings

The electrical data in this chapter is presented separately for each signal group.

Table 2 defines each group and the signals contained in each group.

**Table 2.** Interface Signal Groupings

| Signal Group              | Signals                                                                                                                                                                                  | Notes                                                                                                                                                                                                                                 |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power                     | VID[4:0], VCCA, V <sub>CC_CORE</sub> , COREFB, COREFB#                                                                                                                                   | See , "Voltage Identification (VID[4:0])" on page 26, "" on page 75, "VCCA AC and DC Characteristics" on page 27, "VCCA Pin" on page 75, "V <sub>CC_CORE</sub> Characteristics" on page 28, and "COREFB and COREFB# Pins" on page 71. |

| Frequency                 | FID[3:0]                                                                                                                                                                                 | See "Frequency Identification (FID[3:0])" on page 27 and "FID[3:0] Pins" on page 71.                                                                                                                                                  |

| System Clocks             | SYSCLK, SYSCLK# (Tied to CLKIN/CLKIN# and RSTCLK/RSTCLK#), PLLBYPASSCLK#, PLLBYPASSCLK                                                                                                   | See Table 8, "SYSCLK and SYSCLK# DC Characteristics," on page 31, Table 9, "SYSCLK and SYSCLK# AC Characteristics," on page 32, "SYSCLK and SYSCLK#" on page 75, and "PLL Bypass and Test Pins" on page 74.                           |

| AMD Athlon™<br>System Bus | SADDIN[14:2]#, SADDOUT[14:2]#, SADDINCLK#,<br>SADDOUTCLK#, SFILLVAL#, SDATAINVAL#,<br>SDATAOUTVAL#, SDATA[63:0]#, SDATAINCLK[3:0]#,<br>SDATAOUTCLK[3:0]#, CLKFWDRST, PROCRDY,<br>CONNECT | See "AMD Athlon™ System Bus AC and DC Characteristics" on page 33, and "CLKFWDRST Pin" on page 70.                                                                                                                                    |

**Table 2.** Interface Signal Groupings (Continued)

| Signal Group  | Signals                                                                                            | Notes                                                                                                                                                                                                                                                                                 |

|---------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Southbridge   | RESET#, INTR, NMI, SMI#, INIT#, A20M#, FERR,<br>IGNNE#, STPCLK#, FLUSH#                            | See "General AC and DC Characteristics" on page 35, "INTR Pin" on page 73, "NMI Pin" on page 74, "SMI# Pin" on page 75, "INIT# Pin" on page 73, "A20M# Pin" on page 70, "FERR Pin" on page 71, "IGNNE# Pin" on page 73, "SYSCLK and SYSCLK#" on page 75, and "FLUSH# Pin" on page 73. |

| JTAG          | TMS, TCK, TRST#, TDI, TDO                                                                          | See "General AC and DC Characteristics" on page 35.                                                                                                                                                                                                                                   |

| Test          | PLLBYPASS#, PLLTEST#, PLLMON1, PLLMON2,<br>SCANCLK1, SCANCLK2, SCANSHIFTEN,<br>SCANINTEVAL, ANALOG | See "General AC and DC Characteristics" on page 35, "PLL Bypass and Test Pins" on page 74, "Scan Pins" on page 74, "Analog Pin" on page 70.                                                                                                                                           |

| Miscellaneous | DBREQ#, DBRDY, PWROK                                                                               | See "General AC and DC Characteristics" on page 35, "DBRDY and DBREQ# Pins" on page 71, "PWROK Pin" on page 74.                                                                                                                                                                       |

| APIC          | PICD[1:0]#, PICCLK                                                                                 | See "APIC Pins AC and DC Characteristics" on page 40, and "APIC Pins, PICCLK, PICD[1:0]#" on page 70.                                                                                                                                                                                 |

| Thermal       | THERMDA, THERMDC                                                                                   | See Table 13, "Thermal Diode Electrical<br>Characteristics," on page 38, and "THERMDA<br>and THERMDC Pins" on page 75.                                                                                                                                                                |

### 7.3 Voltage Identification (VID[4:0])

Table 3 shows the VID[4:0] DC Characteristics. For more information on VID[4:0] DC Characteristics, see "" on page 75.

Table 3. VID[4:0] DC Characteristics

| Parameter       | Description         | Min  | Max     |

|-----------------|---------------------|------|---------|

| I <sub>OL</sub> | Output Current Low  | 6 mA |         |

| V <sub>OH</sub> | Output High Voltage | -    | 5.25 V* |

<sup>\*</sup> The VID pins are either open circuit or pulled to ground. It is recommended that these pins are not pulled above 5.25 V, which is 5.0 V + 5%.

### 7.4 Frequency Identification (FID[3:0])

Table 4 shows the FID[3:0] DC characteristics. For more information, see "FID[3:0] Pins" on page 71.

Table 4. FID[3:0] DC Characteristics

| Parameter       | Description         | Min  | Max                                    |

|-----------------|---------------------|------|----------------------------------------|

| I <sub>OL</sub> | Output Current Low  | 6 mA |                                        |

| V               | Output High Voltage |      | 2.625 V <sup>1</sup>                   |

| V <sub>OH</sub> | Output High Voltage | _    | $ V_{OH} - V_{CC\_CORE}  \le 1.60 V^2$ |

#### Note:

- 1. The FID pins must not be pulled above 2.625 V, which is equal to 2.5 V plus a maximum of five percent.

- 2. Refer to "VCC\_2.5V Generation Circuit" found in the section, "Motherboard Required Circuits," of the AMD Athlon™ Processor-Based Motherboard Design Guide, order# 24363.

### 7.5 VCCA AC and DC Characteristics

Table 5 shows the AC and DC characteristics for VCCA. For more information, see "VCCA Pin" on page 75.

**Table 5. VCCA AC and DC Characteristics**

| Symbol            | Parameter        | Min  | Nominal | Max                                                    | Units  | Notes |

|-------------------|------------------|------|---------|--------------------------------------------------------|--------|-------|

| V                 | VCCA Din Voltago | 2.25 | 2.5     | 2.75                                                   | V      | 1     |

| $V_{VCCA}$        | VCCA Pin Voltage | 2.25 | 2.5     | $\mid V_{VCCA} - V_{CC\_CORE} \mid \le 1.60 \text{ V}$ | _      | 2     |

| I <sub>VCCA</sub> | VCCA Pin Current | 0    |         | 50                                                     | mA/GHz | 3     |

#### Notes:

- 1. Minimum and Maximum voltages are absolute. No transients below minimum nor above maximum voltages are permitted.

- 2. For more information, refer to the AMD Athlon™ Processor-Based Motherboard Design Guide, order# 24363.

- 3. Measured at 2.5 V.

### 7.6 Decoupling

See the  $AMD\ Athlon^{\text{TM}}\ Processor\text{-}Based\ Motherboard\ Design\ Guide,$  order# 24363, or contact your local AMD office for information about the decoupling required on the motherboard for use with the AMD Athlon MP processor model 10.

## 7.7 V<sub>CC\_CORE</sub> Characteristics

Table 6 shows the AC and DC characteristics for  $V_{CC\_CORE}$ . See Figure 7 on page 29 for a graphical representation of the  $V_{CC\_CORE}$  waveform.

Table 6.  $V_{CC\_CORE}$  AC and DC Characteristics

|                                                         |                                                                                                                                                                                                           | Units                                                                                                                                                                                                                         |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum static voltage above V <sub>CC_CORE_NOM</sub> * | 50                                                                                                                                                                                                        | mV                                                                                                                                                                                                                            |

| Maximum static voltage below V <sub>CC_CORE_NOM</sub> * | -50                                                                                                                                                                                                       | mV                                                                                                                                                                                                                            |

| Maximum excursion above V <sub>CC_CORE_NOM</sub> *      | 150                                                                                                                                                                                                       | mV                                                                                                                                                                                                                            |

| Maximum excursion below V <sub>CC_CORE_NOM</sub> *      | -100                                                                                                                                                                                                      | mV                                                                                                                                                                                                                            |

| Maximum excursion time for AC transients                | 10                                                                                                                                                                                                        | μς                                                                                                                                                                                                                            |

| Negative excursion time for AC transients               | 5                                                                                                                                                                                                         | μς                                                                                                                                                                                                                            |

|                                                         | Maximum static voltage below V <sub>CC_CORE_NOM</sub> *  Maximum excursion above V <sub>CC_CORE_NOM</sub> *  Maximum excursion below V <sub>CC_CORE_NOM</sub> *  Maximum excursion time for AC transients | Maximum static voltage below V <sub>CC_CORE_NOM</sub> *  —50  Maximum excursion above V <sub>CC_CORE_NOM</sub> *  150  Maximum excursion below V <sub>CC_CORE_NOM</sub> *  —100  Maximum excursion time for AC transients  10 |

<sup>\*</sup> All voltage measurements are taken differentially at the COREFB/COREFB# pins.

Figure 7 shows the processor core voltage ( $V_{CC\_CORE}$ ) waveform response to perturbation. The  $t_{MIN\_AC}$  (negative AC transient excursion time) and  $t_{MAX\_AC}$  (positive AC transient excursion time) represent the maximum allowable time below or above the DC tolerance thresholds.

Figure 7. V<sub>CC CORE</sub> Voltage Waveform

### 7.8 Absolute Ratings

The AMD Athlon MP processor model 10 should not be subjected to conditions exceeding the absolute ratings, as such conditions can adversely affect long-term reliability or result in functional damage.

Table 7 lists the maximum absolute ratings of operation for the AMD Athlon MP processor model 10.

**Table 7. Absolute Ratings**

| Parameter            | Description                      | Min    | Max                              |

|----------------------|----------------------------------|--------|----------------------------------|

| V <sub>CC_CORE</sub> | Processor core voltage supply    | -0.5 V | V <sub>CC_CORE</sub> Max + 0.5 V |

| VCCA                 | Processor PLL voltage supply     | -0.5 V | VCCA Max + 0.5 V                 |

| V <sub>PIN</sub>     | Voltage on any signal pin        | -0.5 V | V <sub>CC_CORE</sub> Max + 0.5 V |

| T <sub>STORAGE</sub> | Storage temperature of processor | -40°C  | 100°C                            |

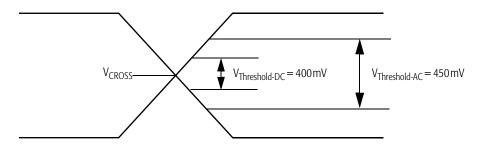

### 7.9 SYSCLK and SYSCLK# AC and DC Characteristics

Table 8 shows the DC characteristics of the SYSCLK and SYSCLK# differential clocks. The SYSCLK signal represents CLKIN and RSTCLK tied together while the SYSCLK# signal represents CLKIN# and RSTCLK# tied together.

Table 8. SYSCLK and SYSCLK# DC Characteristics

| Symbol                    | Description                                                      | Min | Max                          | Units |

|---------------------------|------------------------------------------------------------------|-----|------------------------------|-------|

| V <sub>Threshold-DC</sub> | Crossing before transition is detected (DC)                      | 400 |                              | mV    |

| V <sub>Threshold-AC</sub> | Crossing before transition is detected (AC)                      | 450 |                              | mV    |

| I <sub>LEAK_P</sub>       | Leakage current through P-channel pullup to V <sub>CC_CORE</sub> | -1  |                              | mA    |

| I <sub>LEAK_N</sub>       | Leakage current through N-channel pulldown to VSS (Ground)       |     | 1                            | mA    |

| V <sub>CROSS</sub>        | Differential signal crossover                                    |     | V <sub>CC_CORE</sub> / 2±100 | mV    |

| C <sub>PIN</sub>          | Capacitance *                                                    | 4   | 25 *                         | pF    |

Figure 8 shows the DC characteristics of the SYSCLK and SYSCLK# signals.

Figure 8. SYSCLK and SYSCLK# Differential Clock Signals

<sup>\*</sup> The following processor inputs have twice the listed capacitance because they connect to two input pads—SYSCLK and SYSCLK#.

SYSCLK connects to CLKIN/RSTCLK. SYSCLK# connects to CLKIN#/RSTCLK#.

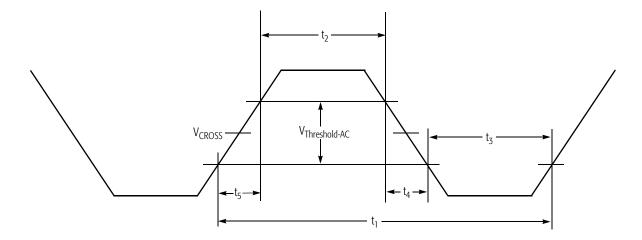

Table 9 shows the SYSCLK/SYSCLK# differential clock AC characteristics of the AMD Athlon MP processor model 10.

Table 9. SYSCLK and SYSCLK# AC Characteristics

| Symbol         | Parameter Description | Minimum | Maximum | Units | Notes |

|----------------|-----------------------|---------|---------|-------|-------|

|                | Clock Frequency       | 50      | 133     | MHz   | 1     |

|                | Duty Cycle            | 30%     | 70%     |       |       |

| t <sub>1</sub> | Period                | 7.5     |         | ns    | 2, 3  |

| t <sub>2</sub> | High Time             | 1.05    |         | ns    |       |

| t <sub>3</sub> | Low Time              | 1.05    |         | ns    |       |

| t <sub>4</sub> | Fall Time             |         | 2       | ns    |       |

| t <sub>5</sub> | Rise Time             |         | 2       | ns    |       |

|                | Period Stability      |         | ± 300   | ps    |       |

- 1. The AMD Athlon™ system bus operates at twice the front-side bus (FSB) frequency shown here.

- 2. Circuitry driving the AMD Athlon system bus clock inputs must exhibit a suitably low closed-loop jitter bandwidth to allow the PLL to track the jitter. The –20dB attenuation point, as measured into a 20- or 30-pF load must be less than 500 kHz.

- 3. Circuitry driving the AMD Athlon system bus clock inputs may purposely alter the AMD Athlon system bus clock frequency (spread spectrum clock generators). In no cases can the AMD Athlon system bus period violate the minimum specification above. AMD Athlon system bus clock inputs can vary from 100% of the specified frequency to 99% of the specified frequency at a maximum rate of 100 kHz.

Figure 9 shows a sample waveform of the SYSCLK signal.

Figure 9. SYSCLK Waveform

### 7.10 AMD Athlon™ System Bus AC and DC Characteristics

Table 10 shows the DC characteristics of the AMD Athlon system bus used by the AMD Athlon MP processor model 10. See Table 6, " $V_{CC\_CORE}$  AC and DC Characteristics," on page 28 for information on  $T_{DIE}$  and  $V_{CC\_CORE}$ . For information about SYSCLK and SYSCLK#, see "SYSCLK and SYSCLK#" on page 75 and Table 19, "Pin Name Abbreviations," on page 54.

Table 10. AMD Athlon™ System Bus DC Characteristics

| Symbol                   | Parameter                                  | Condition                                         | Min                                  | Max                                  | Units      | Notes |

|--------------------------|--------------------------------------------|---------------------------------------------------|--------------------------------------|--------------------------------------|------------|-------|

| V <sub>REF</sub>         | DC Input Reference Voltage                 |                                                   | (0.5 x V <sub>CC_CORE</sub> )<br>-50 | (0.5 x V <sub>CC_CORE</sub> )<br>+50 | mV         | 1     |

| I <sub>VREF_LEAK_P</sub> | V <sub>REF</sub> Tristate Leakage Pullup   | $V_{IN} = V_{REF}$ Nominal                        | -100                                 |                                      | μ <b>A</b> |       |

| I <sub>VREF_LEAK_N</sub> | V <sub>REF</sub> Tristate Leakage Pulldown | $V_{IN} = V_{REF}$ Nominal                        |                                      | 100                                  | μΑ         |       |

| V <sub>IH</sub>          | Input High Voltage                         |                                                   | V <sub>REF</sub> + 200               | V <sub>CC_CORE</sub> + 500           | m۷         |       |

| V <sub>IL</sub>          | Input Low Voltage                          |                                                   | -500                                 | V <sub>REF</sub> – 200               | m۷         |       |

| I <sub>LEAK_P</sub>      | Tristate Leakage Pullup                    | V <sub>IN</sub> = VSS<br>(Ground)                 | -1                                   |                                      | mA         |       |

| I <sub>LEAK_N</sub>      | Tristate Leakage Pulldown                  | V <sub>IN</sub> = V <sub>CC_CORE</sub><br>Nominal |                                      | 1                                    | mA         |       |

| C <sub>IN</sub>          | Input Pin Capacitance                      |                                                   | 4                                    | 7                                    | pF         |       |

| R <sub>ON</sub>          | Output Resistance                          |                                                   | 0.90 x R <sub>setN,P</sub>           | 1.1 x R <sub>setN,P</sub>            | Ω          | 2     |

| R <sub>setP</sub>        | Impedance Set Point, P Channel             |                                                   | 40                                   | 70                                   | Ω          | 2     |

| R <sub>setN</sub>        | Impedance Set Point, N Channel             |                                                   | 40                                   | 70                                   | Ω          | 2     |

<sup>1.</sup>  $V_{REF}$  is nominally set to 50% of  $V_{CC\_CORE}$  with actual values that are specific to motherboard design implementation.  $V_{REF}$  must be created with a sufficiently accurate DC source and a sufficiently quiet AC response to adhere to the  $\pm$  50 mV specification listed above.

<sup>2.</sup> Measured at  $V_{CC\_CORE}$  / 2.

The AC characteristics of the AMD Athlon system bus are shown in Table 11 on page 34. The parameters are grouped based on the source or destination of the signals involved.

**Table 11. AMD Athlon™ System Bus AC Characteristics**

| Group             | Symbol                     | Parameter                                          | Min  | Max  | Units | Notes |

|-------------------|----------------------------|----------------------------------------------------|------|------|-------|-------|

| All Cianale       | T <sub>RISE</sub>          | Output Rise Slew Rate                              | 1    | 3    | V/ns  | 1     |

| All Signals       | T <sub>FALL</sub>          | Output Fall Slew Rate                              | 1    | 3    | V/ns  | 1     |

|                   | T <sub>SKEW-SAMEEDGE</sub> | Output skew with respect to the same clock edge    | -    | 385  | ps    | 2     |

| F                 | T <sub>SKEW-DIFFEDGE</sub> | Output skew with respect to a different clock edge | -    | 770  | ps    | 2     |

| Forward<br>Clocks | T <sub>SU</sub>            | Input Data Setup Time                              | 300  |      | ps    | 3     |

|                   | T <sub>HD</sub>            | Input Data Hold Time                               | 300  |      | ps    | 3     |

|                   | C <sub>IN</sub>            | Capacitance on input clocks                        | 4    | 25   | pF    |       |

|                   | C <sub>OUT</sub>           | Capacitance on output clocks                       | 4    | 12   | pF    |       |

|                   | T <sub>VAL</sub>           | RSTCLK to Output Valid                             | 250  | 2000 | ps    | 4, 5  |

| Sync              | T <sub>SU</sub>            | Setup to RSTCLK                                    | 500  |      | ps    | 4, 6  |

|                   | T <sub>HD</sub>            | Hold from RSTCLK                                   | 1000 |      | ps    | 4, 6  |

- 1. Rise and fall time ranges are guidelines over which the I/O has been characterized.

- T<sub>SKEW-SAMEEDGE</sub> is the maximum skew within a clock forwarded group between any two signals or between any signal and its forward clock, as measured at the package, with respect to the same clock edge.

T<sub>SKEW-DIFFEDGE</sub> is the maximum skew within a clock forwarded group between any two signals or between any signal and its forward clock, as measured at the package, with respect to different clock edges.

- 3. Input SU and HD times are with respect to the appropriate Clock Forward Group input clock.

- 4. The synchronous signals include PROCRDY, CONNECT, and CLKFWDRST.

- 5. T<sub>VAI</sub> is RSTCLK rising edge to output valid for PROCRDY. Test Load is 25 pF.

- 6. T<sub>SU</sub> is setup of CONNECT/CLKFWDRST to rising edge of RSTCLK. T<sub>HD</sub> is hold of CONNECT/CLKFWDRST from rising edge of RSTCLK.

#### 7.11 General AC and DC Characteristics

Table 12 shows the AMD Athlon MP processor model 10 AC and DC characteristics of the Southbridge, JTAG, test, and miscellaneous pins.

**Table 12. General AC and DC Characteristics**

| Symbol              | Parameter Description     | Condition                                         | Min                                    | Max                              | Units | Notes |

|---------------------|---------------------------|---------------------------------------------------|----------------------------------------|----------------------------------|-------|-------|