## PIN-PROGRAMMABLE PRECISION CLOCK MULTIPLIER

#### **Features**

- Not recommended for new designs. For alternatives, see the Si533x family of products.

- Selectable output frequencies ranging from 19.44 to 1050 MHz

- Low jitter clock outputs w/jitter

generation as low as 0.6 ps rms

(50 kHz–80 MHz)

- Integrated loop filter with selectable loop bandwidth (150 kHz to 1.3 MHz)

- Four clock inputs w/manual or automatically controlled switching

- Five clock outputs with selectable signal format (LVPECL, LVDS, CML, CMOS)

- Support for ITU G.709 FEC ratios (255/238, 255/237, 255/236)

- LOS alarm outputs

- Pin-programmable settings

- On-chip voltage regulator for 1.8 ±5%, 2.5 V ±10%, or 3.3 V ±10% operation

- Small size: 14 x 14 mm 100-pin TQFP

- Pb-free, RoHS compliant

Ordering Information: See page 21.

### **Applications**

- SONET/SDH OC-48/STM-16 and STM-64/OC-192 line cards

- GbE/10GbE, 1/2/4/8/10GFC line cards

- ITU G.709 line cards

- Test and measurement

### **Description**

The Si5365 is a low-jitter, precision clock multiplier for high-speed communication systems, including SONET OC-48/OC-192, Ethernet, and Fibre Channel, in which the application requires clock multiplication without jitter attenuation. The Si5365 accepts four clock inputs ranging from 19.44 to 707 MHz and generates five frequency-multiplied clock outputs ranging from 19.44 to 1050 MHz. The input clock frequency and clock multiplication ratio are selectable from a table of popular SONET, Ethernet, and Fibre Channel frequencies. The Si5365 is based on Silicon Laboratories' 3rd-generation DSPLL® technology, which provides any-frequency synthesis in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. The DSPLL loop bandwidth is digitally programmable, providing jitter performance optimization at the application level. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5365 is ideal for providing clock multiplication in high performance timing applications.

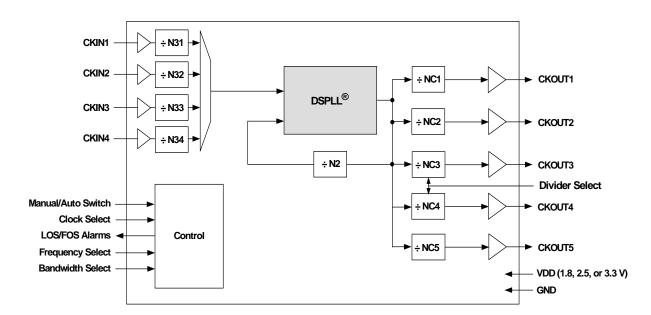

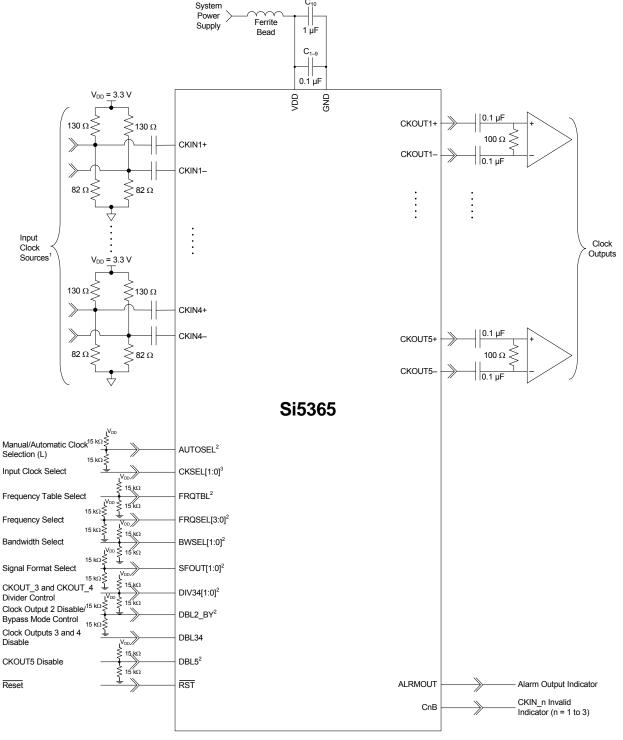

### **Functional Block Diagram**

# TABLE OF CONTENTS

| <u>Section</u>                   | <u>Page</u> |

|----------------------------------|-------------|

| 1. Electrical Specifications     |             |

| 2. Typical Application Schematic |             |

| 3. Functional Description        |             |

| 3.1. Further Documentation       |             |

| 4. Pin Descriptions: Si5365      |             |

| 5. Ordering Guide                |             |

| 6. Package Outline: 100-Pin TQFP |             |

| 7. PCB Land Pattern              |             |

| 8. Top Marking                   |             |

| 8.1. Si5365 Top Marking          |             |

| 8.2. Top Marking Explanation     |             |

| Document Change List             |             |

| Contact Information              |             |

# 1. Electrical Specifications

**Table 1. DC Characteristics**

(V<sub>DD</sub> = 1.8  $\pm$  5%, 2.5  $\pm$ 10%, or 3.3 V  $\pm$ 10%, T<sub>A</sub> = –40 to 85 °C)

| Parameter                                   | Symbol             | Test Condition                                        | Min  | Тур | Max  | Unit            |

|---------------------------------------------|--------------------|-------------------------------------------------------|------|-----|------|-----------------|

| Supply Current <sup>1</sup>                 | I <sub>DD</sub>    | LVPECL Format<br>622.08 MHz Out<br>All CKOUTs Enabled | _    | 394 | 435  | mA              |

|                                             |                    | LVPECL Format<br>622.08 MHz Out<br>1 CKOUT Enabled    | _    | 253 | 294  | mA              |

|                                             |                    | CMOS Format<br>19.44 MHz Out<br>All CKOUTs Enabled    | _    | 278 | 321  | mA              |

|                                             |                    | CMOS Format<br>19.44 MHz Out<br>1 CKOUT Enabled       | _    | 229 | 261  | mA              |

|                                             |                    | Disable Mode                                          | _    | 165 | _    | mA              |

| CKINn Input Pins <sup>2</sup>               |                    |                                                       |      | 1   | 1    |                 |

| Input Common Mode<br>Voltage (Input Thresh- |                    | 1.8 V ± 5%                                            | 0.9  | _   | 1.4  | V               |

| old Voltage)                                |                    | 2.5 V ± 10%                                           | 1    | _   | 1.7  | V               |

|                                             |                    | 3.3 V ± 10%                                           | 1.1  | _   | 1.95 | V               |

| Input Resistance                            | CKN <sub>RIN</sub> | Single-ended                                          | 20   | 40  | 60   | kΩ              |

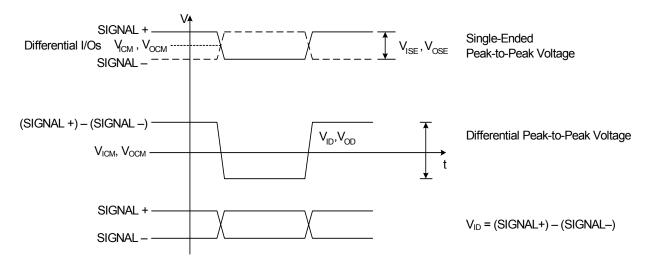

| Single-Ended Input<br>Voltage Swing         | V <sub>ISE</sub>   | f <sub>CKIN</sub> < 212.5 MHz<br>See Figure 1.        | 0.2  | _   | _    | V <sub>PP</sub> |

| (See Absolute Specs)                        |                    | f <sub>CKIN</sub> > 212.5 MHz<br>See Figure 1.        | 0.25 | _   | _    | V <sub>PP</sub> |

| Differential Input<br>Voltage Swing         | V <sub>ID</sub>    | f <sub>CKIN</sub> < 212.5 MHz<br>See Figure 1.        | 0.2  | _   | _    | V <sub>PP</sub> |

| (See Absolute Specs)                        |                    | fCKIN > 212.5 MHz<br>See Figure 1.                    | 0.25 | _   | _    | V <sub>PP</sub> |

#### Notes:

- 1. Current draw is independent of supply voltage

- 2. No under- or overshoot is allowed.

- 3. LVPECL outputs require nominal VDD ≥ 2.5 V.

- **4.** This is the amount of leakage that the 3-Level inputs can tolerate from an external driver. See Si53xx Family Reference Manual for more details.

- **5.** LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

**Table 1. DC Characteristics (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                                                                                  | Symbol               | Test Condition                                | Min                       | Тур                   | Max                   | Unit            |  |  |

|----------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------|---------------------------|-----------------------|-----------------------|-----------------|--|--|

| Output Clocks (CKOUTn) <sup>3</sup>                                                                                        |                      |                                               |                           |                       |                       |                 |  |  |

| Common Mode                                                                                                                | CKO <sub>VCM</sub>   | LVPECL 100 $\Omega$ load lineto-line          | V <sub>DD</sub> –<br>1.42 | _                     | V <sub>DD</sub> –1.25 | V               |  |  |

| Differential Output<br>Swing                                                                                               | CKO <sub>VD</sub>    | LVPECL 100 $\Omega$ load lineto-line          | 1.1                       | _                     | 1.9                   | V <sub>PP</sub> |  |  |

| Single Ended Output<br>Swing                                                                                               | CKO <sub>VSE</sub>   | LVPECL 100 $\Omega$ load lineto-line          | 0.5                       | _                     | 0.93                  | $V_{PP}$        |  |  |

| Differential Output<br>Voltage                                                                                             | CKO <sub>VD</sub>    | CML 100 $\Omega$ load line-to-line            | 350                       | 425                   | 500                   | $mV_PP$         |  |  |

| Common Mode Output<br>Voltage                                                                                              | CKO <sub>VCM</sub>   | CML 100 $\Omega$ load line-to-line            | _                         | V <sub>DD</sub> -0.36 | _                     | V               |  |  |

| Differential Output<br>Voltage                                                                                             | CKO <sub>VD</sub>    | LVDS 100 $\Omega$ load line-to-line           | 500                       | 700                   | 900                   | $mV_PP$         |  |  |

|                                                                                                                            |                      | Low Swing LVDS 100 $\Omega$ load line-to-line | 350                       | 425                   | 500                   | $mV_PP$         |  |  |

| Common Mode Output<br>Voltage                                                                                              | CKO <sub>VCM</sub>   | LVDS 100 $\Omega$ load line-to-line           | 1.125                     | 1.2                   | 1.275                 | V               |  |  |

| Differential Output<br>Resistance                                                                                          | CKO <sub>RD</sub>    | CML, LVPECL, LVDS                             | _                         | 200                   | _                     | Ω               |  |  |

| Output Voltage Low                                                                                                         | CKO <sub>VOLLH</sub> | CMOS                                          |                           | _                     | 0.4                   | V               |  |  |

| Output Voltage High                                                                                                        | CKO <sub>VOHLH</sub> | V <sub>DD</sub> = 1.71 V<br>CMOS              | 0.8 x<br>V <sub>DD</sub>  | _                     | _                     | V               |  |  |

| Output Drive Current (CMOS driving into                                                                                    | CKO <sub>IO</sub>    | V <sub>DD</sub> = 1.8 V                       | _                         | 7.5                   | _                     | mA              |  |  |

| CKO <sub>VOL</sub> for output low<br>or CKO <sub>VOH</sub> for output<br>high. CKOUT+ and<br>CKOUT– shorted<br>externally) |                      | V <sub>DD</sub> = 3.3 V                       | _                         | 32                    | _                     | mA              |  |  |

### Notes:

- 1. Current draw is independent of supply voltage

- 2. No under- or overshoot is allowed.

- 3. LVPECL outputs require nominal VDD ≥ 2.5 V.

- **4.** This is the amount of leakage that the 3-Level inputs can tolerate from an external driver. See Si53xx Family Reference Manual for more details.

- **5.** LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

**Table 1. DC Characteristics (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                       | Symbol           | <b>Test Condition</b>    | Min                       | Тур | Max                    | Unit |

|---------------------------------|------------------|--------------------------|---------------------------|-----|------------------------|------|

| 2-Level LVCMOS Inp              | ut Pins          |                          |                           |     |                        |      |

| Input Voltage Low               | V <sub>IL</sub>  | V <sub>DD</sub> = 1.71 V |                           | _   | 0.5                    | V    |

|                                 |                  | V <sub>DD</sub> = 2.25 V | _                         | _   | 0.7                    | V    |

|                                 |                  | V <sub>DD</sub> = 2.97 V | _                         | _   | 0.8                    | V    |

| Input Voltage High              | V <sub>IH</sub>  | V <sub>DD</sub> = 1.89 V | 1.4                       | _   | _                      | V    |

|                                 |                  | V <sub>DD</sub> = 2.25 V | 1.8                       | _   | _                      | V    |

|                                 | -                | V <sub>DD</sub> = 3.63 V | 2.5                       |     | _                      | V    |

| 3-Level Input Pins <sup>4</sup> | 1                |                          |                           |     |                        |      |

| Input Voltage Low               | V <sub>ILL</sub> |                          | _                         | _   | 0.15 x V <sub>DD</sub> | V    |

| Input Voltage Mid               | V <sub>IMM</sub> |                          | 0.45 x<br>V <sub>DD</sub> | _   | 0.55 x V <sub>DD</sub> | V    |

| Input Voltage High              | V <sub>IHH</sub> |                          | 0.85 x<br>V <sub>DD</sub> | _   | _                      | V    |

| Input Low Current               | I <sub>ILL</sub> | See Note 4               | -20                       | _   | _                      | μΑ   |

| Input Mid Current               | I <sub>IMM</sub> | See Note 4               | -2                        | _   | +2                     | μA   |

| Input High Current              | I <sub>IHH</sub> | See Note 4               | _                         | _   | 20                     | μΑ   |

### Notes:

- 1. Current draw is independent of supply voltage

- 2. No under- or overshoot is allowed.

- 3. LVPECL outputs require nominal VDD ≥ 2.5 V.

- **4.** This is the amount of leakage that the 3-Level inputs can tolerate from an external driver. See Si53xx Family Reference Manual for more details.

- 5. LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

**Table 1. DC Characteristics (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                   | Symbol          | Test Condition                         | Min                   | Тур | Max | Unit |

|-----------------------------|-----------------|----------------------------------------|-----------------------|-----|-----|------|

| LVCMOS Output Pins          |                 |                                        |                       |     |     |      |

| Output Voltage Low          | V <sub>OL</sub> | IO = 2 mA<br>V <sub>DD</sub> = 1.71 V  | _                     | _   | 0.4 | V    |

| Output Voltage Low          |                 | IO = 2 mA<br>V <sub>DD</sub> = 2.97 V  | _                     | _   | 0.4 | V    |

| Output Voltage High         | V <sub>OH</sub> | IO = -2 mA<br>V <sub>DD</sub> = 1.71 V | V <sub>DD</sub> – 0.4 | _   | _   | V    |

| Output Voltage High         |                 | IO = -2 mA<br>V <sub>DD</sub> = 2.97 V | V <sub>DD</sub> – 0.4 | _   | _   | V    |

| Disabled Leakage<br>Current | I <sub>OZ</sub> | RSTb = 0                               | -100                  | _   | 100 | μА   |

#### Notes:

- 1. Current draw is independent of supply voltage

- 2. No under- or overshoot is allowed.

- 3. LVPECL outputs require nominal VDD ≥ 2.5 V.

- 4. This is the amount of leakage that the 3-Level inputs can tolerate from an external driver. See Si53xx Family Reference Manual for more details.

- **5.** LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

Figure 1. Differential Voltage Characteristics

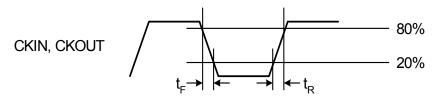

Figure 2. Rise/Fall Time Characteristics

**Table 2. AC Specifications**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                                | Symbol             | Test Condition                                                                              | Min   | Тур | Max    | Unit |

|--------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------|-------|-----|--------|------|

| CKINn Input Pins                                                         |                    |                                                                                             |       |     |        |      |

| Input Frequency                                                          | CKN <sub>F</sub>   |                                                                                             | 19.44 | _   | 707.35 | MHz  |

| Input Duty Cycle<br>(Minimum Pulse<br>Width)                             | CKN <sub>DC</sub>  | Whichever is smaller (i.e., the 40% / 60% limitation applies only to high frequency clocks) | 40    | _   | 60     | %    |

|                                                                          |                    |                                                                                             | 2     | _   | _      | ns   |

| Input Capacitance                                                        | CKN <sub>CIN</sub> |                                                                                             | _     | _   | 3      | pF   |

| Input Rise/Fall Time                                                     | CKN <sub>TRF</sub> | 20–80%<br>See Figure 2                                                                      | -     | _   | 11     | ns   |

| CKOUTn Output Pins                                                       |                    |                                                                                             |       |     |        |      |

| (See ordering section for                                                | or speed grade     | e vs frequency limits)                                                                      |       |     |        |      |

| Output Frequency<br>(Output not config-<br>ured for CMOS or<br>Disabled) | CKO <sub>F</sub>   |                                                                                             | 19.44 | _   | 1050   | MHz  |

| Maximum Output<br>Frequency in CMOS<br>Format                            | CKO <sub>F</sub>   |                                                                                             |       | _   | 212.5  | MHz  |

| Output Rise/Fall<br>(20–80 %) @<br>622.08 MHz output                     | CKO <sub>TRF</sub> | Output not configured for CMOS or Disabled See Figure 2                                     | _     | 230 | 350    | ps   |

| Output Rise/Fall<br>(20–80%) @<br>212.5 MHz output                       | CKO <sub>TRF</sub> | CMOS Output $V_{DD} = 1.71$ $C_{LOAD} = 5 \text{ pF}$                                       | _     | _   | 8      | ns   |

| Output Rise/Fall<br>(20–80%) @<br>212.5 MHz output                       | CKO <sub>TRF</sub> | CMOS Output $V_{DD} = 2.97$ $C_{LOAD} = 5 \text{ pF}$                                       | _     | _   | 2      | ns   |

| Output Duty Cycle<br>Uncertainty @<br>622.08 MHz                         | CKO <sub>DC</sub>  | 100 Ω Load<br>Line-to-Line<br>Measured at 50% Point<br>(Not for CMOS)                       | _     | _   | +/-40  | ps   |

Table 2. AC Specifications (Continued)  $(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, \text{ T}_{A} = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                                    | Symbol              | Test Condition                                 | Min     | Тур  | Max | Unit     |

|----------------------------------------------|---------------------|------------------------------------------------|---------|------|-----|----------|

| LVCMOS Input Pins                            |                     |                                                |         |      |     |          |

| Minimum Reset Pulse<br>Width                 | t <sub>RSTMN</sub>  |                                                | 1       |      |     | μs       |

| Input Capacitance                            | C <sub>in</sub>     |                                                | _       | _    | 3   | pF       |

| LVCMOS Output Pins                           |                     |                                                |         |      |     |          |

| Rise/Fall Times                              | t <sub>RF</sub>     | C <sub>LOAD</sub> = 20pf<br>See Figure 2       | _       | 25   | _   | ns       |

| LOSn Trigger Window                          | LOS <sub>TRIG</sub> | From last CKINn ↑ to<br>LOS↑                   | _       | _    | 750 | μs       |

| Device Skew                                  |                     |                                                |         |      |     |          |

| Output Clock Skew                            | t <sub>SKEW</sub>   | ↑ of CKOUTn to ↑ of CKOUT_m, C                 | _       | _    | 100 | ps       |

| Phase Change due to<br>Temperature Variation | t <sub>TEMP</sub>   | Max phase changes from<br>-40 to +85 °C        | _       | 300  | 500 | ps       |

| PLL Performance<br>(fin=fout = 622.08 MHz    | z; BW=120 Hz        | ;; LVPECL)                                     |         |      |     |          |

| Closed Loop Jitter<br>Peaking                | $J_{PK}$            |                                                | _       | 0.05 | 0.1 | dB       |

| Jitter Tolerance                             | $J_{TOL}$           | Jitter Frequency ≥ Loop<br>Bandwidth           | 5000/BW | _    | _   | ns pk-pk |

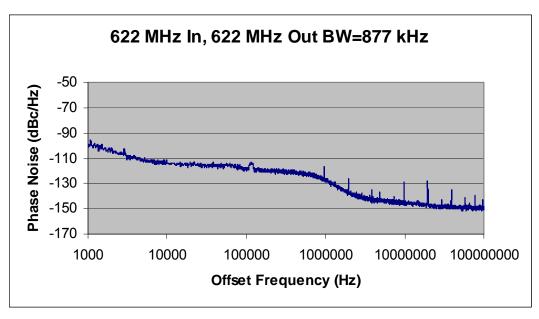

| Phase Noise<br>fout = 622.08 MHz             |                     | 1 kHz Offset                                   | _       | -90  | _   | dBc/Hz   |

| 10dt - 022.00 Wii i2                         | 21/2                | 10 kHz Offset                                  | _       | -113 | _   | dBc/Hz   |

|                                              | CKO <sub>PN</sub>   | 100 kHz Offset                                 | _       | -118 | _   | dBc/Hz   |

|                                              |                     | 1 MHz Offset                                   | _       | -132 | _   | dBc/Hz   |

| Spurious Noise                               | SP <sub>SPUR</sub>  | Max spur @ n x f3<br>(n ≥ 1, n x f3 < 100 MHz) | _       | -93  | -70 | dBc      |

**Table 3. Jitter Generation**

| Parameter            | Symbol | Test Condition*    |                          | Min | Тур | Max | Unit              |

|----------------------|--------|--------------------|--------------------------|-----|-----|-----|-------------------|

|                      |        | Measurement Filter | DSPLL<br>BW <sup>2</sup> |     |     |     |                   |

| Jitter Gen<br>OC-192 | JGEN   | 4–80 MHz           | 120 Hz                   | _   | .23 | _   | ps <sub>rms</sub> |

|                      |        | 0.05–80 MHz        | 120 Hz                   | _   | .47 | _   | ps <sub>rms</sub> |

| Jitter Gen<br>OC-48  | JGEN   | 0.12–20 MHz        | 120 Hz                   | _   | .48 | _   | ps <sub>rms</sub> |

\*Note: Test conditions:

1. fIN = fOUT = 622.08 MHz

2. Clock input: LVPECL

3. Clock output: LVPECL4. PLL bandwidth: 877 kHz

5.  $V_{DD} = 3.3 \text{ V}$

6.  $T_A = 85 \,^{\circ}C$

### **Table 4. Thermal Characteristics**

(V<sub>DD</sub> = 1.8 ±5%, 2.5 ±10%, or 3.3 V ±10%,  $T_A$  = –40 to 85 °C)

| Parameter                              | Symbol        | Test Condition | Value | Unit |

|----------------------------------------|---------------|----------------|-------|------|

| Thermal Resistance Junction to Ambient | $\theta_{JA}$ | Still Air      | 40    | C°/W |

**Table 5. Absolute Maximum Limits**

| Parameter                                                       | Symbol             | Value                           | Unit |  |

|-----------------------------------------------------------------|--------------------|---------------------------------|------|--|

| DC Supply Voltage                                               | $V_{DD}$           | -0.5 to 3.8                     | V    |  |

| LVCMOS Input Voltage                                            | V <sub>DIG</sub>   | -0.3 to (V <sub>DD</sub> + 0.3) | V    |  |

| CKINn Voltage Level Limits                                      | CKN <sub>VIN</sub> | 0 to V <sub>DD</sub>            | V    |  |

| XA/XB Voltage Level Limits                                      | XA <sub>VIN</sub>  | 0 to 1.2                        | V    |  |

| Operating Junction Temperature                                  | T <sub>JCT</sub>   | -55 to 150                      | С    |  |

| Storage Temperature Range                                       | T <sub>STG</sub>   | -55 to 150                      | С    |  |

| ESD HBM Tolerance (100 pF, 1.5 kΩ); All pins except CKIN+/CKIN– |                    | 2                               | kV   |  |

| ESD MM Tolerance; All pins except CKIN+/CKIN-                   |                    | 150                             | V    |  |

| ESD HBM Tolerance (100 pF, 1.5 kΩ); CKIN+/CKIN–                 |                    | 700                             | V    |  |

| ESD MM Tolerance; CKIN+/CKIN-                                   |                    | 100                             | V    |  |

| Latch-Up Tolerance                                              |                    | JESD78 Compliant                |      |  |

**Note:** Permanent device damage may occur if the Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operation sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

Figure 3. Typical Phase Noise Plot

| Jitter Bandwidth            | RMS Jitter (fs) |

|-----------------------------|-----------------|

| OC-48, 12 kHz to 20 MHz     | 374             |

| OC-192, 20 kHz to 80 MHz    | 388             |

| OC-192, 4 MHz to 80 MHz     | 181             |

| OC-192, 50 kHz to 80 MHz    | 377             |

| Broadband, 800 Hz to 80 MHz | 420             |

# 2. Typical Application Schematic

Notes: 1. Assumes differential LVPECL termination (3.3 V) on clock inputs.

- 2. Denotes tri-level input pins with states designated as L (ground), M ( $V_{DD}/2$ ), and H ( $V_{DD}$ ).

- 3. Assumes manual input clock selection.

Figure 4. Si5365 Typical Application Circuit

### 3. Functional Description

The Si5365 is a low jitter, precision clock multiplier for high-speed communication systems, including SONET OC-48/OC-192, SDH STM-16/STM-64, Ethernet, and Fibre Channel, in which the application requires clock multiplication without jitter attenuation. The Si5365 accepts four clock inputs ranging from 19.44 to 707 MHz and generates five frequency-multiplied clock outputs ranging from 19.44 to 1050 MHz. By default the four clock inputs are at the same frequency and the five clock outputs are at the same frequency. Two of the output clocks can be divided down further to generate an integer sub-multiple frequency. The input clock frequency and clock multiplication ratio are selectable from a table of popular SONET, Ethernet, and Fibre Channel frequencies. In addition to providing clock multiplication in SONET and datacom applications, the SONET-to-datacom Si5365 supports frequency translations. Silicon Laboratories offers a PC-based software utility, DSPLLsim, that can be used to look up valid Si5365 frequency translations. This utility can be downloaded from http://www.silabs.com/timing (click on Documentation).

The Si5365 is based on Silicon Laboratories' 3rd-generation DSPLL® technology, which provides any-frequency synthesis in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. The Si5365 PLL loop bandwidth is digitally programmable via the BWSEL[1:0] pins and supports a range from 150 kHz to 1.3 MHz. The DSPLL sim software utility can be used to calculate valid loop bandwidth settings for a given input clock frequency/clock multiplication ratio.

The Si5365 monitors all input clocks for loss-of-signal and provides a LOS alarm when it detects a missing clock.

In the case when the input clocks enter alarm conditions, the PLL will freeze the DCO output frequency near its last value to maintain operation with an internal state close to the last valid operating state.

The Si5365 has five differential clock outputs. The signal format of the clock outputs is programmable to support LVPECL, LVDS, CML, or CMOS loads. If not required, unused clock outputs can be powered down to minimize power consumption. For system-level debugging, a bypass mode is available which drives the output clock directly from the input clock, bypassing the internal DSPLL. The device is powered by a single 1.8, 2.5, or 3.3 V supply.

### 3.1. Further Documentation

Consult the Silicon Laboratories Any-Frequency Precision Clock Family Reference Manual (FRM) for detailed information about the Si5365. Additional design support is available from Silicon Laboratories through your distributor.

Silicon Laboratories has developed a PC-based software utility called DSPLLsim to simplify device configuration, including frequency planning and loop bandwidth selection. The FRM and this utility can be downloaded from <a href="http://www.silabs.com/timing">http://www.silabs.com/timing</a>; click on Documentation.

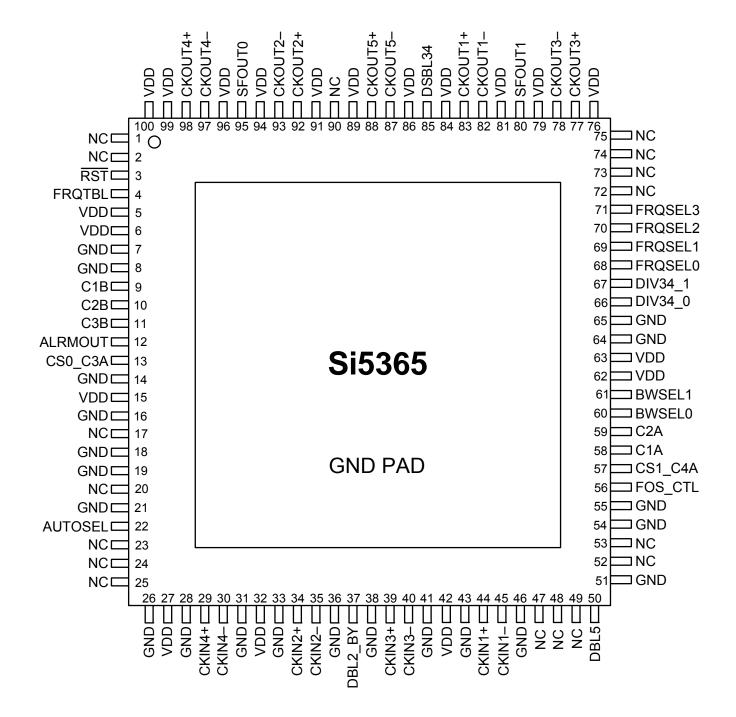

### 4. Pin Descriptions: Si5365

**Table 6. Si5365 Pin Descriptions**

| Pin#                                                                                                               | Pin Name        | I/O             | Signal Level | Description                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 17,<br>20, 23,<br>24, 25,<br>47, 48,<br>49, 52,<br>53, 72,<br>73, 74,<br>75, 90                              | NC              |                 |              | No Connect. These pins must be left unconnected for normal operation.                                                                                                                                                                                                                                                                                      |

| 3                                                                                                                  | RST             | I               | LVCMOS       | External Reset. Active low input that performs external hardware reset of device. Resets all internal logic to a known state and forces the device registers to their default value. Clock outputs are tristated during reset. After rising edge of RST signal, the device will perform an internal self-calibration. This pin has a weak pullup.          |

| 4                                                                                                                  | FRQTBL          | I               | 3-Level      | Frequency Table Select. This pin selects SONET/SDH, datacom, or SONET/SDH to datacom frequency translation table. L = SONET/SDH. M = Datacom. H = SONET/SDH to Datacom. This pin has a weak pullup and weak pulldown and defaults to M. Some designs may require an external resistor voltage divider when driven by an active device that will tri-state. |

| 5, 6, 15,<br>27, 32,<br>42, 62,<br>63, 76,<br>79, 81,<br>84, 86,<br>89, 91,<br>94, 96,<br>99, 100                  | V <sub>DD</sub> | V <sub>DD</sub> | Supply       | $V_{DD}$ . The device operates from a 1.8 or 2.5 V supply. Bypass capacitors should be associated with the following $V_{DD}$ pins: Pins Bypass Cap 5, 6 0.1 μF 15 0.1 μF 15 0.1 μF 162, 63 0.1 μF 162, 63 0.1 μF 163, 84 0.1 μF 164, 84 0.1 μF 165, 89 0.1 μF 166, 89 0.1 μF 166, 99, 100 0.1 μF 166, 99, 100 0.1 μF                                      |

| 7, 8, 14,<br>16, 18,<br>19, 21,<br>26, 28,<br>31, 33,<br>36, 38,<br>41, 43,<br>46, 51,<br>54, 55,<br>56, 64,<br>65 | GND             | GND             | Supply       | Ground. These pins must be connected to system ground. Minimize the ground path impedance for optimal performance.                                                                                                                                                                                                                                         |

Table 6. Si5365 Pin Descriptions (Continued)

| Pin#     | Pin Name           | I/O | Signal Level |                                                                                                                                                                                                                                                                                                                                                                                                                                               | Desc    | cription           |  |

|----------|--------------------|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--|

| 9        | C1B                | 0   | LVCMOS       | CKIN1 Invalid Indicator. This pin is an active high alarm output associated with CKIN1. Once triggered, the alarm will remain high until CKIN1 is validated.  0 = No alarm on CKIN1.  1 = Alarm on CKIN1.                                                                                                                                                                                                                                     |         |                    |  |

| 10       | C2B                | 0   | LVCMOS       | CKIN2 Invalid Indicator.  This pin is an active high alarm output associated with CKIN2. Once triggered, the alarm will remain high until CKIN2 is validated.  0 = No alarm on CKIN2.  1 = Alarm on CKIN2.                                                                                                                                                                                                                                    |         |                    |  |

| 11       | СЗВ                | 0   | LVCMOS       | CKIN3 Invalid Indicator.  This pin is an active high alarm output associated with CKIN3.  0 = No alarm on CKIN3.  1 = Alarm on CKIN3.                                                                                                                                                                                                                                                                                                         |         |                    |  |

| 12       | ALRMOUT            | 0   | LVCMOS       | Alarm Output Indicator. This pin is an active high alarm output associated with CKIN4 or the frame sync alignment alarm. 0 = ALRMOUT not active. 1 = ALRMOUT active.                                                                                                                                                                                                                                                                          |         |                    |  |

| 13<br>57 | CS0_C3A<br>CS1_C4A | I/O | LVCMOS       | Input Clock Select/CKINn Active Clock Indicator. Input: If manual clock selection mode is chosen (AUTOSEL = 1), the CS[1:0] pins function as the manual input clock selector control.                                                                                                                                                                                                                                                         |         |                    |  |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                               | CS[1:0] | Active Input Clock |  |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00      | CKIN1              |  |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 01      | CKIN2              |  |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10      | CKIN3              |  |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11      | CKIN4              |  |

|          |                    |     |              | These inputs are internally deglitched to prevent inadvertent clock switching during changes in the CSn input state. If configured as input, these pins must not float.  Output: If automatic clock detection is chosen (AUTOSEL = M or H), these pins function as the CKINn active clock indicator output. 0 = CKINn is not the active input clock.  1 = CKINn is currently the active input clock to the PLL. This pin has a weak pulldown. |         |                    |  |

| 22       | AUTOSEL            | I   | 3-Level      | Manual/Automatic Clock Selection. Three level input that selects the method of input clock selection to be used. L = Manual. M = Automatic non-revertive. H = Automatic revertive. This pin has a weak pullup and weak pulldown and defaults to M. Some designs may require an external resistor voltage divider when driven by an active device that will tri-state.                                                                         |         |                    |  |

| 29<br>30 | CKIN4+<br>CKIN4–   | I   | MULTI        | Clock Input 4.  Differential clock input. This input can also be driven with a single-ended signal.                                                                                                                                                                                                                                                                                                                                           |         |                    |  |

Table 6. Si5365 Pin Descriptions (Continued)

| Pin#     | Pin Name         | I/O | Signal Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------------------|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34<br>35 | CKIN2+<br>CKIN2- | I   | MULTI        | Clock Input 2. Differential input clock. This input can also be driven with a single-ended signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 37       | DBL2_BY          | _   | 3-Level      | CKOUT2 Disable/PLL Bypass Mode Control.  Controls enable of CKOUT2 divider/output buffer path and PLL bypass mode.  L = CKOUT2 Enabled.  M = CKOUT2 Disabled.  H = BYPASS Mode with CKOUT2 enabled. Bypass is not available with CMOS outputs.  This pin has a weak pullup and weak pulldown and defaults to M.  Some designs may require an external resistor voltage divider when driven by an active device that will tri-state.                                                                                                                                                                                                               |

| 39<br>40 | CKIN3+<br>CKIN3– | Ι   | MULTI        | Clock Input 3. Differential clock input. This input can also be driven with a single-ended signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 44<br>45 | CKIN1+<br>CKIN1- | Ι   | MULTI        | Clock Input 1.  Differential clock input. This input can also be driven with a single-ended signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 50       | DBL5             | l   | 3-Level      | CKOUT5 Disable. This pin performs the following functions: L = Normal operation. Output path is active and signal format is determined by SFOUT inputs. M = CMOS signal format. Overrides SFOUT signal format to allow CKOUT5 to operate in CMOS format while the clock outputs operate in a differential output format. H = Powerdown. Entire CKOUT5 divider and output buffer path is powered down. CKOUT5 output will be in tristate mode during powerdown. This pin has a weak pullup and weak pulldown and defaults to M. Some designs may require an external resistor voltage divider when driven by an active device that will tri-state. |

| 56       | FOS_CTL          |     | 3-Level      | Frequency Offset Control.  This pin enables or disables use of the CKIN2 FOS reference as an input to the clock selection state machine.  L = FOS Disabled.  M = Stratum 3/3E FOS Threshold.  H = SONET Minimum Clock FOS Threshold.  This pin has both weak pullups and weak pulldowns and defaults to M. Some designs may require an external resistor voltage divider when driven by an active device that will tri-state.                                                                                                                                                                                                                     |

| 58       | C1A              | 0   | LVCMOS       | CKIN1 Active Clock Indicator.  This pin serves as the CKIN1 active clock indicator.  0 = CKIN1 is not the active input clock.  1 = CKIN1 is currently the active input clock to the PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 59       | C2A              | 0   | LVCMOS       | CKIN2 Active Clock Indicator.  This pin serves as the CKIN2 active clock indicator.  0 = CKIN2 is not the active input clock.  1 = CKIN2 is currently the active input clock to the PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 6. Si5365 Pin Descriptions (Continued)

| Pin#                 | Pin Name                                 | I/O | Signal Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|------------------------------------------|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60<br>61             | BWSEL0<br>BWSEL1                         | I   | 3-Level      | Bandwidth Select. These pins are three level inputs that select the DSPLL closed loop bandwidth according to the Any-Frequency Precision Clock Family Reference Manual. These pins have both weak pullups and weak pulldowns and default to M. Some designs may require an external resistor voltage divider when driven by an active device that will tri-state.                                                                                                      |

| 66<br>67             | DIV34_0<br>DIV34_1                       | I   | 3-Level      | CKOUT3 and CKOUT4 Divider Control.  These pins control the division of CKOUT3 and CKOUT4 relative to the CKOUT2 output frequency. Detailed operations and timing characteristics for these pins may be found in the Any-Frequency Precision Clock Family Reference Manual.  These pins have both weak pullups and weak pulldowns and default to M.  Some designs may require an external resistor voltage divider when driven by an active device that will tri-state. |

| 68<br>69<br>70<br>71 | FRQSEL0<br>FRQSEL1<br>FRQSEL2<br>FRQSEL3 | I   | 3-Level      | Multiplier Select. These pins are three level inputs that select the input clock and clock multiplication setting according to the Any-Frequency Precision Clock Family Reference Manual, depending on the FRQTBL setting. These pins have both weak pullups and weak pulldowns and default to M. Some designs may require an external resistor voltage divider when driven by an active device that will tri-state.                                                   |

| 77<br>78             | CKOUT3+<br>CKOUT3-                       | 0   | MULTI        | Clock Output 3.  Differential output clock with a frequency specified by FRQSEL and FRQTBL settings. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs.                                                                                                                                                                                                                  |

Table 6. Si5365 Pin Descriptions (Continued)

| Pin#     | Pin Name           | I/O | Signal Level |                                                                                                                                                                                                                                                                                                 | Des                                                                              | cription                                                                                                                                             |                                           |

|----------|--------------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 80<br>95 | SFOUT1<br>SFOUT0   | I   | 3-Level      | Signal Format Select. Three level inputs that select the output signal format (common mode voltage and differential swing) for all of the clock outputs except CKOUT5 (see DBL5).                                                                                                               |                                                                                  |                                                                                                                                                      |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | SFOUT[1:0]                                                                       | Signal Format                                                                                                                                        |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | HH                                                                               | Reserved                                                                                                                                             |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | НМ                                                                               | LVDS                                                                                                                                                 |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | HL                                                                               | CML                                                                                                                                                  |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | MH                                                                               | LVPECL                                                                                                                                               |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | MM                                                                               | Reserved                                                                                                                                             |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | ML                                                                               | LVDS—Low Swing                                                                                                                                       |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | LH                                                                               | CMOS                                                                                                                                                 |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | LM                                                                               | Disable                                                                                                                                              |                                           |

|          |                    |     |              |                                                                                                                                                                                                                                                                                                 | LL                                                                               | Reserved                                                                                                                                             |                                           |

|          |                    |     |              | for thermal reason and CMOS output These pins have M.                                                                                                                                                                                                                                           | ons, there are res<br>uts. See the Si53<br>both weak pullup<br>ay require an ext | CMOS outputs. When V<br>trictions on the number o<br>xx-RM reference manual<br>os and weak pulldowns a<br>ernal resistor voltage div<br>I tri-state. | f LVPECL<br>for details.<br>nd default to |

| 82<br>83 | CKOUT1-<br>CKOUT1+ | 0   | MULTI        | Clock Output 1.  Differential output clock with a frequency specified by FRQSEL and FRQTBL. Output signal format is selected by SFOUT pins. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs.    |                                                                                  |                                                                                                                                                      |                                           |

| 85       | DBL34              | I   | LVCMOS       | Output 3 and 4 Disable. Active high input. When active, entire CKOUT3 and CKOUT4 divider and output buffer path is powered down. CKOUT3 and CKOUT4 outputs will be in tristate mode during powerdown. This pin has a weak pullup.                                                               |                                                                                  |                                                                                                                                                      |                                           |

| 87<br>88 | CKOUT5-<br>CKOUT5+ | 0   | MULTI        | Clock Output 5. Fifth high-speed clock output with a frequency specified by FRQSEL and FRQTBL. Output signal format is selected by SFOUT pins. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs. |                                                                                  |                                                                                                                                                      |                                           |

| 92<br>93 | CKOUT2+<br>CKOUT2- | 0   | MULTI        | Clock Output 2.  Differential output clock with a frequency specified by FRQSEL and FRQTBL. Output signal format is selected by SFOUT pins. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs.    |                                                                                  |                                                                                                                                                      |                                           |

Table 6. Si5365 Pin Descriptions (Continued)

| Pin #      | Pin Name           | I/O | Signal Level | Description                                                                                                                                                                                                                                                                                           |

|------------|--------------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 97<br>98   | CKOUT4-<br>CKOUT4+ | 0   | MULTI        | Clock Output 4.  Differential output clock with a frequency specified by FRQSEL and FRQTBL settings. Output signal format is selected by SFOUT pins. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs. |

| GND<br>PAD | GND PAD            | GND | Supply       | Ground Pad. The ground pad must provide a low thermal and electrical impedance to a ground plane.                                                                                                                                                                                                     |

# 5. Ordering Guide

| Ordering Part Number                                                             | Package                 | ROHS6, Pb-Free | Temperature Range |  |  |

|----------------------------------------------------------------------------------|-------------------------|----------------|-------------------|--|--|

| Si5365-C-GQ*                                                                     | 100-Pin 14 x 14 mm TQFP | Yes            | –40 to 85 °C      |  |  |

| *Note: Not recommended for new designs. For alternatives, see the Si533x family. |                         |                |                   |  |  |

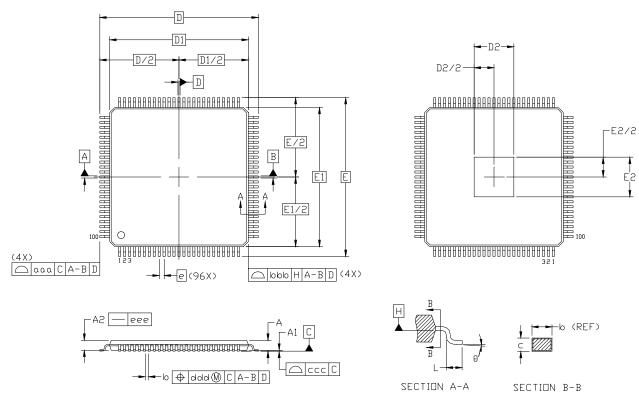

### 6. Package Outline: 100-Pin TQFP

Figure 5 illustrates the package details for the Si5365. Table 7 lists the values for the dimensions shown in the illustration.

Figure 5. 100-Pin Thin Quad Flat Package (TQFP)

Table 7. 100-Pin Package Diagram Dimensions

| Dimension | Min        | Nom  | Max  |

|-----------|------------|------|------|

| Α         |            | _    | 1.20 |

| A1        | 0.05       | _    | 0.15 |

| A2        | 0.95       | 1.00 | 1.05 |

| b         | 0.17       | 0.22 | 0.27 |

| С         | 0.09       | _    | 0.20 |

| D         |            |      |      |

| D1        | 14.00 BSC. |      |      |

| D2        | 3.85       | 4.00 | 4.15 |

| е         | 0.50 BSC.  |      |      |

| Dimension | Min        | Nom  | Max  |  |  |

|-----------|------------|------|------|--|--|

| Е         | 16.00 BSC. |      |      |  |  |

| E1        | 14.00 BSC. |      |      |  |  |

| E2        | 3.85       | 4.00 | 4.15 |  |  |

| L         | 0.45       | 0.60 | 0.75 |  |  |

| aaa       | _          | _    | 0.20 |  |  |

| bbb       | _          | _    | 0.20 |  |  |

| ccc       | _          | _    | 0.08 |  |  |

| ddd       | _          | _    | 0.08 |  |  |

| Θ         | 0°         | 3.5° | 7°   |  |  |

### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This package outline conforms to JEDEC MS-026, variant AED-HD.

- Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

SHIPPN LABO

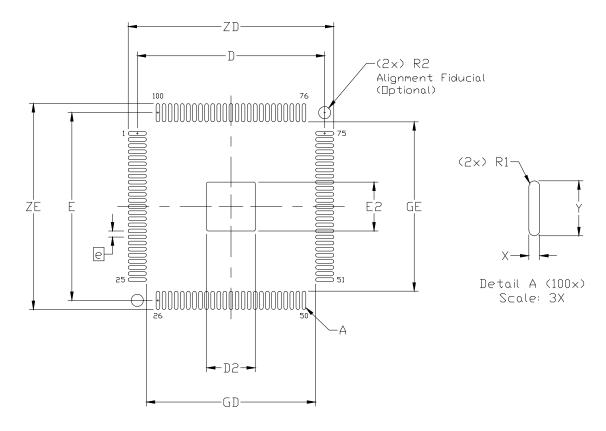

## 7. PCB Land Pattern

Figure 6. PCB Land Pattern Diagram

**Table 8. PCB Land Pattern Dimensions**

| MIN                | MAX                                |  |

|--------------------|------------------------------------|--|

| 0.50 BSC.          |                                    |  |

| 15.40 REF.         |                                    |  |

| 15.40 REF.         |                                    |  |

| 3.90               | 4.10                               |  |

| 3.90               | 4.10                               |  |

| 13.90              | _                                  |  |

| 13.90              | _                                  |  |

| <del>-</del>       | 0.30                               |  |

| 1.50 F             | REF.                               |  |

| <del>-</del>       | 16.90                              |  |

| <del>-</del> 16.90 |                                    |  |

| 0.15 I             | REF                                |  |

| _                  | 1.00                               |  |

|                    | 0.50 E 15.40 15.40 3.90 3.90 13.90 |  |

#### Notes:

### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-7351 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

### Solder Mask Design

**5.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

#### Stencil Design

- **6.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 7. The stencil thickness should be 0.125 mm (5 mils).

- **8.** The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

- **9.** A 4 x 4 array of 0.80 mm square openings on 1.05 mm pitch should be used for the center ground pad.

### **Card Assembly**

- 10. A No-Clean, Type-3 solder paste is recommended.

- **11.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

# 8. Top Marking

# 8.1. Si5365 Top Marking

# 8.2. Top Marking Explanation

| Mark Method:    | Laser                                        |                                                                                           |

|-----------------|----------------------------------------------|-------------------------------------------------------------------------------------------|

| Logo Size:      | 9.2 x 3.1 mm<br>Center-Justified             |                                                                                           |

| Font Size:      | 3.0 Point (1.07 mm)<br>Right-Justified       |                                                                                           |

| Line 1 Marking: | Device Part Number<br>Si5365x-C-GQ           | X = Speed Grade<br>See "5. Ordering Guide" on page 21.                                    |

| Line 2 Marking: | YY = Year<br>WW = Workweek                   | Assigned by the Assembly Supplier. Corresponds to the year and workweek of the mold date. |

|                 | R = Die Revision                             |                                                                                           |

|                 | TTTTT = Mfg Code                             | Manufacturing Code                                                                        |

| Line 3 Marking: | Circle = 1.8 mm Diameter<br>Center-Justified | "e3" Pb-Free Symbol                                                                       |

|                 | Country of Origin ISO Code Abbreviation      |                                                                                           |

### **DOCUMENT CHANGE LIST**

### Revision 0.32 to Revision 0.33

Condensed format.

### Revision 0.33 to Revision 0.34

- Removed references to latency control, INC, and DEC pins.

- Updated Table 1, "Performance Specifications," on page 2.

- Changed LVTTL to LVCMOS in Table 2, "Absolute Maximum Ratings," on page 3.

- Added Figure 1, "Typical Phase Noise Plot," on page 4.

- Updated Figure 4, "Si5365 Typical Application Circuit".

- Updated "4. Pin Descriptions: Si5365".

- Updated "5. Ordering Guide" on page 21.

- Added "7. PCB Land Pattern".

### Revision 0.34 to Revision 0.4

- Changed 1.8 V operating range to ±5%.

- Updated Table 1 on page 2.

- Updated Table 2 on page 3.

- Added page 4.

- Updated "3. Functional Description" on page 13.

- Clarified "4. Pin Descriptions: Si5365" on page 14 including the addition of FOS CTL (pin 56).

### Revision 0.4 to Revision 0.5

- Changed "rate" to "frequency" throughout.

- Added Table of Contents.

- Reordered and expanded spec tables.

- Added 3.3 V operation.

- Added "8. Top Marking" on page 25.

- Added no bypass with CMOS outputs.

- Updated Table 2, "AC Specifications," on page 8.

- Updated Table 3, "Jitter Generation," on page 10.

- Updated "5. Ordering Guide" on page 21.

### Revision 0.5 to Revision 1.0

- Updated logo.

- Transitioned to full production.

Notes:

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are not designed or authorized for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, Silabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA