TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# TC9223P,TC9223F

# PLL Frequency Synthesizer LSI for Communication Use

TC9223P, TC9223F are developed as PLL frequency synthesizer LSI for communication use and has the following features.

### **Features**

- Can be used as PLL LSI in many communication equipment, e.g., personal radio, mobile radio telephone, CB radio and so on because of its system design for wide applications.

- With a built-in 14 bit reference frequency divider, capable of frequency division ranging from 5 to 16,383 divisions.

- Built-in 7 bit and 11 bit programmable dividers of pulse swallow type.

- Provided with 2 systems of phase comparator outputs.

- Provided with one general purpose output port.

- PSC (prescaler control) output can be switched according to input signal rising or falling timing by program.

- DIP16 pin and SOP16 pin packages.

# **Pin Assignment**

Weight DIP16-P-300-2.54A: 1.00 g (typ.) SOP16-P-300-1.27: 0.16 g (typ.)

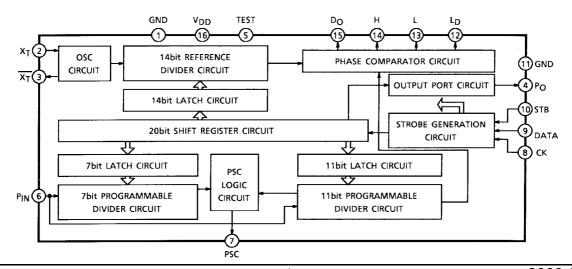

# **Block Diagram**

# **Pin Function**

| Pin No.      | Symbol            | Pin Name                            | Function and Operation                                                                                                                | Remarks                          |  |

|--------------|-------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|

| 1            | GND               | Ground-1                            | Logic ground terminal.                                                                                                                | _                                |  |

| 2            | $\frac{X_T}{X_T}$ | Crystal oscillator terminal         | Reference frequency crystal oscillator input and output.                                                                              | Feedback resistor built in       |  |

| 4            | PO                | General purpose output port         | General purpose output port externally controllable by serial data.                                                                   | CMOS output                      |  |

| 5            | TEST              | Test terminal                       | Used normally at "L" level or Open state.  Test mode operation at "H" level.                                                          | Pull-down resistor built in      |  |

| 6            | P <sub>IN</sub>   | Programmable counter input          | Programmable counter input terminal.  Input an external prescaler output through a coupling capacitor.                                | Built in amps                    |  |

| 7            | PSC               | Prescaler control                   | 2 modulus prescaler frequency division control signal output. "H" level: P, "L" level: P + 1                                          | CMOS output                      |  |

| 8<br>9<br>10 | CK<br>DATA<br>STB | Serial data input                   | Serial data input terminals to control this LSI externally. Schmitt trigger input.                                                    | Built in schmitt trigger circuit |  |

| 11           | GND               | Ground-2                            | Ground terminal of phase comparator charge pump.                                                                                      | _                                |  |

| 12           | L <sub>D</sub>    | Lock detector                       | Outputs "H" level pulse when phase difference is detected by the phase comparator.  Can be set compulsorily by data given externally. | CMOS output                      |  |

| 13           | L                 | Phase comparator                    | Phase comparator output terminals to connect external                                                                                 | CMOS output                      |  |

| 14           | Н                 | output                              | high voltage charge pump.                                                                                                             | N-ch open drain output           |  |

| 15           | D <sub>O</sub>    | Phase comparator charge pump output | D <sub>O</sub> is tri-state output.                                                                                                   | _                                |  |

| 16           | $V_{DD}$          | Power supply                        | +5 V power supply terminal.                                                                                                           | _                                |  |

## Operation

### 1. Serial Data Input

Serial data can control 4 group functions separately. Data is always input from.

LSB and final 2 bits data selects the group.

- Group 1 Reference divider frequency division ratio

- Group 2 Programmable counter frequency division ratio

- Group 3 PSC control

- Phase comparator S, R inputs replace

- Group 4 General purpose output ports

Lock detector compulsory set

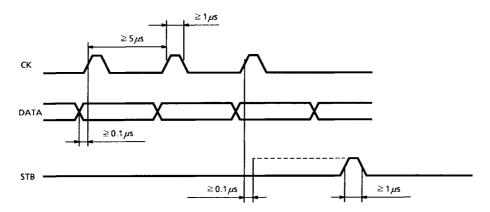

The serial data input circuit is composed of 3 lines of DATA, CK and STB. Data is taken in order into the internal shift register at the leading edge of CK.

By setting STB at "H" level after all data are input, data are transferred to the latch selected by the group code and this LSI is controlled.

Each of 3 serial data input terminals has a built-in Schmitt trigger circuit that prevent data error by

For details of data construction of each group, refer to the explanations of respective blocks.

#### • Serial data transfer timing

Note 1: Set a time from the last CK rising to STB rising at 0.1  $\mu$ s or above.

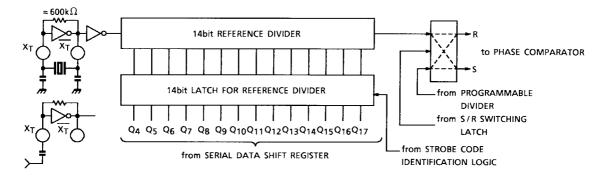

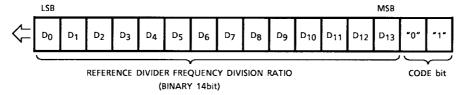

#### 2. Reference Divider

This block generates PLL reference frequency and is composed of an amplifier for a crystal oscillator and 14 bit programmable divider.

• The programmable divider is composed of binary 14 bits and is capable frequency division from 5 to 16,383 divisions by serial data given externally.

3

Therefore, a crystal needed to generate reference frequency is freely selectable and common use of the crystal for other purpose is also possible.

• Serial data to control reference divider block is of 16 bits as following construction.

Note 2: D<sub>0</sub>~D<sub>13</sub> is binary code N of frequency division ratio intended.

$$5 \le N \le 16,383$$

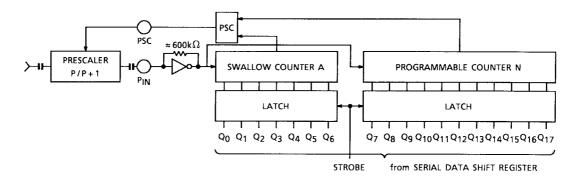

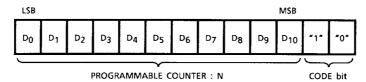

## 3. Programmable Counter

Programmable counter circuit adopts swallow system to generate high frequency and is composed of 7 bits swallow counter, 11 bits programmable counter and prescaler control logic to switch frequency division ratio of 2 modulus prescaler connected externally.

• Total frequency division ratio is defined as below.

Frequency division ratio =

$$(P + 1) \cdot A + P \cdot (N - A)$$

=  $P \cdot N + A$

Note 3: N > A

• Frequency division ratio of the external perscaler should be "P + 1" when PSC is "L" level and "P" when PSC is "H" level.

## • Serial data

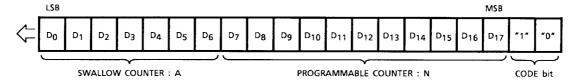

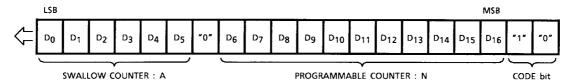

Serial data which defines frequency division ratio of programmable counter is composed of 20 bits but changes according to "P" of external prescaler.

(1) When used with an external prescaler of P = 128

Note 4: D<sub>0</sub>~D<sub>17</sub> is binary code D of frequency division ratio intended.

Generally  $16,384 \le D \le 262,143$

(2) When used with an external prescaler of P = 64

Note 5: D0~D16 is binary code D of frequency division ratio intended.

The 7th bit should be fixed at "L".

Generally  $4,096 \le D \le 131,071$

(3) When used as a normal programmable counter

Note 6:  $D_0 \sim D_{10}$  is binary code D of frequency division ratio intended.

$5 \le D \le 2,047$

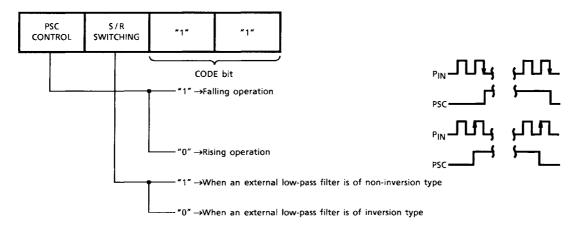

## 4. Inversion of S/R Input to PSC Control/Phase Comparator

• PSC control

"PSC" (prescaler) output is capable of switching operation according to rising or falling timing of "PIN" input signal.

• Inversion of S/R inputs to phase comparator

S/R switching bit is a control latch for mutual replacement of reference divider output and programmable divider output when they are led to the phase comparator.

• Serial data

5

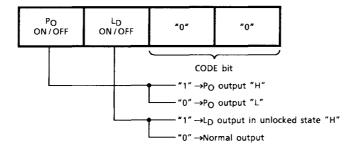

## 5. General Purpose Output Port/Lock Detector

#### • General purpose output port

"PO" output port is available for many functions, e.g., transmitter/receiver switching signal, band switching signal, sensitivity switching and frequency band switching according to serial data.

#### • Lock detector

The lock detector output pulse signal for a phase difference time detected by the phase detector circuit.

In addition, this lock detector output can be fixed in the unlocked state by force by serial data given externally.

By fixing the lock detector in the unlocked state immediately before channel changing to stop transmission output and releasing the detector from the unlocked state at a definite time after the channel change, troubles at channel changing, e.g., by overshoot can be prevented.

#### Serial data

# Maximum Ratings (Ta = 25°C)

| Characteristics       | Symbol           | Rating                     | Unit |

|-----------------------|------------------|----------------------------|------|

| Supply voltage        | $V_{DD}$         | -0.3~7.0                   | V    |

| Input voltage         | V <sub>IN</sub>  | -0.3~V <sub>DD</sub> + 0.3 | V    |

| Power dissipation     | P <sub>D</sub>   | 300                        | mW   |

| Operating temperature | T <sub>opr</sub> | <b>−40~85</b>              | °C   |

| Storage temperature   | T <sub>stg</sub> | -65~150                    | °C   |

# Electrical Characteristics (unless otherwise specified, Ta = 25°C, $V_{DD} = 5$ V)

| Characteristics             |                         | Symbol             | Test<br>Circuit | Test Condition                                                                                                                                                                            |                       | Min  | Тур. | Max      | Unit               |

|-----------------------------|-------------------------|--------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|----------|--------------------|

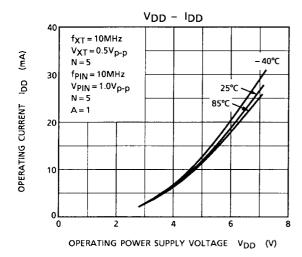

| Oerating supply voltage     |                         | V <sub>DD</sub>    | _               | $f_{XT} = 30 \text{ MHz}, 0.5 \text{ V}_{p-p}$<br>$f_{P \text{ IN}} = 30 \text{ MHz}, 1.0 \text{ V}_{p-p}$<br>(Note 7)                                                                    |                       | 4.5  | 5.0  | 5.5      | >                  |

| Operating supply current    |                         | I <sub>DD</sub>    | _               | $\begin{aligned} f_{XT} &= 30 \text{ MHz},  0.5  \text{V}_{\text{p-p}} \\ f_{\text{P IN}} &= 30 \text{ MHz},  1.0  \text{V}_{\text{p-p}} \\ &\qquad \qquad \text{(Note 7)} \end{aligned}$ |                       | _    | 15.0 | 20.0     | mA                 |

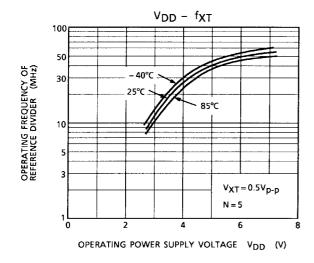

| Operating input frequency   |                         | f <sub>XT1</sub>   | _               | $V_{DD} = 4.5 \sim 5.5 \text{ V},$<br>$V_{IN} = 0.5 \text{ V}_{p-p}$ (Note 8)                                                                                                             |                       | 1.0  |      | 30.0     | - MHz              |

|                             |                         | f <sub>XT2</sub>   | _               | $V_{DD} = 3.0 \text{ V}, V_{IN} = 0.5 \text{ V}_{p-p}$ (Note 8)                                                                                                                           |                       | 1.0  | _    | 10.0     |                    |

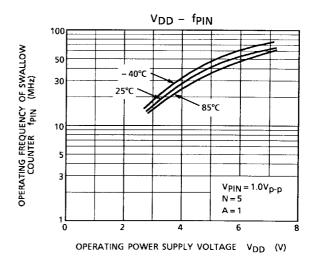

|                             |                         | f <sub>P IN1</sub> | _               | $V_{DD} = 4.5 \sim 5.5 \text{ V},$<br>$V_{IN} = 1.0 \text{ V}_{p-p}$ (Note 9)                                                                                                             |                       | 0.1  | _    | 30.0     |                    |

|                             |                         | f <sub>P IN2</sub> | _               | $V_{DD} = 3.0 \text{ V}, V_{IN} = 1.0 \text{ V}_{p-p}$ (Note 9)                                                                                                                           |                       | 0.1  | _    | 10.0     |                    |

| X'tal oscillation frequency |                         | fosc               | _               | V <sub>DD</sub> = 4.5~5.5 V (Note 11)                                                                                                                                                     |                       | 1.0  | _    | 30.0     | MHz                |

| 0 " ' ' ' '                 |                         | V <sub>XT</sub>    | _               | V <sub>DD</sub> = 4.5~5.5 V                                                                                                                                                               |                       | 0.5  | _    | $V_{DD}$ | - V <sub>p-p</sub> |

| Operating input v           | Operating input voltage |                    | _               | V <sub>DD</sub> = 4.5~5.5 V                                                                                                                                                               |                       | 1.0  | _    | $V_{DD}$ |                    |

| Input voltage               | "H" level               | V <sub>IH</sub>    | _               | CK DATA STD                                                                                                                                                                               |                       | 3.8  | _    | 5.0      | V                  |

|                             | "L" level               | V <sub>IL</sub>    | _               | CK, DATA, STB                                                                                                                                                                             |                       | 0.0  | _    | 1.2      |                    |

| Input current               | "H" level               | l <sub>IH</sub>    | _               | CK, DATA,                                                                                                                                                                                 | V <sub>IH</sub> = 5 V | _    |      | 1.0      | μА                 |

| input current               | "L" level               | I <sub>IL</sub>    | _               | STB                                                                                                                                                                                       | $V_{IL} = 0 V$        | -1.0 | _    | _        | μΛ                 |

| Breakdown voltage           |                         | V <sub>OH</sub>    | _               | I <sub>OH</sub> ≤ 0.1 μA                                                                                                                                                                  |                       | _    |      | 12.0     | <b>V</b>           |

| Tri-state off-leak current  |                         | I <sub>OZ</sub>    | _               | $D_O \qquad V_{OH} = 5 \text{ V}, V_{OL} = 5 \text{ V}$                                                                                                                                   |                       | -0.1 | _    | 0.1      | μΑ                 |

|                             | "H" level               | I <sub>OH1</sub>   | _               | D <sub>O</sub> , L                                                                                                                                                                        | V <sub>OH</sub> = 4 V | _    | -1.0 | -0.5     |                    |

| Output current              | "L" level               | I <sub>OL1</sub>   | _               | D <sub>O</sub> , H, L                                                                                                                                                                     | V <sub>OL</sub> = 1 V | 0.5  | 1.0  | _        | mA                 |

| Output current              | "H" level               | I <sub>OH2</sub>   | _               | $L_D$ , PSC, $P_O$ $V_{OH} = 4 V$ $L_D$ , PSC, $P_O$ $V_{OL} = 1 V$                                                                                                                       |                       | _    | -1.5 | -1.0     | ША                 |

|                             | "L" level               | I <sub>OL2</sub>   | _               |                                                                                                                                                                                           |                       | 1.0  | 1.5  | _        |                    |

| Input frequency             |                         | f <sub>CK</sub>    | _               | СК                                                                                                                                                                                        |                       | _    |      | 200      | kHz                |

Note 7:  $Ta = -40 \sim 85^{\circ}C$

Note 8:  $X_T$  is SIN wave input.

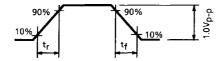

Note 9: P<sub>IN</sub> is SQ wave input. Rising and falling slopes of input waveform are specified as follows.

Note 10:  $t_{\Gamma} = t_f < 200 \text{ ns}$

Note 11: Use a crystal oscillator that has a low CI value and a good starting characteristic.

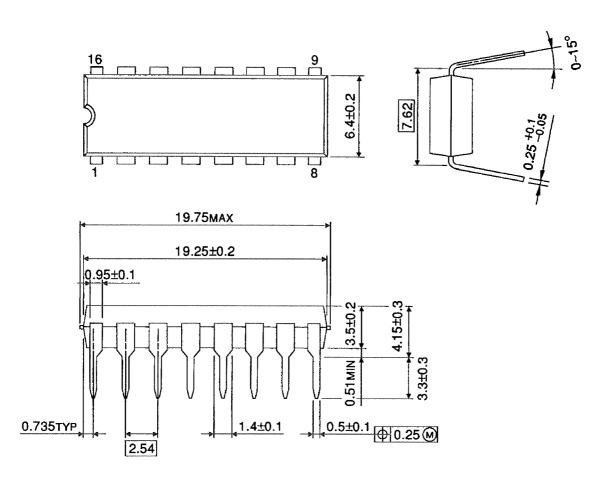

# **Package Dimensions**

DIP16-P-300-2.54A Unit: mm

Weight: 1.00 g (typ.)

# **Package Dimensions**

SOP16-P-300-1.27

Unit:mm

16

9

0.705TYP

10.8MAX

10.3±0.2

10.8MAX

10.3±0.2

10.8MAX

Weight: 0.16 g (typ.)

ZZ 0.1

0.8±0.2

## **RESTRICTIONS ON PRODUCT USE**

Handbook" etc..

030619EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.