## **INTEGRATED CIRCUITS**

# DATA SHEET

## PCK2002P 533 MHz PCI-X clock buffer

Product data Supersedes data of 2001 May 09 2002 Dec 13

## 533 MHz PCI-X clock buffer

## **PCK2002P**

#### **FEATURES**

- General purpose and PCI-X 1:4 clock buffer

- 8-pin TSSOP package

- See PCK2001 for 48-pin 1:18 buffer part

- See PCK2001M for 28-pin 1:10 buffer part

- See PCK2001R for 16-pin 1:6 buffer part

- Operating frequency: 0 533 MHz

- Part-to-part skew < 500 ps

- Low output skew: <200 ps

- 3.3 V operation

- ESD classification testing is done to JEDEC Standard JESD22.

Protection exceeds 2000 V to HBM per method A114.

#### **DESCRIPTION**

The PCK2002PL is a 1-4 fanout buffer used as a high-performance, low skew, general purpose and PCI-X clock buffer. It distributes one input clock (BUF\_IN) signal to four output clocks (BUF\_OUT\_n).

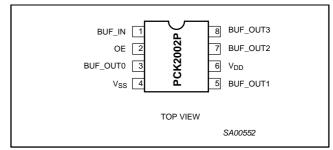

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTION**

| PIN<br>NUMBER | I/O<br>TYPE | SYMBOL           | FUNCTION               |

|---------------|-------------|------------------|------------------------|

| 1             | Input       | BUF_IN           | Buffered clock input   |

| 3, 5, 7, 8    | Output      | BUF_OUT<br>(0-3) | Buffered clock outputs |

| 6             | Input       | $V_{DD}$         | 3.3 V supply           |

| 2             | Input       | OE               | Output Enable          |

| 4             | Input       | V <sub>SS</sub>  | Ground                 |

#### **QUICK REFERENCE DATA**

| SYMBOL                               | PARAMETER                                           | CONDITIONS                                                                       | TYPICAL    | UNIT |

|--------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|------------|------|

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>BUF_IN to BUF_OUT <sub>n</sub> | $V_{CC} = 3.3 \text{ V, } C_L = 25 \text{ pF}$                                   | 2.9<br>2.8 | ns   |

| t <sub>r</sub>                       | Rise time                                           | $V_{CC} = 3.3 \text{ V}, C_L = 25 \text{ pF}, 0.2 V_{DD} \text{ to } 0.6 V_{DD}$ | 800        | ps   |

| t <sub>f</sub>                       | Fall time                                           | $V_{CC} = 3.3 \text{ V}, C_L = 25 \text{ pF}, 0.6 V_{DD} \text{ to } 0.2 V_{DD}$ | 600        | ps   |

| I <sub>CC</sub>                      | Total supply current                                | V <sub>CC</sub> = 3.6 V                                                          | 50         | μΑ   |

#### **ORDERING INFORMATION**

| PACKAGES            | TEMPERATURE RANGE | ORDER CODE | DRAWING NUMBER |

|---------------------|-------------------|------------|----------------|

| 8-Pin Plastic TSSOP | -40 to +85 °C     | PCK2002PDP | SOT505-1       |

| 8-Pin Plastic SO    | -40 to +85 °C     | PCK2002PD  | SOT96-1        |

## 533 MHz PCI-X clock buffer

PCK2002P

#### **FUNCTION TABLE**

| OE | BUF_IN | BUF_OUTn |

|----|--------|----------|

| L  | X      | L        |

| Н  | L      | L        |

| Н  | Н      | Н        |

## ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>

In accordance with the Absolute Maximum Rating System (IEC 134). Voltages are referenced to  $V_{SS}$  ( $V_{SS}$  = 0 V).

| CVMDOL           | DADAMETED                                                     | CONDITION                                                                      | LII  | UNIT                  |      |

|------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------|------|-----------------------|------|

| SYMBOL           | PARAMETER                                                     | CONDITION                                                                      | MIN  | MAX                   | UNII |

| $V_{DD}$         | DC 3.3 V supply voltage                                       |                                                                                | -0.5 | +4.3                  | V    |

| I <sub>IK</sub>  | DC input diode current                                        | V <sub>1</sub> < 0                                                             | _    | -50                   | mA   |

| $V_{I}$          | DC input voltage                                              | Note 2                                                                         | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| I <sub>OK</sub>  | DC output diode current                                       | $V_O > V_{DD}$ or $V_O < 0$                                                    | _    | ±50                   | mA   |

| Vo               | DC output voltage                                             | Note 2                                                                         | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| ΙO               | DC output source or sink current                              | $V_O \ge 0$ to $V_{DD}$                                                        | _    | ±50                   | mA   |

| T <sub>stg</sub> | Storage temperature range                                     |                                                                                | -65  | +150                  | °C   |

| P <sub>tot</sub> | Power dissipation per package plastic medium-shrink SO (SSOP) | For temperature range: 0 to +70 °C above +55 °C derate linearly with 11.3 mW/K | _    | 850                   | mW   |

#### NOTES:

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL           | PARAMETER                                       | CONDITIONS | LIM | UNIT     |      |  |

|------------------|-------------------------------------------------|------------|-----|----------|------|--|

| STIVIBUL         | PARAMETER                                       | CONDITIONS | MIN | MAX      | UNII |  |

| $V_{DD}$         | DC 3.3V supply voltage                          |            | 3.0 | 3.6      | V    |  |

| $C_{L}$          | Capacitive load                                 |            | 20  | 30       | pF   |  |

| VI               | DC input voltage range                          |            | 0   | $V_{DD}$ | V    |  |

| Vo               | DC output voltage range                         |            | 0   | $V_{DD}$ | V    |  |

| T <sub>amb</sub> | Operating ambient temperature range in free air |            | -40 | +85      | °C   |  |

Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2.</sup> The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

## 533 MHz PCI-X clock buffer

PCK2002P

## **DC CHARACTERISTICS**

|                 |                          |                     | TEST CONDITIONS           | LIM                    |                       |                       |    |

|-----------------|--------------------------|---------------------|---------------------------|------------------------|-----------------------|-----------------------|----|

| SYMBOL          | PARAMETER                |                     | TEST CONDITIONS           | T <sub>amb</sub> = -40 | UNIT                  |                       |    |

|                 |                          | V <sub>DD</sub> (V) | OTHER                     |                        | MIN                   | MAX                   |    |

| $V_{IH}$        | HIGH level input voltage | 3.0 to 3.6          | _                         | _                      | 2.0                   | V <sub>DD</sub> + 0.3 | V  |

| $V_{IL}$        | LOW level input voltage  | 3.0 to 3.6          | _                         | _                      | V <sub>SS</sub> - 0.3 | 0.8                   | V  |

|                 |                          | 3.0 to 3.6          | I <sub>OH</sub> = -1 mA   | _                      | V <sub>DD</sub> - 0.2 | _                     | V  |

| Vон             | Output HIGH voltage      | 3.0                 | I <sub>OH</sub> = -24 mA  | _                      | 2.0                   | _                     | V  |

|                 |                          | 3.0                 | I <sub>OH</sub> = -12 mA  | _                      | 2.4                   | _                     | V  |

|                 |                          | 3.0 to 3.6          | I <sub>OL</sub> = 1 mA    | _                      | _                     | 0.2                   | V  |

| $V_{OL}$        | Output LOW voltage       | 3.0                 | I <sub>OL</sub> = 24 mA   | _                      | _                     | 0.8                   | V  |

|                 |                          | 3.0                 | I <sub>OL</sub> = 12 mA   | _                      | _                     | 0.55                  | V  |

|                 | Output HIGH surrent      | 3.0                 | V <sub>OUT</sub> = 1 V    | _                      | -50                   | _                     | mA |

| I <sub>OH</sub> | Output HIGH current      | 3.3                 | V <sub>OUT</sub> = 1.65 V | _                      | _                     | -150                  | mA |

|                 | Output LOW ourrent       | 3.0                 | V <sub>OUT</sub> = 2.0 V  | _                      | 60                    | _                     | mA |

| l <sub>OL</sub> | Output LOW current       | 3.3                 | V <sub>OUT</sub> = 1.65 V | _                      | _                     | 150                   | mA |

| ±l <sub>l</sub> | Input leakage current    | 3.6                 | $V_I = V_{DD}$ or GND     | _                      | _                     | ±5                    | μΑ |

| Icc             | Quiescent supply current | 3.6                 | $V_I = V_{DD}$ or GND     | $I_O = 0$              | _                     | 100                   | μΑ |

2002 Dec 13

## 533 MHz PCI-X clock buffer

PCK2002P

#### **AC CHARACTERISTICS**

| SYMBOL             | PARAMETER                   | TEST CONDI | TIONS | T <sub>am</sub> | UNIT             |     |      |

|--------------------|-----------------------------|------------|-------|-----------------|------------------|-----|------|

|                    |                             |            | NOTES | MIN             | TYP <sup>6</sup> | MAX |      |

| t <sub>H</sub>     | CLK HIGH time               | 66 MHz     | 2     | 6.0             | _                | _   | ns   |

| t∟                 | CLK LOW time                | OD IVITZ   | 3     | 6.0             | _                | _   | ns   |

| t <sub>H</sub>     | CLK HIGH time               | 140 MHz    | 2     | 2.9             | _                | _   | ns   |

| t∟                 | CLK LOW time                | 140 101112 | 3     | 3.0             | _                | _   | ns   |

| t <sub>R</sub>     | Output rise slew rate       |            | 4     | 1.4             | 1.7              | 4.0 | V/ns |

| t <sub>F</sub>     | Output fall slew rate       |            | 4     | 1.5             | 2.2              | 4.0 | V/ns |

| t <sub>PLH</sub>   | Buffer LH propagation delay |            | 5     | 1.8             | 2.9              | 3.4 | ns   |

| t <sub>PHL</sub>   | Buffer HL propagation delay |            | 5     | 1.8             | 2.8              | 3.4 | ns   |

| tskw               | Bus CLK skew                |            | 1     | _               | _                | 200 | ps   |

| t <sub>DDSKW</sub> | Device to device skew       |            | 1     | _               | _                | 500 | ps   |

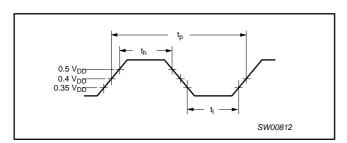

#### NOTES:

- 1. CLK skew is only valid for equal loading of all outputs.

- 2.  $t_H$  is measured at 0.5  $V_{DD}$  as shown in Figure 2. 3.  $t_L$  is measured at 0.35  $V_{DD}$  as shown in Figure 2.

- 4.  $t_R$  and  $t_F$  are measured as a transition through the threshold region 0.2  $V_{DD}$  to 0.6  $V_{DD}$  and 0.6  $V_{DD}$  to 0.2  $V_{DD}$ .

- 5. Input edge rate for these tests must be faster than 1 V/ns.

- 6. All typical values are at  $V_{CC}$  = 3.3 V and  $T_{amb}$  = 25 °C.

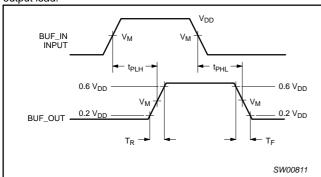

#### **AC WAVEFORMS**

$V_M = 50\% V_{DD}$

$C_{L} = 25 \text{ pF}$

$V_{OL}^{-}$  and  $V_{OH}$  are the typical output voltage drop that occur with the output load.

Figure 1. Load circuitry for switching times.

Figure 2. Buffer Output clock

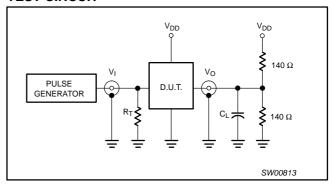

#### **TEST CIRCUIT**

Figure 3. Load circuitry for switching times

2002 Dec 13 5

## 533 MHz PCI-X clock buffer

**PCK2002P**

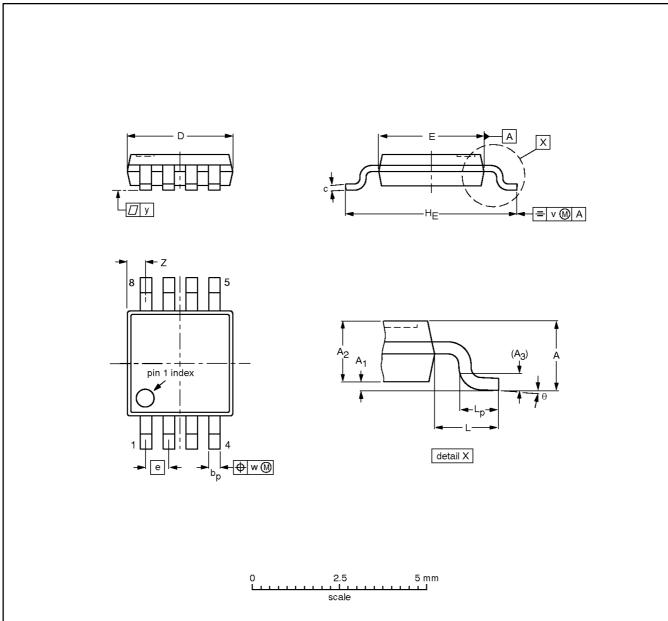

TSSOP8: plastic thin shrink small outline package; 8 leads; body width 3 mm

SOT505-1

#### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bр           | O            | D <sup>(1)</sup> | E <sup>(2)</sup> | e    | HE           | L    | Lр           | v   | w   | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|------|--------------|------|--------------|-----|-----|-----|------------------|----------|

| mm   | 1.10      | 0.15<br>0.05   | 0.95<br>0.80   | 0.25           | 0.45<br>0.25 | 0.28<br>0.15 | 3.10<br>2.90     | 3.10<br>2.90     | 0.65 | 5.10<br>4.70 | 0.94 | 0.70<br>0.40 | 0.1 | 0.1 | 0.1 | 0.70<br>0.35     | 6°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER | RENCES | EUROPEAN   | ISSUE DATE |

|----------|-----|-------|--------|------------|------------|

| VERSION  | IEC | JEDEC | EIAJ   | PROJECTION | 1330E DATE |

| SOT505-1 |     |       |        |            | 99-04-09   |

## 533 MHz PCI-X clock buffer

**PCK2002P**

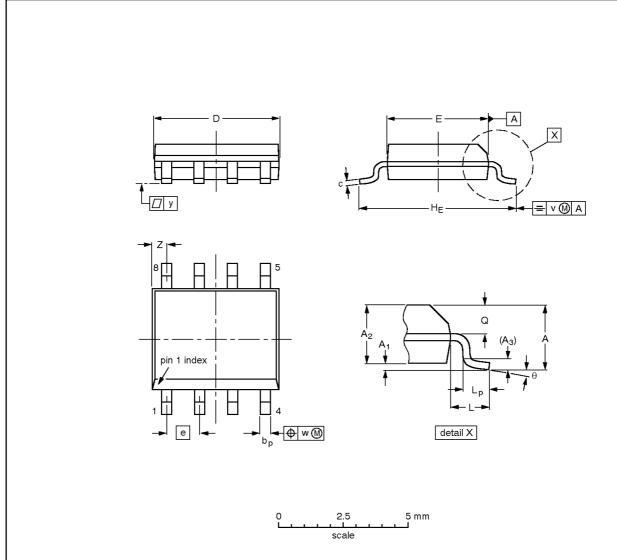

## SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

#### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | е     | HE             | L     | Lp             | Q          | >    | w    | у     | Z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|------|--------------|------------------|------------------|------------------|-------|----------------|-------|----------------|------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25 | 0.49<br>0.36 | 0.25<br>0.19     | 5.0<br>4.8       | 4.0<br>3.8       | 1.27  | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6 | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01 |              | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.050 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 |            | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE |        | REFER  | EUROPEAN | ISSUE DATE |                                 |  |

|---------|--------|--------|----------|------------|---------------------------------|--|

| VERSION | IEC    | JEDEC  | EIAJ     | PROJECTION | 1330E DATE                      |  |

| SOT96-1 | 076E03 | MS-012 |          | <b>(</b>   | <del>97-05-22</del><br>99-12-27 |  |

## 533 MHz PCI-X clock buffer

PCK2002P

## **REVISION HISTORY**

| Rev | Date     | Description                                                           |  |

|-----|----------|-----------------------------------------------------------------------|--|

| _3  | 20021213 | Product data (9397 750 10863); ECN 853-2254 29225 of 22 November 2002 |  |

|     |          | Modifications:                                                        |  |

|     |          | ● Increase F <sub>max</sub> to 533 MHz.                               |  |

| _2  | 20010509 | Product data (9397 750 08348); ECN 853-2254 26252 of 09 May 2001.     |  |

## 533 MHz PCI-X clock buffer

**PCK2002P**

#### **Data sheet status**

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ı     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                   |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

- [1] Please consult the most recently issued data sheet before initiating or completing a design.

- [2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

- [3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825

Document order number:

For sales offices addresses send e-mail to:

sales. addresses @www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2002 All rights reserved. Printed in U.S.A.

Date of release: 12-02

9397 750 10863

\_

Let's make things better.

Philips Semiconductors

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## NXP:

PCK2002PD PCK2002PD-T PCK2002PDP-T