# Digital Power Management IC 2 MHz, 600 mA DC/DC with Dual 300 mA/300 mA Low $V_{\rm IN}$ LDOs

#### **Features**

- 2.7V to 5.5V Input Voltage Range

- · 2 MHz DC/DC Converter and Two LDOs

- · Integrated Power-on Reset (POR)

- · Adjustable POR Delay Time

- · LOWQ Mode

- 30 μA Total I<sub>Q</sub> When in LOWQ Mode

- · DC/DC Converter

- Up to 600 mA of Output Current in PWM Mode

- LOWQ Mode: No Ripple Light Load Mode

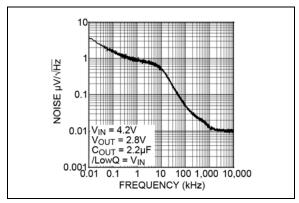

- 53 μV<sub>RMS</sub> Output Noise in LOWQ Mode

- 2 MHz PWM Mode Operation

- >90% Efficiency

- LDO1

- 1.65V to 5.5V Input Voltage Range

- 300 mA Output Current

- Output Voltage Down to 0.8V

- LDO2

- 2.7V to 5.5V Input Voltage Range

- 300 mA Output Current

- Output Voltage Down to 0.8V

- Thermal Shutdown Protection

- · Current-Limit Protection

- Simple, Leakage-Free Interfacing to Host MPU in Applications with Backup Power

- · Tiny 16-Pin 3 mm x 3 mm QFN Package

#### **Applications**

- · Embedded MPU and MCU Power

- · Portable and Wearable Applications

- · Low-Power RF Systems

- · Backup Power Systems

#### **General Description**

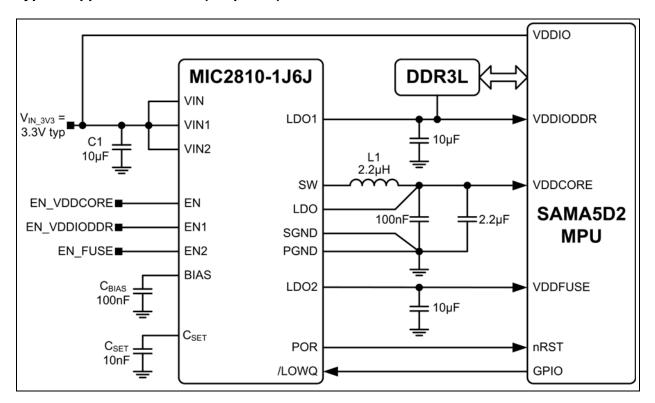

The MIC2810 is a high performance power management IC, featuring three output voltages with independent enable control: a 2 MHz DC/DC converter and two 300 mA LDOs. The MIC2810 features a LOWQ mode, reducing the total current draw while in this mode to less than 30  $\mu A$ . In LOWQ mode, the output noise of the DC/DC converter is 53  $\mu V_{RMS}$ , significantly lower than other converters that use a PFM light load mode that can interfere with sensitive RF circuitry.

The DC/DC converter uses small values of L and C to reduce board space but still retains high efficiency over a wide load range, while supporting load currents up to 600 mA.

The LDOs operate with very small ceramic output capacitors for stability, therefore, reducing required board space and component cost. It is available in various output voltage options in the 16-pin 3 mm x 3 mm QFN leadless package.

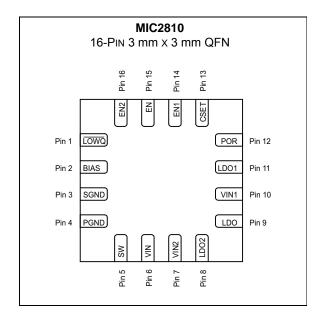

#### Package Type

## **Typical Application Circuit (simplified)**

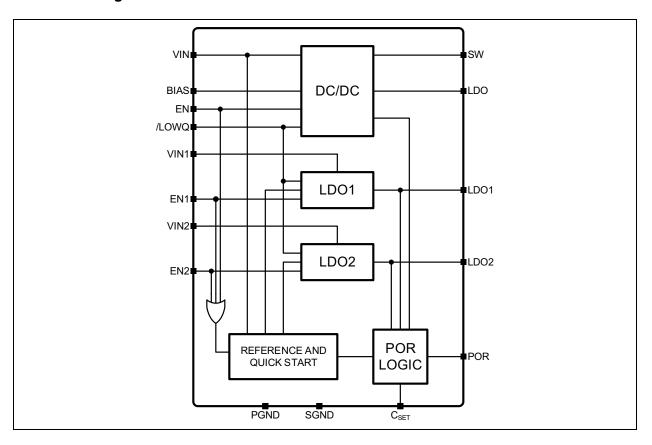

## **Functional Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| Supply Voltage (V <sub>IN</sub> , V <sub>IN1</sub> , V <sub>IN2</sub> )       | 0V to +6.0V           |

|-------------------------------------------------------------------------------|-----------------------|

| Enable Input Voltage (V <sub>EN</sub> , V <sub>EN1</sub> , V <sub>EN2</sub> ) | 0V to V <sub>IN</sub> |

| Power Dissipation (Note 1)                                                    |                       |

| ESD Rating (Note 2)                                                           | 2 kV                  |

#### **Operating Ratings ‡**

| Supply Voltage (V <sub>IN</sub> , V <sub>IN2</sub> )                          | +2.7V to +5.5V         |

|-------------------------------------------------------------------------------|------------------------|

| Supply Voltage (V <sub>IN1</sub> )                                            |                        |

| Enable Input Voltage (V <sub>EN</sub> , V <sub>EN1</sub> , V <sub>EN2</sub> ) | 0V to +V <sub>IN</sub> |

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

**‡ Notice:** The device is not guaranteed to function outside its operating ratings.

- 1: The maximum allowable power dissipation of any  $T_A$  (ambient temperature) is  $P_{D(max)} = (T_{J(max)} T_A) / \theta_{JA}$ . Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the regulator will go into thermal shutdown.

- 2: Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5 k $\Omega$  in series with 100 pF.

#### TABLE 1-1: ELECTRICAL CHARACTERISTICS (Note 1)

Electrical Characteristics:  $V_{IN}$  = EN1 = EN2 =  $\overline{LOWQ}$  =  $V_{OUT}$  (Note 2) + 1V;  $C_{OUTDC/DC}$  = 2.2  $\mu$ F,  $C_{LDO1}$  =  $C_{LDO2}$  = 2.2  $\mu$ F;  $I_{OUTDC/DC}$  = 100 mA;  $I_{OUTLDO1}$  =  $I_{OUTLDO2}$  = 100  $\mu$ A;  $I_{J}$  = 25°C, **bold** values indicate –40°C  $\leq$   $I_{J}$   $\leq$  +125°C; unless noted.

| Parameter                              | Symbol                 | Min. | Тур. | Max. | Units | Conditions                                                                                                                       |

|----------------------------------------|------------------------|------|------|------|-------|----------------------------------------------------------------------------------------------------------------------------------|

| UVLO Threshold                         | UVLO <sub>TH</sub>     | 2.45 | 2.55 | 2.65 | V     | Rising input voltage during turn-on                                                                                              |

| UVLO Hysteresis                        | UVLO <sub>HYS</sub>    | _    | 100  | _    | mV    | _                                                                                                                                |

|                                        |                        | _    | 800  | 1100 |       | V <sub>FB</sub> = GND (not switching)                                                                                            |

| Ground Pin Current                     | I <sub>GND</sub>       | _    | 55   | 85   | μA    | LDO1 or LDO2 (EN = GND; EN1 or                                                                                                   |

|                                        |                        | _    |      | 95   |       | EN2 = GND)                                                                                                                       |

| Ground Pin Current in Shutdown         | I <sub>GND_SHDN</sub>  | _    | 0.2  | 5    | μA    | EN = EN1 = EN2 = 0V                                                                                                              |

|                                        |                        | _    | 30   | 60   |       | All channels on, I <sub>DC/DC</sub> = I <sub>LDO1</sub> =                                                                        |

| Ground Pin Current                     |                        | _    |      | 80   |       | $I_{LDO2} = 0 \text{ mA } (\overline{LOWQ} = GND)$                                                                               |

| (LOWQ mode)                            | I <sub>GND_LOWQ</sub>  | _    | 20   | 70   | μA    | LDO1 or LDO2 (EN = GND; EN1 or<br>EN2 = GND);<br>I <sub>OUT</sub> = 0 mA (LOWQ = GND)                                            |

| Overtemperature<br>Shutdown            | T <sub>SD</sub>        | _    | 160  |      | °C    | _                                                                                                                                |

| Overtemperature<br>Shutdown Hysteresis | T <sub>SDHYS</sub>     | _    | 23   |      | °C    | _                                                                                                                                |

| Enable Inputs (EN; EN1;                | EN2; LOWQ)             |      |      |      |       |                                                                                                                                  |

| Enable Input Voltage                   | V <sub>IH</sub>        | _    | _    | 0.2  | V     | Logic Low                                                                                                                        |

| Litable input voltage                  | V <sub>IL</sub>        | 1.0  | _    | _    | V     | Logic High                                                                                                                       |

| Enable Input Current                   | l                      | _    | 0.1  | 1    | μA    | V <sub>IL</sub> ≤ 0.2V                                                                                                           |

| Enable input current                   | I <sub>ENLK</sub>      |      | 0.1  | 1    | μA    | V <sub>IH</sub> ≥ 1.0V                                                                                                           |

| Turn-on Time                           |                        |      |      |      |       |                                                                                                                                  |

| Turn-on Time<br>(LDO1 and LDO2)        | t <sub>TURN-ON</sub>   | _    | 240  | 500  | μs    | _                                                                                                                                |

| Turn-on Time (DC/DC)                   | t <sub>TURN-ON</sub>   | _    | 83   | 350  | μs    | $(\overline{\text{LOWQ}} = V_{\text{IN}}; I_{\text{LOAD}} = 300 \text{ mA});$<br>(LOWQ = GND; $I_{\text{LOAD}} = 10 \text{ mA})$ |

| POR Output                             |                        |      |      |      |       |                                                                                                                                  |

| POR Threshold Voltage, Falling         | V <sub>THLOW_POR</sub> | 90   | 91   | l    | %     | Low Threshold, % of nominal ( $V_{DC/DC}$ or $V_{LDO1}$ or $V_{LDO2}$ ) (Flag ON)                                                |

| POR Threshold Voltage,<br>Rising       | V <sub>THIGH_POR</sub> | _    | 96   | 99   | %     | High Threshold, % of nominal ( $V_{DC/DC}$ and $V_{LDO1}$ and $V_{LDO2}$ ) (Flag OFF)                                            |

| VOL                                    | VOL <sub>POR</sub>     | _    | 10   | 100  | mV    | POR Output Logic Low Voltage; $I_L = 250 \mu A$                                                                                  |

| IPOR                                   | ILEAK <sub>POR</sub>   | _    | 0.01 | 1    | μA    | Flag Leakage Current, Flag OFF                                                                                                   |

| SET INPUT                              |                        |      |      |      |       |                                                                                                                                  |

| SET Pin Current Source                 | I <sub>SET</sub>       | 0.75 | 1.25 | 1.75 | μΑ    | V <sub>SET</sub> = 0V                                                                                                            |

| SET Pin Threshold<br>Voltage           | VTH <sub>SET</sub>     | _    | 1.25 | _    | V     | POR = High                                                                                                                       |

**Note 1:** Specification for packaged product only.

<sup>2:</sup>  $V_{OUT}$  denotes the highest of the three output voltages of DC/DC, LDO1 and LDO2.

TABLE 1-2: ELECTRICAL CHARACTERISTICS - DC/DC CONVERTER

Electrical Characteristics:  $V_{IN}$  =  $V_{OUTDC/DC}$  + 1V; EN1 =  $V_{IN}$ ; EN2 = GND;  $I_{OUTDC/DC}$  = 100 mA; L = 2.2  $\mu$ H;  $C_{OUTDC/DC}$  = 2.2  $\mu$ F;  $T_J$  = 25°C, **bold** values indicate –40°C to + 125°C; unless noted.

| Parameter                         | Symbol                                                      | Min. | Тур. | Max. | Units         | Conditions                                                                                                                                  |  |  |

|-----------------------------------|-------------------------------------------------------------|------|------|------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LOWQ = High (Full Power Mode)     |                                                             |      |      |      |               |                                                                                                                                             |  |  |

| Output Valtage Assure             |                                                             | -2   | _    | 2    | %             | Nominal V <sub>OUT</sub> tolerance                                                                                                          |  |  |

| Output Voltage Accuracy           | V <sub>OUT</sub>                                            | -3   | _    | 3    | 70            | Norminal V <sub>OUT</sub> tolerance                                                                                                         |  |  |

| Output Voltage Line<br>Regulation | (ΔV <sub>OUT</sub> /V <sub>OUT</sub> )<br>/ΔV <sub>IN</sub> | _    | 0.2  | _    | %/V           | $V_{OUT}$ > 2.4V; $V_{IN}$ = $V_{OUT}$ + 300 mV to 5.5V, $I_{LOAD}$ = 100 mA $V_{OUT}$ < 2.4V; $V_{IN}$ = 2.7V to 5.5V, $I_{LOAD}$ = 100 mA |  |  |

| Output Voltage Load Regulation    | ΔV <sub>OUT</sub> /V <sub>OUT</sub>                         | _    | 0.1  | _    | %             | 20 mA < I <sub>LOAD</sub> < 600 mA                                                                                                          |  |  |

| Maximum Duty Cycle                | DC <sub>MAX</sub>                                           | 100  | _    | _    | %             | V <sub>FB</sub> ≤ 0.4V                                                                                                                      |  |  |

| PWM Switch                        | _                                                           | _    | 0.5  | _    | Ω             | $I_{SW}$ = 150 mA, $V_{FB}$ = 0.7 $V_{FB\_NOM}$ PMOS                                                                                        |  |  |

| ON-Resistance                     |                                                             | _    | 0.6  | _    | Ω             | $I_{SW}$ = -150 mA, $V_{FB}$ = 1.1 $V_{FB\_NOM}$<br>NMOS                                                                                    |  |  |

| Oscillator Frequency              | f <sub>osc</sub>                                            | 1.8  | 2    | 2.2  | MHz           | _                                                                                                                                           |  |  |

| Current Limit in PWM Mode         | _                                                           | 0.75 | 1    | 1.6  | Α             | V <sub>FB</sub> = 0.9 * V <sub>NOM</sub>                                                                                                    |  |  |

| LOWQ = Low (Light Load            | d Mode)                                                     |      |      |      |               |                                                                                                                                             |  |  |

|                                   |                                                             | -2   | _    | 2    |               | Variation from nominal V <sub>OUT</sub>                                                                                                     |  |  |

| Output Voltage Accuracy           | V <sub>OUT</sub>                                            | -3   | _    | 3    | %             | Variation from nominal V <sub>OUT</sub> ;<br>–40°C to +125°C                                                                                |  |  |

| Line Regulation                   | $(\Delta V_{OUT}/V_{OUT})$<br>$/\Delta V_{IN}$              | _    | 0.02 | 0.3  | %/V           | $V_{IN} = V_{OUT} + 1V \text{ to 5.5V};$                                                                                                    |  |  |

| Line Negulation                   |                                                             | _    | _    | 0.6  |               | I <sub>OUT</sub> = 100 μA                                                                                                                   |  |  |

| Load Regulation                   | $\Delta V_{OUT}/V_{OUT}$                                    | _    | 0.4  | 1.5  | %             | I <sub>OUT</sub> = 100 μA to 50 mA                                                                                                          |  |  |

| Ripple Rejection                  | PSRR                                                        |      | 45   | _    | dB            | f = up to 1 kHz                                                                                                                             |  |  |

| Current Limit                     | I <sub>LIM_LOWQ</sub>                                       | 80   | 120  | 190  | mA            | V <sub>OUT</sub> = 0V                                                                                                                       |  |  |

| Output Voltage Noise              | $V_N$                                                       | _    | 53   | _    | $\mu V_{RMS}$ | 10 Hz to 100 kHz                                                                                                                            |  |  |

#### TABLE 1-3: ELECTRICAL CHARACTERISTICS - LDO1/LDO2

Electrical Characteristics:  $V_{IN1} = V_{IN2} = V_{OUTLDO1} + 1.0V$  or  $V_{IN1} = V_{IN2} = V_{OUTLDO2} + 1.0V$ ; EN = GND; EN1 = EN2 =  $V_{IN1} = V_{IN2}$ ;  $C_{LDO1} = C_{LDO2} = 2.2~\mu\text{F}$ ;  $I_{OUTLDO1} = 100~\mu\text{A}$ ;  $T_J = 25^{\circ}\text{C}$ , **bold** values indicate  $-40^{\circ}\text{C} \le T_J \le +125^{\circ}\text{C}$ ; unless noted.

| Parameter                     | Symbol                   | Min. | Тур. | Max. | Units             | Conditions                                                   |  |  |

|-------------------------------|--------------------------|------|------|------|-------------------|--------------------------------------------------------------|--|--|

| LOWQ = High (Full Power Mode) |                          |      |      |      |                   |                                                              |  |  |

|                               |                          | -2   | _    | 2    |                   | Variation from nominal V <sub>OUT</sub>                      |  |  |

| Output Voltage Accuracy       | V <sub>OUT</sub>         | -3   | _    | 3    | %                 | Variation from nominal V <sub>OUT</sub> ;<br>-40°C to +125°C |  |  |

| Line Degulation               |                          | _    | 0.02 | 0.3  | %/V               | \\ -\\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                       |  |  |

| Line Regulation               | _                        | _    | _    | 0.6  | 70/ V             | $V_{IN} = V_{OUT} + 1V \text{ to } 5.5V$                     |  |  |

|                               |                          | _    | 0.20 | _    |                   | I <sub>OUT</sub> = 100 μA to 150 mA                          |  |  |

| Load Regulation               | $\Delta V_{OUT}/V_{OUT}$ | _    | 0.25 | _    | %                 | I <sub>OUT</sub> = 100 μA to 200 mA                          |  |  |

|                               |                          | _    | 0.40 | 1.5  |                   | I <sub>OUT</sub> = 100 μA to 300 mA                          |  |  |

|                               |                          | _    | 70   | _    |                   | I <sub>OUT</sub> = 150 mA                                    |  |  |

| Dropout Voltage               | $V_{DO}$                 | _    | 94   | _    | mV                | I <sub>OUT</sub> = 200 mA                                    |  |  |

|                               |                          | _    | 142  | 300  |                   | I <sub>OUT</sub> = 300 mA                                    |  |  |

| Ripple Rejection              | PSRR                     | _    | 35   | _    | dB                | f = up to 1 kHz                                              |  |  |

| Current Limit                 | I <sub>LIM</sub>         | 400  | 600  | 850  | mA                | V <sub>OUT</sub> = 0V                                        |  |  |

| Output Voltage Noise          | V <sub>N</sub>           | _    | 91   | _    | μV <sub>RMS</sub> | 10 Hz to 100 kHz                                             |  |  |

| LOWQ = Low (Light Load        | d Mode)                  |      |      |      |                   |                                                              |  |  |

|                               |                          | -3   | _    | 3    |                   | Variation from nominal V <sub>OUT</sub>                      |  |  |

| Output Voltage Accuracy       | V <sub>OUT</sub>         | -4   | _    | 4    | %                 | Variation from nominal V <sub>OUT</sub> ;<br>–40°C to +125°C |  |  |

| Line Degulation               |                          | _    | 0.02 | 0.3  | 0/ /\             | \\ -\\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                       |  |  |

| Line Regulation               | _                        | _    | _    | 0.6  | %/V               | $V_{IN} = V_{OUT} + 1V \text{ to } 5.5V$                     |  |  |

| Load Regulation               | $\Delta V_{OUT}/V_{OUT}$ | _    | 0.2  | 1.0  | %                 | I <sub>OUT</sub> = 100 μA to 10 mA                           |  |  |

| Dropout Voltage               | V <sub>DO</sub>          | _    | 22   | 35   | mV                | - 10 mA                                                      |  |  |

|                               |                          |      | _    | 50   |                   | I <sub>OUT</sub> = 10 mA                                     |  |  |

| Current Limit                 | I <sub>LIM</sub>         | 50   | 85   | 125  | mA                | V <sub>IN</sub> = 2.7V; V <sub>OUT</sub> = 0V                |  |  |

| Ripple Rejection              | PSRR                     |      | 35   |      | dB                | f = up to 1 kHz                                              |  |  |

TABLE 1-4: TEMPERATURE SPECIFICATIONS (Note 1)

| Parameters                 | Sym.           | Min. | Тур. | Max. | Units | Conditions         |

|----------------------------|----------------|------|------|------|-------|--------------------|

| Temperature Ranges         |                |      |      |      |       |                    |

| Storage Temperature Range  | T <sub>S</sub> | -65  | _    | +150 | °C    | _                  |

| Lead Temperature           | _              | _    | _    | +260 | °C    | Soldering, 10 sec. |

| Junction Temperature       | TJ             | -40  | _    | +125 | °C    | _                  |

| Package Thermal Resistance |                |      |      |      |       |                    |

| 16-Ld QFN                  | $\theta_{JA}$  | _    | 56   | _    | °C/W  | _                  |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +125°C rating. Sustained junction temperatures above +125°C can impact the device reliability.

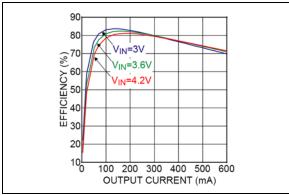

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

For this page only, DC/DC Normal Mode ( $\overline{LOWQ} = V_{IN}$ )

FIGURE 2-1: 1.2V<sub>OUT</sub> Efficiency.

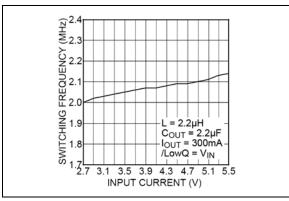

**FIGURE 2-2:** Switching Frequency vs. Input Voltage.

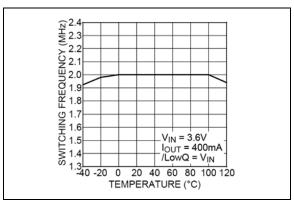

**FIGURE 2-3:** Switching Frequency vs. Temperature.

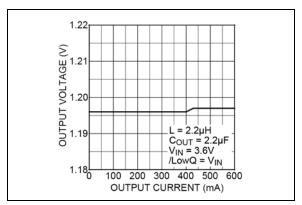

FIGURE 2-4: Load Regulation.

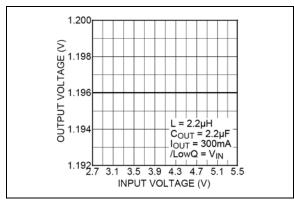

FIGURE 2-5: Line Regulation.

FIGURE 2-6: Current Limit vs. Input Voltage.

For this page only, DC/DC LOWQ Mode ( $\overline{LOWQ} = GND$ )

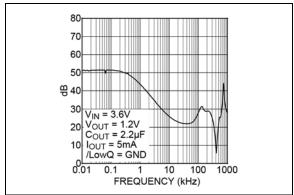

FIGURE 2-7: Power Supply Rejection Ratio.

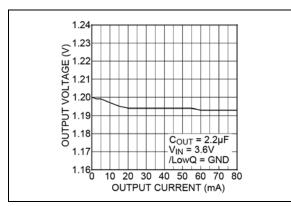

FIGURE 2-8: Load Regulation.

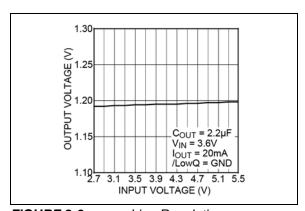

FIGURE 2-9: Line Regulation.

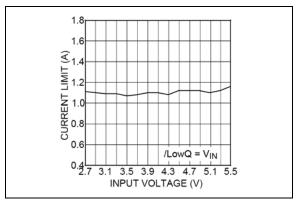

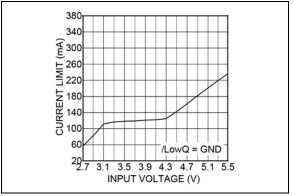

FIGURE 2-10: Current Limit vs. Input Voltage.

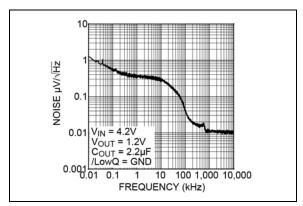

**FIGURE 2-11:** Output Noise Spectral Density.

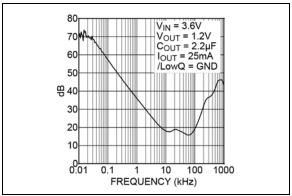

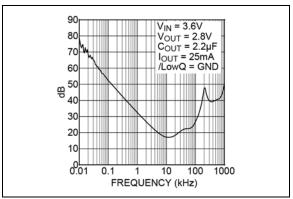

**FIGURE 2-12:** Power Supply Rejection Ratio LDO1 (LOWQ Mode).

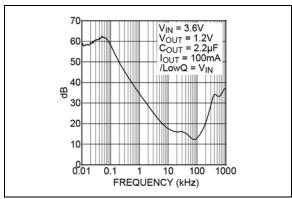

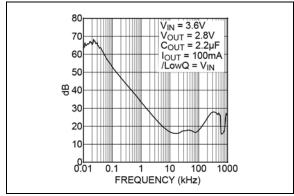

FIGURE 2-13: Power Supply Rejection Ratio LDO1 (Normal Mode).

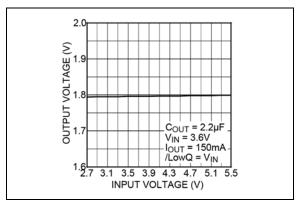

FIGURE 2-14: LDO1 Line Regulation.

**FIGURE 2-15:** Power Supply Rejection Ratio LDO2 (LOWQ Mode).

**FIGURE 2-16:** Power Supply Rejection Ratio LDO2 (Normal Mode).

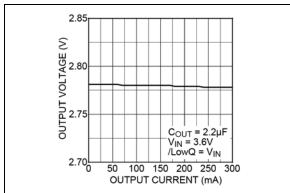

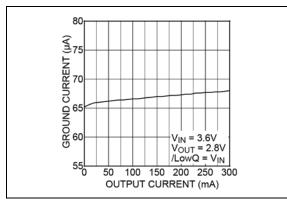

FIGURE 2-17: LDO2 Load Regulation.

**FIGURE 2-18:** Output Current.

LDO2 Ground Current vs.

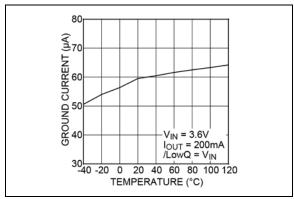

**FIGURE 2-19:** Temperature.

LDO2 Ground Current vs.

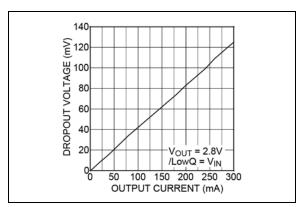

**FIGURE 2-20:** Output Current.

LDO2 Dropout Voltage vs.

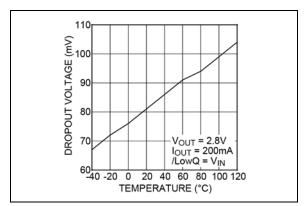

**FIGURE 2-21:** Temperature.

LDO2 Dropout Voltage vs.

**FIGURE 2-22:** Density.

LDO2 Output Noise Spectral

**FIGURE 2-23:** Transient.

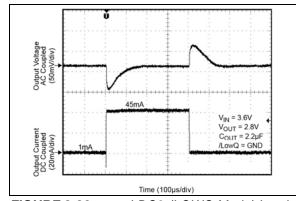

LDO2 (LOWQ Mode) Load

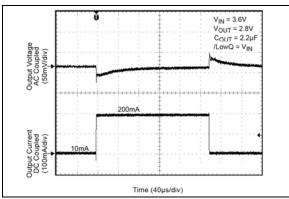

FIGURE 2-24: Transient.

LDO2 (Normal Mode) Load

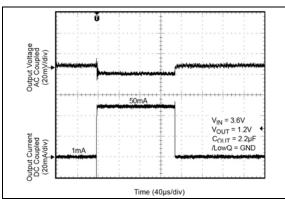

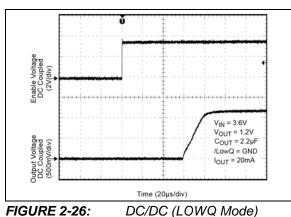

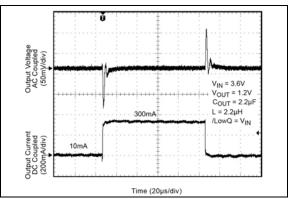

FIGURE 2-25: DC/DC (LOWQ Mode) Load Transient.

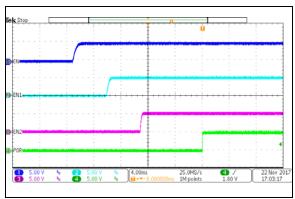

FIGURE 2-26: DC/Start-Up Waveform.

**FIGURE 2-27:**

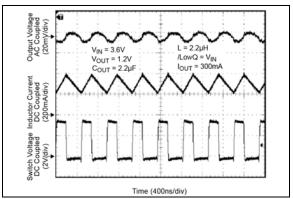

DC/DC PWM Waveforms.

**FIGURE 2-28:**

DC/DC Load Transient.

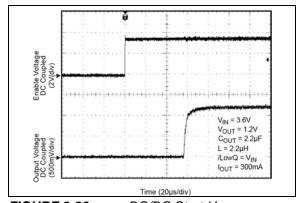

FIGURE 2-29: Waveforms.

DC/DC Start-Up

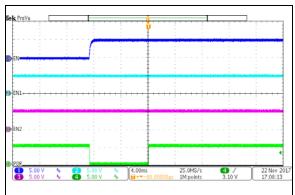

FIGURE 2-30: POR Behavior; EN1 = EN2 = High, Low-to-High Transition on EN.

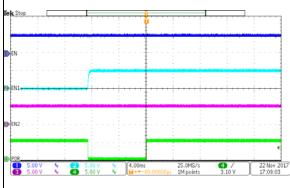

FIGURE 2-31: POR Behavior; EN = EN2 = High, Low-to-High Transition on EN1.

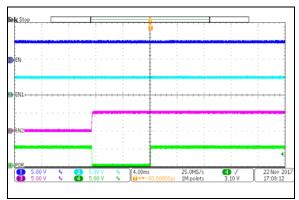

FIGURE 2-32: POR Behavior; EN = EN1 = High, Low-to-High Transition on EN2.

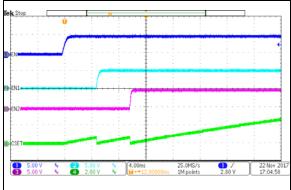

**FIGURE 2-33:** C<sub>SET</sub> Pin Voltage for Correct Sequencing.

FIGURE 2-34: POR Behavior for Correct Sequencing.

#### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| Pin Number | Pin Name         | Description                                                                                                                                                             |

|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | LOWQ             | LOWQ Mode. Active Low Input. Logic High = Full Power Mode; Logic Low = LOWQ Mode; Do not leave floating.                                                                |

| 2          | BIAS             | Internal circuit bias supply. It must be decoupled to signal ground with a 0.1 $\mu\text{F}$ capacitor and should not be loaded.                                        |

| 3          | SGND             | Signal ground.                                                                                                                                                          |

| 4          | PGND             | Power ground.                                                                                                                                                           |

| 5          | SW               | Switch (Output): Internal power MOSFET output switches.                                                                                                                 |

| 6          | V <sub>IN</sub>  | Supply Input – DC/DC and other circuitry shared with LDO1 and LDO2. Must be connected to Pin 7.                                                                         |

| 7          | V <sub>IN2</sub> | Supply Input – LDO2. Must be connected to Pin 6.                                                                                                                        |

| 8          | LDO2             | Output of LDO regulator 2.                                                                                                                                              |

| 9          | LDO              | LDO Output: Connect to V <sub>OUT</sub> of the DC/DC for LOWQ mode operation.                                                                                           |

| 10         | $V_{IN1}$        | Supply Input – LDO1.                                                                                                                                                    |

| 11         | LDO1             | Output of LDO regulator 1.                                                                                                                                              |

| 12         | POR              | Power-on Reset Output: Open-drain output. Active low indicates an output undervoltage condition on either one of the three regulated outputs.                           |

| 13         | C <sub>SET</sub> | Delay Set Input: Connect external capacitor to GND to set the internal delay for the POR output. When left open, there is a minimum delay. This pin cannot be grounded. |

| 14         | EN1              | Enable Input (LDO1). Active High Input. Logic high = On; Logic low = Off; do not leave floating.                                                                        |

| 15         | EN               | Enable Input (DC/DC). Active High Input. Logic High = On; Logic Low = Off; Do not leave floating.                                                                       |

| 16         | EN2              | Enable Input (LDO2). Active High Input. Logic high = On; Logic low = Off; do not leave floating.                                                                        |

#### 3.1 LOWQ

The  $\overline{LOWQ}$  pin provides a logic level control between the internal PWM switching regulator mode, and the low noise linear regulator mode. With  $\overline{LOWQ}$  pulled low ( $\leq$  0.2V), quiescent current of the device is greatly reduced by switching to a low noise linear regulator mode that has a typical supply current of 38  $\mu$ A. In linear (LDO) mode, the output can deliver 60 mA of current to the output. By placing  $\overline{LOWQ}$  high ( $\geq$  1V), the device transitions into a constant frequency PWM step-down regulator mode. This allows the device the ability to efficiently deliver up to 600 mA of output current at the same output voltage.

LOWQ mode also limits the output load of both LDO1 and LDO2 to less than 50 mA.

#### **3.2 BIAS**

The BIAS pin supplies the power to the internal control and reference circuitry. The bias is powered from  $V_{IN}$  through an internal  $6\Omega$  resistor. A small  $0.1~\mu F$  capacitor is required for bypassing.

#### 3.3 **SGND**

Signal ground (SGND) is the ground path for the biasing and control circuitry. The current loop for the signal ground should be as small as possible.

#### 3.4 PGND

Power ground (PGND) is the ground path for the high current PWM mode. The current loop for the power ground should be as small as possible.

#### 3.5 SW

The switch (SW) pin connects directly to the inductor and provides the switching current necessary to operate in PWM mode. Due to the high speed switching on this pin, the switch node should be routed away from sensitive nodes.

#### $V_{IN}/V_{IN1}/V_{IN2}$

Three input voltage pins provide power to the switch mode regulator, LDO1, and LDO2.  $V_{\rm IN}$  provides power to the control circuitry of the DC/DC converter and voltage reference circuitry shared by all the regulators in the MIC2810. LDO1's input voltage ( $V_{\rm IN1}$ ) can go down to 1.65V, but LDO2 and the DC/DC converter input voltages are limited to 2.7V minimum.

For the switch mode regulator,  $V_{IN}$  provides power to the MOSFET along with current limiting sense circuitry. Due to the high switching speeds, a 4.7  $\mu$ F capacitor is recommended close to  $V_{IN}$  and the power ground (PGND) pin for bypassing. Please refer to the PCB layout section for an example of an appropriate circuit layout.

#### 3.7 LDO2

Regulated output voltage of LDO2. Power is provided by  $V_{IN2}$ . The minimum recommended output capacitance is 2.2  $\mu F$ .

#### 3.8 LDO

The LDO pin is the output of the linear regulator and should be connected to the output of the step-down PWM regulator. In LOWQ mode ( $\overline{\text{LOWQ}}$  < 0.2V), the LDO provides the output voltage of the DC/DC regulator.

#### 3.9 LDO1

Regulated output voltage of LDO1. Input power is provided by  $V_{IN1}$ . The minimum recommended output capacitance is 2.2  $\mu$ F.

#### 3.10 Power-on Reset (POR)

The power-on reset output is an open-drain N-Channel device, requiring a pull-up resistor to either the input voltage or output voltage for proper voltage levels. The POR output has a delay time that is programmable with a capacitor from the CSET pin to ground. The delay time can be programmed to be as long as 1 second. In steady-state conditions, the POR output is high if at least one channel (DC/DC, LDO1, and LDO2) is enabled and has reached regulation. This is equivalent to performing a logic OR operation on the status of the output voltages.

If any of the outputs are subsequently pulled out of regulation (e.g., due to a momentary overload), the POR signal goes low and it remains low as long as the affected output is out of regulation. If the affected output returns within regulation, POR is asserted high after the delay time programmed with the capacitor at the CSET pin.

The ESD protection of the POR pin is free from clamping diodes to the input supply rails. Therefore, the POR signal can be asserted to host I/Os under backup power domains or pulled up to backup power sources without the risk of parasitic leakage, even if the main power to the MIC2810 is removed.

#### 3.11 C<sub>SET</sub>

The CSET pin is a current source output that charges a capacitor that sets the delay time for the power-on reset output from low to high. The delay for POR high to low (detecting an undervoltage on any of the outputs) is always minimal. The current source of  $1.25\mu\text{A}$  charges a capacitor up from 0V. When the capacitor reaches 1.25V, the output of the POR is allowed to go high. The delay time in microseconds is equal to the  $C_{\text{SET}}$  in picofarads.

#### **EQUATION 3-1:**

$$PORDelay(\mu s) = C_{SET}(pF)$$

#### 3.12 EN/EN1/EN2

All enable inputs are active high, requiring 1.0V for guaranteed operation. EN provides logic control for the DC/DC regulator. EN2 provides logic control for LDO2, and EN1 provides logic control for LDO1. The enable inputs are CMOS logic and cannot be left floating.

The enable pins provide logic level control of the specified outputs. When all enable pins are in the off state, supply current of the device is greatly reduced (typically <1  $\mu$ A). When the DC/DC regulator is in the off state, the output drive is placed in a "tri-stated" condition, where both the high side P-channel MOSFET and the low-side N-channel are in an "off" or non-conducting state. Do not drive any of the enable pins above the supply voltage.

#### 4.0 APPLICATION INFORMATION

The MIC2810 is a power management IC with a single integrated step-down regulator and two low dropout regulators. LDO1 and LDO2 are 300 mA low dropout regulators supplied from the input voltage pins. The step-down regulator is a 600 mA PWM power supply. All three regulators utilize a LOWQ light load mode to maximize battery efficiency under light load conditions. This is achieved with a LOWQ control pin that, when pulled low, shuts down all the biasing and drive current for the PWM regulator, along with reducing the current limit of the two independent LDOs. When the LOWQ pin is pulled low, the MIC2810 draws only 30 µA of operating current. This mode allows the output to be regulated through the LDO output, which is capable of providing 60 mA of output current. This method has the advantage of producing a clean, low current, ultra-low noise output in LOWQ mode. During LOWQ mode, the SW node becomes high impedance, blocking current flow. Other methods of reducing quiescent current, such as pulse frequency modulation (PFM) or bursting techniques create large amplitude and low frequency ripple voltages that can be detrimental to system operation.

When more than 60 mA is required, the LOWQ pin can be forced high, causing the MIC2810 to enter PWM mode. In this case, the LDO output makes a "hand-off" to the PWM regulator with virtually no variation in output voltage. The LDO output then turns off allowing up to 600 mA of current to be efficiently supplied through the PWM output to the load.

#### 4.1 Output Capacitor

LDO1 and LDO2 outputs require a 2.2 µF ceramic output capacitor for stability. The DC/DC switch mode regulator also requires a 2.2 µF ceramic output capacitor to be stable. All output capacitor values can be increased to improve transient response, but performance has been optimized for a 2.2 µF ceramic on the LDOs and the DC/DC regulator. X7R/X5R dielectric-type ceramic capacitors are recommended of their temperature performance. X5R/X7R-type capacitors change capacitance by 15% over their operating temperature range and are the most stable type of ceramic capacitors. Z5U and Y5V dielectric capacitors change value by as much as 50% to 60% respectively over their operating temperature ranges.

#### 4.2 Input Capacitor

A minimum 1  $\mu$ F ceramic, 4.7  $\mu$ F recommended, should be placed as close as possible to the V<sub>IN</sub> pin for optimal bypassing. X5R or X7R dielectrics are recommended for the input capacitor. Y5V dielectrics lose most of their capacitance over temperature and are therefore, not recommended. A minimum 1  $\mu$ F is recommended close to the V<sub>IN</sub> and PGND pins for high frequency filtering. Smaller case size capacitors are

recommended due to their lower ESR and ESL. Please refer to the PCB layout section for an example of an appropriate circuit layout.

#### 4.3 Inductor Selection

The MIC2810 is designed for use with a 2.2 µH inductor. Proper selection should ensure the inductor can handle the maximum average and peak currents required by the load. Maximum current ratings of the inductor are generally given in two methods; permissible DC current and saturation current. Permissible DC current can be rated either for a 40°C temperature rise or a 10% to 20% loss in inductance. Ensure that the inductor selected can handle the maximum operating current. When saturation current is specified, make sure that there is enough margin that the peak current will not saturate the inductor. Peak inductor current can be calculated as follows:

#### **EQUATION 4-1:**

$$I_{PK} = I_{OUT} + \frac{V_{OUT} \left( I - \frac{V_{OUT}}{V_{IN}} \right)}{2 \times f \times L}$$

Where:

I<sub>PK</sub> = Peak inductor current.

I<sub>OUT</sub> = Output/load current.

V<sub>IN</sub> = Input voltage.

$V_{OUT}$  = Output voltage.

f = Switching frequency of the PWM regulator.

L = Inductor value.

#### 4.4 POR Delay Time

The POR signal also goes low for the duration of the delay time given by Equation 3-1 when only one of the enable inputs (EN, EN1, EN2) transitions from low to high, with the others being already high and the corresponding output being in regulation. This is shown in Figure 2-30, Figure 2-31, and Figure 2-32. At the low-to-high transition of either enable input, the CSET pin capacitor is discharged to ground, and the POR delay time is restarted.

At start-up, in order to prevent a momentary HIGH glitch of the POR signal between subsequent enable commands, it is recommended to set the POR delay time longer than the maximum delay expected between the enable command signals plus the turn-on time  $t_{\mbox{\scriptsize TURN-ON}}.$

For a given delay between the enable signals, an example of correct POR delay time design is shown in Figure 2-33 and Figure 2-34. In Figure 2-33, it can be seen that the  $C_{SET}$  voltage is reset to ground by subsequent low-to-high enable signals transitions before it reaches the VTH $_{CSET}$  voltage (1.25V typ.), thus extending the duration of the POR LOW assertion (Figure 2-34).

#### 5.0 PACKAGING INFORMATION

#### 5.1 Package Marking Information

16-Pin QFN\*

| Part Number        | Code  |

|--------------------|-------|

| MIC2810-1JGMYML-TR | D1JGM |

| MIC2810-1J6JYML-TR | D1J6J |

| MIC2810-1J6SYML-TR | D1J6S |

| MIC2810-44MYML-TR  | YD44M |

| MIC2810-4GKYML-TR  | YD4GK |

| MIC2810-4GMYML-TR  | YD4GM |

| MIC2810-4GPYML-TR  | YD4GP |

| MIC2810-4GSYML-TR  | YD4GS |

| MIC2810-4LSYML-TR  | YD4LS |

| MIC2810-4MSYML-TR  | YD4MS |

| MIC2810-CGJYML-TR  | YDCGJ |

| MIC2810-FGSYML-TR  | YDFGS |

Refer to the Product Identification System section for information on the output voltage for each device.

Example

**Legend:** XX...X Product code or customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC® designator for Matte Tin (Sn)

\* This package is Pb-free. The Pb-free JEDEC designator (@3) can be found on the outer packaging for this package.

•, ▲, ▼ Pin one index is identified by a dot, delta up, or delta down (triangle mark).

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. Package may or may not include the corporate logo.

Underbar ( ) and/or Overbar ( ) symbol may not be to scale.

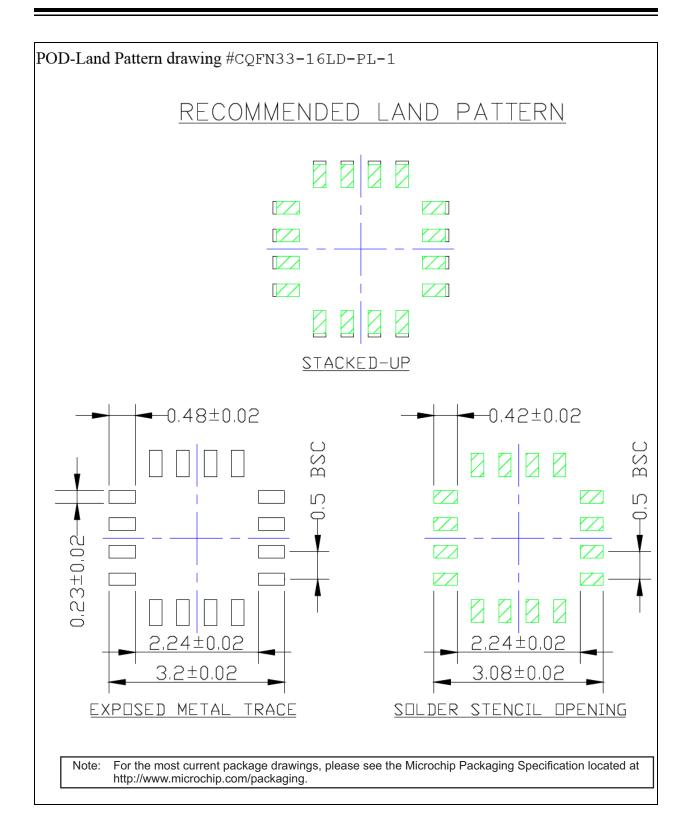

#### 16-Lead QFN 3 mm x 3 mm Package Outline and Recommended Land Pattern

# TITLE 16 LEAD QFN 3.0x3.0mm COL PACKAGE OUTLINE & RECOMMENDED LAND PATTERN DRAWING # UNIT CQFN33-16LD-PL-1 MM Lead Frame NiPdAu Lead Finish NiPdAu Pln 1 Dot By Marking $3.00 \pm 0.05$ PIN #1 IDENTIFICATION 0.23±0.05 0.50 $3.00 \pm 0.05$ 1.50 Ref Bsc 0.50±0.05 TOP VIEW **BOTTOM VIEW** $0.85 \pm 0.05$ 0.00-0.05 SIDE VIEW NOTES: ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES. N IS THE TOTAL NUMBER OF TERMINALS. 2. MAX PACKAGE WARPAGE IS 0.05mm, MAX ALLOWABLE BURRS IS 0.076 mm IN ALL DIRECTIONS. 3. PIN #1 ID ON TOP WILL BE LASER/INK MARKED. For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging.

NOTES:

## **APPENDIX A: REVISION HISTORY**

## **Revision A (November 2017)**

- Converted Micrel document MIC2810 to Microchip data sheet DS20005910A.

- Minor text changes throughout.

**NOTES:**

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

|                                            | (4)                                                                                                                                                                                              | Examples:                                                                                                                                                                                                                                                                    |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | XX X X - XX <sup>(1)</sup>                                                                                                                                                                       | a) MIC2810-44MYML-TR: Digital Power Management IC 2 MHz, 600 mA DC/DC with Dual 300 mA/300 mA Low VIN LDOs, 1.2V/1.2V/2.8V Output Voltage,                                                                                                                                   |

| Device:                                    | MIC2810: Digital Power Management IC 2 MHz, 600 mA DC/DC with Dual 300 mA/300 mA Low VIN LDOs                                                                                                    | b) MIC2810-4GMYML-TR: Digital Power Management IC 2 MHz, 600 mA DC/DC with Dual 300 mA/300 mA                                                                                                                                                                                |

| Output Voltages:<br>(DC/DC, LDO1,<br>LDO2) | 1JGM= 1.25V/1.8V/2.8V<br>1J6J = 1.25V/1.4V/2.5V<br>1J6S = 1.25V/1.4V/3.3V<br>44M = 1.2V/1.2V/2.8V<br>4GK = 1.2V/1.8V/2.6V<br>4GM= 1.2V/1.8V/3.0V<br>4GS = 1.2V/1.8V/3.3V<br>4LS = 1.2V/1.8V/3.3V | Low VIN LDOs, 1.2V/1.8V/2.8V Output Voltage, -40°C to +125°C 16LD QFN Package, 5,000/Reel Digital Power Management IC 2 MHz, 600 mA DC/DC with Dual 300 mA/300 mA Low VIN LDOs, 1.2V/1.8V/3.3V Output Voltage, -40°C to +125°C 16LD QFN Package, 5,000/Reel                  |

| Temperature:                               | 4MS = 1.2V/2.8V/3.3V<br>CGJ = 1.2V/1.8V/2.5V<br>FGS = 1.5V/1.8V/3.3V<br>Y = Pb-Free with Industrial Temperature Grade                                                                            | d) MIC2810-4MSYML-TR: Digital Power Management IC 2 MHz, 600 mA DC/DC with Dual 300 mA/300 mA Low VIN LDOs, 1.2V/2.8V/3.3V Output Voltage, –40°C to +125°C 16LD QFN Package, 5,000/Reel                                                                                      |

| Package: Tape and Reel:                    | $(-40^{\circ}\text{C to } + 125^{\circ}\text{C})$ $ML = 16-\text{lead}, 3 \text{ mm x } 3 \text{ mm QFN}, 0.85 \text{ mm thickness}$ $TR = 5.000/\text{Reel}$                                    | e) MIC2810-FGSYML-TR: Digital Power Management IC 2 MHz, 600 mA DC/DC with Dual 300 mA/300 mA Low VIN LDOs, 1.5V/1.8V/3.3V Output Voltage, -40°C to +125°C 16LD QFN Package, 5,000/Reel                                                                                      |

| rape and Neel.                             | TIX = 0,000/Nee/                                                                                                                                                                                 | Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option. |

**NOTES:**

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2017, Microchip Technology Incorporated, All Rights Reserved. ISBN: 978-1-5224-2428-4

## Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614

Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston** Westborough, MA

Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423

Fax: 972-818-7423 Fax: 972-818-2924 **Detroit**

Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Fax: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800 Raleigh, NC

Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

**China - Xian** Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu

Tel: 82-53-744-4301 **Korea - Seoul** Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

**Romania - Bucharest** Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820