# 3.5MHz, 500mA Synchronous Step Down DC-DC Regulator

#### **POWER MANAGEMENT**

#### **Features**

- Input Voltage 2.9V to 5.5V

- Output Voltage 0.8V to 3.3V

- Output current capability 500mA

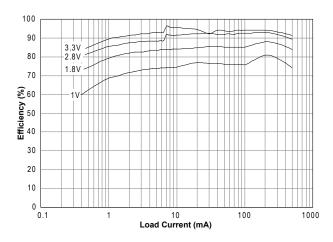

- Efficiency up to 94%

- 15 Programmable output voltages

- High light-load efficiency via automatic PSAVE mode

- Fast transient response

- Oscillator frequency 3.5MHz

- 100% duty cycle capability

- Quiescent current 38µA typ

- Shutdown Current 0.1µA typ

- Internal soft-start

- Over-voltage protection

- Current limit and short circuit protection

- Over-temperature protection

- Under-voltage lockout

- Floating control pin protection

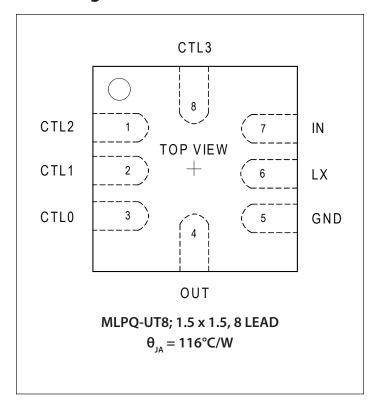

- MLPQ-UT8 1.5 x 1.5 x 0.6 (mm) package

- Pb free, halogen free, and RoHS/WEEE compliant

### **Applications**

- Smart phones and cellular phones

- MP3/Personal media players

- Personal navigation devices

- Digital cameras

- Single Li-ion cell or 3 NiMH/NiCd cell devices

- Devices with 3.3V or 5V internal power rails

### **Description**

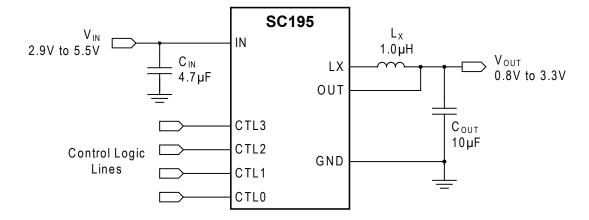

The SC195 is a high efficiency, 500mA step down regulator designed to operate with an input voltage range of 2.9V to 5.5 V. The input voltage range makes it ideal for battery operated applications with space limitations. The SC195 also includes fifteen programmable output voltage settings that can be selected using the four control pins, eliminating the need for external feedback resistors. The output voltage can be fixed to a single setting or dynamically switched between different levels. Pulling all four control pins low disables the output.

The SC195 operates at a fixed 3.5MHz switching frequency in normal PWM (Pulse-Width Modulation) mode. A variable frequency PSAVE (power-save) mode is used to optimize efficiency at light loads for each output setting. Built-in hysteresis prevents chattering between the two modes.

The SC195 provides several protection features to safeguard the device under stressed conditions. These include short circuit protection, over-temperature protection, under-voltage lockout, and soft-start to control in-rush current. These features, coupled with the small  $1.5 \times 1.5 \times 0.6$  (mm) package make the SC195 a versatile device ideal for step-down regulation in products needing high efficiency and a small PCB footprint.

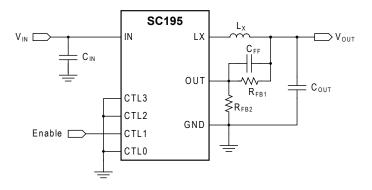

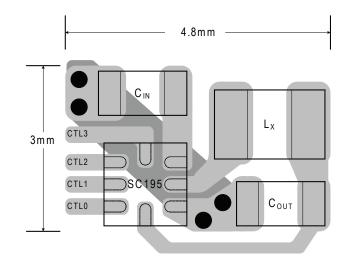

### **Typical Application Circuit**

### **Pin Configuration**

### **Ordering Information**

| Device                       | Package            |

|------------------------------|--------------------|

| SC195ULTRT <sup>(1)(2)</sup> | MLPQ-UT8 1.5 x 1.5 |

| SC195EVB                     | Evaluation Board   |

#### Notes:

- (1) Available in tape and reel only. A reel contains 3,000 devices.

- (2) Lead-free packaging only. Device is WEEE and RoHS compliant and halogen-free.

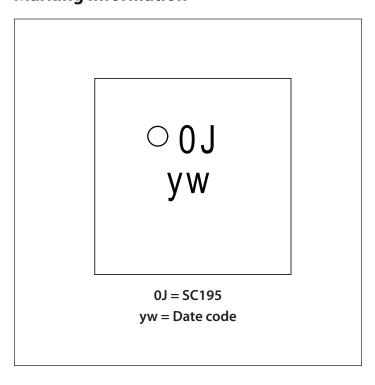

# **Marking Information**

**Table 1 – Output Voltage Settings**

| CTL3 | CTL2 | CTL1 | CTL0 | Vout     |

|------|------|------|------|----------|

| 0    | 0    | 0    | 0    | Shutdown |

| 0    | 0    | 0    | 1    | 0.80     |

| 0    | 0    | 1    | 0    | 1.00     |

| 0    | 0    | 1    | 1    | 1.20     |

| 0    | 1    | 0    | 0    | 1.40     |

| 0    | 1    | 0    | 1    | 1.50     |

| 0    | 1    | 1    | 0    | 1.60     |

| 0    | 1    | 1    | 1    | 1.80     |

| 1    | 0    | 0    | 0    | 1.85     |

| 1    | 0    | 0    | 1    | 1.90     |

| 1    | 0    | 1    | 0    | 2.00     |

| 1    | 0    | 1    | 1    | 2.20     |

| 1    | 1    | 0    | 0    | 2.50     |

| 1    | 1    | 0    | 1    | 2.80     |

| 1    | 1    | 1    | 0    | 3.00     |

| 1    | 1    | 1    | 1    | 3.30     |

### **Absolute Maximum Ratings**

| IN (V) -0.3 to +6.0                       |

|-------------------------------------------|

| LX Voltage (V)1.0 to V <sub>IN</sub> +0.5 |

| Other Pins (V)0.3 to $V_{IN} + 0.3$       |

| Output Short Circuit to GND Continuous    |

| ESD Protection Level <sup>(1)</sup> (kV)  |

### **Recommended Operating Conditions**

Input Voltage Range (V) . . . . . . . . . . . . +2.9 to +5.5

#### **Thermal Information**

| Thermal Resistance, Junction to Ambient $({}^{(2)}({}^{\circ}C/W)$ 116 |

|------------------------------------------------------------------------|

| Junction Temperature Range (°C)40 to +150                              |

| Storage Temperature Range (°C)65 to +150                               |

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

#### NOTES:

- (1) Tested according to JEDEC standard JESD22-A114.

- (2) Calculated from package in still air, mounted to 3 x 4.5 (in), 4 layer FR4 PCB per JESD51 standards.

#### **Electrical Characteristics**

Unless otherwise specified:  $V_{IN}$  = 3.6V,  $C_{IN}$  = 4.7 $\mu$ F,  $C_{OUT}$  = 10 $\mu$ F,  $L_{x}$  = 1 $\mu$ H,  $V_{OUT}$  = 1.8V,  $T_{J(MAX)}$  = 125°C,  $T_{A}$  = -40 to +85 °C. Typical values are  $T_{A}$  = +25 °C

| Parameter                                  | Symbol                  | Condition                                      | Min  | Тур | Max     | Units |

|--------------------------------------------|-------------------------|------------------------------------------------|------|-----|---------|-------|

| Output Voltage Range                       | V <sub>OUT</sub>        |                                                | 0.8  |     | 3.3 (1) | V     |

|                                            | .,                      | I <sub>OUT</sub> = 200mA                       | -2.0 |     | 2.0     | 0/    |

| Output Voltage Tolerance                   | V <sub>OUT_TOL</sub>    | PSAVE mode                                     |      | 1.5 |         | %     |

| Line Regulation                            | $\Delta V_{_{LINEREG}}$ | $2.9 \le V_{IN} \le 5.5V$ , $I_{OUT} = 200$ mA |      | 0.3 |         | %/V   |

| Load Regulation                            | $\Delta V_{LOADREG}$    | 200mA ≤ I <sub>OUT</sub> ≤ 500mA               |      | -1  |         | %/A   |

| Output Current Capability                  | I <sub>OUT</sub>        |                                                | 500  |     |         | mA    |

| Current Limit Threshold                    | I <sub>LIMIT</sub>      |                                                | 800  |     | 1300    | mA    |

| Foldback Current Limit                     | I <sub>FB_LIM</sub>     | I <sub>LOAD</sub> > I <sub>LIMIT</sub>         |      | 150 |         | mA    |

|                                            | .,                      | Rising V <sub>IN</sub>                         |      |     | 2.9     | V     |

| Under-Voltage Lockout                      | V <sub>UVLO</sub>       | Hysteresis                                     |      | 200 |         | mV    |

| Quiescent Current                          | I <sub>Q</sub>          | No switching, I <sub>OUT</sub> = 0mA           |      | 38  | 60      | μΑ    |

| Shutdown Current                           | I <sub>SD</sub>         | V <sub>CTL 0-3</sub> = 0V                      |      | 0.1 | 1.0     | μΑ    |

| LX Leakage Current                         | I <sub>LX</sub>         | Into LX pin                                    |      | 0.1 | 1.0     | μΑ    |

| High Side Switch Resistance <sup>(2)</sup> | R <sub>DSON_P</sub>     | I <sub>out</sub> = 100mA                       |      | 250 |         |       |

| Low Side Switch Resistance <sup>(3)</sup>  | R <sub>DSON_N</sub>     | I <sub>out</sub> = 100mA                       |      | 350 |         | mΩ    |

# **Electrical Characteristics (continued)**

| Parameter                              | Symbol            | Condition                              | Min  | Тур | Max | Units |

|----------------------------------------|-------------------|----------------------------------------|------|-----|-----|-------|

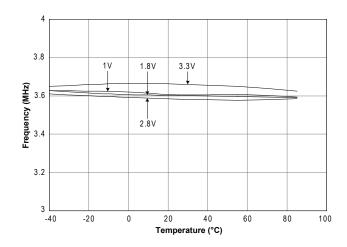

| Switching Frequency                    | f <sub>sw</sub>   |                                        | 2.8  | 3.5 | 4.2 | MHz   |

| Soft-Start                             | t <sub>ss</sub>   | V <sub>OUT</sub> = 90% of final value  |      | 100 | 500 | μs    |

| Thermal Shutdown                       | T <sub>ot</sub>   | Rising temperature                     |      | 160 |     | °C    |

| Thermal Shutdown Hysteresis            | T <sub>HYST</sub> |                                        |      | 20  |     | °C    |

| Logic Inputs - CTL0, CTL1, CTL2, and C | TL3               |                                        |      |     |     |       |

| Input High Voltage                     | V <sub>IH</sub>   |                                        | 1.2  |     |     | V     |

| Input Low Voltage                      | V <sub>IL</sub>   |                                        |      |     | 0.4 | V     |

| Input High Current                     | I <sub>IH</sub>   | V <sub>CTL 0-3</sub> = V <sub>IN</sub> | -2.0 |     | 5.0 | μΑ    |

| Input Low Current                      | I <sub>IL</sub>   | V <sub>CTL 0-3</sub> = GND             | -2.0 |     | 2.0 | μΑ    |

#### Notes

- (1) Maximum output voltage is limited to VIN if the input is less than 3.3V.

- (2) Measured from IN to LX.

- (3) Measured from LX to GND.

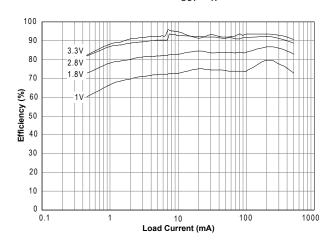

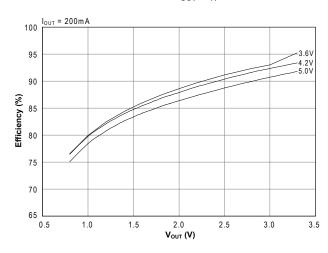

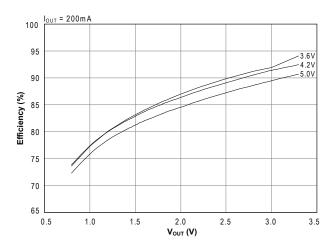

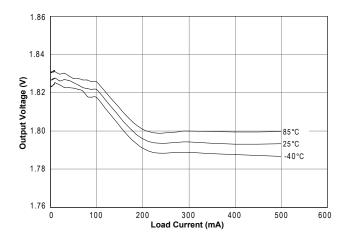

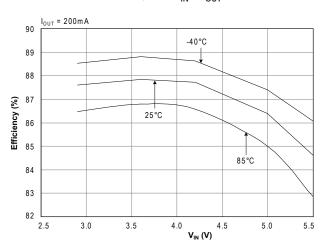

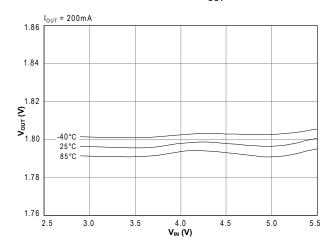

### **Typical Characteristics**

$V_{_{IN}}=4.0V~for~V_{_{OUT}}=3.3V, V_{_{IN}}=3.6V~for~all~others.~~C_{_{IN}}=4.7\mu F, C_{_{OUT}}=10\mu F, L_{_{X}}=1\mu H, T_{_{A}}=25^{\circ}C~unless~otherwise~noted.$

### Efficiency vs. $I_{OUT}$ ( $T_A = -40$ °C)

### Efficiency vs. $I_{OUT}$ ( $T_A = 25$ °C)

### Efficiency vs. $I_{OUT}$ ( $T_A = 85$ °C)

### Efficiency vs. $V_{OUT}$ ( $T_A = -40^{\circ}C$ )

### Efficiency vs. $V_{OUT}$ ( $T_A = 25$ °C)

### Efficiency vs. $V_{OUT}$ ( $T_A = 85^{\circ}C$ )

$V_{_{IN}}=4.0V~for~V_{_{OUT}}=3.3V, V_{_{IN}}=3.6V~for~all~others.~~C_{_{IN}}=4.7\mu F,~C_{_{OUT}}=10\mu F,~L_{_{X}}=1\mu H,~T_{_{A}}=25^{\circ}C~unless~otherwise~noted.$

### Frequency vs. Temperature

# Load Regulation ( $V_{OUT} = 1.8V$ )

# Efficiency vs. $V_{IN} (V_{OUT} = 1.8V)$

# Line Regulation (V<sub>OUT</sub>=1.8V)

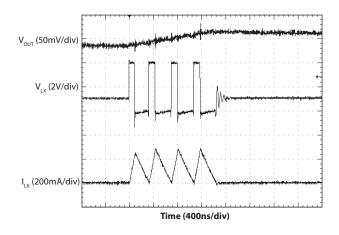

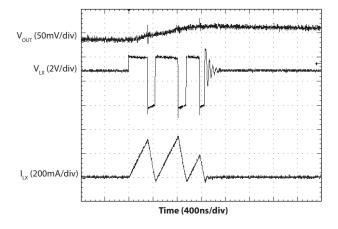

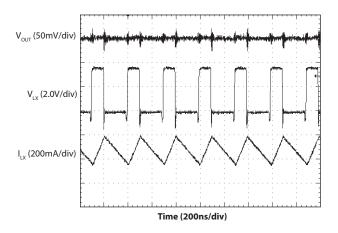

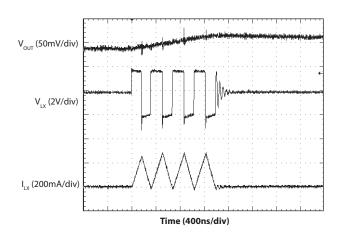

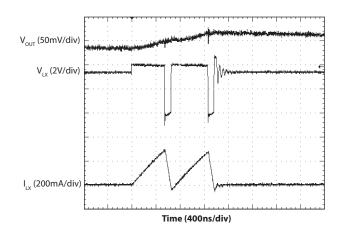

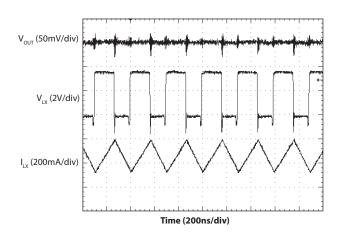

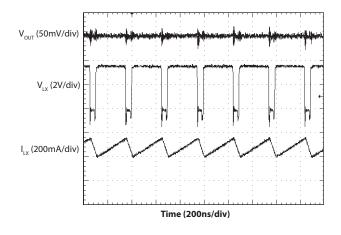

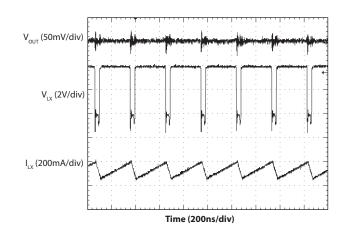

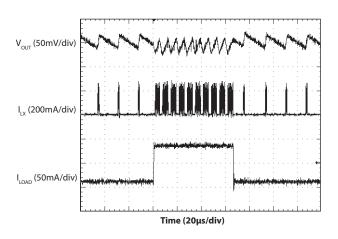

### $\textbf{Light Load Switching} - \textbf{V}_{\text{OUT}} = \textbf{1.0V}$

### $\textbf{Light Load Switching} - \textbf{V}_{\text{OUT}} = \textbf{2.8V}$

### Heavy Load Switching — $V_{OUT} = 1.0V$

### Light Load Switching — $V_{OUT} = 1.8V$

### Light Load Switching — $V_{OUT} = 3.3V$

# Heavy Load Switching — $V_{OUT} = 1.8V$

# Heavy Load Switching — $V_{OUT} = 2.8V$

### Heavy Load Switching — $V_{OUT} = 3.3V$

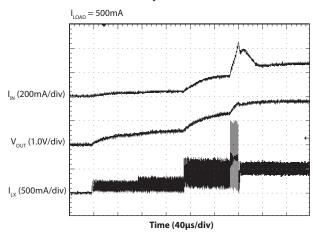

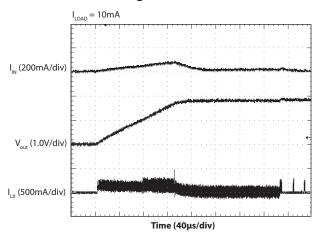

#### **Heavy Load Soft-start**

#### **Light Load Soft-start**

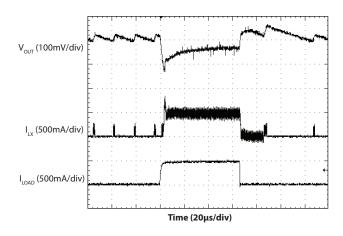

### Load Transient Response — 10 to 80mA

#### Load Transient Response — 10 to 500mA

#### Load Transient Response — 200 to 500mA

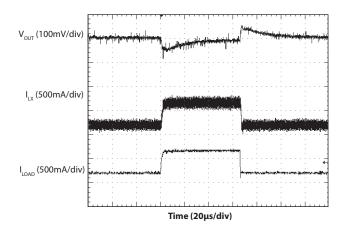

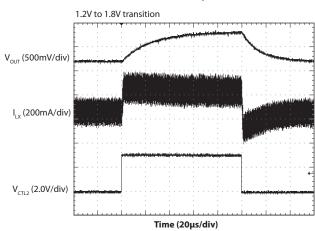

#### VID Transient Response — PWM

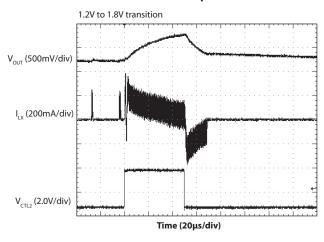

#### VID Transient Response — PSAVE

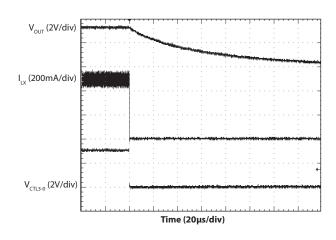

#### **Shutdown Transient Response**

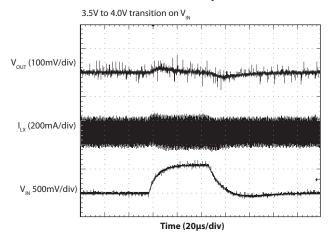

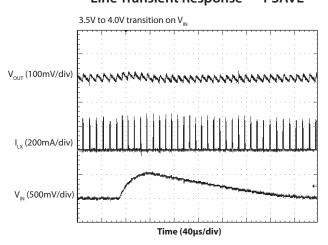

#### **Line Transient Response** — PWM

#### Line Transient Response — PSAVE

# **Pin Descriptions**

| Pin | Pin Name | Pin Function                                                                                                                                                                                    |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CTL2     | Control bit 2 — see Table 1, page 2, for decoding. This pin has a weak pull-down resistor (> $1M\Omega$ ) in place at reset that is removed when CTL2 is pulled above the logic high threshold. |

| 2   | CTL1     | Control bit 1 — see Table 1, page 2, for decoding. This pin has a weak pull-down resistor (> $1M\Omega$ ) in place at reset that is removed when CTL1 is pulled above the logic high threshold. |

| 3   | CTL0     | Control bit 0 — see Table 1, page 2, for decoding. This pin has a weak pull-down resistor (> $1M\Omega$ ) in place at reset that is removed when CTL0 is pulled above the logic high threshold. |

| 4   | OUT      | Output voltage sense pin — output voltage regulation point (connection node of inductor and output capacitor).                                                                                  |

| 5   | GND      | Ground reference and power ground for the SC195.                                                                                                                                                |

| 6   | LX       | Switching output — connect an inductor between this pin and the load to filter the pulsed output current.                                                                                       |

| 7   | IN       | Input power supply pin — connect a bypass capacitor from this pin to GND.                                                                                                                       |

| 8   | CTL3     | Control bit 3 — see Table 1, page 2, for decoding. This pin has a weak pull-down resistor (> $1M\Omega$ ) in place at reset that is removed when CTL3 is pulled above the logic high threshold. |

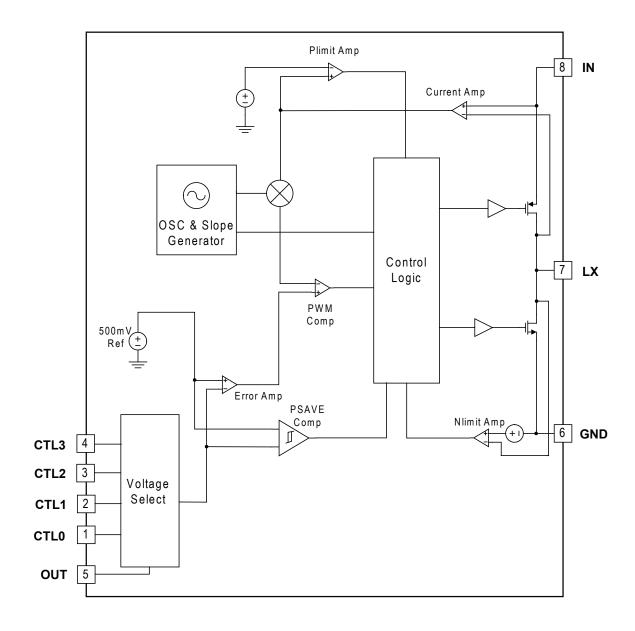

# **Block Diagram**

### **Applications Information**

#### **General Description**

The SC195 is a synchronous step-down Pulse Width Modulated (PWM) DC-DC regulator utilizing a 3.5MHz fixed-frequency voltage mode architecture. The device is designed to operate in fixed-frequency PWM mode and enter power save (PSAVE) mode utilizing pulse frequency modulation under light load conditions to maximize efficiency. The device requires only two capacitors and a single inductor to be implemented in most systems. The switching frequency has been chosen to minimize the size of the inductor and capacitors while maintaining high efficiency. The output voltage is programmable, eliminating the need for external programming resistors. Loop compensation is also internal, eliminating the need for external components to control stability.

### **Programmable Output Voltage**

The SC195 has 15 fixed output voltage levels which can be individually selected by programming the CTL control pins (CTL3-0 — see Table 1 on page 2 for settings). The device is disabled whenever all four CTL pins are pulled low and enabled whenever at least one of the CTL pins is pulled high. This configuration eliminates the need for a dedicated enable pin. Each CTL pin is internally pulled down via  $1 M\Omega$  if  $V_{\rm IN}$  is below 1.5V or if the voltage on the control pin is below the input high voltage. This ensures that the output is disabled when power is applied if there are no inputs to the CTL pins. Each weak pull-down is disabled whenever its pin is pulled high and remains disabled until all CTL pins are pulled low.

The output voltage can be set using different approaches. If a static output voltage is required, the CTL pins can be tied to either IN or GND to set the desired voltage whenever power is applied at IN. If enable control is required, each CTL pin can be tied to either GND or to a microprocessor I/O line to create the desired control code whenever the control signal is forced high. This approach is equivalent to using the CTL pins collectively as a single enable pin. A third option is to connect each of the four CTL pins to individual microprocessor I/O lines. Any of the 15 output voltages can be programmed using this approach. If only two output voltages are needed, the CTL pins can be combined in a way that will reduce the number of I/O lines to 1, 2, or 3, depending on the control code for each desired voltage. Other CTL pins could be hard wired to

GND or IN. This option allows dynamic voltage adjustment for systems that reduce the supply voltage when entering sleep states. Note that applying all zeros to the CTL pins when changing the output voltages will temporarily disable the device, so it is important to avoid this combination when dynamically changing levels.

#### **Adjustable Output Voltage Selection**

If an output voltage other than one of the 15 programmable settings is needed, an external resistor divider network can be added to the SC195 to adjust the output voltage setting. This network scales the output based on the resistor ratio and the programmed output setting. The resistor values can be determined using the equation

$$V_{\text{OUT}} = V_{\text{SET}} \times \left[ \frac{R_{\text{FB1}} + R_{\text{FB2}}}{R_{\text{FB2}}} \right] + I_{\text{LEAK}} \times R_{\text{FB1}}$$

where  $V_{OUT}$  is the desired output voltage,  $V_{SET}$  is the voltage setting selected by the CTL pins,  $R_{FB1}$  is the resistor between the output capacitor and the OUT pin,  $R_{FB2}$  is the resistor between the OUT pin and ground, and  $I_{LEAK}$  is the leakage current into the OUT pin during normal operation. The current into the OUT pin is typically  $1\mu A$ , so the last term of the equation can be neglected if the current through  $R_{FB2}$  is much larger than  $1\mu A$ . Selecting a resistor value of  $10k\Omega$  or lower will simplify the design. If  $I_{LEAK}$  is neglected and  $R_{FB2}$  is fixed,  $R_{FB1}$  can be determined using the equation

$$R_{\text{FB1}} = R_{\text{FB2}} \times \frac{V_{\text{OUT}} - V_{\text{SET}}}{V_{\text{SET}}}$$

Inserting resistance in the feedback loop will adversely affect the system's transient performance if feed-forward capacitance is not included in the circuit. The circuit in Figure 1 illustrates how the resistor divider and feed-forward capacitor can be added to the SC195 schematic. The value of feed-forward capacitance needed can be determined using the equation

$$C_{\text{FF}} = 4 \times 10^{-6} \times \frac{V_{\text{SET}} \big( V_{\text{OUT}} - 0.5 \big)^2}{R_{\text{FB1}} \big( V_{\text{OUT}} - V_{\text{SET}} \big) \big( V_{\text{SET}} - 0.5 \big)}$$

Figure 1 — Application Circuit with External Resistors

To simplify the design, it is recommended to program the output setting to 1.0V, use resistor values smaller than  $10k\Omega$ , and include a feed-forward capacitance calculated with the equation above. If the output voltage is set to 1.0V, the previous equation reduces to

$$C_{\text{FF}} = 8 \times 10^{-6} \times \frac{\left(V_{\text{OUT}} - 0.5\right)^2}{R_{\text{FR}_1}\left(V_{\text{OUT}} - 1\right)}$$

#### **Example:**

An output voltage of 1.3V is desired, but this is not a programmable option. What external component values for Figure 1 are needed?

Solution: To keep the circuit simple, set  $R_{FB2}$  to  $10k\Omega$  so current into the OUT pin can be neglected and set the CTL3-0 pins to 0010 (1.0V setting). The necessary component values for this situation are

$$R_{\text{FB1}} = R_{\text{FB2}} \times \frac{V_{\text{OUT}} - V_{\text{SET}}}{V_{\text{SFT}}} = 3k\Omega$$

$$C_{\text{FF}} = 8 \times 10^{-6} \times \frac{(V_{\text{OUT}} - 0.5)^2}{R_{\text{FB1}}(V_{\text{OUT}} - 1)} = 5.69 nF$$

#### **PWM Operation**

Normal PWM operation occurs when the output load current exceeds the PSAVE threshold. In this mode, the PMOS high side switch is activated with the duty cycle required to produce the output voltage programmed by the CTL pins. An internal synchronous NMOS rectifier eliminates the need for an external Schottky diode on the LX pin. The duty cycle (percentage of time PMOS is active)

increases as  $V_{\rm IN}$  decreases to maintain output voltage regulation. As the input voltage approaches the programmed output voltage, the duty cycle approaches 100% (PMOS always on) and the device enters a pass-through mode until the input voltage increases or the load decreases enough to allow PWM switching to resume.

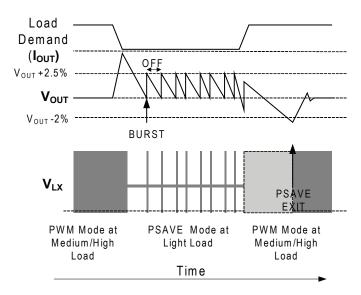

#### **Power Save Mode Operation**

When the load current decreases below the PSAVE threshold, PWM switching stops and the device automatically enters PSAVE mode. This threshold varies depending on the input voltage and output voltage setting, optimizing efficiency for all possible load currents in PWM or PSAVE mode. While in PSAVE mode, output voltage regulation is controlled by a series of switching bursts. During a burst, the inductor current is limited to a peak value which controls the on-time of the PMOS switch. After reaching this peak, the PMOS switch is disabled and the inductor current decreases to near 0mA. Switching bursts continue until the output voltage climbs to  $\rm V_{\scriptscriptstyle OUT}$  +2.5% or until the PSAVE current limit is reached. Switching is then stopped to eliminate switching losses, enhancing overall efficiency. Switching resumes when the output voltage reaches the lower threshold of  $V_{OUT}$ and continues until the upper threshold again is reached. Note that the output voltage is regulated hysteretically while in PSAVE mode between  $\rm V_{out}$  and  $\rm V_{out}$  + 2.5%. The period and duty cycle while in PSAVE mode are solely determined by  $V_{IN}$  and  $V_{OUT}$  until PWM mode resumes. This can result in the switching frequency being much lower than the PWM mode frequency.

If the output load current increases enough to cause  $V_{OUT}$  to decrease below the PSAVE exit threshold ( $V_{OUT}$  -2%), the device automatically exits PSAVE and operates in continuous PWM mode. Note that the PSAVE high and low threshold levels are both set at or above  $V_{OUT}$  to minimize undershoot when the SC195 exits PSAVE. Figure 2 illustrates the transitions from PWM mode to PSAVE mode and back to PWM mode.

Figure 2 — Transitions Between PWM and PSAVE Modes

#### **Protection Features**

The SC195 provides the following protection features:

- Soft-Start Operation

- Over-Voltage Protection

- Current Limit

- Thermal Shutdown

- Under-Voltage Lockout

#### **Soft-Start**

The soft-start sequence is activated after a transition from an all zeros CTL code to a non-zero CTL code enables the device. At start-up, the PMOS current limit is stepped through four levels: 25%, 40%, 60%, and 100%. Each step is maintained for 60µs following an internal reference start up of 20µs, resulting in a total nominal start-up period of 260µs. If  $V_{\text{OUT}}$  reaches 90% of the target within the first 2 steps, the device continues in PSAVE mode at the end of soft-start; otherwise, it goes into PWM mode. Note the  $V_{\text{OUT}}$  ripple in PSAVE mode can be larger than the ripple in PWM mode.

#### **Over-Voltage Protection**

Over-voltage protection ensures the output voltage does not rise to a level that could damage its load. When  $V_{\text{OUT}}$  exceeds the regulation voltage by 15%, the PWM drive is

disabled. Switching does not resume until  $V_{OUT}$  has fallen below the regulation voltage by 2%.

#### **Current Limit**

The SC195 switching stage is protected by a current limit function. If the output load exceeds the PMOS current limit for 32 consecutive switching cycles, the device enters fold-back current limit mode and the output current is limited to approximately 150mA. Under these conditions, the output voltage will be the product of I<sub>FB-LIM</sub> and the load resistance. The load must fall below I<sub>FB-LIM</sub> for the device to exit fold-back current limit mode. This function makes the device capable of sustaining an indefinite short circuit on its output under fault conditions.

#### Thermal Shutdown

The SC195 has a thermal shutdown feature to protect the device if the junction temperature exceeds 160°C. During thermal shutdown, the PMOS and NMOS switches are both disabled, tri-stating the LX output. When the junction temperature drops by the hysteresis value (20°C), the device goes through the soft-start process and resumes normal operation.

#### **Under-Voltage Lockout**

Under-Voltage Lockout (UVLO) activates when the supply voltage drops below the UVLO threshold. This prevents the device from entering an ambiguous state in which regulation cannot be maintained. Hysteresis of approximately 200mV is included to prevent chattering near the threshold.

#### **Inductor Selection**

The SC195 is designed to operate with a 1 $\mu$ H inductor between the LX pin and the OUT pin. Other values may lead to instability, malfunction, or out-of-specification performance. The specified current levels for PSAVE entry, PSAVE exit, and current limit are dependent on the inductor value.

The SC195 converter has internal loop compensation. The compensation is designed to work with a specific single-

pole output filter corner frequency defined by the equation

$$f_{\text{C}} = \frac{1}{2\pi\sqrt{L \times C_{\text{OUT}}}}$$

where  $L = 1\mu H$  and  $C_{OUT} = 10\mu F$ .

When selecting output filter components, the LC product should not vary over a wide range. Selection of smaller inductor and capacitor values will move the corner frequency, potentially impacting system stability.

It is also important to consider the change in inductance with DC bias current when choosing an inductor. The inductor saturation current is specified as the current at which the inductance drops a specific percentage from the nominal value (approximately 30%). Except for shortcircuit or other fault conditions, the peak current must always be less than the saturation current specified by the manufacturer. The peak current is the maximum load current plus one half of the inductor ripple current at the maximum input voltage. Load and/or line transients can cause the peak current to exceed this level for short durations. Maintaining the peak current below the inductor saturation specification keeps the inductor ripple current and the output voltage ripple at acceptable levels. Manufacturers often provide graphs of actual inductance and saturation characteristics versus applied inductor current. The saturation characteristics of the inductor can vary significantly with core temperature. Core and ambient temperatures should be considered when examining the core saturation characteristics.

When the inductor value has been determined, the DC resistance (DCR) must be examined. Efficiency can be optimized by lowering the inductor's DCR as much as possible. Low DCR in an inductor requires either more surface area for the increased wire diameter or fewer turns to reduce the length of the copper winding. Fewer turns requires an inductor core with a larger cross-sectional area in order to maintain the same saturation characteristics. The inductor size must always be considered when examining the inductor DCR to determine the best compromise between DCR and component area on a PCB. Note that

the ripple component of the inductor is a small percentage of the DC load. AC losses in the inductor core and winding do not contribute significantly to the total losses.

Magnetic fields associated with the output inductor can interfere with nearby circuitry. This can be minimized by the use of low-noise shielded inductors which use the minimum gap possible to limit the distance that magnetic fields can radiate from the inductor. Shielded inductors, however, typically have a higher DCR and are, therefore, less efficient than a similar sized non-shielded inductor.

Final inductor selection depends on various design considerations such as efficiency, EMI, size, and cost. Table 2 lists the manufacturers of recommended inductor options. The inductors with larger packages tend to provide better overall efficiency, while the smaller package inductors provide decent efficiency with reduced footprint or height. The saturation current ratings and DC characteristics are also shown.

Table 2 — Recommended Inductors

| Manufacturer<br>Part Number  | L<br>(μH) | DCR<br>(Ω) | Saturation<br>Current<br>(mA) | L at<br>400mA<br>(μH) | Dimensions<br>LxWxH<br>(mm) |

|------------------------------|-----------|------------|-------------------------------|-----------------------|-----------------------------|

| Murata<br>LQM21PN1R0MC0      | 1.0±20%   | 0.19       | 800                           | 0.75                  | 2.0x1.25x0.55               |

| Murata<br>LQM2HPN1R0MJ0      | 1.0±20%   | 0.09       | 1500                          | 0.95                  | 2.5x2.0x1.1                 |

| Murata<br>LQM31PN1R0M00      | 1.0±20%   | 0.12       | 1200                          | 0.95                  | 3.2x1.6x0.85                |

| Taiyo Yuden<br>CKP25201R0M-T | 1.0±20%   | 0.08       | 800                           | 0.88                  | 2.5x2.0x1.0                 |

| Toko<br>MDT2012-CR1R0N       | 1.0±30%   | 0.08       | 1350                          | 1.00                  | 2.0x1.25x1.0                |

| FDK<br>MIPSZ2012D1R0         | 1.0±30%   | 0.09       | 1100                          | 1.00                  | 2.0x1.25x1.0                |

| FDK<br>MIPSU2520D1R0         | 1.0±30%   | 0.08       | 1300                          | 0.78                  | 2.5x2.0x0.5                 |

| FDK<br>MIPSA2520D1R0         | 1.3±30%   | 0.09       | 1200                          | 1.20                  | 2.5x2.0x1.2                 |

| Taiyo Yuden<br>BRC1608T1R0M  | 1.0±20%   | 0.18       | 850                           | 0.90                  | 1.6x0.8x0.8                 |

### $C_{\text{out}}$ Selection

The internal voltage loop compensation in the SC195 limits the minimum output capacitor value to  $10\mu F$ . This is due to its influence on the the loop crossover frequency, phase margin, and gain margin. Increasing the output capacitor above this minimum value will reduce the crossover frequency and provide greater phase margin.

The output capacitor determines the output voltage ripple and contributes load current during large step load transitions. A capacitor between  $10\mu F$  and  $22\mu F$  will usually be adequate in stabilizing the output during large load transitions.

Capacitors with X7R or X5R ceramic dielectric are recommended for their low ESR and superior temperature and voltage characteristics. Y5V capacitors should not be used as their temperature coefficients make them unsuitable for this application.

In addition to ensuring stability, the output capacitor serves other important functions. This capacitor determines the output voltage ripple — as capacitance increases, ripple voltage decreases. It also supplies current during a large load step for a few switching cycles until the control loop responds (typically 3 switching cycles). Once the loop responds, regulation is restored and the desired output is reached. During the period prior to PWM operation resuming, the relationship between output voltage and output capacitance can be approximated using the equation

$$C_{\text{OUT}} = \frac{3 \times \Delta I_{\text{LOAD}}}{V_{\text{DROOP}} \times f}$$

This equation can be used to approximate the minimum output capacitance needed to ensure voltage does not droop below an acceptable level. For example, a load step from 50mA to 400mA requiring droop less than 50mV would require the minimum output capacitance to be

$$C_{\text{OUT}} = \frac{3 \times 0.4}{0.05 \times 4 \times 10^6} = 6.0 \mu F$$

In this example, using a standard  $10\mu F$  capacitor would be adequate to keep voltage droop less than the desired limit. Note that if the voltage droop limit were decreased from 50mV to 25mV, the output capacitance would need to be increased to at least  $12\mu F$  (twice as much capacitance for half the droop). Capacitance will decrease from the nominal value when a ceramic capacitor is biased with a DC current, so it is important to select a capacitor whose value exceeds the necessary capacitance value at the programmed output voltage. Check the manufacturer's capacitance vs. DC voltage graphs when selecting an output capacitor to ensure the capacitance will be adequate.

Table 3 lists the manufacturers of recommended output capacitor options.

Table 3 — Recommended Output Capacitors

| Manufacturer<br>Part Nunber    | Value<br>(μF) | Туре | Rated<br>Voltage<br>(VDC) | Dimensions<br>LxWxH (mm)<br>Case Size |

|--------------------------------|---------------|------|---------------------------|---------------------------------------|

| Murata<br>GRM188R60J106ME47D   | 10±20%        | X5R  | 6.3                       | 1.6x0.8x0.8<br>0603                   |

| Murata<br>GRM21BR60J106K       | 10±10%        | X5R  | 6.3                       | 2.0x1.25x1.25<br>0805                 |

| Taiyo Yuden<br>JMK107BJ106MA-T | 10±20%        | X5R  | 6.3                       | 1.6x0.8x0.8<br>0603                   |

| TDK<br>C1608X5R0J106MT         | 10±20%        | X5R  | 6.3                       | 1.6x0.8x0.8<br>0603                   |

### **C**<sub>IN</sub> Selection

The SC195 input source current will appear as a DC supply current with a triangular ripple imposed on it. To prevent large input voltage ripple, a low ESR ceramic capacitor is required. A minimum value of 4.7 $\mu$ F should be used. It is important to consider the DC voltage coefficient characteristics when determining the actual required value. For example, a 10 $\mu$ F, 6.3V, X5R ceramic capacitor with 5V DC applied may exhibit a capacitance as low as 4.5 $\mu$ F. The value of required input capacitance is estimated by determining the acceptable input ripple voltage and calculating the minimum value required for C $_{IN}$  using the equation

$$C_{\text{IN}} = \frac{\frac{V_{\text{OUT}}}{V_{\text{IN}}} \left( 1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}} \right)}{\left( \frac{\Delta V}{I_{\text{OUT}}} - \text{ESR} \right) f}$$

The input voltage ripple is at maximum level when the input voltage is twice the output voltage (50% duty cycle scenario).

The input capacitor provides a low impedance loop for the edges of pulsed current drawn by the PMOS switch. Low ESR/ESL X5R ceramic capacitors are recommended for this function. To minimize stray inductance, the capacitor should be placed as closely as possible to the IN and GND pins of the SC195. Table 4 lists the recommended input capacitor options from different manufacturers.

| Table 4 — | Recommended In | put Capacitors |

|-----------|----------------|----------------|

|-----------|----------------|----------------|

| Manufacturer<br>Part Nunber  | Value<br>(μF) | Туре | Rated<br>Voltage<br>(VDC) | Dimensions<br>LxWxH (mm)<br>Case Size |

|------------------------------|---------------|------|---------------------------|---------------------------------------|

| Murata<br>GRM188R60J475K     | 4.7±10%       | X5R  | 6.3                       | 1.6x0.8x0.8<br>0603                   |

| Murata<br>GRM188R60J106K     | 10±10%        | X5R  | 6.3                       | 1.6x0.8x0.8<br>0603                   |

| Taiyo Yuden<br>JMK107BJ475KA | 4.7±10%       | X5R  | 6.3                       | 1.6x0.8x0.8<br>0603                   |

| TDK<br>C1608X5R0J475KT       | 4.7±10%       | X5R  | 6.3                       | 1.6x0.8x0.8<br>0603                   |

#### **PCB Layout Considerations**

The layout diagram in Figure 3 shows a recommended PCB top-layer for the SC195 and supporting components. Specified layout rules must be followed since the layout is critical for achieving the performance specified in the Electrical Characteristics table. Poor layout can degrade the performance of the DC-DC converter and can contribute to EMI problems, ground bounce, and resistive voltage losses. Poor regulation and instability can result.

The following guidelines are recommended for designing a PCB layout:

C<sub>IN</sub> should be placed as close to the IN and GND pins as possible. This capacitor provides a low impedance loop for the pulsed currents present at the buck converter's input. Use short wide traces to minimize trace impedance. This will also minimize EMI and input voltage ripple by localizing the high frequency current pulses.

- 2. Keep the LX pin traces as short as possible to minimize pickup of high frequency switching edges to other parts of the circuit.  $C_{OUT}$  and  $L_X$  should be connected as close as possible between the LX and GND pins, with a direct return to the GND.

- 3. Use a ground plane referenced to the GND pin. Use several vias to connect to the component side ground to further reduce noise and interference on sensitive circuit nodes.

- 4. Route the output voltage feedback/sense path away from the inductor and LX node to minimize noise and magnetic interference.

- 5. Minimize the resistance from the OUT and GND pins to the load. This will reduce errors in DC regulation due to voltage drops in the traces.

Figure 3 — Recommended PCB Layout

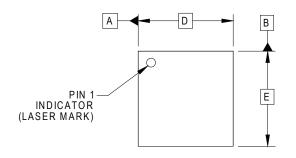

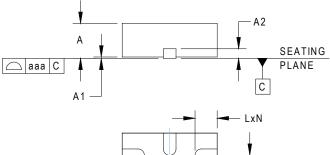

# Outline Drawing — MLPQ-UT8

|       | DIMENSIONS |        |      |          |        |      |  |

|-------|------------|--------|------|----------|--------|------|--|

| DIM L |            | NCHE   | S    | MILL     | IMET   | ERS  |  |

| DIIVI | MIN        | NOM    | MAX  | MIN      | NOM    | MAX  |  |

| Α     | .020       | -      | .024 | 0.50     | -      | 0.60 |  |

| A1    | .000       | -      | .002 | 0.00     | -      | 0.05 |  |

| A2    | (.006)     |        |      | (        | 0.1524 | )    |  |

| b     | .006       | .008   | .010 | 0.15     | 0.20   | 0.25 |  |

| D     | .(         | )59 BS | С    | 1.50 BSC |        |      |  |

| Е     | .(         | )59 BS | С    | 1        | .50 BS | С    |  |

| е     | .(         | 16 BS  | С    | 0.40 BSC |        |      |  |

| L     | 0.12       | .014   | 0.16 | 0.30     | 0.35   | 0.40 |  |

| N     | 8          |        |      |          | 8      |      |  |

| aaa   | .004       |        |      | 0.10     |        |      |  |

| bbb   |            | .004   |      |          | 0.10   |      |  |

#### NOTES:

1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

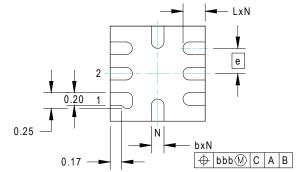

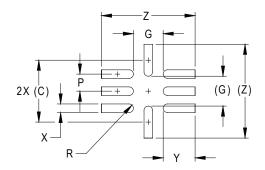

### Land Pattern — MLPQ-UT8

| DIMENSIONS |        |             |

|------------|--------|-------------|

| DIM        | INCHES | MILLIMETERS |

| С          | (.057) | (1.45)      |

| G          | .028   | 0.70        |

| Р          | .016   | 0.40        |

| R          | .004   | 0.10        |

| Χ          | .008   | 0.20        |

| Υ          | .030   | 0.75        |

| Z          | .087   | 2.20        |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY.

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR

COMPANY'S MANUFACTURING GUIDELINES ARE MET.

#### © Semtech 2015

All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights. Semtech assumes no responsibility or liability whatsoever for any failure or unexpected operation resulting from misuse, neglect improper installation, repair or improper handling or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified range.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

#### **Contact Information**

Semtech Corporation

Power Management Products Division

200 Flynn Road, Camarillo, CA 93012

Phone: (805) 498-2111 Fax: (805) 498-3804

www.semtech.com