# TMS320C80 **Digital Signal Processor**

## Data Sheet

Printed in U.S.A., October 1997 SPRS023B

SPRS023B - JULY 1994 - REVISED OCTOBER 1997

- Single-Chip Parallel Multiple Instruction/Multiple Data (MIMD) DSP

- More Than Two Billion RISC-Equivalent **Operations per Second**

- **Master Processor (MP)**

- 32-Bit Reduced Instruction Set Computing (RISC) Processor

- IEEE-754 Floating-Point Capability

- 4K-Byte Instruction Cache

- 4K-Byte Data Cache

- Four Parallel Processors (PP)

- 32-Bit Advanced DSPs

- 64-Bit Opcode Provides Many Parallel **Operations per Cycle**

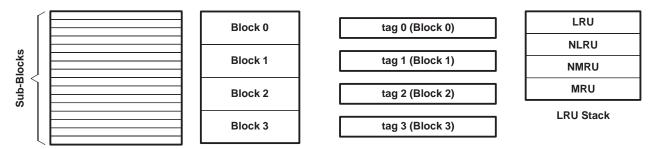

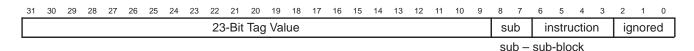

- 2K-Byte Instruction Cache and 8K-Byte Data RAM per PP

- Transfer Controller (TC)

- 64-Bit Data Transfers

- Up to 480M-Byte/s Transfer Rate

- 32-Bit Addressing

- Direct DRAM / VRAM Interface With **Dynamic Bus Sizing**

- Intelligent Queuing and Cycle **Prioritization**

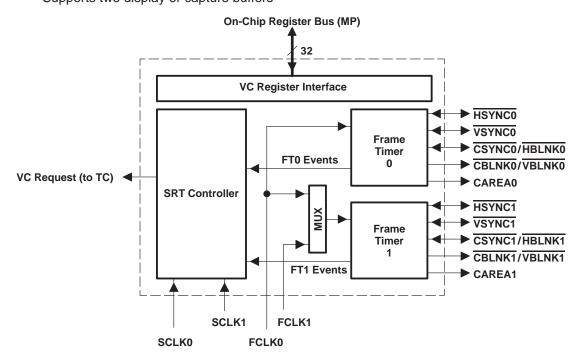

- Video Controller (VC)

- Provides Video Timing and VRAM Control

- Dual-Frame Timers for Two Simultaneous Image-Capture and / or Display Systems

- **Big- or Little-Endian Operation**

- 50K-Byte On-Chip RAM

- **4G-Byte Address Space**

- 16.6-ns Cycle Time

- 3.3-V Operation

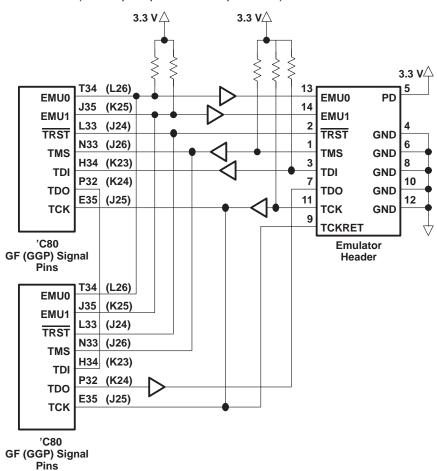

- IEEE Standard 1149.1<sup>†</sup> Test Access Port (JTAG)

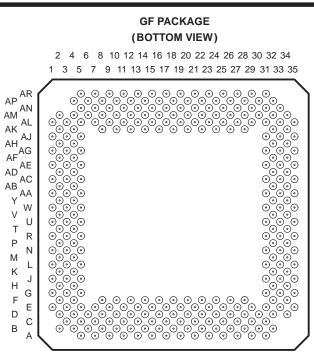

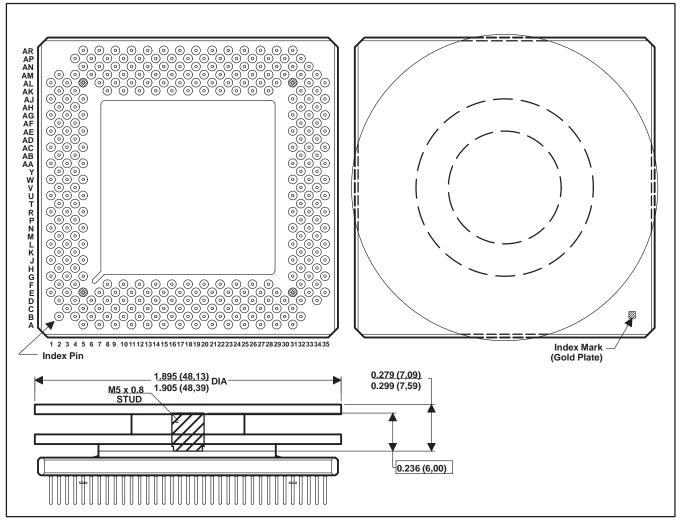

#### **GGP PACKAGE** (BOTTOM VIEW)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

† IEEE Standard 1149.1–1990, IEEE Standard Test Access Port and Boundary-Scan Architecture

#### TMS320C80 DIGITAL SIGNAL PROCESSOR

SPRS023B - JULY 1994 - REVISED OCTOBER 1997

#### description

The TMS320C80 is a single chip, MIMD parallel processor capable of performing over two billion operations per second. It consists of a 32-bit RISC master processor with a 120-MFLOP IEEE floating-point unit, four 32-bit parallel processing digital signal processors (DSPs), a transfer controller with up to 480M-byte/s off-chip transfer rate, and a video controller. All the processors are coupled tightly through an on-chip crossbar that provides shared access to on-chip RAM. This performance and programmability make the 'C80 ideally suited for video, imaging, and high-speed telecommunications applications.

#### **GF Terminal Assignments – Numerical Listing**

|     | TERMINAL        |     | TERMINAL        |     | TERMINAL        | TE  | RMINAL          |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| NO. | NAME            | NO. | NAME            | NO. | NAME            | NO. | NAME            |

| A5  | CT1             | C21 | $V_{DD}$        | E33 | HSYNC0          | L5  | $V_{SS}$        |

| A7  | $V_{DD}$        | C23 | W               | E35 | TCK             | L31 | $V_{SS}$        |

| A9  | HACK            | C25 | DBEN            | F2  | $V_{DD}$        | L33 | TRST            |

| A11 | Vss             | C27 | V <sub>SS</sub> | F4  | V <sub>SS</sub> | L35 | XPT1            |

| A13 | CAS/DQM7        | C29 | CAREA0          | F8  | $V_{DD}$        | M2  | $V_{DD}$        |

| A15 | CAS/DQM5        | C31 | CBLNK0 / VBLNK0 | F10 | V <sub>SS</sub> | M4  | V <sub>SS</sub> |

| A17 | $V_{DD}$        | D2  | RETRY           | F12 | $V_{DD}$        | M32 | V <sub>SS</sub> |

| A19 | V <sub>SS</sub> | D4  | $V_{DD}$        | F14 | PS0             | M34 | $V_{DD}$        |

| A21 | RAS             | D6  | $V_{SS}$        | F16 | $V_{SS}$        | N1  | $V_{DD}$        |

| A23 | DSF             | D8  | AS0             | F18 | CT2             | N3  | A8              |

| A25 | Vss             | D10 | UTIME           | F20 | $V_{DD}$        | N5  | VSS             |

| A27 | SCLK1           | D12 | V <sub>SS</sub> | F22 | V <sub>SS</sub> | N31 | Vss             |

| A29 | $V_{DD}$        | D14 | RESET           | F24 | $V_{DD}$        | N33 | TMS             |

| A31 | EINT1           | D16 | REQ0            | F26 | V <sub>SS</sub> | N35 | $V_{DD}$        |

| B2  | No Connect      | D18 | V <sub>SS</sub> | F28 | $V_{DD}$        | P2  | A4              |

| B4  | BS1             | D20 | CAS/DQM0        | F32 | Vss             | P4  | A9              |

| В6  | $V_{DD}$        | D22 | FCLK1           | F34 | $V_{DD}$        | P32 | TDO             |

| B8  | PS1             | D24 | Vss             | G1  | $V_{DD}$        | P34 | XPT0            |

| B10 | REQ1            | D26 | CAREA1          | G3  | A2              | R1  | VSS             |

| B12 | $V_{DD}$        | D28 | SCLK0           | G5  | A1              | R3  | $V_{DD}$        |

| B14 | CAS/DQM6        | D30 | V <sub>SS</sub> | G31 | EINT2           | R5  | $V_{DD}$        |

| B16 | CAS/DQM3        | D32 | $V_{DD}$        | G33 | CBLNK1 / VBLNK1 | R31 | $V_{DD}$        |

| B18 | $V_{DD}$        | D34 | VSYNC0          | G35 | $V_{DD}$        | R33 | $V_{DD}$        |

| B20 | CAS/DQM1        | E1  | AS1             | H2  | STATUS0         | R35 | Vss             |

| B22 | TRG/CAS         | E3  | FAULT           | H4  | A3              | T2  | A5              |

| B24 | $V_{DD}$        | E5  | V <sub>SS</sub> | H32 | CSYNC1 / HBLNK1 | T4  | A13             |

| B26 | DDIN            | E7  | STATUS2         | H34 | TDI             | T32 | D62             |

| B28 | FCLK0           | E9  | READY           | J1  | STATUS1         | T34 | EMU0            |

| B30 | $V_{DD}$        | E11 | BS0             | J3  | V <sub>SS</sub> | U1  | $V_{DD}$        |

| B32 | CSYNC0 / HBLNK0 | E13 | V <sub>SS</sub> | J5  | $V_{DD}$        | U3  | A10             |

| C3  | Vss             | E15 | HREQ            | J31 | $V_{DD}$        | U5  | PS3             |

| C5  | STATUS3         | E17 | CAS/DQM4        | J33 | V <sub>SS</sub> | U31 | FF1             |

| C7  | AS2             | E19 | RL              | J35 | EMU1            | U33 | D61             |

| C9  | $V_{SS}$        | E21 | STATUS5         | K2  | STATUS4         | U35 | $V_{DD}$        |

| C11 | CT0             | E23 | V <sub>SS</sub> | K4  | A6              | V2  | $V_{DD}$        |

| C13 | PS2             | E25 | CLKOUT          | K32 | VSYNC1          | V4  | V <sub>SS</sub> |

| C15 | $V_{DD}$        | E27 | LINT4           | K34 | HSYNC1          | V32 | V <sub>SS</sub> |

| C17 | CLKIN           | E29 | EINT3           | L1  | A0              | V34 | $V_{DD}$        |

| C19 | CAS/DQM2        | E31 | Vss             | L3  | A7              | W1  | A11             |

#### **GF Terminal Assignments – Numerical Listing (Continued)**

| TER  | TERMINAL        |      | VINAL           | TERM | IINAL           | TERI | MINAL           |

|------|-----------------|------|-----------------|------|-----------------|------|-----------------|

| NO.  | NAME            | NO.  | NAME            | NO.  | NAME            | NO.  | NAME            |

| W3   | A18             | AG1  | A16             | AL17 | D20             | AN29 | D35             |

| W5   | V <sub>SS</sub> | AG3  | V <sub>SS</sub> | AL19 | D21             | AN31 | D45             |

| W31  | V <sub>SS</sub> | AG5  | $V_{DD}$        | AL21 | D24             | AN33 | $V_{DD}$        |

| W33  | D59             | AG31 | $V_{DD}$        | AL23 | VSS             | AP4  | A27             |

| W35  | D63             | AG33 | Vss             | AL25 | D29             | AP6  | $V_{DD}$        |

| Y2   | A12             | AG35 | D57             | AL27 | D32             | AP8  | D5              |

| Y4   | A19             | AH2  | A20             | AL29 | D38             | AP10 | D8              |

| Y32  | XPT2            | AH4  | A30             | AL31 | V <sub>SS</sub> | AP12 | $V_{DD}$        |

| Y34  | D56             | AH32 | D44             | AL33 | D48             | AP14 | D13             |

| AA1  | V <sub>SS</sub> | AH34 | D54             | AL35 | D53             | AP16 | D17             |

| AA3  | V <sub>DD</sub> | AJ1  | $V_{DD}$        | AM2  | A24             | AP18 | V <sub>DD</sub> |

| AA5  | $V_{DD}$        | AJ3  | A31             | AM4  | $V_{DD}$        | AP20 | D26             |

| AA31 | $V_{DD}$        | AJ5  | Vss             | AM6  | VSS             | AP22 | D34             |

| AA33 | $V_{DD}$        | AJ31 | V <sub>SS</sub> | AM8  | D2              | AP24 | $V_{DD}$        |

| AA35 | V <sub>SS</sub> | AJ33 | D42             | AM10 | D6              | AP26 | D39             |

| AB2  | A14             | AJ35 | $V_{DD}$        | AM12 | VSS             | AP28 | D41             |

| AB4  | A21             | AK2  | $V_{DD}$        | AM14 | D14             | AP30 | V <sub>DD</sub> |

| AB32 | D55             | AK4  | V <sub>SS</sub> | AM16 | D19             | AP32 | D47             |

| AB34 | D60             | AK8  | V <sub>DD</sub> | AM18 | V <sub>SS</sub> | AR5  | D0              |

| AC1  | V <sub>DD</sub> | AK10 | V <sub>SS</sub> | AM20 | D23             | AR7  | V <sub>DD</sub> |

| AC3  | A22             | AK12 | $V_{DD}$        | AM22 | D25             | AR9  | D7              |

| AC5  | V <sub>SS</sub> | AK14 | V <sub>SS</sub> | AM24 | V <sub>SS</sub> | AR11 | VSS             |

| AC31 | V <sub>SS</sub> | AK16 | $V_{DD}$        | AM26 | D31             | AR13 | D11             |

| AC33 | D52             | AK18 | FF2             | AM28 | D33             | AR15 | D15             |

| AC35 | $V_{DD}$        | AK20 | Vss             | AM30 | V <sub>SS</sub> | AR17 | VSS             |

| AD2  | $V_{DD}$        | AK22 | D27             | AM32 | $V_{DD}$        | AR19 | $V_{DD}$        |

| AD4  | V <sub>SS</sub> | AK24 | $V_{DD}$        | AM34 | D50             | AR21 | D30             |

| AD32 | V <sub>SS</sub> | AK26 | V <sub>SS</sub> | AN5  | A29             | AR23 | D36             |

| AD34 | V <sub>DD</sub> | AK28 | $V_{DD}$        | AN7  | D1              | AR25 | V <sub>SS</sub> |

| AE1  | A15             | AK32 | V <sub>SS</sub> | AN9  | V <sub>SS</sub> | AR27 | D40             |

| AE3  | A26             | AK34 | $V_{DD}$        | AN11 | D9              | AR29 | V <sub>DD</sub> |

| AE5  | V <sub>SS</sub> | AL1  | A23             | AN13 | D12             | AR31 | D43             |

| AE31 | V <sub>SS</sub> | AL3  | A25             | AN15 | V <sub>DD</sub> |      |                 |

| AE33 | D51             | AL5  | V <sub>SS</sub> | AN17 | D18             |      |                 |

| AE35 | D58             | AL7  | D3              | AN19 | D22             |      |                 |

| AF2  | A17             | AL9  | D4              | AN21 | V <sub>DD</sub> |      |                 |

| AF4  | A28             | AL11 | D10             | AN23 | D28             |      |                 |

| AF32 | D46             | AL13 | V <sub>SS</sub> | AN25 | D37             |      |                 |

| AF34 | D49             | AL15 | D16             | AN27 | VSS             |      |                 |

#### **GF Terminal Assignments – Alphabetical Listing**

| TERM   | MINAL | TERMINA       | L    | TERM | IINAL | TERM    | ERMINAL |  |

|--------|-------|---------------|------|------|-------|---------|---------|--|

| NAME   | NO.   | NAME          | NO.  | NAME | NO.   | NAME    | NO.     |  |

| A0     | L1    | CAS/DQM0      | D20  | D22  | AN19  | D61     | U33     |  |

| A1     | G5    | CAS/DQM1      | B20  | D23  | AM20  | D62     | T32     |  |

| A2     | G3    | CAS/DQM2      | C19  | D24  | AL21  | D63     | W35     |  |

| A3     | H4    | CAS/DQM3      | B16  | D25  | AM22  | DBEN    | C25     |  |

| A4     | P2    | CAS/DQM4      | E17  | D26  | AP20  | DDIN    | B26     |  |

| A5     | T2    | CAS/DQM5      | A15  | D27  | AK22  | DSF     | A23     |  |

| A6     | K4    | CAS/DQM6      | B14  | D28  | AN23  | EINT1   | A31     |  |

| A7     | L3    | CAS/DQM7      | A13  | D29  | AL25  | EINT2   | G31     |  |

| A8     | N3    | CBLNK0/VBLNK0 | C31  | D30  | AR21  | EINT3   | E29     |  |

| A9     | P4    | CBLNK1/VBLNK1 | G33  | D31  | AM26  | EMU0    | T34     |  |

| A10    | U3    | CLKIN         | C17  | D32  | AL27  | EMU1    | J35     |  |

| A11    | W1    | CLKOUT        | E25  | D33  | AM28  | FAULT   | E3      |  |

| A12    | Y2    | CSYNC0/HBLNK0 | B32  | D34  | AP22  | FCLK0   | B28     |  |

| A13    | T4    | CSYNC1/HBLNK1 | H32  | D35  | AN29  | FCLK1   | D22     |  |

| A14    | AB2   | СТО           | C11  | D36  | AR23  | FF1     | U31     |  |

| A15    | AE1   | CT1           | A5   | D37  | AN25  | FF2     | AK18    |  |

| A16    | AG1   | CT2           | F18  | D38  | AL29  | HACK    | A9      |  |

| A17    | AF2   | D0            | AR5  | D39  | AP26  | HREQ    | E15     |  |

| A18    | W3    | D1            | AN7  | D40  | AR27  | HSYNC0  | E33     |  |

| A19    | Y4    | D2            | AM8  | D41  | AP28  | HSYNC1  | K34     |  |

| A20    | AH2   | D3            | AL7  | D42  | AJ33  | LINT4   | E27     |  |

| A21    | AB4   | D4            | AL9  | D43  | AR31  | PS0     | F14     |  |

| A22    | AC3   | D5            | AP8  | D44  | AH32  | PS1     | B8      |  |

| A23    | AL1   | D6            | AM10 | D45  | AN31  | PS2     | C13     |  |

| A24    | AM2   | D7            | AR9  | D46  | AF32  | PS3     | U5      |  |

| A25    | AL3   | D8            | AP10 | D47  | AP32  | RAS     | A21     |  |

| A26    | AE3   | D9            | AN11 | D48  | AL33  | READY   | E9      |  |

| A27    | AP4   | D10           | AL11 | D49  | AF34  | REQ0    | D16     |  |

| A28    | AF4   | D11           | AR13 | D50  | AM34  | REQ1    | B10     |  |

| A29    | AN5   | D12           | AN13 | D51  | AE33  | RESET   | D14     |  |

| A30    | AH4   | D13           | AP14 | D52  | AC33  | RETRY   | D2      |  |

| A31    | AJ3   | D14           | AM14 | D53  | AL35  | RL      | E19     |  |

| AS0    | D8    | D15           | AR15 | D54  | AH34  | SCLK0   | D28     |  |

| AS1    | E1    | D16           | AL15 | D55  | AB32  | SCLK1   | A27     |  |

| AS2    | C7    | D17           | AP16 | D56  | Y34   | STATUS0 | H2      |  |

| BS0    | E11   | D18           | AN17 | D57  | AG35  | STATUS1 | J1      |  |

| BS1    | B4    | D19           | AM16 | D58  | AE35  | STATUS2 | E7      |  |

| CAREA0 | C29   | D20           | AL17 | D59  | W33   | STATUS3 | C5      |  |

| CAREA1 | D26   | D21           | AL19 | D60  | AB34  | STATUS4 | K2      |  |

#### **GF Terminal Assignments – Alphabetical Listing (Continued)**

| TERM     | INAL | TERM     | IINAL | TERM            | /INAL | TERM            | /INAL |

|----------|------|----------|-------|-----------------|-------|-----------------|-------|

| NAME     | NO.  | NAME     | NO.   | NAME            | NO.   | NAME            | NO.   |

| STATUS5  | E21  | $V_{DD}$ | R31   | $V_{DD}$        | AR29  | V <sub>SS</sub> | AA35  |

| TCK      | E35  | $V_{DD}$ | R33   | V <sub>SS</sub> | A11   | V <sub>SS</sub> | AC5   |

| TDI      | H34  | $V_{DD}$ | U1    | V <sub>SS</sub> | A19   | VSS             | AC31  |

| TDO      | P32  | $V_{DD}$ | U35   | V <sub>SS</sub> | A25   | V <sub>SS</sub> | AD4   |

| TMS      | N33  | $V_{DD}$ | V2    | V <sub>SS</sub> | C3    | VSS             | AD32  |

| TRG/CAS  | B22  | $V_{DD}$ | V34   | V <sub>SS</sub> | C9    | Vss             | AE5   |

| TRST     | L33  | $V_{DD}$ | AA3   | V <sub>SS</sub> | C27   | V <sub>SS</sub> | AE31  |

| UTIME    | D10  | $V_{DD}$ | AA5   | V <sub>SS</sub> | D6    | V <sub>SS</sub> | AG3   |

| $V_{DD}$ | A7   | $V_{DD}$ | AA31  | V <sub>SS</sub> | D12   | V <sub>SS</sub> | AG33  |

| $V_{DD}$ | A17  | $V_{DD}$ | AA33  | V <sub>SS</sub> | D18   | Vss             | AJ5   |

| $V_{DD}$ | A29  | $V_{DD}$ | AC1   | V <sub>SS</sub> | D24   | Vss             | AJ31  |

| $V_{DD}$ | B6   | $V_{DD}$ | AC35  | V <sub>SS</sub> | D30   | Vss             | AK4   |

| $V_{DD}$ | B12  | $V_{DD}$ | AD2   | V <sub>SS</sub> | E5    | Vss             | AK10  |

| $V_{DD}$ | B18  | $V_{DD}$ | AD34  | V <sub>SS</sub> | E13   | V <sub>SS</sub> | AK14  |

| $V_{DD}$ | B24  | $V_{DD}$ | AG5   | V <sub>SS</sub> | E23   | V <sub>SS</sub> | AK20  |

| $V_{DD}$ | B30  | $V_{DD}$ | AG31  | V <sub>SS</sub> | E31   | VSS             | AK26  |

| $V_{DD}$ | C15  | $V_{DD}$ | AJ1   | V <sub>SS</sub> | F4    | V <sub>SS</sub> | AK32  |

| $V_{DD}$ | C21  | $V_{DD}$ | AJ35  | V <sub>SS</sub> | F10   | V <sub>SS</sub> | AL5   |

| $V_{DD}$ | D4   | $V_{DD}$ | AK2   | V <sub>SS</sub> | F16   | Vss             | AL13  |

| $V_{DD}$ | D32  | $V_{DD}$ | AK8   | VSS             | F22   | Vss             | AL23  |

| $V_{DD}$ | F2   | $V_{DD}$ | AK12  | V <sub>SS</sub> | F26   | V <sub>SS</sub> | AL31  |

| $V_{DD}$ | F8   | $V_{DD}$ | AK16  | V <sub>SS</sub> | F32   | Vss             | AM6   |

| $V_{DD}$ | F12  | $V_{DD}$ | AK24  | V <sub>SS</sub> | J3    | Vss             | AM12  |

| $V_{DD}$ | F20  | $V_{DD}$ | AK28  | V <sub>SS</sub> | J33   | VSS             | AM18  |

| $V_{DD}$ | F24  | $V_{DD}$ | AK34  | V <sub>SS</sub> | L5    | VSS             | AM24  |

| $V_{DD}$ | F28  | $V_{DD}$ | AM4   | V <sub>SS</sub> | L31   | VSS             | AM30  |

| $V_{DD}$ | F34  | $V_{DD}$ | AM32  | V <sub>SS</sub> | M4    | VSS             | AN9   |

| $V_{DD}$ | G1   | $V_{DD}$ | AN15  | V <sub>SS</sub> | M32   | V <sub>SS</sub> | AN27  |

| $V_{DD}$ | G35  | $V_{DD}$ | AN21  | V <sub>SS</sub> | N5    | VSS             | AR11  |

| $V_{DD}$ | J5   | $V_{DD}$ | AN33  | V <sub>SS</sub> | N31   | VSS             | AR17  |

| $V_{DD}$ | J31  | $V_{DD}$ | AP6   | V <sub>SS</sub> | R1    | VSS             | AR25  |

| $V_{DD}$ | M2   | $V_{DD}$ | AP12  | V <sub>SS</sub> | R35   | VSYNC0          | D34   |

| $V_{DD}$ | M34  | $V_{DD}$ | AP18  | V <sub>SS</sub> | V4    | VSYNC1          | K32   |

| $V_{DD}$ | N1   | $V_{DD}$ | AP24  | V <sub>SS</sub> | V32   | W               | C23   |

| $V_{DD}$ | N35  | $V_{DD}$ | AP30  | V <sub>SS</sub> | W5    | XPT0            | P34   |

| $V_{DD}$ | R3   | $V_{DD}$ | AR7   | V <sub>SS</sub> | W31   | XPT1            | L35   |

| $V_{DD}$ | R5   | $V_{DD}$ | AR19  | VSS             | AA1   | XPT2            | Y32   |

#### **GGP Terminal Assignments – Numerical Listing**

| Т   | ERMINAL         | Т   | ERMINAL    | Т   | ERMINAL         | TERMINAL |                 |  |

|-----|-----------------|-----|------------|-----|-----------------|----------|-----------------|--|

| NO. | NAME            | NO. | NAME       | NO. | NAME            | NO.      | NAME            |  |

| A1  | No Connect      | B1  | No Connect | C1  | No Connect      | D1       | A0              |  |

| A2  | No Connect      | B2  | No Connect | C2  | No Connect      | D2       | $V_{DD}$        |  |

| А3  | No Connect      | В3  | No Connect | C3  | No Connect      | D3       | STATUS4         |  |

| A4  | STATUS1         | B4  | STATUS2    | C4  | Vss             | D4       | STATUS3         |  |

| A5  | AS1             | B5  | AS2        | C5  | STATUS0         | D5       | $V_{DD}$        |  |

| A6  | RETRY           | B6  | READY      | C6  | FAULT           | D6       | AS0             |  |

| A7  | CT1             | B7  | BS0        | C7  | BS1             | D7       | UTIME           |  |

| A8  | PS0             | B8  | PS1        | C8  | PS2             | D8       | CT0             |  |

| A9  | $V_{DD}$        | В9  | HACK       | C9  | HREQ            | D9       | RESET           |  |

| A10 | V <sub>SS</sub> | B10 | Vss        | C10 | Vss             | D10      | REQ1            |  |

| A11 | V <sub>SS</sub> | B11 | $V_{DD}$   | C11 | $V_{DD}$        | D11      | REQ0            |  |

| A12 | $V_{DD}$        | B12 | CAS/DQM7   | C12 | CLKIN           | D12      | $V_{DD}$        |  |

| A13 | No Connect      | B13 | No Connect | C13 | Vss             | D13      | CAS/DQM6        |  |

| A14 | No Connect      | B14 | Vss        | C14 | CAS/DQM5        | D14      | $V_{DD}$        |  |

| A15 | $V_{DD}$        | B15 | CAS/DQM4   | C15 | CAS/DQM3        | D15      | CT2             |  |

| A16 | CAS/DQM2        | B16 | Vss        | C16 | CAS/DQM1        | D16      | $V_{DD}$        |  |

| A17 | CAS/DQM0        | B17 | RL         | C17 | V <sub>SS</sub> | D17      | V <sub>SS</sub> |  |

| A18 | V <sub>SS</sub> | B18 | RAS        | C18 | $V_{DD}$        | D18      | TRG/CAS         |  |

| A19 | FCLK1           | B19 | $V_{DD}$   | C19 | W               | D19      | STATUS5         |  |

| A20 | $V_{DD}$        | B20 | DSF        | C20 | V <sub>SS</sub> | D20      | DBEN            |  |

| A21 | $V_{DD}$        | B21 | DDIN       | C21 | CLKOUT          | D21      | CAREA1          |  |

| A22 | V <sub>SS</sub> | B22 | SCLK1      | C22 | $V_{DD}$        | D22      | FCLK0           |  |

| A23 | V <sub>SS</sub> | B23 | SCLK0      | C23 | $V_{DD}$        | D23      | CAREA0          |  |

| A24 | No Connect      | B24 | No Connect | C24 | No Connect      | D24      | LINT4           |  |

| A25 | No Connect      | B25 | No Connect | C25 | No Connect      | D25      | EINT3           |  |

| A26 | No Connect      | B26 | No Connect | C26 | No Connect      | D26      | EINT2           |  |

#### **GGP Terminal Assignments – Numerical Listing (Continued)**

|     | TERMINAL        |     | ERMINAL         | Т   | ERMINAL         | TEI  | TERMINAL        |  |  |

|-----|-----------------|-----|-----------------|-----|-----------------|------|-----------------|--|--|

| NO. | NAME            | NO. | NAME            | NO. | NAME            | NO.  | NAME            |  |  |

| E1  | A3              | J23 | HSYNC0          | P1  | No Connect      | V23  | D52             |  |  |

| E2  | A2              | J24 | TRST            | P2  | No Connect      | V24  | V <sub>SS</sub> |  |  |

| E3  | V <sub>SS</sub> | J25 | TCK             | P3  | Vss             | V25  | V <sub>SS</sub> |  |  |

| E4  | A1              | J26 | TMS             | P4  | V <sub>SS</sub> | V26  | D53             |  |  |

| E23 | EINT1           | K1  | A12             | P23 | V <sub>SS</sub> | W1   | A24             |  |  |

| E24 | CBLNK1/VBLNK1   | K2  | $V_{DD}$        | P24 | D59             | W2   | V <sub>SS</sub> |  |  |

| E25 | CBLNK0/VBLNK0   | K3  | A11             | P25 | $V_{DD}$        | W3   | V <sub>SS</sub> |  |  |

| E26 | V <sub>SS</sub> | K4  | V <sub>SS</sub> | P26 | No Connect      | W4   | V <sub>SS</sub> |  |  |

| F1  | A4              | K23 | TDI             | R1  | V <sub>SS</sub> | W23  | D49             |  |  |

| F2  | $V_{DD}$        | K24 | TDO             | R2  | A17             | W24  | D50             |  |  |

| F3  | $V_{DD}$        | K25 | EMU1            | R3  | A18             | W25  | D51             |  |  |

| F4  | $V_{DD}$        | K26 | XPT0            | R4  | V <sub>SS</sub> | W26  | $V_{DD}$        |  |  |

| F23 | V <sub>SS</sub> | L1  | $V_{DD}$        | R23 | XPT2            | Y1   | A25             |  |  |

| F24 | CSYNC1/HBLNK1   | L2  | A13             | R24 | D57             | Y2   | A26             |  |  |

| F25 | $V_{DD}$        | L3  | V <sub>SS</sub> | R25 | $V_{DD}$        | Y3   | A27             |  |  |

| F26 | CSYNC0/HBLNK0   | L4  | V <sub>SS</sub> | R26 | D58             | Y4   | $V_{DD}$        |  |  |

| G1  | $V_{SS}$        | L23 | XPT1            | T1  | A19             | Y23  | $V_{DD}$        |  |  |

| G2  | V <sub>SS</sub> | L24 | V <sub>SS</sub> | T2  | $V_{DD}$        | Y24  | D48             |  |  |

| G3  | A5              | L25 | V <sub>SS</sub> | T3  | $V_{DD}$        | Y25  | V <sub>SS</sub> |  |  |

| G4  | $V_{SS}$        | L26 | EMU0            | T4  | A20             | Y26  | $V_{SS}$        |  |  |

| G23 | VSYNC1          | M1  | $V_{DD}$        | T23 | $V_{DD}$        | AA1  | $V_{DD}$        |  |  |

| G24 | VSYNC0          | M2  | A15             | T24 | $V_{DD}$        | AA2  | $V_{DD}$        |  |  |

| G25 | V <sub>SS</sub> | М3  | PS3             | T25 | D56             | AA3  | A28             |  |  |

| G26 | V <sub>SS</sub> | M4  | A14             | T26 | V <sub>SS</sub> | AA4  | V <sub>SS</sub> |  |  |

| H1  | A8              | M23 | $V_{DD}$        | U1  | V <sub>SS</sub> | AA23 | D45             |  |  |

| H2  | $V_{DD}$        | M24 | D63             | U2  | V <sub>SS</sub> | AA24 | D46             |  |  |

| H3  | A7              | M25 | D62             | U3  | A21             | AA25 | D47             |  |  |

| H4  | A6              | M26 | D61             | U4  | $V_{DD}$        | AA26 | $V_{DD}$        |  |  |

| H23 | HSYNC1          | N1  | No Connect      | U23 | $V_{DD}$        | AB1  | V <sub>SS</sub> |  |  |

| H24 | $V_{DD}$        | N2  | A16             | U24 | D54             | AB2  | A29             |  |  |

| H25 | $V_{DD}$        | N3  | $V_{DD}$        | U25 | V <sub>SS</sub> | AB3  | A30             |  |  |

| H26 | $V_{DD}$        | N4  | $V_{DD}$        | U26 | D55             | AB4  | V <sub>SS</sub> |  |  |

| J1  | A10             | N23 | V <sub>SS</sub> | V1  | A22             | AB23 | $V_{DD}$        |  |  |

| J2  | $V_{DD}$        | N24 | D60             | V2  | A23             | AB24 | D44             |  |  |

| J3  | A9              | N25 | No Connect      | V3  | $V_{DD}$        | AB25 | V <sub>SS</sub> |  |  |

| J4  | V <sub>SS</sub> | N26 | No Connect      | V4  | $V_{DD}$        | AB26 | V <sub>SS</sub> |  |  |

### **GGP Terminal Assignments – Numerical Listing (Continued)**

| TE   | TERMINAL TER    |      | ERMINAL         | TE   | TERMINAL TERMINAL |      |                 |  |

|------|-----------------|------|-----------------|------|-------------------|------|-----------------|--|

| NO.  | NAME            | NO.  | NAME            | NO.  | NAME              | NO.  | NAME            |  |

| AC1  | A31             | AD1  | No Connect      | AE1  | No Connect        | AF1  | No Connect      |  |

| AC2  | $V_{DD}$        | AD2  | No Connect      | AE2  | No Connect        | AF2  | No Connect      |  |

| AC3  | $V_{DD}$        | AD3  | No Connect      | AE3  | No Connect        | AF3  | No Connect      |  |

| AC4  | D0              | AD4  | V <sub>SS</sub> | AE4  | D1                | AF4  | D2              |  |

| AC5  | D3              | AD5  | $V_{DD}$        | AE5  | D4                | AF5  | V <sub>SS</sub> |  |

| AC6  | V <sub>SS</sub> | AD6  | D5              | AE6  | D6                | AF6  | D7              |  |

| AC7  | $V_{DD}$        | AD7  | $V_{DD}$        | AE7  | D8                | AF7  | $V_{SS}$        |  |

| AC8  | D9              | AD8  | D10             | AE8  | D11               | AF8  | $V_{DD}$        |  |

| AC9  | D12             | AD9  | $V_{SS}$        | AE9  | D13               | AF9  | D14             |  |

| AC10 | $V_{DD}$        | AD10 | $V_{DD}$        | AE10 | D15               | AF10 | V <sub>SS</sub> |  |

| AC11 | D16             | AD11 | V <sub>SS</sub> | AE11 | V <sub>SS</sub>   | AF11 | D17             |  |

| AC12 | D18             | AD12 | D19             | AE12 | $V_{DD}$          | AF12 | $V_{DD}$        |  |

| AC13 | D20             | AD13 | V <sub>SS</sub> | AE13 | $V_{SS}$          | AF13 | No Connect      |  |

| AC14 | $V_{DD}$        | AD14 | D21             | AE14 | No Connect        | AF14 | No Connect      |  |

| AC15 | D24             | AD15 | $V_{DD}$        | AE15 | D23               | AF15 | D22             |  |

| AC16 | D27             | AD16 | D26             | AE16 | D25               | AF16 | V <sub>SS</sub> |  |

| AC17 | V <sub>SS</sub> | AD17 | $V_{SS}$        | AE17 | D28               | AF17 | $V_{DD}$        |  |

| AC18 | D31             | AD18 | D30             | AE18 | $V_{DD}$          | AF18 | D29             |  |

| AC19 | $V_{DD}$        | AD19 | $V_{DD}$        | AE19 | D32               | AF19 | VSS             |  |

| AC20 | D35             | AD20 | D34             | AE20 | D33               | AF20 | $V_{SS}$        |  |

| AC21 | D37             | AD21 | $V_{SS}$        | AE21 | D36               | AF21 | $V_{DD}$        |  |

| AC22 | D40             | AD22 | $V_{DD}$        | AE22 | D39               | AF22 | D38             |  |

| AC23 | D42             | AD23 | D41             | AE23 | V <sub>SS</sub>   | AF23 | V <sub>SS</sub> |  |

| AC24 | D43             | AD24 | No Connect      | AE24 | No Connect        | AF24 | No Connect      |  |

| AC25 | $V_{DD}$        | AD25 | No Connect      | AE25 | No Connect        | AF25 | No Connect      |  |

| AC26 | $V_{DD}$        | AD26 | No Connect      | AE26 | No Connect        | AF26 | No Connect      |  |

#### **GGP Terminal Assignments – Alphabetical Listing**

| TERMINAL | TERMINAL |               |      | TERMIN | IAL  | TERMINA | AL  |

|----------|----------|---------------|------|--------|------|---------|-----|

| NAME     | NO.      | NAME          | NO.  | NAME   | NO.  | NAME    | NO. |

| A0       | D1       | CAS/DQM0      | A17  | D22    | AF15 | D61     | M26 |

| A1       | E4       | CAS/DQM1      | C16  | D23    | AE15 | D62     | M25 |

| A2       | E2       | CAS/DQM2      | A16  | D24    | AC15 | D63     | M24 |

| A3       | E1       | CAS/DQM3      | C15  | D25    | AE16 | DBEN    | D20 |

| A4       | F1       | CAS/DQM4      | B15  | D26    | AD16 | DDIN    | B21 |

| A5       | G3       | CAS/DQM5      | C14  | D27    | AC16 | DSF     | B20 |

| A6       | H4       | CAS/DQM6      | D13  | D28    | AE17 | EINT1   | E23 |

| A7       | НЗ       | CAS/DQM7      | B12  | D29    | AF18 | EINT2   | D26 |

| A8       | H1       | CBLNK0/VBLNK0 | E25  | D30    | AD18 | EINT3   | D25 |

| A9       | J3       | CBLNK1/VBLNK1 | E24  | D31    | AC18 | EMU0    | L26 |

| A10      | J1       | CLKIN         | C12  | D32    | AE19 | EMU1    | K25 |

| A11      | K3       | CLKOUT        | C21  | D33    | AE20 | FAULT   | C6  |

| A12      | K1       | CSYNC0/HBLNK0 | F26  | D34    | AD20 | FCLK0   | D22 |

| A13      | L2       | CSYNC1/HBLNK1 | F24  | D35    | AC20 | FCLK1   | A19 |

| A14      | M4       | CT0           | D8   | D36    | AE21 | HACK    | В9  |

| A15      | M2       | CT1           | A7   | D37    | AC21 | HREQ    | C9  |

| A16      | N2       | CT2           | D15  | D38    | AF22 | HSYNC0  | J23 |

| A17      | R2       | D0            | AC4  | D39    | AE22 | HSYNC1  | H23 |

| A18      | R3       | D1            | AE4  | D40    | AC22 | LINT4   | D24 |

| A19      | T1       | D2            | AF4  | D41    | AD23 | PS0     | A8  |

| A20      | T4       | D3            | AC5  | D42    | AC23 | PS1     | B8  |

| A21      | U3       | D4            | AE5  | D43    | AC24 | PS2     | C8  |

| A22      | V1       | D5            | AD6  | D44    | AB24 | PS3     | M3  |

| A23      | V2       | D6            | AE6  | D45    | AA23 | RAS     | B18 |

| A24      | W1       | D7            | AF6  | D46    | AA24 | READY   | B6  |

| A25      | Y1       | D8            | AE7  | D47    | AA25 | REQ0    | D11 |

| A26      | Y2       | D9            | AC8  | D48    | Y24  | REQ1    | D10 |

| A27      | Y3       | D10           | AD8  | D49    | W23  | RESET   | D9  |

| A28      | AA3      | D11           | AE8  | D50    | W24  | RETRY   | A6  |

| A29      | AB2      | D12           | AC9  | D51    | W25  | RL      | B17 |

| A30      | AB3      | D13           | AE9  | D52    | V23  | SCLK0   | B23 |

| A31      | AC1      | D14           | AF9  | D53    | V26  | SCLK1   | B22 |

| AS0      | D6       | D15           | AE10 | D54    | U24  | STATUS0 | C5  |

| AS1      | A5       | D16           | AC11 | D55    | U26  | STATUS1 | A4  |

| AS2      | B5       | D17           | AF11 | D56    | T25  | STATUS2 | B4  |

| BS0      | B7       | D18           | AC12 | D57    | R24  | STATUS3 | D4  |

| BS1      | C7       | D19           | AD12 | D58    | R26  | STATUS4 | D3  |

| CAREA0   | D23      | D20           | AC13 | D59    | P24  | STATUS5 | D19 |

| CAREA1   | D21      | D21           | AD14 | D60    | N24  |         |     |

#### **GGP Terminal Assignments – Alphabetical Listing (Continued)**

| TERMINA          | AL  | TERMIN   | IAL  | TERMINAL TERM   |     | TERMINA         | MINAL |  |

|------------------|-----|----------|------|-----------------|-----|-----------------|-------|--|

| NAME             | NO. | NAME     | NO.  | NAME            | NO. | NAME            | NO.   |  |

| TCK              | J25 | $V_{DD}$ | P25  | V <sub>SS</sub> | A10 | V <sub>SS</sub> | U25   |  |

| TDI              | K23 | $V_{DD}$ | R25  | $V_{SS}$        | A11 | $V_{SS}$        | V24   |  |

| TDO              | K24 | $V_{DD}$ | T2   | V <sub>SS</sub> | A18 | V <sub>SS</sub> | V25   |  |

| TMS              | J26 | $V_{DD}$ | T3   | V <sub>SS</sub> | A22 | V <sub>SS</sub> | W2    |  |

| TRG/CAS          | D18 | $V_{DD}$ | T23  | V <sub>SS</sub> | A23 | V <sub>SS</sub> | W3    |  |

| TRST             | J24 | $V_{DD}$ | T24  | V <sub>SS</sub> | B10 | V <sub>SS</sub> | W4    |  |

| UTIME            | D7  | $V_{DD}$ | U4   | V <sub>SS</sub> | B14 | V <sub>SS</sub> | Y25   |  |

| $V_{DD}$         | A9  | $V_{DD}$ | U23  | V <sub>SS</sub> | B16 | V <sub>SS</sub> | Y26   |  |

| $V_{DD}$         | A12 | $V_{DD}$ | V3   | Vss             | C4  | V <sub>SS</sub> | AA4   |  |

| $V_{DD}$         | A15 | $V_{DD}$ | V4   | Vss             | C10 | V <sub>SS</sub> | AB1   |  |

| $V_{DD}$         | A20 | $V_{DD}$ | W26  | Vss             | C13 | V <sub>SS</sub> | AB4   |  |

| $V_{DD}$         | A21 | $V_{DD}$ | Y4   | VSS             | C17 | V <sub>SS</sub> | AB25  |  |

| $V_{DD}$         | B11 | $V_{DD}$ | Y23  | V <sub>SS</sub> | C20 | V <sub>SS</sub> | AB26  |  |

| $V_{DD}$         | B19 | $V_{DD}$ | AA1  | V <sub>SS</sub> | D17 | V <sub>SS</sub> | AC6   |  |

| $V_{	extsf{DD}}$ | C11 | $V_{DD}$ | AA2  | V <sub>SS</sub> | E3  | V <sub>SS</sub> | AC17  |  |

| $V_{	extsf{DD}}$ | C18 | $V_{DD}$ | AA26 | V <sub>SS</sub> | E26 | V <sub>SS</sub> | AD4   |  |

| $V_{DD}$         | C22 | $V_{DD}$ | AB23 | V <sub>SS</sub> | F23 | V <sub>SS</sub> | AD9   |  |

| $V_{DD}$         | C23 | $V_{DD}$ | AC2  | V <sub>SS</sub> | G1  | V <sub>SS</sub> | AD11  |  |

| $V_{DD}$         | D2  | $V_{DD}$ | AC3  | V <sub>SS</sub> | G2  | V <sub>SS</sub> | AD13  |  |

| $V_{ m DD}$      | D5  | $V_{DD}$ | AC7  | V <sub>SS</sub> | G4  | V <sub>SS</sub> | AD17  |  |

| $V_{	extsf{DD}}$ | D12 | $V_{DD}$ | AC10 | V <sub>SS</sub> | G25 | V <sub>SS</sub> | AD21  |  |

| $V_{DD}$         | D14 | $V_{DD}$ | AC14 | V <sub>SS</sub> | G26 | V <sub>SS</sub> | AE11  |  |

| $V_{DD}$         | D16 | $V_{DD}$ | AC19 | V <sub>SS</sub> | J4  | V <sub>SS</sub> | AE13  |  |

| $V_{DD}$         | F2  | $V_{DD}$ | AC25 | Vss             | K4  | V <sub>SS</sub> | AE23  |  |

| $V_{DD}$         | F3  | $V_{DD}$ | AC26 | V <sub>SS</sub> | L3  | V <sub>SS</sub> | AF5   |  |

| $V_{DD}$         | F4  | $V_{DD}$ | AD5  | V <sub>SS</sub> | L4  | V <sub>SS</sub> | AF7   |  |

| $V_{DD}$         | F25 | $V_{DD}$ | AD7  | V <sub>SS</sub> | L24 | V <sub>SS</sub> | AF10  |  |

| $V_{DD}$         | H2  | $V_{DD}$ | AD10 | $V_{SS}$        | L25 | $V_{SS}$        | AF16  |  |

| $V_{DD}$         | H24 | $V_{DD}$ | AD15 | VSS             | N23 | V <sub>SS</sub> | AF19  |  |

| $V_{DD}$         | H25 | $V_{DD}$ | AD19 | VSS             | P3  | V <sub>SS</sub> | AF20  |  |

| $V_{DD}$         | H26 | $V_{DD}$ | AD22 | V <sub>SS</sub> | P4  | V <sub>SS</sub> | AF23  |  |

| $V_{DD}$         | J2  | $V_{DD}$ | AE12 | V <sub>SS</sub> | P23 | VSYNC0          | G24   |  |

| $V_{DD}$         | K2  | $V_{DD}$ | AE18 | V <sub>SS</sub> | R1  | VSYNC1          | G23   |  |

| $V_{DD}$         | L1  | $V_{DD}$ | AF8  | V <sub>SS</sub> | R4  | W               | C19   |  |

| $V_{DD}$         | M1  | $V_{DD}$ | AF12 | V <sub>SS</sub> | T26 | XPT0            | K26   |  |

| $V_{DD}$         | M23 | $V_{DD}$ | AF17 | V <sub>SS</sub> | U1  | XPT1            | L23   |  |

| $V_{DD}$         | N3  | $V_{DD}$ | AF21 | V <sub>SS</sub> | U2  | XPT2            | R23   |  |

| $V_{DD}$         | N4  |          |      |                 |     |                 |       |  |

#### **Terminal Functions**

| TERMINAL              | TVDET | DESCRIPTION                                                                                                                                                                                                        |

|-----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | TYPET | LOCAL MEMORY INTERFACE                                                                                                                                                                                             |

| A31-A0                | 0     | Address bus. A31–A0 output the 32-bit byte address of the external memory cycle. The address can be multiplexed for DRAM accesses.                                                                                 |

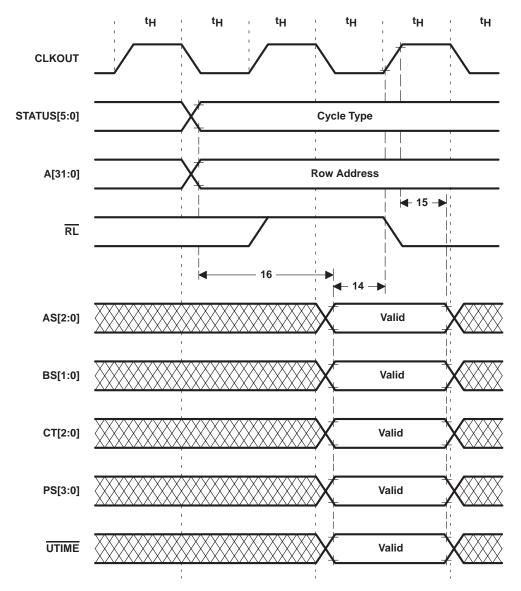

| AS2-AS0               | I     | Address-shift selection. AS2 – AS0 determine how the column address appears on the address bus. Eight shift values are supported, including zero.                                                                  |

| BS1-BS0               | I     | Bus-size selection. BS1 – BS0 indicate the bus size of the memory or other device being accessed, allowing dynamic bus sizing for data buses less than 64-bits wide.                                               |

| CT2-CT0               | I     | Cycle-timing selection. CT2 – CT0 signals determine the timing of the current memory access.                                                                                                                       |

| D63-D0                | I/O   | Data bus. D63-D0 transfer up to 64 bits of data per memory cycle into or out of the 'C80.                                                                                                                          |

| DBEN                  | 0     | Data-buffer enable. DBEN drives the active-low output-enables of bi-directional transceivers that can be used to buffer input and output data on D63-D0.                                                           |

| DDIN                  | 0     | Data-direction indicator. DDIN indicates the direction of the data that passes through the transceivers. When DDIN is low, the transfer is from external memory into the 'C80.                                     |

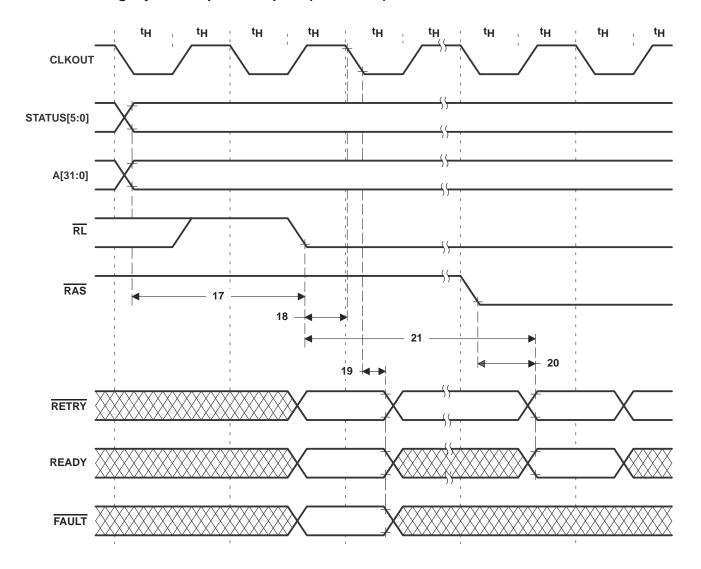

| FAULT                 | I     | Fault. FAULT is driven low by external circuitry to inform the 'C80 that a fault has occurred on the current memory row-access.                                                                                    |

| PS3-PS0               | I     | Page-size indication. PS3-PS0 indicate the page size of the memory device(s) being accessed by the current cycle. The 'C80 uses this information to determine when to begin a new row-access.                      |

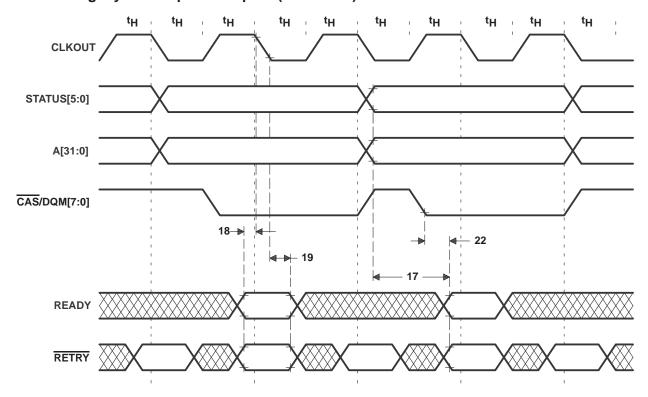

| READY                 | I     | Ready. READY indicates that the external device is ready to complete the memory cycle. READY is driven low by external circuitry to insert wait states into a memory cycle.                                        |

| RL                    | 0     | Row latch. The high-to-low transition of $\overline{RL}$ can be used to latch the valid 32-bit byte address that is present on A31 – A0.                                                                           |

| RETRY                 | I     | Retry. RETRY is driven low by external circuitry to indicate that the addressed memory is busy. The 'C80 memory cycle is rescheduled.                                                                              |

| STATUS5-STATUS0       | 0     | Status code. At row time, STATUS5-STATUS0 indicate the type of cycle being performed. At column time, they identify the processor and type of request that initiated the cycle.                                    |

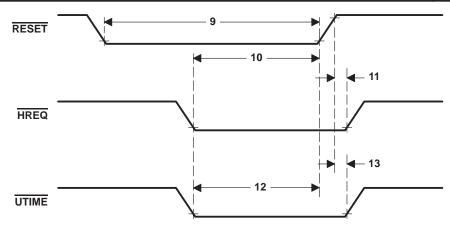

| UTIME                 | I     | User-timing selection. UTIME causes the timing of RAS and CAS/DQM7-CAS/DQM0 to be modified so that custom memory timings can be generated. During reset, UTIME selects the endian mode in which the 'C80 operates. |

|                       |       | DRAM, VRAM, AND SDRAM CONTROL                                                                                                                                                                                      |

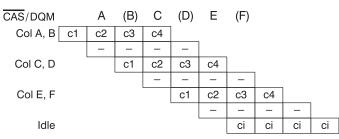

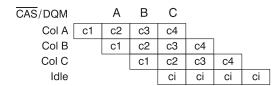

| CAS/DQM7-<br>CAS/DQM0 | 0     | Column-address strobes. CAS/DQM7-CAS/DQM0 drive the CAS inputs of DRAMs and VRAMs, or the DQM input of SDRAMs. The eight strobes provide byte-write access to memory.                                              |

| DSF                   | 0     | Special function. DSF selects special VRAM functions such as block-write, load color register, split-register transfer, and SGRAM block write.                                                                     |

| RAS                   | 0     | Row-address strobe. RAS drives the RAS inputs of DRAMs, VRAMs, and SDRAMs.                                                                                                                                         |

| TRG/CAS               | 0     | Transfer/output enable or column-address strobe. TRG/CAS is used as an output-enable for DRAMs and VRAMs, and also as a transfer-enable for VRAMs. TRG/CAS also drives the CAS inputs of SDRAMs.                   |

| $\overline{w}$        | 0     | Write enable. W is driven low before CAS during write cycles. W controls the direction of the transfer during VRAM transfer cycles.                                                                                |

$<sup>\</sup>uparrow$  I = input, O = output, Z = high impedance

#### **Terminal Functions (Continued)**

| TERMINAL<br>NAME    | TYPET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |       | HOST INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                      |

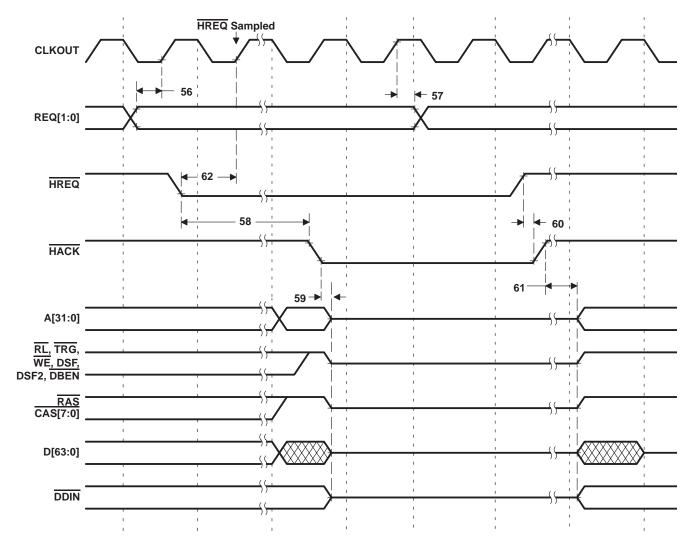

| HACK                | 0     | Host acknowledge. The 'C80 drives HACK output low following an active HREQ to indicate that it has driven the local-memory-bus signals to the high-impedance state and is relinquishing the bus. HACK is driven high asynchronously following HREQ being detected inactive, and then the 'C80 resumes driving the bus.                                                                                                                              |

| HREQ                | I     | Host request. An external device drives HREQ low to request ownership of the local-memory bus. When HREQ is high, the 'C80 owns and drives the bus. HREQ is synchronized internally to the 'C80's internal clock. Also, HREQ is used at reset to determine the power-up state of the MP. If HREQ is low at the rising edge of RESET, the MP comes up running. If HREQ is high, the MP remains halted until the first interrupt occurrence on EINT3. |

| REQ1, REQ0          | 0     | Internal cycle request. REQ1 and REQ0 provide a two-bit code indicating the highest-priority memory-cycle request that is being received by the TC. External logic can monitor REQ1 and REQ0 to determine if it is necessary to relinquish the local-memory bus to the 'C80.                                                                                                                                                                        |

|                     |       | SYSTEM CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                      |

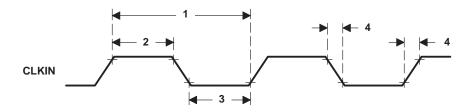

| CLKIN               | ı     | Input clock. CLKIN generates the internal 'C80 clocks to which all processor functions (except the frame timers) are synchronous.                                                                                                                                                                                                                                                                                                                   |

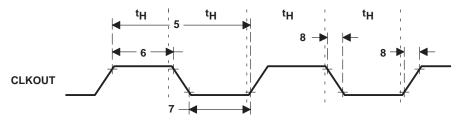

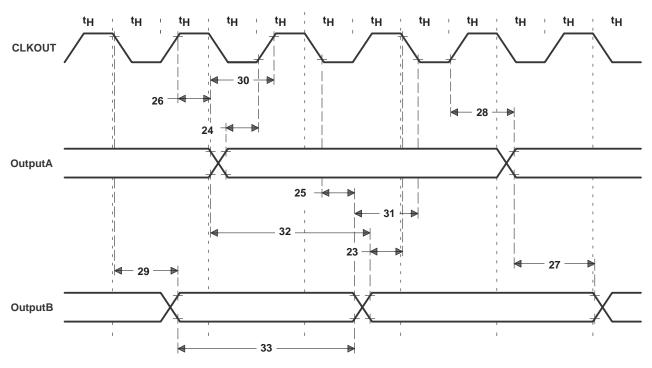

| CLKOUT              | 0     | Local output clock. CLKOUT provides a way to synchronize external circuitry to internal timings. All 'C80 output signals (except the VC signals) are synchronous to this clock.                                                                                                                                                                                                                                                                     |

| EINT1, EINT2, EINT3 | I     | Edge-triggered interrupts. EINT1, EINT2 and EINT3 allow external devices to interrupt the master processor (MP) on one of three interrupt levels (EINT1 is the highest priority). The interrupts are rising-edge triggered. EINT3 also serves as an unhalt signal. If the MP is powered-up halted, the first rising edge on EINT3 causes the MP to unhalt and fetch its reset vector (the EINT3 interrupt-pending bit is not set in this case).     |

| LINT4               | I     | Level-triggered interrupt. LINT4 provides an active-low level-triggered interrupt to the MP. Its priority falls below that of the edge-triggered interrupts. Any interrupt request should remain low until it is recognized by the 'C80.                                                                                                                                                                                                            |

| RESET               | I     | Reset. RESET is driven low to reset the 'C80 (all processors). During reset, all internal registers are set to their initial state and all outputs are driven to their inactive or high-impedance levels. During the rising edge of RESET, the MP reset mode and the 'C80's operating endian mode are determined by the levels of HREQ and UTIME pins, respectively.                                                                                |

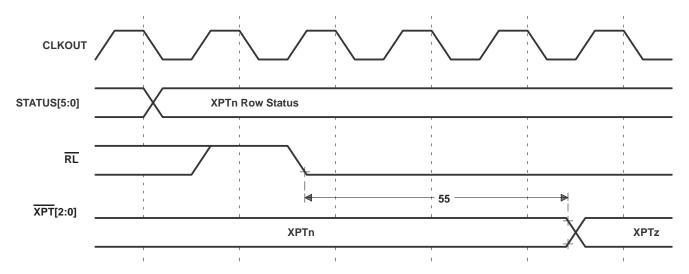

| XPT2-XPT0           | I     | External packet transfer. XPT2 – XPT0 are used by external devices to request a high-priority XPT by the TC.                                                                                                                                                                                                                                                                                                                                        |

|                     |       | EMULATION CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EMU0, EMU1‡         | I/O   | Emulation pins. EMU0 and EMU1 are used to support emulation host interrupts, special functions targeted at a single processor, and multiprocessor halt-event communications.                                                                                                                                                                                                                                                                        |

| тск‡                | I     | Test clock. TCK provides the clock for the 'C80 IEEE-1149.1 logic, allowing it to be compatible with other IEEE-1149.1 devices, controllers, and test equipment designed for different clock rates.                                                                                                                                                                                                                                                 |

| TDI <sup>‡</sup>    | ı     | Test data input. TDI provides input data for all IEEE-1149.1 instructions and data scans of the 'C80.                                                                                                                                                                                                                                                                                                                                               |

| TDO                 | 0     | Test data output. TDO provides output data for all IEEE-1149.1 instructions and data scans of the 'C80.                                                                                                                                                                                                                                                                                                                                             |

| TMS <sup>‡</sup>    | I     | Test-mode select. TMS controls the IEEE-1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                                                       |

| TRST§               | I     | Test reset. TRST resets the 'C80 IEEE-1149.1 module. When low, all boundary-scan logic is disabled, allowing normal 'C80 operation.                                                                                                                                                                                                                                                                                                                 |

<sup>†</sup> I = input, O = output, Z = high impedance ‡ This pin has an internal pullup and can be left unconnnected during normal operation. § This pin has an internal pulldown and can be left unconnnected during normal operation.

#### **Terminal Functions (Continued)**

| TERMINAL<br>NAME                                                                                                                                | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                 |       | VIDEO INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

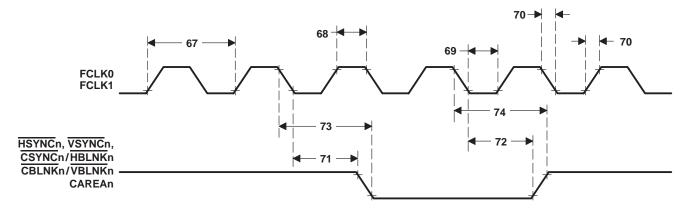

| CAREA0, CAREA1                                                                                                                                  | 0     | Composite area. CAREA0 and CAREA1 define a special area such as an overscan boundary. This area represents the logical OR of the internal horizontal and vertical area signals.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                 |       | Composite blanking/vertical blanking. Each of CBLNK0 / VBLNK0 and VBLNK1 provides one of two blanking functions, depending on the configuration of the CSYNC/HBLNK pin:                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CBLNK0 / VBLNK0,                                                                                                                                | 0     | Composite blanking disables pixel display/capture during both horizontal and vertical retrace periods and is enabled when CSYNC is selected for composite sync video systems.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CBLNK1 / VBLNK1                                                                                                                                 | Ü     | Vertical blanking disables pixel display/capture during vertical retrace periods and is enabled when HBLNK is selected for separate-sync video systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                 |       | Following reset, CBLNK0 / VBLNK0 and CBLNK1 / VBLNK1 are configured as CBLNK0 and CBLNK1, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                 |       | Composite sync/horizontal blanking. CSYNC0 / HBLNK0 and CSYNC1 / HBLNK1 can be programmed for one of two functions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CSYNCO / HBLNKO,<br>CSYNC1 / HBLNK1                                                                                                             | I/O/Z | Composite sync is for use on composite-sync video systems and can be programmed as an input, output, or high-impedance signal. As an input, the 'C80 extracts horizontal and vertical sync information from externally generated active-low <a href="mailto:sync-pulses">sync-pulses</a> . As an output, the active-low composite sync pulses are generated from either external <a href="https://dx.ncbi.org/hs/hs/4">HSYNC</a> and <a href="https://dx.ncbi.org/hs/4">VSYNC</a> signals or the 'C80's internal video timers. In the high-impedance state, the pin is neither driven nor allowed to drive circuitry. |

|                                                                                                                                                 |       | Horizontal blank disables pixel display/capture during horizontal retrace periods in separate-sync video systems and can be used as an output only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                 |       | Immediately following reset, <u>CSYNC0 / HBLNK0</u> and <u>CSYNC1 / HBLNK1</u> are configured as high-impedance <u>CSYNC0</u> and <u>CSYNC1</u> , respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

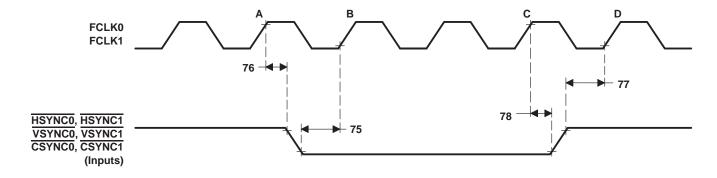

| FCLK0, FCLK1                                                                                                                                    | I     | Frame clock. FCLK0 and FCLK1 are derived from the external video system's dotclock and are used to drive the 'C80 video logic for frame timer 0 and frame timer 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Horizontal sync. HSYNC0 an output, or high impedance s generated horizontal sync pul by the 'C80 on-chip frame ti synchronization is allowed to |       | Horizontal sync. HSYNC0 and HSYNC1 control the video system. They can be programmed as input, output, or high impedance signals. As an input, HSYNC synchronizes the video timer to externally generated horizontal sync pulses. As an output, HSYNC is an active-low horizontal sync pulse generated by the 'C80 on-chip frame timer. In the high-impedance state, the pin is not driven, and no internal synchronization is allowed to occur. Immediately following reset, HSYNC0 and HSYNC1 are in the high-impedance state.                                                                                       |

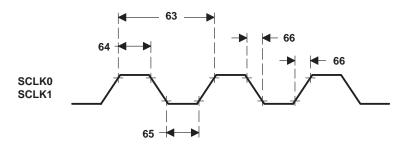

| SCLK0, SCLK1                                                                                                                                    | I     | Serial-data clock. SCLK0 and SCLK1 are used by the 'C80 SRT controller to track the VRAM tap point when using midline reload. SCLK0 and SCLK1 should be the same signals that clock the serial register on the VRAMs controlled by frame timer 0 and frame timer 1, respectively.                                                                                                                                                                                                                                                                                                                                     |

| VSYNCO,<br>VSYNC1                                                                                                                               | I/O/Z | Vertical sync. VSYNC0 and VSYNC1 control the video system. They can be programmed as inputs, outputs, or high-impedance signals. As inputs, VSYNCx synchronizes the frame timer to externally generated vertical-sync pulses. As outputs, VSYNCx are active-low vertical-sync pulses generated by the 'C80 on-chip frame timer. In the high-impedance state, the pin is not driven and no internal synchronization is allowed to occur. Immediately following reset, VSYNCx is in the high-impedance state.                                                                                                           |

|                                                                                                                                                 |       | POWER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>SS</sub> <sup>‡</sup>                                                                                                                    | I     | Ground. Electrical ground inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>DD</sub> ‡                                                                                                                               | I     | Power. Nominal 3.3-V power supply inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                 | -     | MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| No Connect                                                                                                                                      |       | No connect serves as an alignment key and must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FF2-FF1                                                                                                                                         |       | FF2-FF1 (GF package only) are reserved for factory use and should be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

$<sup>^{\</sup>dagger}$ I = input, O = output, Z = high-impedance

$<sup>\</sup>ddagger$  For proper operation, all VDD and VSS pins must be connected externally.

#### architecture

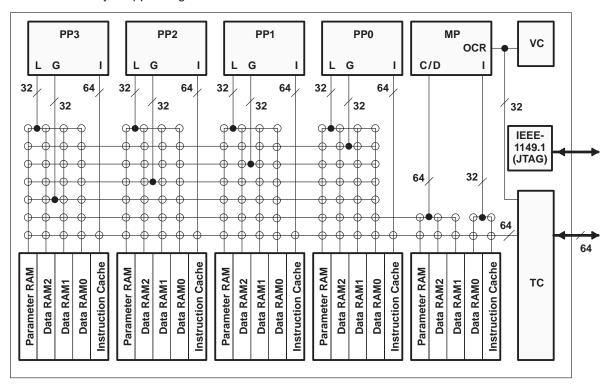

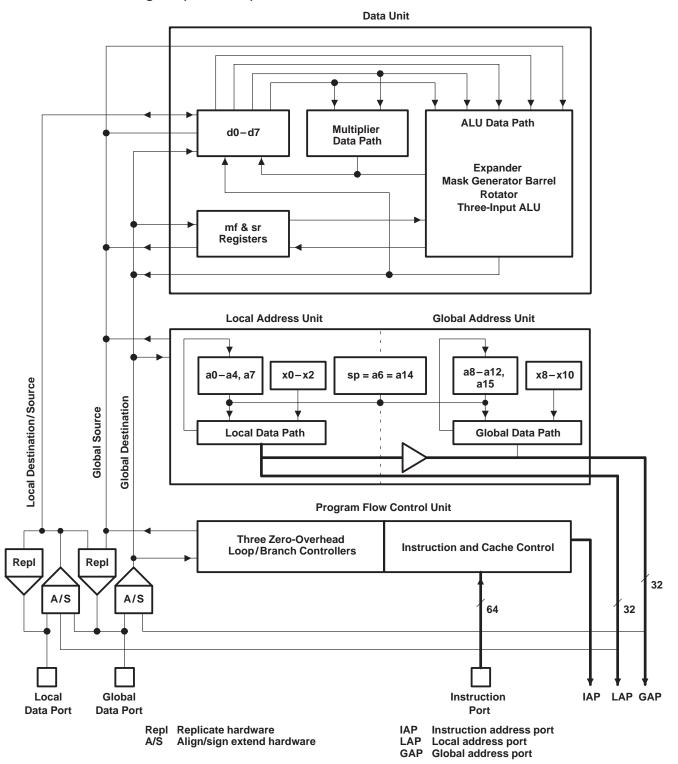

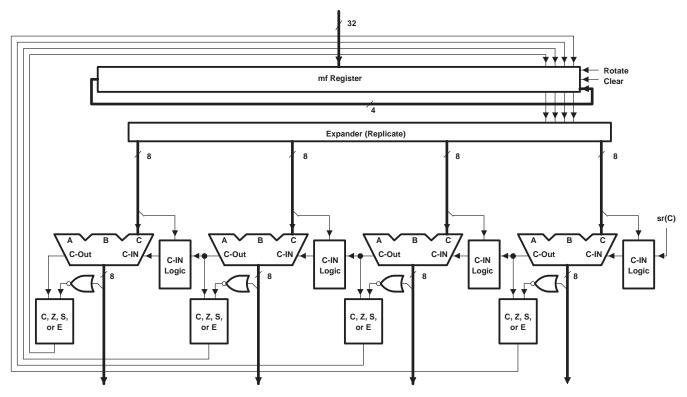

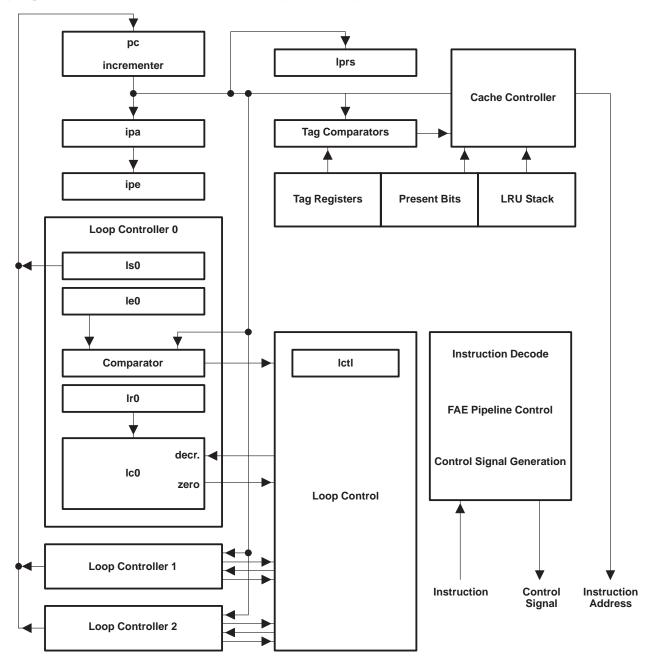

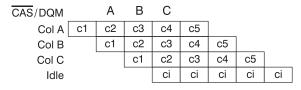

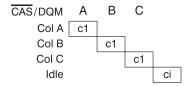

Figure 1 shows the major components of the 'C80: the master processor (MP), the parallel digital signal processors (PPs), the transfer controller (TC), the video controller (VC), and the IEEE-1149.1 emulation interface. Shared access to on-chip RAM is achieved through the crossbar. Crossbar connections are represented by  $\bigcirc$ . Each PP can perform three accesses per cycle through its local (L), global (G), and instruction (I) ports. The MP can access two RAMs per cycle through its crossbar/data (C/D) and instruction (I) ports, and the TC can access one RAM through its crossbar interface. Up to 15 simultaneous accesses are supported in each cycle. Addresses can be changed every cycle, allowing the crossbar matrix to be changed on a cycle-by-cycle basis. Contention between processors for the same RAM in the same cycle is resolved by a round-robin priority scheme. In addition to the crossbar, a 32-bit datapath exists between the MP and the TC and VC. This allows the MP to access TC and VC on-chip registers that are memory mapped into the MP memory space.

The 'C80 has a 4G-byte address space as shown in Figure 2. The lower 32M bytes are used to address internal RAM and memory-mapped registers.

Figure 1. Block Diagram Showing Datapaths

#### architecture (continued)

|                                 | _                                       |

|---------------------------------|-----------------------------------------|

| PP0 Data RAM0                   | 0x00000000                              |

| (2K Bytes)                      | 0x000007FF                              |

| PP0 Data RAM1                   | 0x00000800                              |

| (2K Bytes)                      | 0x00000FFF                              |

| PP1 Data RAM0                   | 0x00001000                              |

| (2K Bytes)                      | 0x000017FF                              |

| PP1 Data RAM1                   | 0x00001800                              |

| (2K Bytes)                      | 0x00001FFF                              |

| PP2 Data RAM0                   | 0x00002000                              |

| (2K Bytes)                      | 0x000027FF                              |

| PP2 Data RAM1                   | 0x00002800                              |

| (2K Bytes)                      | 0x00002FFF                              |

| PP3 Data RAM0                   | 0x00003000                              |

| (2K Bytes)                      | 0x000037FF                              |

| PP3 Data RAM1                   | 0x00003800                              |

| (2K Bytes)                      | 0x00003FFF                              |

|                                 | 0x00003111                              |

| Reserved                        |                                         |

| (16K Bytes)                     | 0x00007FFF                              |

| PP0 Data RAM2                   | 0x00008000                              |

| (2K Bytes)                      | 0x000087FF                              |

| Reserved                        | 0x00008800                              |

| (2K Bytes)                      | 0x00008FFF                              |

| PP1 Data RAM2                   | 0x00009000                              |

| (2K Bytes)                      | 0x000097FF                              |

| Reserved                        | 0x00009800                              |

| (2K Bytes)                      | 0x00009FFF                              |

| PP2 Data RAM2                   | 0x00003111                              |

| (2K Bytes)                      | 0x0000A7FF                              |

| Reserved                        | 0x0000A711                              |

| (2K Bytes)                      | 0x0000AFFF                              |

| PP3 Data RAM2                   | 0x0000AFFF                              |

| (2K Bytes)                      |                                         |

| (2.1. 29.100)                   | 0x0000B7FF<br>0x0000B800                |

| Reserved                        | 000000000000000000000000000000000000000 |

| (16730112 Bytes)                | 0x00FFFFF                               |

| PP0 Parameter RAM               | 0x01000000                              |

| (2K Bytes)                      | 0x010007FF                              |

| Reserved                        | 0x01000800                              |

| (2K Bytes)                      | 0x01000FFF                              |

| PP1 Parameter RAM               | 0x01000111                              |

| (2K Bytes)                      | 0x010017FF                              |

| Reserved                        | 0x010017FF                              |

| (2K Bytes)                      |                                         |

| PP2 Parameter RAM               | 0x01001FFF<br>0x01002000                |

| (2K Bytes)                      |                                         |

| ` , ,                           | 0x010027FF                              |

| Reserved<br>(2K Bytes)          | 0x01002800                              |

| (ZN Bytes)                      | 0x01002FFF                              |

| DD0 D 1 D 1 1 1                 |                                         |

| PP3 Parameter RAM<br>(2K Bytes) | 0x01003000                              |

| Reserved                   | 0x01003800 |

|----------------------------|------------|

| (51 200 Bytes)             |            |

|                            | 0x0100FFFF |

| MP Parameter RAM           | 0x01010000 |

| (2K Bytes)                 | 0x010107FF |

| ` , ,                      | 0x01010711 |

| Reserved                   | 0.01010000 |

| (8327168 Bytes)            |            |

| (0327 100 Bytes)           |            |

|                            | 0x018017FF |

| PP0 Instruction Cache      | 0x01801800 |

| (2K Bytes)                 | 0x01801FFF |

| Reserved                   | 0x01802000 |

| (6K Bytes)                 | 0x018037FF |

| PP1 Instruction Cache      | 0x01803800 |

| (2K Bytes)                 |            |

|                            | 0x01803FFF |

| Reserved                   | 0x01804000 |

| (6K Bytes)                 | 0x018057FF |

| PP2 Instruction Cache      | 0x01805800 |

| (2K Bytes)                 | 0x01805FFF |

| Reserved                   | 0x01806000 |

| (6K Bytes)                 |            |

| <u> </u>                   | 0x018077FF |

| PP3 Instruction Cache      | 0x01807800 |

| (2K Bytes)                 | 0x01807FFF |

| Reserved                   | 0x01808000 |

| (32K Bytes)                | 0x0180FFFF |

| MP Data Cache              | 0x01810000 |

| (4K Bytes)                 |            |

| (4K Bytes)                 | 0x01810FFF |

| Reserved                   | 0x01811000 |

| (28K Bytes)                |            |

| . , ,                      | 0x01817FFF |

| MP Instruction Cache       | 0x01818000 |

| (4K Bytes)                 | 0x01818FFF |

| Reserved                   | 0x01819000 |

| (28K Bytes)                |            |

| (20K Bytes)                | 0x0181FFFF |

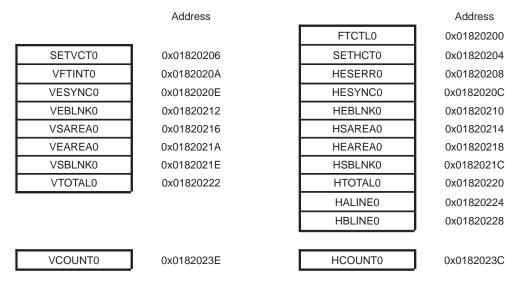

| Memory-Mapped TC Registers | 0x01820000 |

| (512 Bytes)                | 0x018201FF |

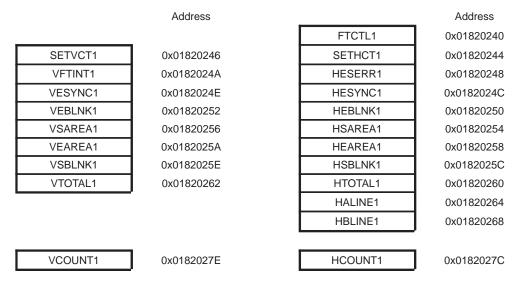

| Memory-Mapped VC Registers | 0x01820200 |

| (512 Bytes)                |            |

| (312 Bytes)                | 0x018203FF |

| Reserved                   | 0x01820400 |

| (8327168 Bytes)            |            |

|                            | 0x01FFFFFF |

|                            | 0x02000000 |

|                            |            |

| 1                          |            |

| External Memory            |            |

| (4064M Bytes)              |            |

| (122 2,132,                |            |

|                            |            |

|                            |            |

|                            | 0xFFFFFFF  |

|                            |            |

Figure 2. Memory Map

#### master processor (MP) architecture

The master processor (MP) is a 32-bit RISC processor with an integral IEEE-754 floating-point unit. The MP is designed for effective execution of C code and is capable of performing at well over 130K dhrystones/s. Major tasks which the MP typically performs are:

- Task control and user interface

- Information processing and analysis

- IEEE-754 floating point (including graphics transforms)

#### MP functional block diagram

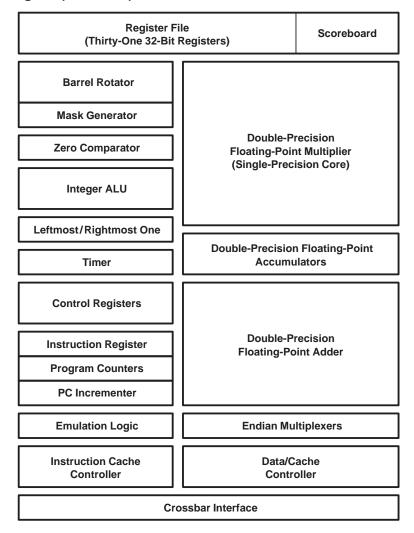

Figure 3 shows a block diagram of the master processor. Key features of the MP include:

- 32-bit RISC processor

- Load/store architecture