# **FAN5009**

# **Dual Bootstrapped 12V MOSFET Driver**

#### **Features**

- Drives N-channel High-Side and Low-Side MOSFETs in a synchronous buck configuration

- 12V High-Side and 12V Low-Side Drive

- Internal Adaptive "Shoot-Through" Protection

- Integrated Bootstrap Diode for High-Side Drive

- · Fast rise and fall times

- Switching Frequency Up to 500kHz

- OD input for Output Disable allows for synchronization with PWM controller

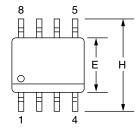

- SOIC-8 Package

- Available in low thermal resistance MLP package

### **Applications**

- Multi-phase VRM/VRD regulators for Microprocessor Power

- High Current/High Frequency DC/DC Converters

- High Power Modular Supplies

### **General Description**

The FAN5009 is a dual, high frequency Mc FET duer, specifically designed to drive N-Chanry pow MO ETs in a synchronous-rectified buck corrector. These livers, combined with a Fairchild Multi-Pha WM introller and power MOSFETs, form a corrector age regulator solution for advanced microrcesse.

The FAN5009 drives the upper a power MOSFL gates of a synchronous buck required boot diode and requires only an external but the capacitor ( $C_{BOOT}$ ) and of the capacitor ( $C_{BOOT}$ ) and of the power MOSFL is the encies up to 0k. The product's a power through protation powers the MOSFETs from only sting simultations.

The AN5009 is read for open on from 0°C to +85°C and available in lover SOIC-8 or MLP packages.

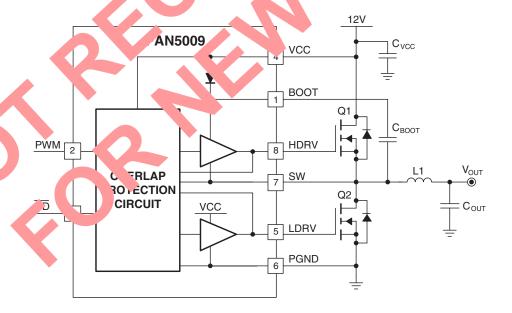

# **Typical Application**

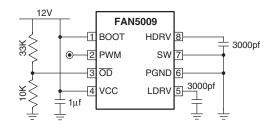

Figure 1. Typical Application.

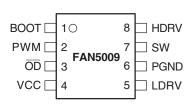

# **Pin Configuration**

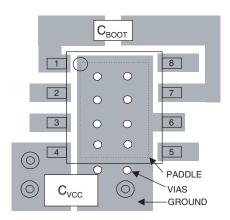

FAN5009MP 8-pin MLP package (Paddle should be connected to ground or left floating)

# **Pin Definitions**

| Pin # | Pin Name | Pin Function Description                                                                                                                                                        |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | ВООТ     | <b>Bootstrap Supply Input.</b> Provides voltage supply to high-side MOSFET driver. Connect to bootstrap capacitor. See Applications Section.                                    |

| 2     | PWM      | PWM Signal Input. This pin accepts a logic-level PWM signal from the controller.                                                                                                |

| 3     | ŌD       | Output Disable. When low, this pin disables FET switching (HDRV and LDRV are held low).                                                                                         |

| 4     | VCC      | Power Input. +12V chip bias power. Bypass with a 1µF ceramic capacitor.                                                                                                         |

| 5     | LDRV     | Low Side Gate Drive Output. Connect to the gate of low-side power MOSFET(s).                                                                                                    |

| 6     | PGND     | Power ground. Connect directly to source of low-side MOSFET(s).                                                                                                                 |

| 7     | SW       | <b>Switch Node Input</b> . Connect as shown in Figure 1. SW provides return for high-side bootstrapped driver and acts as a sense point for the adaptive shoot-thru protection. |

| 8     | HDRV     | High Side Gate Drive Output – Connect to the gate of high-side power MOSFET(s).                                                                                                 |

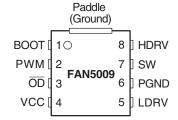

# **Functional Block Diagram**

# **Absolute Maximum Ratings**

Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational section of this specification is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability. Absolute maximum ratings apply individually, not in combination. Unless otherwise specified, voltages are referenced to PGND.

| Parameter       |                                  | Min.                   | Max.                 | Units |

|-----------------|----------------------------------|------------------------|----------------------|-------|

| VCC to PGND     |                                  | -0.3                   | 15                   | V     |

| PWM and OD pins |                                  | -0.3                   | 5.5                  | ٧     |

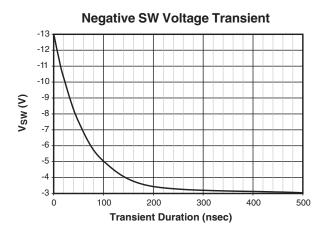

| SW to PGND      | Continuous                       | -1                     | 15                   | V     |

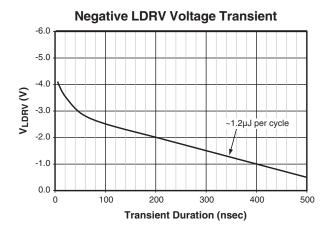

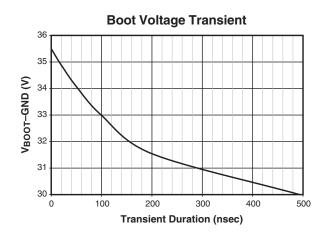

|                 | Transient ( t=100nsec, F≤500kHz) | -5 <sup>(1)</sup>      | 25                   | V     |

| BOOT to SW      | ·                                | -0.3                   | 15                   | ٧     |

| BOOT to PGND    | Continuous                       | -0.3                   | 30                   | ٧     |

|                 | Transient ( t=100nsec, F≤500kHz) |                        | 33 <sup>(1)</sup>    | ٧     |

| HDRV            | V <sub>SW</sub> -1               | V <sub>BOOT</sub> +0.3 | V                    |       |

| LDRV Continuous |                                  | -0.5                   | V <sub>CC</sub> +0.3 | ٧     |

|                 | Transient ( t=200nsec)           | -2 <sup>(1)</sup>      |                      | ٧     |

#### Notes:

### **Thermal Information**

| Parameter                                                                     | Min. | Тур. | Max. | Units |

|-------------------------------------------------------------------------------|------|------|------|-------|

| Junction Temperature (T <sub>J</sub> )                                        | 0    |      | 150  | °C    |

| Storage Temperature                                                           | -65  |      | 150  | °C    |

| Lead Soldering Temperature, 10 seconds                                        |      |      | 300  | °C    |

| Vapor Phase, 60 seconds                                                       |      |      | 215  | °C    |

| Infrared, 15 seconds                                                          |      |      | 220  | °C    |

| Power Dissipation (P <sub>D</sub> ) T <sub>A</sub> = 25°C                     |      |      | 715  | mW    |

| Thermal Resistance, SO8 – Junction to Case θ <sub>JC</sub>                    |      | 40   |      | °C/W  |

| Thermal Resistance, SO8 – Junction to Ambient $\theta_{JA}$                   |      | 140  |      | °C/W  |

| Thermal Resistance, MLP – Junction to Paddle $\theta_{\mbox{\scriptsize JC}}$ |      | 4    |      | °C/W  |

# **Recommended Operating Conditions**

| Parameter                              | Conditions  | Min. | Тур. | Max. | Units |

|----------------------------------------|-------------|------|------|------|-------|

| Supply Voltage VCC                     | VCC to PGND | 10   | 12   | 13.5 | V     |

| Ambient Temperature (T <sub>A</sub> )  |             | 0    |      | 85   | °C    |

| Junction Temperature (T <sub>J</sub> ) |             | 0    |      | 125  | °C    |

<sup>1.</sup> For transient derating beyond the levels indicated, refer to the graphs on page 7.

# **Electrical Specifications**

$V_{CC}$  = 12V, and  $T_A$  = 25°C using circuit in Figure 2 unless otherwise noted. The • denotes specifications which apply over the full operating temperature range.

| Parameter                           | Symbol                   | Conditions              |   | Min. | Тур. | Max. | Units |

|-------------------------------------|--------------------------|-------------------------|---|------|------|------|-------|

| Input Supply                        | '                        |                         |   |      | !    | '    |       |

| VCC Voltage Range                   | V <sub>CC</sub>          |                         | • | 6.4  | 12   | 13.5 | V     |

| VCC Current                         | I <sub>CC</sub>          | <u>OD</u> = 0V          | • |      | 3.5  | 8    | mA    |

| Bootstrap Diode                     |                          |                         |   |      | •    |      | •     |

| Continuous Forward Current          | I <sub>F(AVG)</sub>      |                         | • |      |      | 25   | mA    |

| Reverse Breakdown Voltage           | V <sub>R</sub>           |                         | • | 15   |      |      | V     |

| Reverse Recovery Time <sup>2</sup>  | t <sub>RR</sub>          |                         |   |      | 10   |      | ns    |

| Forward Voltage <sup>2</sup>        | V <sub>F</sub>           | I <sub>F</sub> = 10mA   |   |      | 0.8  | 0.95 | V     |

| OD Input                            | '                        |                         |   |      |      |      | •     |

| Input High Voltage                  | V <sub>IH (OD)</sub>     |                         | • | 2.5  |      |      | V     |

| Input Low Voltage                   | V <sub>IL (OD)</sub>     |                         | • |      |      | 0.8  | V     |

| Input Current                       | I <sub>OD</sub>          | <del>OD</del> = 3.0V    | • | -300 |      | +300 | nA    |

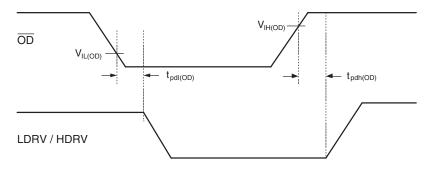

| Propagation Delay <sup>2</sup>      | $t_{pdl(\overline{OD})}$ | See Figure 3            |   |      | 30   | 40   | ns    |

|                                     | $t_{pdh(\overline{OD})}$ |                         |   |      | 30   | 45   | ns    |

| PWM Input                           |                          |                         |   |      | •    |      | •     |

| Input High Voltage                  | V <sub>IH(PWM)</sub>     |                         | • | 3.5  |      |      | V     |

| Input Low Voltage                   | V <sub>IL(PWM)</sub>     |                         | • |      |      | 0.8  | V     |

| Input Current                       | I <sub>IL(PWM)</sub>     |                         | • | -1   |      | +1   | μΑ    |

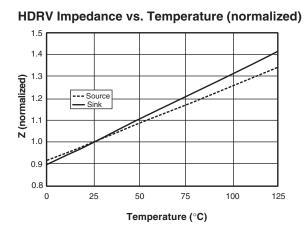

| High-Side Driver                    |                          |                         |   |      | •    |      | •     |

| Output Resistance, Sourcing Current | R <sub>HUP</sub>         | $V_{BOOT}-V_{SW} = 12V$ |   |      | 3.8  | 4.4  | Ω     |

| Output Resistance, Sinking Current  | R <sub>HDN</sub>         | $V_{BOOT}-V_{SW} = 12V$ |   |      | 1.4  | 1.8  | Ω     |

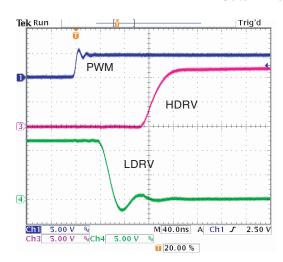

| Transition Times <sup>2,4</sup>     | t <sub>R(HDRV)</sub>     | See Figure 2            |   |      | 40   | 55   | ns    |

|                                     | t <sub>F(HDRV)</sub>     |                         |   |      | 20   | 30   | ns    |

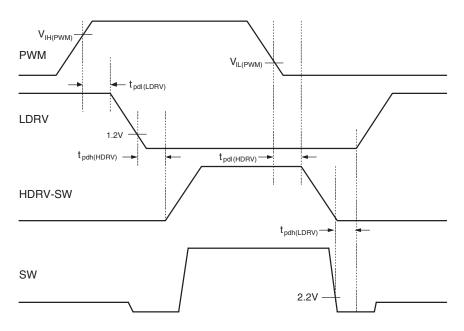

| Propagation Delay <sup>2,3</sup>    | t <sub>pdh(HDRV)</sub>   | See Figure 2, and 4     |   |      | 50   | 65   | ns    |

|                                     | t <sub>pdl(HDRV)</sub>   |                         |   |      | 25   | 40   | ns    |

Figure 2. Test Circuit

# **Electrical Specifications** (continued)

| Parameter                           | Symbol                 | Conditions                                        | Min. | Тур. | Max. | Units |

|-------------------------------------|------------------------|---------------------------------------------------|------|------|------|-------|

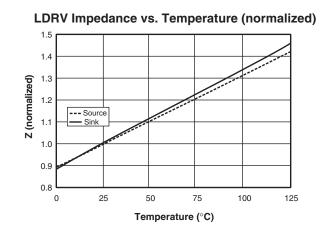

| Low-Side Driver                     | •                      |                                                   |      |      |      | •     |

| Output Resistance, Sourcing Current | R <sub>LUP</sub>       |                                                   |      | 3.4  | 4.0  | Ω     |

| Output Resistance, Sinking Current  | R <sub>LDN</sub>       |                                                   |      | 1.4  | 1.8  | Ω     |

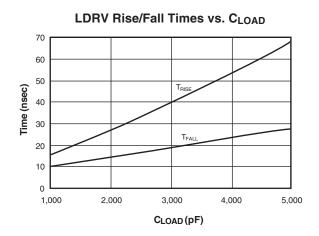

| Transition Times <sup>2,4</sup>     | t <sub>R(LDRV)</sub>   | See Figure 2                                      |      | 40   | 50   | ns    |

|                                     | t <sub>F(LDRV)</sub>   |                                                   |      | 20   | 30   | ns    |

| Propagation Delay <sup>2,3</sup>    | t <sub>pdh(LDRV)</sub> | See Figures 2, 4                                  |      | 20   | 30   | ns    |

|                                     | t <sub>pdl(LDRV)</sub> |                                                   |      | 25   | 40   | ns    |

|                                     | t <sub>pdh(ODRV)</sub> | See Adaptive Gate<br>Drive Circuit<br>description |      | 240  |      | ns    |

#### NOTES:

- 1. All limits at operating temperature extremes are guaranteed by design, characterization and statistical quality control

- 2. AC Specifications guaranteed by design/characterization (not production tested).

- 3. For propagation delays, "tpdh" refers to low-to-high signal transition and "tpdl" refers to high-to-low signal transition

- 4. Transition times are defined for 10% and 90% of DC values

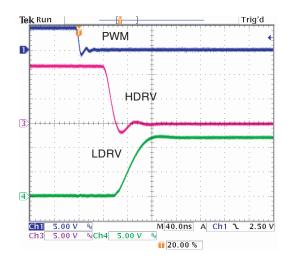

Figure 3. Output Disable Timing

Figure 4. Adaptive Gate Drive Timing

# **Typical Characteristics**

#### **Gate Drive Rise and Fall Times**

HDRV Rise/Fall Times vs. CLOAD 70 60 50 Time (nsec) 40 30 20 T<sub>FALL</sub> 10 2,000 3,000 1,000 4,000 5,000 CLOAD (pF)

# **Typical Characteristics** (continued)

### **Circuit Description**

The FAN5009 is a dual MOSFET driver optimized for driving N-channel MOSFETs in a synchronous buck converter topology. A single PWM input signal is all that is required to properly drive the high-side and the low-side MOSFETs. Each driver is capable of driving a 3nF load at speeds up to 500kHz.

For a more detailed description of the FAN5009 and its features, refer to the Internal Block Diagram and Figure 1.

#### **Low-Side Driver**

The low-side driver (LDRV) is designed to drive a ground-referenced low  $R_{DS(on)}$  N-channel MOSFETs. The bias for LDRV is internally connected between VCC and PGND. When the driver is enabled, the driver's output is  $180^{\circ}$  out of phase with the PWM input. When the FAN5009 is disabled  $(\overline{OD} = 0V)$ , LDRV is held low.

#### **High-Side Driver**

The high-side driver (HDRV) is designed to drive a floating N-channel MOSFET. The bias voltage for the high-side driver is developed by a bootstrap supply circuit, consisting of the internal diode and external bootstrap capacitor  $(C_{\rm BOOT})$ .

During start-up, SW is held at PGND, allowing  $C_{BOOT}$  to charge to VCC through the internal diode. When the PWM input goes high, HDRV will begin to charge the high-side MOSFET's gate (Q1). During this transition, charge is removed from  $C_{BOOT}$  and delivered to Q1's gate. As Q1 turns on, SW rises to  $V_{IN}$ , forcing the BOOT pin to  $V_{IN} + V_{C(BOOT)}$ , which provides sufficient  $V_{GS}$  enhancement for Q1.

To complete the switching cycle, Q1 is turned off by pulling HDRV to SW.  $C_{BOOT}$  is then recharged to VCC when SW falls to PGND.

HDRV output is in phase with the PWM input. When the driver is disabled, the high-side gate is held low.

#### **Adaptive Gate Drive Circuit**

The FAN5009 embodies an advanced design that ensures minimum MOSFET dead-time while eliminating potential shoot-through (cross-conduction) currents. It senses the state of the MOSFETs and adjusts the gate drive, adaptively, to ensure they do not conduct simultaneously. Refer to Figure 4 for the relevant timing waveforms.

To prevent overlap during the low-to-high switching transition (Q2 OFF to Q1 ON), the adaptive circuitry monitors the voltage at the LDRV pin. When the PWM signal goes HIGH, Q2 will begin to turn OFF after some propagation delay ( $t_{pdl(LDRV)}$ ).

Once the LDRV pin is discharged below ~1.2V, Q1 begins to turn ON after adaptive delay  $t_{pdh(HDRV)}$ .

To preclude overlap during the high-to-low transition (Q1 OFF to Q2 ON), the adaptive circuitry monitors the voltage at the SW pin. When the PWM signal goes LOW, Q1 will begin to turn OFF after some propagation delay ( $t_{pdl(HDRV)}$ ). Once the SW pin falls below ~2.2V, Q2 begins to turn ON after adaptive delay  $t_{pdh(LDRV)}$ .

Additionally,  $V_{GS}$  of Q1 is monitored. When  $V_{GS(Q1)}$  is discharged below ~1.2V, a secondary adaptive delay is initiated, which results in Q2 being driven ON after  $t_{pdh(ODRV)}$ , regardless of SW state. This function is implemented to ensure  $C_{BOOT}$  is recharged each switching cycle, particularly for cases where the power convertor is sinking current and SW voltage does not fall below the 2.2V adaptive threshold. Secondary delay  $t_{pdh(ODRV)}$  is longer than  $t_{pdh(DRV)}$ .

### **Application Information**

#### **Supply Capacitor Selection**

For the supply input ( $V_{CC}$ ) of the FAN5009, a local ceramic bypass capacitor is recommended to reduce the noise and to supply the peak current. Use at least a 1 $\mu$ F, X7R or X5R capacitor. Keep this capacitor close to the FAN5009  $V_{CC}$  and PGND pins.

#### **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor  $(C_{BOOT})$  and the internal diode, as shown in Figure 1. Selection of these components should be done after the high-side MOSFET has been chosen. The required capacitance is determined using the following equation:

$$C_{BOOT} = \frac{Q_{G}}{\Delta V_{BOOT}} \tag{1}$$

where  $Q_G$  is the total gate charge of the high-side MOSFET, and  $\Delta V_{BOOT}$  is the voltage droop allowed on the high-side MOSFET drive. For example, the  $Q_G$  of the FDD6696 is about 35nC @ 12 $V_{GS}$ . For an allowed droop of ~300mV, the required bootstrap capacitance is 100nF. A good quality ceramic capacitor must be used.

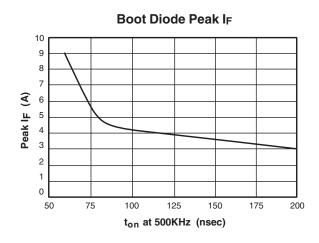

The average diode forward current,  $I_{F(AVG)}$ , can be estimated by:

$$I_{F(AVG)} = Q_{GATE} \times F_{SW}$$

(2)

where F<sub>SW</sub> is the switching frequency of the controller.

The peak surge current rating of the internal diode should be checked in-circuit, since this is dependent on the equivalent impedance of the entire bootstrap circuit, including the PCB traces. For applications requiring higher  $I_{\rm F}$ , an external diode may be used in parallel to the internal diode.

#### **Thermal Considerations**

Total device dissipation:

$$P_{D} = P_{Q} + P_{R} + P_{HDRV} + P_{LDRV}$$

(3)

where P<sub>O</sub> represents quiescent power dissipation:

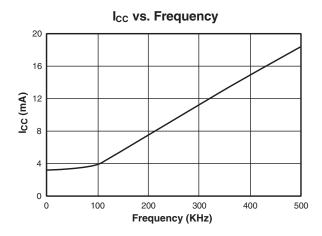

$$P_Q = V_{CC} \times [4mA + 0.036 (F_{SW} - 100)]$$

(4)

where F<sub>SW</sub> is switching frequency (in kHz).

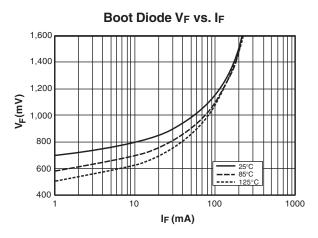

P<sub>R</sub> is power dissipated in the bootstrap rectifier:

$$P_{R} = V_{F} \times F_{SW} \times Q_{G1}$$

(5)

Where  $Q_{G1}$  is total gate charge of the upper FET (Q1) for it's applied  $V_{GS}$ .

$V_F$  for the applied  $I_{F(AVG)}$  can be graphically determined using the datasheet curves, where:

$$I_{F(AVG)} = F_{SW} \times Q_{G1}$$

(6)

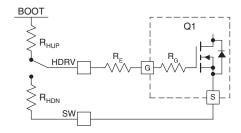

P<sub>HDRV</sub> represents internal power dissipation of the upper FET driver.

$$P_{HDRV} = P_{H(R)} + P_{H(F)} \tag{7}$$

Where  $P_{H(R)}$  and  $P_{H(F)}$  are internal dissipations for the rising and falling edges, respectively:

$$P_{H(R)} = P_{Q1} \times \frac{R_{HUP}}{R_{HUP} + R_E + R_G}$$

(8)

$$P_{H(F)} = P_{Q1} \times \frac{R_{HDN}}{R_{HDN} + R_{E} + R_{G}}$$

(9)

where:

$$P_{Q1} = \frac{1}{2} \times Q_{G1} \times V_{GS(Q1)} \times F_{SW}$$

(10)

As described in eq. 8 and 9 above, the total power consumed in driving the gate is divided in proportion to the resistances in series with the MOSFET's internal gate node as shown below:

Figure 5. Driver dissipation model

$R_{G}$  is the polysilicon gate resistance, internal to the FET.  $R_{E}$  is the external gate drive resistor implemented in many designs. Note that the introduction of  $\,R_{E}$  can reduce driver power dissipation, but excess  $R_{E}$  may cause errors in the "adaptive gate drive" circuitry. For more information please refer to Fairchild app note AN-6003, "Shoot-through" in Synchronous Buck Converters.

P<sub>LDRV</sub> is dissipation of the lower FET driver.

$$P_{LDRV} = P_{L(R)} + P_{L(F)} \tag{11}$$

Where  $P_{H(R)}$  and  $P_{H(F)}$  are internal dissipations for the rising and falling edges, respectively:

$$P_{L(R)} = P_{Q2} \times \frac{R_{LUP}}{R_{LUP} + R_F + R_G}$$

(12)

$$P_{L(F)} = P_{Q2} \times \frac{R_{LDN}}{R_{HDN} + R_{F} + R_{G}}$$

(13)

where:

$$P_{Q2} = \frac{1}{2} \times Q_{G2} \times V_{GS(Q2)} \times F_{SW}$$

(14)

### **Layout Considerations**

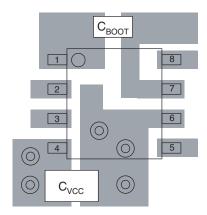

Use the following general guidelines when designing printed circuit boards (see Figures 6 and 7):

- 1. Trace out the high-current paths and use short, wide (>25 mil) traces to make these connections.

- 2. Connect the PGND pin of the FAN5009 as close as possible to the source of the lower MOSFET.

- The V<sub>CC</sub> bypass capacitor should be located as close as possible to V<sub>CC</sub> and PGND pins.

- 4. Use vias to other layers when possible to maximize thermal conduction away from the IC.

Figure 6. External component placement recommendation for SO8 package (not to scale)

5. The paddle on the MLP package is internally referenced to ground. It can be left floating or connected to ground. For best thermal performance it should be connected to ground as shown in Figure 7.

Figure 7. Recommended layout for MLP package. Also accepts SO8 package (not to scale)

6. The recommended land pattern shown in the MLP mechanical dimensions will work with both MLP-8 and SO-8 packages.

The circuit in Figure 1 illustrates a typical implementation of a single phase of a multi-phase buck converter for  $V_{\rm CORE}$  applications. For a complete VR10 design example, please refer to the FAN5019 or FAN5018 datasheets.

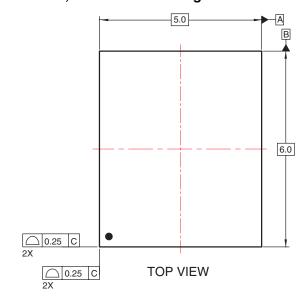

### **Mechanical Dimensions**

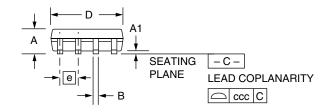

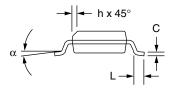

## 0.150, 8 Lead SOIC Package

| Cymphol | Inches   |      | Millim | Notes |       |

|---------|----------|------|--------|-------|-------|

| Symbol  | Min.     | Max. | Min.   | Max.  | notes |

| Α       | .053     | .069 | 1.35   | 1.75  |       |

| A1      | .004     | .010 | 0.10   | 0.25  |       |

| В       | .013     | .020 | 0.33   | 0.51  |       |

| С       | .0075    | .010 | 0.20   | 0.25  | 5     |

| D       | .189     | .197 | 4.80   | 5.00  | 2     |

| Е       | .150     | .158 | 3.81   | 4.01  | 2     |

| е       | .050 BSC |      | 1.27   | BSC   |       |

| Н       | .228     | .244 | 5.79   | 6.20  |       |

| h       | .010     | .020 | 0.25   | 0.50  |       |

| L       | .016     | .050 | 0.40   | 1.27  | 3     |

| N       | 8        | 3    | 8      |       | 6     |

| α       | 0°       | 8°   | 0°     | 8°    |       |

| CCC     |          | .004 | _      | 0.10  |       |

#### Notes:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- "D" and "E" do not include mold flash. Mold flash or protrusions shall not exceed .010 inch (0.25mm).

- 3. "L" is the length of terminal for soldering to a substrate.

- 4. Terminal numbers are shown for reference only.

- 5. "C" dimension does not include solder finish thickness.

- 6. Symbol "N" is the maximum number of terminals.

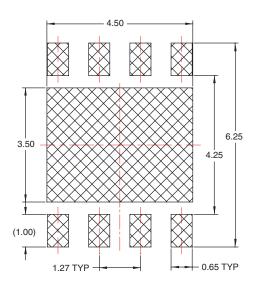

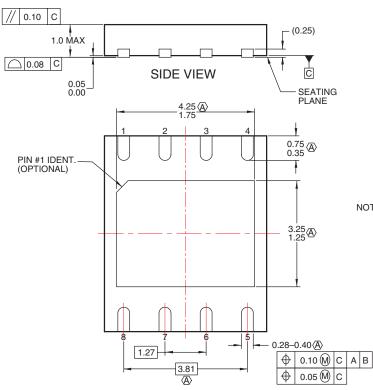

### **Mechanical Dimensions**

## 5mm x 6mm, 8 Lead MLP Package

LAND PATTERN RECOMMENDATION

**BOTTOM VIEW**

NOTES:

- DOES NOT FULLY CONFORM TO JEDEC REGISTRATION MO-229, DATED 11/2001.

- DIMENSIONS ARE IN MILLIMETERS.

- DIMENSIONING AND TOLERANCES PER ASME Y14.5–1994.

## **Ordering Information**

| Part Number | Temperature Range | Package | Packing       |

|-------------|-------------------|---------|---------------|

| FAN5009M    | 0°C to 85°C       | SOIC-8  | Rails         |

| FAN5009MX   | 0°C to 85°C       | SOIC-8  | Tape and Reel |

| FAN5009MPX  | 0°C to 85°C       | MLP-8   | Tape and Reel |

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Fairchild Semiconductor:

FAN5063M